# **Dual-Phase PWM Controller for GPU Core Power Supply**

### **General Description**

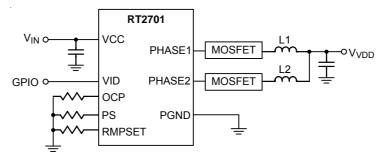

The RT2701 is a dual-phase synchronous Buck PWM controller with integrated drivers which are optimized for high performance graphic microprocessor and computer applications. The IC integrates a PWM controller, two 12V MOSFET drivers with internal bootstrap diodes, as well as output current monitoring and protection functions into the WQFN-24L 4x4 package. The RT2701 adopts DCR and R<sub>DS(ON)</sub> current sensing. Over current protection is accomplished through continuous inductor DCR current sensing, while R<sub>DS(ON)</sub> current sensing is used for accurate channel current balance. Using both methods of current sampling utilizes the best advantages of each technique. The RT2701 also features an one-bit VID control operation in which the feedback voltage is regulated and tracks external input reference voltage. Other features include adjustable operating frequency, external compensation and enable/shutdown functions.

### Ordering Information

### Note:

### Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- Dual-Phase PWM Controller

- Two Embedded MOSFET Drivers and Embedded **Switching Boot Diode**

- Dynamic Auto Phase Control with Adjustable **Threshold**

- Cross-talk Jitter Suspend (CJS<sup>™</sup>)

- Remote GND Detection for High Accuracy

- Automatic Diode Emulation Mode/Or Ultrasonic Mode at Light Load

- Lossless R<sub>DS(ON)</sub> Current Sensing for Current Balance

- Lossless DCR Current Sensing for AVP & OCP

- Reference Voltage Output with 1% Accuracy

- External Reference Input with Soft-Start (RISS)

- Embedded One-Bit VID Control

- Adjustable OCP Threshold

- Adjustable Switching Frequency

- Reference Tracking UVP/OVP Protection

- Shoot Through Protection and Short Pulse Free **Technology**

- RoHS Compliant and Halogen Free

### **Applications**

- · Middle to High End GPU Core Power

- High End Desktop PC Memory Core Power

- Low Voltage, High Current DC/DC Converter

- Voltage Regulator Modules

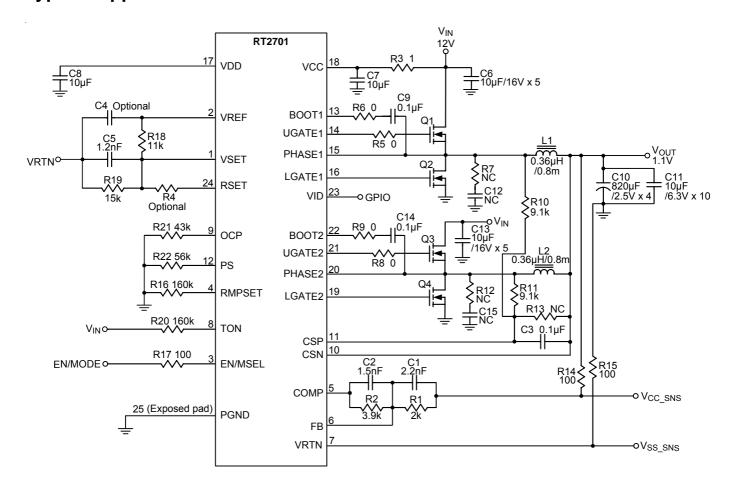

### Simplified Application Circuit

Copyright ©2013 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

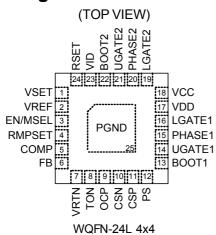

# **Pin Configurations**

# Marking Information 03=: Product Code

03=YM DNN YMDNN: Date Code

### **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                                |  |  |  |  |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | VSET     | Output Voltage Setting. Connect a voltage divider from VREF to VSET to set the output voltage.                                                                                                                                                                                              |  |  |  |  |

| 2       | VREF     | Reference Voltage Output (2V). The RT2701 generates a 2V reference voltage from VREF to VRTN.                                                                                                                                                                                               |  |  |  |  |

| 3       | EN/MSEL  | Enable Control Input and Mode Selection. This pin is a tri-state input. Pull up this pin to be higher than 4.2V, the controller operates in DEM mode. Pull up this pin to between 1.2V to 3V, the controller operates in ASM mode. Pull down this pin to GND, the controller will shutdown. |  |  |  |  |

| 4       | RMPSET   | Internal Ramp Slew Rate Setting. Connect a resistor ( $R_{RMP}$ ) from RMPSET to GND to the ramp slew rate. The value of $R_{RMP}$ must be set equal to $R_{TON}$ .                                                                                                                         |  |  |  |  |

| 5       | COMP     | Compensation Node. This pin is the output node of the error amplifier.                                                                                                                                                                                                                      |  |  |  |  |

| 6       | FB       | Feedback Voltage Input. This pin is the negative input node of the error amplifier.                                                                                                                                                                                                         |  |  |  |  |

| 7       | VRTN     | Remote Differential Feedback, Invert Input. This pin is the negative node of the differential remote voltage sensing.                                                                                                                                                                       |  |  |  |  |

| 8       | TON      | Switching Frequency Setting. Connect a resistor ( $R_{TON}$ ) from TON to VIN to set the switching frequency. The value of $R_{TON}$ must be set equal to $R_{RMP}$ .                                                                                                                       |  |  |  |  |

| 9       | ОСР      | OCP Level Setting. Connect a resistor from OCP to GND to set the current limit threshold.                                                                                                                                                                                                   |  |  |  |  |

| 10      | CSN      | Negative Input of Current Sensing.                                                                                                                                                                                                                                                          |  |  |  |  |

| 11      | CSP      | Positive Input of Current Sensing.                                                                                                                                                                                                                                                          |  |  |  |  |

| 12      | PS       | Dynamic Phase Control Input. Connect a resistor from PS to GND to set the auto down phase threshold.                                                                                                                                                                                        |  |  |  |  |

| 13      | BOOT1    | Bootstrap Supply for High Side MOSFET Driver of Phase1.                                                                                                                                                                                                                                     |  |  |  |  |

| 14      | UGATE1   | High Side Gate Driver of Phase1. Connect this pin to the Gate of high side MOSFET.                                                                                                                                                                                                          |  |  |  |  |

| 15      | PHASE1   | Return node of Phase1 High Side Driver. Connect this pin to the Source of high side MOSFET together with the drain of low side MOSFET and the inductor.                                                                                                                                     |  |  |  |  |

| 16      | LGATE1   | Low Side Gate Driver of Phase1. Connect this pin to the Gate of low side MOSFET.                                                                                                                                                                                                            |  |  |  |  |

| Pin No.             | Pin Name | Pin Function                                                                                                                                            |  |  |  |  |

|---------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 17                  | VDD      | Regulator Power for Internal Circuit. The regulated voltage provides power sup for all low voltage circuits.                                            |  |  |  |  |

| 18                  | VCC      | Supply Voltage Input. Connect this pin to GND by a ceramic cap larger than 1μF.                                                                         |  |  |  |  |

| 19                  | LGATE2   | Low Side Gate Driver of Phase2. Connect this pin to the Gate of low side MOSFET.                                                                        |  |  |  |  |

| 20                  | PHASE2   | Return node of Phase2 High Side Driver. Connect this pin to the Source of high side MOSFET together with the Drain low side of MOSFET and the inductor. |  |  |  |  |

| 21                  | UGATE2   | High Side Gate Driver of Phase2. Connect this pin to the Gate of high side MOSFET.                                                                      |  |  |  |  |

| 22                  | BOOT2    | Bootstrap Supply for High Side MOSFET Driver of Phase2.                                                                                                 |  |  |  |  |

| 23                  | VID      | Programming Output Voltage Control. When VID pin is logic high, internal N-MOSFET that connected to RSET pin is turn on.                                |  |  |  |  |

| 24                  | RSET     | Output Voltage Setting. Connect a resistor from RSET pin to VSET pin, the output voltage can be switched two levels by driving VID pin.                 |  |  |  |  |

| 25<br>(Exposed Pad) | PGND     | Power Ground. The exposed pad must be soldered to a large PCB and connected to PGND for maximum power dissipation.                                      |  |  |  |  |

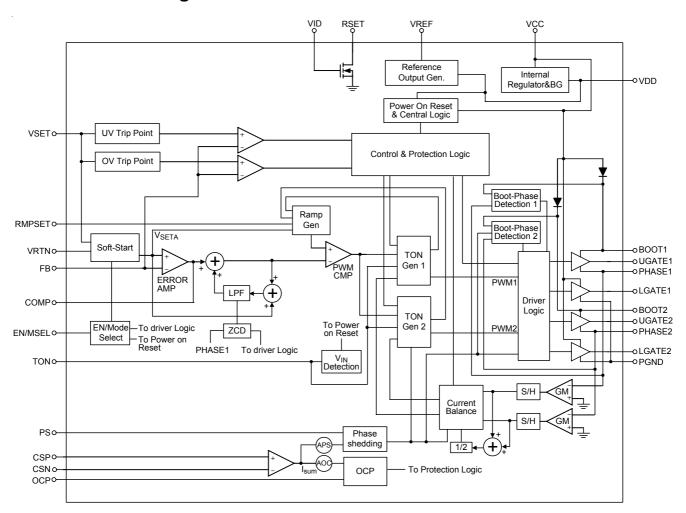

# **Function Block Diagram**

Copyright ©2013 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

### Operation

The RT2701 integrates a PWM controller, two 12V MOSFET drivers with internal bootstrap diodes, as well as output current monitoring and protection functions.

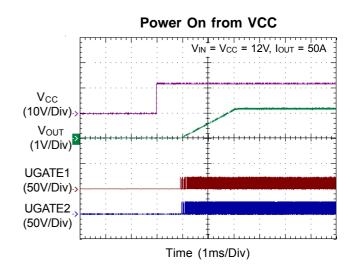

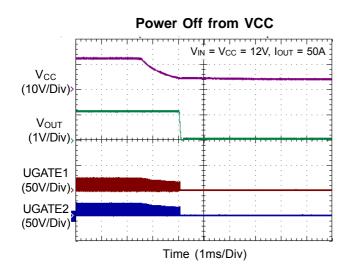

#### **Power On Reset**

The Power On Reset (POR) circuit monitors the supply voltage of the controller (VCC). When VCC exceeds the POR rising threshold, the controller will be enabled. If VCC falls below the POR falling threshold during normal operation, all MOSFETs stop switching. There is a hysteresis between the POR rising threshold and falling threshold to prevent noise mis-trigger.

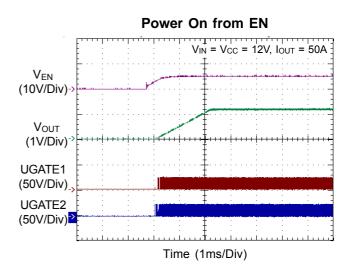

#### Soft-Start

An internal soft-start function is used to prevent large inrush current while converter is powered-up. The FB voltage will track the internal soft-start voltage during softstart interval. During the soft-start period, the controller will operate in dual-phase mode to ensure enough charge for output loads.

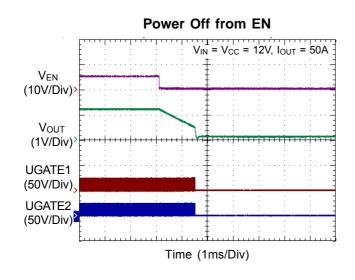

#### **EN/Mode Select**

The RT2701 supports DEM (Diode Emulation Mode) and ASM (Audio Skipping Mode) operation which can be enabled by EN/MSEL pin. When the EN/MSEL pin is pulled up above 4.2V, the controller will operate in DEM and reduce the switching frequency at light load conditions for saving power loss. If the EN/MSEL voltage is between 1.2V and 3V, the controller will operate in ASM. In ASM operation, the minimum switching frequency is limited to 30kHz to avoid acoustic noises. If the pin is pulled to GND, the RT2701 will be shut down.

#### **Current Balance**

The RT2701 implements internal current balance mechanism in the current loop. The RT2701 senses each phase current signal and compares it with the average current. If the sensed current of any particular phase is higher than average current, the on-time of this phase will be adjusted to be shorter.

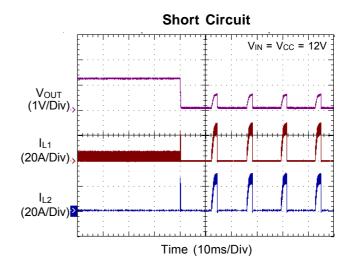

#### **OCP**

Once the sensed total current exceeds the current limit threshold, the driver will be forced to turn off the gate drivers for high side power MOSFETs. Until the OCP situation is removed.

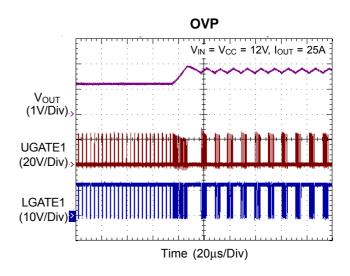

### **Over Voltage Protection**

The RT2701 monitors the output voltage via the CSN pin for Over Voltage Protection (OVP). Once the output voltage exceeds the OVP threshold, the controller will turn off high side MOSFETs and turn on low side MOSFETs to protect the load until the OVP situation is removed.

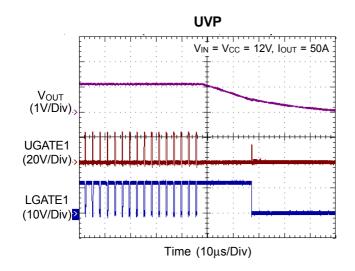

### **Under Voltage Protection**

The voltage on CSN pin is also monitored for Under Voltage Protection (UVP). If the output voltage is lower than the UVP threshold, the controller will turn off both high side and low side MOSFETs. When the UVP is triggered, the RT2701 will enter hiccup mode and continuously try to restart until the UVP situation is removed.

www.richtek.com

# **Absolute Maximum Ratings** (Note 1)

| <ul> <li>VDD, VSEN, COMP, VSET, VREF, EN/MSEL, PS, OCP, CSN,</li> </ul>     |                             |

|-----------------------------------------------------------------------------|-----------------------------|

| CSP, RSET, VID, RMPSET to PGND                                              | –0.3V to 6V                 |

| • VCC, TON to PGND                                                          | –0.3V to 15V                |

| VRTN to PGND                                                                | 0.3V to 0.3V                |

| • BOOTx to PHASEx                                                           | –0.3V to 15V                |

| PHASEx to PGND                                                              |                             |

| DC                                                                          | –3V to 15V                  |

| <20ns                                                                       | 5V to 30V                   |

| UGATEx to PHASEx                                                            |                             |

| DC                                                                          | 0.3V to BOOTx - PHASEx      |

| <20ns                                                                       | 5V to (BOOTx - PHASEx + 5V) |

| LGATEx to PGND                                                              |                             |

| DC                                                                          | 0.3V to PVCC+ 0.3V          |

| <20ns                                                                       | 5V to (VCC + 5V)            |

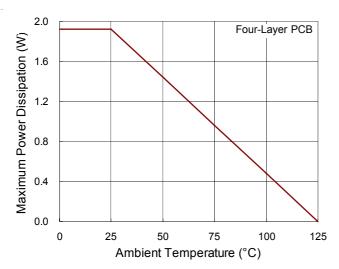

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                             |

| WQFN-24L 4x4                                                                | 1.923W                      |

| Package Thermal Resistance (Note 2)                                         |                             |

| WQFN-24L 4x4, $\theta_{JA}$                                                 | 52°C/W                      |

| WQFN-24L 4x4, $\theta_{JC}$                                                 | 7°C/W                       |

| Junction Temperature                                                        | 150°C                       |

| Lead Temperature (Soldering, 10 sec.)                                       | 260°C                       |

| Storage Temperature Range                                                   | –65°C to 150°C              |

| ESD Susceptibility (Note 3)                                                 |                             |

| HBM (Human Body Model)                                                      | 2kV                         |

|                                                                             |                             |

| Recommended Operating Conditions (Note 4)                                   |                             |

| Supply Voltage, VCC                                                         | 4.5V to 13.2V               |

| Junction Temperature Range                                                  | –40°C to 125°C              |

| Ambient Temperature Range                                                   | –40°C to 85°C               |

|                                                                             |                             |

### **Electrical Characteristics**

(V<sub>CC</sub> = 12V, No Load,  $T_A = -40^{\circ}C$  to 85°C, unless otherwise specified)

| Parameter                                     | Symbol                               | Test Conditions                                                                       | Min  | Тур | Max  | Unit      |  |  |  |

|-----------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------|------|-----|------|-----------|--|--|--|

| Supply Input                                  |                                      |                                                                                       |      |     |      |           |  |  |  |

| Supply Current                                | I <sub>VCC</sub> + I <sub>PVCC</sub> | EN = 3.3V, Not Switching                                                              |      | 3.5 | 5    | mA        |  |  |  |

| Shutdown Current                              | I <sub>CC</sub> + I <sub>PVCC</sub>  | EN = 0V                                                                               |      |     | 600  | μΑ        |  |  |  |

| Power On Reset                                |                                      |                                                                                       |      |     |      |           |  |  |  |

| VCC POR Threshold                             | Vvcc_th                              | VCC Rising                                                                            |      | 4.2 | 4.5  | V         |  |  |  |

| Power On Reset Hysteresis                     | V <sub>VCC_hys</sub>                 |                                                                                       |      | 0.3 |      | V         |  |  |  |

| Reference                                     |                                      |                                                                                       |      |     |      |           |  |  |  |

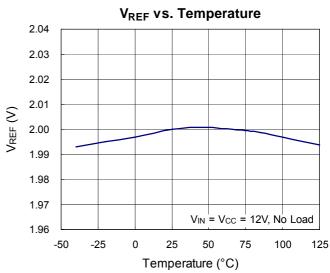

| Reference Output                              | V <sub>REF</sub>                     | (No Load, Active Mode )                                                               | 1.98 | 2   | 2.02 | V         |  |  |  |

| Reference Input Range                         | V <sub>SET</sub>                     | VSET pin (this max. voltage will affect V <sub>COMP</sub> max.)                       | 0.5  |     | 2    | V         |  |  |  |

| Start Up Delay                                |                                      |                                                                                       |      |     |      |           |  |  |  |

| Initial Soft-Start time                       | t <sub>b</sub>                       | Initially, V <sub>OUT</sub> = 0.1V to 1.2V                                            |      | 1.5 |      | ms        |  |  |  |

| Reference Change Delay Time                   | t <sub>c</sub>                       |                                                                                       |      | 300 |      | μS        |  |  |  |

| Error Amplifier                               |                                      |                                                                                       |      |     |      |           |  |  |  |

| Input Offset Voltage                          | Vosea                                |                                                                                       | -8   |     | 8    | mV        |  |  |  |

| DC Gain                                       |                                      | $R_L = 47k\Omega$                                                                     | 1    | 80  |      | dB        |  |  |  |

| Gain Bandwidth Product                        | GBW                                  | C <sub>LOAD</sub> = 5pF                                                               |      | 10  |      | MHz       |  |  |  |

| Slew Rate                                     | SR                                   | $C_{LOAD}$ = 10pF (Gain = -4,<br>R <sub>f</sub> = 47k, V <sub>OUT</sub> = 0.5V to 3V) | 1    | 5   | 1    | V/μs      |  |  |  |

| Output Voltage Range                          | V <sub>COMP</sub>                    | $R_L$ = 47k $\Omega$ (max. depend on VSET max.)                                       | 0.5  |     | 2    | V         |  |  |  |

| MAX Source Current                            | I <sub>OUTEA</sub>                   | V <sub>COMP</sub> = 2V                                                                |      | 250 |      | μΑ        |  |  |  |

| Current Sense Amplifier (f                    | or Droop and                         | OCP and Phase Shedding)                                                               |      |     |      |           |  |  |  |

| Input Offset Voltage                          | Voscs                                |                                                                                       | -2   |     | 2    | mV        |  |  |  |

| Impedance at Neg. Input                       | R <sub>CSN</sub>                     |                                                                                       | 1    |     |      | $M\Omega$ |  |  |  |

| Impedance at Pos Input                        | R <sub>CSP</sub>                     |                                                                                       | 1    |     |      | $M\Omega$ |  |  |  |

| Maximum Input Range                           | V <sub>CSP</sub> – V <sub>CSN</sub>  |                                                                                       | -    |     | 65   | mV        |  |  |  |

| TON Setting                                   |                                      |                                                                                       |      |     |      |           |  |  |  |

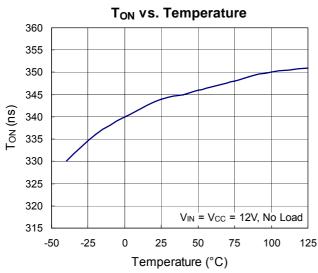

| On-Time Setting                               | t <sub>ON</sub>                      | I <sub>RTON</sub> = 62μA                                                              | 315  | 350 | 385  | ns        |  |  |  |

| Protection                                    |                                      |                                                                                       |      |     |      |           |  |  |  |

| Absolute Over Voltage<br>Protection Threshold | V <sub>OVABS</sub>                   | With Respect to V <sub>OUT(MAX)</sub>                                                 | 2.1  | 2.2 |      | V         |  |  |  |

| Relative Over Voltage<br>Protection Threshold | V <sub>REL_OV</sub>                  | With Respect to V <sub>OUT</sub>                                                      |      | 138 |      | %         |  |  |  |

| Parameter                                    | Symbol                                                                                                           | Test Conditions                                        |     | Тур | Max | Unit |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----|-----|-----|------|--|--|

| Under Voltage Protection Threshold           | ler Voltage Protection Threshold V <sub>UV</sub> Measured at VSENS with Respect to Unloaded Output Voltage (UOV) |                                                        |     | 50% |     | %    |  |  |

| Current Source by OCP Pin                    | IOCP                                                                                                             |                                                        | 7.2 | 8   | 8.8 | μΑ   |  |  |

| Logic Inputs                                 | Logic Inputs                                                                                                     |                                                        |     |     |     |      |  |  |

| EN Threshold Voltage                         | V <sub>IL</sub>                                                                                                  | Low Level (SD) (Hysteresis)                            |     |     | 0.5 | V    |  |  |

| EN Die Made Calact Valtage                   |                                                                                                                  | ASM Mode                                               | 1.2 |     | 3   | .,   |  |  |

| EN Pin Mode Select Voltage                   |                                                                                                                  | DEM Mode                                               | 4.5 |     |     | V    |  |  |

| Leakage Current of EN                        |                                                                                                                  | EN = 0V                                                | -1  |     | 5   | μΑ   |  |  |

| Auto Phase Control                           |                                                                                                                  |                                                        |     |     |     |      |  |  |

| Current Source by PSI Pin                    | IPS                                                                                                              |                                                        |     | 8   |     | μА   |  |  |

| Maximum Duty Cycle                           |                                                                                                                  |                                                        |     |     |     |      |  |  |

| UGATE Min. Off Time                          |                                                                                                                  |                                                        |     | 500 |     | ns   |  |  |

| Gate Driver                                  |                                                                                                                  |                                                        |     |     |     |      |  |  |

| Upper Driver Sink                            | R <sub>UGATEsk</sub> V <sub>UGATEx</sub> - V <sub>PHASEx</sub> = 0.1V,<br>I <sub>UGATEx</sub> = 50mA             |                                                        | 1   | 2   | 3.5 | Ω    |  |  |

| Lower Driver Sink                            | R <sub>LGATEsk</sub>                                                                                             | V <sub>LGATEX</sub> = 0.1V, I <sub>LGATEX</sub> = 50mA | 0.7 | 1.4 | 2.5 | Ω    |  |  |

| Internal Boost Charging Switch On-Resistance | R <sub>BOOT</sub>                                                                                                | PVCC to BOOTx                                          |     | 20  |     | Ω    |  |  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

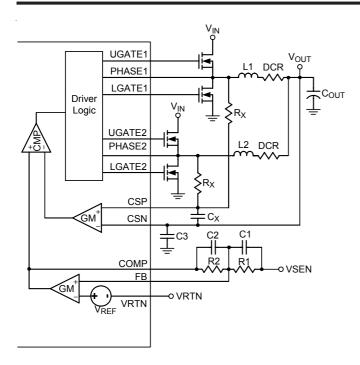

# **Typical Application Circuit**

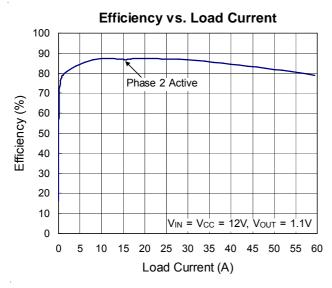

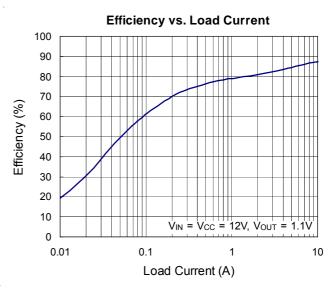

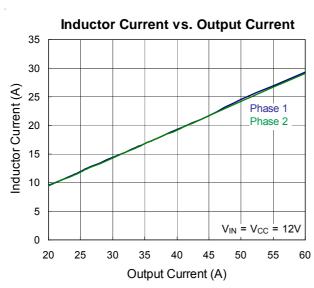

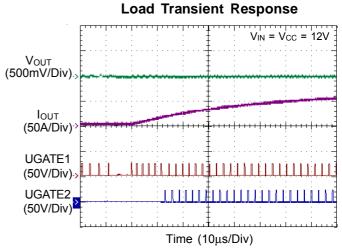

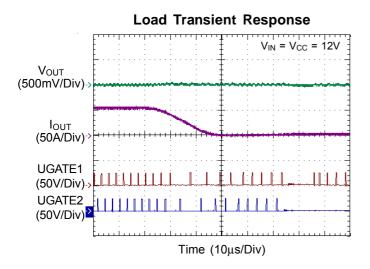

### **Typical Operating Characteristics**

Copyright ©2013 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

### **Application Information**

The RT2701 is a dual-phase synchronous Buck PWM controller with integrated drivers which is optimized for high-performance graphic microprocessor and computer applications. A COT (Constant-On-Time) PWM controller and two 12V MOSFET drivers with internal bootstrap diodes are integrated so that the external circuit can be easily designed and the component count can be reduced.

The IC also adopts lossless DCR and R<sub>DS(ON)</sub> current sensing. Dynamic phase control and current limit are accomplished through continuous inductor DCR current sensing, while R<sub>DS(ON)</sub> current sensing is used for accurate channel current balance.

Dynamic mode transition function with various operating states, which include dual-phase, single phase, diode emulation and audio skipping modes is supported. These different operating states make the system efficiency as high as possible.

A one-bit VID control operation in which the feedback voltage is regulated and tracks external input reference voltage is provided. The RT2701 also features complete fault protection functions including over voltage, under voltage and current limit.

### **DEM/ASM Mode Selection**

DEM (Diode Emulation Mode) and ASM (Audio Skipping Mode) operation can be enabled by driving the tri-state EN/MSEL pin to a logic high level. The RT2701 can switch operation into DEM when EN/MSEL pin is pulled up to above 4.2V. In DEM operation, the RT2701 automatically reduces the operation frequency at light load conditions for saving power loss. If EN/MSEL is pulled between 1.2V to 3V, the controller will switch operation into ASM. In ASM operation, the minimum switching frequency is limited to 30kHz to avoid the acoustic noise. Finally, if the pin is pulled to GND, the RT2701 will shutdown.

#### **Power On Reset**

The POR (power on reset) circuit monitors the supply voltage of the controller (V<sub>CC</sub>). When V<sub>CC</sub> exceeds the POR rising threshold, the controller will be enabled. During soft-start period, the output voltage will first boot to around 1V, and directly ramp to the set level. If V<sub>CC</sub> falls below the POR falling threshold during normal operation, all MOSFETs stop switching and the controller resets. The POR rising and falling threshold has a hysteresis to prevent noise mis-trigger.

#### Soft-Start

The RT2701 provides soft-start function. The soft-start function is used to prevent large inrush current while converter is being powered-up. The FB voltage will track the internal soft-start voltage during soft-start interval. Therefore, the duty cycle of the UGATE signal at power up as well as the input current limited. During the softstart period, the controller will be in dual-phase operation by default to ensure enough charge during start-up.

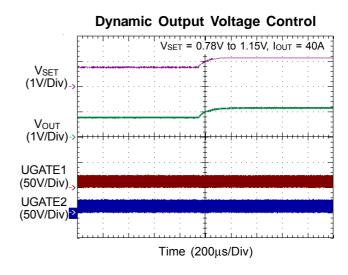

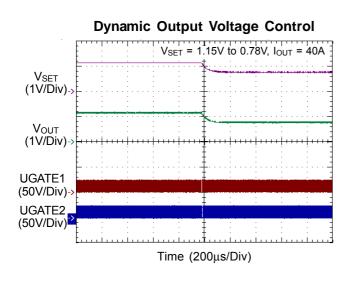

### One-Bit VID and Dynamic Output Voltage Control

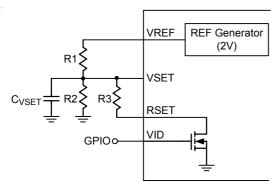

The output voltage is determined by the applied voltage on the VSET pin. The RT2701 generates a 2V reference voltage from VREF to VRTN. As shown in Figure 1, connecting a resistive divider from the VREF pin to the VSET pin can set the output voltage according to the equation below:

$$V_{OUT} = 2V \times \left(\frac{R2}{R1 + R2}\right)$$

The RT2701 also features a one-bit VID control through an internal N-MOSFET also shown in Figure 1. Connecting a resistor (R3) from RSET pin to VSET pin, the output voltage can be switched between two levels by controlling the VID pin. When the VID pin is logic high, the internal N-MOSFET turns on to set the output voltage to a lower level. The output voltage can be calculated as below:

$$V_{OUT} = 2V \times \left[ \frac{(R2//R3)}{R1 + (R2//R3)} \right]$$

The available setting range of the VSET voltage is from 0.5V to 2V.

### One-Bit VID and Dynamic Output Voltage Control

For the RT2701, it can be set lower than 10mV/µs by  $C_{VSET}$  as shown in Figure 1. That is, assume the  $\Delta V_{OUT}$  = 300mV, R1=11k $\Omega$ , R2 = R3 = 27k $\Omega$ , the desired slew rate at falling is  $SR_F = 10 \text{mV/}\mu\text{s}$ , and the  $C_{VSET}$  can be calculated by the formula below:

$$C_{VSET} = \frac{\Delta V_{OUT}}{5 \times (R1 \text{ // } R2 \text{ // } R3) \times SR_F} = 1nF$$

And then, the rising slew rate SR<sub>R</sub> will be

$$SR_{R} = \frac{\Delta V_{OUT}}{5 \times (R1 \text{ // } R2) \times C_{VSET}} = 7.67 \text{mV/} \mu \text{s}$$

Figure 1. Output Voltage Setting with One Bit VID

Control

### **Switching Frequency Setting**

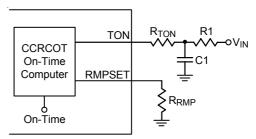

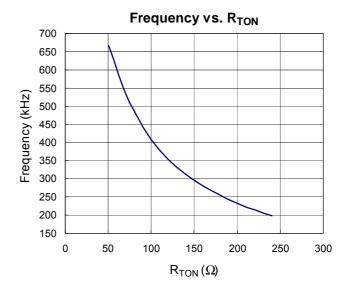

Switching frequency is a trade-off between efficiency and converter size. Higher operation frequency allows the use of smaller components. This is common in ultra portable devices where the load currents are lower and the controller is powered from a lower voltage supply. On the other hand, lower frequency operation offers higher overall efficiency at the expense of component size and board space. Figure 2 shows the On-Time Setting Circuit. Connect a resistor ( $R_{\text{TON}}$ ) from TON to  $V_{\text{IN}}$  and a resistor ( $R_{\text{RMP}}$ ) from RMPSET to GND to set the switching frequency according to the formula below :

$$R_{TON} = \frac{V_{IN} - V_{SET}}{f_S \times C \times V_{REF}} \times \frac{V_{SET} + I_L \times (R_{DS(ON)\_L-MOS} + R_{DC} - R_{LL})}{V_{IN} + I_L \times (R_{DS(ON)\_L-MOS} - R_{DS(ON)\_H-MOS})}$$

Where

fs: Switching frequency

R<sub>TON</sub>: TON setting resistor

C: Capacitance for on time compute (13.7pF)

V<sub>REF</sub>: Reference voltage for on time compute

IL: Inductor current

$R_{DS(ON)\_L\text{-}MOS}\colon R_{DS(ON)}$  of Low Side MOSFET

R<sub>DS(ON)</sub> H-MOS: R<sub>DS(ON)</sub> of High Side MOSFET

R<sub>DC</sub>: DCR of inductor

R<sub>LL</sub>: Load line resistance

The value of  $R_{TON}$  can be selected using Figure 3 and the value of  $R_{RMP}$  must be set equal to  $R_{TON}$ .

The current through  $R_{TON}$  should be set between  $30\mu A$  to  $280\mu A.$

Figure 2. On-Time Setting with RC Filter

Figure 3. Frequency vs. R<sub>TON</sub>

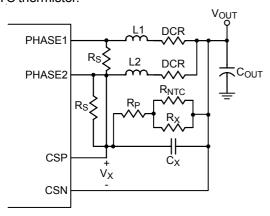

# Current Sense Setting (with Temperature Compensation)

The RT2701 uses continuous inductor current sensing to make the controller less noise sensitive. Low offset amplifiers are used for loop control and over current detection. The CSP and CSN denote the positive and negative input of the current sense amplifier of any phase. Since the DCR of the inductor is temperature dependent, it affects the down phase threshold, OCP threshold and output voltage accuracy, especially at heavy load. Temperature compensation is recommended for the lossless inductor DCR current sense method. Figure 4

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

shows a simple but effective way to compensate the unwanted temperature variations of the inductor DCR by using an NTC thermistor.

Figure 4. Inductor DCR Sensing

The RT2701 observes the voltage V<sub>X</sub>, across the CSP and CSN pins for inductor current information. To design V<sub>X</sub> without regard to the temperature coefficient, refer to the formula below:

$$\frac{DCR_{TH}}{DCR_{TL}} = \frac{2 + \frac{R_S}{R_{EQU\_TH}}}{2 + \frac{R_S}{R_{EQU\_TL}}}$$

(1)

where  $R_{EQU\ TH}$  is equal to  $R_P$  +  $R_{NTC}$  //  $R_X$  at high temperature and R<sub>EQU</sub> T<sub>L</sub> is equal to R<sub>P</sub> + R<sub>NTC</sub> // R<sub>X</sub> at low temperature. Usually, R<sub>X</sub> is set to equal R<sub>NTC</sub> (25°C). R<sub>P</sub> and R<sub>X</sub> are selected to linearize the NTC's temperature characteristic. For a given NTC and RP, the design is to first obtain  $R_S$  and then  $C_X$ . Usually, set  $R_X = R_{NTC}$ . To solve (1), R<sub>S</sub> must first be obtained as below:

$$R_{S} = \frac{2 (\alpha - 1)}{\frac{1}{R_{EQU\_TH}} - \frac{\alpha}{RE_{QU\_TL}}}$$

(2)

Where  $\alpha$  is equal to DCR<sub>TH</sub>/DCR<sub>TL</sub>

The standard formula for the resistance of the NTC thermistor as a function of temperature is given by :

$$R_{\text{NTC, T}^{\circ}\text{C}} = R_{25^{\circ}\text{C}} \times e^{\left\{\beta \left[ \left(\frac{1}{T+273}\right) - \left(\frac{1}{278}\right) \right] \right\}}$$

(3)

where R<sub>25°C</sub> is the thermistor's nominal resistance at room temperature,  $\beta$  (beta) is the thermistor's material constant in Kelvins, and T is the thermistor's actual temperature in Celsius.

To calculate DCR value at different temperatures, can use the equation below:

$$DCR_{T^{\circ}C} = DCR_{25^{\circ}C} \times [1 + 0.00393 \times (T - 25)]$$

(4)

where the 0.00393 is the temperature coefficient of copper.

C<sub>X</sub> can be obtained by below formula,

$$C_{X} = \frac{L \times \left(2 + \frac{R_{S}}{R_{EQU\_25^{\circ}C}}\right)}{R_{S} \times DCR_{25^{\circ}C}}$$

(5)

### **Loop Compensation**

Optimized compensation of the RT2701 allows for best possible load step response of the regulator's output. A type-I compensator with a single pole and single zero is adequate for a proper compensation. Figure 5 shows the compensation circuit. Prior design procedure shows how to determine the resistive feedback components of the error amplifier gain, C1 and C2 must be calculated for the compensation. The target is to achieve the constant resistive output impedance over the widest possible frequency, range. The pole frequency, fp, of the compensator must be set to compensate the output capacitor ESR zero:

$$f_{P} = \frac{1}{2\pi \times R_{C} \times C} \tag{6}$$

where C is the capacitance of the output capacitor, and R<sub>C</sub> is the ESR of output capacitor. C2 can be calculated as follows:

$$C2 = \frac{R_C \times C}{R2} \tag{7}$$

The zero of compensator has to be placed at half of the switching frequency to filter the switching related noise, such that,

$$C1 = \frac{1}{R1 \times \pi \times f_S} \tag{8}$$

Figure 5. Compensation Circuit

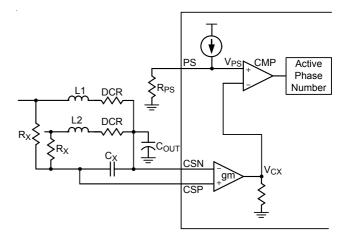

### **Dynamic Phase Number Control**

The RT2701 controls the operation phase number according to the total current. Figure 6 shows the dynamic phase number control circuit. By connecting a resistor ( $R_{PS}$ ) from the PS pin to GND, the phase transition threshold can be set. The formula is :

$$R_{PS} = \frac{DCR \times I_{SUM} \times 5}{1\mu}$$

where  $I_{SUM}$  is the sum of the inductor valley current. For example, if DCR is  $0.74m\Omega$ , and the desired up phase threshold is 15A, the value of  $R_{PS}$  will be

$$R_{PS} = \frac{0.74 \times 10^{-3} \times 15 \times 5}{1 \times 10^{-6}} = 55.5 k\Omega$$

Once the total inductor valley current is higher than the threshold, the controller will transit to dual-phase operation. when the total current becomes lower than the setting threshold minus around 5A hysteresis, the active phase number will return to single phase. If the PS pin is set floating, the controller will force to dual-phase operation.

Figure 6. Dynamic Phase Number Control Circuit

#### **Current Balance**

The RT2701 implements internal current balance mechanism in the current loop. The RT2701 senses per phase current signal and compares it with the average current. If the sensed current of any particular phase is higher than average current, the on-time of this phase will be adjusted to be shorter.

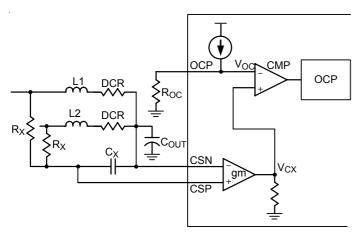

### **Current Limit Setting**

The RT2701 includes a built-in current limit protection function. Figure 7 shows the protection circuit. The current limit threshold is adjusted by an external resistor,  $R_{OC}$ , at the OCP pin. The value of  $R_{OC}$  can be set according to the following formula :

$$R_{OC} = \frac{DCR \times I_{SUM} \times 6}{8\mu}$$

where  $I_{\text{SUM}}$  is the desired current limit threshold. Once the sensed total current exceeds the current limit threshold, the driver will be forced to turn off UGATE until the OCP situation is removed.

Copyright © 2013 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

Figure 7. Over Current Protection Circuit

### **Over Voltage Protection**

The RT2701 monitors the output voltage via the CSN pin for Over Voltage Protection (OVP). Once the output voltage exceeds the OVP threshold, OVP is triggered. The RT2701 will turn on low side MOSFETs and turn off high side MOSFETs to protect the load until the OVP situation is removed. A 4µs delay is used in the OVP detection circuit to prevent false trigger.

### **Under Voltage Protection**

The voltage on CSN pin is also monitored for under voltage protection. If the output voltage is lower than the UVP threshold, UVP will be triggered. The RT2701 will then turn off both high side and low side MOSFETs. When UVP is triggered, the RT2701 will enter hiccup mode and continuously try to restart until the UVP situation is cleared.

### **Inductor Selection**

The switching frequency and ripple current determine the inductor value as follows:

$$L_{(MIN)} = \frac{V_{IN} - V_{OUT}}{I_{RIPPLE(MAX)}} \times T_{ON}$$

where T<sub>ON</sub> is the UGATE turn on period.

Higher inductance results in lower ripple current and higher efficiency but brings slower load transient response. Thus, more output capacitors may be required. The lower DC resistance can reduce power loss. The core must be large enough and not to be saturated at the peak inductor current.

### **Output Capacitor Selection**

Output capacitors are used to maintain high performance for the output beyond the bandwidth of the converter itself. Two different kinds of output capacitors can be found, bulk capacitors closely located to the inductors and ceramic output capacitors close to the load. The latter are for mid-frequency decoupling with especially small ESR and ESL values while the bulk capacitors have to provide enough stored energy to overcome the low-frequency bandwidth gap between the regulator and the GPU.

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WQFN-24L 4x4 package, the thermal resistance,  $\theta_{JA}$ , is 52°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by the following formula:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (52^{\circ}C/W) = 1.923W$$

for

WQFN-24L 4x4 package

The maximum power dissipation depends on the operating ambient temperature for fixed T<sub>J(MAX)</sub> and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 8 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 8. Derating Curve of Maximum Power Dissipation

### **Layout Considerations**

Careful PC board layout is critical to achieving low switching losses and clean, stable operation. The switching power stage requires particular attention. If possible, mount all of the power components on the top side of the board with their ground terminals flushed against one another. Follow these guidelines for optimum PC board layout:

- Keep the high current paths short, especially at the ground terminals.

- Keep the power traces and load connections short. This is essential for high efficiency.

- When trade-offs in trace lengths must be made, it's preferable to allow the inductor charging path to be made longer than the discharging path.

- Place the current sense components close to the controller. CSP and CSN connections for current limit and voltage positioning must be made using Kelvin sense connections to guarantee the current sense accuracy. The PCB trace from the sense nodes should be paralleled back to the controller.

- Route high speed switching nodes away from sensitive analog areas (COMP, FB, CSP, CSN, etc...)

Copyright © 2013 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

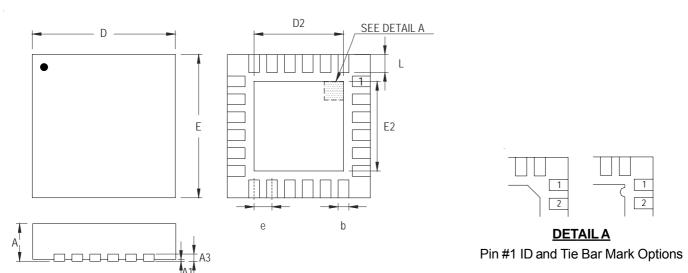

### **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol |          | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|----------|--------------|---------------|----------------------|-------|--|

|        |          | Min          | Max           | Min                  | Max   |  |

| Α      |          | 0.700        | 0.800         | 0.028                | 0.031 |  |

|        | A1       | 0.000        | 0.050         | 0.000                | 0.002 |  |

| A3     |          | 0.175        | 0.250         | 0.007                | 0.010 |  |

|        | b        | 0.180        | 0.300         | 0.007                | 0.012 |  |

|        | D        | 3.950        | 4.050         | 0.156                | 0.159 |  |

| D2     | Option 1 | 2.400        | 2.500         | 0.094                | 0.098 |  |

| D2     | Option 2 | 2.650        | 2.750         | 0.104                | 0.108 |  |

| E      |          | 3.950        | 4.050         | 0.156                | 0.159 |  |

| E2     | Option 1 | 2.400        | 2.500         | 0.094                | 0.098 |  |

| E2     | Option 2 | 2.650        | 2.750         | 0.104                | 0.108 |  |

| е      |          | 0.500        |               | 0.020                |       |  |

| L      |          | 0.350        | 0.450         | 0.014                | 0.018 |  |

W-Type 24L QFN 4x4 Package

### **Richtek Technology Corporation**

5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Richtek manufacturer:

Other Similar products are found below:

EVB\_RT5047GSP EVB\_RT7275GQW EVB\_RT7297CHZSP RT9080N-08GJ5 EVB\_RT5047AGSP EVB\_RT7243GQW

EVB\_RT7272BGSP RT8097AHGE EVB\_RT7247CHGSP EVB\_RT7276GQW EVB\_RT8293AHZSP EVB\_RT6200GE

EVB\_RT7235GQW EVB\_RT7237AHGSP EVB\_RT7251AZQW RT5047AGSP EVB\_RT7272AGSP EVB\_RT7237CHGSP

EVB\_RT7247AHGSP EVB\_RT7252BZSP EVB\_RT7280GQW EVB\_RT8292AHZSP EVB\_RT8297BZQW EVB\_RT7231GQW

EVB\_RT7232GQW EVB\_RT7236GQW EVB\_RT7250BZSP EVB\_RT7251BZQW EVB\_RT7279GQW EVB\_RT8008GB RT8207MZQW

RT8296AHZSP RT9011-JGPJ6 RT8258GE RT5711AHGQW RT9081AGQZA(2) RT6154BGQW RT7238BGQUF RT5788AGJ8F

RT8812AGQW RT6278BHGQUF RT7270HZSP RD0004 RT5789AGQUF RT9076-18GVN RT9193-15GU5 RT3602AJGQW

RT8296BHZSP RT6214AHGJ6F RT9276GQW(Z00)