### Standard 8K x 8 SRAM

#### **Features**

### ☐ 8192 x 8 bit static CMOS RAM ¬ 70 ns Access Times Common data inputs and outputs ☐ Three-state outputs ☐ Typ. operating supply current 70 ns: 10 mA ☐ Standby current: < 2 $\mu$ A at $T_a \le 70$ °C Data retention current at 2 V: < 1 μA at T<sub>a</sub> ≤ 70 °C ☐ TTL/CMOS-compatible Automatic reduction of power dissipation in long Read or Write ☐ Power supply voltage 5 V ☐ Operating temperature ranges: 0 to 70 °C -40 to 85 °C -40 to 125 °C QS 9000 Quality Standard ☐ ESD protection > 2000 V (MIL STD 883C M3015.7) ☐ Latch-up immunity > 100 mA

☐ Packages: PDIP28 (600 mil)

SOP28 (330 mil)

#### **Description**

The U6264B is a static RAM manufactured using a CMOS process technology with the following operating modes:

- Read Standby

- Write Data Retention

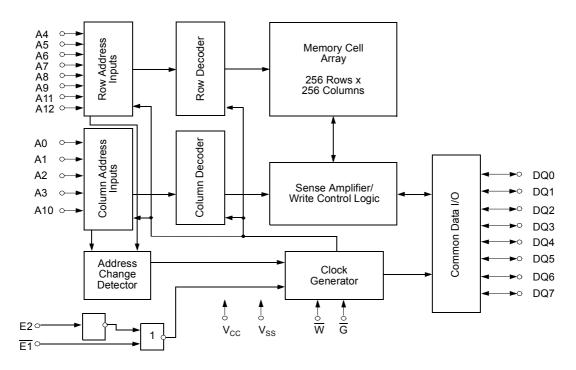

The memory array is based on a 6-transistor cell.

The circuit is activated by the rising edge of E2 (at E1 = L), or the falling edge of E1 (at E2 = H). The address and control inputs open simultaneously. According to the information of W and G, the data inputs, or outputs, are active. In a Read cycle, the data outputs are activated by the falling edge of  $\overline{G}$ , afterwards the data word read will be available at the outputs DQ0 -DQ7. After the address change, the data outputs go High-Z until the new read information is available. The data outputs have no preferred state. If the memory is driven by CMOS levels in the active state, and if there is no change of the

address, data input and control signals  $\overline{W}$  or  $\overline{G}$ , the operating current (at  $I_O = 0$  mA) drops to the value of the operating current in the Standby mode. The Read cycle is finished by the falling edge of  $\overline{E}$ 2 or  $\overline{W}$ , or by the rising edge of  $\overline{E}$ 1, respectively.

Data retention is guaranteed down to 2 V. With the exception of E2, all inputs consist of NOR gates, so that no pull-up/pull-down resistors are required. This gate circuit allows to achieve low power standby requirements by activation with TTL-levels too.

If the circuit is inactivated by E2 = L, the standby current (TTL) drops to 150  $\mu$ A typ.

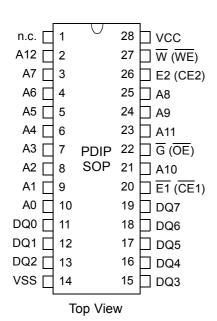

#### **Pin Configuration**

#### **Pin Description**

| Signal Name | Signal Description   |

|-------------|----------------------|

| A0 - A12    | Address Inputs       |

| DQ0 - DQ7   | Data In/Out          |

| E1          | Chip Enable 1        |

| E2          | Chip Enable 2        |

| G           | Output Enable        |

| W           | Write Enable         |

| VCC         | Power Supply Voltage |

| VSS         | Ground               |

| n.c.        | not connected        |

### **Block Diagram**

## **Truth Table**

| Operating Mode        | E1 | E2 | w | G | DQ0 - DQ7          |  |

|-----------------------|----|----|---|---|--------------------|--|

| Standby/not selected  | *  | L  | * | * | High-Z             |  |

| Standby/flot selected | Н  | *  | * | * | High-Z             |  |

| Internal Read         | L  | Н  | Н | Н | High-Z             |  |

| Read                  | L  | Н  | Н | L | Data Outputs Low-Z |  |

| Write                 | L  | Н  | L | * | Data Inputs High-Z |  |

\* H or L

#### **Characteristics**

All voltages are referenced to  $V_{SS} = 0 \text{ V (ground)}$ .

All characteristics are valid in the power supply voltage range and in the operating temperature range specified. Dynamic measurements are based on a rise and fall time of  $\leq 5$  ns, measured between 10 % and 90 % of  $V_I$ , as well as input levels of  $V_{IL} = 0$  V and  $V_{IH} = 3$  V. The timing reference level of all input and output signals is 1.5 V, with the exception of the  $t_{dis}$ -times, in which cases transition is measured  $\pm$  200 mV from steady-state voltage.

| Absolute Maximum Ratir                                                       | ngs <sup>a</sup>           | Symbol           | Min.            | Max.                               | Unit           |

|------------------------------------------------------------------------------|----------------------------|------------------|-----------------|------------------------------------|----------------|

| Power Supply Voltage                                                         |                            | V <sub>CC</sub>  | -0.3            | 7                                  | V              |

| Input Voltage                                                                |                            | V <sub>I</sub>   | -0.3            | V <sub>CC</sub> + 0.5 <sup>b</sup> | V              |

| Output Voltage                                                               |                            | V <sub>O</sub>   | -0.3            | V <sub>CC</sub> + 0.5 <sup>b</sup> | V              |

| Power Dissipation                                                            |                            | P <sub>D</sub>   | -               | 1                                  | W              |

| Operating Temperature                                                        | C-Type<br>K-Type<br>A-Type | T <sub>a</sub>   | 0<br>-40<br>-40 | 70<br>85<br>125                    | °C<br>°C<br>°C |

| Storage Temperature                                                          | C/K-Type<br>A-Type         | T <sub>stg</sub> | -55<br>-65      | 125<br>150                         | °C<br>°C       |

| Output Short-Circuit Curre at V <sub>CC</sub> = 5 V and V <sub>O</sub> = 0 V |                            | I <sub>os</sub>  |                 | 100                                | mA             |

<sup>&</sup>lt;sup>a</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability

<sup>&</sup>lt;sup>c</sup> Not more than 1 output should be shorted at the same time. Duration of the short circuit should not exceed 30 s.

| Recommended Operating Conditions | Symbol              | Conditions | Min. | Max.                  | Unit |

|----------------------------------|---------------------|------------|------|-----------------------|------|

| Power Supply Voltage             | V <sub>CC</sub>     |            | 4.5  | 5.5                   | V    |

| Data Retention Voltage           | V <sub>CC(DR)</sub> |            | 2.0  |                       | V    |

| Input Low Voltage d              | V <sub>IL</sub>     |            | -0.3 | 0.8                   | V    |

| Input High Voltage               | V <sub>IH</sub>     |            | 2.2  | V <sub>CC</sub> + 0.3 | V    |

d -2 V at Pulse Width 10 ns

<sup>&</sup>lt;sup>b</sup> Maximum voltage is 7 V

# U6264B

| <b>Electrical Characteristics</b>                     | Symbol               | Symbol Conditions                                                                                                                                 |                                                   | Min.     | Max.          | Unit           |

|-------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------|---------------|----------------|

| Supply Current - Operating Mode                       | I <sub>CC(OP)</sub>  | V <sub>CC</sub><br>V <sub>IL</sub><br>V <sub>IH</sub><br>t <sub>cW</sub>                                                                          | = 5.5 V<br>= 0.8 V<br>= 2.2 V<br>= 70 ns          |          | 55            | mA             |

| Supply Current - Standby Mode (CMOS level)            | I <sub>CC(SB)</sub>  | $V_{CC}$ $V_{\overline{E}1} = V_{E2}$ or $V_{E2}$ C-Type K-Type A-Type                                                                            | = 5.5 V<br>= V <sub>CC</sub> - 0.2 V<br>= 0.2 V   |          | 2<br>5<br>100 | μΑ<br>μΑ<br>Αμ |

| Supply Current - Standby Mode (TTL level)             | I <sub>CC(SB)1</sub> | $V_{CC}$ $V_{\overline{E1}} = V_{E2}$ or $V_{E2}$                                                                                                 | = 5.5 V<br>= 2.2 V<br>= 0.8 V                     |          | 3             | mA             |

| Supply Current - Data Retention<br>Mode               | I <sub>CC(DR)</sub>  | $V_{\text{CC(DR)}} \\ V_{\overline{\text{E1}}} = V_{\text{E2}} \\ \text{or } V_{\text{E2}} \\ \text{C-Type} \\ \text{K-Type} \\ \text{A-Type} \\$ | = 2 V<br>= V <sub>CC(DR)</sub> - 0.2 V<br>= 0.2 V |          | 1<br>3<br>50  | μΑ<br>μΑ<br>μΑ |

| Output High Voltage                                   | V <sub>OH</sub>      | V <sub>CC</sub>                                                                                                                                   | = 4.5 V<br>= -1.0 mA                              | 2.4      |               | V              |

| Output Low Voltage                                    | V <sub>OL</sub>      | I <sub>OH</sub><br>V <sub>CC</sub><br>I <sub>OL</sub>                                                                                             | = 4.5 V<br>= 3.2 mA                               |          | 0.4           | V              |

| Output High Current                                   | I <sub>OH</sub>      | V <sub>CC</sub>                                                                                                                                   | = 4.5 V<br>= 2.4 V                                |          | -1            | mA             |

| Output Low Current                                    | I <sub>OL</sub>      | V <sub>OH</sub><br>V <sub>CC</sub><br>V <sub>OL</sub>                                                                                             | = 4.5 V<br>= 0.4 V                                | 3.2      |               | mA             |

| Input Leakage Current<br>High                         | I <sub>IH</sub>      | V <sub>CC</sub><br>V <sub>IH</sub><br>C/K-Type<br>A-Type                                                                                          | = 5.5 V<br>= 5.5 V                                | -<br>-   | 1 2           | μΑ<br>μΑ       |

| Low                                                   | I <sub>IL</sub>      | V <sub>CC</sub><br>V <sub>IL</sub><br>C/K-Type<br>A-Type                                                                                          | = 5.5 V<br>= 0 V                                  | -1<br>-2 | -<br>-        | μΑ<br>μΑ       |

| Output Leakage Current<br>High at Three-State Outputs | Гонz                 | V <sub>CC</sub><br>V <sub>OH</sub><br>C/K-Type<br>A-Type                                                                                          | = 5.5 V<br>= 5.5 V                                | -<br>-   | 1 2           | μΑ<br>μΑ       |

| Low at Three-State Outputs                            | I <sub>OLZ</sub>     | V <sub>CC</sub><br>V <sub>OL</sub><br>C/K-Type<br>A-Type                                                                                          | = 5.5 V<br>= 0 V                                  | -1<br>-2 | -<br>-        | μΑ<br>μΑ       |

| Switching Characteristics                                                                    | Syı                                                                      | mbol                                                                            |                     |                |                      |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------|----------------|----------------------|

| Switching Characteristics                                                                    | Alt.                                                                     | IEC                                                                             | Min.                | Max.           | Unit                 |

| Time to Output in Low-Z                                                                      | t <sub>LZ</sub>                                                          | t <sub>t(QX)</sub>                                                              | 5                   | 10             | ns                   |

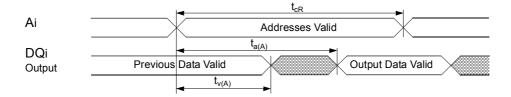

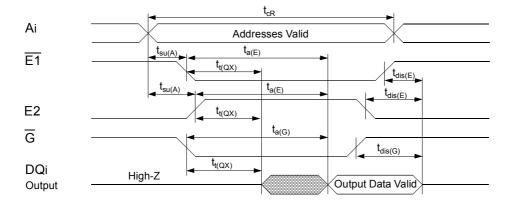

| Cycle Time Write Cycle Time Read Cycle Time                                                  | t <sub>wc</sub>                                                          | t <sub>cW</sub><br>t <sub>cR</sub>                                              | 70<br>70            |                | ns<br>ns             |

| Access Time E1 LOW or E2 HIGH to Data Valid G LOW to Data Valid Address to Data Valid        | t <sub>ACE</sub><br>t <sub>OE</sub><br>t <sub>AA</sub>                   | t <sub>a(E)</sub><br>t <sub>a(G)</sub><br>t <sub>a(A)</sub>                     | -<br>-<br>-         | 70<br>40<br>70 | ns<br>ns<br>ns       |

| Pulse Widths Write Pulse Width Chip Enable to End of Write                                   | t <sub>WP</sub><br>t <sub>CW</sub>                                       | t <sub>w(W)</sub> t <sub>w(E)</sub>                                             | 50<br>65            |                | ns<br>ns             |

| Setup Times Address Setup Time Chip Enable to End of Write Write Pulse Width Data Setup Time | t <sub>AS</sub><br>t <sub>CW</sub><br>t <sub>WP</sub><br>t <sub>DS</sub> | $\begin{array}{c} t_{su(A)} \\ t_{su(E)} \\ t_{su(W)} \\ t_{su(D)} \end{array}$ | 0<br>65<br>50<br>35 |                | ns<br>ns<br>ns<br>ns |

| Data Hold Time<br>Address Hold from End of Write                                             | t <sub>DH</sub><br>t <sub>AH</sub>                                       | t <sub>h(D)</sub><br>t <sub>h(A)</sub>                                          | 0                   |                | ns<br>ns             |

| Output Hold Time from Address Change                                                         | t <sub>OH</sub>                                                          | t <sub>v(A)</sub>                                                               | 5                   |                | ns                   |

| E1 HIGH or E2 LOW to Output in High-Z W LOW to Output in High-Z                              | t <sub>HZCE</sub>                                                        | t <sub>dis(E)</sub>                                                             | 0                   | 25             | ns                   |

| G HIGH to Output in High-Z                                                                   | t <sub>HZWE</sub><br>t <sub>HZOE</sub>                                   | t <sub>dis(W)</sub><br>t <sub>dis(G)</sub>                                      | 0<br>0              | 30<br>25       | ns<br>ns             |

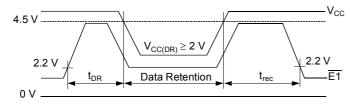

# Data Retention Mode E1-Controlled

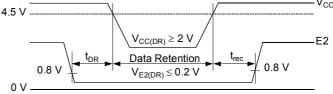

#### **Data Retention Mode E2-Controlled**

$$\begin{split} &V_{E2(DR)} \geq V_{CC(DR)} \text{ - } 0.2 \text{ V or } V_{E2(DR)} \leq 0.2 \text{ V} \\ &V_{CC(DR)} \text{ - } 0.2 \text{ V} \leq V_{E1(DR)} \leq V_{CC(DR)} \text{ + } 0.3 \text{ V} \end{split}$$

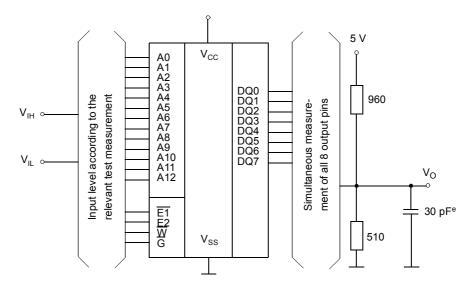

#### **Test Configuration for Functional Check**

$<sup>^{\</sup>text{e}}$  In measurement of  $t_{\text{dis}(E)},\,t_{\text{dis}(W)},\,t_{\text{dis}(G)}$  the capacitance is 5 pF.

| Capacitance        | Conditions                                | Symbol         | Min. | Max. | Unit |

|--------------------|-------------------------------------------|----------------|------|------|------|

| Input Capacitance  | $V_{CC} = 5.0 \text{ V}$ $V_{I} = V_{SS}$ | C <sub>I</sub> |      | 8    | pF   |

| Output Capacitance | f = 1 MHz<br>T <sub>a</sub> = 25 °C       | C <sub>O</sub> |      | 10   | pF   |

All pins not under test must be connected with ground by capacitors.

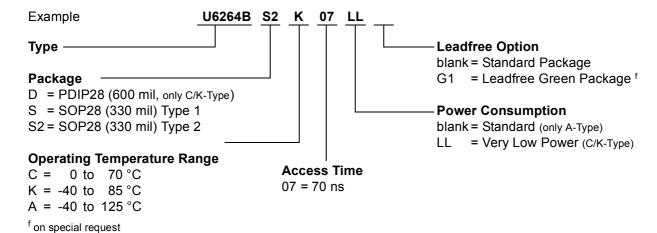

#### **Ordering Code**

# Read Cycle 1 (during Read cycle: $\overline{E1} = \overline{G} = V_{IL}$ , $E2 = \overline{W} = V_{IH}$ )

# Read Cycle 2 (during Read cycle: $\overline{W} = V_{IH}$ )

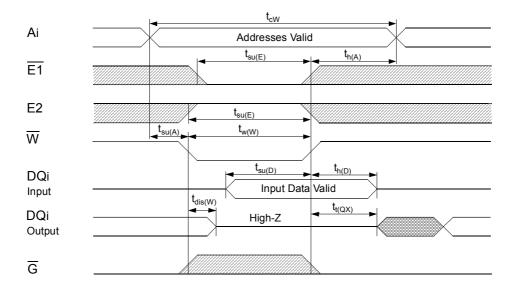

# Write Cycle 1 (W-controlled)

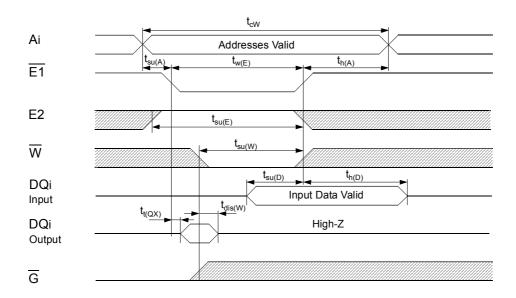

## Write Cycle 2 (E1-controlled)

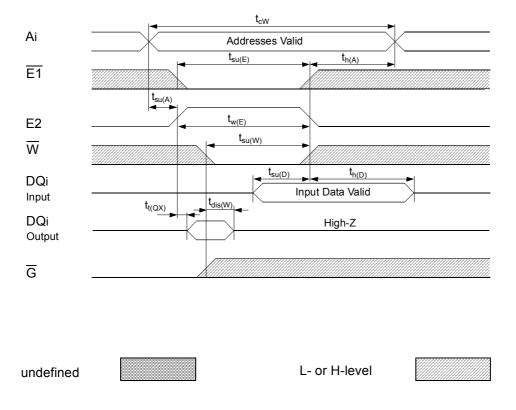

### Write Cycle 3 (E2-controlled)

The information describes the type of component and shall not be considered as assured characteristic. Terms of delivery and rights to change design reserved.

#### LIFE SUPPORT POLICY

ZMD products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the ZMD product could create a situation where personal injury or death may occur. Components used in life-support devices or systems must be expressly authorized by ZMD for such purpose.

#### LIMITED WARRANTY

The information in this document has been carefully checked and is believed to be reliable. However Zentrum Mikroelektronik Dresden AG (ZMD) makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon it. The information in this document describes the type of component and shall not be considered as assured characteristics.

ZMD does not guarantee that the use of any information contained herein will not infringe upon the patent, trademark, copyright, mask work right or other rights of third parties, and no patent or licence is implied hereby. This document does not in any way extent ZMD's warranty on any product beyond that set forth in its standard terms and conditions of sale.

ZMD reserves terms of delivery and reserves the right to make changes in the products or specifications, or both, presented in this publication at any time and without notice.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for SRAM category:

Click to view products by Alliance Memory manufacturer:

Other Similar products are found below:

5962-8855206XA CY6116A-35DMB CY7C1049GN-10VXI CY7C128A-45DMB CY7C1461KV33-133AXI CY7C199-45LMB

GS88237CB-200I R1QDA7236ABB-20IB0 RMLV0408EGSB-4S2#AA0 MT41K256M16HA-125:E IS64WV3216BLL-15CTLA3

IS66WVE4M16ECLL-70BLI PCF8570P K6T4008C1B-GB70 CY7C1353S-100AXC AS6C8016-55BIN AS7C164A-15PCN 515712X

IS62WV51216EBLL-45BLI IS63WV1288DBLL-10HLI IS66WVE2M16ECLL-70BLI UPD43256BCZ-85-LL KE 1368 433750H 47L16E/SN 621488F IS66WVE4M16EALL-70BLI IS62WV6416DBLL-45BLI IS61WV102416DBLL-10TLI CY7C1381KV33-100AXC

CY7C1381KV33-100BZXI CY7C1373KV33-100AXC CY7C1381KVE33-133AXI CY7C1382KV33-167AXC CY7C4042KV13-933FCXC

CY7S1041GE30-10BVXI 8602501XA 5962-8855206YA 5962-8866201YA 5962-8866204TA 5962-8866207NA 5962-8959841MZA

7130LA100PDG GS882Z18CD-150I GS81284Z36B-250I M38510/28902BVA 5962-8971203XA 5962-8971202ZA 5962-8872501LA 5962-8866208YA