## 500mA, 80V, 350kHz Synchronous Step-Down Converter

### **General Description**

The RT6210 is a 80V, 500mA, 350kHz, high-efficiency, synchronous step-down DC-DC converter with an inputvoltage range of 5.2V to 80V and a programmable outputvoltage range of 0.8V to 72V. It features current-mode control to simplify external compensation and to optimize transient response with a wide range of inductors and output capacitors. High efficiency can be achieved through integrated N-MOSFETs, and pulse-skipping mode at light loads. With EN pin, power-up sequence can be more flexible and shutdown quiescent current can be reduced to <  $3\mu$ A.

The RT6210 features cycle-by-cycle current limit for overcurrent protection against short-circuit outputs, and userprogrammable soft-start time to prevent inrush current during startup. It also includes input under-voltage lockout, output under-voltage, and thermal shutdown protection to provide safe and smooth operation in all operating conditions.

The RT6210 is available in the SOP-8 (Exposed pad) package.

### Features

- 0.8V Feedback Reference Voltage with ±1.5% Accuracy

- Wide Input Voltage Range : 5.2V to 80V

- Output Current : 500mA

- Integrated N-MOSFETs

- Current-Mode Control

- Fixed Switching Frequency : 350kHz

- Programmable Output Voltage : 0.8V to 72V

- Low < 3µA Shutdown Quiescent Current

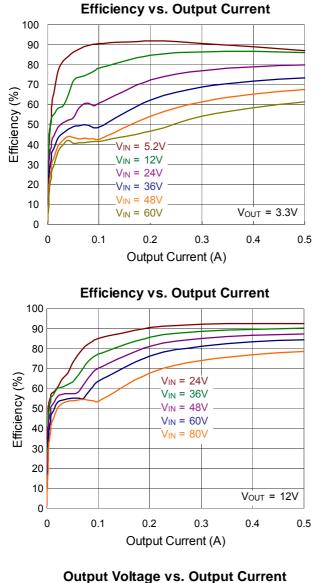

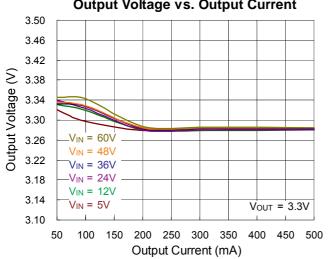

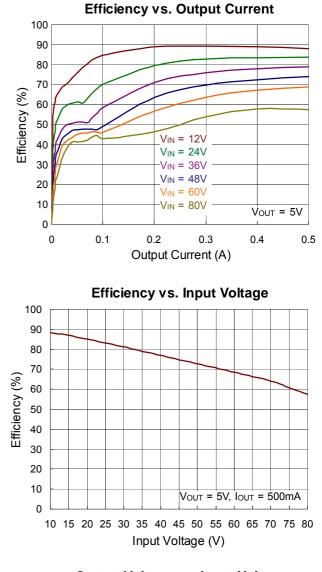

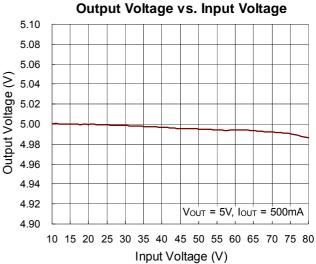

- Up to 92% Efficiency

- Pulse-Skipping Mode for Light-Load Efficiency

- Programmable Soft-Start Time

- Cycle-by-Cycle Current Limit Protection

- Input Under-Voltage Lockout, Output Under-Voltage and Thermal Shutdown Protection

### **Applications**

- 4-20mA Loop-Powered Sensors

- OBD-II Port Power Supplies

- Low-Power Standby or Bias Voltage Supplies

- Industrial Process Control, Metering, and Security Systems

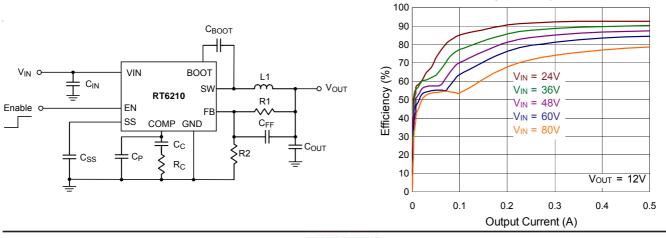

Efficiency vs. Output Current

- High-Voltage LDO Replacement

- Telecommunications Systems

- Commercial Vehicle Power Supplies

- General Purpose Wide Input Voltage Regulation

**Simplified Application Circuit**

### **Ordering Information**

RT6210

Package Type SP: SOP-8 (Exposed Pad-Option 2)

> Lead Plating System G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

```

RT6210

GSPYMDNN

```

RT6210GSP : Product Number

YMDNN : Date Code

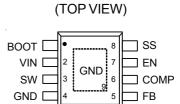

### **Pin Configuration**

SOP-8 (Exposed Pad)

| Pin No.               | Pin Name | Pin Function                                                                                                                                                                                                                                                                                |

|-----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | BOOT     | Bootstrap capacitor connection node for high-side gate driver. Connect a $0.1 \mu F$ ceramic capacitor from BOOT to SW to power the internal gate driver.                                                                                                                                   |

| 2                     | VIN      | Supply voltage input, 5.2V to 80V. Bypass VIN to GND with a large high-quality capacitor.                                                                                                                                                                                                   |

| 3                     | SW       | Switch node for output inductor connection.                                                                                                                                                                                                                                                 |

| 4, 9<br>(Exposed Pad) | GND      | Power ground. The exposed pad must be connected to GND and well soldered to the input and output capacitors and a large PCB copper area for maximum power dissipation.                                                                                                                      |

| 5                     | FB       | Feedback voltage input. Connect FB to the midpoint of the external feedback resistor divider to sense the output voltage. The device regulates the FB voltage at 0.8V (typical) Feedback Reference Voltage.                                                                                 |

| 6                     | COMP     | Compensation node for the compensation of the regulation control loop.<br>Connect a series RC network from COMP to GND. In some cases, another<br>capacitor from COMP to GND may be required.                                                                                               |

| 7                     | EN       | Enable control input. A logic High (V <sub>EN</sub> > 1.35V) enables the device, and a logic Low (V <sub>EN</sub> < 0.925V) shuts down the device, reducing the supply current to $3\mu$ A or below. Connect EN pin to VIN pin with a 100k $\Omega$ pull-up resistor for automatic startup. |

| 8                     | SS       | Soft-start capacitor connection node. Connect an external capacitor from SS to GND to set the soft-start time. Do not leave SS pin unconnected. A capacitor of capacitance from 10nF to 100nF is recommended, which can set the soft-start time from 1.33ms to 13.3ms, accordingly.         |

## **Functional Pin Description**

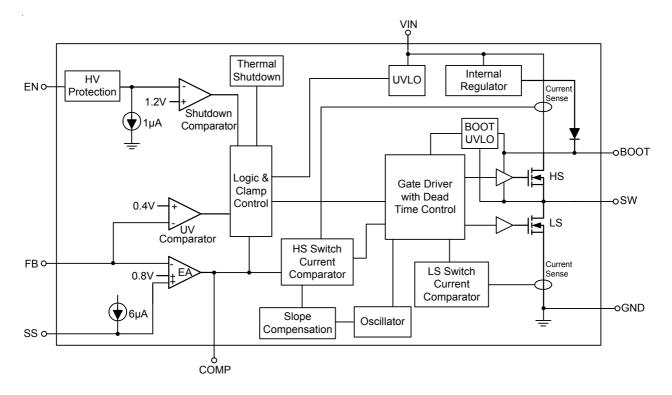

### **Functional Block Diagram**

## Operation

The RT6210 is a synchronous step-down converter, integrated with both high-side (HS) and low-side (LS) MOSFETs to reduce external component count and a gate driver with dead-time control logic to prevent shoot-through condition from happening. The RT6210 also features constant frequency and peak current-mode control with slope compensation. During PWM operation, output voltage is regulated down, and is sensed from the FB pin to be compared with an internal 0.8V reference voltage V<sub>REF</sub>. In normal operation, the high-side N-MOSFET is turned on when an S-R latch is set by the rising edge of an internal oscillator output as the PWM clock, and is turned off when the S-R latch is reset by the output of a (high-side) current comparator, which compares the highside sensed current signal with the current signal related to the COMP voltage. While the high-side N-MOSFET is turned off, the low-side N-MOSFET will be turned on. If the output voltage is not established, the high-side power switch will be turned on again and another cycle begins.

### **Pulse Skipping Operation**

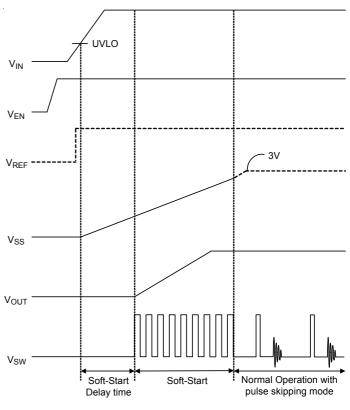

At very light-load condition, the RT6210 provides pulse skipping technique to decrease switching loss for better efficiency. When load current decreases, the FB voltage  $V_{FB}$  will increase slightly. With  $V_{FB}$  1% higher than  $V_{REF}$ , the COMP voltage will be clamped at a minimum value and the converter will enter into pulse skipping mode. When the converter operates in pulse skipping mode, the internal oscillator will be stopped, which makes the switching period being extended. In pulse skipping mode, as the load current decreases, V<sub>FB</sub> will be discharged more slowly, which in turn will extend the switching period even more.

### **Error Amplifier**

The RT6210 adopts a transconductance amplifier as the error amplifier. The error amplifier of a typical 970µA/V transconductance (qm) compares the feedback voltage V<sub>FB</sub> with the lower one of the soft-start voltage or the internal reference voltage V<sub>REF</sub>, 0.8V. As V<sub>FB</sub> drops due to the load current increase, the output voltage of the error

amplifier will go up so that the device will supply more inductor current to match the load current. The frequency compensation components, such as the series resistor and capacitor, and an optional capacitor, are placed between the COMP pin and ground.

#### Oscillator

The internal oscillator frequency is set to a typical 350kHz as a fixed frequency for PWM operation.

### **Slope Compensation**

In order to prevent sub-harmonic oscillations that may occur over all specified load and line conditions when operating at duty cycle higher than 50%, the RT6210 features an internal slope compensation, which adds a compensating slope signal to the sensed current signal to support applications with duty cycle up to 93%.

#### **Internal Regulator**

When the VIN is plugged in, the internal regulator will generate a low voltage to drive internal control circuitry and to supply the bootstrap power for the high-side gate driver.

### **Chip Enable**

The RT6210 provides an EN pin, as an external chip enable control, to enable or disable the device. When VIN is higher than the input under-voltage lockout threshold ( $V_{UVLO}$ ) with the EN voltage ( $V_{EN}$ ) higher than 1.3V, the converter will be turned on. When  $V_{EN}$  is lower than 0.875V, the converter will enter into shutdown mode, during which the supply current can be even reduced to  $3\mu$ A or below.

### **External Soft-Start**

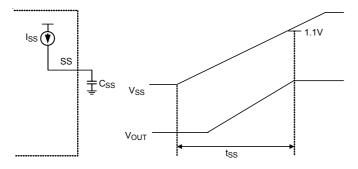

The RT6210 provides external soft-start feature to reduce input inrush current. The soft-start time can be programmed by selecting the value of the capacitor  $C_{SS}$  connected from the SS pin to GND. An internal current source  $I_{SS}$  (typically,  $6\mu$ A) charges the external capacitor  $C_{SS}$  to build a softstart ramp voltage. The feedback voltage  $V_{FB}$  will be compared with the soft-start ramp voltage during soft-start time. For the RT6210, the external capacitor  $C_{SS}$  is required, and for soft-start control, the SS pin should never be left unconnected, and it is not recommended to be connected to an external voltage source. The soft-start time depends on  $C_{SS}$  capacitance; for example, a  $0.1\mu F$  capacitor for programming soft-start time will result in 18.333ms (typ.) soft-start time.

## Output Under-Voltage Protection (UVP) with Hiccup Mode

The RT6210 provides under-voltage protection with hiccup mode. When the feedback voltage  $V_{FB}$  drops below undervoltage protection threshold  $V_{TH-UVP}$ , half of the feedback reference voltage  $V_{REF}$ , the UVP function will be triggered to turn off the high-side MOSFET immediately. The converter will attempt auto-recovery soft-start after undervoltage condition has occurred for a period of time. Once the under-voltage condition is removed, the converter will resume switching and be back to normal operation.

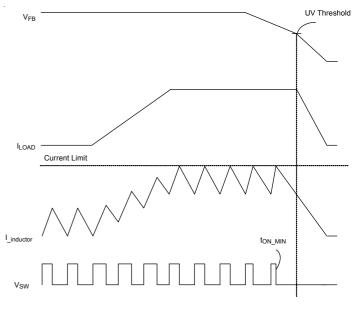

### **Current Limit Protection**

The RT6210 provides cycle-by-cycle current limit protection against over-load or short-circuited condition. When the peak inductor current reaches the current limit, the high-side MOSFET will be turned off immediately with no violating minimum on-time  $t_{ON\_MIN}$  requirement to prevent the device from operating in an over-current condition.

### **Thermal Shutdown**

The RT6210 provides over-temperature protection (OTP) function to prevent the chip from damaging due to overheating. The over-temperature protection function will shut down the switching operation when the junction temperature exceeds 165°C. Once the over-temperature condition is removed, the converter will resume switching and be back to normal operation.

## Absolute Maximum Ratings (Note 1)

| –0.3V to 90V                      |

|-----------------------------------|

|                                   |

| –0.3V to (V <sub>IN</sub> + 0.3V) |

| –5V to (V <sub>IN</sub> + 4V)     |

| –0.3V to 90V                      |

| –0.3V to 6V                       |

| –0.3V to 6V                       |

|                                   |

| 3.44W                             |

|                                   |

| 29°C/W                            |

| 2°C/W                             |

| 260°C                             |

| 150°C                             |

| –65°C to 150°C                    |

|                                   |

| 2kV                               |

|                                   |

### Recommended Operating Conditions (Note 4)

| Supply Input Voltage       | 5.2V to 80V    |

|----------------------------|----------------|

| Ambient Temperature Range  | –40°C to 85°C  |

| Junction Temperature Range | –40°C to 125°C |

### **Electrical Characteristics**

( $V_{IN}$  = 12V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                                 |            | Symbol            | Test Conditions                              | Min   | Тур | Max   | Unit |  |  |

|-------------------------------------------|------------|-------------------|----------------------------------------------|-------|-----|-------|------|--|--|

| Supply Current                            |            |                   |                                              |       |     |       |      |  |  |

|                                           |            |                   | V <sub>EN</sub> = 0V                         |       | 0.5 | 3     |      |  |  |

| Shutdown Supply Curre                     | ent        | ISHDN             | V <sub>EN</sub> = 0V, V <sub>IN</sub> = 80V  |       | 20  |       | μA   |  |  |

| Quiescent Supply Current                  |            | lq                | V <sub>EN</sub> = 3V, V <sub>FB</sub> = 0.9V |       | 0.6 |       | mA   |  |  |

| Reference                                 |            |                   |                                              |       |     |       |      |  |  |

| Feedback Reference Voltage                |            | V <sub>REF</sub>  | $5V \leq V_{IN} \leq 80V$                    | 0.788 | 0.8 | 0.812 | V    |  |  |

| Enable and UVLO                           |            |                   |                                              |       |     |       |      |  |  |

| Input Under-Voltage Lockout<br>Threshold  |            | V <sub>UVLO</sub> | V <sub>IN</sub> rising                       | 4     | 4.6 | 5.2   | V    |  |  |

| Input Under-Voltage Lockout<br>Hysteresis |            | VUVLO_HYS         |                                              | 200   | 350 | 500   | mV   |  |  |

| EN Input Threshold                        | Rising     | VTH_EN            |                                              | 1.1   | 1.2 | 1.3   | V    |  |  |

| Voltage                                   | Hysteresis | VTH_EN_HYS        | Falling                                      | 25    |     | 225   | mV   |  |  |

| Parameter                                 | Symbol                | Test Conditions                            | Min | Тур | Max | Unit |

|-------------------------------------------|-----------------------|--------------------------------------------|-----|-----|-----|------|

| Error Amplifier                           |                       |                                            |     |     | 1   | 1    |

| Error Amplifier Transconductance          | gm_ea                 | $\Delta IC = \pm 10 \mu A$                 |     | 970 |     | μA/V |

| Error Amplifier Source/Sink Current       |                       |                                            |     | 160 |     | μA   |

| COMP to Current Sense<br>Transconductance | <b>g</b> m_CS         |                                            |     | 0.9 |     | A/V  |

| Internal MOSFET                           |                       |                                            |     |     |     |      |

| Lligh Cide Cultab On Desistance           | RDS(ON)_H1            |                                            |     | 660 | 850 | mΩ   |

| High-Side Switch On-Resistance            | RDS(ON)_H2            | V <sub>IN</sub> = 80V                      |     | 930 |     |      |

| Low-Side Switch On-Resistance             | R <sub>DS(ON)_L</sub> |                                            |     | 330 | 500 | mΩ   |

| Switching                                 |                       |                                            |     |     |     |      |

| Oscillation Frequency                     | fosc1                 |                                            |     | 350 |     | kHz  |

| Short-Circuit Oscillation Frequency       | fosc2                 | V <sub>FB</sub> = 0V                       |     | 100 |     | kHz  |

| Maximum Duty Cycle                        | DMAX                  | V <sub>FB</sub> = 0.7V                     |     | 93  |     | %    |

| Minimum On-Time                           | t <sub>ON_MIN</sub>   |                                            |     | 90  |     | ns   |

| Soft-Start                                |                       |                                            |     |     |     |      |

| Soft-Start Current                        | Iss                   | V <sub>SS</sub> = 0V                       |     | 6   |     | μA   |

| Protection Function                       |                       |                                            |     | •   |     |      |

| High-Side Switch Leakage Current          |                       | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 0V |     | 0   | 10  | μA   |

| High-Side Switch Current Limit            | I <sub>LIM_HS</sub>   | Minimum duty cycle                         | 600 | 860 |     | mA   |

| Under-Voltage Protection Threshold VTH_UV |                       | After soft-start, with respect to $V_{FB}$ |     | 50  |     | %    |

| Thermal Shutdown                          | T <sub>SD</sub>       |                                            |     | 165 |     | °C   |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- **Note 5.** When VIN is beyond the recommended operating voltage (80V) and within the absolute maximum voltage (90V), the conducting current through SW pin has to be less than 0.5A to avoid instant damage to the devices.

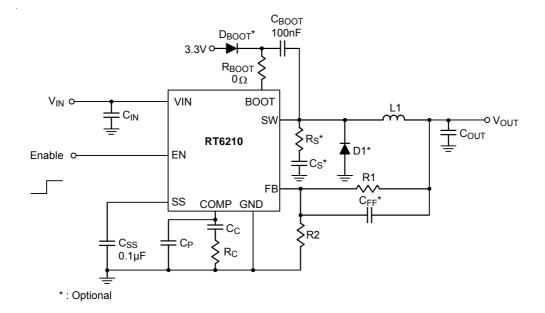

## **Typical Application Circuit**

## Table 1. Suggested component selections for the application of 500mA load current for some common output voltages

| V <sub>OUT</sub> (V) | <b>R1 (k</b> Ω) | <b>R2 (k</b> Ω) | <b>L1 (</b> μ <b>H)</b> | <b>C</b> ουτ (μ <b>F</b> ) | Rc (k $\Omega$ ) | C <sub>C</sub> (nF) | C <sub>P</sub> (pF) |

|----------------------|-----------------|-----------------|-------------------------|----------------------------|------------------|---------------------|---------------------|

| 1                    | 2.49            | 10              | 22                      | 20                         | 4.02             | 6.8                 | NC                  |

| 1.2                  | 4.99            | 10              | 22                      | 20                         | 4.99             | 6.8                 | NC                  |

| 1.8                  | 12.4            | 10              | 33                      | 20                         | 6.98             | 6.8                 | NC                  |

| 2.5                  | 21              | 10              | 33                      | 20                         | 10               | 6.8                 | NC                  |

| 3.3                  | 30.9            | 10              | 47                      | 20                         | 16               | 6.8                 | 68                  |

| 5                    | 52.3            | 10              | 100                     | 20                         | 24               | 6.8                 | 47                  |

| 9                    | 102             | 10              | 150                     | 20                         | 34.9             | 6.8                 | 47                  |

| 12<br>(Note)         | 140             | 10              | 220                     | 20                         | 34.9             | 6.8                 | 47                  |

Note : For  $V_{IN}$  < 17V &  $V_{OUT}$  = 12V application, the snubber components need to be added (R<sub>S</sub> = 3.9 $\Omega$ , C<sub>S</sub> = 1nF)

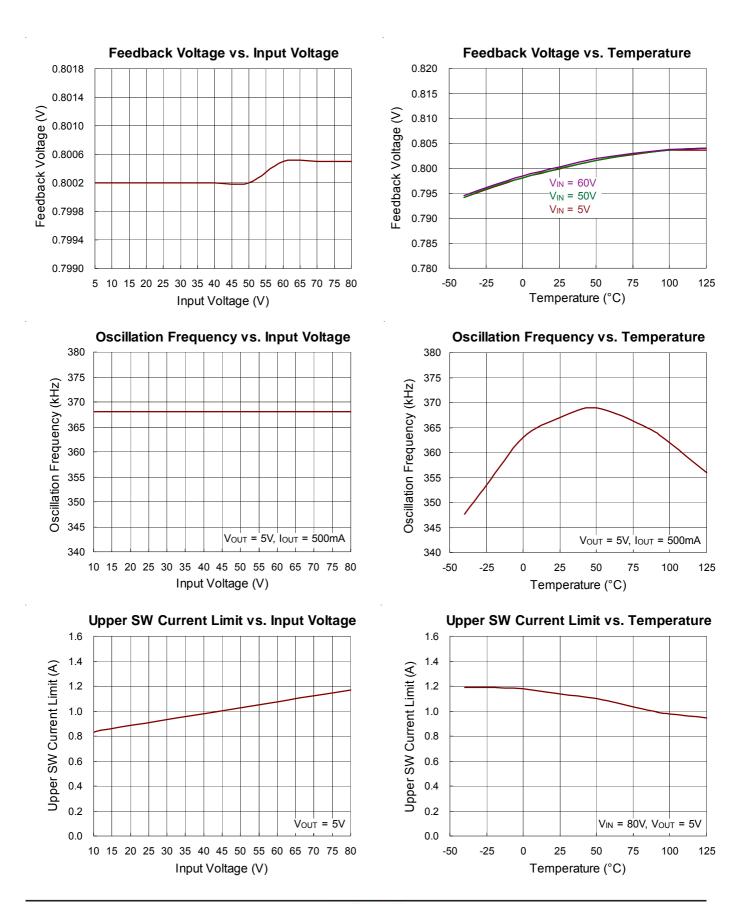

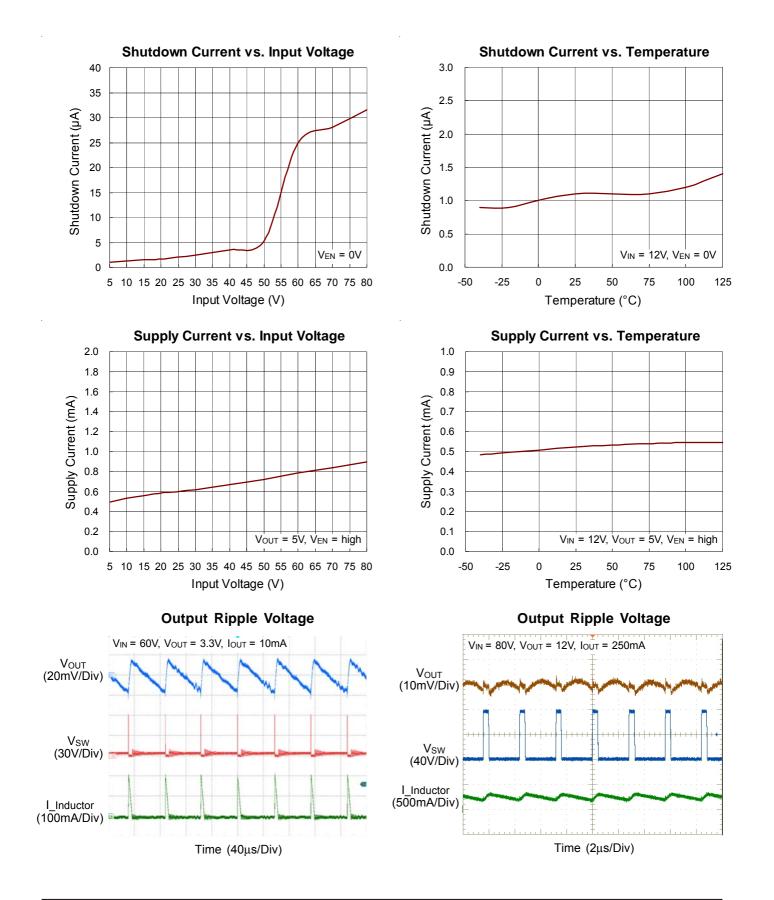

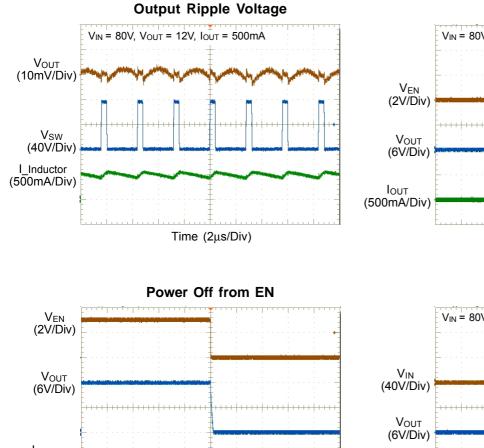

### **Typical Operating Characteristics**

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

8

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## **RT6210**

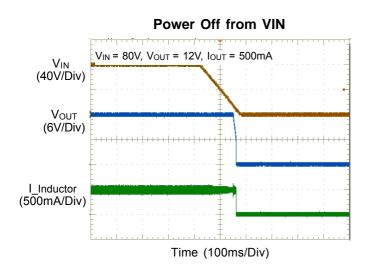

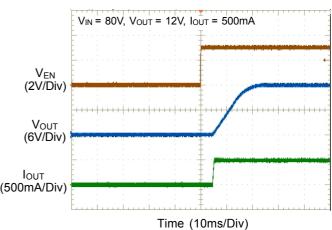

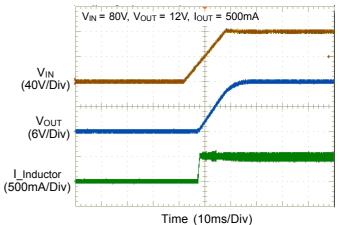

Iout (500mA/Div) V<sub>IN</sub> = 80V, Vout = 12V, Iout = 500mA Time (4ms/Div)

Power On from EN

Power On from VIN

### **Application Information**

#### **Output Voltage Setting**

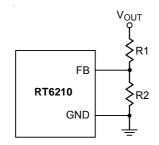

The output voltage can be adjusted by setting the feedback resistors R1 and R2, as Figure 1. Choose a  $10k\Omega$  resistor for R2 and calculate R1 by using the equation below :

$$V_{OUT} = V_{FB} \times (1 + \frac{R1}{R2})$$

where  $V_{FB}$  is the feedback voltage (typically equal to  $V_{REF}$ )

Figure 1. Output Voltage Setting by a Resistive Voltage Divider

#### **Chip Enable Operation**

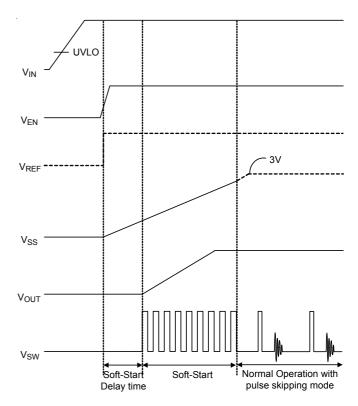

The RT6210 provides enable/disable control through the EN pin. The chip remains in shutdown mode by pulling the EN pin below Logic-Low threshold (0.875V). During the shutdown mode, the RT6210 disables most of the logic circuitry to lower the quiescent current. When  $V_{EN}$  rises above Logic-High threshold ( $V_{TH_EN}$  1.3V), the RT6210 will begin initialization for a new soft-start cycle.

If the EN pin is floating,  $V_{EN}$  will be pulled Low by a 1µA current drawn from the EN pin. Connecting a 1k $\Omega$  to 100k $\Omega$  pull-up resistor is recommended. An external MOSFET can be added to implement a logic-controlled enable control. Figure 2 shows the power up sequence, which is controlled by the EN pin.

The RT6210 also provides enable control through VIN pin. If the V<sub>EN</sub> is above Logic-High threshold first, the chip will remain in shutdown mode until the V<sub>IN</sub> rises above V<sub>UVLO</sub>.

Figure 3 shows the power up sequence, which is controlled by the VIN pin.

Figure 2. Power-Up Sequence Controlled by the EN Pin

Figure 3. Power-Up Sequence Controlled by the VIN Pin

#### Soft-Start

When start-up, a large inrush may be observed for high output voltages and output capacitances. To solve this, the RT6210 provides an external soft-start function to reduce input inrush current to meet various applications.

For the RT6210, the soft-start time t<sub>SS</sub> can be programmed by selecting the value of the capacitor C<sub>SS</sub> connected between the SS pin and GND. During the soft-start period, an internal pull-up current source  $I_{SS}$  (typically,  $6\mu A$ ) charges the external capacitor C<sub>SS</sub> to generate a softstart voltage ramp, and then output voltage will follow this voltage ramp to monotonically start up.

The soft-start time can be calculated as :

$$t_{SS} = \frac{\left[C_{SS} \times (V_{REF} + 0.3V)\right]}{I_{SS}}$$

where  $I_{SS}$  = 6µA (typical),  $V_{REF}$  is the feedback reference voltage, and C<sub>SS</sub> is the external capacitor placed from the SS pin to GND, where a 10nF to 100nF capacitor is recommended to set the soft-start time from 1.833ms to 18.333ms.

Figure 4. External Soft-Start Time Setting

### **Current Limit**

The RT6210 provides peak current limit function to prevent chip damaging from short-circuited output, the VIN voltage and SW voltage are sensed when the internal high-side MOSFET is turned on. During this period, the VIN-SW voltage is increasing when the inductor current is increasing. The peak inductor current will be monitored every switching cycle. If the current sense signal exceeds the internal current limit, clamped by the maximum COMP voltage, the high-side MOSFET will be turned off immediately, while the minimum on-time ton MIN requirement still needs to be met, to prevent the device from operating in an over-current condition.

In the current-limited condition, the maximum sourcing current is fixed because the peak inductor current is limited. When the load is further increasing and is over the sourcing capability of the high-side switch, the output voltage will start to drop and eventually be lower than the under-voltage protection threshold so that the IC will enter shutdown mode and may restart with hiccup mechanism.

Figure 5. Peak-Current Limit

#### **Under-Voltage Protection**

The feedback voltage is constantly monitored for undervoltage protection. When the feedback voltage is lower than under-voltage protection threshold V<sub>TH-UVP</sub>, the undervoltage protection is triggered, the high-side MOSFET will be turned off and the low-side MOSFET is turned on to discharge the output voltage. The under-voltage protection is not a latched mechanism; if the under-voltage condition remains for a period of time, the RT6210 will enter hiccup mode. During the soft-start time, the under-voltage protection is masked and a 5µs deglitch time is built in the UVP circuit to prevent false transitions.

### **Hiccup Mode**

If the under-voltage protection condition continues for a period of time, the RT6210 will enter hiccup mode, in which the soft-start process will be initialized without VIN being

re-powered on. During this period of time, the SW starts to switch since the under-voltage protection is masked during soft-start time. When soft-start finishes, if the under-voltage condition is removed, the converter will resume normal operation; if the under-voltage condition, however, still remains, that is, the FB voltage is still lower than under-voltage threshold  $V_{TH_UVP}$ , the under-voltage protection will be triggered again. The cycle will repeat until this fault condition is removed.

### **Output Voltage Limitation**

The output voltage must be set higher than (V<sub>IN</sub> x 6.3%) due to the limitation of the minimum on-time  $t_{ON\_MIN}$  and switching frequency. When current limiting protection is triggered and the load current is still increasing slowly, the output voltage will start to drop and the on-time of the high-side MOSFET will decrease as well. When the output voltage drops below V<sub>TH\_UVP</sub>, the under-voltage protection is triggered to turn off the internal driver to protect the converter. If the output voltage, however, does not drop below V<sub>TH\_UVP</sub> yet when the on-time of the high-side MOSFET has decreased to  $t_{ON\_MIN}$  (~90ns), the internal gate driver will keep switching to maintain the output voltage, which may damage the chip under this over-current condition.

In order to make sure the output voltage can drop below  $V_{TH\_UVP}$  once current limiting protection is triggered, the output voltage setting must be satisfied with the equation below :

The output voltage at the time, when the switch has been turned on for the minimum on-time, is

$V_{OUT\_MIN} = V_{IN} \times t_{ON} \times f_{OSC1} = 0.0315 V_{IN}$

where  $t_{ON_{MIN}}$  = ~90ns,  $f_{OSC1}$  = 350kHz

The UVP is triggered when the V<sub>FB</sub> is lower than  $V_{TH_UVP}$ , which is 50%. That is to say  $V_{OUT_MIN}$  should be lower than 50% of the actual  $V_{OUT}$  to guarantee the UVP can be triggered under this condition.

$V_{OUT\_MIN} < 0.5 \text{ x } V_{OUT}$

The duty cycle limitation can be obtained.

D<sub>MIN</sub> > 0.063

For example, if the  $V_{\text{IN}}$  = 50V, the  $V_{\text{OUT}}$  should be set higher than 3.15V.

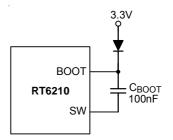

#### **External Bootstrap Diode**

A 0.1 $\mu$ F capacitor C<sub>BOOT</sub>, where a low ESR ceramic capacitor is typically used, is connected between the BOOT and SW pins to provide the gate driver supply voltage for the high-side N-MOSFET.

It is recommended to add an external bootstrap diode from an external 3.3V supply voltage to the BOOT pin to improve efficiency when the input voltage  $V_{IN}$  is lower than 5.5V or duty cycle is higher than 65%. A low-cost bootstrap diode can be used, such as IN4148 or BAT54.

Note that the external BOOT voltage must be lower than 5.5V.

Figure 6. External Bootstrap Diode

### **Inductor Selection**

Output inductor plays a very important role in step-down converters because it stores energy from input power rail and releases to output load. For better efficiency, DC resistance (DCR) of the inductor must be minimized to reduce copper loss. In addition, since the inductor takes up most of the PCB space, its size also matters. Lowprofile inductors can also save board space if height limitation exists. However, low-DCR and low-profile inductors are usually not cost effective.

On the other hand, while larger inductance may lower ripple current, and then power loss, rise time of the inductor current, however, increases with inductance, which degrades the transient responses. Therefore, the inductor design is a trade-off among performance, size and cost.

The first thing to consider is inductor ripple current. The inductor ripple current is recommended in the range of 20% to 40% of full-load current, and thus the inductance can be calculated using the following equation.

$$L_{MIN} = \frac{V_{IN} - V_{OUT}}{f_{SW} \times k \times I_{OUT}} \times \frac{V_{OUT}}{V_{IN}}$$

where k is the ratio of peak-to-peak ripple current to rated output current. From above, 0.2 to 0.4 of the ratio k is recommended.

The next thing to consider is inductor saturation current. Choose an inductor with saturation current rating greater than maximum inductor peak current. The peak inductor current can be calculated using the following equation :

$$\Delta I_{L} = \frac{V_{IN} - V_{OUT}}{L_{MIN} \times f_{SW}} \times \left(\frac{V_{OUT}}{V_{IN}}\right)$$

where  $\Delta I_L$  is the inductor peak to peak current, and

$$I_{L}PEAK = I_{OUT} + \frac{\Delta I_{L}}{2}$$

### **Input Capacitor Selection**

A high-quality ceramic capacitor of  $4.7\mu$ F or greater, such as X5R or X7R, are recommended for the input decoupling capacitor. X5R and X7R ceramic capacitors are commonly used in power regulator applications because the dielectric material has less capacitance variation and more temperature stability.

Voltage rating and current rating are the key parameters to select an input capacitor. An input capacitor with voltage rating 1.5 times greater than the maximum input voltage is a conservative and safe design choice. As for current rating, the input capacitor is used to supply the input RMS current, which can be approximately calculated using the following equation :

$I_{IN_{RMS}} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$

It is practical to have several capacitors with low equivalent series resistance (ESR), being paralleled to form a capacitor bank, to meet size or height requirements, and to be placed close to the drain of the high-side MOSFET, which is very helpful in reducing input voltage ripple at heavy load. Besides, the input voltage ripple is determined by the input capacitance, which can be approximately calculated by the following equation :

$$\Delta V_{IN} = \frac{I_{OUT}(MAX)}{C_{IN} \times f_{SW}} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

#### **Output Capacitor Selection**

Output capacitance affects stability of the control feedback loop, ripple voltage, and transient response. In steady state condition, inductor ripple current flows into the output capacitor, which results in voltage ripple. Output voltage ripple V<sub>RIPPLE</sub> can be calculated by the following equation :

$$V_{\text{RIPPLE}} = \Delta I_{\text{L}} \times \left( \text{ESR} + \frac{1}{8 \times \text{Cout} \times \text{fsw}} \right)$$

where  $\Delta I_L$  is the peak-to-peak inductor current.

The output inductor and capacitor form a second-order low-pass filter for the buck converter.

It takes a few switching cycles to respond to load transient due to the delay from the control loop. During the load transient, the output capacitor will supply current before the inductor can supply current high enough to output load. Therefore, a voltage drop, caused by the current change onto output capacitor, and the current flowing through ESR of the capacitor, will occur. To meet the transient response requirement, the output capacitance should be large enough and its ESR should be as small as possible. The output voltage drop ( $\Delta V$ ) can be calculated by the equation below :

$$\Delta V = \Delta I_{OUT} \times ESR + \frac{\Delta I_{OUT}}{C_{OUT}} \times t_{S}$$

$$C_{OUT} > \frac{\Delta I_{OUT} \times t_{S}}{\Delta V - (\Delta I_{OUT} \times ESR)}$$

where  $\Delta I_{OUT}$  is the size of the output current transient, and t<sub>S</sub> is the control-loop delay time. For the worst-case scenario, from no load to full load, ts is about 1 to 3 switching cycles.

Given that a transient response requirement is 4% for 5V output voltage V<sub>OUT</sub>, output current transient  $\Delta I_{OUT}$  is from 0A to 0.5A, ESR of the ceramic capacitor is  $2m\Omega$ , t<sub>S</sub> is 3 switching cycles for the longest delay, and switching frequency is 350kHz, a minimum output capacitance  $21.53\mu$ F can then be calculated from above.

Another factor for output voltage drop is equivalent series inductance (ESL). A big change in load current, i.e. large di/dt, along with the ESL of the capacitor, causes a drop on the output voltage. A better transient performance can be obtained by using a capacitor with low ESL. Generally, using several capacitors connected in parallel can have better transient performance than using a single capacitor with the same total ESR.

#### **External Diode Selection**

In order to reduce conduction loss, an external diode between SW pin and GND is recommended. Since a low forward voltage of a diode may cause low conduction loss during OFF-time, SCHOTTKY diodes with current rating greater than maximum inductor peak current are good design choice for the application. During the on-time, the diode can prevent the reverse voltage back to the input voltage. Therefore, the voltage rating should be higher than maximum input voltage.

#### **Thermal Considerations**

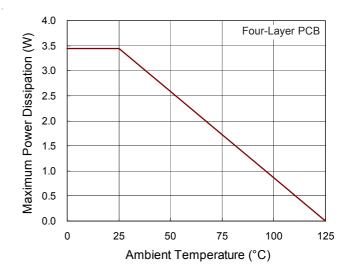

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a SOP-8 (Exposed Pad) package, the thermal resistance,  $\theta_{JA}$ , is 29° C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A = 25^{\circ}$ C can be calculated as below :

$P_{D(MAX)}$  = (125°C - 25°C) / (29°C/W) = 3.44W for a SOP-8 (Exposed Pad) package.

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 7 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

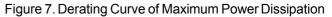

#### Layout Considerations

PCB layout is very important for high-frequency switching converter applications. The PCB traces can radiate excessive noise and contribute to converter instability with improper layout. It is good design to mount power components and route the power traces on the same layer. If the power trace, for example,  $V_{IN}$  trace, must be routed to another layer, there must be enough vias on the power trace for passing current through with less power loss. The width of power trace is decided by the maximum current which may go through. With wide traces and enough vias, resistance of the entire power trace can be reduced to minimum to improve converter performance. Below are some other layout guidelines, which should be considered :

- Place input decoupling capacitors close to the VIN pin. Input capacitor can provide instant current to the converter when high-side MOSFET is turned on. It is better to connect the input capacitors to the VIN pin directly with a trace on the same layer.

- Place an inductor close to the SW pin and the trace between them should be wide and short. It can gain better efficiency with minimum resistance of the SW trace since the output current will flow through the SW trace. It is also a good design to keep the area of SW trace as large as possible, without affecting other paths. The area can help dissipate the heat in the internal power stages. However, since a large voltage and current

## RT6210

variation usually occur on the SW trace, any sensitive trace should be kept away from this node.

The connection point of the feedback trace on the VOUT side should be kept away from the current path for the VOUT trace and be close to the output capacitor, which is closest to the inductor. The feedback trace should be also kept away from any dirty trace, for example, a trace with high dv/dt, di/dt, or current rating, etc., and the total length should be kept as short as possible to reduce the risk of noise coupling, and the signal delay.

If possible, tie the grounds of the input capacitor and the output capacitor together as the same reference ground.

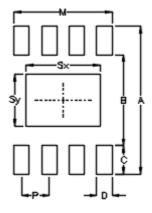

Figure 8. PCB Layout Guide

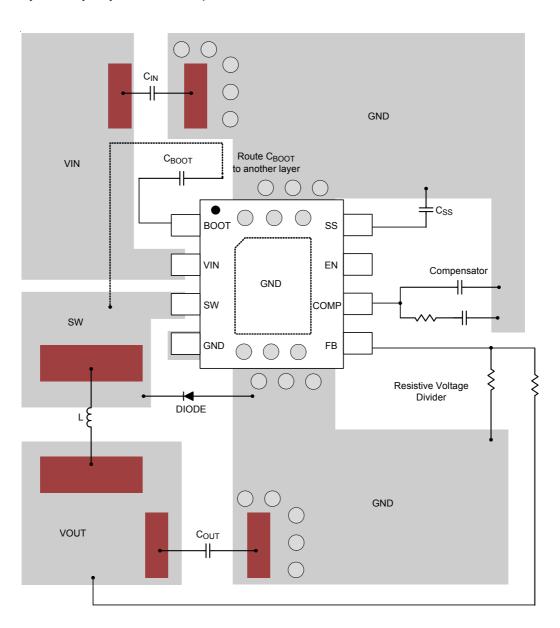

### **Outline Dimension**

| O much   | - | Dimensions | n Millimeters | <b>Dimensions In Inches</b> |       |  |  |

|----------|---|------------|---------------|-----------------------------|-------|--|--|

| Symbol   |   | Min        | Max           | Min                         | Max   |  |  |

| A        |   | 4.801      | 5.004         | 0.189                       | 0.197 |  |  |

| В        |   | 3.810      | 4.000         | 0.150                       | 0.157 |  |  |

| С        |   | 1.346      | 1.753         | 0.053                       | 0.069 |  |  |

| D        |   | 0.330      | 0.510         | 0.013                       | 0.020 |  |  |

| F        |   | 1.194      | 1.346         | 1.346 0.047                 |       |  |  |

| н        |   | 0.170      | 0.254         | 0.007                       | 0.010 |  |  |

| I        |   | 0.000      | 0.152 0.000   |                             | 0.006 |  |  |

| J        |   | 5.791      | 6.200         | 6.200 0.228                 |       |  |  |

| М        |   | 0.406      | 1.270 0.016   |                             | 0.050 |  |  |

| Option 1 | Х | 2.000      | 2.300         | 0.079                       | 0.091 |  |  |

| Option 1 | Y | 2.000      | 2.300         | 0.079                       | 0.091 |  |  |

| Ontion 2 | Х | 2.100      | 2.500         | 0.083                       | 0.098 |  |  |

| Option 2 | Y | 3.000      | 3.500         | 0.118                       | 0.138 |  |  |

8-Lead SOP (Exposed Pad) Plastic Package

## **Footprint Information**

| Packago | Number of Pin | Footprint Dimension (mm) |      |      |      |      |      |      | Tolerance |      |             |

|---------|---------------|--------------------------|------|------|------|------|------|------|-----------|------|-------------|

| Package |               |                          | Р    | А    | В    | С    | D    | Sx   | Sy        | М    | TOIEIdilice |

| PSOP-8  | Option1       | 8                        | 1.27 | 6.80 | 4.20 | 1.30 | 0.70 | 2.30 | 2.30      | 4.51 | ±0.10       |

|         | Option2       |                          | 1.27 |      |      |      |      | 3.40 | 2.40      |      |             |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Richtek manufacturer:

Other Similar products are found below :

EVB\_RT5047GSP\_EVB\_RT7275GQW\_EVB\_RT7297CHZSP\_RT9080N-08GJ5\_EVB\_RT5047AGSP\_EVB\_RT7243GQW EVB\_RT7272BGSP\_RT8097AHGE\_EVB\_RT7247CHGSP\_EVB\_RT7276GQW\_EVB\_RT8293AHZSP\_EVB\_RT6200GE EVB\_RT7235GQW\_EVB\_RT7237AHGSP\_EVB\_RT7251AZQW\_RT5047AGSP\_EVB\_RT7272AGSP\_EVB\_RT7237CHGSP EVB\_RT7247AHGSP\_EVB\_RT7252BZSP\_EVB\_RT7280GQW\_EVB\_RT8292AHZSP\_EVB\_RT8297BZQW\_EVB\_RT7231GQW EVB\_RT7232GQW\_EVB\_RT7236GQW\_EVB\_RT7250BZSP\_EVB\_RT7251BZQW\_EVB\_RT7279GQW\_EVB\_RT8008GB\_RT8207MZQW RT8296AHZSP\_RT9011-JGPJ6\_RT8258GE\_RT5711AHGQW\_RT9081AGQZA(2)\_RT6154BGQW\_RT7238BGQUF\_RT5788AGJ8F RT8812AGQW\_RT6278BHGQUF\_RT7270HZSP\_RD0004\_RT5789AGQUF\_RT9076-18GVN\_RT9193-15GU5\_RT3602AJGQW RT8296BHZSP\_RT6214AHGJ6F\_RT9276GQW(Z00)