8-Bit

# XC886/888CLM

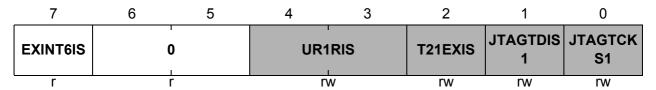

8-Bit Single Chip Microcontroller

User's Manual V1.3 2010-02

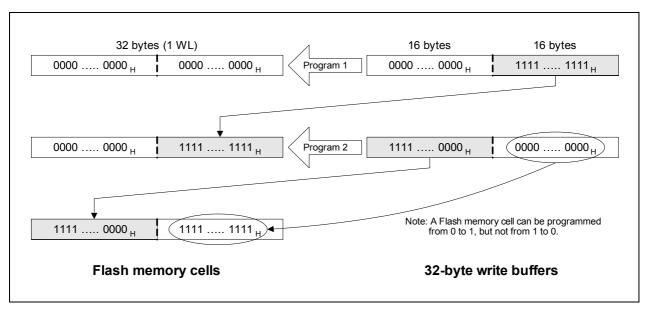

Microcontrollers

Edition 2010-02

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2010 Infineon Technologies AG

All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

8-Bit

XC886/888CLM

8-Bit Single Chip Microcontroller

User's Manual V1.3 2010-02

Microcontrollers

#### XC886/888 User's Manual

Revision History: V1.3 2010-02

| Previous Ve      | ersions: V1.0, V1.1, V1.2                                                               |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| Page             | Subjects (major changes since last revision)                                            |  |  |  |  |

| Changes from     | Changes from V1.2 2009-04 to V1.3 2010-02                                               |  |  |  |  |

| 2-9              | Footnote on instruction cycles is added.                                                |  |  |  |  |

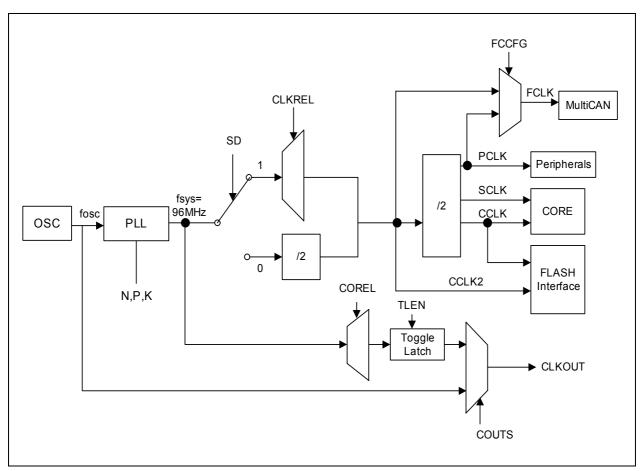

| 7-11             | Figure 7-6 on CGU block diagram is updated.                                             |  |  |  |  |

| 7-12             | PLL loss of lock recovery sequence is updated.                                          |  |  |  |  |

| 7-13             | Select external oscillator sequence is updated.                                         |  |  |  |  |

| 7-14             | Note on PLL base mode is updated.                                                       |  |  |  |  |

| 10-3             | The wording 'integer' is removed since normalization always involves a 32-bit variable. |  |  |  |  |

| 12-31            | Direction of RXD (slave) signal in Figure 12-11 is corrected.                           |  |  |  |  |

| 14-3             | Handling of T12 period register is elaborated.                                          |  |  |  |  |

| 16-6             | Conversion time example is updated.                                                     |  |  |  |  |

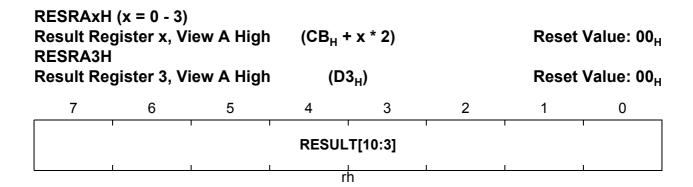

| 16-39, 16-<br>53 | SFR address formula for CHCTRx, RESRxL/H and RESRAxL/H registers are corrected.         |  |  |  |  |

| 18-19            | Header block of LIN BSL Modes 0/2/8 is corrected                                        |  |  |  |  |

|                  |                                                                                         |  |  |  |  |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

User's Manual V1.3, 2010-02

| Table of | Contents                                          | Page |

|----------|---------------------------------------------------|------|

| 1        | Introduction                                      | 1-1  |

| 1.1      | Feature Summary                                   | 1-4  |

| 1.2      | Pin Configuration                                 |      |

| 1.3      | Pin Definitions and Functions                     |      |

| 1.4      | Chip Identification Number                        |      |

| 1.5      | Text Conventions                                  |      |

| 1.6      | Reserved, Undefined and Unimplemented Terminology | 1-19 |

| 1.7      | Acronyms                                          |      |

| 2        | Processor Architecture                            | 2-1  |

| 2.1      | Functional Description                            |      |

| 2.2      | CPU Register Description                          |      |

| 2.2.1    | Stack Pointer (SP)                                |      |

| 2.2.2    | Data Pointer (DPTR)                               |      |

| 2.2.3    | Accumulator (ACC)                                 |      |

| 2.2.4    | B Register                                        |      |

| 2.2.5    | Program Status Word                               |      |

| 2.2.6    | Extended Operation (EO)                           |      |

| 2.2.7    | Power Control (PCON)                              |      |

| 2.3      | Instruction Timing                                |      |

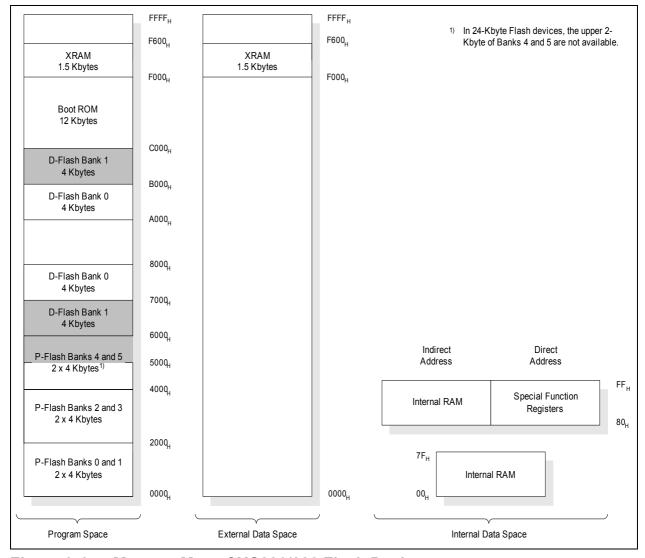

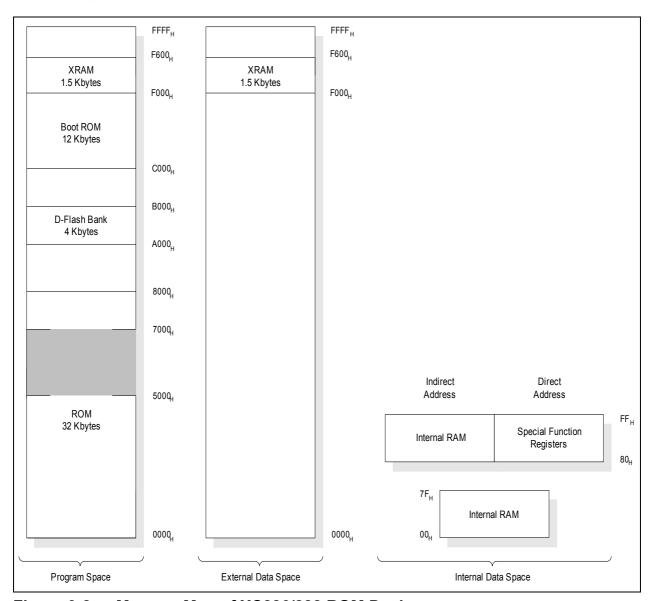

| 3        | Memory Organization                               | 3-1  |

| 3.1      | Compatibility between Flash and ROM devices       | 3-3  |

| 3.2      | Program Memory                                    | 3-4  |

| 3.3      | Data Memory                                       | 3-4  |

| 3.3.1    | Internal Data Memory                              | 3-4  |

| 3.3.2    | External Data Memory                              | 3-5  |

| 3.4      | Memory Protection Strategy                        | 3-6  |

| 3.4.1    | Flash Memory Protection                           | 3-6  |

| 3.4.2    | Miscellaneous Control Register                    | 3-9  |

| 3.5      | Special Function Registers                        | 3-10 |

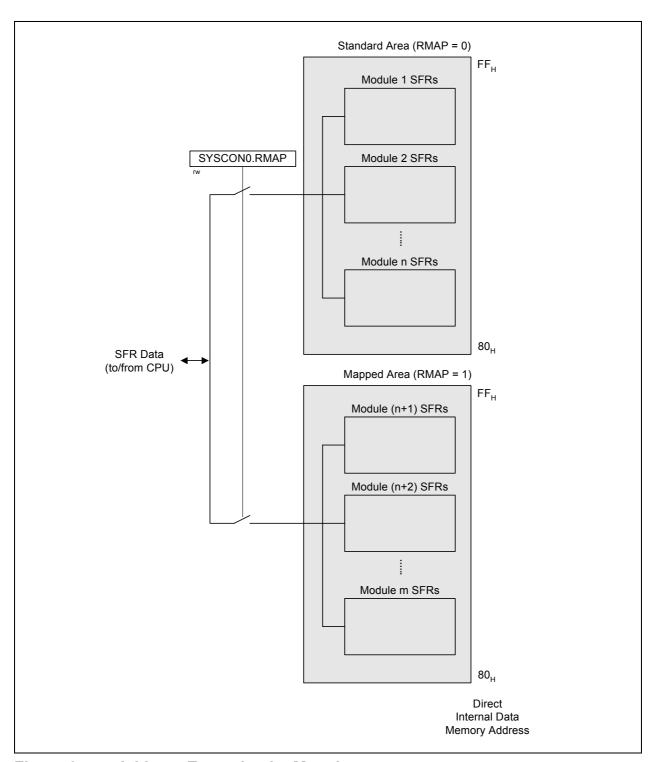

| 3.5.1    | Address Extension by Mapping                      |      |

| 3.5.1.1  | System Control Register 0                         | 3-12 |

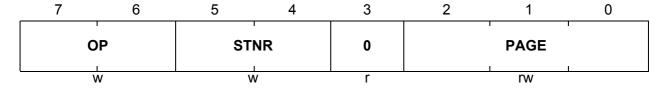

| 3.5.2    | Address Extension by Paging                       |      |

| 3.5.2.1  | Page Register                                     | 3-15 |

| 3.5.3    | Bit-Addressing                                    |      |

| 3.5.4    | System Control Registers                          | 3-17 |

| 3.5.4.1  | Bit Protection Scheme                             |      |

| 3.5.5    | XC886/888 Register Overview                       |      |

| 3.5.5.1  | CPU Registers                                     |      |

| 3.5.5.2  | MDU Registers                                     |      |

| 3.5.5.3  | CORDIC Registers                                  |      |

| 3.5.5.4  | System Control Registers                          | 3-24 |

| Table of | Contents                             | Page   |

|----------|--------------------------------------|--------|

| 3.5.5.5  | WDT Registers                        | . 3-26 |

| 3.5.5.6  | Port Registers                       | . 3-27 |

| 3.5.5.7  | ADC Registers                        | . 3-29 |

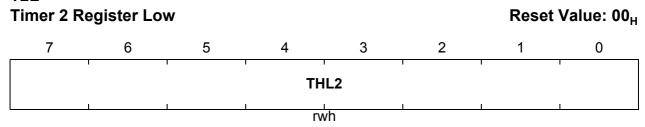

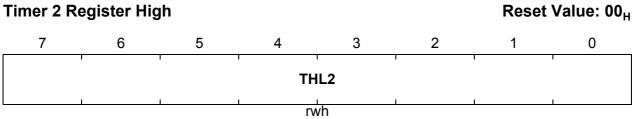

| 3.5.5.8  | Timer 2 Registers                    | . 3-33 |

| 3.5.5.9  | Timer 21 Registers                   | . 3-33 |

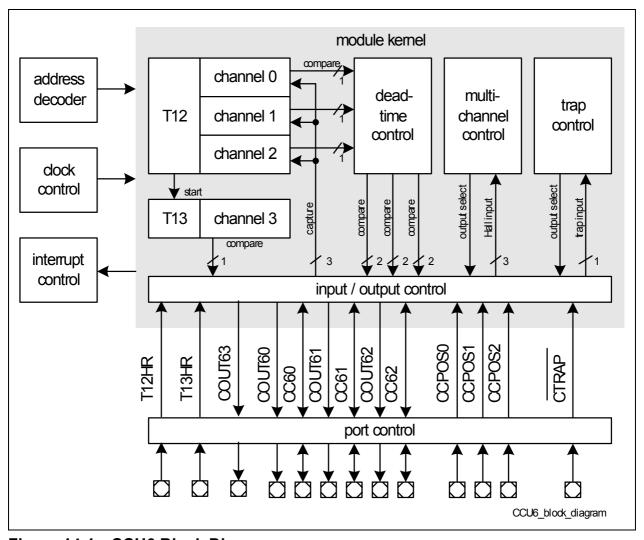

| 3.5.5.10 | CCU6 Registers                       | . 3-34 |

| 3.5.5.11 | UART1 Registers                      | . 3-38 |

| 3.5.5.12 | SSC Registers                        | . 3-39 |

| 3.5.5.13 | MultiCAN Registers                   | . 3-39 |

| 3.5.5.14 | OCDS Registers                       | . 3-40 |

| 3.6      | Boot ROM Operating Mode              | . 3-41 |

| 3.6.1    | User Mode                            | . 3-42 |

| 3.6.2    | Bootstrap Loader Mode                | . 3-42 |

| 3.6.3    | OCDS Mode                            | . 3-43 |

| 3.6.4    | User JTAG Mode                       |        |

| 4        | Flash Memory                         | 4-1    |

| 4.1      | Flash Memory Map                     |        |

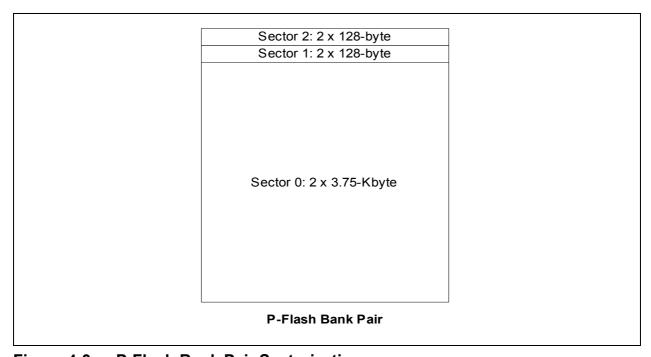

| 4.2      | Flash Bank Sectorization             |        |

| 4.3      | Parallel Read Access of P-Flash      |        |

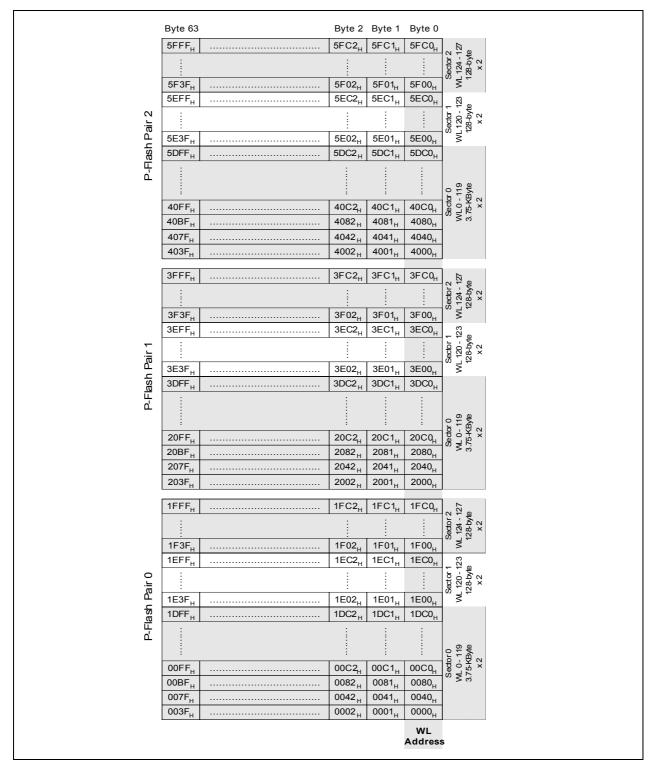

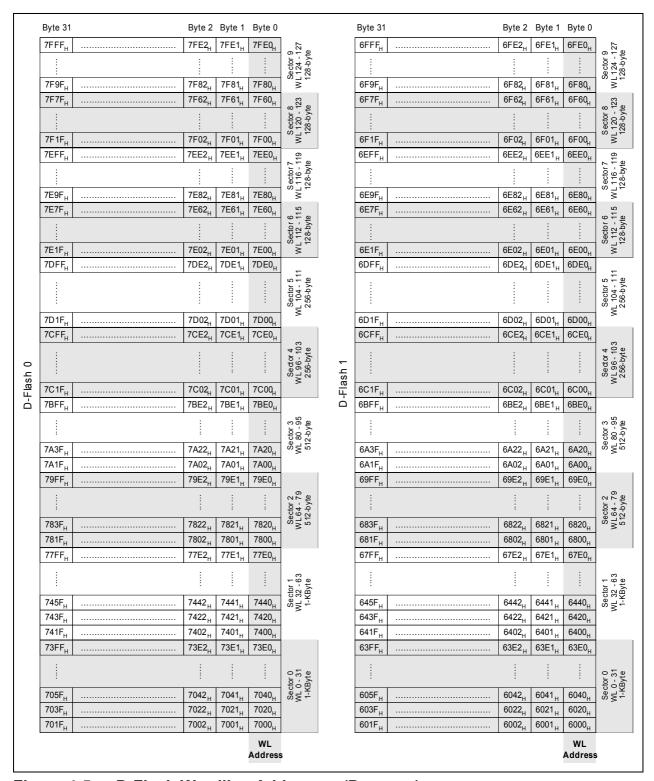

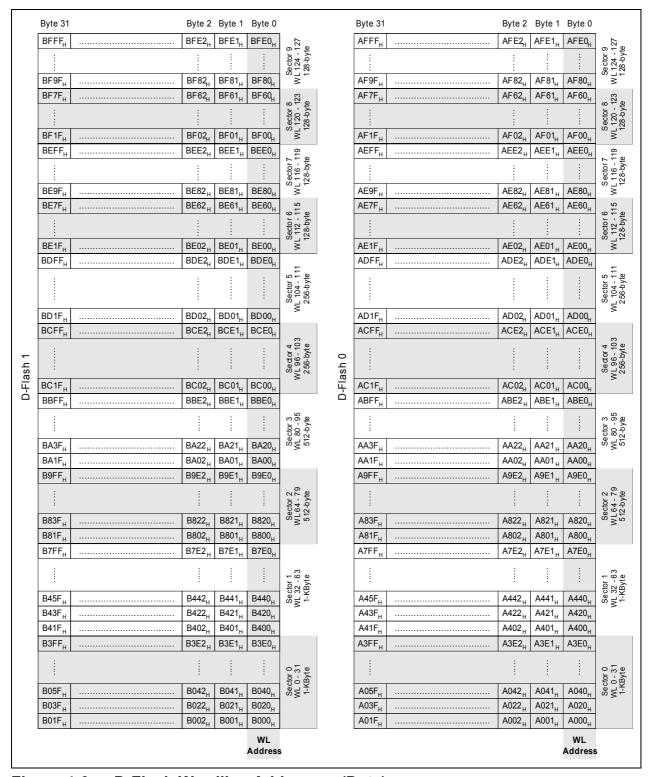

| 4.4      | Wordline Address                     | 4-6    |

| 4.5      | Operating Modes                      | . 4-11 |

| 4.6      | Error Detection and Correction       |        |

| 4.6.1    | Flash Error Address Register         |        |

| 4.7      | In-System Programming                |        |

| 4.8      | In-Application Programming           |        |

| 4.8.1    | Flash Programming                    |        |

| 4.8.2    | Flash Erasing                        |        |

| 4.8.3    | Aborting Flash Erase                 |        |

| 4.8.4    | Flash Bank Read Status               |        |

| 4.8.5    | P-Flash Parallel Read Enable/Disable | . 4-20 |

| 4.8.6    | Get Chip Information                 | . 4-21 |

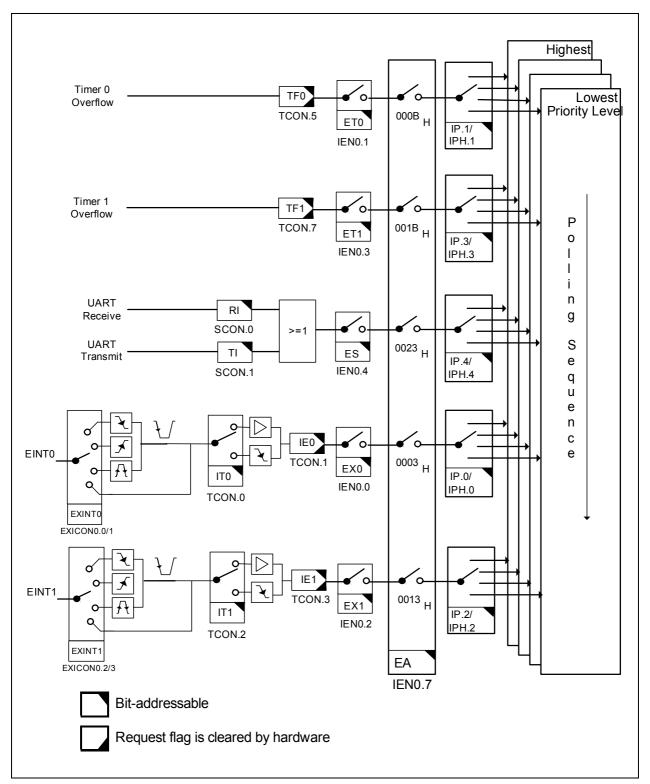

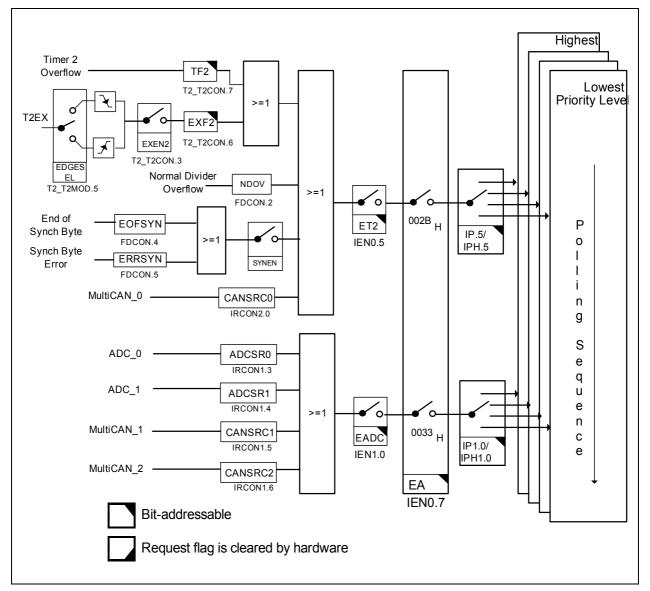

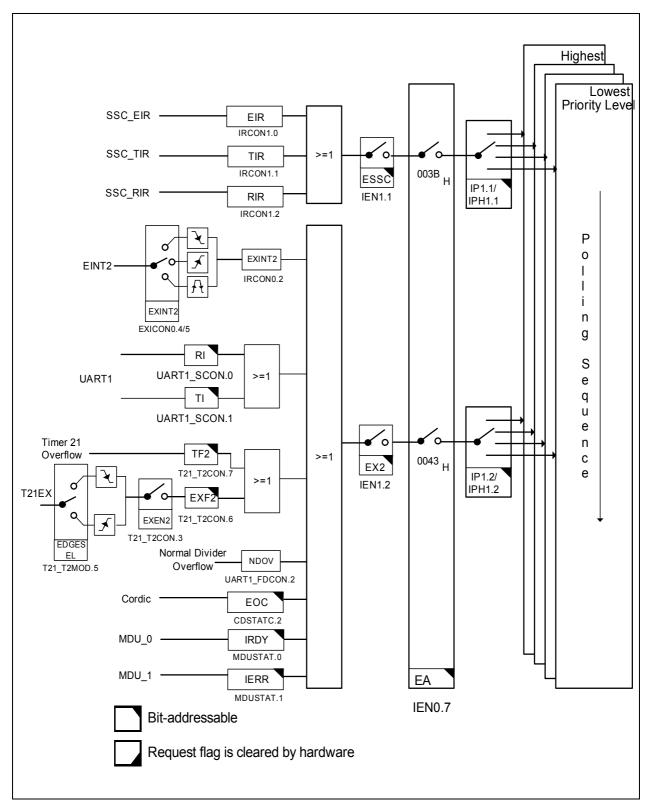

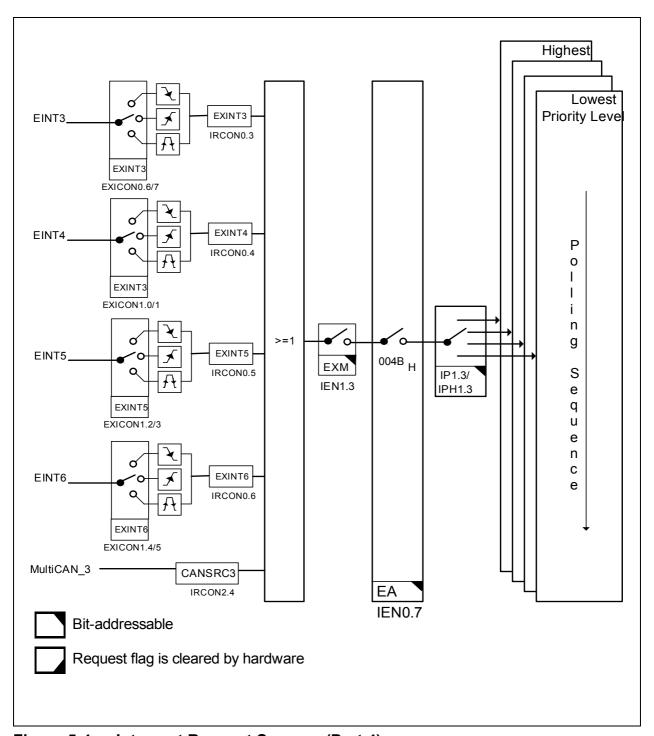

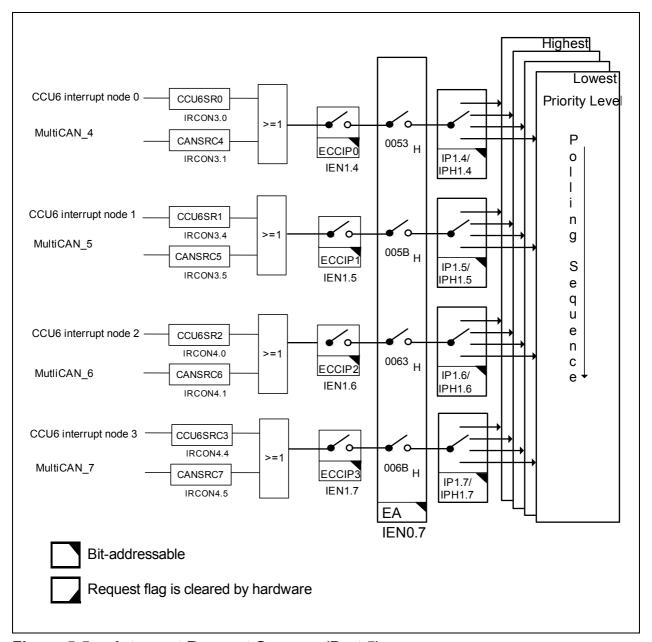

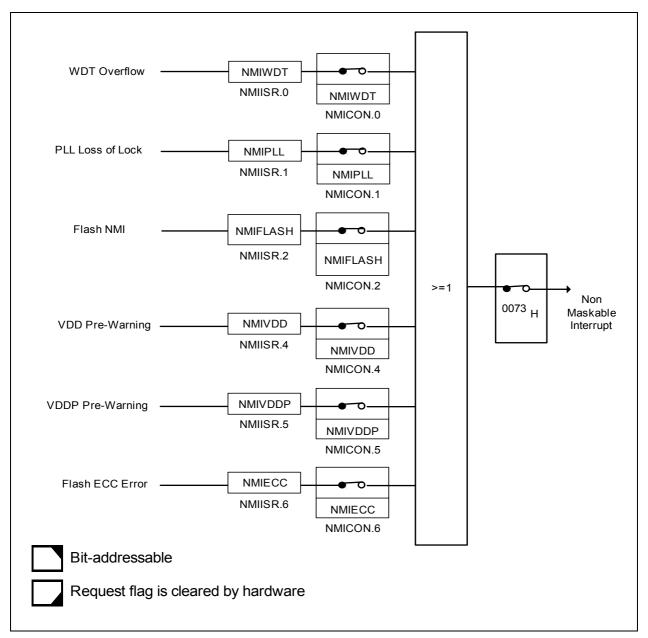

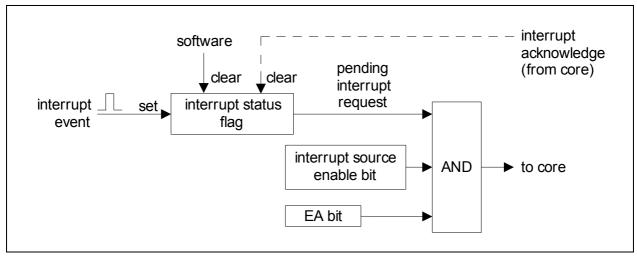

| 5        | Interrupt System                     | 5-1    |

| 5.1      | Interrupt Structure                  |        |

| 5.1.1    | Interrupt Structure 1                |        |

| 5.1.2    | Interrupt Structure 2                |        |

| 5.1.2.1  | System Control Register 0            |        |

| 5.2      | Interrupt Source and Vector          |        |

| 5.3      | Interrupt Priority                   |        |

| 5.4      | Interrupt Handling                   |        |

| 5.5      | Interrupt Response Time              |        |

| 5.6      | Interrupt Registers                  |        |

| Table of                                                                 | Contents                                                                                                                                                                                                      | Page                            |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.7                                  | Interrupt Node Enable Registers External Interrupt Control Registers Interrupt Flag Registers Interrupt Priority Registers Interrupt Flag Overview                                                            | 5-21<br>5-25<br>5-32            |

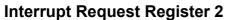

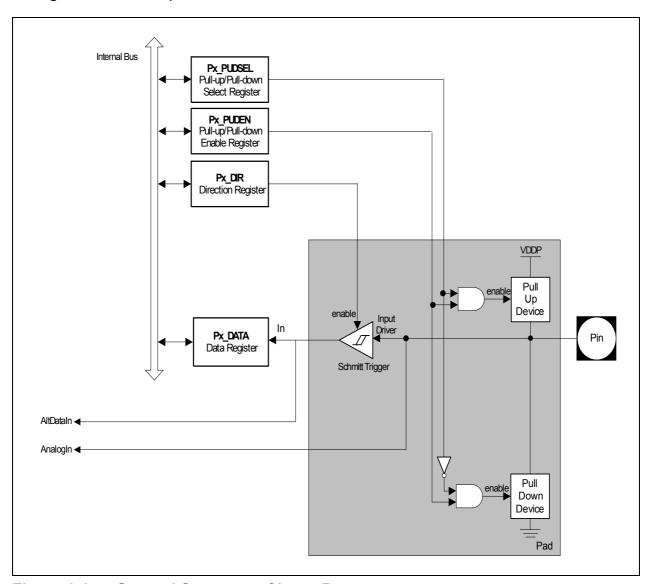

| 6<br>6.1<br>6.1.1<br>6.1.1.1<br>6.1.1.2<br>6.1.1.3<br>6.1.1.4<br>6.1.1.5 | Parallel Ports  General Port Operation  General Register Description  Data Register  Direction Register  Open Drain Control Register  Pull-Up/Pull-Down Device Register  Alternate Input and Output Functions | 6-2<br>6-5<br>6-6<br>6-7<br>6-8 |

| 6.2<br>6.3<br>6.3.1<br>6.3.1.1                                           | Register Map Port 0 Functions Register Description Port 1                                                                                                                                                     | 6-11<br>6-13<br>6-13<br>6-20    |

| 6.4.1<br>6.4.2<br>6.5<br>6.5.1<br>6.5.2                                  | Functions Register Description Port 2 Functions Register Description Register Description                                                                                                                     | 6-24<br>6-27<br>6-30            |

| 6.6<br>6.6.1<br>6.6.2<br>6.7<br>6.7.1<br>6.7.2                           | Port 3                                                                                                                                                                                                        | 6-32<br>6-36<br>6-39            |

| 6.8<br>6.8.1<br>6.8.2                                                    | Register Description Port 5 Functions Register Description                                                                                                                                                    | 6-46<br>6-46<br>6-50            |

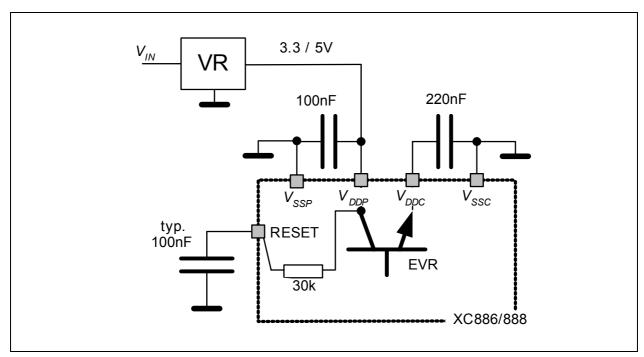

| <b>7</b> 7.1 7.2 7.2.1                                                   | Power Supply, Reset and Clock Management  Power Supply System with Embedded Voltage Regulator  Reset Control  Types of Resets  Power On Reset                                                                 | 7-1<br>7-3                      |

| 7.2.1.1<br>7.2.1.2<br>7.2.1.3<br>7.2.1.4<br>7.2.1.5                      | Power-On Reset  Hardware Reset  Watchdog Timer Reset  Power-Down Wake-Up Reset                                                                                                                                | 7-5<br>7-5                      |

| <i>1</i> .∠. 1.5                                                         | Brownout Reset                                                                                                                                                                                                | / -0                            |

| Table of                                                                                                                   | Contents                                                                                                                                                                                                                                             | Page                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.3.1<br>7.3.1.1<br>7.3.2<br>7.3.3<br>7.3.4                                              | Module Reset Behavior Booting Scheme Register Description Clock System Clock Generation Unit Functional Description Clock Source Control Clock Management Register Description                                                                       | 7-8<br>7-9<br>. 7-11<br>. 7-11<br>. 7-12<br>. 7-13                                     |

| 8<br>8.1<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2                                                                        | Power Saving Modes  Functional Description  Idle Mode  Slow-Down Mode  Power-down Mode  Peripheral Clock Management  Register Description                                                                                                            | 8-2<br>8-2<br>8-3<br>8-5                                                               |

| 9<br>9.1<br>9.1.1<br>9.2<br>9.3                                                                                            | Watchdog Timer  Functional Description  Module Suspend Control  Register Map  Register Description                                                                                                                                                   | 9-2<br>9-4<br>9-5                                                                      |

| 10<br>10.1<br>10.1.1<br>10.1.2<br>10.1.3<br>10.1.4<br>10.1.5<br>10.2<br>10.3<br>10.4<br>10.5<br>10.5.1<br>10.5.2<br>10.5.3 | Multiplication/Division Unit Functional Description Division Operation Normalize Shift Busy Flag Error Detection Interrupt Generation Low Power Mode Register Map Register Description Operand and Result Registers Control Register Status Register | . 10-2<br>. 10-3<br>. 10-3<br>. 10-4<br>. 10-4<br>. 10-5<br>. 10-6<br>. 10-7<br>. 10-9 |

| 11<br>11.1<br>11.2<br>11.2.1<br>11.2.2                                                                                     | CORDIC Coprocessor  Features  Functional Description  Operation of the CORDIC Coprocessor Interrupt                                                                                                                                                  | . 11-2<br>. 11-3<br>. 11-3                                                             |

| Table of           | Contents                                            | Page  |

|--------------------|-----------------------------------------------------|-------|

| 11.2.3             | Normalized Result Data                              | 11-4  |

| 11.2.4             | CORDIC Coprocessor Operating Modes                  |       |

| 11.2.4.1           | Domains of Convergence                              | 11-7  |

| 11.2.4.2           | Overflow Considerations                             | 11-8  |

| 11.2.5             | CORDIC Coprocessor Data Format                      | 11-8  |

| 11.2.6             | Accuracy of CORDIC Coprocessor                      | 11-9  |

| 11.2.7             | Performance of CORDIC Coprocessor                   |       |

| 11.3               | The CORDIC Coprocessor Kernel                       |       |

| 11.3.1             | Arctangent and Hyperbolic Arctangent Look-Up Tables |       |

| 11.3.2             | Linear Function Emulated Look-Up Table              |       |

| 11.4               | Low Power Mode                                      |       |

| 11.5               | Register Map                                        |       |

| 11.6               | Register Description                                |       |

| 11.6.1             | Control Register                                    |       |

| 11.6.2             | Status and Data Control Register                    |       |

| 11.6.3             | Data Registers                                      |       |

| 12                 | Serial Interfaces                                   |       |

| 12.1               | UART                                                |       |

| 12.1.1             | UART Modes                                          |       |

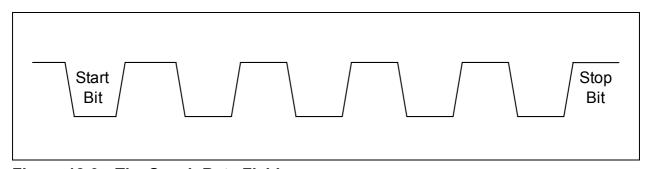

| 12.1.1.1           | Mode 0, 8-Bit Shift Register, Fixed Baud Rate       |       |

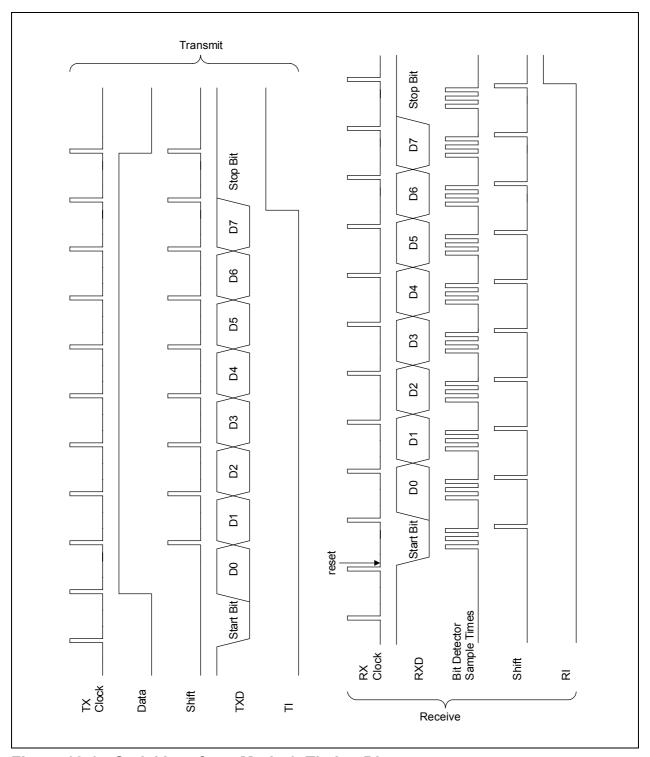

| 12.1.1.2           | Mode 1, 8-Bit UART, Variable Baud Rate              |       |

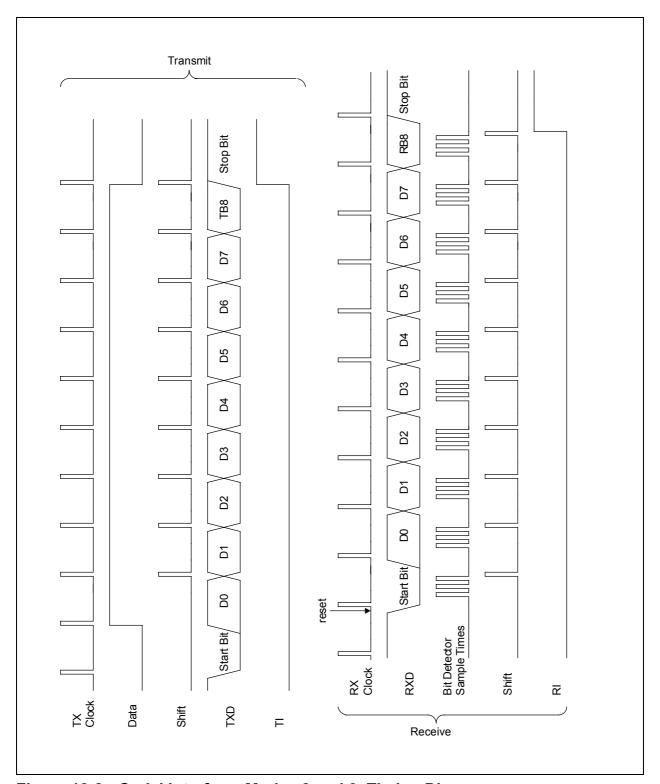

| 12.1.1.3           | Mode 2, 9-Bit UART, Fixed Baud Rate                 |       |

| 12.1.1.4<br>12.1.2 | Mode 3, 9-Bit UART, Variable Baud Rate              |       |

| 12.1.2             | Multiprocessor Communication                        |       |

| 12.1.3             | UART Register Description                           |       |

| 12.1.4             | Fixed Clock                                         |       |

| 12.1.4.2           | Dedicated Baud-rate Generator                       |       |

| 12.1.4.3           | Timer 1                                             |       |

| 12.1.5             | Port Control                                        |       |

| 12.1.6             | Low Power Mode                                      |       |

| 12.1.7             | Register Map                                        |       |

| 12.2               | LIN                                                 |       |

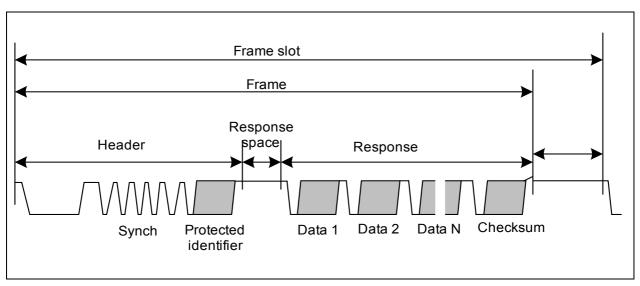

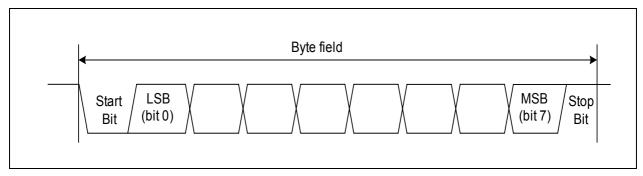

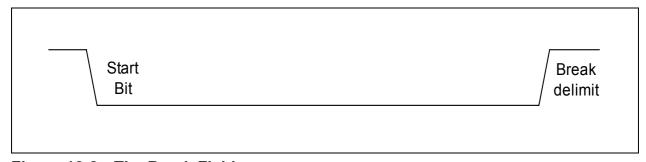

| 12.2.1             | LIN Protocol                                        |       |

| 12.2.2             | LIN Header Transmission                             |       |

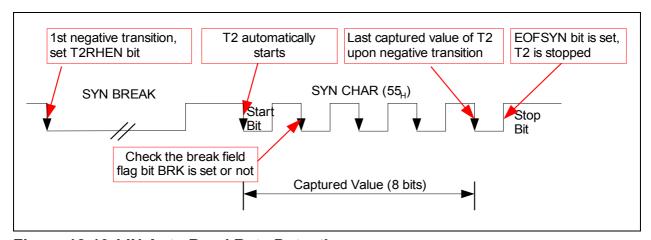

| 12.2.2.1           | Automatic Synchronization to the Host               | 12-28 |

| 12.2.2.2           | Baud Rate Detection of LIN                          |       |

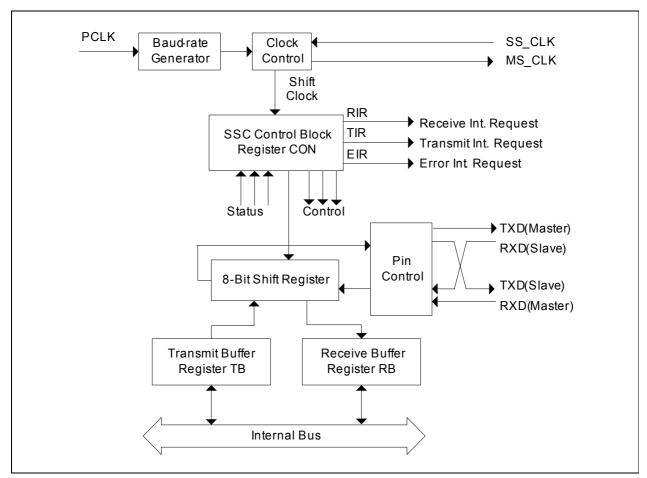

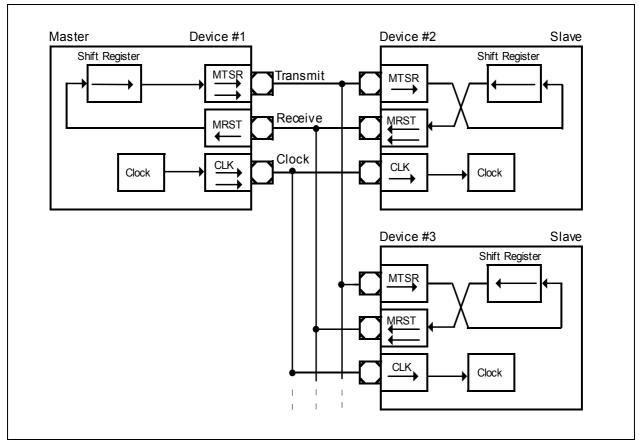

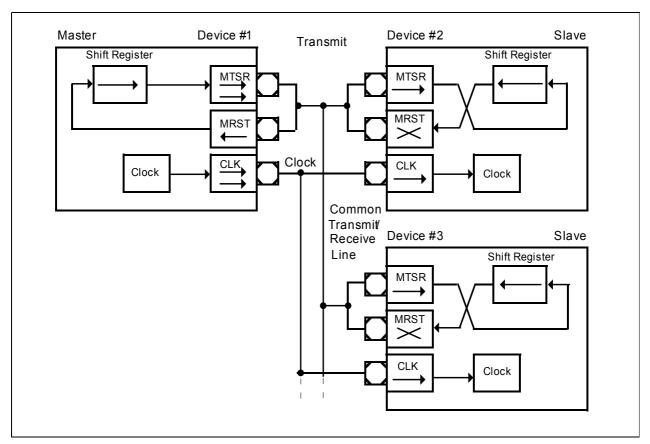

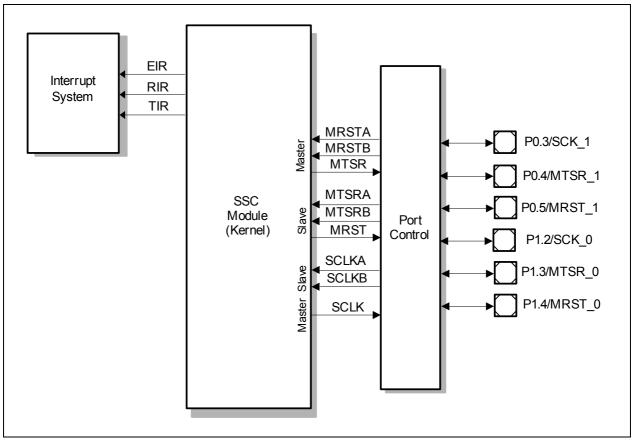

| 12.3               | High-Speed Synchronous Serial Interface             | 12-31 |

| 12.3.1             | General Operation                                   |       |

| 12.3.1.1           | Operating Mode Selection                            | 12-32 |

| 12.3.1.2           | Full-Duplex Operation                               |       |

| 12.3.1.3           | Half-Duplex Operation                               | 12-36 |

| Table of | Contents                             | Page   |

|----------|--------------------------------------|--------|

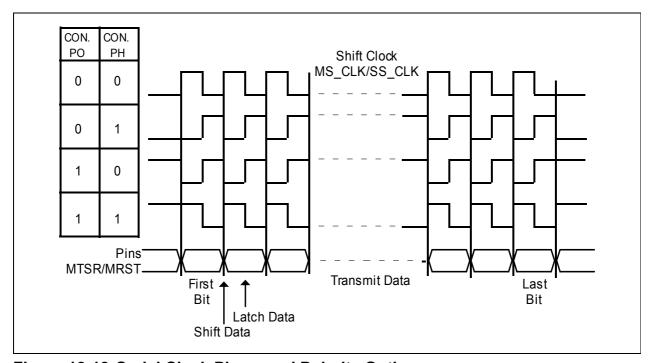

| 12.3.1.4 | Continuous Transfers                 | 12-37  |

| 12.3.1.5 | Port Control                         | 12-38  |

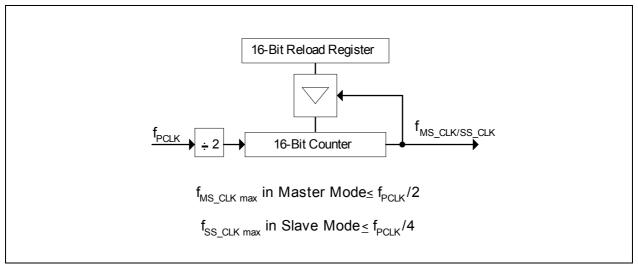

| 12.3.1.6 | Baud Rate Generation                 | 12-39  |

| 12.3.1.7 | Error Detection Mechanisms           | 12-41  |

| 12.3.2   | Interrupts                           |        |

| 12.3.3   | Low Power Mode                       |        |

| 12.3.4   | Register Map                         |        |

| 12.3.5   | Register Description                 |        |

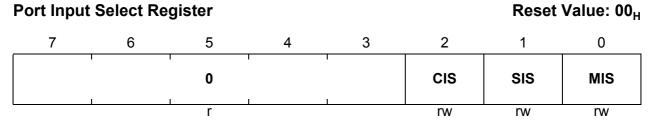

| 12.3.5.1 | Port Input Select Register           |        |

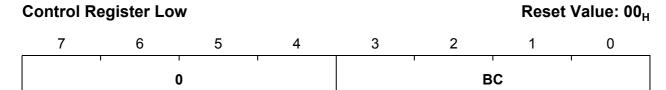

| 12.3.5.2 | Configuration Register               |        |

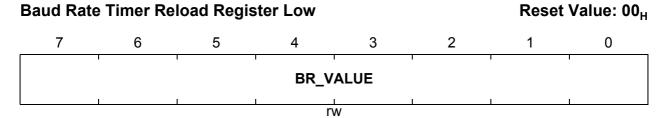

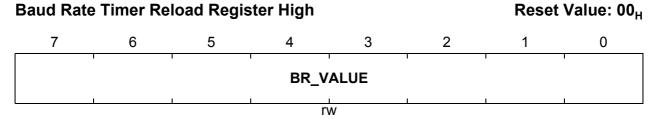

| 12.3.5.3 | Baud Rate Timer Reload Register      |        |

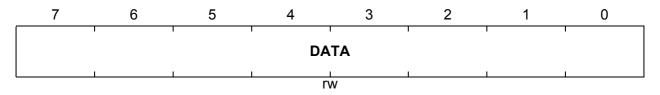

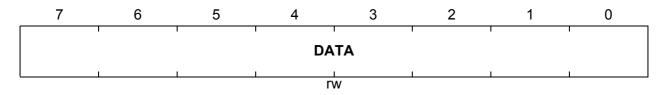

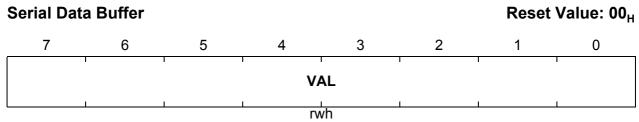

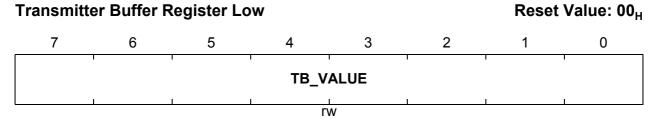

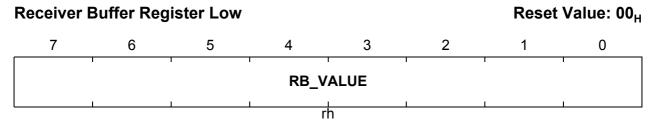

| 12.3.5.4 | Transmit and Receive Buffer Register | 12-51  |

| 13       | Timers                               |        |

| 13.1     | Timer 0 and Timer 1                  | . 13-2 |

| 13.1.1   | Basic Timer Operations               | . 13-2 |

| 13.1.2   | Timer Modes                          | . 13-3 |

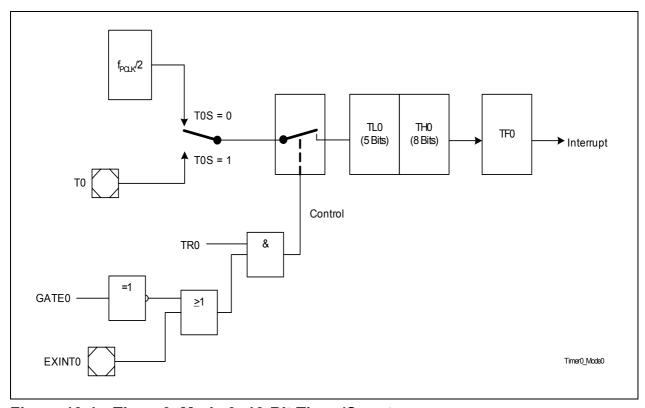

| 13.1.2.1 | Mode 0                               | . 13-4 |

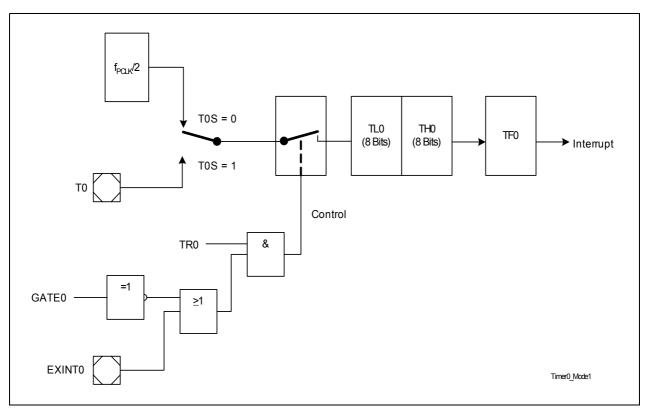

| 13.1.2.2 | Mode 1                               | . 13-5 |

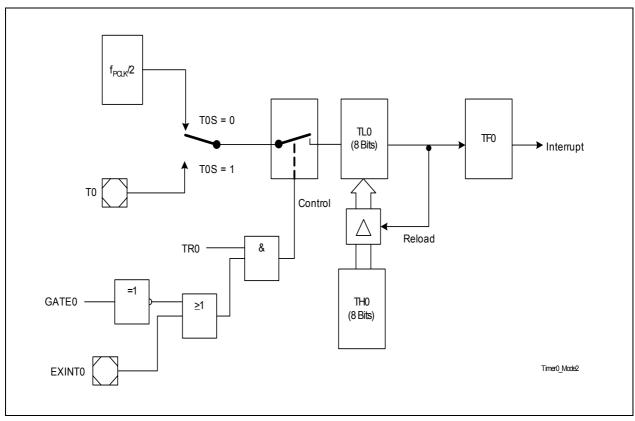

| 13.1.2.3 | Mode 2                               | . 13-6 |

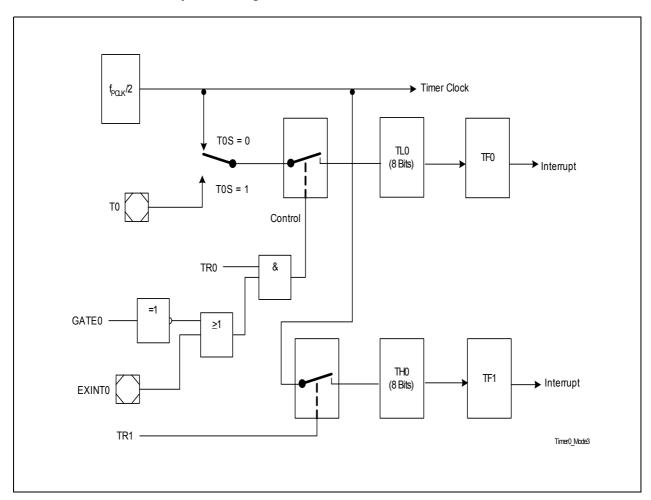

| 13.1.2.4 | Mode 3                               | . 13-7 |

| 13.1.3   | Port Control                         |        |

| 13.1.4   | Register Map                         |        |

| 13.1.5   | Register Description                 |        |

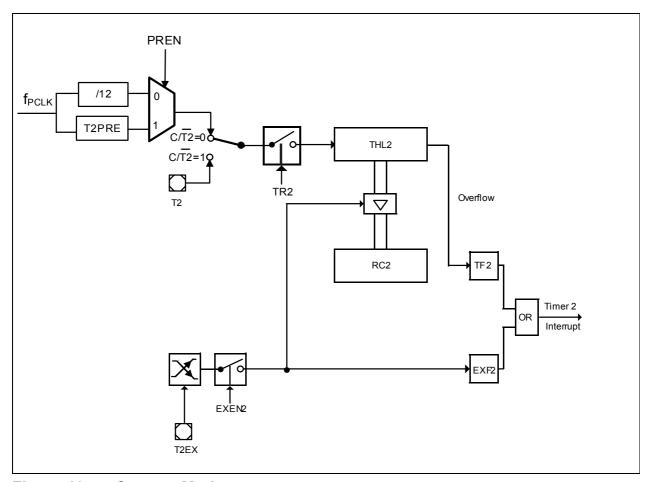

| 13.2     | Timer 2 and Timer 21                 | 13-14  |

| 13.2.1   | Basic Timer Operations               |        |

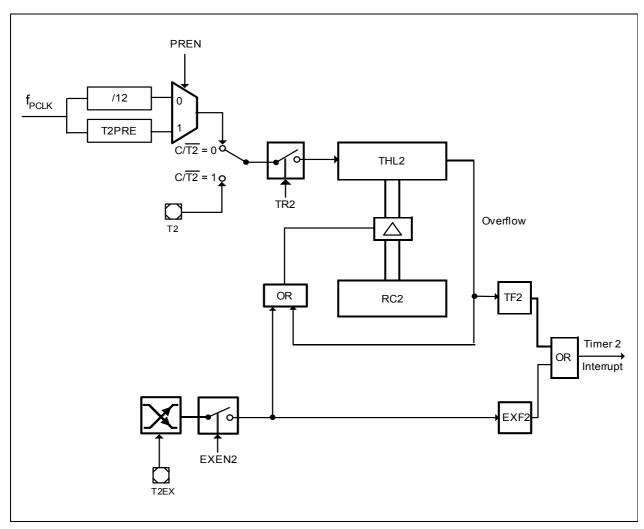

| 13.2.2   | Auto-Reload Mode                     | 13-14  |

| 13.2.2.1 | Up/Down Count Disabled               |        |

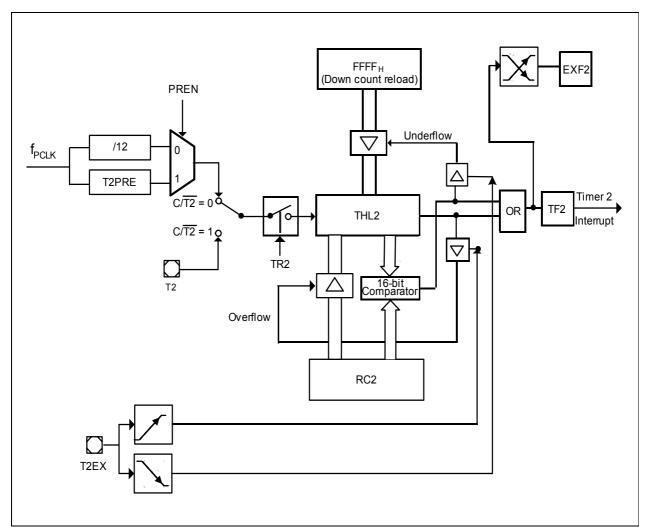

| 13.2.2.2 | Up/Down Count Enabled                |        |

| 13.2.3   | Capture Mode                         |        |

| 13.2.4   | Count Clock                          |        |

| 13.2.5   | External Interrupt Function          |        |

| 13.2.6   | Port Control                         |        |

| 13.2.7   | Low Power Mode                       |        |

| 13.2.8   | Module Suspend Control               |        |

| 13.2.9   | Register Map                         |        |

| 13.2.10  | Register Description                 | 13-24  |

| 14       | Capture/Compare Unit 6               |        |

| 14.1     | Functional Description               |        |

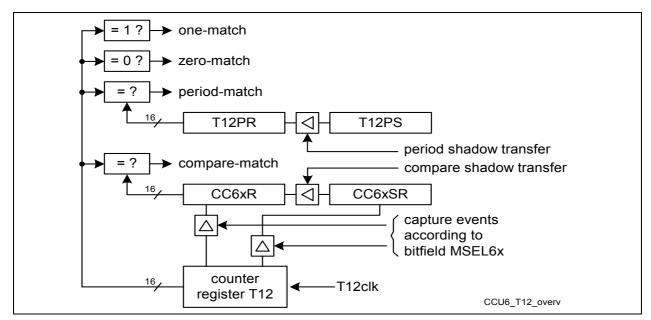

| 14.1.1   | Timer T12                            |        |

| 14.1.1.1 | Timer Configuration                  |        |

| 14.1.1.2 | Counting Rules                       | . 14-4 |

| Table of | Contents                                      | Page    |

|----------|-----------------------------------------------|---------|

| 14.1.1.3 | Switching Rules                               | 14-5    |

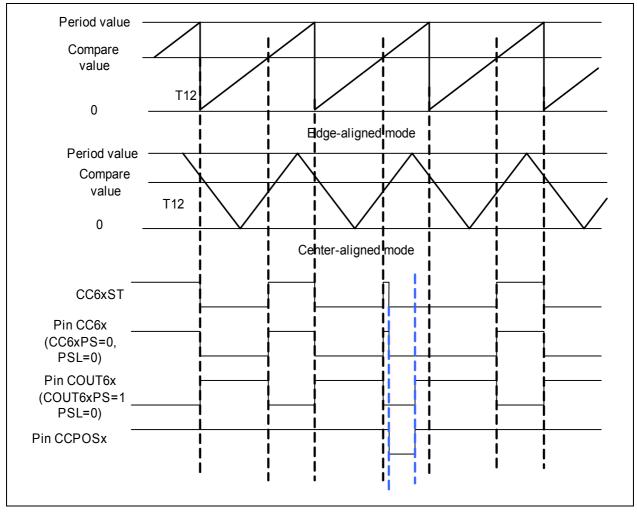

| 14.1.1.4 | Compare Mode of T12                           | 14-6    |

| 14.1.1.5 | Duty Cycle of 0% and 100%                     | 14-8    |

| 14.1.1.6 | Dead-time Generation                          | 14-8    |

| 14.1.1.7 | Capture Mode                                  | 14-9    |

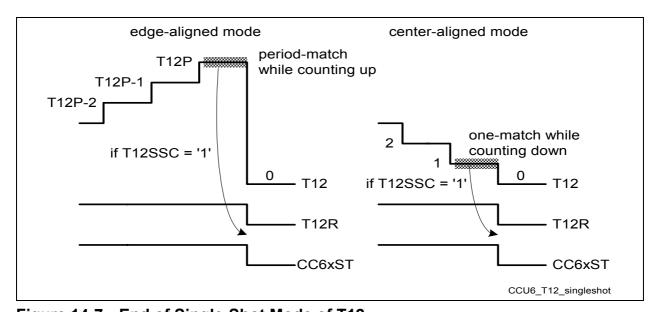

| 14.1.1.8 | Single-Shot Mode                              | . 14-10 |

| 14.1.1.9 | Hysteresis-Like Control Mode                  | . 14-10 |

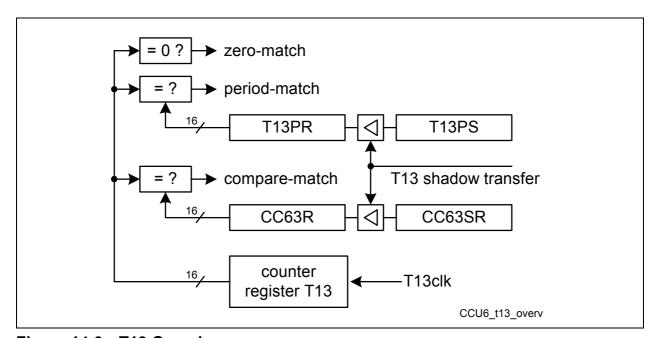

| 14.1.2   | Timer T13                                     | . 14-12 |

| 14.1.2.1 | Timer Configuration                           | . 14-12 |

| 14.1.2.2 | Compare Mode                                  | . 14-13 |

| 14.1.2.3 | Single-Shot Mode                              | . 14-13 |

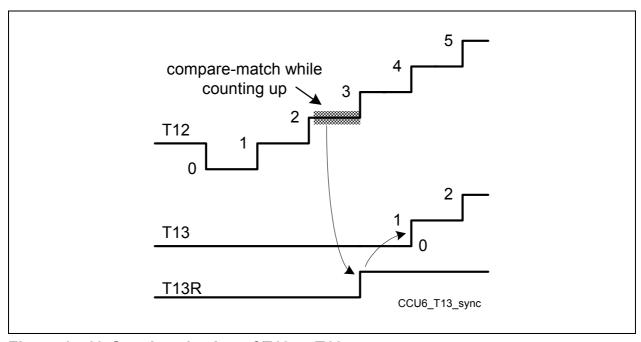

| 14.1.2.4 | Synchronization of T13 to T12                 | . 14-13 |

| 14.1.3   | Modulation Control                            | . 14-15 |

| 14.1.4   | Trap Handling                                 |         |

| 14.1.5   | Multi-Channel Mode                            | . 14-19 |

| 14.1.6   | Hall Sensor Mode                              | . 14-21 |

| 14.1.6.1 | Sampling of the Hall Pattern                  |         |

| 14.1.6.2 | Brushless-DC Control                          | . 14-22 |

| 14.1.7   | Interrupt Generation                          | . 14-25 |

| 14.1.8   | Low Power Mode                                | . 14-26 |

| 14.1.9   | Module Suspend Control                        |         |

| 14.1.10  | Port Connection                               |         |

| 14.2     | Register Map                                  |         |

| 14.3     | Register Description                          |         |

| 14.3.1   | System Registers                              |         |

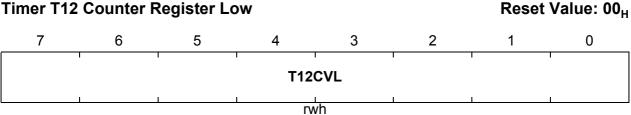

| 14.3.2   | Timer 12 – Related Registers                  |         |

| 14.3.3   | Timer 13 – Related Registers                  |         |

| 14.3.4   | Capture/Compare Control Registers             |         |

| 14.3.5   | Global Modulation Control Registers           |         |

| 14.3.6   | Multi-Channel Modulation Control Registers    |         |

| 14.3.7   | Interrupt Control Registers                   | . 14-79 |

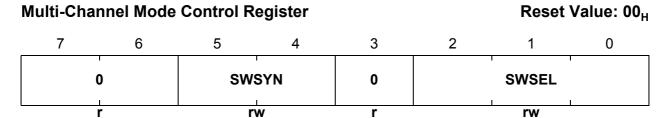

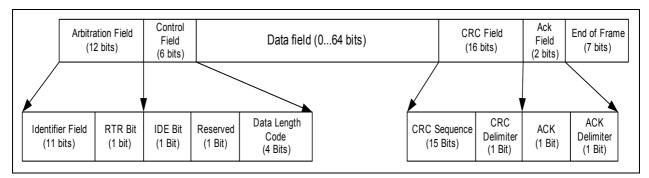

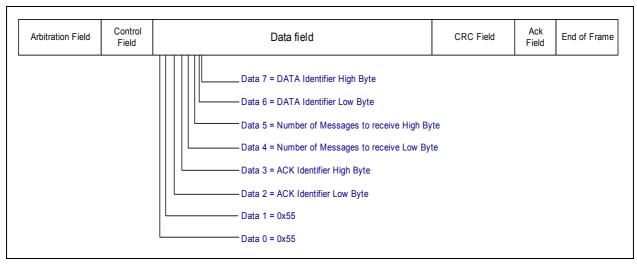

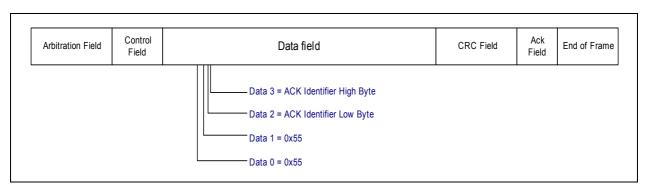

| 15       | Controller Area Network (MultiCAN) Controller | 15-1    |

| 15.1     | MultiCAN Kernel Functional Description        | 15-4    |

| 15.1.1   | Module Structure                              | 15-4    |

| 15.1.2   | Clock Control                                 | 15-7    |

| 15.1.3   | CAN Node Control                              | 15-8    |

| 15.1.3.1 | Bit Timing Unit                               | 15-8    |

| 15.1.3.2 | Bitstream Processor                           | 15-9    |

| 15.1.3.3 | Error Handling Unit                           | . 15-10 |

| 15.1.3.4 | CAN Frame Counter                             | . 15-11 |

| 15.1.3.5 | CAN Node Interrupts                           | . 15-11 |

| 15.1.4   | Message Object List Structure                 | . 15-13 |

| Table of | Contents                          | Page   |

|----------|-----------------------------------|--------|

| 15.1.4.1 | Basics                            | 15-13  |

| 15.1.4.2 | List of Unallocated Elements      | 15-14  |

| 15.1.4.3 | Connection to the CAN Nodes       | 15-14  |

| 15.1.4.4 | List Command Panel                | 15-15  |

| 15.1.5   | CAN Node Analysis Features        | 15-18  |

| 15.1.5.1 | Analyze Mode                      | 15-18  |

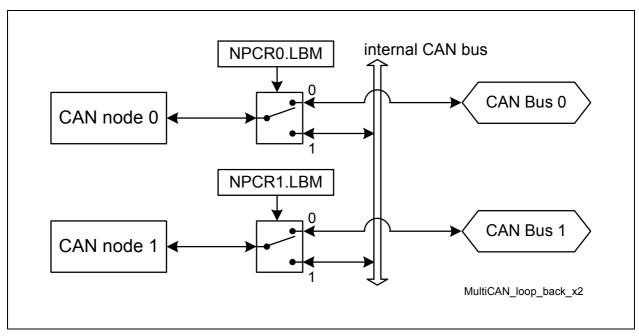

| 15.1.5.2 | Loop-Back Mode                    | 15-18  |

| 15.1.5.3 | Bit Timing Analysis               | 15-19  |

| 15.1.6   | Message Acceptance Filtering      | 15-21  |

| 15.1.6.1 | Receive Acceptance Filtering      | 15-21  |

| 15.1.6.2 | Transmit Acceptance Filtering     | 15-22  |

| 15.1.7   | Message Postprocessing            | 15-23  |

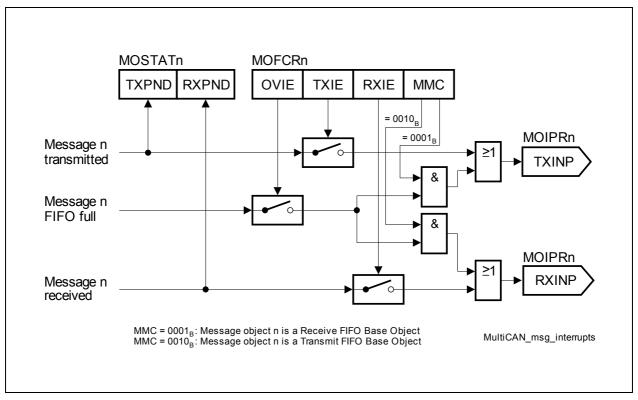

| 15.1.7.1 | Message Interrupts                | 15-23  |

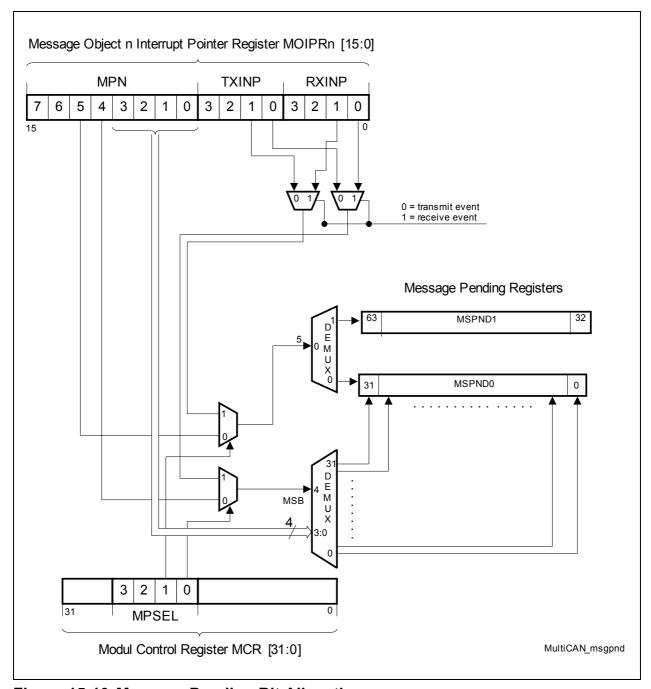

| 15.1.7.2 | Pending Messages                  | 15-25  |

| 15.1.8   | Message Object Data Handling      | 15-27  |

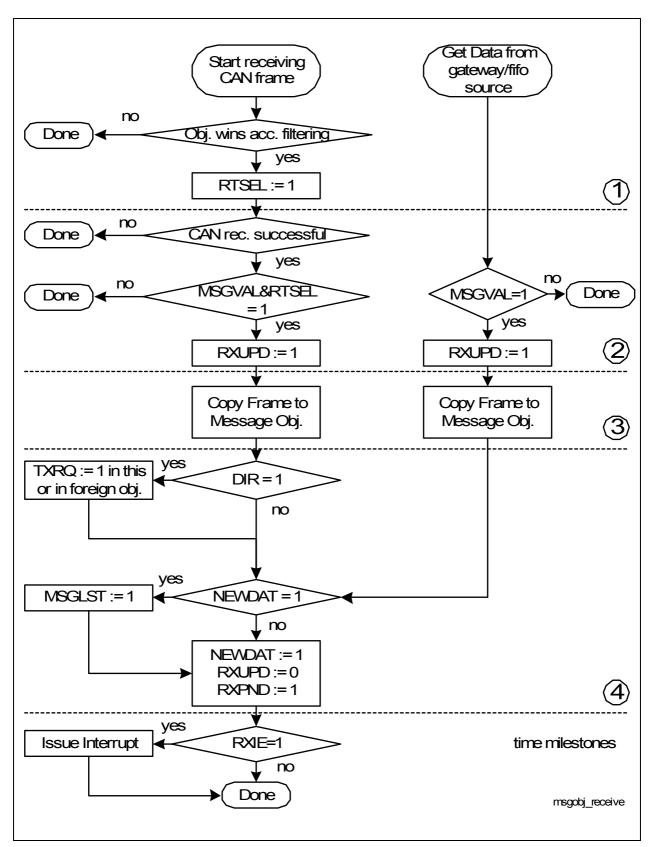

| 15.1.8.1 | Frame Reception                   | 15-27  |

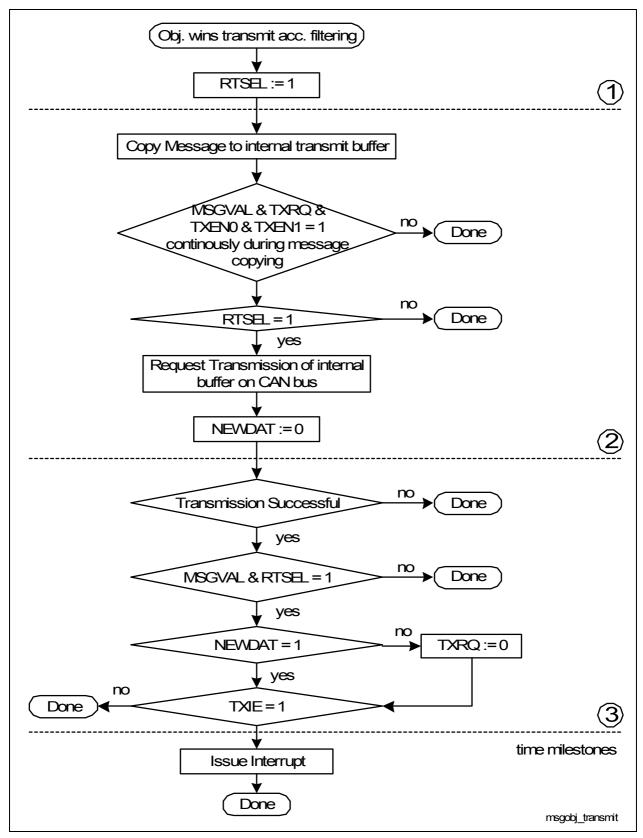

| 15.1.8.2 | Frame Transmission                | 15-30  |

| 15.1.9   | Message Object Functionality      | 15-33  |

| 15.1.9.1 | Standard Message Object           | 15-33  |

| 15.1.9.2 | Single Data Transfer Mode         | 15-33  |

| 15.1.9.3 | Single Transmit Trial             |        |

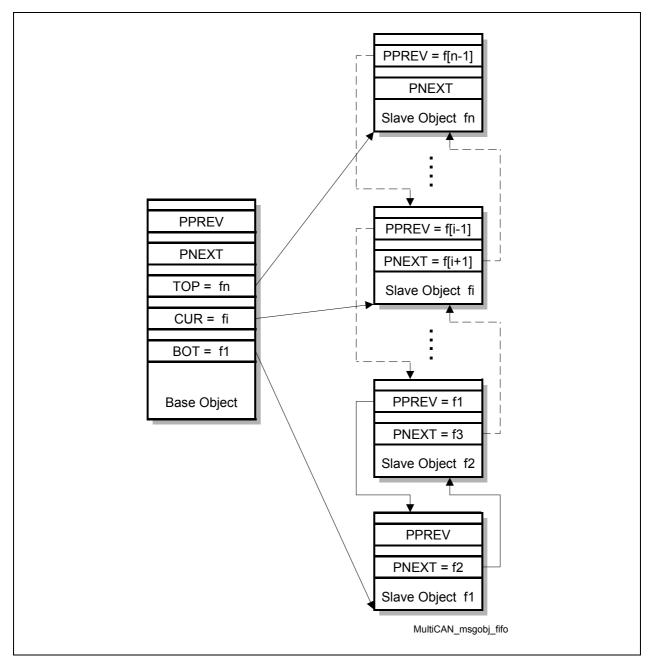

| 15.1.9.4 | Message Object FIFO Structure     |        |

| 15.1.9.5 | Receive FIFO                      |        |

| 15.1.9.6 | Transmit FIFO                     |        |

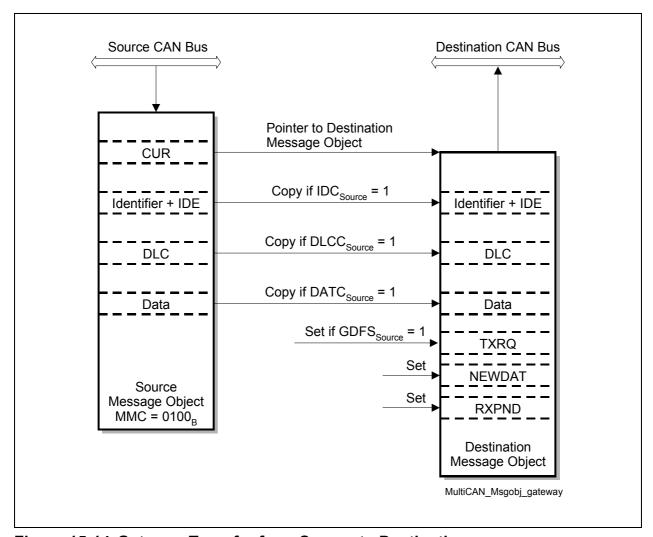

| 15.1.9.7 | Gateway Mode                      |        |

| 15.1.9.8 | Foreign Remote Requests           |        |

| 15.1.10  | Access Mediator                   |        |

| 15.1.11  | Port Control                      |        |

| 15.1.12  | Low Power Mode                    |        |

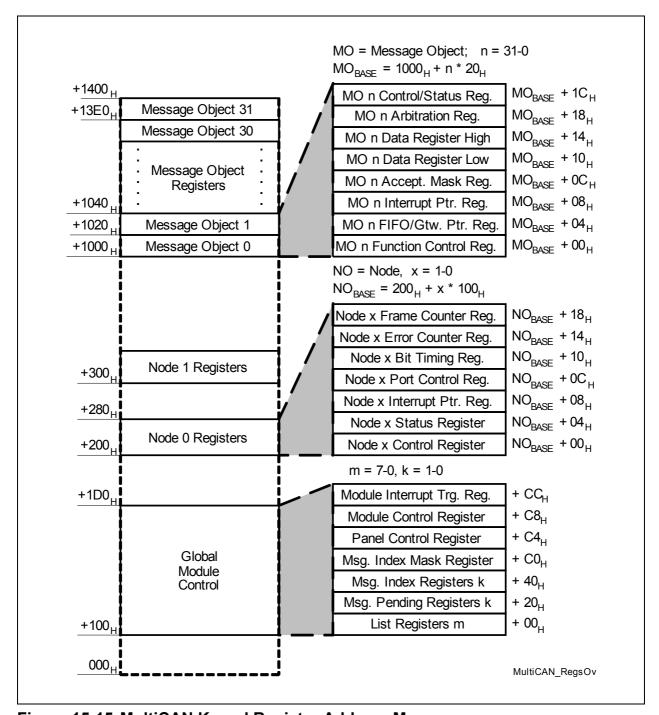

| 15.2     | Registers Description             |        |

| 15.2.1   | Global Module Registers           |        |

| 15.2.2   | CAN Node Registers                |        |

| 15.2.3   | Message Object Registers          |        |

| 15.2.4   | MultiCAN Access Mediator Register | 15-97  |

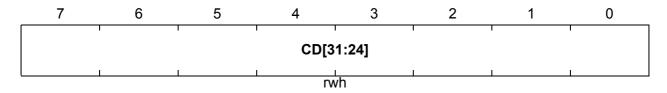

| 16       | Analog-to-Digital Converter       | . 16-1 |

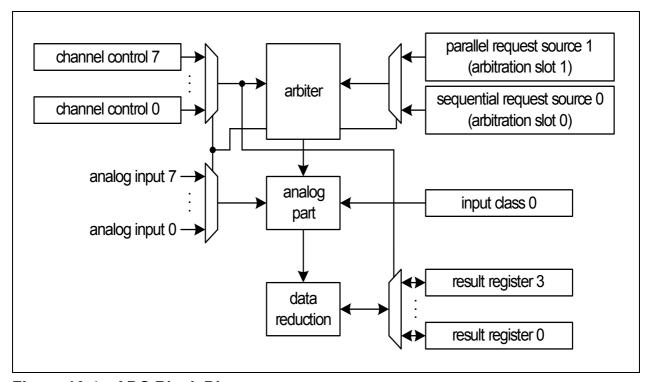

| 16.1     | Structure Overview                |        |

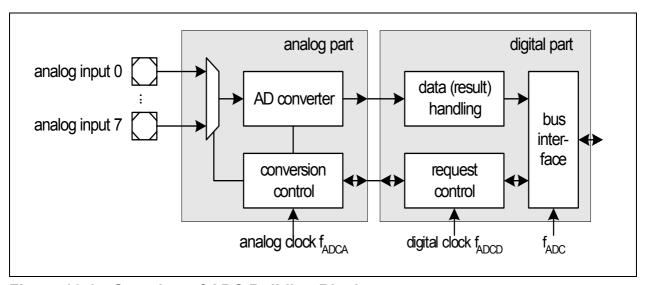

| 16.2     | Clocking Scheme                   |        |

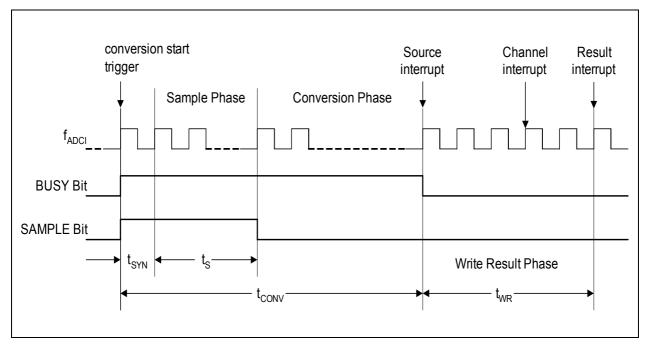

| 16.2.1   | Conversion Timing                 |        |

| 16.3     | Low Power Mode                    |        |

| 16.4     | Functional Description            | . 16-8 |

| 16.4.1   | Request Source Arbiter            |        |

| 16.4.2   | Conversion Start Modes            | 16-10  |

| Table of | Contents                           | Page    |

|----------|------------------------------------|---------|

| 16.4.3   | Channel Control                    | . 16-10 |

| 16.4.4   | Sequential Request Source          | . 16-11 |

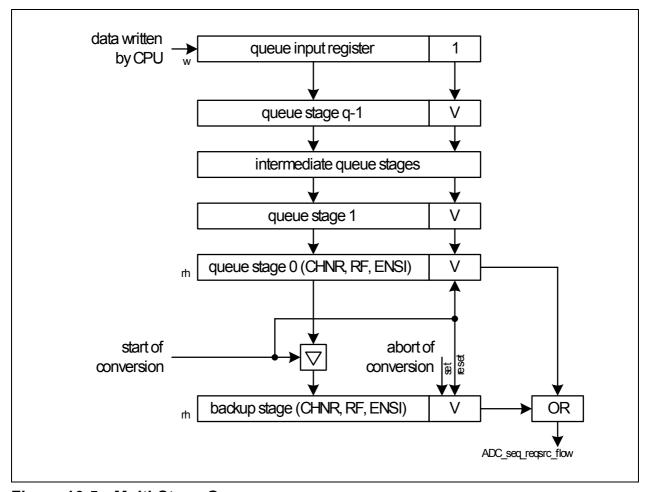

| 16.4.4.1 | Overview                           | . 16-11 |

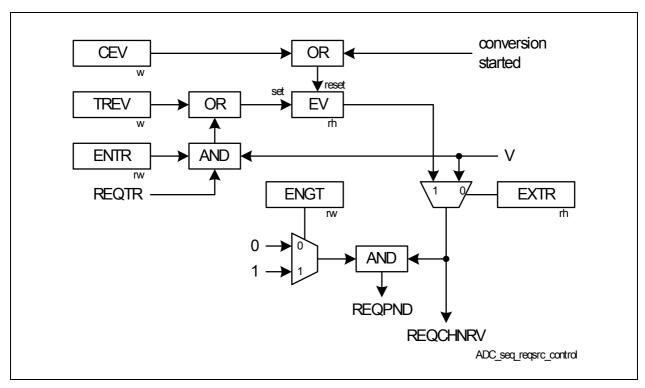

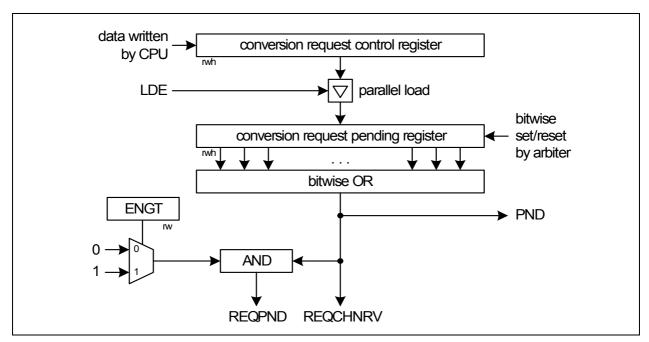

| 16.4.4.2 | Request Source Control             | . 16-13 |

| 16.4.5   | Parallel Request Source            | . 16-14 |

| 16.4.5.1 | Overview                           | . 16-14 |

| 16.4.5.2 | Request Source Control             | . 16-15 |

| 16.4.5.3 | External Trigger                   | . 16-16 |

| 16.4.5.4 | Software Control                   | . 16-16 |

| 16.4.5.5 | Autoscan                           | . 16-16 |

| 16.4.6   | Wait-for-Read Mode                 | . 16-17 |

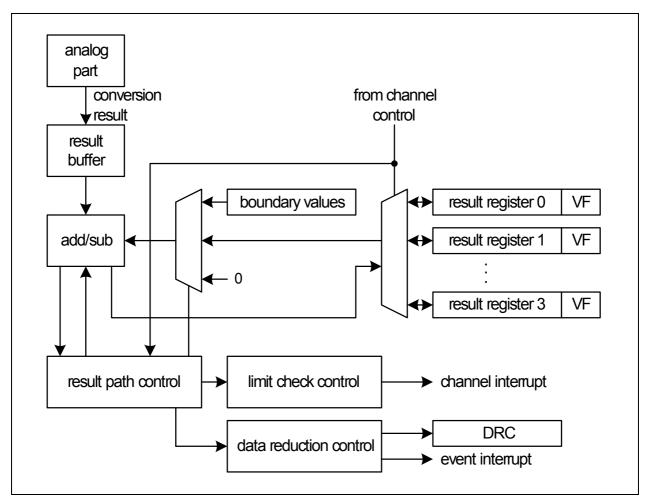

| 16.4.7   | Result Generation                  | . 16-17 |

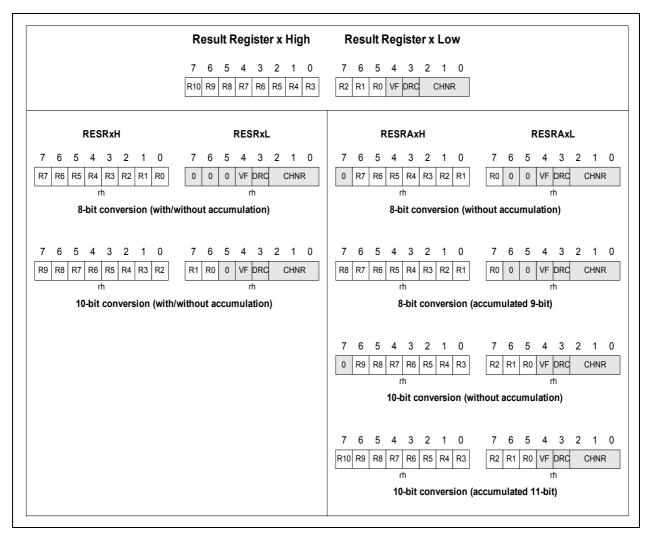

| 16.4.7.1 | Overview                           | . 16-17 |

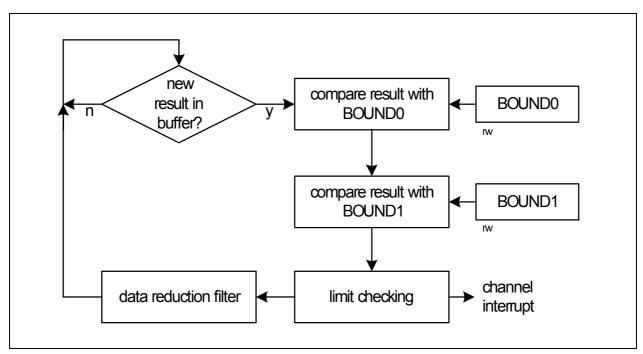

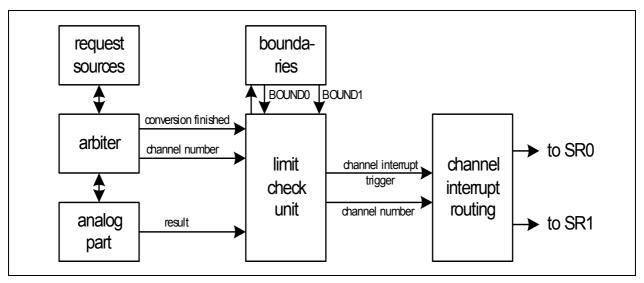

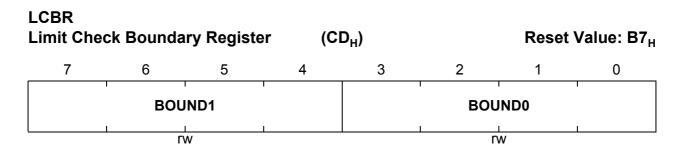

| 16.4.7.2 | Limit Checking                     | . 16-19 |

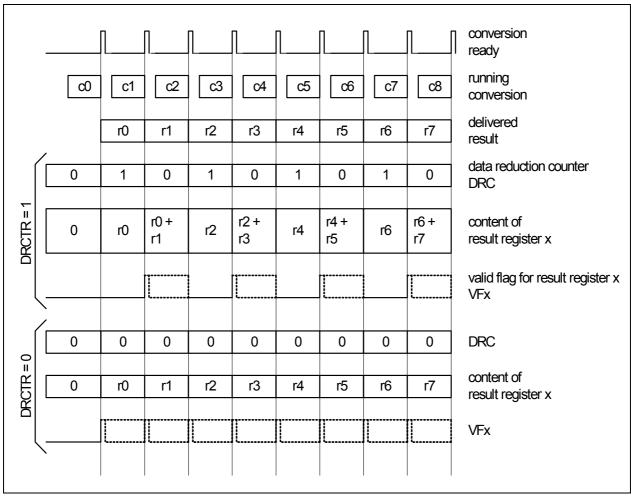

| 16.4.7.3 | Data Reduction Filter              | . 16-20 |

| 16.4.7.4 | Result Register View               | . 16-21 |

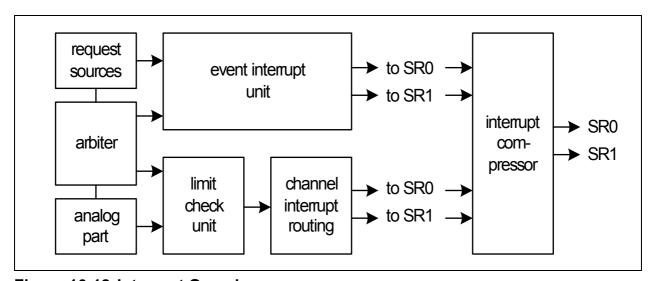

| 16.4.8   | Interrupts                         | . 16-23 |

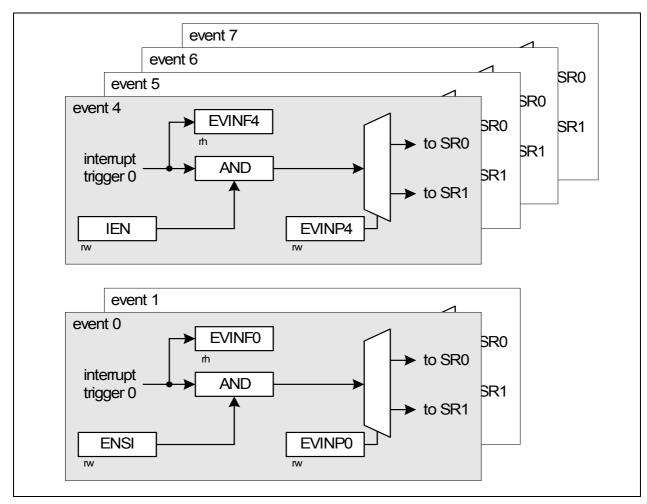

| 16.4.8.1 | Event Interrupts                   | . 16-24 |

| 16.4.8.2 | Channel Interrupts                 | . 16-25 |

| 16.4.9   | External Trigger Inputs            | . 16-27 |

| 16.5     | ADC Module Initialization Sequence |         |

| 16.6     | Register Map                       | . 16-30 |

| 16.7     | Register Description               |         |

| 16.7.1   | General Function Registers         | . 16-33 |

| 16.7.2   | Priority and Arbitration Register  |         |

| 16.7.3   | External Trigger Control Register  | . 16-38 |

| 16.7.4   | Channel Control Registers          | . 16-39 |

| 16.7.5   | Input Class Register               | . 16-40 |

| 16.7.6   | Sequential Source Registers        | . 16-41 |

| 16.7.7   | Parallel Source Registers          | . 16-49 |

| 16.7.8   | Result Registers                   | . 16-53 |

| 16.7.9   | Interrupt Registers                |         |

| 17       | On-Chip Debug Support              | 17-1    |

| 17.1     | Features                           |         |

| 17.2     | Functional Description             |         |

| 17.3     | Debugging                          |         |

| 17.3.1   | Debug Events                       |         |

| 17.3.1.1 | Hardware Breakpoints               |         |

| 17.3.1.2 | Software Breakpoints               |         |

| 17.3.1.3 | External Breaks                    |         |

| 17.3.1.4 | NMI-mode priority over Debug-mode  |         |

| 17.3.2   | Debug Actions                      |         |

| Table of                                                                                                                                                                                                                                                                                   | Contents                                                                                                                                           | Page                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17.3.2.1<br>17.3.2.2<br>17.4<br>17.5<br>17.5.1<br>17.5.2<br>17.6                                                                                                                                                                                                                           | Call the Monitor Program Activate the MBC pin  Debug Suspend Control  Register Description Monitor Work Register 2 Input Select Registers  JTAG ID | . 17-7<br>. 17-7<br>. 17-9<br>17-10                                                                                                                                                    |

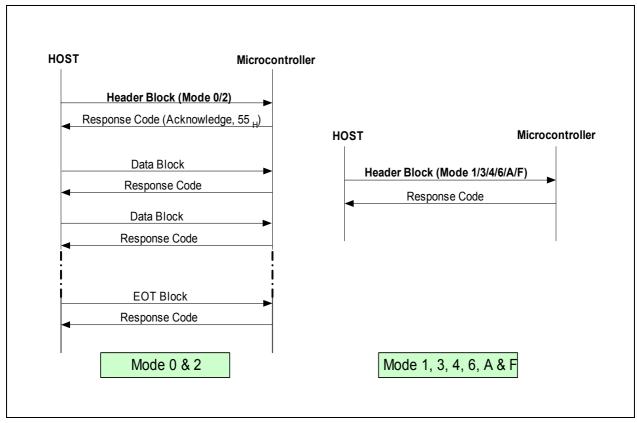

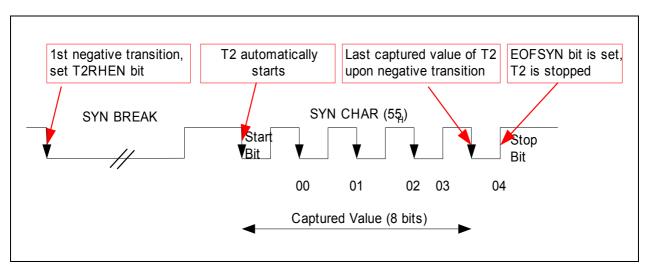

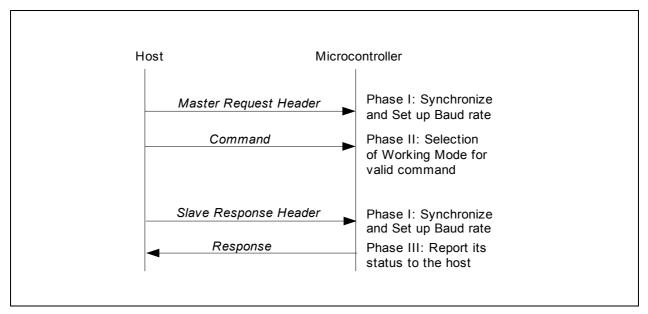

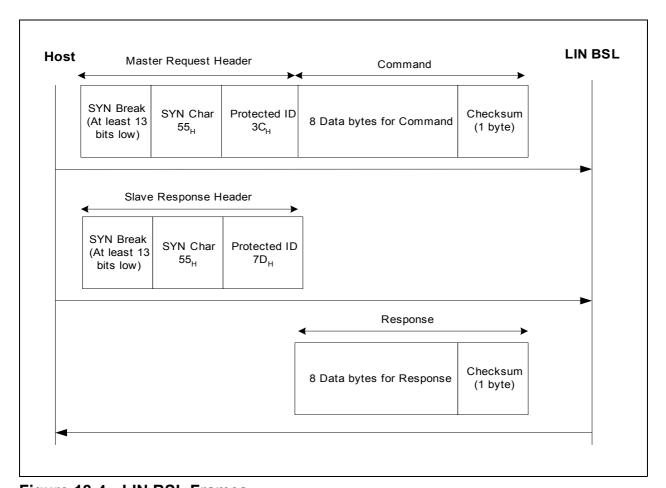

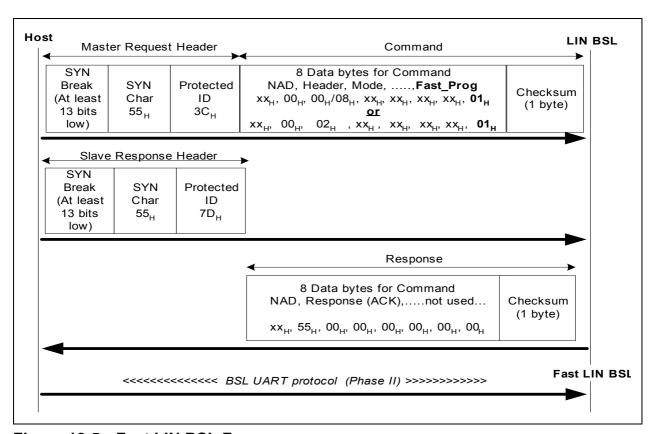

| 18<br>18.1<br>18.1.1<br>18.1.1.1<br>18.1.1.2<br>18.1.2.1<br>18.1.2.1<br>18.1.2.2<br>18.1.2.3<br>18.1.2.3<br>18.1.2.5<br>18.1.2.6<br>18.1.2.7<br>18.1.3.1<br>18.1.3.2<br>18.1.3.3<br>18.1.3.4<br>18.1.3.5<br>18.1.3.6<br>18.1.3.7<br>18.1.3.8<br>18.1.3.9<br>18.1.3.10<br>18.1.3.11<br>18.2 | User Defined Parameter for LIN BSL                                                                                                                 | . 18-2<br>. 18-3<br>. 18-4<br>. 18-6<br>. 18-8<br>. 18-9<br>18-10<br>18-12<br>18-14<br>18-15<br>18-16<br>18-17<br>18-19<br>18-21<br>18-21<br>18-24<br>18-24<br>18-25<br>18-25<br>18-27 |

| 18.2.1<br>18.2.2<br>18.2.3                                                                                                                                                                                                                                                                 | Communication protocol                                                                                                                             | 18-30                                                                                                                                                                                  |

| <b>19</b><br>19.1<br>19.2                                                                                                                                                                                                                                                                  | Index                                                                                                                                              | . 19-1                                                                                                                                                                                 |

# 1 Introduction

The XC886/888 is a member of the high-performance XC800 family of 8-bit microcontrollers. It is based on the XC800 Core that is compatible with the industry standard 8051 processor. Furthermore, the XC886/888 is a superset of the Infineon XC866 8-bit microcontroller, thus offering an easy upgrade path for XC866 users.

The XC886/888 features both a CAN controller and LIN support integrated on a single chip to provide advance networking capabilities. The on-chip CAN module reduces the CPU load by performing most of the functions required by the networking protocol (masking, filtering and buffering of CAN frames).

The XC886/888 is equipped with either embedded Flash memory to offer high flexibility in development and ramp-up, or compatible ROM versions to provide cost-saving potential in high-volume production. The XC886/888 memory protection strategy features read-out protection of user intellectual property (IP), along with Flash program and erase protection to prevent data corruption.

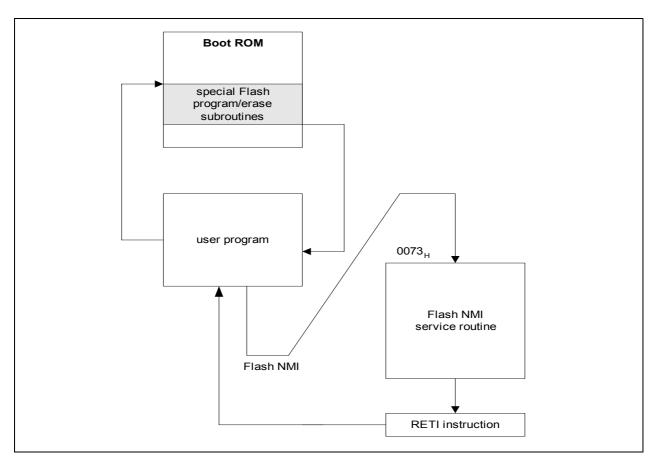

The multi-bank Flash architecture supports In-Application Programming (IAP), allowing user program to modify Flash contents during program execution. In-System Programming (ISP) is available through the Boot ROM-based BootStrap Loader (BSL), enabling convenient programming and erasing of the embedded Flash via an external host (e.g., personal computer).

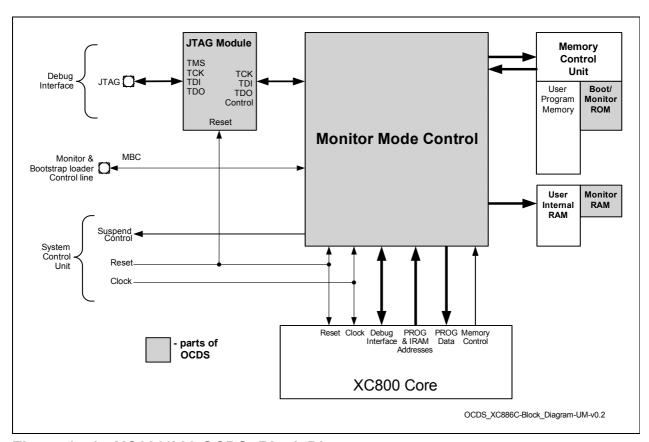

Other key features include a Capture/Compare Unit 6 (CCU6) for the generation of pulse width modulated signal with special modes for motor control; a 10-bit Analog-to-Digital Converter (ADC) with extended functionalities such as autoscan and result accumulation for anti-aliasing filtering or for averaging; a Multiplication/Division Unit (MDU) to support the XC800 Core in math-intensive real-time control applications; a CORDIC (COrdinate Rotation DIgital Computer) Coprocessor for high-speed computation of trigonometric, linear or hyperbolic functions; and an On-Chip Debug Support (OCDS) unit for software development and debugging of XC800-based systems.

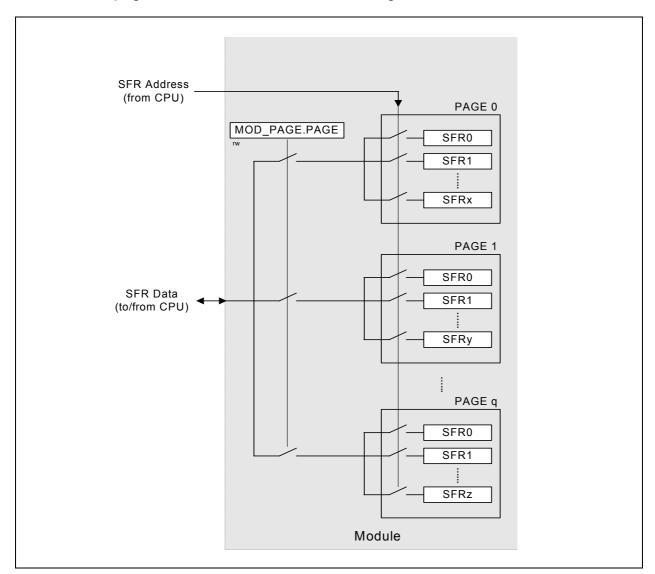

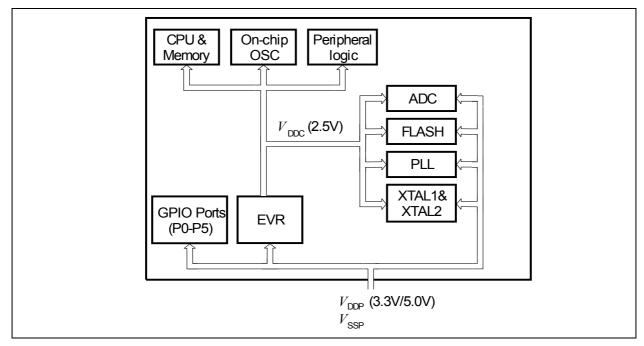

The XC886/888 also features an on-chip oscillator and an integrated voltage regulator to allow a single voltage supply of 3.3 or 5.0 V. For low power applications, various power saving modes are available for selection by the user. Control of the numerous on-chip peripheral functionalities is achieved by extending the Special Function Register (SFR) address range with an intelligent paging mechanism optimized for interrupt handling.

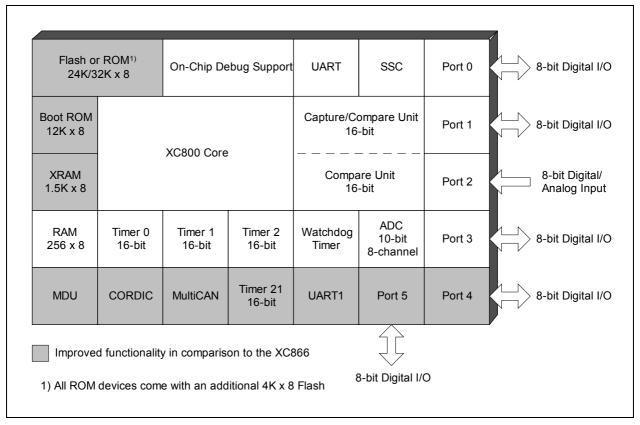

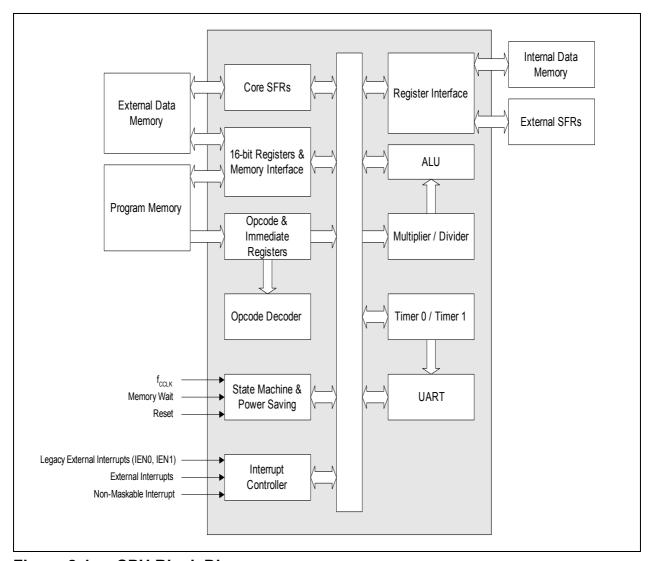

Figure 1-1 shows the functional units of the XC886/888.

Figure 1-1 XC886/888 Functional Units

The XC886/888 product family features devices with different configurations, program memory sizes, package options, temperature and quality profiles (Automotive or Industrial), to offer cost-effective solutions for different application requirements.

The list of XC886/888 device configurations are summarized in **Table 1-1**. For each configuration, 2 types of packages are available:

- TQFP-48, which is denoted by XC886 and;

- TQFP-64, which is denoted by XC888.

**Table 1-1** Device Configuration

| <b>Device Name</b> | CAN<br>Module | LIN BSL<br>Support | MDU<br>Module |

|--------------------|---------------|--------------------|---------------|

| XC886/888          | No            | No                 | No            |

| XC886/888C         | Yes           | No                 | No            |

| XC886/888CM        | Yes           | No                 | Yes           |

| XC886/888LM        | No            | Yes                | Yes           |

| XC886/888CLM       | Yes           | Yes                | Yes           |

Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module and UART BSL.

From these 10 different combinations of configuration and package type, each are further made available in many sales types, which are grouped according to device type, program memory sizes, power supply voltage, temperature and quality profile (Automotive or Industrial), as shown in **Table 1-2**.

Table 1-2 Device Profile

| Sales Type               | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|--------------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAA-XC886*-8FFA 5V       | Flash          | 32                            | 5.0                    | -40 to 140               | Automotive         |

| SAA-XC886*-6FFA 5V       | Flash          | 24                            | 5.0                    | -40 to 140               | Automotive         |

| SAK-XC886*/888*-8FFA 5V  | Flash          | 32                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 5V  | Flash          | 24                            | 5.0                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 5V  | Flash          | 32                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 5V  | Flash          | 24                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 5V  | Flash          | 32                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 5V  | Flash          | 24                            | 5.0                    | -40 to 85                | Industrial         |

| SAK-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Industrial         |

Note: The asterisk (\*) above denotes the device configuration letters from **Table 1-1**. Corresponding ROM derivatives will be available on request.

The term "XC886/888" in this document refers to all devices of the XC886/888 family unless stated otherwise.

# 1.1 Feature Summary

The following list summarizes the main features of the XC886/888:

- High-performance XC800 Core

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 12 Kbytes of Boot ROM

- 256 bytes of RAM

- 1.5 Kbytes of XRAM

- 24/32 Kbytes of Flash; or

24/32 Kbytes of ROM, with additional 4 Kbytes of Flash (includes memory protection strategy)

- I/O port supply at 3.3 or 5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

- Power-on reset generation

- · Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Six ports

- Up to 48 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Four 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 and Timer 21 (T2 and T21)

- Multiplication/Division Unit for arithmetic calculation (MDU)

- Software libraries to support floating point and MDU calculations

- CORDIC Coprocessor for computation of trigonometric, hyperbolic and linear functions

- MultiCAN with 2 nodes, 32 message objects

- Capture/compare unit for PWM signal generation (CCU6)

- Two full-duplex serial interfaces (UART and UART1)

- Synchronous serial channel (SSC)

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 12-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- PG-TQFP-48 or PG-TQFP-64 pin packages

- Temperature range T<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

- SAA (-40 to 140 °C)<sup>1)</sup>

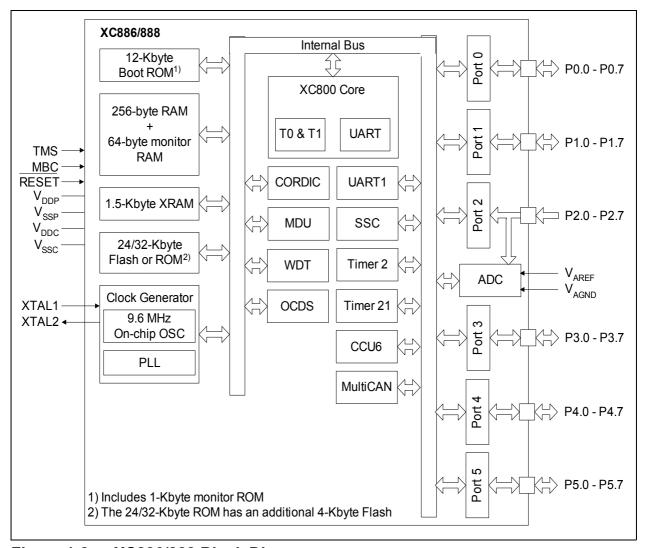

The block diagram of the XC886/888 is shown in Figure 1-2.

Figure 1-2 XC886/888 Block Diagram

<sup>1)</sup> The SAA temperature variant is available only in PG-TQFP-48 pin package, with 5.0 V power supply voltage.

# 1.2 Pin Configuration

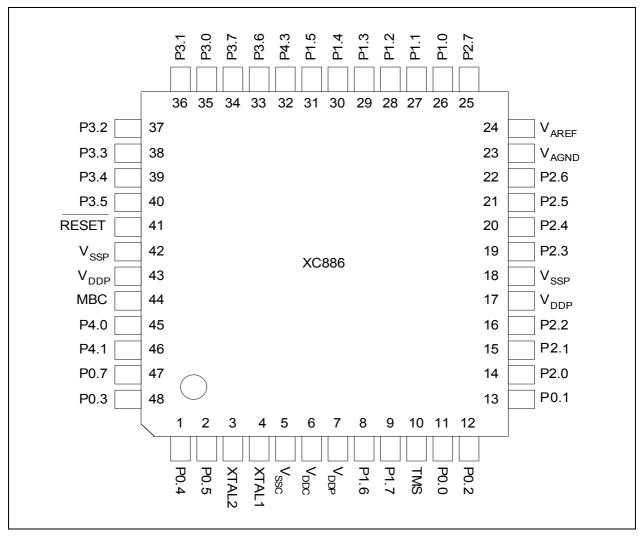

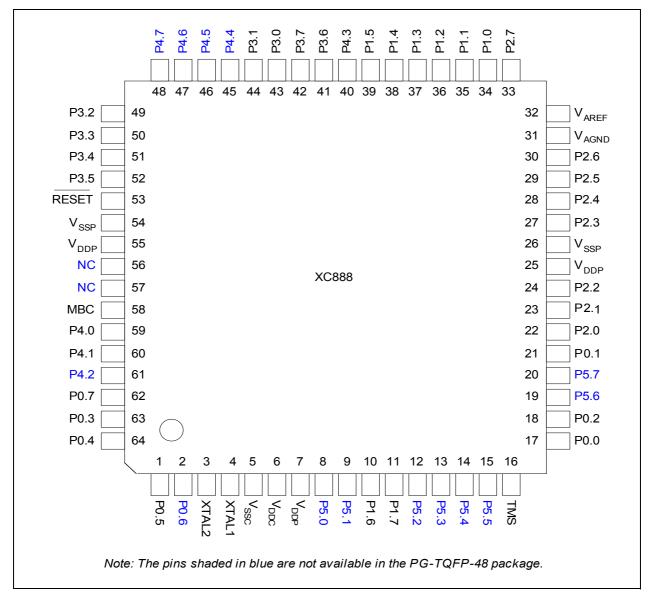

The pin configuration of the XC886, which is based on the PG-TQFP-48 package, is shown in **Figure 1-3**, while that of the XC888, which is based on the PG-TQFP-64 package, is shown in **Figure 1-4**.

Figure 1-3 XC886 Pin Configuration, PG-TQFP-48 Package (top view)

Figure 1-4 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

# 1.3 Pin Definitions and Functions

After reset, all pins are configured as input with one of the following:

- Pull-up device enabled only (PU)

- Pull-down device enabled only (PD)

- High impedance with both pull-up and pull-down devices disabled (Hi-Z)

The functions and default states of the XC886/888 external pins are provided in **Table 1-3**.

Table 1-3 Pin Definitions and Functions

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                   |                                                                                                                                                                                 |

|--------|----------------------------|------|----------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0     |                            | I/O  |                | I/O port. It ca<br>for the JTAG                            | B-bit bidirectional general purpose an be used as alternate functions i, CCU6, UART, UART1, Timer 2, ultiCAN and SSC.                                                           |

| P0.0   | 11/17                      |      | Hi-Z           | TCK_0<br>T12HR_1<br>CC61_1<br>CLKOUT_0<br>RXDO_1           | JTAG Clock Input CCU6 Timer 12 Hardware Run Input Input/Output of Capture/Compare channel 1 Clock Output UART Transmit Data Output                                              |

| P0.1   | 13/21                      |      | Hi-Z           | TDI_0<br>T13HR_1<br>RXD_1<br>RXDC1_0<br>COUT61_1<br>EXF2_1 | JTAG Serial Data Input CCU6 Timer 13 Hardware Run Input UART Receive Data Input MultiCAN Node 1 Receiver Input Output of Capture/Compare channel 1 Timer 2 External Flag Output |

| P0.2   | 12/18                      |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1<br>TXDC1_0                       | CCU6 Trap Input JTAG Serial Data Output UART Transmit Data Output/Clock Output MultiCAN Node 1 Transmitter Output                                                               |

**Table 1-3 Pin Definitions and Functions** (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function          |                                                            |

|--------|----------------------------|------|----------------|-------------------|------------------------------------------------------------|

| P0.3   | 48/63                      |      | Hi-Z           | SCK_1<br>COUT63_1 | SSC Clock Input/Output Output of Capture/Compare channel 3 |

|        |                            |      |                | RXDO1_0           | UART1 Transmit Data Output                                 |

| P0.4   | 1/64                       |      | Hi-Z           | MTSR_1            | SSC Master Transmit Output/<br>Slave Receive Input         |

|        |                            |      |                | CC62_1            | Input/Output of Capture/Compare channel 2                  |

|        |                            |      |                | TXD1_0            | UART1 Transmit Data Output/Clock Output                    |

| P0.5   | 2/1                        |      | Hi-Z           | MRST_1            | SSC Master Receive Input/Slave Transmit Output             |

|        |                            |      |                | EXINT0_0          | External Interrupt Input 0                                 |

|        |                            |      |                | T2EX1_1           | Timer 21 External Trigger Input                            |

|        |                            |      |                | RXD1_0            | UART1 Receive Data Input                                   |

|        |                            |      |                | COUT62_1          | Output of Capture/Compare channel 2                        |

| P0.6   | <b>-/2</b>                 |      | PU             | GPIO              |                                                            |

| P0.7   | 47/62                      |      | PU             | CLKOUT_1          | Clock Output                                               |

**Table 1-3 Pin Definitions and Functions** (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                       |                                                                                                                                            |

|--------|----------------------------|------|----------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| P1     |                            | I/O  |                | I/O port. It ca<br>for the JTAG                | B-bit bidirectional general purpose an be used as alternate functions i, CCU6, UART, Timer 0, Timer 1, er 21, MultiCAN and SSC.            |

| P1.0   | 26/34                      |      | PU             | RXD_0<br>T2EX<br>RXDC0_0                       | UART Receive Data Input<br>Timer 2 External Trigger Input<br>MultiCAN Node 0 Receiver Input                                                |

| P1.1   | 27/35                      |      | PU             | EXINT3<br>T0_1<br>TDO_1<br>TXD_0               | External Interrupt Input 3 Timer 0 Input JTAG Serial Data Output UART Transmit Data Output/Clock Output MultiCAN Node 0 Transmitter Output |

| P1.2   | 28/36                      |      | PU             | SCK_0                                          | SSC Clock Input/Output                                                                                                                     |

| P1.3   | 29/37                      |      | PU             | MTSR_0 TXDC1_3                                 | SSC Master Transmit Output/Slave Receive Input MultiCAN Node 1 Transmitter Output                                                          |

| P1.4   | 30/38                      |      | PU             | MRST_0 EXINT0_1 RXDC1_3                        | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>MultiCAN Node 1 Receiver Input                         |

| P1.5   | 31/39                      |      | PU             | CCPOS0_1<br>EXINT5<br>T1_1<br>EXF2_0<br>RXDO_0 | CCU6 Hall Input 0 External Interrupt Input 5 Timer 1 Input Timer 2 External Flag Output UART Transmit Data Output                          |

**Table 1-3 Pin Definitions and Functions** (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                               |                                                                                                     |

|--------|----------------------------|------|----------------|----------------------------------------|-----------------------------------------------------------------------------------------------------|

| P1.6   | 8/10                       |      | PU             | CCPOS1_1<br>T12HR_0                    | CCU6 Hall Input 1<br>CCU6 Timer 12 Hardware Run<br>Input                                            |

|        |                            |      |                | EXINT6_0<br>RXDC0_2<br>T21_1           | External Interrupt Input 6 MultiCAN Node 0 Receiver Input Timer 21 Input                            |

| P1.7   | 9/11                       |      | PU             | CCPOS2_1<br>T13HR_0<br>T2_1<br>TXDC0_2 | CCU6 Hall Input 2 CCU6 Timer 13 Hardware Run Input Timer 2 Input MultiCAN Node 0 Transmitter Output |

|        |                            |      |                |                                        | .6 can be used as a software chip to the SSC.                                                       |

**Table 1-3 Pin Definitions and Functions** (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                  |                                                                                                                                                        |

|--------|----------------------------|------|----------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2     |                            | I    |                | port. It can be the digital inp                           | B-bit general purpose input-only e used as alternate functions for outs of the JTAG and CCU6. It is the analog inputs for the ADC.                     |

| P2.0   | 14/22                      |      | Hi-Z           | CCPOS0_0<br>EXINT1_0<br>T12HR_2<br>TCK_1<br>CC61_3<br>AN0 | CCU6 Hall Input 0 External Interrupt Input 1 CCU6 Timer 12 Hardware Run Input JTAG Clock Input Input of Capture/Compare channel 1 Analog Input 0       |

| P2.1   | 15/23                      |      | Hi-Z           | CCPOS1_0<br>EXINT2_0<br>T13HR_2<br>TDI_1<br>CC62_3<br>AN1 | CCU6 Hall Input 1 External Interrupt Input 2 CCU6 Timer 13 Hardware Run Input JTAG Serial Data Input Input of Capture/Compare channel 2 Analog Input 1 |

| P2.2   | 16/24                      |      | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>CC60_3<br>AN2                      | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare<br>channel 0<br>Analog Input 2                                                        |

| P2.3   | 19/27                      |      | Hi-Z           | AN3                                                       | Analog Input 3                                                                                                                                         |

| P2.4   | 20/28                      |      | Hi-Z           | AN4                                                       | Analog Input 4                                                                                                                                         |

| P2.5   | 21/29                      |      | Hi-Z           | AN5                                                       | Analog Input 5                                                                                                                                         |

| P2.6   | 22/30                      |      | Hi-Z           | AN6                                                       | Analog Input 6                                                                                                                                         |

| P2.7   | 25/33                      |      | Hi-Z           | AN7                                                       | Analog Input 7                                                                                                                                         |

**Table 1-3 Pin Definitions and Functions** (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                 |                                                                                                                                         |

|--------|----------------------------|------|----------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| P3     |                            | I/O  |                | I/O port. It ca                          | B-bit bidirectional general purpose an be used as alternate functions ART1, Timer 21 and MultiCAN.                                      |

| P3.0   | 35/43                      |      | Hi-Z           | CCPOS1_2<br>CC60_0<br>RXDO1_1            | CCU6 Hall Input 1 Input/Output of Capture/Compare channel 0 UART1 Transmit Data Output                                                  |

| P3.1   | 36/44                      |      | Hi-Z           | CCPOS0_2<br>CC61_2<br>COUT60_0<br>TXD1_1 | CCU6 Hall Input 0 Input/Output of Capture/Compare channel 1 Output of Capture/Compare channel 0 UART1 Transmit Data Output/Clock Output |

| P3.2   | 37/49                      |      | Hi-Z           | CCPOS2_2<br>RXDC1_1<br>RXD1_1<br>CC61_0  | CCU6 Hall Input 2 MultiCAN Node 1 Receiver Input UART1 Receive Data Input Input/Output of Capture/Compare channel 1                     |

| P3.3   | 38/50                      |      | Hi-Z           | COUT61_0<br>TXDC1_1                      | Output of Capture/Compare channel 1 MultiCAN Node 1 Transmitter Output                                                                  |

| P3.4   | 39/51                      |      | Hi-Z           | CC62_0<br>RXDC0_1<br>T2EX1_0             | Input/Output of Capture/Compare channel 2 MultiCAN Node 0 Receiver Input Timer 21 External Trigger Input                                |

| P3.5   | 40/52                      |      | Hi-Z           | COUT62_0<br>EXF21_0<br>TXDC0_1           | Output of Capture/Compare<br>channel 2<br>Timer 21 External Flag Output<br>MultiCAN Node 0 Transmitter<br>Output                        |

| P3.6   | 33/41                      |      | PD             | CTRAP_0                                  | CCU6 Trap Input                                                                                                                         |

**Table 1-3 Pin Definitions and Functions** (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | <br>Reset<br>State | Function           |                                                                |

|--------|----------------------------|--------------------|--------------------|----------------------------------------------------------------|

| P3.7   | 34/42                      | Hi-Z               | EXINT4<br>COUT63_0 | External Interrupt Input 4 Output of Capture/Compare channel 3 |

**Table 1-3 Pin Definitions and Functions** (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                     |                                                                                                    |

|--------|----------------------------|------|----------------|------------------------------|----------------------------------------------------------------------------------------------------|

| P4     |                            | I/O  |                | I/O port. It ca              | 3-bit bidirectional general purpose an be used as alternate functions mer 0, Timer 1, Timer 21 and |

| P4.0   | 45/59                      |      | Hi-Z           | RXDC0_3<br>CC60_1            | MultiCAN Node 0 Receiver Input<br>Output of Capture/Compare<br>channel 0                           |

| P4.1   | 46/60                      |      | Hi-Z           | TXDC0_3<br>COUT60_1          | MultiCAN Node 0 Transmitter Output Output of Capture/Compare channel 0                             |

| P4.2   | <b>-</b> /61               |      | PU             | EXINT6_1<br>T21_0            | External Interrupt Input 6 Timer 21 Input                                                          |

| P4.3   | 32/40                      |      | Hi-Z           | EXF21_1<br>COUT63_2          | Timer 21 External Flag Output<br>Output of Capture/Compare<br>channel 3                            |

| P4.4   | <b>-/45</b>                |      | Hi-Z           | CCPOS0_3<br>T0_0<br>CC61_4   | CCU6 Hall Input 0 Timer 0 Input Output of Capture/Compare channel 1                                |

| P4.5   | -/46                       |      | Hi-Z           | CCPOS1_3<br>T1_0<br>COUT61_2 | CCU6 Hall Input 1 Timer 1 Input Output of Capture/Compare channel 1                                |

| P4.6   | -/47                       |      | Hi-Z           | CCPOS2_3<br>T2_0<br>CC62_2   | CCU6 Hall Input 2 Timer 2 Input Output of Capture/Compare channel 2                                |

| P4.7   | -/48                       |      | Hi-Z           | CTRAP_3<br>COUT62_2          | CCU6 Trap Input Output of Capture/Compare channel 2                                                |

**Table 1-3 Pin Definitions and Functions** (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                          |                                                                        |

|--------|----------------------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| P5     |                            | I/O  |                | Port 5 Port 5 is an 8-bit bidirectional general purpose I/O port. It can be used as alternate functions for UART, UART1 and JTAG. |                                                                        |

| P5.0   | <b>-/8</b>                 |      | PU             | EXINT1_1                                                                                                                          | External Interrupt Input 1                                             |

| P5.1   | <b>-/9</b>                 |      | PU             | EXINT2_1                                                                                                                          | External Interrupt Input 2                                             |

| P5.2   | <b>-/12</b>                |      | PU             | RXD_2                                                                                                                             | UART Receive Data Input                                                |

| P5.3   | _/13                       |      | PU             | TXD_2                                                                                                                             | UART Transmit Data Output/Clock Output                                 |

| P5.4   | <b>-/14</b>                |      | PU             | RXDO_2                                                                                                                            | UART Transmit Data Output                                              |

| P5.5   | <b>-/15</b>                |      | PU             | TDO_2<br>TXD1_2                                                                                                                   | JTAG Serial Data Output<br>UART1 Transmit Data Output/<br>Clock Output |

| P5.6   | <del>-</del> /19           |      | PU             | TCK_2<br>RXDO1_2                                                                                                                  | JTAG Clock Input<br>UART1 Transmit Data Output                         |

| P5.7   | <b>-/20</b>                |      | PU             | TDI_2<br>RXD1_2                                                                                                                   | JTAG Serial Data Input<br>UART1 Receive Data Input                     |

**Table 1-3 Pin Definitions and Functions** (cont'd)

| Symbol                   | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                        |

|--------------------------|----------------------------|------|----------------|-------------------------------------------------------------------------------------------------|

| $V_{DDP}$                | 7, 17, 43/<br>7, 25, 55    | _    | _              | I/O Port Supply (3.3 or 5.0 V) Also used by EVR and analog modules. All pins must be connected. |

| $V_{SSP}$                | 18, 42/26, 54              | _    | _              | I/O Ground All pins must be connected.                                                          |

| $\overline{V_{DDC}}$     | 6/6                        | _    | _              | Core Supply Monitor (2.5 V)                                                                     |

| $\overline{V_{\rm SSC}}$ | 5/5                        | _    | _              | Core Supply Ground                                                                              |

| $\overline{V_{AREF}}$    | 24/32                      | _    | _              | ADC Reference Voltage                                                                           |

| $\overline{V_{AGND}}$    | 23/31                      | _    | _              | ADC Reference Ground                                                                            |

| XTAL1                    | 4/4                        | I    | Hi-Z           | External Oscillator Input (backup for on-chip OSC, normally NC)                                 |

| XTAL2                    | 3/3                        | 0    | Hi-Z           | External Oscillator Output (backup for on-chip OSC, normally NC)                                |

| TMS                      | 10/16                      | I    | PD             | Test Mode Select                                                                                |

| RESET                    | 41/53                      | I    | PU             | Reset Input                                                                                     |

| MBC <sup>1)</sup>        | 44/58                      | I    | PU             | Monitor & BootStrap Loader Control                                                              |

| NC                       | <b>-</b> /56, 57           | _    | _              | No Connection                                                                                   |

<sup>1)</sup> An external pull-up device in the range of 4.7 k $\Omega$  to 100 k $\Omega$  is required to enter user mode. Alternatively MBC can be tied to high if alternate functions (for debugging) of the pin are not utilized.

# 1.4 Chip Identification Number

Each device variant of XC886/888 is assigned an unique chip identification number to allow easy identification of one device variant from the others. The differentiation is based on the product, variant type and device step information.

Two methods are provided to read a device variant's chip identification number:

- In-application subroutine, see Chapter 4.8.6;

- Bootstrap loader (BSL) mode A, see Chapter 18.1.2.7 or Chapter 18.1.3.7.

#### 1.5 Text Conventions

This document uses the following text conventions for named components of the XC886/888:

- Functional units of the XC886/888 are shown in upper case. For example: "The SSC can be used to communicate with shift registers."

- Pins using negative logic are indicated by an overbar. For example: "A reset input pin RESET is provided for the hardware reset."

- Bit fields and bits in registers are generally referenced as "Register name.Bit field" or "Register name.Bit". Most of the register names contain a module name prefix, separated by an underscore character "\_" from the actual register name. In the example of "SSC\_CON", "SSC" is the module name prefix, and "CON" is the actual register name).

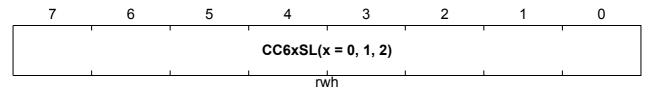

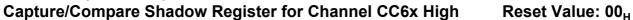

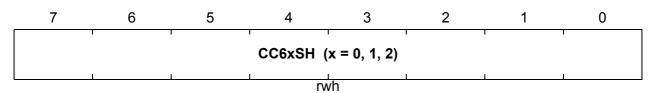

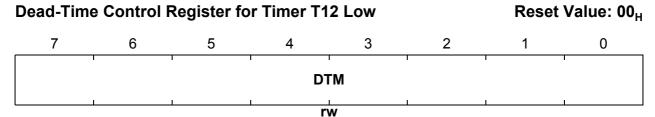

- Variables that are used to represent sets of processing units or registers appear in mixed-case type. For example, the register name "CC6xR" refers to multiple "CC6xR" registers with the variable x (x = 0, 1, 2). The bounds of the variables are always specified where the register expression is first used (e.g., "x = 0 2"), and is repeated as needed.

- The default radix is decimal. Hexadecimal constants have a suffix with the subscript letter "H" (e.g., C0<sub>H</sub>). Binary constants have a suffix with the subscript letter "B" (e.g., 11<sub>B</sub>).

- When the extents of register fields, groups of signals, or groups of pins are

collectively named in the body of the document, they are represented as

"NAME[A:B]", which defines a range, from B to A, for the named group. Individual

bits, signals, or pins are represented as "NAME[C]", with the range of the variable C

provided in the text (e.g., CFG[2:0] and TOS[0]).

- Units are abbreviated as follows:

- MHz = Megahertz

- $\mu s = Microseconds$

- kBaud, kbit = 1000 characters/bits per second

- MBaud, Mbit = 1,000,000 characters/bits per second

- Kbyte = 1024 bytes of memory

- Mbyte = 1,048,576 bytes of memory

- In general, the k prefix scales a unit by 1000 whereas the K prefix scales a unit by 1024. Hence, the Kbyte unit scales the expression preceding it by 1024. The kBaud unit scales the expression preceding it by 1000. The M prefix scales by 1,000,000 or 1048576, and  $\mu$  scales by 0.000001. For example, 1 Kbyte is 1024 bytes, 1 Mbyte is 1024  $\times$  1024 bytes, 1 kBaud/kbit are 1000 characters/bits per second, 1 MBaud/Mbit are 1,000,000 characters/bits per second, and 1 MHz is 1.000,000 Hz.

- Data format quantities are defined as follows:

- Byte = 8-bit quantity

# 1.6 Reserved, Undefined and Unimplemented Terminology

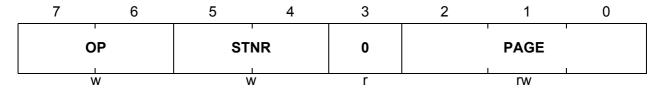

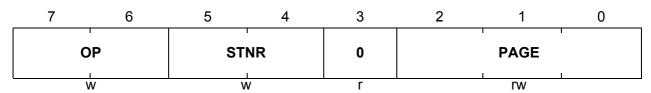

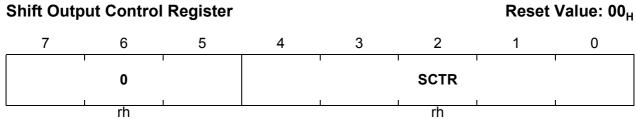

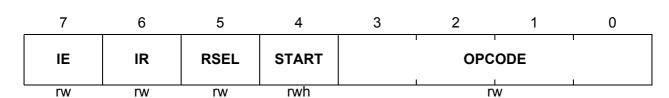

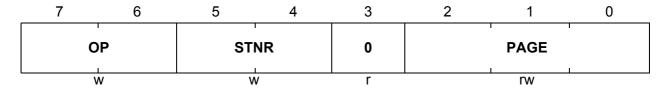

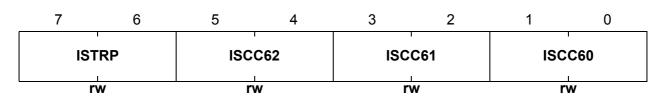

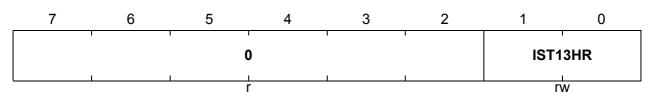

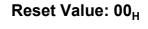

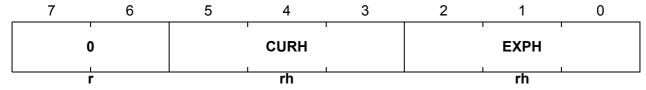

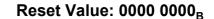

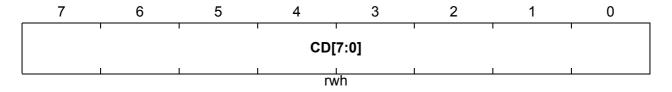

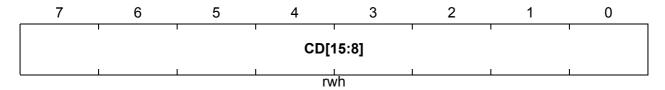

In tables where register bit fields are defined, the following conventions are used to indicate undefined and unimplemented function. Further, types of bits and bit fields are defined using the abbreviations shown in **Table 1-4**.

Table 1-4 Bit Function Terminology

| Function of Bits | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unimplemented    | Register bit fields named "0" indicate unimplemented functions with the following behavior. Reading these bit fields returns 0. Writing to these bit fields has no effect. These bit fields are reserved. When writing, software should always set such bit fields to 0 in order to preserve compatibility with future products. Setting the bit fields to 1 may lead to unpredictable results.               |

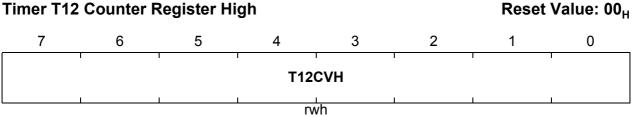

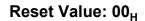

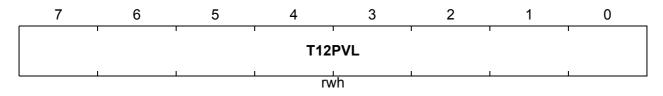

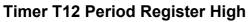

| Undefined        | Certain bit combinations in a bit field can be labeled "Reserved", indicating that the behavior of the XC886/888 is undefined for that combination of bits. Setting the register to undefined bit combinations may lead to unpredictable results. Such bit combinations are reserved. When writing, software must always set such bit fields to legal values as provided in the bit field description tables. |

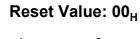

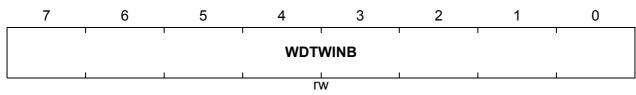

| rw               | The bit or bit field can be read and written.                                                                                                                                                                                                                                                                                                                                                                 |

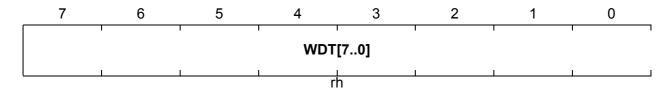

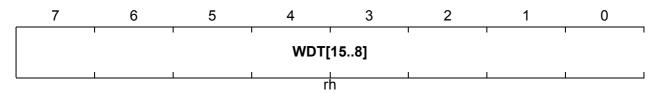

| r                | The bit or bit field can only be read (read-only).                                                                                                                                                                                                                                                                                                                                                            |

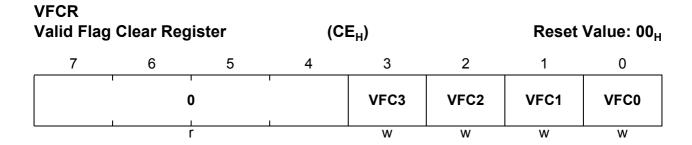

| w                | The bit or bit field can only be written (write-only). Reading always return 0.                                                                                                                                                                                                                                                                                                                               |

| h                | The bit or bit field can also be modified by hardware (such as a status bit). This attribute can be combined with 'rw' or 'r' bits to 'rwh' and 'rh' bits, respectively.                                                                                                                                                                                                                                      |

# 1.7 Acronyms

Table 1-5 lists the acronyms used in this document.

Table 1-5 Acronyms

| Acronym | Description                 |

|---------|-----------------------------|

| ADC     | Analog-to-Digital Converter |

| ALU     | Arithmetic/Logic Unit       |

| BSL     | BootStrap Loader            |

Table 1-5 Acronyms (cont'd)

| Table 1-5 Acronyms (cont a) |                                             |

|-----------------------------|---------------------------------------------|

| Acronym                     | Description                                 |

| CAN                         | Controller Area Network                     |

| CCU6                        | Capture/Compare Unit 6                      |

| CGU                         | Clock Generation Unit                       |

| CORDIC                      | Cordinate Rotation Digital Computer         |

| CPU                         | Central Processing Unit                     |

| ECC                         | Error Correction Code                       |

| EVR                         | Embedded Voltage Regulator                  |

| FDR                         | Fractional Divider                          |

| GPIO                        | General Purpose I/O                         |

| IAP                         | In-Application Programming                  |

| I/O                         | Input/Output                                |

| ISP                         | In-System Programming                       |

| JTAG                        | Joint Test Action Group                     |

| LIN                         | Local Interconnect Network                  |

| MDU                         | Multiplication/Division Unit                |

| NMI                         | Non-Maskable Interrupt                      |

| OCDS                        | On-Chip Debug Support                       |

| PC                          | Program Counter                             |

| POR                         | Power-On Reset                              |

| PLL                         | Phase-Locked Loop                           |

| PSW                         | Program Status Word                         |

| PWM                         | Pulse Width Modulation                      |

| RAM                         | Random Access Memory                        |

| ROM                         | Read-Only Memory                            |

| SFR                         | Special Function Register                   |

| SPI                         | Serial Peripheral Interface                 |

| SSC                         | Synchronous Serial Channel                  |

| UART                        | Universal Asynchronous Receiver/Transmitter |

| WDT                         | Watchdog Timer                              |

| -                           |                                             |

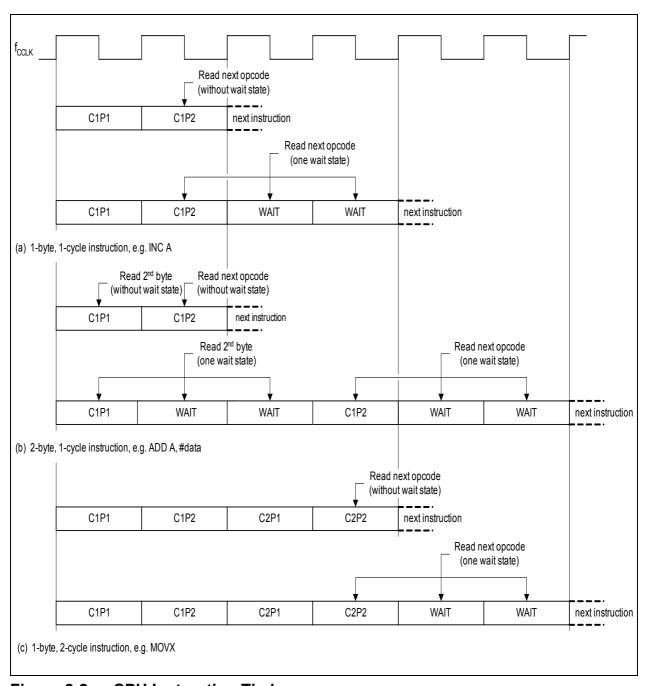

#### **Processor Architecture**

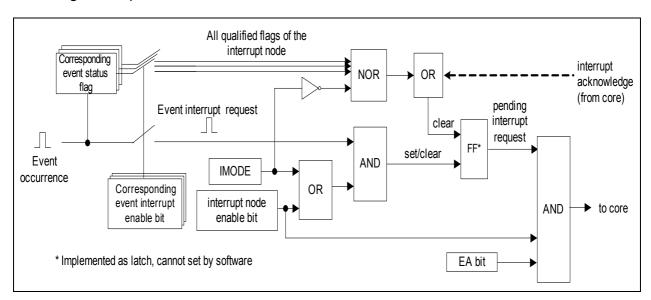

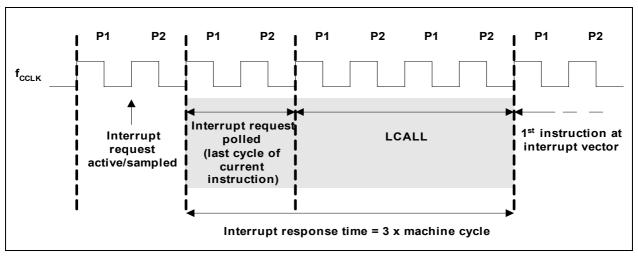

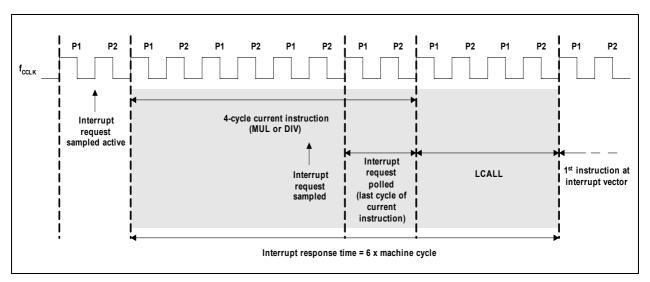

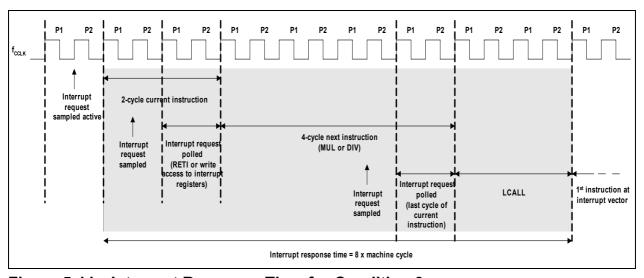

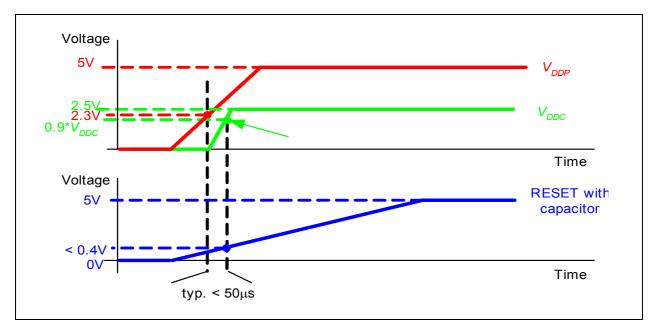

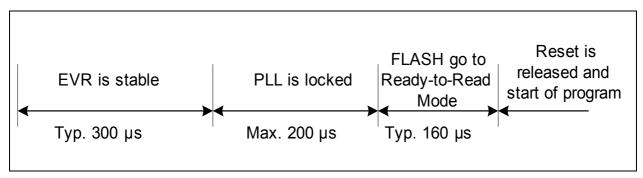

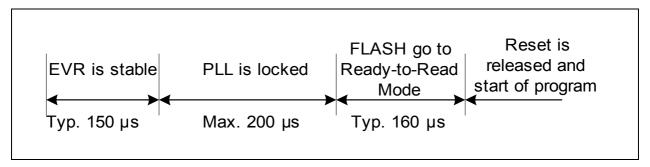

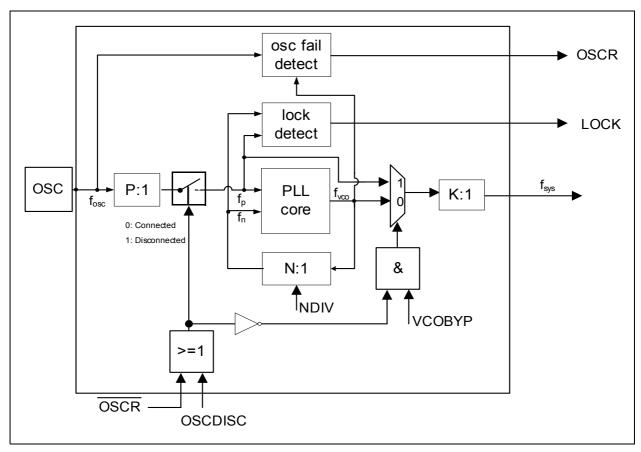

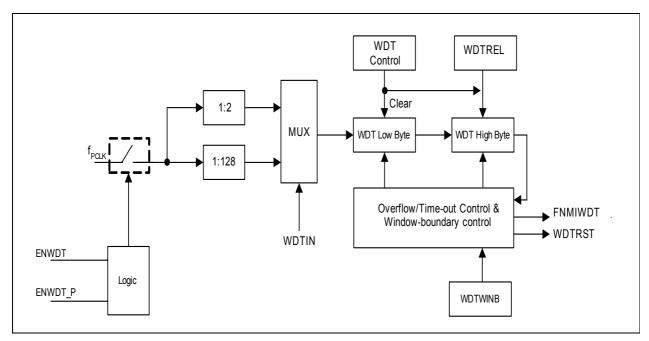

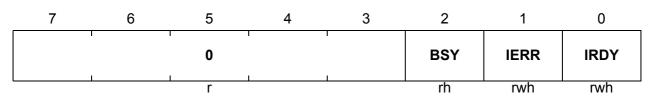

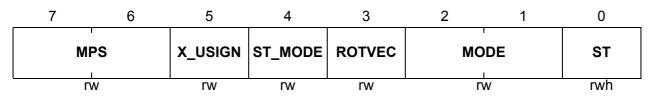

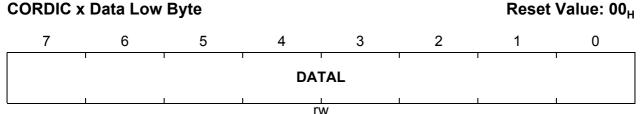

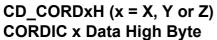

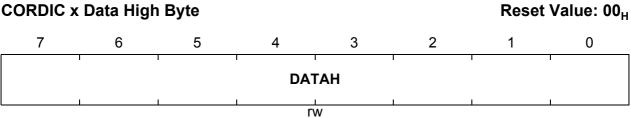

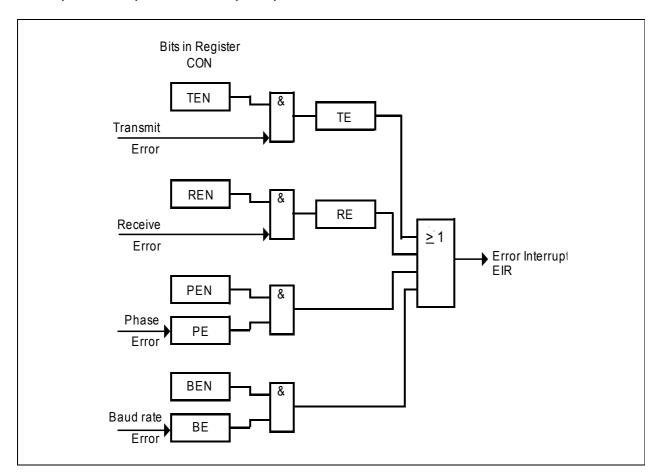

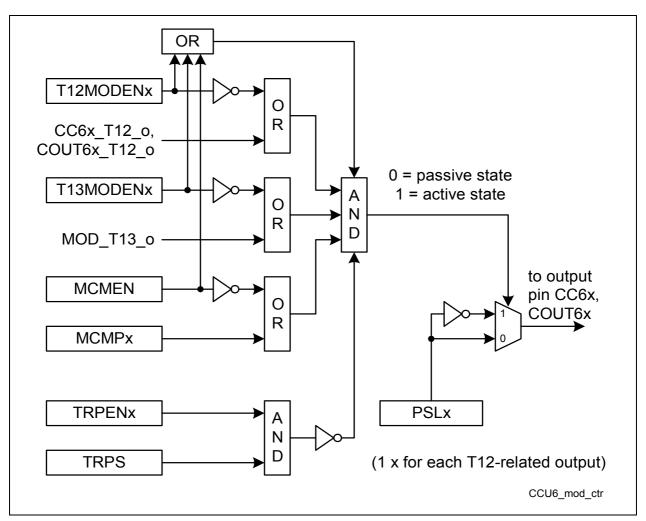

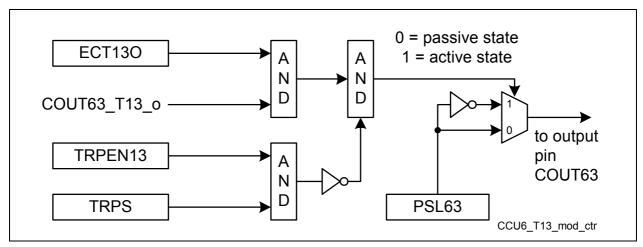

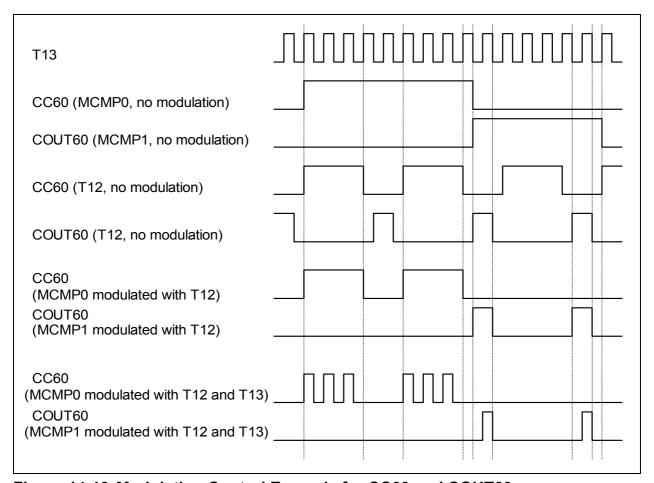

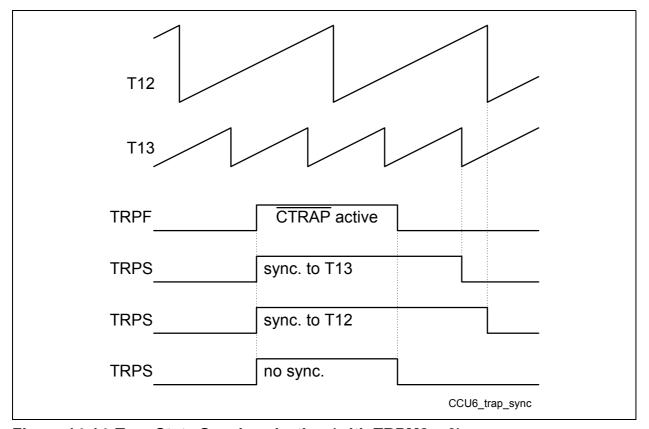

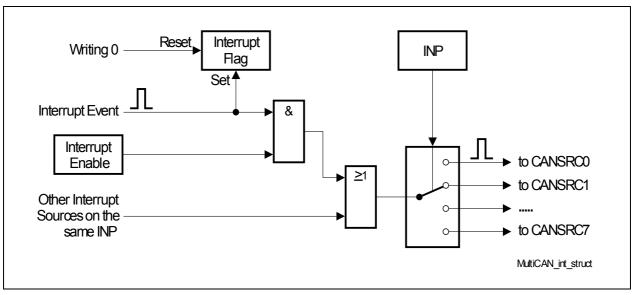

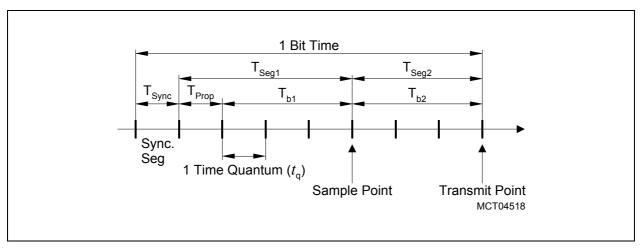

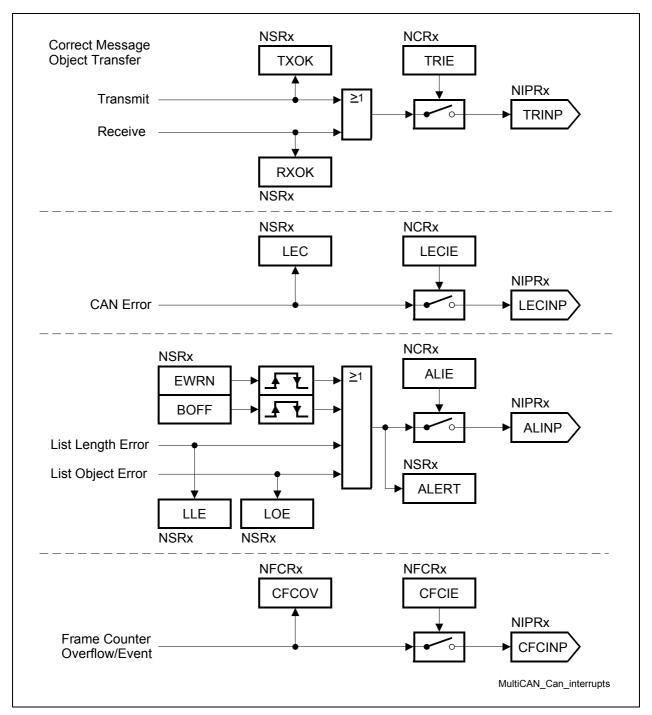

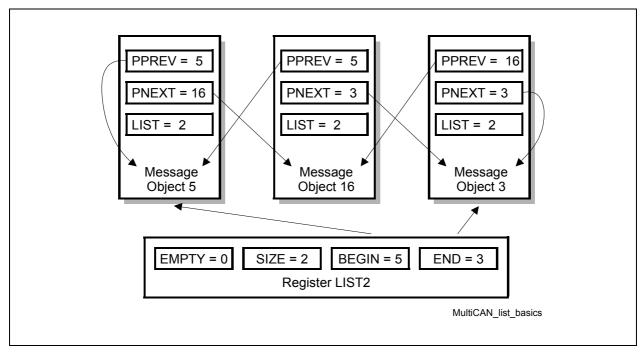

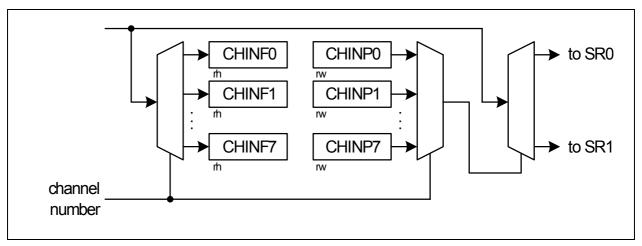

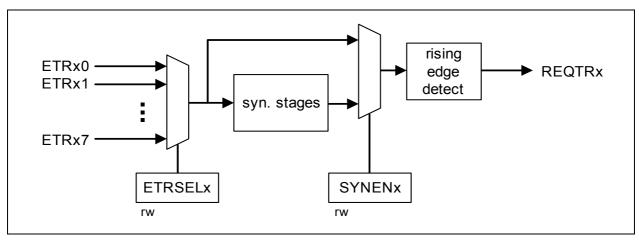

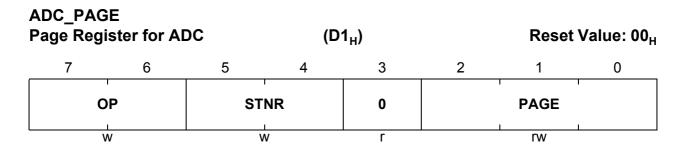

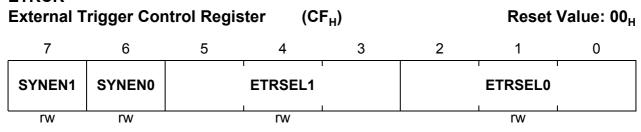

# 2 Processor Architecture