# NIPPON PRECISION CIRCUITS INC.

## CMOS LSI DECO SM5872A/B

Digital Audio D/A Converters with Built-in Digital Filters

## **OVERVIEW**

The  $\Sigma DECO$  SM5872A/B D/A converters are high-speed converters for digital audio systems. They are fabricated in Molybdenum-gate CMOS. They incorporate a two-channel, 16-bit D/A converter and a digital eight-times oversampling filter, making them ideal for use in PCM and CD players and digital amplifiers. The  $\Sigma DECO$  SM5872A/B operate at 32, 44.1 and 48kHz sampling frequencies and incorporate deemphasis, attenuation and soft mute functions. These functions are controlled either by input pin logic levels or by the micro-controller interface. The  $\Sigma DECO$  SM5872A/B linearly interpolates the input signal at a high multiple of the original sampling frequency, and then requantizes the resulting signal. A fourth-order noise shaper removes most of the quantizing noise before the signal is output as a pulsewidth-modulated waveform. The  $\Sigma DECO$  SM5872A/B operate from a 3.2 to 5.5V supply and are available in 28-pin SOPs.

#### **FEATURES**

- Two-channel ΣΔ D/A converter

- 8-times oversampling FIR filter

- 69 + 13 + 5 tap, 8fs FIR filter

- 53dB stopband attenuation

- ± 0.05dB passband ripple

- Fourth-order zero-shift noise shaper

- Digital deemphasis

- 128-step, linear attenuator

- Soft muting

- 13-level, quasi-symmetrical PWM outputs

- Normal- and double-speed operation (SM5872A only)

- On-chip crystal oscillation circuit

- 2s complement, msb-first, 16-bit serial input data format

- Single 5V supply in normal- and double-speed modes

- Low-voltage operation

- 3.2V minimum supply voltage operation in normal-speed mode

- 4.5V minimum supply voltage operation in double-speed mode

- Molybdenum-gate CMOS process

- Package: 28-pin SOP

## ORDERING INFORMATION

| Device   | System clock                            | Package    |

|----------|-----------------------------------------|------------|

| SM5872AS | 256fs or 512fs<br>(selected using CKSL) | 28-pin SOP |

| SM5872BS | 384fs                                   |            |

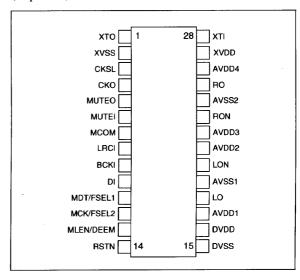

#### **PINOUT**

(Top view)

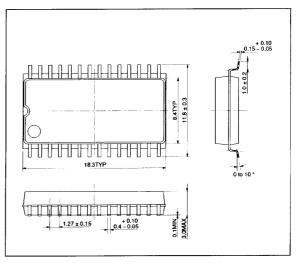

## PACKAGE DIMENSIONS

(Unit: mm)

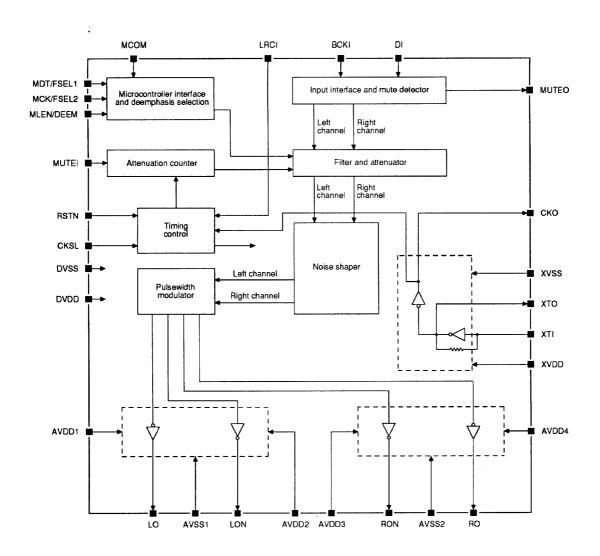

## **BLOCK DIAGRAM**

## PIN DESCRIPTION

| Number | Name      |                                                               | Description                                                                               |                              |  |  |

|--------|-----------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------|--|--|

| 1      | хто       | Crystal oscillator output                                     |                                                                                           |                              |  |  |

| 2      | xvss      | Clock ground                                                  |                                                                                           |                              |  |  |

|        |           | Clock frequency select input.                                 |                                                                                           |                              |  |  |

|        |           |                                                               | Frequ                                                                                     | Jency                        |  |  |

| •      | OKOL      | Device                                                        | CLSL = HIGH                                                                               | CKSL = LOW                   |  |  |

| 3      | CKSL      | SM5872A                                                       | 512fs                                                                                     | 256fs                        |  |  |

|        |           | SM5872B                                                       | 384fs                                                                                     | Not used                     |  |  |

|        |           | Internal pull-up resistor                                     |                                                                                           |                              |  |  |

|        |           | Clock output.                                                 |                                                                                           |                              |  |  |

|        |           | Device                                                        | Frequ                                                                                     | Jency                        |  |  |

| 4      | ско       | Device                                                        | CLSL = HIGH                                                                               | CKSL = LOW                   |  |  |

|        |           | SM5872A                                                       | 512fs                                                                                     | 256fs                        |  |  |

|        |           | SM5872B                                                       | 384fs                                                                                     | Not used                     |  |  |

| 5      | MUTEO     | Mute detect output                                            |                                                                                           |                              |  |  |

| 6      | MUTEI     | Mute input. Soft muting is ON                                 | when HIGH, and OFF when                                                                   | LOW. Internal pull-resistor  |  |  |

| 7      | мсом      |                                                               | IDT, MCK and MLEN control in the LOW. Internal pull-up resis                              |                              |  |  |

| 8      | LRCI      | Data sample rate clock input.<br>Internal pull-up resistor    | Left channel when HIGH and                                                                | right channel when LOW.      |  |  |

| 9      | ВСКІ      | Bit clock input. Internal pull-up                             | resistor                                                                                  |                              |  |  |

| 10     | DI        | Serial data input. Internal pull-                             | up resistor                                                                               |                              |  |  |

|        |           | Microcontroller interface data in select input FSEL1 when MCC | nput MDT when MCOM is HIO<br>DM is LOW.                                                   | GH, and local mode frequency |  |  |

|        |           | FSEL1                                                         | FSEL2                                                                                     | fs                           |  |  |

|        |           | LOW                                                           | LOW                                                                                       | 44.1 kHz                     |  |  |

| 11     | MDT/FSEL1 | LOW                                                           | HIGH                                                                                      | 48.0 kHz                     |  |  |

|        |           | HIGH                                                          | LOW                                                                                       | 44.1 kHz                     |  |  |

|        |           | HIGH                                                          | HIGH                                                                                      | 32.0 kHz                     |  |  |

|        |           | Internal pull-up resistor                                     |                                                                                           |                              |  |  |

|        |           | Microcontroller interface clock<br>select input FSEL2 when MC | input MCK when MCOM is HI<br>DM is LOW.                                                   | GH, and local mode frequence |  |  |

|        |           | FSEL1                                                         | FSEL2                                                                                     | fs                           |  |  |

|        |           | LOW                                                           | LOW                                                                                       | 44.1 kHz                     |  |  |

| 12     | MCK/FSEL2 | LOW                                                           | HIGH                                                                                      | 48.0 kHz                     |  |  |

|        |           | HIGH                                                          | LOW                                                                                       | 44.1 kHz                     |  |  |

|        |           | HIGH                                                          | HIGH                                                                                      | 32.0 kHz                     |  |  |

|        |           | Internal pull-up resistor                                     |                                                                                           |                              |  |  |

| 13     | MLEN/DEEM | deemphasis control input DEE                                  | enable input MLEN when MCC<br>M when MCOM is LOW. Deer<br>is LOW. Internal pull-up resist | mphasis is ON when DEEM i    |  |  |

## CMOS LSI $\Sigma$ DECO SM5872A/B

| Number | Name  |                                        | Description                 |                            |  |  |  |  |

|--------|-------|----------------------------------------|-----------------------------|----------------------------|--|--|--|--|

| 14     | RSTN  | Reset input. Normal operation resistor | when HIGH, and system reset | when LOW. Internal pull-up |  |  |  |  |

| 15     | DVSS  | Digital ground                         |                             |                            |  |  |  |  |

| 16     | DVDD  | 5 V digital supply                     |                             |                            |  |  |  |  |

| 17     | AVDD1 | Analog supply 1                        |                             |                            |  |  |  |  |

| 18     | LO    | Left-channel positive PWM outp         | out                         |                            |  |  |  |  |

| 19     | AVSS1 | Analog ground 1                        |                             |                            |  |  |  |  |

| 20     | LON   | Left-channel negative PWM out          | put                         |                            |  |  |  |  |

| 21     | AVDD2 | Analog supply 2                        | Analog supply 2             |                            |  |  |  |  |

| 22     | AVDD3 | Analog supply 3                        |                             |                            |  |  |  |  |

| 23     | RON   | Right-channel negative PWM o           | utput                       |                            |  |  |  |  |

| 24     | AVSS2 | Analog ground 2                        |                             |                            |  |  |  |  |

| 25     | RO    | Right-channel positive PWM ou          | itput.                      |                            |  |  |  |  |

| 26     | AVDD4 | Analog supply 4                        |                             |                            |  |  |  |  |

| 27     | XVDD  | Clock supply                           |                             |                            |  |  |  |  |

|        |       | Crystal oscillator or external cl      | ock input.                  |                            |  |  |  |  |

|        |       | Device                                 | Frequ                       | uency                      |  |  |  |  |

| 28     | хті   | Device                                 | CLSL = HIGH                 | CKSL = LOW                 |  |  |  |  |

|        | •     | SM5872A                                | 512fs                       | 256fs                      |  |  |  |  |

|        |       | SM5872B                                | 384fs                       | Not used                   |  |  |  |  |

## **SPECIFICATIONS**

## **Absolute Maximum Ratings**

$DV_{SS} = AV_{SS} = XV_{SS} = 0 V$ ,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$

| Parameter                                     | Symbol                                                 | Rating                             | Unit   |

|-----------------------------------------------|--------------------------------------------------------|------------------------------------|--------|

| Supply voltage range                          | DV <sub>DD</sub> , AV <sub>DD</sub> , XV <sub>DD</sub> | -0.3 to 7.0                        | ٧      |

| Input voltage range for all inputs except XTI | V <sub>I1</sub>                                        | $DV_{SS}$ - 0.3 to $DV_{DD}$ + 0.3 | V      |

| XTI input voltage range                       | V <sub>I2</sub>                                        | $XV_{SS}$ - 0.3 to $XV_{DD}$ + 0.3 | V      |

| Power dissipation                             | P <sub>D</sub>                                         | 250                                | mW     |

| Storage temperature range                     | T <sub>stg</sub>                                       | -40 to 125                         | deg. C |

| Soldering temperature                         | T <sub>SLD</sub>                                       | 255                                | deg. C |

| Soldering time                                | tsld                                                   | 10                                 | s      |

## **Recommended Operating Conditions**

$DV_{SS} = AV_{SS} = XV_{SS} = 0 V$ ,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$

| Parameter                   | Symbol                                                 | Rating     | Unit   |

|-----------------------------|--------------------------------------------------------|------------|--------|

| Supply voltage range        | DV <sub>DD</sub> , AV <sub>DD</sub> , XV <sub>DD</sub> | 3.2 to 5.5 | ٧      |

| Operating temperature range | T <sub>opr</sub>                                       | -20 to 80  | deg. C |

#### Note

All power supply pins (VDD and VSS) must be connected to the same external power supply unit.

## **DC Electrical Characteristics**

## SM5872A

## Normal supply voltage operation

$DV_{DD} = AV_{DD} = XV_{DD} = 4.5$  to 5.5 V,  $DV_{SS} = AV_{SS} = XV_{SS} = 0$  V,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$ ,  $T_a = -20$  to 80 deg. C

| Donomotor.                                | 0                | O and data                                                 |                        | Rating       |                      |                  |

|-------------------------------------------|------------------|------------------------------------------------------------|------------------------|--------------|----------------------|------------------|

| Parameter                                 | Symbol           | Condition                                                  | min                    | typ m        | max                  | Unit             |

| Digital circuitry supply current          | l <sub>DDD</sub> | $DV_{DD} = AV_{DD} = XV_{DD} =$                            | _                      | 27           | 35                   | mA               |

| Clock circuitry supply current            | loox             | $f_{XTI} = 256 \text{fs} = 24.6 \text{ MHz},$              | -                      | 3            | 5                    | mA               |

| Analog circuitry supply current           | IDDA             | no load, double speed<br>mode. CKSL is LOW.<br>See note 4. | -                      | 1            | 2                    | mA               |

| XTI HIGH-level input voltage              | V <sub>IH1</sub> | Estamal alask issue                                        | $0.7 \times XV_{DD}$   | -            | -                    | ٧                |

| XTI LOW-level input voltage               | V <sub>IL1</sub> | External clock input                                       | -                      | _            | $0.3 \times XV_{DD}$ | ٧                |

| XTI AC input voltage                      | VINAC            | AC coupled input                                           | 0.3 × XV <sub>DD</sub> | _            | -                    | V <sub>p-p</sub> |

| HIGH-level input voltage.<br>See note 1.  | V <sub>IH2</sub> |                                                            | 2.4                    | -            | -                    | ٧                |

| LOW-level input voltage.<br>See note 1.   | V <sub>IL2</sub> |                                                            | -                      | _            | 0.5                  | ٧                |

| HIGH-level output voltage.<br>See note 2. | V <sub>OHA</sub> | I <sub>OH</sub> = -1 mA                                    | AV <sub>DD</sub> - 0.3 | _            | -                    | ٧                |

| LOW-level output voltage.<br>See note 2.  | Vola             | I <sub>OL</sub> = 1 mA                                     | -                      | _            | 0.3                  | ٧                |

| CKO HIGH-level output voltage             | V <sub>OHC</sub> | I <sub>OH</sub> = -1 mA                                    | 4.0                    | -            | -                    | ٧                |

| CKO LOW-level output voltage              | Volc             | loL = 2 mA                                                 | -                      | <del>-</del> | 0.5                  | ٧                |

| MUTEO HIGH-level output voltage           | V <sub>ОНМ</sub> | I <sub>OH</sub> = -1 mA                                    | 4.0                    | _            |                      | ٧                |

| MUTEO LOW-level output voltage            | VOLM             | I <sub>OL</sub> = 2 mA                                     | -                      | <del>-</del> | 0.4                  | ٧                |

| XTI HIGH-level input current              | инт              | $V_{I} = XV_{DD}$                                          | -                      | 10           | 20                   | μΑ               |

| XTI LOW-level input current               | I <sub>IL1</sub> | V <sub>I</sub> = 0 V                                       | -                      | 10           | 20                   | μА               |

| LOW-level input current.<br>See note 1.   | l <sub>IL2</sub> | V <sub>I</sub> = 0 V                                       | -                      | 10           | 20                   | μΑ               |

| Input leakage current. See note 1.        | ILH              | V <sub>I</sub> = DV <sub>DD</sub>                          | _                      | _            | 1.0                  | μΑ               |

#### **Notes**

- 1. Pins CKSL, LRCI, BCKI, DI, MUTEI, MCOM, RSTN, MDT/FSEL1, MCK/FSEL2 and MLEN/DEEM

- 2. Pins LO, LON, RO and RON

- 3. I<sub>DDA</sub> is the total current.

- 4. I<sub>DDD</sub> in normal-speed mode is 20 mA (typ) and 25 mA (max).

## Low supply voltage operation

$DV_{DD} = AV_{DD} = XV_{DD} = 3.2$  to 4.5 V,  $DV_{SS} = AV_{SS} = XV_{SS} = 0$  V,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$ ,  $T_a = -20$  to 70 deg. C

| 0                                         | Sumbal           | O - m diai - m                                             |                        | Unit    |                        |                  |

|-------------------------------------------|------------------|------------------------------------------------------------|------------------------|---------|------------------------|------------------|

| Parameter                                 | Symbol           | Condition                                                  | min                    | typ max | max                    | Oilit            |

| Digital circuitry supply current          | lood             | $DV_{DD} = AV_{DD} = XV_{DD} =$                            | -                      | 11      | 15                     | mA               |

| Clock circuitry supply current            | I <sub>DDX</sub> | = 3.4  V,<br>$f_{XTI} = 512 \text{fs} = 24.6 \text{ MHz},$ | -                      | 2       | 3                      | mA               |

| Analog circuitry supply current           | IDDA             | no load, normal speed mode. CKSL is HIGH.                  | -                      | 0.5     | 1                      | mA               |

| XTI HIGH-level input voltage              | V <sub>IH1</sub> | Estaval alask issut                                        | $0.7 \times XV_{DD}$   | -       | _                      | ٧                |

| XTI LOW-level input voltage               | V <sub>IL1</sub> | External clock input                                       | -                      | _       | 0.3 × XV <sub>DD</sub> | ٧                |

| XTI AC input voltage                      | VINAC            | AC coupled input                                           | $0.3 \times XV_{DD}$   | -       | -                      | V <sub>p-p</sub> |

| HIGH-level input voltage.<br>See note 1.  | V <sub>IH2</sub> |                                                            | 2.4                    | _       | _                      | ٧                |

| LOW-level input voltage.<br>See note 1.   | VIL2             |                                                            | _                      | _       | 0.5                    | ٧                |

| HIGH-level output voltage.<br>See note 2. | Voha             | I <sub>OH</sub> = -1 mA                                    | AV <sub>DD</sub> - 0.3 | _       | _                      | ٧                |

| LOW-level output voltage.<br>See note 2.  | Vola             | I <sub>OL</sub> = 1 mA                                     | -                      | _       | 0.3                    | ٧                |

| CKO HIGH-level output voltage             | V <sub>OHC</sub> | I <sub>OH</sub> = -0.4 mA                                  | 2.5                    | -       | -                      | ٧                |

| CKO LOW-level output voltage              | V <sub>OLC</sub> | l <sub>OL</sub> = 0.8 mA                                   | _                      | -       | 0.4                    | ٧                |

| MUTEO HIGH-level output voltage           | V <sub>OHM</sub> | I <sub>OH</sub> = -0.4 mA                                  | 2.5                    | -       | -                      | ٧                |

| MUTEO LOW-level output voltage            | VOLM             | l <sub>OL</sub> = 0.8 mA                                   | -                      | _       | 0.4                    | ٧                |

| XTI HIGH-level input current              | l <sub>H1</sub>  | $V_{I} = XV_{DD}$                                          | -                      | _       | 15                     | μΑ               |

| XTI LOW-level input current               | l <sub>IL1</sub> | V <sub>I</sub> = 0 V                                       | _                      | -       | 15                     | μА               |

| LOW-level input current.<br>See note 1.   | l <sub>IL2</sub> | V <sub>I</sub> = 0 V                                       | -                      | _       | 15                     | μА               |

| Input leakage current. See note 1.        | I <sub>LH</sub>  | $V_I = DV_{DD}$                                            | -                      | _       | 1.0                    | μΑ               |

## **Notes**

- 1. Pins CKSL, LRCI, BCKI, DI, MUTEI, MCOM, RSTN, MDT/FSEL1, MCK/FSEL2 and MLEN/DEEM

- 2. Pins LO, LON, RO and RON

- 3. I<sub>DDA</sub> is the total current.

## SM5872B

## Normal supply voltage operation

$DV_{DD} = AV_{DD} = XV_{DD} = 4.5$  to 5.5 V,  $DV_{SS} = AV_{SS} = XV_{SS} = 0$  V,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$ ,  $T_a = -20$  to 80 deg. C

| D                                | Combal           | Condition                                                                                  |     | Unit |     |       |

|----------------------------------|------------------|--------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Parameter                        | Symbol           | Condition                                                                                  | min | typ  | max | Oilit |

| Digital circuitry supply current | lood             | $DV_{DD} = AV_{DD} = XV_{DD} =$                                                            | -   | 15   | 25  | mA    |

| Clock circuitry supply current   | I <sub>DDX</sub> | $ \begin{cases} 5 \text{ V,} \\ f_{XTI} = 384 \text{ fs} = 16.9 \text{ MHz,} \end{cases} $ | -   | 3    | - 5 | mA    |

| Analog circuitry supply current  | IDDA             | no load. CKSL is HIGH.                                                                     | -   | 1    | 2   | mA    |

## CMOS LSI DECO SM5872A/B

|                                           | Symbol           | 0 - 124                           |                        | Rating |                        |                 |

|-------------------------------------------|------------------|-----------------------------------|------------------------|--------|------------------------|-----------------|

| Parameter                                 |                  | Condition                         | min                    | typ    | max                    | Unit            |

| XTI HIGH-level input voltage              | V <sub>IH1</sub> | E. d. al. al. d. i. a. a          | $0.7 \times XV_{DD}$   | _      | -                      | ٧               |

| XTI LOW-level input voltage               | V <sub>IL1</sub> | External clock input              | -                      | -      | 0.3 × XV <sub>DD</sub> | ٧               |

| XTI AC input voltage                      | VINAC            | AC coupled input                  | $0.3 \times XV_{DD}$   | -      | -                      | $V_{p \cdot p}$ |

| HIGH-level input voltage.<br>See note 1.  | V <sub>1H2</sub> |                                   | 2.4                    | -      | -                      | ٧               |

| LOW-level input voltage.<br>See note 1.   | V <sub>IL2</sub> |                                   | -                      | -      | 0.5                    | ٧               |

| HIGH-level output voltage.<br>See note 2. | V <sub>OHA</sub> | I <sub>OH</sub> = -1 mA           | AV <sub>DD</sub> - 0.3 | _      | -                      | ٧               |

| LOW-level output voltage.<br>See note 2.  | VOLA             | I <sub>OL</sub> = 1 mA            | -                      | _      | 0.3                    | ٧               |

| CKO HIGH-level output voltage             | V <sub>OHC</sub> | I <sub>OH</sub> = -1 mA           | 4.0                    | -      | -                      | ٧               |

| CKO LOW-level output voltage              | Volc             | I <sub>OL</sub> = 2 mA            | -                      | -      | 0.5                    | ٧               |

| MUTEO HIGH-level output voltage           | V <sub>ОНМ</sub> | I <sub>OH</sub> = -1 mA           | 4.0                    | -      | -                      | ٧               |

| MUTEO LOW-level output voltage            | Volm             | I <sub>OL</sub> = 2 mA            | -                      | -      | 0.4                    | ٧               |

| XTI HIGH-level input current              | l <sub>lH1</sub> | V <sub>I</sub> = XV <sub>DD</sub> | _                      | 10     | 20                     | μΑ              |

| XTI LOW-level input current               | liLi             | V <sub>1</sub> = 0 V              | -                      | 10     | 20                     | μΑ              |

| LOW-level input current.<br>See note 1.   | l <sub>IL2</sub> | V <sub>1</sub> = 0 V              | -                      | 10     | 20                     | μА              |

| Input leakage current. See note 1.        | Іцн              | $V_{i} = DV_{DD}$                 | _                      | _      | 1.0                    | μΑ              |

## **Notes**

- 1. Pins CKSL, LRCI, BCKI, DI, MUTEI, MCOM, RSTN, MDT/FSEL1, MCK/FSEL2 and MLEN/DEEM

- 2. Pins LO, LON, RO and RON

- 3.  $I_{\text{DDA}}$  is the total current.

## Low supply voltage operation

$$DV_{DD} = AV_{DD} = XV_{DD} = 3.2$$

to 4.5 V,  $DV_{SS} = AV_{SS} = XV_{SS} = 0$  V,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$ ,  $T_a = -20$  to 70 deg. C

| Danamatan .                               |                  | O a malinia m                                             | Rating                 |          |                                             | Unit             |

|-------------------------------------------|------------------|-----------------------------------------------------------|------------------------|----------|---------------------------------------------|------------------|

| Parameter                                 | Symbol           | Condition                                                 | min                    | typ      | 12<br>3<br>1<br>-<br>0.3 × XV <sub>DD</sub> | O.M.             |

| Digital circuitry supply current          | I <sub>DDD</sub> | $DV_{DD} = AV_{DD} = XV_{DD} =$                           | -                      | 8        | 12                                          | mA               |

| Clock circuitry supply current            | l <sub>DDX</sub> | $\frac{1}{1}$ 3.4 V,<br>$\frac{1}{1}$ = 384fs = 16.9 MHz, | -                      | 2        | 3                                           | mA               |

| Analog circuitry supply current           | IDDA             | no load, normal speed<br>mode. CKSL is HIGH.              | -                      | 0.5      | 1                                           | mA               |

| XTI HIGH-level input voltage              | VIH1             | 1                                                         | $0.7 \times XV_{DD}$   | _        |                                             | ٧                |

| XTI LOW-level input voltage               | V <sub>IL1</sub> | External clock input                                      | -                      | <u>-</u> | 0.3 × XV <sub>DD</sub>                      | ٧                |

| XTI AC input voltage                      | VINAC            | AC coupled input                                          | 0.3 × XV <sub>DD</sub> | _        | -                                           | V <sub>p-p</sub> |

| HIGH-level input voltage.<br>See note 1.  | V <sub>IH2</sub> |                                                           | 2.4                    | -        | -                                           | ٧                |

| LOW-level input voltage.<br>See note 1.   | V <sub>IL2</sub> |                                                           | _                      | -        | 0.5                                         | V                |

| HIGH-level output voltage.<br>See note 2. | Voha             | loH = -1 mA                                               | AV <sub>DD</sub> - 0.3 | -        | -                                           | V                |

## CMOS LSI DECO SM5872A/B

| Parameter                                | Symbol Condition |                           | Rating |     |     |      |

|------------------------------------------|------------------|---------------------------|--------|-----|-----|------|

| Parameter                                | Symbol           | Condition                 | min    | typ | max | Unit |

| LOW-level output voltage.<br>See note 2. | Vola             | loL = 1 mA                | -      | -   | 0.3 | ٧    |

| CKO HIGH-level output voltage            | Vonc             | I <sub>OH</sub> = -0.4 mA | 2.5    | -   | -   | ٧    |

| CKO LOW-level output voltage             | Volc             | I <sub>OL</sub> = 0.8 mA  | -      | -   | 0.4 | ٧    |

| MUTEO HIGH-level output voltage          | Vohm             | I <sub>OH</sub> = -0.4 mA | 2.5    | -   | -   | ٧    |

| MUTEO LOW-level output voltage           | VOLM             | I <sub>OL</sub> = 0.8 mA  | -      | _   | 0.4 | ٧    |

| XTI HIGH-level input current             | lін1             | $V_1 = XV_{DD}$           | _      | -   | 15  | μΑ   |

| XTI LOW-level input current              | l <sub>IL1</sub> | V <sub>1</sub> = 0 V      | _      | -   | 15  | μΑ   |

| LOW-level input current.<br>See note 1.  | l <sub>iL2</sub> | V <sub>I</sub> = 0 V      | _      | -   | 15  | μΑ   |

| Input leakage current. See note 1.       | Іцн              | $V_I = DV_{DD}$           | -      | -   | 1.0 | μΑ   |

## **Notes**

- 1. Pins CKSL, LRCI, BCKI, DI, MUTEI, MCOM, RSTN, MDT/FSEL1, MCK/FSEL2 and MLEN/DEEM

- 2. Pins LO, LON, RO and RON

- 3. I<sub>DDA</sub> is the total current.

## **AC Digital Characteristics**

The conditions for normal supply voltage operation are  $DV_{DD} = AV_{DD} = XV_{DD} = 4.5$  to 5.5 V,  $DV_{SS} = AV_{SS} = XV_{SS} = 0$  V,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$ ,  $T_a = -20$  to 80 deg. C unless otherwise noted. The conditions for low supply voltage operation are  $DV_{DD} = AV_{DD} = XV_{DD} = 3.2$  to 4.5 V,  $DV_{SS} = AV_{SS} = XV_{SS} = 0$  V,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$ ,  $T_a = -20$  to 70 deg. C unless otherwise noted.

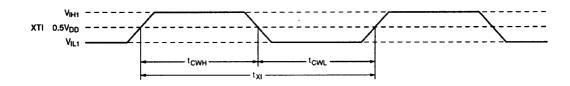

## System clock

#### SM5872A

## Normal-speed mode

| D                                   | Symbol Condition | Condition           |      | Rating |      |       |

|-------------------------------------|------------------|---------------------|------|--------|------|-------|

| Parameter                           |                  | min                 | typ  | max    | Unit |       |

| Olada faransa                       | ı                | CKSL is LOW. 256fs  | 4.0  | 12.3   | 13.0 | M1 (= |

| Clock frequency                     | fosc             | CKSL is HIGH. 512fs | 4.0  | 24.6   | 26.0 | MHz   |

|                                     | <sup>‡</sup> CWL | CKSL is LOW. 256fs  | 34   | 40.7   | 125  | ns    |

| External clock LOW-level pulsewidth |                  | CKSL is HIGH. 512fs | 17   | 20.3   | 125  |       |

| External clock HIGH-level           | tсwн             | CKSL is LOW. 256fs  | 34   | 40.7   | 125  |       |

| pulsewidth                          |                  | CKSL is HIGH. 512fs | 17   | 20.3   | 125  | ns    |

| External clock period               | txı              | CKSL is LOW. 256fs  | 77   | 81.4   | 250  | ns    |

|                                     |                  | CKSL is HIGH. 512fs | 38.5 | 40.7   | 250  |       |

## Note

Typical values shown are for fs = 48 kHz.

## Double-speed mode

$DV_{DD} = AV_{DD} = XV_{DD} = 4.5$  to 5.5 V,  $DV_{SS} = AV_{SS} = XV_{SS} = 0$  V,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$ ,  $T_a = -20$  to 70 deg. C

| Barrandari                           | O h a l         | Condition                                        | Rating |      |      | Unit  |

|--------------------------------------|-----------------|--------------------------------------------------|--------|------|------|-------|

| Parameter                            | Symbol          | Condition                                        | min    | typ  | max  | Oille |

| Clock frequency                      | fosc            | CKSL is LOW. 256fs, crystal oscillator operation | 4.0    | 24.6 | 25.0 | MHz   |

| External clock LOW-level pulsewidth  | 1cwl            | CKSL is LOW. 256fs                               | 17     | 20.3 | 125  | ns    |

| External clock HIGH-level pulsewidth | tсwн            | CKSL is LOW. 256fs                               | 17     | 20.3 | 125  | ns    |

| External clock period                | t <sub>XI</sub> | CKSL is LOW. 256fs                               | 40.0   | 40.7 | 250  | ns    |

## Note

Typical values shown are for fs = 96 kHz.

## SM5872B

|                                      | 0                | Condition                              | Rating |      |      | Unit |

|--------------------------------------|------------------|----------------------------------------|--------|------|------|------|

| Parameter                            | Parameter Symbol |                                        | min    | typ  | max  | Oill |

| Clock frequency                      | fosc             | 384fs,<br>crystal oscillator operation | 4.0    | 16.9 | 19.3 | MHz  |

| External clock LOW-level pulsewidth  | tcwL             | 384fs                                  | 21.7   | 29.5 | 125  | ns   |

| External clock HIGH-level pulsewidth | tсwн             | 384fs                                  | 21.7   | 29.5 | 125  | ns   |

| External clock period                | txı              | 384fs                                  | 51.7   | 59.0 | 250  | ns   |

## System clock timing waveform

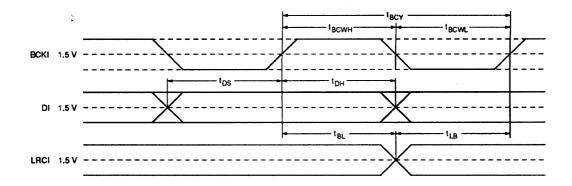

## Serial Input timing

| Parameter                  | Combal            | Rating |     |     | Unit  |

|----------------------------|-------------------|--------|-----|-----|-------|

| rai ali letei              | Symbol            | min    | typ | max | Oilit |

| BCKI LOW-level pulsewidth  | t <sub>BCWL</sub> | 50     | -   | _   | ns    |

| BCKI HIGH-level pulsewidth | tвсwн             | 50     | -   | -   | ns    |

| BCKI period                | tacy              | 100    | -   | -   | ns    |

| DI setup time              | tos               | 50     | -   | -   | ns    |

| DI hold time               | t <sub>DH</sub>   | 50     | _   | -   | ns    |

| BCKI to LRCI delay time    | tBL tBL           | 50     | -   | _   | ns    |

| LRCI to BCKI delay time    | tlB               | 50     |     | -   | ns    |

## Serial input timing waveform

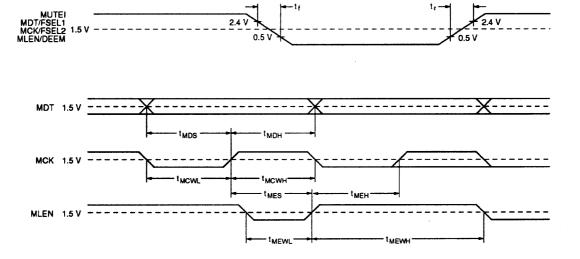

## Control Input timing

| D                          | 0                 | Rating |     |     | Unit |

|----------------------------|-------------------|--------|-----|-----|------|

| Parameter                  | Symbol            | min    | typ | max | Unit |

| Clock signal rise time     | t <sub>r</sub>    | -      | -   | 100 | ns   |

| Clock signal fall time     | tı                | -      | -   | 100 | ns   |

| MCK LOW-level pulsewidth   | 1 <sub>MCWL</sub> | 50     | -   | -   | ns   |

| MCK HIGH-level pulsewidth  | twcwh             | 50     | -   | -   | ns   |

| MDT setup time             | t <sub>MDS</sub>  | 50     | -   |     | ns   |

| MDT hold time              | t <sub>MDH</sub>  | 50     | _   | -   | ns   |

| MLEN LOW-level pulsewidth  | t <sub>MEWL</sub> | 50     | -   | -   | ns   |

| MLEN HIGH-level pulsewidth | 1 <sub>MEWH</sub> | 50     | _   | -   | ns   |

| MLEN setup time            | †MES              | 50     | -   | _   | ns   |

| MLEN hold time             | 1 <sub>MEH</sub>  | 50     | -   | -   | ns   |

## Note

Pins MUTEI, MDT/FSEL1, MCK/FSEL2 and MLEN/DEEM

## Control input timing waveforms

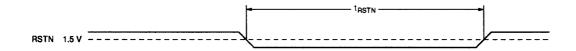

## Reset input timing

| Parameter                 | Symbol            | Condition      |     | Unit |     |       |

|---------------------------|-------------------|----------------|-----|------|-----|-------|

| Lai ai leítai             | Syllibol          | Condition      | min | typ  | max | Oiiit |

| RSTN LOW-level pulsewidth | <sup>t</sup> rstn | After power-up | 20  | -    | -   | ns    |

#### Reset input timing waveform

## **AC Analog Characteristics**

$DV_{DD} = AV_{DD} = XV_{DD} = 5$  V,  $DV_{SS} = AV_{SS} = XV_{SS} = 0$  V,  $AV_{SS} = AV_{SS1} = AV_{SS2}$ ,  $AV_{DD} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4}$ , CKSL is HIGH, crystal oscillator operation,  $f_{OSC} = 22.5792$  MHz (SM5872A) or 16.9344 MHz (SM5872B),  $T_a = 25$  deg. C

| Parameter                           | Symbol Condition — |                                                                                         | Rating |        |        | Unit             |

|-------------------------------------|--------------------|-----------------------------------------------------------------------------------------|--------|--------|--------|------------------|

| Parameter                           |                    |                                                                                         | min    | typ    | max    | Offic            |

| Total harmonic distortion and noise | THD + N            | $f = 1 \text{ kHz}, V_1 = 0 \text{ dB}$                                                 | -      | 0.0020 | 0.0035 | %                |

| Output level                        | Vout               | $f = 1 \text{ kHz}, V_1 = 0 \text{ dB}$                                                 | 1.8    | 2.0    | 2.2    | V <sub>rms</sub> |

| Dynamic range                       | D.R                | $f = 1 \text{ kHz}, V_1 = -60 \text{ dB}$                                               | 92     | 98     | _      | dB               |

| Signal-to-noise ratio               | S/N                | $ \begin{cases} f = 1 & kHz, \\ V_I = 0 & to -\infty & dB. \\ See & note. \end{cases} $ | 96     | 102    | -      | dB               |

| Channel separation                  | Ch. Sep            | $  f = 1 \text{ kHz}, $ $  V_I = 0 \text{ to } -\infty \text{ dB} $                     | 92     | 98     | _      | dB               |

#### Note

The signal-to-noise ratio (S/N) is measured after reset has been cancelled and with DI held LOW. This includes the noise produced by the noise shaper.

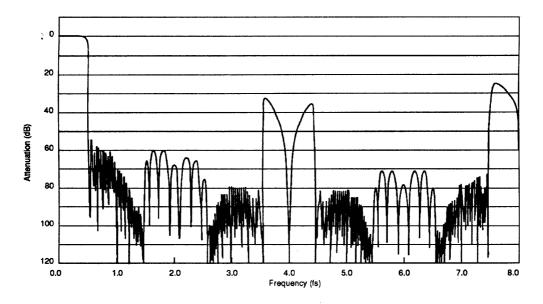

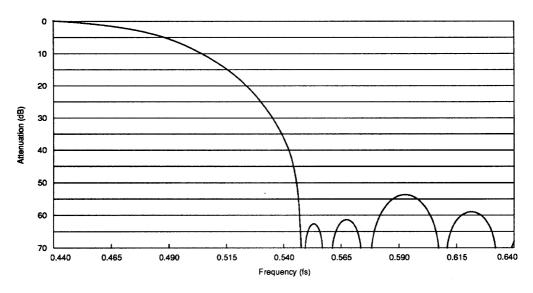

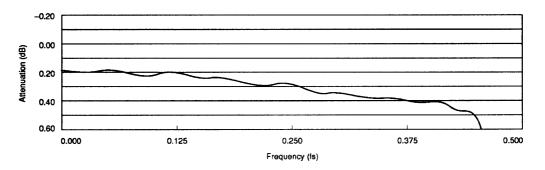

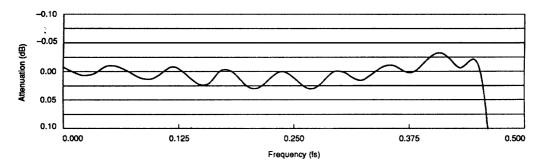

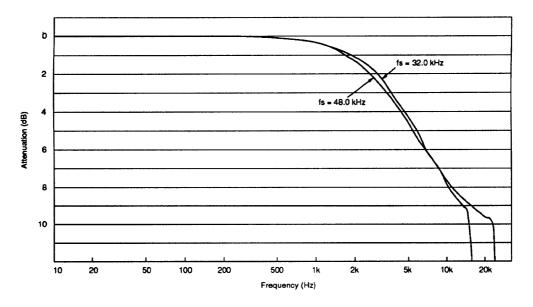

## Theoretical Filter Characteristics

The overall frequency characteristics of the IIR deemphasis filter, the eight-times oversampling FIR

filter, and the 32fs sample-and-hold circuit are shown in the following tables and graphs.

## Deemphasis disabled

|                                      | Frequency range |                | Rating |     |      |      |

|--------------------------------------|-----------------|----------------|--------|-----|------|------|

| Parameter                            | fs              | @fs = 44.1 kHz | min    | typ | max  | Unit |

| Passband ripple                      | 0 to 0.4535     | 0 to 20.0      | -0.05  | -   | 0.05 | dB   |

| Attenuation relative to 1 kHz signal | 0.4535          | 20.0           | _      | -   | 0.34 | dB   |

|                                      | 0.5465 to 3.45  | 24.1 to 152    | 53     | _   | _    |      |

| Stopband attenuation                 | 3.45 to 4.55    | 152 to 201     | 32     | -   | -    | dB   |

|                                      | 4.55 to 7.45    | 201 to 328     | 70     | -   | _    |      |

## Overall frequency characteristic (Deemphasis OFF)

## Transition band characteristic (Deemphasis OFF)

## Passband characteristic (Deemphasis OFF)

## Passband-only ripple characteristic (Deemphasis OFF)

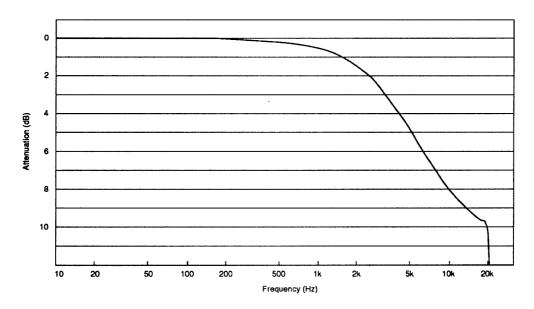

## Deemphasis enabled

| Parameter                            | Sampling      | Passband      |      | Rating |     | Unit |

|--------------------------------------|---------------|---------------|------|--------|-----|------|

| Latational                           | frequency, is | rassband      | min  | typ    | max | Unit |

| Deviation from ideal characteristics | 44.1 kHz      | 0 to 19.6 kHz | -0.1 | -      | 0.3 | dB   |

|                                      | 48.0 kHz      | 0 to 21.4 kHz | -0.1 | -      | 0.3 | dB   |

|                                      | 32.0 kHz      | 0 to 14.0 kHz | -0.4 | -      | 0.6 | dB   |

## Note

All frequencies are doubled in double-speed mode.

## Overall frequency characteristic (Deemphasis ON)

fs = 44.1 kHz

fs = 32.0 or 48.0 kHz

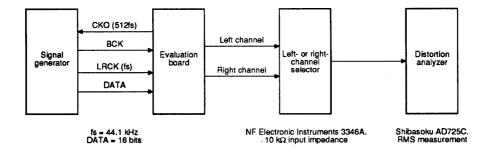

## **Measurement Circuits**

## Measurement circuit block diagram

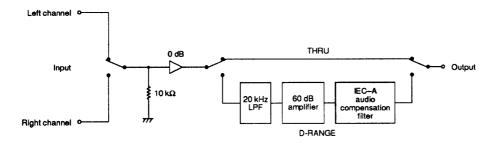

## Channel selector internal circuit

## **Measurement conditions**

| Parameter                           | Symbol  | 3346A channel selector position | AD725C distortion analyzer setting                                                              |

|-------------------------------------|---------|---------------------------------|-------------------------------------------------------------------------------------------------|

| Total harmonic distortion and noise | THD + N | THRU                            | :                                                                                               |

| Output level                        | Vo      | Inno                            | 20 kHz lowpass filter is ON.<br>400 Hz highpass filter is OFF.                                  |

| Dynamic range                       | D.R     | D-RANGE                         |                                                                                                 |

| Signal-to-noise ratio               | S/N     | THRU                            | 20 kHz lowpass filter is ON.<br>400 Hz highpass filter is OFF.<br>JIS* A-weighted filter is ON. |

| Channel separation                  | Ch. Sep | THRU                            | 20 kHz lowpass filter is ON.<br>400 Hz highpass filter is OFF.                                  |

## Note

JIS = Japanese Industrial Standard

## **FUNCTIONAL DESCRIPTION**

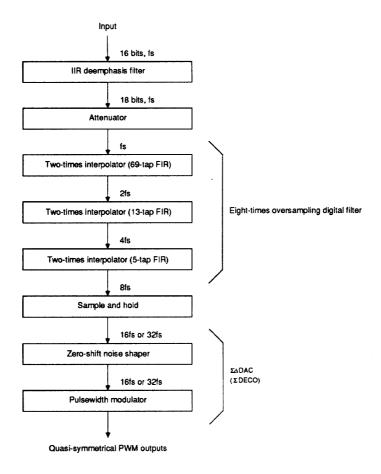

## **Functional Block Diagram**

The basic arithmetic operation of the  $\Sigma DECO$  SM5872A/B is shown in figure 1.

Figure 1. Arithmetic operation

## Oversampling Filter

The oversampling filter comprises three, two-times oversampling filters—a 69-tap finite impulse response (FIR) filter, a 13-tap FIR filter and a 5-tap FIR filter. These filters raise the sample rate of the input signal to 8fs and attenuate quantization noise between 0.5465fs and 7.4535fs. The signal is oversampled again to either 16fs or 32fs by the sample-and-hold circuit and then input to the zero-shift noise shaper.

## Controlling the Built-in Functions

The built-in functions are controlled either by input pin logic levels or by the microcontroller interface as shown in table 1.

Table 1. Built-in functions

| Function                | Input pin logic<br>level mode<br>(MCOM is LOW) | Microcontroller interface<br>mode (MCOM is HIGH) |

|-------------------------|------------------------------------------------|--------------------------------------------------|

| Deemphasis<br>ON/OFF    | DEEM                                           | FDEEM                                            |

| Deemphasis fs<br>mode   | FSEL1, FSEL2                                   | FFSL1, FFSL2                                     |

| Attenuator data         | No attenuation                                 | 7-bit data (a1 to a7)                            |

| IIS (64fs BCKI)<br>mode | Not selectable                                 | IIS                                              |

| BCKI polarity<br>mode   | Not selectable                                 | BCPL                                             |

Note that the deemphasis functions can be controlled using both methods. The MCOM state and the control mode should not be changed after a reset or power-ON.

#### Microcontroller Interface

When MCOM is HIGH, MDT, MCK and MLEN function as the microcontroller data clock and latch enable inputs, respectively. Using this interface, an external microcontroller can control the built-in functions and also read the attenuation data and mode flag registers.

The data from the microcontroller input on MDT is latched into the internal shift register on the rising edge of MCK. Changing the state of MDT should, therefore, be done on the falling edge of MCK. The data in the serial-in-parallel-out (SIPO) shift register is latched into either the attenuation data or the mode flag registers on the rising edge of MLEN.

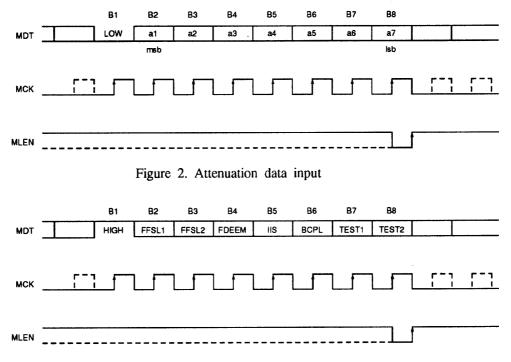

When the first data bit, B1 is LOW, the attenuation data, shown in figure 2, is written to the attenuation data register. When B1 is HIGH, the mode flags, shown in figure 3 and table 2 are written to the mode flag register. Note that MCK and MLEN can have waveforms as shown by the dotted lines in the following two figures.

Figure 3. Mode flag data input

Table 2. Mode flags (B1 = HIGH)

| Bit | Mode flag | Description                     | 0.                                                                                   | 1                                  |  |  |

|-----|-----------|---------------------------------|--------------------------------------------------------------------------------------|------------------------------------|--|--|

| B2  | FFSL1     | Doomahasia frasusany aslast hit | See table 3.                                                                         |                                    |  |  |

| B3  | FFSL2     | Deemphasis frequency select bit | See table 3.                                                                         |                                    |  |  |

| B4  | FDEEM     | Deemphasis ON/OFF select        | Deemphasis is OFF.                                                                   | Deemphasis is ON.                  |  |  |

| B5  | IIS       | IIS (64fs BCKI) mode select     | Normal format data (data at end of channel time, LRCI is HIGH for the left channel.) | IIS format data (64fs BCKI)        |  |  |

| B6  | BCPL      | BCKI polarity select            | Data read on rising edge of BCKI.                                                    | Data read on falling edge of BCKI. |  |  |

| B7  | TEST1     | Test mode select                | Tie LOW for normal appretion                                                         |                                    |  |  |

| B8  | TEST2     | Test mode select                | Tie LOW for normal operation.                                                        |                                    |  |  |

Note that all mode flags are LOW after the devices are reset.

## Deemphasis Filter

The deemphasis filter is an infinite impulse response (IIR) filter with variable filter coefficients that reproduces the gain and phase characteristics of an analog filter. The filter coefficients can be set to one of three sampling rates as shown in table 3. Deemphasis is turned ON and OFF by DEEM when MCOM is LOW and by the FDEEM flag when MCOM is HIGH.

Table 3. Deemphasis selection

| MCOM  | is LOW. | MCOM  | s HIGH. | Deemphasis      |

|-------|---------|-------|---------|-----------------|

| FSEL2 | FSEL1   | FFSL2 | FFSL1   | frequency (kHz) |

| LOW   | LOW     | 0     | 0       | 44.1            |

| LOW   | HIGH    | 0     | 1       | 44.1            |

| HIGH  | LOW     | 1 .   | 0       | 48.0            |

| HIGH  | HIGH    | 1     | 1       | 32.0            |

#### **Attenuator**

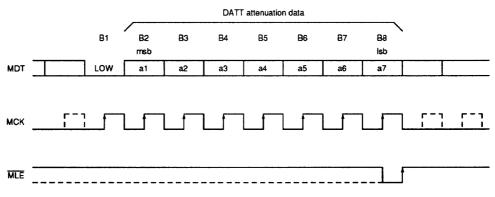

The 7-bit attenuation coefficient data, DATT, is loaded by the SM5872A/B as shown in figure 4.

Figure 4. Attenuation data

The output signals are attenuated by multiplying the signal data by the contents of the built-in 7-bit attenuation up/down counter. If the counter value equals the DATT attenuation coefficient, the gain for each channel is given by the following equation.

$Gain = 20 \times log_{10} (1 - DATT/127) dB$

Both channels are muted completely when the DATT coefficient is 127. Upon reset, DATT is set to zero, corresponding to the maximum gain of 0 dB.

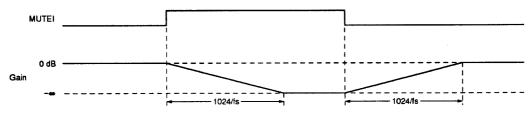

When a new DATT attenuation coefficient is loaded, the gain for each channel ramps up or down to the new level set by the coefficient as shown in

figure 5. If another attenuation coefficient is loaded before this new level has been reached, the gain ramps in the direction of the newest level setting.

The gain can change in this way because the current attenuation level is stored in a different register from the DATT coefficient register.

Figure 5. Attenuation example

## Soft mute

When MUTEI is taken HIGH, the soft mute function using the built-in attenuation counter is enabled. The counter increments, decreasing the gain level, until the outputs are completely muted. Muting takes 1024/fs seconds, or approximately 23.2 ms when fs is 44.1 kHz.

Whe MUTEI is taken LOW again, muting is cancelled and the attenuation counter decrements, increasing the gain level. Returning to the 0 dB level also takes 1024/fs seconds as shown in figure 6.

Figure 6. Soft muting

## System Clock

The system clock can oscillate at 256fs, 384fs or 512fs, depending upon the device, selected by the level on CKSL. When the system clock frequency is 256fs (SM5872A only), double-speed playback is

possible. The normal- and double-speed mode system clock frequencies are shown in the following tables.

## SM5872A

## Normal-speed mode

$V_{DD} = 3.2$  to 5.5 V,  $T_a = -20$  to 70 deg. C

| f <sub>LRC1</sub> = fs (kHz) | fxTI = fcko (MHz) |              |

|------------------------------|-------------------|--------------|

|                              | CKSL is HIGH.     | CKSL is LOW. |

| 44.1                         | 22.5792           | 11.2896      |

| 48.0                         | 24.576            | 12.288       |

| 32.0                         | 16.384            | 8.192        |

#### Double-speed mode

$V_{DD} = 4.5$  to 5.5 V,  $T_a = -20$  to 70 deg. C, CKSL is LOW.

| f <sub>LRCI</sub> = fs (kHz) | f <sub>XTI</sub> = f <sub>CKO</sub> (MHz) |

|------------------------------|-------------------------------------------|

| 88.2                         | 22.5792                                   |

| 96.0                         | 24.576                                    |

| 64.0                         | 16.384                                    |

#### SM5872B

#### Normal-speed mode

$V_{DD} = 3.2$  to 5.5 V,  $T_a = -20$  to 70 deg. C

| f <sub>LRCI</sub> = fs (kHz) | fxті = fcко (MHz) |              |  |

|------------------------------|-------------------|--------------|--|

|                              | CKSL is HIGH.     | CKSL is LOW. |  |

| 44.1                         | 16.9344           | Not used     |  |

| 48.0                         | 18.432            | Not used     |  |

| 32.0                         | 12.288            | Not used     |  |

As the stability and signal-to-noise ratio of the system clock greatly affects the AC analog characteristics, care should be taken to ensure that the clock is free from jitter.

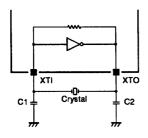

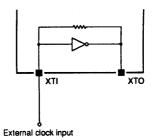

The system clock can be controlled by a crystal oscillator connected as shown in figure 7. Capacitors C1 and C2 should be chosen to match the crystal oscillator.

Figure 7. External crystal oscillator connection

The system clock can also be supplied externally as shown in figure 8. When using this method, XTO should be left open. As the system clock inverter has an internal feedback resistor, the external clock input can be AC coupled.

Figure 8. External system clock connection

To optimize the AC analog characteristics, use an external crystal oscillator connected to a 74HCU04 inverter to drive XTI.

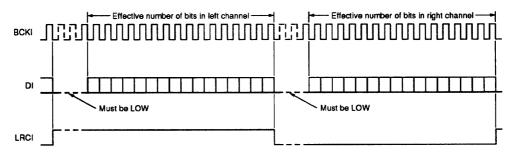

## **Audio Data Input**

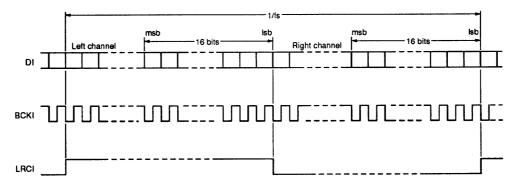

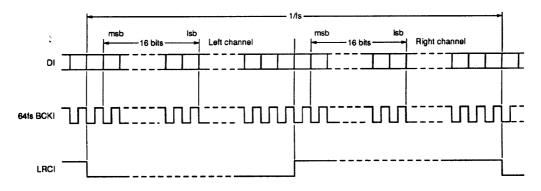

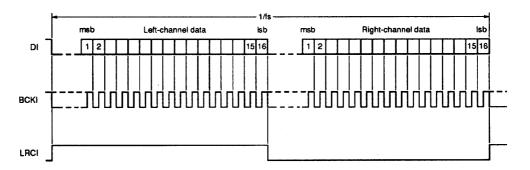

The digital audio data is input on DIN in 2s-complement, msb-first, 16-bit serial data format with interleaved left- and right-channel data words.

When the IIS flag is 0, the normal data format shown in figure 9 is selected. When the IIS flag is 1, the IIS data format shown in figure 10 is selected.

The data input on DI is latched into the internal SIPO shift register on either the rising edge of BCKI (when the BCPL flag is 0) or the falling edge (when the BCPL flag is 1).

The data is latched into either the left-channel or right-channel input register on the rising and falling edges of LRCI. When the IIS flag is 0, the data is latched to the left-channel input register on the falling edge of LRCI, and when the IIS flag is 1, the data is latched to the left-channel register on the rising edge of LRCI.

Figure 9. Normal data format (IIS = 0)

Figure 10. IIS data format (IIS = 1)

The timing of the arithmetic and output circuits is independent of the input circuits, isolating them from jitter or skew on the input circuit clocks. As a result, phase differences between LRCI, BCKI and XTI that may occur after a reset do not affect the correct operation of the device. However, the correct frequency ratio between LRCI and XTI should be maintained.

If the input data format uses word lengths greater than 16 bits (for example, 24- or 32-bit words) then the mute detector will not work unless all bits in the word other than the 16 data bits are set to 0. This condition does not have to be satisfied, however, if MUTEO is not being used.

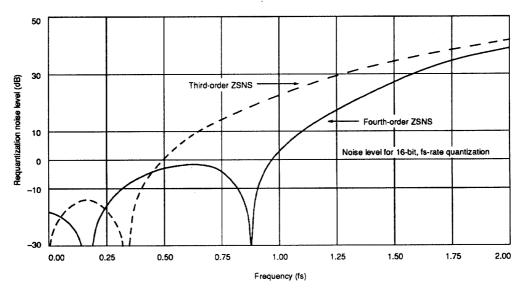

## Zero-shift Noise Shaper

The fourth-order zero-shift noise shaper (ZSNS) virtually eliminates noise in the 13-level quantized signal by altering the noise characteristic. The characteristic is altered by shifting the zeros in the z-plane, moving the noise out of the audio band so it is then removed by the output filters.

The ZSNS suppresses noise in a frequency range exceeding twice the audio bandwidth for a 32fs

oversampled signal, and over almost the entire audio bandwidth for a 16fs oversampled signal. A theoretical characteristic is shown in figure 11, calculated by converting the data back into its original form, before the PWM output stage. Note that when CKSL is LOW, the frequency values should be halved.

Figure 11. Requantizer noise characteristic

## **Pulsewidth Modulation Waveforms**

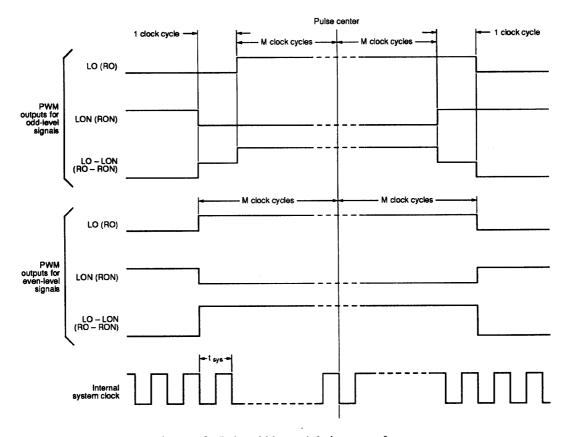

The signals output by the EDECO SM5872A/B are quasi-symmetrical. When the PWM outputs produce odd-valued output levels, the individual output signals are not symmetrical about the center of the output pulses, however, the difference signals (LO

- LON) and (RO - RON) are symmetrical as shown in figure 12. Even-valued output signals have symmetrical waveforms. Using this output method, the SM5872A/B can operate at half the clock frequency required by conventional devices.

Figure 12. Pulsewidth modulation waveforms

#### Reset

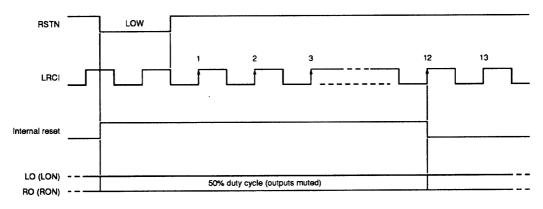

The  $\Sigma DECO$  SM5872A/B should be reset after power-up, when MCOM changes state or when the XTI clock stops for longer than 10  $\mu s.$  A LOW-level pulse on RSTN will resynchronize the

ΣDECO SM5872A/B internal arithmetic and output clocks on the first rising edge of LRCI after RSTN returns HIGH as shown in 13.

Figure 13. Reset waveforms

An external microcontroller can reset the devices at power-ON, or power-ON reset can be performed automatically if a capacitor is connected between RSTN and VSS. If the XTI and LRCI clocks are stable at power-up, then a value of 300 pF is sufficient to satisfy the reset timing requirements. If the XTI and LRCI clocks are not stable at power-up, then a value should be chosen such that RSTN goes HIGH only after both clocks have stabilized.

Upon reset, the PWM outputs are muted with a 50% duty cycle signal from the time when RSTN goes LOW until the 12th rising edge of LRCI after RSTN goes HIGH. Note that the duty cycle may change temporarily as the circuits resynchronize following the first rising edge of LRCI.

#### **Mute Detection**

MUTEO is LOW under the following three conditions.

- 1. While RSTN is LOW and for approximately 12 LRCI cycles after RSTN goes HIGH.

- 2. For approximately 12 LRCI cycles after CKSL changes state.

- 3. While a muted signal is detected as explained in the following paragraphs.

Note that the mute detector detects when the data bits are all 0 and does not detect when the bits are all 1.

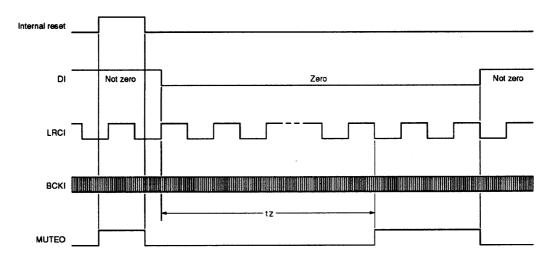

The mute detector monitors the BCKI, DI and LRCI inputs. DI should be LOW when not transmitting data if there are more BCKI pulses than there are data bits as shown in figure 14.

Figure 14. Input waveforms

When both channels contain zeros for 2<sup>19</sup> consecutive BCKI cycles, the internal counter overflows and MUTEO goes HIGH. When a 1 is input on DI, the counter is reset and MUTEO goes LOW again.

The time to overflow the counter can be calculated using the following equation.

$$t_z = 2^{19}/(NB \times fs)$$

where NB = the number of BCKI cycles per LRCI period (typically 32 or 48).

Figure 15. MUTEO output waveforms

For a 44.1 kHz sampling rate and 32 BCKI pulses per sampling period, 2<sup>19</sup> bits corresponds to a mute detect time of 372 ms. When there are 48 BCKI pulses per sampling period, the mute detect time becomes 248 ms as shown in table 4.

Table 4. Mute detect time

| Bit clock frequency | Mute detect time | Unit |

|---------------------|------------------|------|

| 32fs                | 372              | ms   |

| 48fs                | 248              | ms   |

Note

fs = 44.1 kHz

## TIMING DIAGRAMS

## **Digital Audio Input Formats**

Figure 16. Normal format (IIS is 0 and BCPL is 0.)

Figure 17. IIS format (IIS is 1 and BCPL is 0.)

## **APPLICATION NOTES**

## Input Interfaces

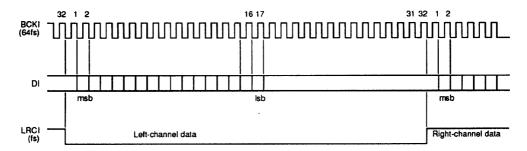

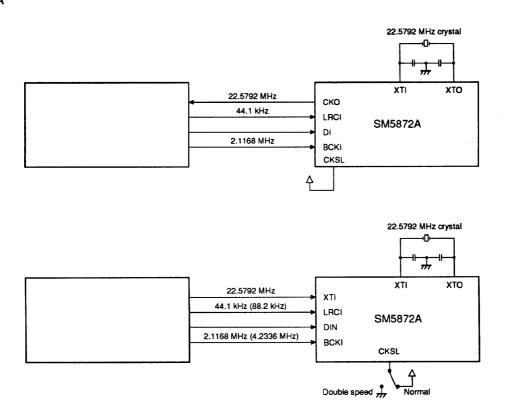

Normal data format (IIS is 0.)

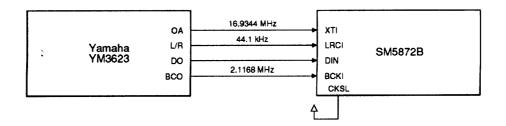

## Normal replay mode

SM5872A

## Note

The values in parentheses are for double-speed mode.

## SM5872B

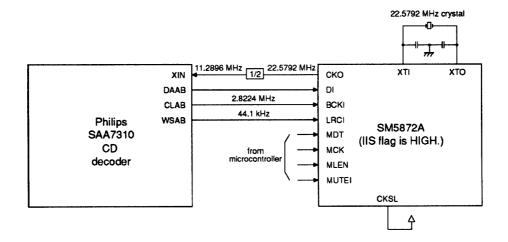

## IIS data format (IIS is 1.)

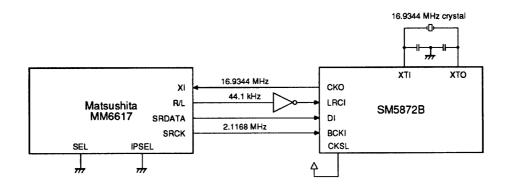

Figure 18. Phillips SAA7310 interface

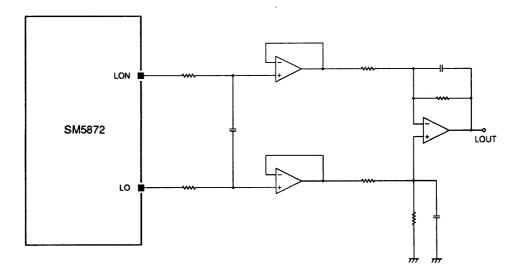

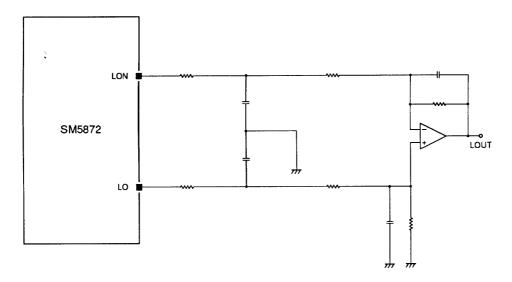

## **Output Interfaces**

In the following figures, only the left channel has been shown to avoid duplication.

Figure 19. Output interface 1

Figure 20. Output interface 2

Please pay your attention to the following points at time of using the products shown in this document.

The products shown in this document (hereinafter "Products") are not intended to be used for the apparatus that exerts harmful influence on human lives due to the defects, failure or malfunction of the Products. Customers are requested to obtain prior written agreement for such use from NIPPON PRECISION CIRCUITS INC. (hereinafter "NPC"). Customers shall be solely responsible for, and indemnify and hold NPC free and harmless from, any and all claims, damages, losses, expenses or lawsuits, due to such use without such agreement. NPC reserves the right to change the specifications of the Products in order to improve the characteristic or reliability thereof. NPC makes no claim or warranty that the contents described in this document dose not infringe any intellectual property right or other similar right owned by third parties. Therefore, NPC shall not be responsible for such problems, even if the use is in accordance with the descriptions provided in this document. Any descriptions including applications, circuits, and the parameters of the Products in this documents are for reference to use the Products, and shall not be guaranteed free from defect, inapplicability to the design for the mass-production products without further testing or modification. Customers are requested not to export or re-export, directly or indirectly, the Products to any country or any entity not in compliance with or in violation of the national export administration laws, treaties, orders and regulations. Customers are requested appropriately take steps to obtain required permissions or approvals from appropriate government agencies.

#### NIPPON PRECISION CIRCUITS INC.

4-3, Fukuzumi 2-chome, Koto-ku, Tokyo 135-8430, Japan Telephone: +81-3-3642-6661 Facsimile: +81-3-3642-6698 http://www.npc.co.jp/ Email: sales@npc.co.jp

NC9242BE 2002.11

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for nippon precision circuits manufacturer:

Other Similar products are found below:

Nippon Precision Circuits