# Am186™CC

# High-Performance, 80C186-Compatible 16-Bit Embedded Communications Controller

#### DISTINCTIVE CHARACTERISTICS

# ■ E86<sup>™</sup> family of x86 embedded processors offers improved time-to-market

- Software migration (backwards- and upwardscompatible)

- World-class development tools, applications, and system software

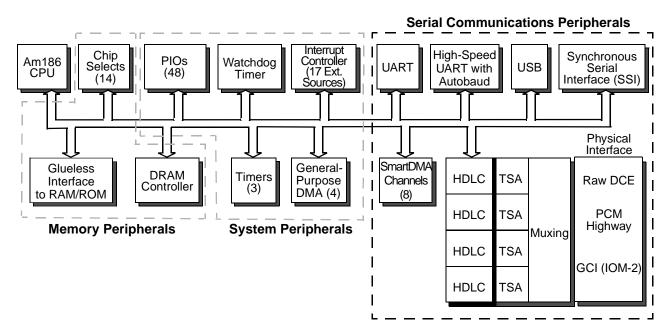

#### ■ Serial Communications Peripherals

- Four High-level Data Link Control (HDLC) channels

- Four independent Time Slot Assigners (TSAs)

- Physical interface for HDLC channels can be raw DCE, PCM Highway, or GCI (IOM-2)

- USB peripheral controller

- High-Speed UART with autobaud

- UART

- Synchronous serial interface (SSI)

- SmartDMA™ channels (8) to support USB/HDLC

#### ■ System Peripherals

- Three programmable 16-bit timers

- Hardware watchdog timer

- General-purpose DMA (4 channels)

- Programmable I/O (48 PIO signals)

- Interrupt Controller (36 maskable interrupts)

# ■ Memory and Peripheral Interface

- Integrated DRAM controller

- Glueless interface to RAM/ROM/Flash memory (55-ns Flash memory required for zero-wait-state operation at 50 MHz)

- Fourteen chip selects (8 peripherals, 6 memory)

- External bus mastering support

- Multiplexed and nonmultiplexed address/data bus

- Programmable bus sizing

- 8-bit boot option

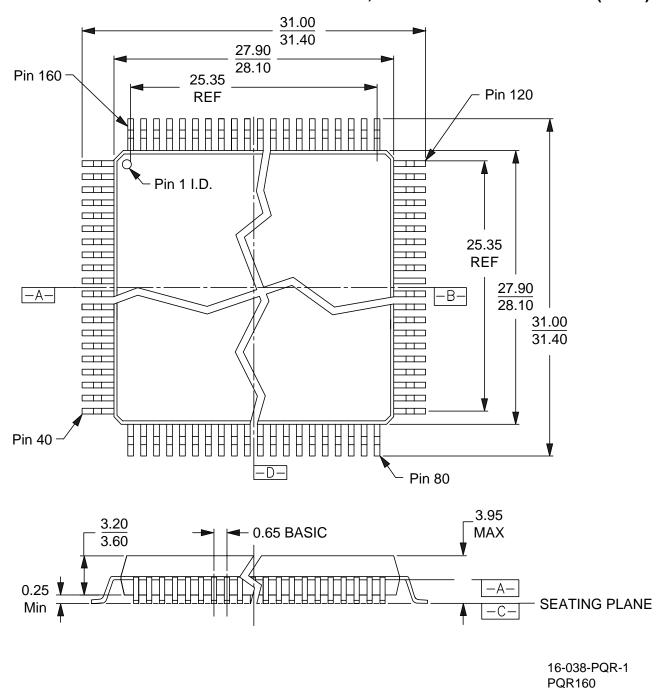

#### Available in the following package

- 160-pin plastic quad flat pack (PQFP)

- 25-, 40-, and 50-MHz operating frequencies

- Low-voltage operation,  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$

- Commercial and industrial temperature rating

- 5-V-tolerant I/O (3.3-V output levels)

#### **GENERAL DESCRIPTION**

The Am186™CC embedded communications controller is the first member in the AMD Comm86™ product family. The Am186CC controller is a cost-effective, high-performance microcontroller solution for communications applications. This highly integrated microcontroller enables customers to save system costs and increase performance over 8-bit microcontrollers and other 16-bit microcontrollers.

The Am186CC communications controller offers the advantages of the x86 development environment's widely available native development tools, applications, and system software. Additionally, the controller uses the industry-standard 186 instruction set that is part of the AMD E86™ family, which continually offers instruction-set-compatible upgrades. Built into the Am186CC controller is a wide range of communications features required in many communications applications, including High-level Data Link Control (HDLC) and the Universal Serial Bus (USB).

AMD offers complete solutions with the Am186CC controller. A customer development platform board is available. Reference designs under development include a low-end router with Integrated Services Digital Network (ISDN), Ethernet, USB, Plain Old Telephone Service (POTS), and an ISDN Terminal Adapter featuring USB. AMD and its FusionE86<sup>SM</sup> Partners offer boards, schematics, drivers, protocol stacks, and routing software for these reference designs to enable fast time to market.

Publication# 21915 Rev: B Amendment/0 Issue Date: May 2000

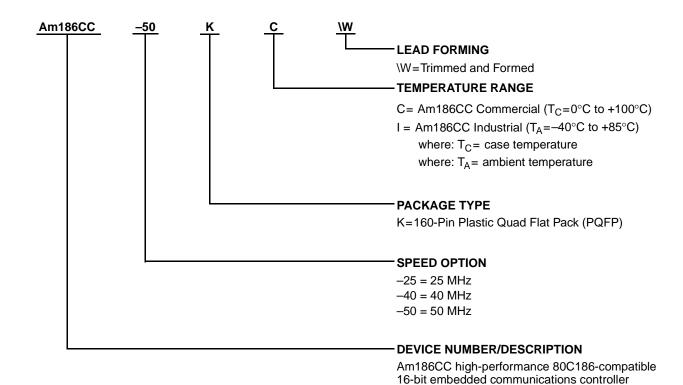

# ORDERING INFORMATION

| Valid Combinations |       |  |  |  |  |  |

|--------------------|-------|--|--|--|--|--|

| Am186CC-25         |       |  |  |  |  |  |

| Am186CC-40         | KC\W  |  |  |  |  |  |

| Am186CC-50         |       |  |  |  |  |  |

| Am186CC-25         | KI\W  |  |  |  |  |  |

| Am186CC-40         | KI\VV |  |  |  |  |  |

#### **Valid Combinations**

Valid combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# **TABLE OF CONTENTS**

| Distinctive Characteristics                                        | 1    |

|--------------------------------------------------------------------|------|

| General Description                                                | 1    |

| Ordering Information                                               | 2    |

| Logic Diagram by Interface                                         | 6    |

| Logic Diagram by Default Pin Function                              | 7    |

| Pin Connection Diagram—160-Pin PQFP Package                        | 8    |

| Pin and Signal Tables                                              | 9    |

| Signal Descriptions                                                |      |

| Architectural Overview                                             |      |

| Detailed Description                                               | . 28 |

| Am186 Embedded CPU                                                 | . 29 |

| Memory Organization                                                | . 29 |

| I/O Space                                                          |      |

| Serial Communications Support                                      | . 30 |

| Universal Serial Bus                                               |      |

| Four HDLC Channels and Four TSAs                                   |      |

| General Circuit Interface                                          |      |

| Eight SmartDMA™ Channels                                           |      |

| Two Asynchronous Serial Ports                                      |      |

| Synchronous Serial Port                                            |      |

| System Peripherals                                                 |      |

| Interrupt Controller                                               |      |

| Four General-Purpose DMA Channels                                  |      |

| 48 Programmable I/O Signals                                        |      |

| Three Programmable Timers                                          |      |

| Hardware Watchdog Timer                                            |      |

| Memory and Peripheral Interface                                    |      |

| System Interfaces                                                  |      |

| DRAM Support                                                       |      |

| Chip Selects                                                       |      |

| Clock Control                                                      |      |

| In-Circuit Emulator Support                                        |      |

| Applications                                                       |      |

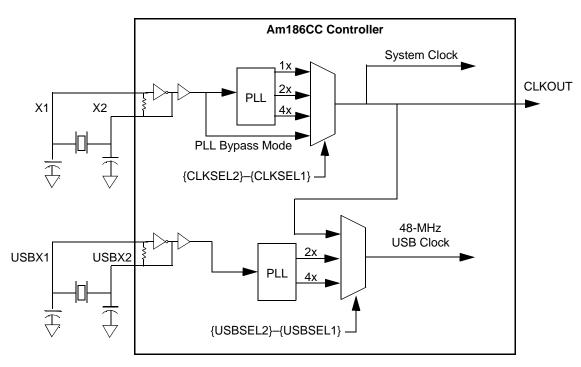

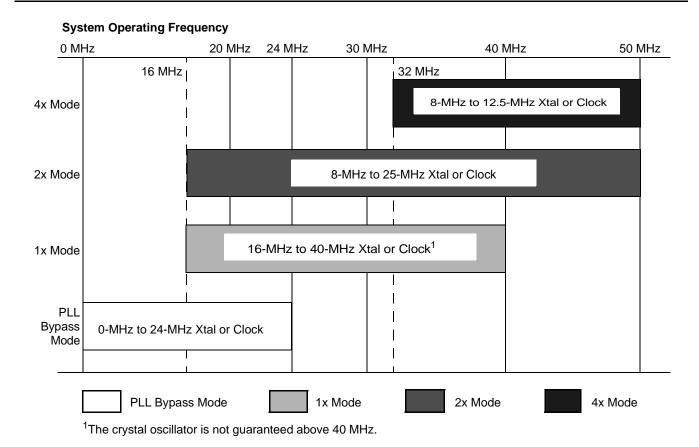

| Clock Generation and Control                                       |      |

| Features                                                           |      |

| System Clock                                                       |      |

| USB Clock                                                          |      |

| Clock Sharing by System and USB                                    |      |

| Crystal-Driven Clock Source                                        |      |

| External Clock Source                                              |      |

| Static Operation                                                   | . 43 |

| PLL Bypass Mode                                                    |      |

| UART Baud Clock                                                    |      |

| Power Supply Operation                                             |      |

| Power Supply Connections                                           |      |

| Input/Output Circuitry                                             |      |

| PIO Supply Current Limit                                           |      |

| Absolute Maximum Ratings                                           |      |

| Operating Ranges                                                   |      |

| Driver Characteristics—Universal Serial Bus                        |      |

| DC Characteristics over Commercial and Industrial Operating Ranges |      |

| Capacitance                                                        |      |

#

|                     | oad Derating<br>Dly Current                                                                         |      |

|---------------------|-----------------------------------------------------------------------------------------------------|------|

| • • •               |                                                                                                     |      |

|                     | aracteristics                                                                                       |      |

|                     | ackage                                                                                              |      |

|                     | and Industrial Switching Characteristics and Waveforms                                              |      |

|                     | Characteristics over Commercial and Industrial Operating Ranges                                     |      |

|                     | —Pin Tables                                                                                         |      |

|                     | Table Column Definitions                                                                            |      |

|                     | —Physical Dimensions: PQR160, Plastic Quad Flat Pack (PQFP)                                         |      |

|                     | —Customer Support                                                                                   |      |

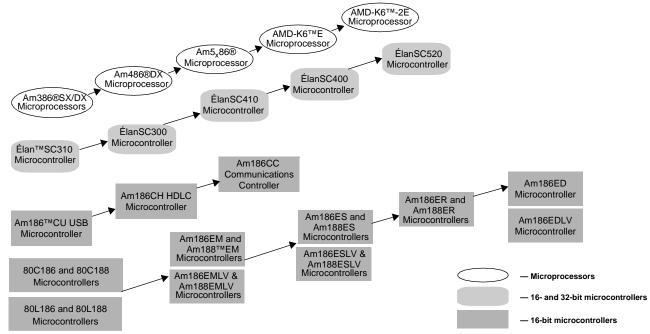

|                     | AMD Products—E86™ Family Devices                                                                    |      |

|                     | Documents Documents                                                                                 |      |

|                     | C/CH/CU Microcontroller Customer Development Platform                                               |      |

|                     | ty Development Support Products                                                                     |      |

|                     | r Service                                                                                           |      |

|                     | e and World Wide Web Support                                                                        |      |

| •                   | rate Applications Hotline                                                                           |      |

|                     | Wide Web Home Page                                                                                  |      |

|                     | nentation and Literature                                                                            |      |

|                     | ture Ordering                                                                                       |      |

| inaex               | Ind                                                                                                 | ex-1 |

| LIST OF F           | IGURES                                                                                              |      |

|                     | Am186CC Controller Block Diagram                                                                    | 20   |

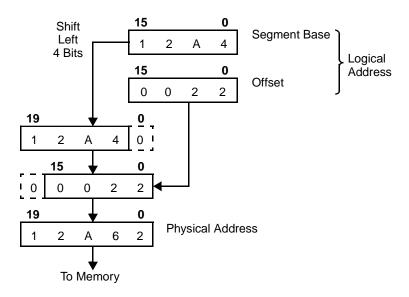

| Figure 1.           | Two-Component Address Example                                                                       |      |

| Figure 2.           |                                                                                                     |      |

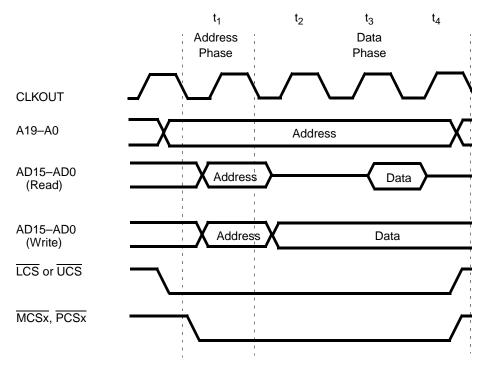

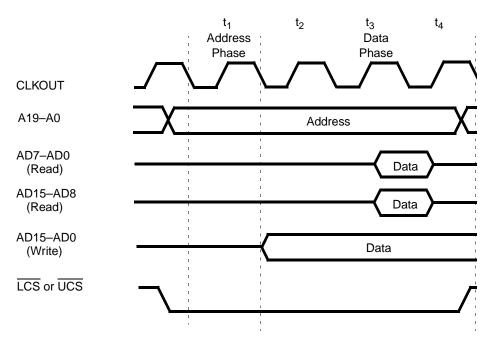

| Figure 3.           | Am186CC Controller Address Bus — Default Operation Am186CC Controller—Address Bus Disable In Effect |      |

| Figure 4.           |                                                                                                     |      |

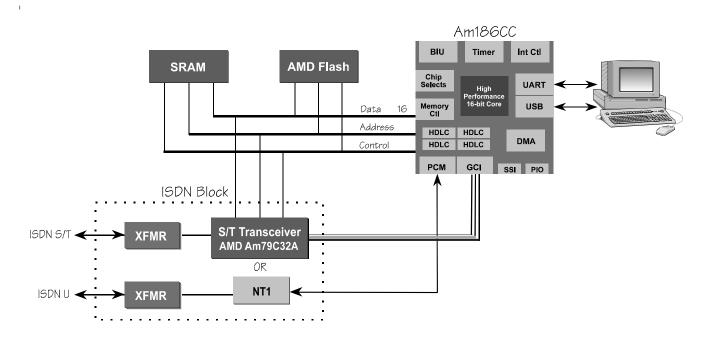

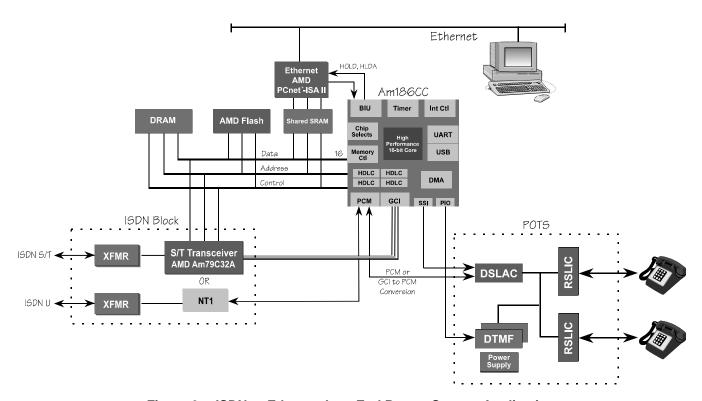

| Figure 5.           | ISDN Terminal Adapter System ApplicationISDN to Ethernet Low-End Router System Application          |      |

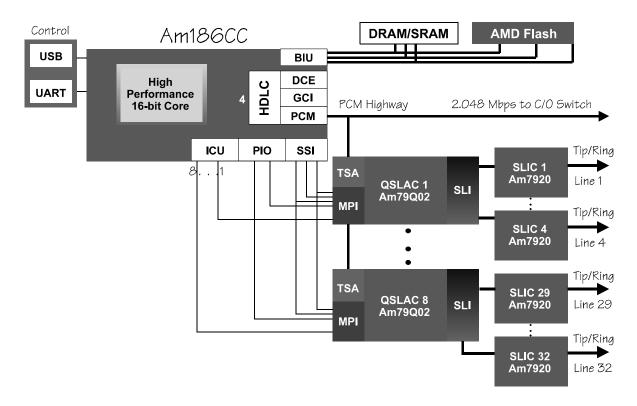

| Figure 6.           | 32-Channel Linecard System Application                                                              |      |

| Figure 7. Figure 8. | System and USB Clock Generation                                                                     |      |

| •                   | Suggested System Clock Frequencies, Clock Modes, and Crystal Frequencies                            |      |

| Figure 9.           |                                                                                                     |      |

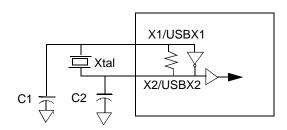

| Figure 10.          | External Interface to Support Clocks—Fundamental Mode Crystal                                       |      |

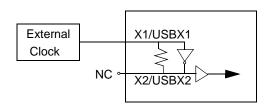

| Figure 11.          | External Interface to Support Clocks—External Clock Source                                          |      |

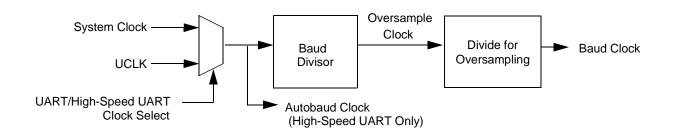

| Figure 12.          | UART and High-Speed UART Clocks                                                                     |      |

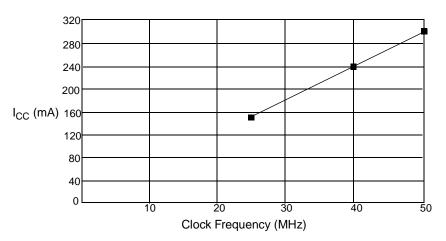

| Figure 13.          | Typical I <sub>cc</sub> Versus Frequency                                                            |      |

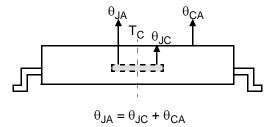

| Figure 14.          | Thermal Resistance (°C/Watt)                                                                        |      |

| Figure 15.          | Thermal Characteristics Equations                                                                   |      |

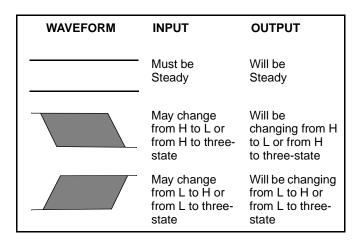

| Figure 16.          | Key to Switching Waveforms                                                                          |      |

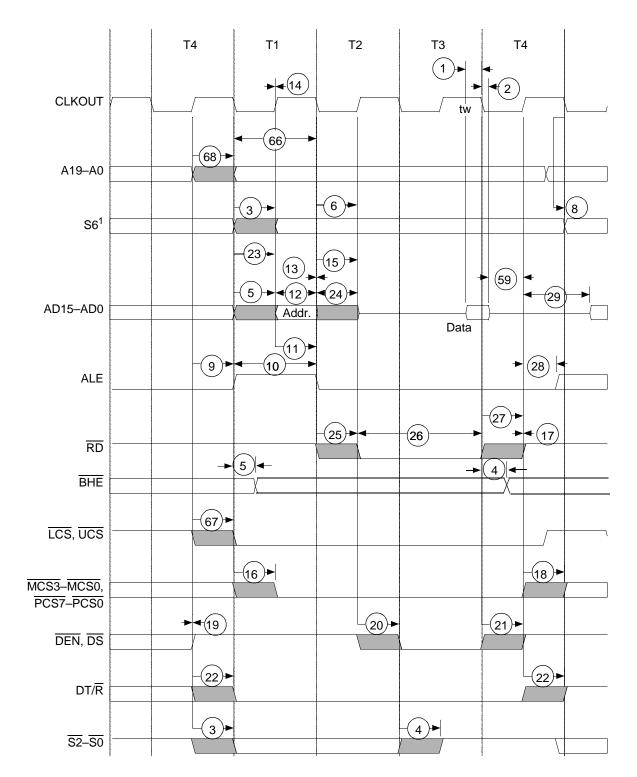

| Figure 17.          | Read Cycle Waveforms                                                                                |      |

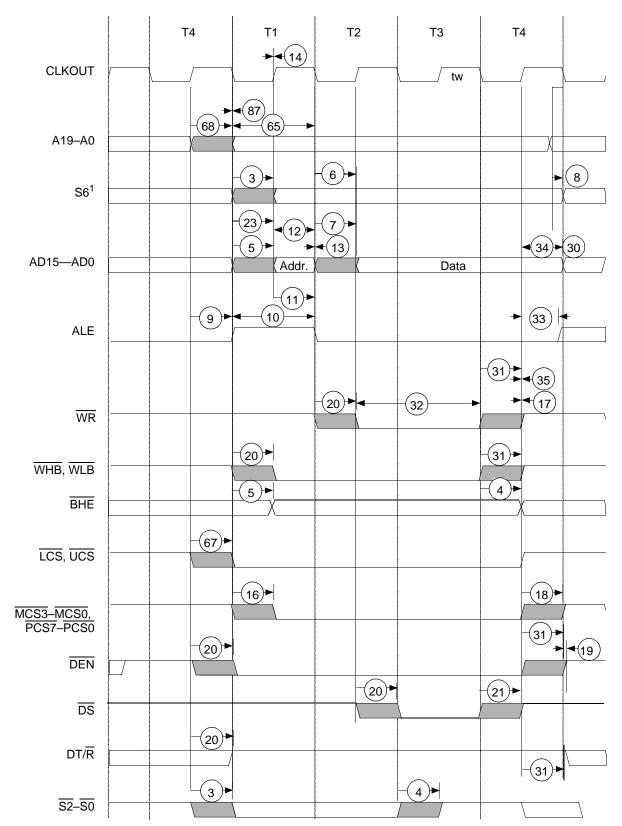

| Figure 18.          | Write Cycle Waveforms                                                                               |      |

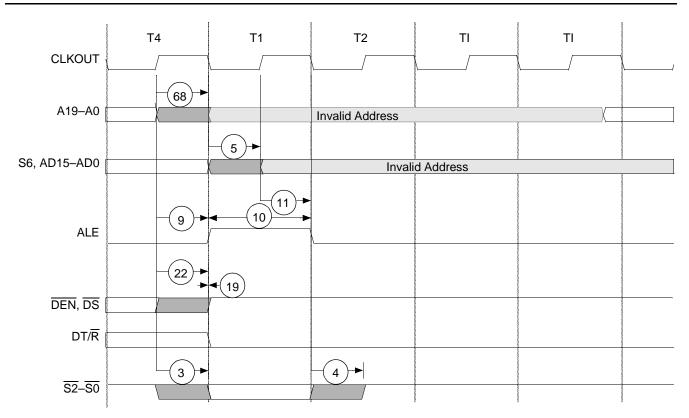

| Figure 19.          | Software Halt Cycle Waveforms                                                                       |      |

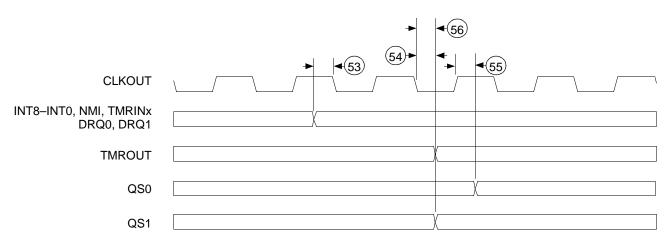

| Figure 20.          | Peripheral Timing Waveforms                                                                         |      |

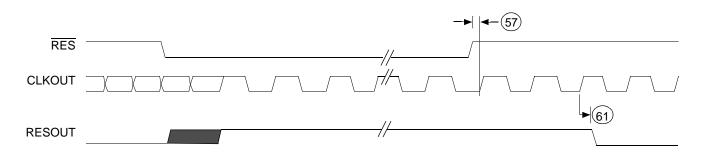

| Figure 21.          | Reset Waveforms                                                                                     |      |

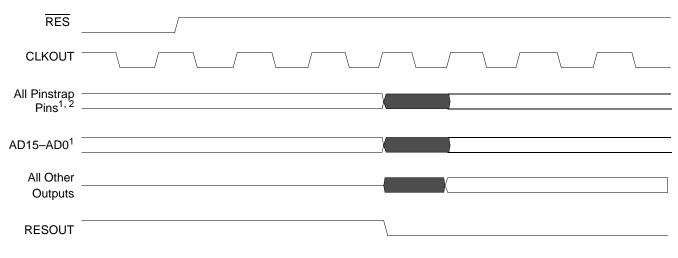

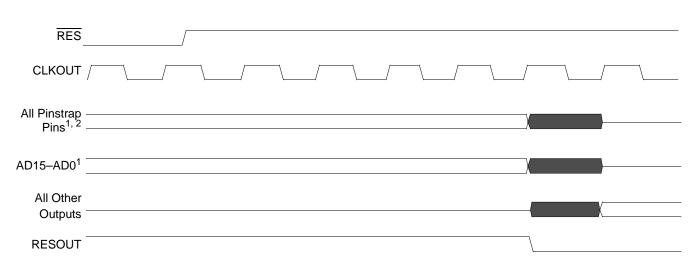

| Figure 22.          | Signals Related to Reset (System PLL in 1x or 2x Mode)                                              |      |

| Figure 23.          | Signals Related to Reset (System PLL in 4x Mode)                                                    |      |

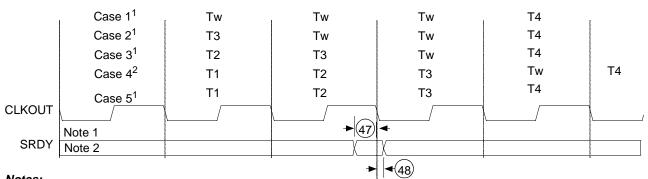

| Figure 24.          | Synchronous Ready Waveforms                                                                         |      |

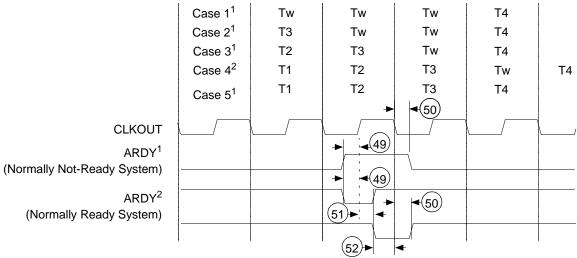

| Figure 25.          | Asynchronous Ready Waveforms                                                                        |      |

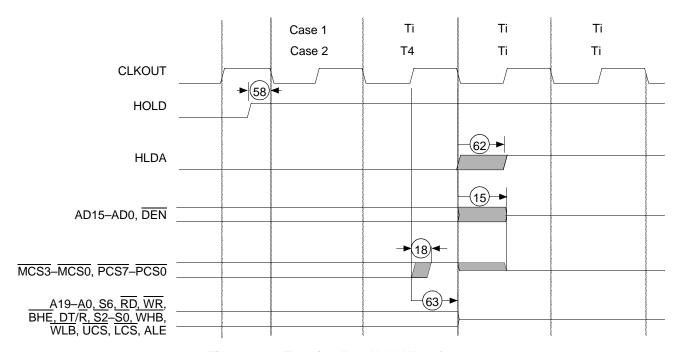

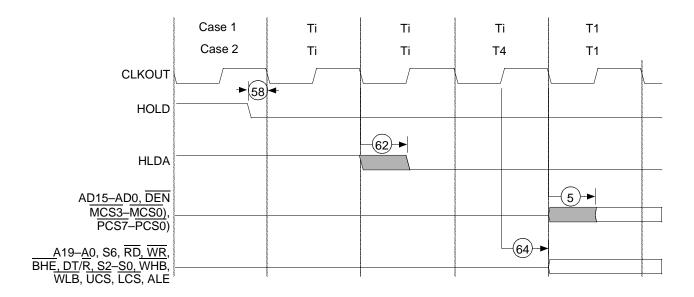

| Figure 26.          | Entering Bus Hold Waveforms                                                                         |      |

| Figure 27.          | Exiting Bus Hold Waveforms                                                                          |      |

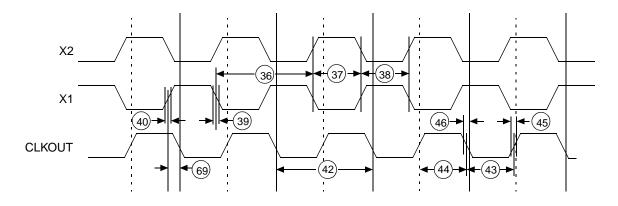

| Figure 28.          | System Clock Timing Waveforms—Active Mode (PLL 1x Mode)                                             |      |

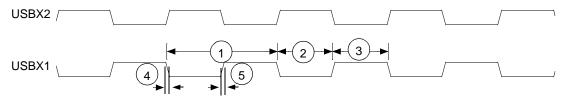

| Figure 29.          | USB Clock Timing Waveforms                                                                          |      |

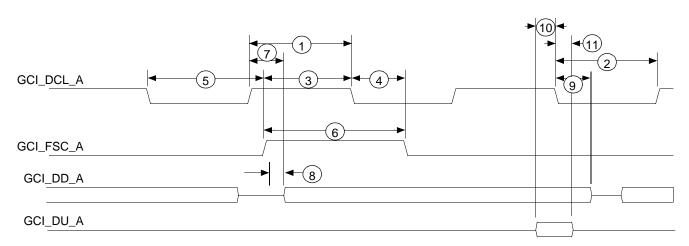

| Figure 30.          | GCI Bus Waveforms                                                                                   | 73   |

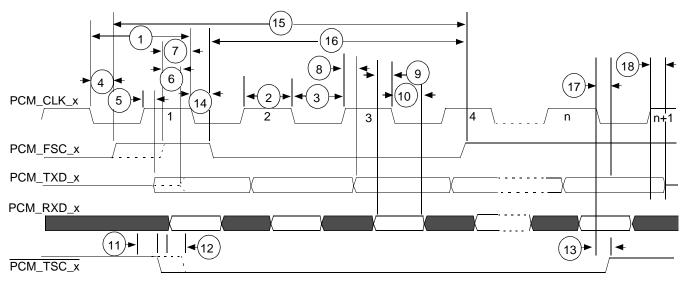

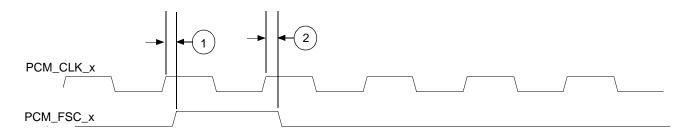

| Figure 31. | PCM Highway Waveforms (Timing Slave)            | 75          |

|------------|-------------------------------------------------|-------------|

| Figure 32. | PCM Highway Waveforms (Timing Master)           | 76          |

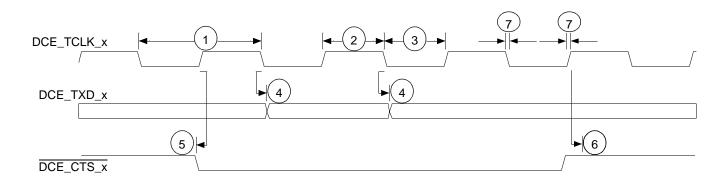

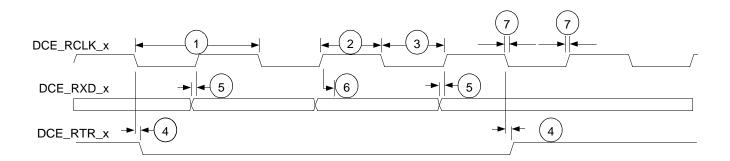

| Figure 33. | DCE Transmit Waveforms                          | 77          |

| Figure 34. | DCE Receive Waveforms                           | 77          |

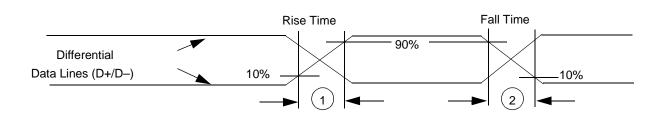

| Figure 35. | USB Data Signal Rise and Fall Times             | 78          |

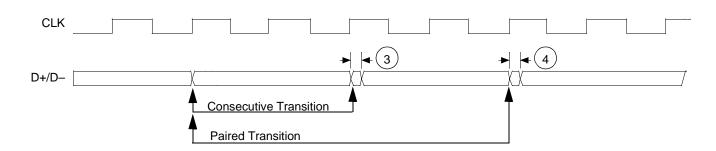

| Figure 36. | USB Receiver Jitter Tolerance                   | 78          |

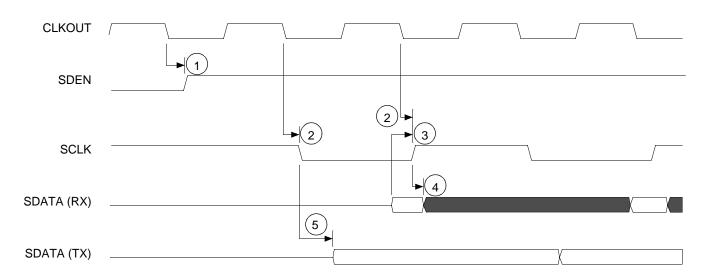

| Figure 37. | Synchronous Serial Interface Waveforms          | 79          |

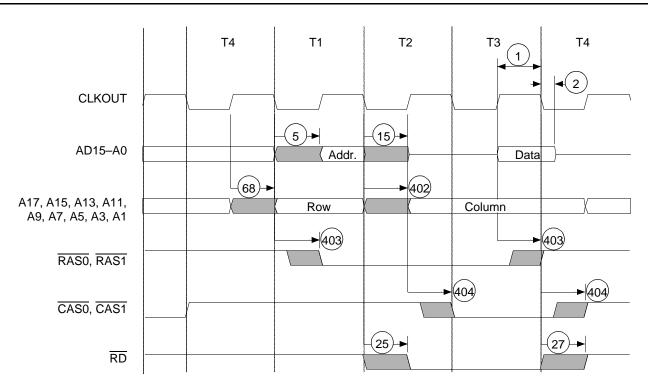

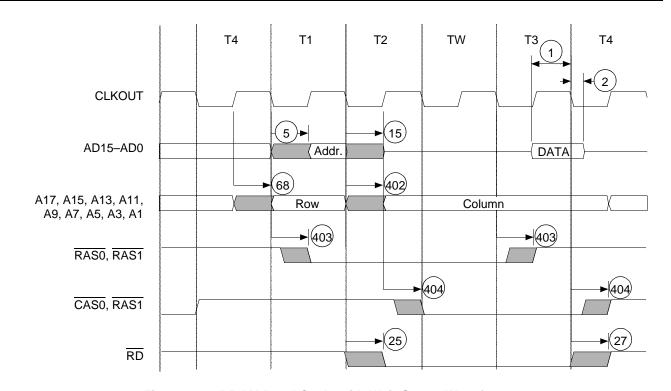

| Figure 38. | DRAM Read Cycle without Wait-States Waveform    |             |

| Figure 39. | DRAM Read Cycle with Wait-States Waveform       | 81          |

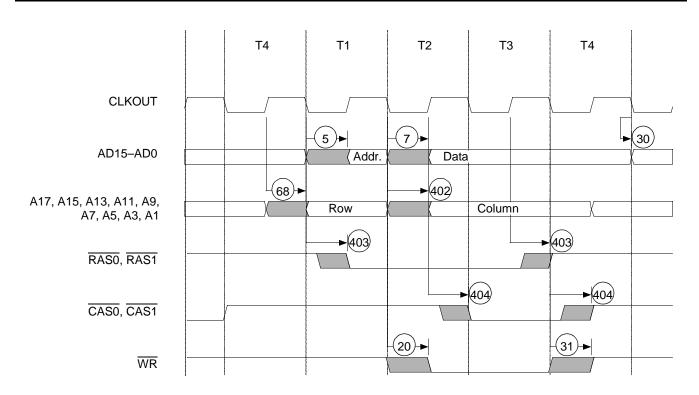

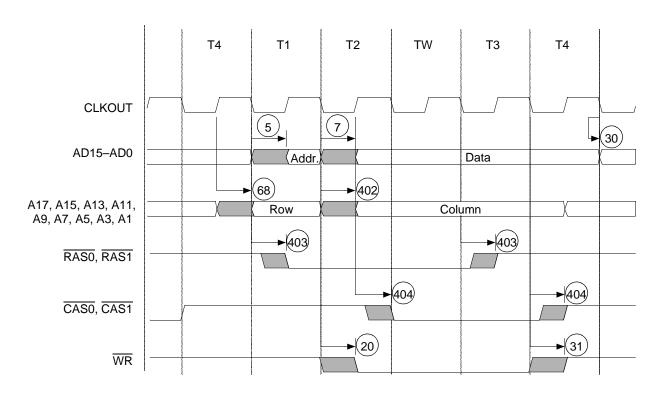

| Figure 40. | DRAM Write Cycle without Wait-States Waveform   |             |

| Figure 41. | DRAM Write Cycle with Wait-States Waveform      |             |

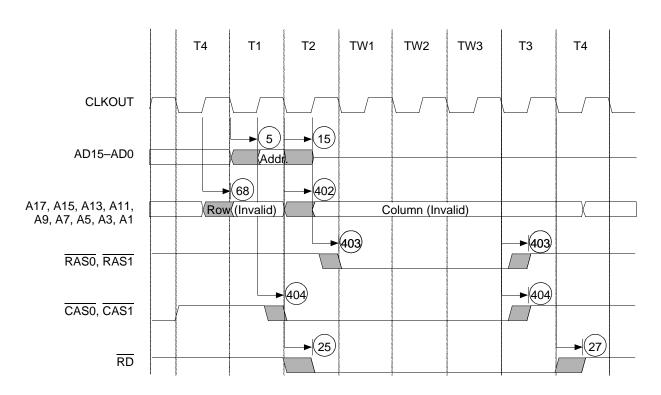

| Figure 42. | DRAM Refresh Cycle Waveform                     |             |

| 3          | •                                               |             |

| LIST OF TA | ABLES                                           |             |

| Table 1.   | PQFP Pin Assignments—Sorted by Pin Number       | 10          |

| Table 2.   | PQFP Pin Assignments—Sorted by Signal Name      |             |

| Table 3.   | Signal Description Table Definitions            |             |

| Table 4.   | Signal Descriptions                             |             |

| Table 5.   | Segment Register Selection Rules                |             |

| Table 6.   | Crystal Parameters                              |             |

| Table 7.   | Typical Power Consumption Calculation           |             |

| Table 8.   | Thermal Characteristics (°C/Watt)               |             |

| Table 9.   | Alphabetical Key to Switching Parameter Symbols |             |

| Table 10.  | Numerical Key to Switching Parameter Symbols    |             |

| Table 11.  | Read Cycle Timing                               |             |

| Table 12.  | Write Cycle Timing                              |             |

| Table 13.  | Software Halt Cycle Timing                      |             |

| Table 14.  | Peripheral Timing                               |             |

| Table 15.  | Reset Timing                                    |             |

| Table 16.  | External Ready Cycle Timing                     |             |

| Table 17.  | Bus Hold Timing                                 |             |

| Table 18.  | System Clocks Timing                            |             |

| Table 19.  | USB Clocks Timing                               |             |

| Table 20.  | GCI Bus Timing                                  |             |

| Table 21.  | PCM Highway Timing (Timing Slave)               |             |

| Table 22.  | PCM Highway Timing (Timing Master)              |             |

| Table 23.  | DCE Interface Timing                            |             |

| Table 24.  | USB Timing                                      |             |

| Table 25.  | SSI Timing                                      |             |

| Table 26.  | DRAM Timing                                     |             |

| Table 27.  | Power-On Reset (POR) Pin Defaults               |             |

| Table 28.  | Multiplexed Signal Trade-offs                   |             |

| Table 29.  | PIOs Sorted by PIO Number                       |             |

| Table 30.  | PIOs Sorted by Signal Name                      |             |

| Table 31.  | Reset Configuration Pins (Pinstraps)            |             |

| Table 32.  | CPU PLL Modes                                   |             |

| Table 33.  | USB PLL Modes                                   |             |

| Table 34.  | Pin List Table Definitions                      |             |

| Table 35.  | Pin List Summary                                |             |

|            |                                                 | · · · · · - |

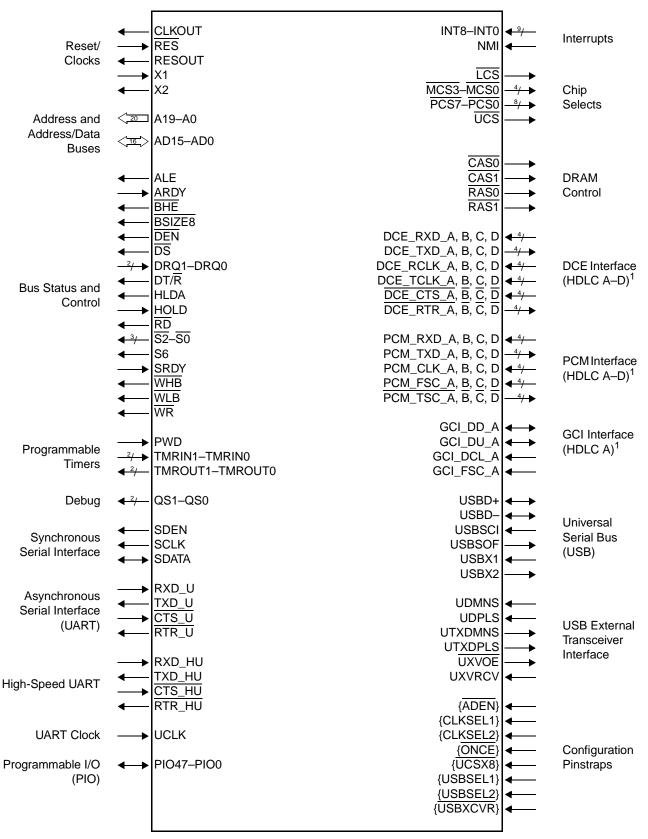

# LOGIC DIAGRAM BY INTERFACE<sup>1</sup>

#### Notes:

<sup>1.</sup> Because of multiplexing, not all interfaces are available at once. Refer to Table 28, "Multiplexed Signal Trade-offs," on page A-5.

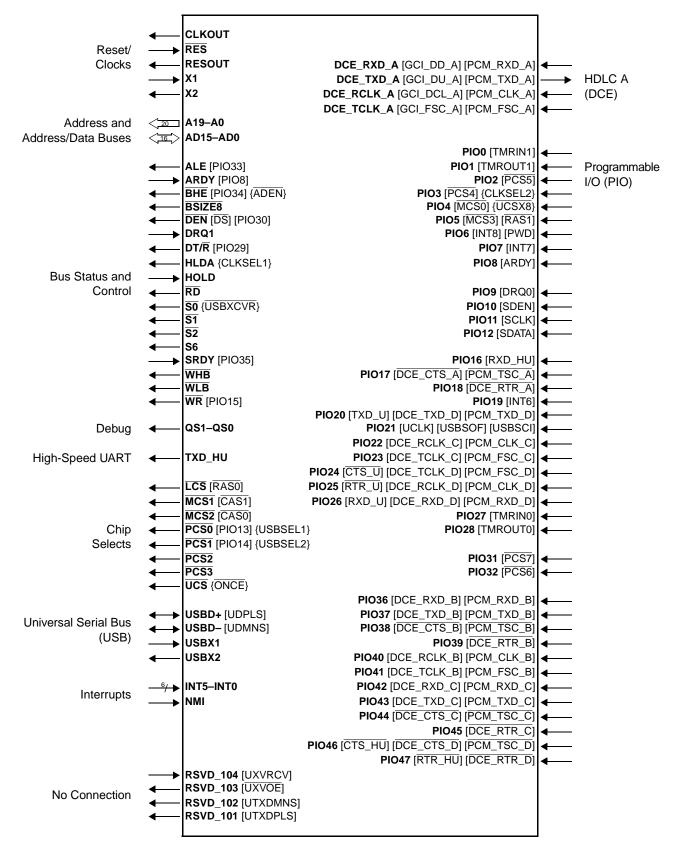

# LOGIC DIAGRAM BY DEFAULT PIN FUNCTION1

#### Notes:

1. Pin names in bold indicate the default pin function. Brackets, [], indicate alternate, multiplexed functions. Braces, {}, indicate pinstrap pins.

# PIN CONNECTION DIAGRAM—160-PIN PQFP PACKAGE

```

TXD_U/DCE_TXD_D/PCM_TXD_D

RXD_U/DCE_RXD_D/PCM_RXD_D

CTS_U/DCE_TCLK_D/PCM_FSC_D

RTR_U/DCE_RCLK_D/PCM_CLK_D

0,0

5 V<sub>SS</sub>

54 DCE_RXD_C/PCM_TXD_C

53 DCE_RXD_C/PCM_TSC_C

151 DCE_CTS_C/PCM_TSC_C

150 DCE_RTR_C

150 DCE_RTR_C

150 DCE_RCLK_C/PCM_CLK

149 DCE_TCLK_C/PCM_FSC

CLK_B

C/PCM_CLK_C

V<sub>CC</sub>

DRQ0

DCE_CTS_A/PCM_TSC_A

DCE_RTR_A

B DCE_RXD_B/PCM_RXD_E

DCE_CTS_B/PCM_TSC_B

DCE_RTR_B

DCE_RCIK_B/PCM_CLK

DCE_TCLKB/PCM_FSC_B

B/PCM_TXD

VCC

UCS (ONCE)

LCS/RAS0

\frac{\overline{V}_{SS}}{MCS3/RAS1}

\frac{MCS2/CAS0}{MCS1/CAS1}

Vss

DCE_TXD_E

V<sub>CC</sub>

INT8/PWD

INT7

INTE

TMRIN1

TMROUT1

TMRIN0

TMROUT0

V_{SS}

V_{CC}

SDEN

DCE_TXD_A/GCI_DU_A/PCM_TXD_A

SCLK

DCE_RXD_A/GCI_DD_A/PCM_RXD_A

118

3

SDATA

DCE_RCLK_A/GCI_DCL_A/PCM_CLK_A

117

PCS0 {USBSEL1}

DCE_TCLK_A/GCI_FSC_A/PCM_FSC_A

5

116

PCS1 {USBSEL2}

115

PCS2

7

RES 114

PCS3

INT5 113

8

PCS4 (CLKSEL2)

INT4 112

9

10 PCS5

INT3 111

INT2 110

11 PCS6

V<sub>CC</sub>

12

INT1 109

13 PCS7

V<sub>SS</sub> 108

14 ARDY

INTO 107

15

SRDY

V<sub>CC</sub> 106

16 WR

DRQ1

105

RSVD_104/UXVRCV 104

17 DT/R

18 DEN/DS

RSVD_103/UXVOE 103

19 ALE

RSVD 102/UTXDMNS 102

20 BHE {ADEN}

RSVD_101/UTXDPLS 101

21 V<sub>SS</sub>

V_{SS}

100

22 UCLK/USBSOF/USBSCI

HOLD

99

23 RTR_HU/DCE_RTR_D

HLDA {CLKSEL1}

98

24 CTS_HU/DCE_CTS_D/PCM_TSC_D

RD

97

RXD_HU

WLB

96

26 TXD_HU

WHB

95

27

V_{CC}

BSIZE8 94

28 AD0

AD15

93

29 AD8

AD7

92

V_{\text{CC}}

30

A0

31

Α1

A19 90

32

Α2

A18 89

33 V<sub>SS</sub>

A17

88

34

AD1

AD14

87

35

AD9

AD6

86

АЗ

36

A16

85

37

A4

A15

84

VSS

38 AD2

83

39 AD10

V_{SS}USB

82

USBD+/UDPLS

40 V<sub>CC</sub>

81

V<sub>CC</sub> A 7 V<sub>CC</sub> V<sub>CC</sub> V<sub>CC</sub> V<sub>CC</sub> USB V<sub>CC</sub> USB R V<sub>CC</sub> USB R V<sub>CC</sub> USB R V<sub>CC</sub> USB R V<sub>CC</sub> V<sub>CC</sub>

V<sub>CC</sub>

CLKOUT

USBX1

USBX2

```

## **PIN AND SIGNAL TABLES**

Table 1 on page 10 and Table 2 on page 11 show the pins sorted by pin number and signal name, respectively.

Table 4 on page 14 contains the signal descriptions (grouped alphabetically and by function). The table includes columns listing the multiplexed functions and I/O type. Table 3 on page 13 shows terms used in Table 4.

Refer to Appendix A, "Pin Tables," on page A-1 for an additional group of tables with the following information:

- Power-on reset (POR) pin defaults including pin numbers and multiplexed functions—Table 27 on page A-2.

- Multiplexed signal trade-offs—Table 28 on page A-5.

- Programmable I/O (PIO) pins ordered by PIO pin number and multiplexed signal name, respectively, including columns listing multiplexed functions and pin configurations following system reset—Table 29 on page A-8 and Table 30 on page A-9.

- Pinstraps and pinstrap options—Table 31 or page A-10.

- Pin and signal summary showing signal name and alternate function, pin number, I/O type, load values, POR default function, reset state, POR default operation, hold state, and voltage—Table 35 on page A-12.

In all tables the brackets, [], indicate alternate, multiplexed functions, and braces, {}, indicate reset configuration pins (pinstraps). The line over a pin name indicates an active Low. The word pin refers to the physical wire; the word signal refers to the electrical signal that flows through it.

Table 1. PQFP Pin Assignments—Sorted by Pin Number<sup>1</sup>

| Pin No. | Name—Left Side                 |    | Name—Bottom Side   |     | Name—Right Side           | Pin No. | Name—Top Side            |

|---------|--------------------------------|----|--------------------|-----|---------------------------|---------|--------------------------|

| 1       | V <sub>SS</sub>                | 41 | V <sub>SS</sub>    | 81  | USBD+/UDPLS               | 121     | V <sub>SS</sub>          |

| 2       | VSS<br>SDEN                    | 42 | A5                 | 82  | V <sub>SS</sub> _USB      | 122     | <u>vss</u><br>DCE_RTR_A  |

| 3       | SCLK                           | 43 | A6                 | 83  | V <sub>SS</sub> _USB      | 123     | DCE_CTS_A/               |

| 3       |                                | 43 |                    | 03  |                           |         | PCM_TSC_A                |

| 4       | SDATA                          | 44 | A7                 | 84  | A15                       | 124     | DRQ0                     |

| 5       | PCS0 {USBSEL1}                 | 45 | A8                 | 85  | A16                       | 125     | V <sub>CC</sub>          |

| 6       | PCS1 {USBSEL2}                 | 46 | AD3                | 86  | AD6                       | 126     | MCS0 {UCSX8}             |

| 7       | PCS2                           | 47 | AD11               | 87  | AD14                      | 127     | MCS1/CAS1                |

| 8       | PCS3                           | 48 | V <sub>CC</sub>    | 88  | A17                       | 128     | MCS2/CAS0                |

| 9       | PCS4 {CLKSEL2}                 | 49 | A9                 | 89  | A18                       | 129     | MCS3/RAS1                |

| 10      | PCS5                           | 50 | A10                | 90  | A19                       | 130     | V <sub>SS</sub>          |

| 11      | PCS6                           | 51 | AD4                | 91  | V <sub>CC</sub>           | 131     | LCS/RAS0                 |

| 12      | V <sub>CC</sub>                | 52 | AD12               | 92  | AD7                       | 132     | UCS (ONCE)               |

| 13      | PCS7                           | 53 | V <sub>SS</sub>    | 93  | AD15                      | 133     | V <sub>CC</sub>          |

| 14      | ARDY                           | 54 | S6                 | 94  | BSIZE8                    | 134     | DCE_TCLK_B/<br>PCM_FSC_B |

| 15      | SRDY                           | 55 | <u>S2</u>          | 95  | WHB                       | 135     | DCE_RCLK_B/<br>PCM_CLK_B |

| 16      | WR                             | 56 | S1                 | 96  | WLB                       | 136     | DCE_RTR_B                |

| 17      | DT/R                           | 57 | S0 (USBXCVR)       | 97  | RD                        | 137     | DCE_CTS_B/<br>PCM_TSC_B  |

| 18      | DEN/DS                         | 58 | RESOUT             | 98  | HLDA {CLKSEL1}            | 138     | DCE_RXD_B/<br>PCM_RXD_B  |

| 19      | ALE                            | 59 | V <sub>CC</sub>    | 99  | HOLD                      | 139     | DCE_TXD_B/<br>PCM_TXD_B  |

| 20      | BHE {ADEN}                     | 60 | CLKOUT             | 100 | V <sub>SS</sub>           | 140     | V <sub>SS</sub>          |

| 21      | V <sub>SS</sub>                | 61 | V <sub>SS</sub>    | 101 | RSVD_101/UTXDPLS          | 141     | TMROUT0                  |

| 22      | UCLK/USBSOF/USBSCI             | 62 | QS0                | 102 | RSVD_102/UTXDMNS          | 142     | TMRIN0                   |

| 23      | RTR_HU/DCE_RTR_D               | 63 | QS1                | 103 | RSVD_103/UXVOE            | 143     | TMROUT1                  |

| 24      | CTS_HU/DCE_CTS_D/<br>PCM_TSC_D | 64 | A11                | 104 | RSVD_104/UXVRCV           | 144     | TMRIN1                   |

| 25      | RXD_HU                         | 65 | A12                | 105 | DRQ1                      | 145     | INT6                     |

| 26      | TXD_HU                         | 66 | AD5                | 106 | V <sub>CC</sub>           | 146     | INT7                     |

| 27      | V <sub>CC</sub>                | 67 | AD13               | 107 | INT0                      | 147     | INT8/PWD                 |

| 28      | AD0                            | 68 | V <sub>CC</sub>    | 108 | V <sub>SS</sub>           | 148     | V <sub>CC</sub>          |

| 29      | AD8                            | 69 | A13                | 109 | INT1                      | 149     | DCE_TCLK_C/<br>PCM_FSC_C |

| 30      | A0                             | 70 | A14                | 110 | INT2                      | 150     | DCE_RCLK_C/<br>PCM_CLK_C |

| 31      | A1                             | 71 | V <sub>SS</sub>    | 111 | INT3                      | 151     | DCE_RTR_C                |

| 32      | A2                             | 72 | V <sub>SS</sub> _A | 112 | INT4                      | 152     | DCE_CTS_C/               |

|         |                                |    |                    |     |                           | . 3_    | PCM_TSC_C                |

| 33      | $V_{SS}$                       | 73 | X1                 | 113 | INT5                      | 153     | DCE_RXD_C/<br>PCM_RXD_C  |

| 34      | AD1                            | 74 | X2                 | 114 | RES                       | 154     | DCE_TXD_C/<br>PCM_TXD_C  |

| 35      | AD9                            | 75 | USBX1              | 115 | NMI                       | 155     | V <sub>SS</sub>          |

| 36      | A3                             | 76 | USBX2              | 116 | DCE_TCLK_A/<br>GCI_FSC_A/ | 156     | RTR_U/<br>DCE_RCLK_D/    |

| 37      | A4                             | 77 | V <sub>CC</sub> _A | 117 | PCM_FSC_A<br>DCE_RCLK_A / | 157     | PCM_CLK_D<br>CTS_U/      |

|         |                                |    | <br>-              |     | GCI_DCL_A/<br>PCM_CLK_A   |         | DCE_TCLK_D/<br>PCM_FSC_D |

Table 1. PQFP Pin Assignments—Sorted by Pin Number (Continued)

| Pin No. | Name—Left Side  | Pin No. | Name—Bottom Side     | Pin No. | Name—Right Side                  | Pin No. | Name—Top Side                 |

|---------|-----------------|---------|----------------------|---------|----------------------------------|---------|-------------------------------|

| 38      | AD2             | 78      | V <sub>CC</sub>      | 118     | DCE_RXD_A/GCI_DD_A/<br>PCM_RXD_A | 158     | RXD_U/DCE_RXD_D/<br>PCM_RXD_D |

| 39      | AD10            | 79      | V <sub>CC</sub> _USB | 119     | DCE_TXD_A/GCI_DU_A/<br>PCM_TXD_A | 159     | TXD_U/DCE_TXD_D/<br>PCM_TXD_D |

| 40      | V <sub>CC</sub> | 80      | USBD-/UDMNS          | 120     | V <sub>CC</sub>                  | 160     | V <sub>CC</sub>               |

#### Notes:

1. See Table 29, "PIOs Sorted by PIO Number," on page A-8 for PIOs sorted by PIO number.

Table 2. PQFP Pin Assignments—Sorted by Signal Name<sup>1</sup>

| Signal Name | Pin No. |                                    | Pin No. | Signal Name                    | Pin No. |                      | Pin No. |

|-------------|---------|------------------------------------|---------|--------------------------------|---------|----------------------|---------|

| A0          | 30      | CLKOUT                             | 60      | MCS3/RAS1                      | 129     | USBD-/UDMNS          | 80      |

| A1          | 31      | CTS_HU/DCE_CTS_D/ PCM_TSC_D        | 24      | NMI                            | 115     | USBX1                | 75      |

| A2          | 32      | CTS_U/DCE_TCLK_D/ PCM_FSC_D        | 157     | PCS0 {USBSEL1}                 | 5       | USBX2                | 76      |

| A3          | 36      | DCE_CTS_A/PCM_TSC_A                | 123     | PCS1 {USBSEL2}                 | 6       | V <sub>CC</sub>      | 12      |

| A4          | 37      | DCE_CTS_B/<br>PCM_TSC_B            | 137     | PCS2                           | 7       | V <sub>CC</sub>      | 27      |

| A5          | 42      | DCE_CTS_C/PCM_TSC_C                | 152     | PCS3                           | 8       | V <sub>CC</sub>      | 40      |

| A6          | 43      | DCE_RCLK_A/<br>GCI_DCL_A/PCM_CLK_A | 117     | PCS4 {CLKSEL2}                 | 9       | V <sub>CC</sub>      | 48      |

| A7          | 44      | DCE_RCLK_B/<br>PCM_CLK_B           | 135     | PCS5                           | 10      | V <sub>CC</sub>      | 59      |

| A8          | 45      | DCE_RCLK_C/PCM_CLK_C               | 150     | PCS6                           | 11      | V <sub>CC</sub>      | 68      |

| A9          | 49      | DCE_RTR_A                          | 122     | PCS7                           | 13      | $V_{CC}$             | 78      |

| A10         | 50      | DCE_RTR_B                          | 136     | QS0                            | 62      | $V_{CC}$             | 91      |

| A11         | 64      | DCE_RTR_C                          | 151     | QS1                            | 63      | $V_{CC}$             | 106     |

| A12         | 65      | DCE_RXD_A/GCI_DD_A/<br>PCM_RXD_A   | 118     | RD                             | 97      | V <sub>CC</sub>      | 120     |

| A13         | 69      | DCE_RXD_B/<br>PCM_RXD_B            | 138     | RES                            | 114     | V <sub>CC</sub>      | 125     |

| A14         | 70      | DCE_RXD_C/<br>PCM_RXD_C            | 153     | RESOUT                         | 58      | V <sub>CC</sub>      | 133     |

| A15         | 84      | DCE_TCLK_A/<br>GCI_FSC_A/PCM_FSC_A | 116     | RSVD_104/UXVRCV                | 104     | V <sub>CC</sub>      | 148     |

| A16         | 85      | DCE_TCLK_B/<br>PCM_FSC_B           | 134     | RSVD_103/UXVOE                 | 103     | V <sub>CC</sub>      | 160     |

| A17         | 88      | DCE_TCLK_C/<br>PCM_FSC_C           | 149     | RSVD_102/UTXDMNS               | 102     | V <sub>CC</sub> _A   | 77      |

| A18         | 89      | DCE_TXD_A/GCI_DU_A/<br>PCM_TXD_A   | 119     | RSVD_101/UTXDPLS               | 101     | V <sub>CC</sub> _USB | 79      |

| A19         | 90      | DCE_TXD_B/<br>PCM_TXD_B            | 139     | RTR_HU/DCE_RTR_D               | 23      | V <sub>SS</sub>      | 1       |

| AD0         | 28      | DCE_TXD_C/<br>PCM_TXD_C            | 154     | RTR_U/DCE_RCLK_D/<br>PCM_CLK_D | 156     | V <sub>SS</sub>      | 21      |

| AD1         | 34      | DEN/DS                             | 18      | RXD_HU                         | 25      | V <sub>SS</sub>      | 33      |

| AD2         | 38      | DRQ0                               | 124     | RXD_U/DCE_RXD_D/<br>PCM_RXD_D  | 158     | V <sub>SS</sub>      | 41      |

| AD3         | 46      | DRQ1                               | 105     | S0 {USBXCVR}                   | 57      | V <sub>SS</sub>      | 53      |

| AD4         | 51      | DT/R                               | 17      | S1                             | 56      | V <sub>SS</sub>      | 61      |

| AD5         | 66      | HLDA {CLKSEL1}                     | 98      | S2                             | 55      | V <sub>SS</sub>      | 71      |

| AD6         | 86      | HOLD                               | 99      | S6                             | 54      | V <sub>SS</sub>      | 83      |

| AD7         | 92      | INT0                               | 107     | SCLK                           | 3       | V <sub>SS</sub>      | 100     |

| AD8         | 29      | INT1                               | 109     | SDATA                          | 4       | V <sub>SS</sub>      | 108     |

| AD9         | 35      | INT2                               | 110     | SDEN                           | 2       | V <sub>SS</sub>      | 121     |

| AD10        | 39      | INT3                               | 111     | SRDY                           | 15      | V <sub>SS</sub>      | 130     |

Table 2. PQFP Pin Assignments—Sorted by Signal Name<sup>1</sup> (Continued)

| Signal Name | Pin No. | Signal Name  | Pin No. | Signal Name                   | Pin No. | Signal Name          | Pin No. |

|-------------|---------|--------------|---------|-------------------------------|---------|----------------------|---------|

| AD11        | 47      | INT4         | 112     | TMRIN0                        | 142     | V <sub>SS</sub>      | 140     |

| AD12        | 52      | INT5         | 113     | TMRIN1                        | 144     | V <sub>SS</sub>      | 155     |

| AD13        | 67      | INT6         | 145     | TMROUT0                       | 141     | V <sub>SS</sub> _A   | 72      |

| AD14        | 87      | INT7         | 146     | TMROUT1                       | 143     | V <sub>SS</sub> _USB | 82      |

| AD15        | 93      | INT8/PWD     | 147     | TXD_HU                        | 26      | WHB                  | 95      |

| ALE         | 19      | LCS/RAS0     | 131     | TXD_U/DCE_TXD_D/<br>PCM_TXD_D | 159     | WLB                  | 96      |

| ARDY        | 14      | MCS0 (UCSX8) | 126     | UCLK/USBSOF/USBSCI            | 22      | WR                   | 16      |

| BHE {ADEN}  | 20      | MCS1/CAS1    | 127     | UCS (ONCE)                    | 132     | X1                   | 73      |

| BSIZE8      | 94      | MCS2/CAS0    | 128     | USBD+/UDPLS                   | 81      | X2                   | 74      |

#### Notes:

<sup>1.</sup> For PIOs sorted by signal name, refer to Table 30, "PIOs Sorted by Signal Name," on page A-9.

# **Signal Descriptions**

Table 4 on page 14 contains a description of the Am186CC controller signals. Table 3 describes the terms used in Table 4. The signals are organized alphabetically within the following functional groups:

- Bus interface/general-purpose DMA request (page 14)

- Clocks/reset/watchdog timer (page 17)

- No connects (page 18)

- Power and ground (page 19)

- Debug support (page 19)

- Chip selects (page 19)

- DRAM (page 20)

- Interrupts (page 21)

- Programmable I/O (PIOs) (page 22)

- Programmable timers (page 22)

- Asynchronous serial ports (UART and High-Speed UART) (page 22)

- Synchronous serial interface (SSI) (page 23)

- HDLC synchronous communications: channels A–D for Data Communications Equipment (DCE), Pulse-Code Modulation (PCM), and General Circuit Interface (GCI) interfaces (page 23)

- Universal serial bus (USB) (page 26)

For pinstraps, refer to Table 31, "Reset Configuration Pins (Pinstraps)," on page A-10.

**Table 3. Signal Description Table Definitions**

| Term        | Definition                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General t   | erms                                                                                                                                                                                                                                                                                                                                                                             |

| []          | Pin alternate function; a pin defaults to the signal named without the brackets                                                                                                                                                                                                                                                                                                  |

| {}          | Reset configuration pin (pinstrap)                                                                                                                                                                                                                                                                                                                                               |

| pin         | Refers to the physical wire                                                                                                                                                                                                                                                                                                                                                      |

| reset       | An external or power-on reset is caused by asserting RES. An internal reset is initiated by the watchdog timer. A system reset is one that resets the Am186CC controller (the CPU plus the internal peripherals) as well as any external peripherals connected to RESOUT. An external reset always causes a system reset; an internal reset can optionally cause a system reset. |

| signal      | Refers to the electrical signal that flows across a pin                                                                                                                                                                                                                                                                                                                          |

| SIGNAL      | A line over a signal name indicates that the signal is active Low; a signal name without a line is active High.                                                                                                                                                                                                                                                                  |

| Signal type | oes                                                                                                                                                                                                                                                                                                                                                                              |

| В           | Bidirectional                                                                                                                                                                                                                                                                                                                                                                    |

| Н           | High                                                                                                                                                                                                                                                                                                                                                                             |

| LS          | Programmable to hold last state of pin                                                                                                                                                                                                                                                                                                                                           |

| 0           | Totem pole output                                                                                                                                                                                                                                                                                                                                                                |

| OD          | Open drain output                                                                                                                                                                                                                                                                                                                                                                |

| OD-O        | Open drain output or totem pole output                                                                                                                                                                                                                                                                                                                                           |

| PD          | Internal pulldown resistor                                                                                                                                                                                                                                                                                                                                                       |

| PU          | Internal pullup resistor                                                                                                                                                                                                                                                                                                                                                         |

| STI         | Schmitt trigger Input                                                                                                                                                                                                                                                                                                                                                            |

| STI-OD      | Schmitt trigger input or open drain output                                                                                                                                                                                                                                                                                                                                       |

| TS          | Three-state output                                                                                                                                                                                                                                                                                                                                                               |

Table 4. Signal Descriptions

| Signal Name | Multiplexed Signal(s) | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-----------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUS INTERFA | ACE/GENERAL-PUR       | POSE DI | MA REQUEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A19–A0      |                       | 0       | Address Bus supplies nonmultiplexed memory or I/O addresses to the system one half of a CLKOUT period earlier than the multiplexed address and data bus (AD15–AD0). During bus-hold or reset conditions, the address bus is three-stated with pulldowns.  When the lower or upper chip-select regions are configured for DRAM mode, the A19–A0 bus provides the row and column addresses at the appropriate times. The upper and lower memory chip-select ranges can be individually configured for DRAM mode.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AD15–AD0    |                       | В       | Address and Data Bus time-multiplexed pins supply memory or I/O addresses and data to the system. This bus can supply an address to the system during the first period of a bus cycle (t <sub>1</sub> ). It transmits (write cycle) or receives (read cycle) data to or from the system during the remaining periods of that cycle (t <sub>2</sub> , t <sub>3</sub> , and t <sub>4</sub> ). The address phase of these pins can be disabled—see the {ADEN} pin description in Table 31, "Reset Configuration Pins (Pinstraps)," on page A-10.  During a reset condition, the address and data bus is three-stated with pulldowns, and during a bus hold it is three-stated.  In addition, during a reset the state of the address and data bus pins (AD15–AD0) is latched into the Reset Configuration (RESCON) register. This feature can be used to provide software with information about the external system at reset time. |

| ALE         | [PIO33]               | 0       | Address Latch Enable indicates to the system that an address appears on the address and data bus (AD15–AD0). The address is guaranteed valid on the falling edge of ALE.  ALE is three-stated and has a pulldown resistor during bus-hold or reset conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ARDY        | [PIO8]                | STI     | Asynchronous Ready is a true asynchronous ready that indicates to the Am186CC controller that the addressed memory space or I/O device will complete a data transfer. The ARDY pin is asynchronous to CLKOUT and is active High. To guarantee the number of wait states inserted, ARDY or SRDY must be synchronized to CLKOUT. If the falling edge of ARDY is not synchronized to CLKOUT as specified, an additional clock period can be added.  To always assert the ready condition to the microcontroller, tie ARDY and SRDY High. If the system does not use ARDY, tie the pin Low to yield control to SRDY.                                                                                                                                                                                                                                                                                                                 |

| Signal Name    | Multiplexed              | Type       | 4. Signal Description                                                                                                                                                                                                                                                |                                                                                                                                      | ,                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|----------------|--------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BHE            | Signal(s) [PIO34] {ADEN} | 0          | Bus High Enable: During a memory access, BHE and the least-significant address bit (AD0) indicate to the system which bytes of the data bus (upper, lower, or both) participate in a bus cycle. The BHE and AD0 pins are encoded as follows:  Data Byte Encoding     |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                |                          |            | BHE AD0 Type of Bus Cycle                                                                                                                                                                                                                                            |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                |                          |            | 0                                                                                                                                                                                                                                                                    | 0                                                                                                                                    | Word transfer                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                |                          |            | 0                                                                                                                                                                                                                                                                    | 1                                                                                                                                    | High byte transfer (bits 15–8)                                                                                                                                                                                                                                                                                                                                      |  |  |

|                |                          |            | 1                                                                                                                                                                                                                                                                    | 0                                                                                                                                    | Low byte transfer (bits 75–0)                                                                                                                                                                                                                                                                                                                                       |  |  |

|                |                          |            | 1                                                                                                                                                                                                                                                                    | 1                                                                                                                                    | Refresh                                                                                                                                                                                                                                                                                                                                                             |  |  |

| BSIZE8         | _                        | 0          | write enables, and bus interface.  BHE also signals D data (AD) bus. A re During refresh cycle during the t <sub>2</sub> , t <sub>3</sub> , and a refresh cycle. For signal to determine  Bus Size 8 is asset                                                        | RAM refresh of the stresh cycle is es, the AD bust the stresh cycle. The this reason, the refresh cycle the during the stresh cycle. | actionality of BHE and AD0 for high and low byte ng appropriate for use with the nonmultiplexed cycles when using the multiplexed address and indicated when both BHE and AD0 are High. In a six driven during the t <sub>1</sub> phase and three-stated the value driven on the A bus is undefined during the AO signal cannot be used in place of the AD0 states. |  |  |

| DEN            | [DS]<br>[PIO30]          | 0          | indicate a 16-bit cycle.  Data Enable supplies an output enable to an external data-bus transceiver. DEN is asserted during memory and I/O cycles. DEN is deasserted when DT/R changes state. DEN is three-stated with a pullup during bus-hold or reset conditions. |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| [DS]           | DEN<br>PIO30             | 0          | Data Strobe provided cycle timing. When 68K-type peripherary When [DS] is assetted data is valid. When                                                                                                                                                               | used with other lls without the red, addresse [DS] is assert his pin is confi                                                        | ere the write cycle timing is identical to the reader control signals, [DS] provides an interface for need for additional system interface logic.  es are valid. When [DS] is asserted on writes, ed on reads, data can be driven on the AD bus. igured as DEN. The pin is then configured by                                                                       |  |  |

| DT/R           | [PIO29]                  | 0          | external data-bus to controller transmits                                                                                                                                                                                                                            | ransceiver. Wh<br>_data. When t                                                                                                      | tes which direction data should flow through an<br>hen DT/R is asserted High, the Am186CC<br>his pin is deasserted Low, the controller<br>ed with a pullup during a bus-hold or reset                                                                                                                                                                               |  |  |

| DRQ1<br>[DRQ0] | PIO9                     | STI<br>STI | device is ready for                                                                                                                                                                                                                                                  | a DMA chann<br>internally syn                                                                                                        | to the Am186CC controller that an external el to perform a transfer. DRQ1–[DRQ0] are chronized. DRQ1–[DRQ0] are not latched and .                                                                                                                                                                                                                                   |  |  |

| Signal Name | Multiplexed Signal(s) | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HLDA        | {CLKSEL1}             | 0    | Bus-Hold Acknowledge is asserted to indicate to an external bus master that the Am186CC controller has relinquished control of the local bus. When an external bus master requests control of the local bus (by asserting HOLD), the microcontroller completes the bus cycle in progress, then relinquishes control of the bus to the external bus master by asserting HLDA and three-stating \$\overline{S2}\$-\$\overline{S0}\$, AD15-AD0, \$6, and \$A19-A0\$. The following are also three-stated and have pullups: UCS, LCS, MCS3-MCS0, PCS7-PCS0, DEN, RD, WR, BHE, WHB, WLB, and DT/R. ALE is three-stated and has a pulldown.                                                                                                                                                                               |

|             |                       |      | When the external bus master has finished using the local bus, it indicates this to the Am186CC controller by deasserting HOLD. The controller responds by deasserting HLDA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                       |      | If the Am186CC controller requires access to the bus (for example, for refresh), the controller deasserts HLDA before the external bus master deasserts HOLD. The external bus master must be able to deassert HOLD and allow the controller access to the bus. See the timing diagrams for bus hold on page 70.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HOLD        | _                     | STI  | <b>Bus-Hold Request</b> indicates to the Am186CC controller that an external bus master needs control of the local bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |                       |      | The Am186CC controller's HOLD latency time—the time between HOLD request and HOLD acknowledge—is a function of the activity occurring in the processor when the HOLD request is received. A HOLD request is second only to DRAM refresh requests in priority of activity requests received by the processor. This implies that if a HOLD request is received just as a DMA transfer begins, the HOLD latency can be as great as four bus cycles. This occurs if a DMA word transfer operation is taking place from an odd address to an odd address. This is a total of 16 clock cycles or more if wait states are required. In addition, if locked transfers are performed, the HOLD latency time is increased by the length of the locked transfer. HOLD latency is also potentially increased by DRAM refreshes. |

|             |                       |      | The board designer is responsible for properly terminating the HOLD input.  For more information, see the HLDA pin description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RD          | _                     | 0    | Read Strobe indicates to the system that the Am186CC controller is performing a memory or I/O read cycle. RD is guaranteed to not be asserted before the address and data bus is three-stated during the address-to-data transition. RD is three-stated with a pullup during bus-hold or reset conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| S6          | _                     | 0    | <b>Bus Cycle Status Bit 6:</b> This signal is asserted during $t_1$ – $t_4$ to indicate a DMA-initiated bus cycle or a refresh cycle. S6 is three-stated during bus hold and three-stated with a pulldown during reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SRDY        | [PIO35]               | STI  | <b>Synchronous Ready</b> indicates to the Am186CC controller that the addressed memory space or I/O device will complete a data transfer. The SRDY pin accepts an active High input synchronized to CLKOUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                       |      | Using SRDY instead of ARDY allows a relaxed system timing because of the elimination of the one-half clock period required to internally synchronize ARDY. To always assert the ready condition to the microcontroller, tie SRDY High. If the system does not use SRDY, tie the pin Low to yield control to ARDY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                              | Table 4. Signal Descriptions (Continued) |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |