# **Electronic Telephone Line Switch**

#### **Features**

- 350V breakdown voltage

- ► 18Ω maximum switch resistance

- Current limiting protection

- Operates at 2.3V input

### **Applications**

- Telephone handsets

- Modems

- Fax machines

- Answering machines

- Remote meter reading

- Telephone interface products

### **General Description**

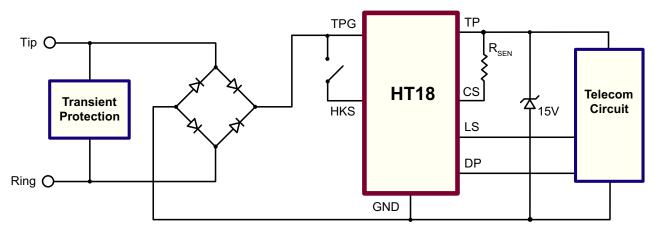

The Supertex HT18LG is an electronic line switch circuit that replaces the mechanical hook switch contact or a discrete hook switch in a telephone handset or modem. It switches the positive side of the telephone line using control inputs that are referenced to the negative side of the line. In its off state, it can withstand 350V on the positive input. In its on state, it has a maximum series resistance of  $18\Omega$ .

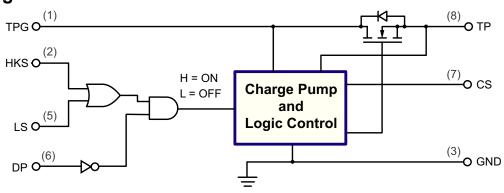

The device provides current limiting determined by an external resistor. There are three control inputs. The HKS pin turns on the hook switch when connected to the TPG pin. This can be accomplished by using a mechanical switch which closes when the handset is physically off-hook. The LS pin allows a logic signal to turn on the hook switch. The dial pulse, Pin 6, is used to turn the hook switch off for pulse dialing. The dial pulse (DP) is active high.

# **Typical Application Circuit**

### **Ordering Information**

| <u></u> |                                                                                      |  |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|         | Package Option                                                                       |  |  |  |  |  |  |  |

| Device  | 8-Lead SOIC (Narrow Body)<br>4.90x3.90mm body<br>1.75mm height (max)<br>1.27mm pitch |  |  |  |  |  |  |  |

| HT18    | HT18LG-G                                                                             |  |  |  |  |  |  |  |

<sup>-</sup>G indicates package is RoHS compliant ('Green')

## **Absolute Maximum Ratings**

| Parameter                             | Value           |

|---------------------------------------|-----------------|

| V <sub>TPG</sub> , Input line voltage | +350V           |

| V <sub>TP</sub> , Output line voltage | +18V            |

| DP continuous input voltage           | +10V            |

| Storage temperature                   | -65°C to +150°C |

| Junction temperature                  | +150°C          |

| Soldering temperature*                | +300°C          |

| Power dissipation                     | 0.8W            |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

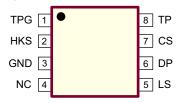

# **Pin Configuration**

8-Lead SOIC (Narrow Body) (LG) (top view)

### **Product Marking**

Y = Last Digit of Year Sealed WW = Week Sealed L = Lot Number \_\_\_\_\_ = "Green" Packaging

Package may or may not include the following marks: Si or

8-Lead SOIC (Narrow Body) (LG)

#### Electrical Characteristics (T = 25°C unless otherwise specified)

| Electrica                          | Electrical Characteristics (T <sub>A</sub> = 25°C unless otherwise specified) |     |     |           |       |                                                      |  |  |  |  |  |  |

|------------------------------------|-------------------------------------------------------------------------------|-----|-----|-----------|-------|------------------------------------------------------|--|--|--|--|--|--|

| Sym                                | Parameter                                                                     | Min | Тур | Max       | Units | Conditions                                           |  |  |  |  |  |  |

| $V_{TPG}$                          | High voltage positive supply                                                  | -   | -   | 350       | V     | I <sub>TPG</sub> = 500μA, HKS, LS, DP = open circuit |  |  |  |  |  |  |

|                                    | Input lookage ourrent                                                         | -   | -   | 2.0       |       | V <sub>TPG</sub> = 100V, HKS, LS, DP = open circuit  |  |  |  |  |  |  |

| TPG                                | Input leakage current                                                         | -   | -   | 200       | μA    | V <sub>TPG</sub> = 290V, HKS, LS,DP = open circuit   |  |  |  |  |  |  |

|                                    |                                                                               | -   | -   | 18        |       | $V_{TPG}$ = 17V, $I_{TPG}$ = 180mA, SW = on          |  |  |  |  |  |  |

| R <sub>sw</sub>                    | TPG to TP switch resistance                                                   | -   | -   | 18        | Ω     | $V_{TPG} = 3.0V, I_{TPG} = 20mA, SW = on$            |  |  |  |  |  |  |

|                                    |                                                                               | -   | -   | 30        |       | $V_{TPG} = 2.3V$ , $I_{TPG} = 5.0$ mA, SW = on       |  |  |  |  |  |  |

|                                    | Bias current                                                                  | -   | -   | 75        |       | $V_{TPG} = 5.0V$ , SW = on                           |  |  |  |  |  |  |

| I <sub>TPG</sub> - I <sub>TP</sub> | Dias current                                                                  | -   | -   | 100       | μA    | V <sub>TPG</sub> = 10V, SW = on                      |  |  |  |  |  |  |

| L <sub>LIM</sub>                   | I <sub>TPG</sub> current limiting                                             | 188 | 250 | 330       | mA    | $R_{EXT} = 200\Omega \pm 1\%$                        |  |  |  |  |  |  |

| I <sub>HKS</sub>                   | HKS input current                                                             | -   | -   | 200       | μΑ    | V <sub>HKS</sub> = 40 to 70V                         |  |  |  |  |  |  |

| I <sub>LS</sub> , I <sub>DP</sub>  | LS and DP logic input current                                                 | -   | -   | 30        | μΑ    | $V_{LS} = 3.0V, V_{DP} = 3.0V$                       |  |  |  |  |  |  |

| V <sub>IL(HKS)</sub>               | HKS input low                                                                 | 0   | -   | 0.2       | V     | V <sub>TPG</sub> = 3.0 to 70V                        |  |  |  |  |  |  |

| V <sub>IH(HKS)</sub>               | HKS input high                                                                | 2.0 | -   | $V_{TPG}$ | V     | V <sub>TPG</sub> = 3.0 to 70V                        |  |  |  |  |  |  |

| $V_{IL(LS)}, V_{IL(DP)}$           | Input logic low for DP and LS                                                 | 0   | -   | 0.2       | V     | V <sub>TPG</sub> = 3.0 to 70V                        |  |  |  |  |  |  |

| $V_{IH(LS)}, V_{IH(DP)}$           | Input logic high for DP and LS                                                | 1.5 | -   | 10        | V     | V <sub>TPG</sub> = 3.0 to 70V                        |  |  |  |  |  |  |

| T <sub>on</sub>                    | Turn-on time                                                                  | -   | -   | 1.0       | ms    | V <sub>TPG</sub> = 4.5V                              |  |  |  |  |  |  |

| T <sub>OFF</sub>                   | Turn-off time                                                                 | -   | -   | 1.0       | ms    | $V_{TPG} = 4.5V$                                     |  |  |  |  |  |  |

<sup>\*</sup> Distance of 1.6mm from case for 10 seconds.

# **Logic Truth Table**

| HKS    | LS     | DP     | Switch State |

|--------|--------|--------|--------------|

| Н      | L or Z | L or Z | ON           |

| Н      | Н      | L or Z | ON           |

| L or Z | L or Z | L or Z | OFF          |

| L or Z | Н      | L or Z | ON           |

| X      | X      | Н      | OFF          |

Z = high impedance, open circuit

# **Block Diagram**

# **Pin Description**

|     | 2000. p. 101 |                                                                                                                                         |  |  |  |  |  |  |  |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin | Name         | Description                                                                                                                             |  |  |  |  |  |  |  |

| 1   | TPG          | Positive input side of a telephone line, typically tip side.                                                                            |  |  |  |  |  |  |  |

| 2   | HKS          | Hookswitch input. Connect HKS to TPG to turn on the hook switch. Internally pulled low with a high value resistor.                      |  |  |  |  |  |  |  |

| 3   | GND          | Device ground. Negative side of a telephone line, typically ring side.                                                                  |  |  |  |  |  |  |  |

| 4   | NC           | No connect. Open circuit. No internal connections to the device.                                                                        |  |  |  |  |  |  |  |

| 5   | LS           | Line switch input. Input logic high turns on the hook switch. Internally pulled low with a high value resistor.                         |  |  |  |  |  |  |  |

| 6   | DP           | Dial pulse input. Input logic high turns off the hook switch. Used for pulse dialing. Internally pulled low with a high value resistor. |  |  |  |  |  |  |  |

| 7   | CS           | Current sense input. An external resistor connected between CS and TP sets the current limit.                                           |  |  |  |  |  |  |  |

| 8   | TP           | Positive output side of a telephone line. Zener protection to prevent this output from rising above 18V is required.                    |  |  |  |  |  |  |  |

X = irrelevant

L = logic level low

H = logic level high

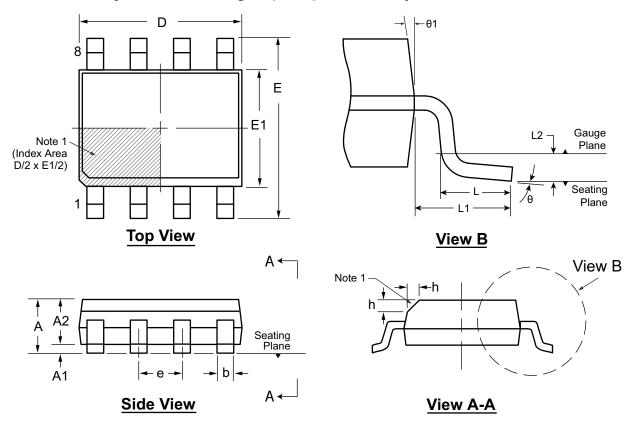

# 8-Lead SOIC (Narrow Body) Package Outline (LG)

4.90x3.90mm body, 1.75mm height (max), 1.27mm pitch

#### Note:

1. This chamfer feature is optional. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbol         |     | Α     | A1   | A2    | b    | D     | Е     | E1    | е           | h    | L         | L1          | L2          | θ          | θ1  |

|----------------|-----|-------|------|-------|------|-------|-------|-------|-------------|------|-----------|-------------|-------------|------------|-----|

| Dimension (mm) | MIN | 1.35* | 0.10 | 1.25  | 0.31 | 4.80* | 5.80* | 3.80* | 1.27<br>BSC | 0.25 | 0.40      | 1.04<br>REF | 0.25<br>BSC | <b>0</b> ° | 5°  |

|                | NOM | -     | -    | -     | -    | 4.90  | 6.00  | 3.90  |             | -    | -         |             |             | -          | -   |

|                | MAX | 1.75  | 0.25 | 1.65* | 0.51 | 5.00* | 6.20* | 4.00* |             | 0.50 | 0.50 1.27 |             |             | <b>8</b> º | 15° |

JEDEC Registration MS-012, Variation AA, Issue E, Sept. 2005.

Drawings are not to scale.

Supertex Doc. #: DSPD-8SOLGTG, Version 1041309.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the Supertex inc. website: http://www.supertex.com.

©2009 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switch ICs - Various category:

Click to view products by Microchip manufacturer:

Other Similar products are found below:

LC824206XA-VH FSA806UMX 80HCPS1432CHMHI MAX4936ACTO+ 80HSPS1616CHMGI NL3S325FCT2G BCM56024B0KPBG

CPC7583BA NC7SZ157P6X ACST12-7CG-TR FSA9280AUMX NL7SZ19DFT2G SRC0CS25D MAX14808ETK MAX4937CTN+

DG2788ADN-T1-GE4 DGQ2788AEN-T1-GE4 LTC6943IGN#PBF MCZ33999EKR2 LTC1471CS#PBF LTC1472CS#PBF

LTC1043CSW#PBF PI4MSD5V9548ALEX NCX8200UKZ LTC6943HGN#PBF PI3CH480QE HT1204 89H48T12G2ZCBLG

PI3C3245QE ADG409BRZ-REEL7 ADG5462FBRUZ-RL7 ADN4604ASVZ LTC1043CN LTC1043CN#PBF LTC1470ES8#PBF

PI4MSD5V9548AZDEX AP2280-2FMG-7 AZV5001RA4-7 PI3B3253QEX PI3CH480QEX 74HC4053N 74HC139N 74HC138N

XD74LS138 XD74LS139 XD74LS148 XD74LS147 XD4051 XD4052 XD4053