## Product Preview Low Voltage 2.5V and 3.3V CMOS PLL Clock Driver

The MPC9600 is a low voltage 2.5V and 3.3V compatible, 1:21 PLL based clock driver and fanout buffer. With output frequencies up to 200 MHz, output skews of 150 ps and part–to–part skews of 300 ps the device meets the needs of the most demanding clock tree applications.

#### Features:

- Multiplication of input frequency by 2, 3, 4 and 6

- Distribution of output frequency to 21 outputs organized in three output banks: QA0-QA6, QB0-QB6, QC0-QC6, each fully selectable

- Fully integrated PLL

- Selectable output frequency range is 50 to 100 MHz and 100 to 200 MHz

- Selectable input frequency range is 16 to 33 MHz and 25 to 50 MHz

- LVCMOS outputs

- Outputs disable to high impedance (except QFB)

- LVCMOS or LVPECL reference clock options

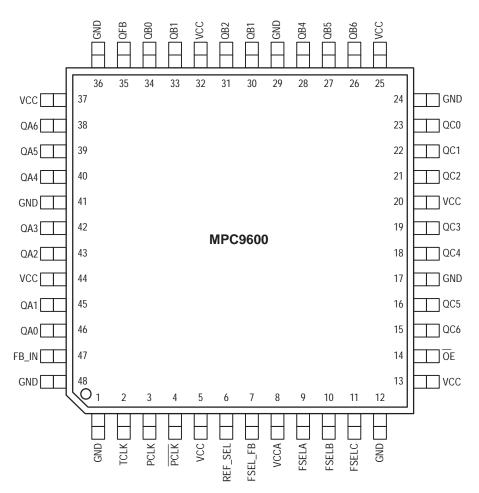

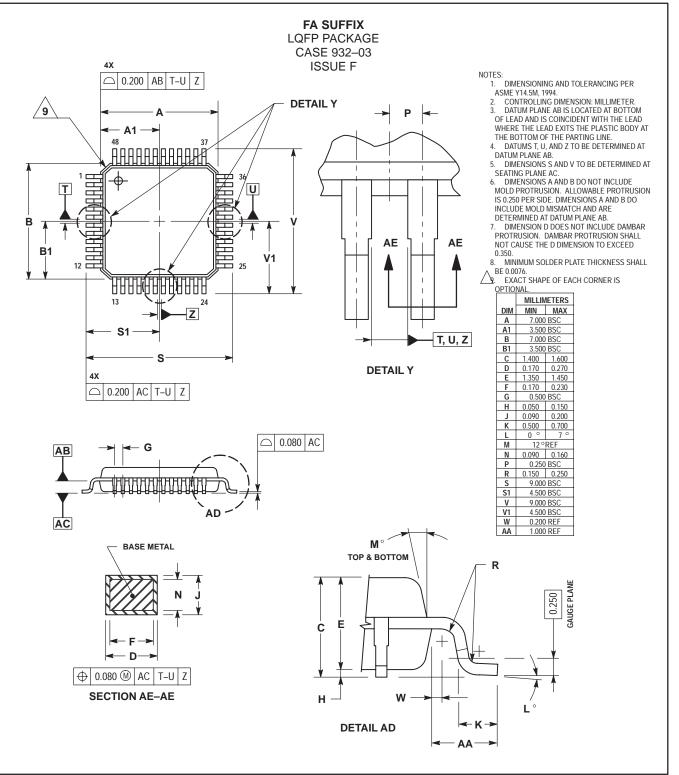

- 48 lead QFP packaging

- ±50 ps cycle-to-cycle jitter

- 150 ps maximum output-to-output skew

- 300 ps maximum device-to-device skew

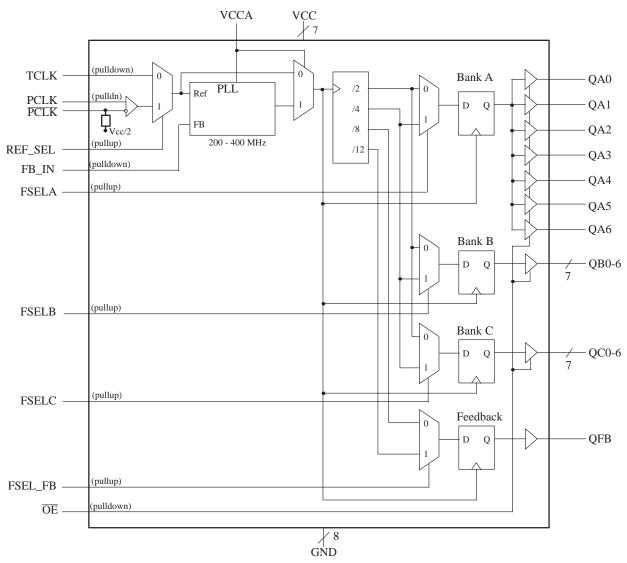

The MPC9600 is fully 2.5V and 3.3V compatible. The MPC9600 has the capability to generate clock signals of 50 to 200 MHz from clock sources of 16 to 50 MHz. The internal PLL is optimized for this frequency range and does not require external loop filter components. QFB provides an output for the external feedback path to the feedback input FB\_IN. The QFB divider ratio is configurable and determines the PLL frequency multiplication factor when QFB is directly connected to FB\_IN. The MPC9600 is optimized for minimizing the propagation delay between the clock input and FB\_IN.

Three output banks of 7 outputs each bank can be individually configured to divide the VCO frequency by 2 or by 4. Combining the feedback and output divider ratios, the MPC9600 is capable to multiply the input frequency by 2, 3, 4 and 6.

The reference clock is selectable either LVPECL or LVCMOS. The LVPECL reference clock feature allows the designer to use LVPECL fanout buffers for the inner branches of the clock distribution tree. All control inputs accept LVCMOS compatible levels. The outputs provide low impedance LVCMOS outputs capable of driving parallel terminated  $50\Omega$  transmission to V<sub>TT</sub>=V<sub>CC</sub>/2. For series terminated lines the MPC9600 can drive two lines per output giving the device and effective total fanout of 1:42. With guaranteed maximum output-to-output skew of 150 ps, the MPC9600 PLL clock driver meets the synchronization requirements of the most demanding systems.

The V<sub>CCA</sub> analog power pin doubles as a PLL bypass select line for test purpose. When the V<sub>CCA</sub> is driven to GND the reference clock will bypass the PLL and will drive the outputs (except QFB) into a high impedance state.

The device is packaged in a 48-lead LQFP package to provide optimum combination of board density and performance.

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

**MPC9600**

MOTOROLA

Figure 1. MPC9600 Logic Diagram

#### **PIN CONFIGURATION**

| Pin        | I/O    | Туре         | Description                                  |

|------------|--------|--------------|----------------------------------------------|

| PCLK, PCLK | Input  | PECL         | Differential reference clock frequency input |

| TCLK       | Input  | LVCMOS       | Reference clock input                        |

| FB_IN      | Input  | LVCMOS       | PLL feedback clock input                     |

| QAn        | Output | LVCMOS       | Bank A outputs                               |

| QBn        | Output | LVCMOS       | Bank B outputs                               |

| QCn        | Output | LVCMOS       | Bank C outputs                               |

| QFB        | Output | LVCMOS       | Differential feedback output                 |

| REF_SEL    | Input  | LVCMOS       | Reference clock input select                 |

| FSELA      | Input  | LVCMOS       | Selection of bank A output frequency         |

| FSELB      | Input  | LVCMOS       | Selection of bank B output frequency         |

| FSELC      | Input  | LVCMOS       | Selection of bank C output frequency         |

| FSEL_FB    | Input  | LVCMOS       | Selection of feedback frequency              |

| OE         | Input  | LVCMOS       | Output enable                                |

| VCCA       |        | Power supply | Analog power supply and PLL bypass           |

| VCC        |        | Power supply | Core power supply                            |

| GND        |        | Ground       | Ground                                       |

Figure 2. 48 Lead Package Pinout (Top View)

### FUNCTION TABLE (CONTROLS)

| Control Pin | 0                        | 1                             |

|-------------|--------------------------|-------------------------------|

| REF_SEL     | TCLK                     | PCLK                          |

| VCCA        | PLL Bypass               | PLL Power                     |

| OE          | Outputs Enabled          | Outputs Disabled (except QFB) |

| FSELA       | Output Bank A at VC0/2   | Output Bank A at VCO/4        |

| FSELB       | Output Bank B at VC0/2   | Output Bank B at VCO/4        |

| FSELC       | Output Bank C at VC0/2   | Output Bank C at VCO/4        |

| FSEL_FB     | Feedback Output at VCO/8 | Feedback Output at VCO/12     |

### ABSOLUTE MAXIMUM RATINGS\*

| Symbol            | Parameter                 | Min  | Мах                   | Unit |

|-------------------|---------------------------|------|-----------------------|------|

| VCC               | Supply Voltage            | -0.3 | 4.6                   | V    |

| VI                | Input Voltage             | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| IIN               | Input Current             |      | ±20                   | mA   |

| T <sub>Stor</sub> | Storage Temperature Range | -40  | 125                   | °C   |

\* Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute–maximum–rated conditions is not implied.

## **DC CHARACTERISTICS** (T<sub>A</sub> = 0° to 70°C, V<sub>CC</sub> = 3.3V $\pm$ 5%)

| Symbol            | Characteristics                                               | Min                  | Тур | Max                   | Unit | Condition                            |

|-------------------|---------------------------------------------------------------|----------------------|-----|-----------------------|------|--------------------------------------|

| VIH               | Input high voltage                                            | 2.0                  |     | V <sub>CC</sub> + 0.3 | V    | LVCMOS                               |

| VIL               | Input low voltage                                             | -0.3                 |     | 0.8                   | V    | LVCMOS                               |

| VPP               | Peak-t <u>o-peak</u> input voltage <sup>a</sup><br>PCLK, PCLK | 500                  |     | 1000                  | mV   | LVPECL                               |

| VCMR <sup>b</sup> | Comm <u>on Mo</u> de Range <sup>C</sup><br>PCLK, PCLK         | V <sub>CC</sub> -1.4 |     | V <sub>CC</sub> -0.6  | V    | LVPECL                               |

| VOH               | Output High Voltage                                           | 2.4                  |     |                       | V    | I <sub>OH</sub> =-24 mA <sup>d</sup> |

| V <sub>OL</sub>   | Output Low Voltage                                            |                      |     | 0.55                  | V    | I <sub>OL</sub> = 24mA               |

| I <sub>IN</sub>   | Input Current                                                 |                      |     | ±120                  | μA   |                                      |

| C <sub>IN</sub>   | Input capacitance                                             |                      | 4.0 |                       | pF   |                                      |

| C <sub>PD</sub>   | Power Dissipation Capacitance                                 |                      | 25  |                       | pF   | Per Output                           |

| ICCA              | Maximum PLL Supply Current                                    |                      | 15  | 20                    | mA   | V <sub>CCA</sub> Pin                 |

| ICC               | Maximum Quiescent Supply Current                              |                      |     |                       | mA   | All V <sub>CC</sub> Pins             |

a. Pending characterization

b.  $V_{CMR}$  is the difference from  $V_{CC}$  and the most positive side of the differential input signal. Normal operation is obtained when the "high" input is within the  $V_{CMR}$  range and the input swing lies within the  $V_{PP}$  specification.

c. Pending characterization

d. The MPC9600 is capable of driving  $50\Omega$  transmission lines on the incident edge. Each output drives one  $50\Omega$  parallel terminated

transmission line to a termination voltage of V<sub>TT</sub> = V<sub>CC</sub>/2. Alternatively, the device drives up to two 50Ω series terminated transmission lines.

| Symbol                          | Characteristics                                    | Min       | Тур | Мах        | Unit       | Condition    |

|---------------------------------|----------------------------------------------------|-----------|-----|------------|------------|--------------|

| fref                            | Input Frequency<br>FSEL_FB=1<br>FSEL_FB=0          | 16<br>25  |     | 33<br>50   | MHz<br>MHz |              |

| fMAX                            | Maximum Output Frequency<br>FSEL_FB=1<br>FSEL_FB=0 | 100<br>50 |     | 200<br>100 | MHz        |              |

| frefDC                          | Reference Input Duty Cycle                         | 25        |     | 75         | %          |              |

| <sup>t</sup> PD                 | Propagation Delay<br>Input to QFB<br>(PLL locked)  | X -100    | Х   | X+100      | ps         |              |

| <sup>t</sup> sk(o)              | Output-to-output Skew                              |           |     | 150        | ps         |              |

| <sup>t</sup> sk(pp)             | Part-to-part Skew                                  |           |     | 300        | ps         |              |

| tPW                             | Output Duty Cycle                                  | 45        | 50  | 55         | %          |              |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                              | 0.1       |     | 1.0        | ns         | 0.55 to 2.0V |

| <sup>t</sup> PLZ, HZ            | Output Disable Time                                |           |     |            | ns         |              |

| <sup>t</sup> PZL                | Output Enable Time                                 |           |     |            | ns         |              |

| <sup>t</sup> JIT(CC)            | Cycle-to-cycle Jitter (Peak-to-Peak)               |           | ±50 |            |            |              |

| <sup>t</sup> LOCK               | Maximum PLL Lock Time                              |           |     | 10         | ms         |              |

## AC CHARACTERISTICS (T<sub>A</sub> = 0° to 70°C, V<sub>CC</sub> = 3.3V ±5%)

a. AC characterisitics apply for parallel output termination of 50  $\Omega$  to VTT = VCC/2

## **DC CHARACTERISTICS** (T<sub>A</sub> = 0° to 70°C, V<sub>CC</sub> = 2.5V $\pm$ 5%)

| Symbol            | Characteristics                                  | Min                  | Тур | Max                   | Unit | Condition                            |

|-------------------|--------------------------------------------------|----------------------|-----|-----------------------|------|--------------------------------------|

| VIH               | Input high voltage                               | 1.7                  |     | V <sub>CC</sub> + 0.3 | V    | LVCMOSa                              |

| VIL               | Input low voltage                                | -0.3                 |     | 0.7                   | V    | LVCMOS <sup>b</sup>                  |

| Vpp               | Peak-to <u>-peak</u> input voltage<br>PCLK, PCLK | 500                  |     | 1000                  | mV   | LVPECL                               |

| VCMR <sup>C</sup> | Comm <u>on Mo</u> de Range<br>PCLK, PCLK         | V <sub>CC</sub> -1.4 |     | V <sub>CC</sub> -0.6  | V    | LVPECL                               |

| VOH               | Output High Voltage                              | 1.8                  |     |                       | V    | I <sub>OH</sub> =-15 mA <sup>d</sup> |

| V <sub>OL</sub>   | Output Low Voltage                               |                      |     | 0.6                   | V    | I <sub>OL</sub> = 15 mA              |

| I <sub>IN</sub>   | Input Current                                    |                      |     |                       | μA   |                                      |

| C <sub>IN</sub>   | Input capacitance                                |                      |     |                       | pF   |                                      |

| C <sub>PD</sub>   | Power Dissipation Capacitance                    |                      |     |                       | pF   | Per Output                           |

| ICCA              | Maximum PLL Supply Current                       |                      |     |                       | mA   | V <sub>CCA</sub> Pin                 |

| ICC               | Maximum Quiescent Supply Current                 |                      |     |                       | mA   | All $V_{CC}$ Pins                    |

a. The MPC9600 inputs are CMOS-type inputs with a threshold of 30% of  $\mathsf{V}_{CC}$

b. The MPC9600 inputs are CMOS-type inputs with a threshold of 30% of V<sub>CC</sub>

c. V<sub>CMR</sub> is the difference from V<sub>CC</sub> and the most positive side of the differential input signal. Normal operation is obtained when the "high" input is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> specification.

d. The MPC9600 is capable of driving  $50\Omega$  transmission lines on the incident edge. Each output drives one  $50\Omega$  parallel terminated

transmission line to a termination voltage of  $V_{TT} = V_{CC}/2$ . Alternatively, the device drives up to two 50 $\Omega$  series terminated transmission lines per output.

| Symbol                          | Characteristics                                    | Min       | Тур | Max        | Unit       | Condition   |

|---------------------------------|----------------------------------------------------|-----------|-----|------------|------------|-------------|

| fref                            | Input Frequency<br>FSEL_FB=1<br>FSEL_FB=0          | 16<br>25  |     | 33<br>50   | MHz<br>MHz |             |

| fMAX                            | Maximum Output Frequency<br>FSEL_FB=1<br>FSEL_FB=0 | 100<br>50 |     | 200<br>100 | MHz        |             |

| frefDC                          | Reference Input Duty Cycle                         | 25        |     | 75         | %          |             |

| <sup>t</sup> PD                 | Propagation Delay<br>Input to QFB<br>(PLL locked)  | X -100    | Х   | X+100      | ps         |             |

| <sup>t</sup> sk(o)              | Output-to-output Skew                              |           |     | 150        | ps         |             |

| <sup>t</sup> sk(pp)             | Part-to-part Skew                                  |           |     | 300        | ps         |             |

| tpw                             | Output Duty Cycle                                  | 45        | 50  | 55         | %          |             |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                              | 0.1       |     | 1.0        | ns         | 0.5 to 1.8V |

| <sup>t</sup> PLZ, HZ            | Output Disable Time                                |           |     |            | ns         |             |

| <sup>t</sup> PZL                | Output Enable Time                                 |           |     |            | ns         |             |

| <sup>t</sup> JIT(CC)            | Cycle-to-cycle Jitter (Peak-to-Peak)               |           | ±50 |            |            |             |

| <sup>t</sup> LOCK               | Maximum PLL Lock Time                              |           |     | 10         | ms         |             |

## AC CHARACTERISTICS (T<sub>A</sub> = 0° to 70°C, V<sub>CC</sub> = 2.5V $\pm$ 5%)

a. AC characterisitics apply for parallel output termination of 50  $\Omega$  to VTT = VCC/2

NOTES

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized applications, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (**w**) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

$\Diamond$

Technical Information Center: 1-800-521-6274

HOME PAGE: http://www.motorola.com/semiconductors/

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3–20–1, Minami–Azabu. Minato–ku, Tokyo 106–8573 Japan. 81–3–3440–3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2, Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26668334

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Generators & Support Products category:

Click to view products by IDT manufacturer:

Other Similar products are found below :

5P49V5901A748NLGI 5P49V5901B680NLGI 5P49V5901B744NLGI 5P49V5929B502NLGI 5P49V5935B520LTGI 5V49EE903-116NLGI CV183-2TPAG 82P33814ANLG/W 8T49N004A-002NLGI 8T49N004A-039NLGI 9FGV0631CKLF 9FGV0641AKLFT 9LRS3197AKLF 9UMS9633BFILF 9VRS4450AKLF NB3N51132DTR2G 8N3Q001EG-0035CDI 932SQ426AKLF 950810CGLF 9DBV0531AKILF 9DBV0741AKILF 9FGV0641AKLF 9UMS9633BKLF 9VRS4420DKILF 9VRS4420DKLF 9VRS4420DKLFT CY25404ZXI226 CY25422SXI-004 5P49V5901B712NLGI NB3H5150-01MNTXG 6INT61041NDG PL602-20-K52TC PL613-51QC 8N3Q001FG-1114CDI 9FGV0641AKILF ZL30314GKG2 ZL30253LDG1 ZL30251LDG1 ZL30250LDG1 ZL30169LDG1 ZL30142GGG2 9UMS9633BKILFT 9FGV0631CKLFT 9FGV0631CKILF 5P49V5935B536LTGI PI6LC48P0101LIE DS1099U-ST+ MAX24305EXG+ PI6LC48H02-01LIE 82P33814ANLG