# AT93C86A

# Atmel

## 3-wire Serial EEPROM 16K (2,048 x 8 or 1,024 x 16)

### DATASHEET

#### **Features**

- Low-voltage Operation

- V<sub>CC</sub> = 1.8V to 5.5V

- V<sub>CC</sub> = 2.7V to 5.5V

- User-selectable Internal Organization

- 16K: 2,048 x 8 or 1,024 x 16

- 3-wire Serial Interface

- Sequential Read Operation

- Schmitt Trigger, Filtered Inputs for Noise Suppression

- 2MHz Clock Rate (5V)

- Self-timed Write Cycle (10ms Max)

- High Reliability

- Endurance: 1,000,000 Write Cycles

- Data Retention: 100 Years

- 8-lead JEDEC SOIC, 8-lead TSSOP, 8-pad UDFN, and 8-lead PDIP Packages

- Die Sales: Wafer Form, Waffle Pack, and Bumped Wafers

#### **Description**

The Atmel<sup>®</sup> AT93C86A provides 16,384 bits of Serial Electrically Erasable Programmable Read-Only Memory (EEPROM) organized as 1,024 words of 16 bits each (when the ORG pin is connected to  $V_{CC}$ ) and 2,048 words of 8 bits each (when the ORG pin is tied to ground). The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operations are essential. The AT93C86A is available in space-saving 8-lead JEDEC SOIC, 8-lead TSSOP, 8-pad UDFN, and 8-lead PDIP packages.

The AT93C86A is enabled through the Chip Select pin (CS) and accessed via a 3-wire serial interface consisting of Data Input (DI), Data Output (DO), and Shift Clock (SK). Upon receiving a Read instruction at DI, the address is decoded, and the data is clocked out serially on the DO pin. The write cycle is completely self-timed, and no separate erase cycle is required before Write. The write cycle is only enabled when the part is in the Erase/Write Enable state. When CS is brought high following the initiation of a write cycle, the DO pin outputs the Ready/Busy status of the part.

The AT93C86A operates from 1.8V to 5.5V or from 2.7V to 5.5V.

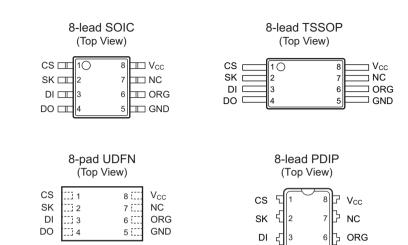

## 1. Pin Configurations and Pinouts

#### Table 1-1. Pin Configurations

| Pin Name        | Function              |

|-----------------|-----------------------|

| CS              | Chip Select           |

| SK              | Serial Data Clock     |

| DI              | Serial Data Input     |

| DO              | Serial Data Output    |

| GND             | Ground                |

| V <sub>CC</sub> | Power Supply          |

| ORG             | Internal Organization |

| NC              | No Connect            |

Note: Drawings are not to scale.

# 2. Absolute Maximum Ratings\*

| Operating Temperature55°C to +125°C                         |

|-------------------------------------------------------------|

| Storage Temperature                                         |

| Voltage on any pin<br>with respect to ground1.00V to +7.00V |

| Maximum Operating Voltage 6.25V                             |

| DC Output Current                                           |

\*Notice: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DO

GND

5||凸

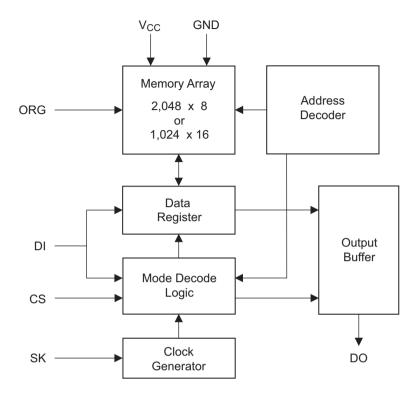

# 3. Block Diagram

Figure 3-1. Block Diagram

Note: When the ORG pin is connected to  $V_{CC}$ , the x16 organization is selected. When it is connected to ground, the x8 organization is selected. If the ORG pin is left unconnected, and the application does not load the input beyond the capability of the internal  $1M\Omega$  pull-up resistor, then the x16 organization is selected.

## 4. Memory Organization

#### 4.1 Pin Capacitance

#### Table 4-1.Pin Capacitance<sup>(1)</sup>

Applicable over recommended operating range from  $T_A = 25^{\circ}C$ , f = 1.0MHz,  $V_{CC} = 5.0V$  (unless otherwise noted).

| Symbol           | Test Conditions                | Мах | Units | Conditions            |

|------------------|--------------------------------|-----|-------|-----------------------|

| C <sub>OUT</sub> | Output Capacitance (DO)        | 5   | pF    | V <sub>OUT</sub> = 0V |

| C <sub>IN</sub>  | Input Capacitance (CS, SK, DI) | 5   | pF    | V <sub>IN</sub> = 0V  |

Note: 1. This parameter is characterized, and is not 100% tested.

#### 4.2 DC Characteristics

#### Table 4-2. DC Characteristics

Applicable over recommended operating range from  $T_{AI} = -40^{\circ}$ C to  $+85^{\circ}$ C,  $V_{CC} = 1.8$ V to 5.5V (unless otherwise noted).

| Symbol                          | Parameter           | Test Condition               |                          | Min                   | Тур  | Max                   | Unit |

|---------------------------------|---------------------|------------------------------|--------------------------|-----------------------|------|-----------------------|------|

| V <sub>CC1</sub>                | Supply Voltage      |                              |                          | 1.8                   |      | 5.5                   | V    |

| V <sub>CC2</sub>                | Supply Voltage      |                              |                          | 2.7                   |      | 5.5                   | V    |

| V <sub>CC3</sub>                | Supply Voltage      |                              |                          |                       |      | 5.5                   | V    |

| 1                               | Supply Current      | V <sub>CC</sub> = 5.0V       | Read at 1.0MHz           |                       | 0.5  | 2.0                   | mA   |

| I <sub>CC</sub>                 | Supply Current      | V <sub>CC</sub> – 5.0V       | Write at 1.0MHz          |                       | 0.5  | 2.0                   | mA   |

| I <sub>SB1</sub>                | Standby Current     | V <sub>CC</sub> = 1.8V       | CS = 0V                  |                       | 0.4  | 1.0                   | μA   |

| I <sub>SB2</sub>                | Standby Current     | V <sub>CC</sub> = 2.7V       | CS = 0V                  |                       | 6.0  | 10.0                  | μA   |

| I <sub>SB3</sub>                | Standby Current     | V <sub>CC</sub> = 5.0V       | CS = 0V                  |                       | 10.0 | 15.0                  | μA   |

| I <sub>IL</sub>                 | Input Leakage       | $V_{IN}$ = 0V to $V_{CC}$    | '                        |                       | 0.1  | 3.0                   | μA   |

| I <sub>OL</sub>                 | Output Leakage      | $V_{IN}$ = 0V to $V_{CC}$    |                          |                       | 0.1  | 3.0                   | μA   |

| V <sub>IL1</sub> <sup>(1)</sup> | Input Low Voltage   | $2.7V \leq V_{CC} \leq 5.5V$ |                          | -0.6                  |      | 0.8                   | V    |

| V <sub>IH1</sub> <sup>(1)</sup> | Input High Voltage  | $2.7V \leq V_{CC} \leq 5.5V$ |                          | 2.0                   |      | V <sub>CC</sub> + 1   | V    |

| V <sub>IL2</sub> <sup>(1)</sup> | Input Low Voltage   | $1.8V \leq V_{CC} \leq 2.7V$ |                          | -0.6                  |      | V <sub>CC</sub> x 0.3 | V    |

| V <sub>IH2</sub> <sup>(1)</sup> | Input High Voltage  | $1.8V \leq V_{CC} \leq 2.7V$ |                          | V <sub>CC</sub> x 0.7 |      | V <sub>CC</sub> + 1   | V    |

| V <sub>OL1</sub>                | Output Low Voltage  | $2.7V \leq V_{CC} \leq 5.5V$ | I <sub>OL</sub> = 2.1mA  |                       |      | 0.4                   | V    |

| V <sub>OH1</sub>                | Output High Voltage | $2.7V \leq V_{CC} \leq 5.5V$ | I <sub>OH</sub> = -0.4mA | 2.4                   |      |                       | V    |

| V <sub>OL2</sub>                | Output Low Voltage  | $1.8V \leq V_{CC} \leq 2.5V$ | I <sub>OL</sub> = 0.15mA |                       |      | 0.2                   | V    |

| V <sub>OH2</sub>                | Output High Voltage | $1.8V \leq V_{CC} \leq 2.7V$ | Ι <sub>ΟΗ</sub> = –100μΑ | $V_{CC} - 0.2$        |      |                       | V    |

Note: 1.  $V_{IL}$  min and  $V_{IH}$  max are reference only, and are not tested.

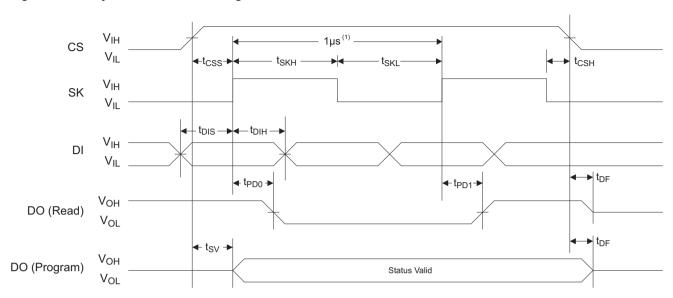

## 4.3 AC Characteristics

#### Table 4-3. AC Characteristics

Applicable over recommended operating range from  $T_{AI} = -40^{\circ}C$  to + 85°C, CL = 1 TTL gate and 100pF (unless otherwise noted).

| Symbol                   | Parameter           | Test Condition            | I                              | Min  | Тур       | Max  | Units           |

|--------------------------|---------------------|---------------------------|--------------------------------|------|-----------|------|-----------------|

|                          |                     | $4.5V \le V_{CC} \le 5.$  | 5V                             | 0    |           | 2    | MHz             |

| f <sub>SK</sub>          | SK Clock Frequency  | $2.7V \le V_{CC} \le 5.$  | $2.7V \leq V_{CC} \ \leq 5.5V$ |      |           | 1    | MHz             |

|                          |                     | $1.8V \le V_{CC} \le 5.$  | $1.8V \leq V_{CC} \leq 5.5V$   |      |           | 250  | kHz             |

|                          |                     | $2.7V \le V_{CC} \le 5.1$ | 5V                             | 250  |           |      | ns              |

| t <sub>sкн</sub>         | SK High Time        | $1.8V \le V_{CC} \le 5.$  | 5V                             | 1000 |           |      | ns              |

| 4                        | SK Low Time         | $2.7V \le V_{CC} \le 5.1$ | 5V                             | 250  |           |      | ns              |

| t <sub>SKL</sub>         | SK LOW TIME         | $1.8V \le V_{CC} \le 5.$  | 5V                             | 1000 |           |      | ns              |

|                          |                     | $2.7V \le V_{CC} \le 5.1$ | 5V                             | 250  |           |      | ns              |

| t <sub>cs</sub>          | Minimum CS Low Time | $1.8V \le V_{CC} \le 5.$  | 5V                             | 1000 |           |      | ns              |

| 1                        |                     | Deletive to CK            | $2.7V \leq V_{CC} \ \leq 5.5V$ | 50   |           |      | ns              |

| t <sub>css</sub>         | CS Setup Time       | Relative to SK            | $1.8V \le V_{CC} \ \le 5.5V$   | 200  |           |      | ns              |

| 4                        | DI Sotup Timo       | Relative to SK            | $2.7V \leq V_{CC} \ \leq 5.5V$ | 100  |           |      | ns              |

| t <sub>DIS</sub>         | DI Setup Time       | Relative to SK            | $1.8V \leq V_{CC} \ \leq 5.5V$ | 400  |           |      | ns              |

| t <sub>CSH</sub>         | CS Hold Time        | Relative to SK            |                                | 0    |           |      | ns              |

| +                        | DI Hold Time        | Relative to SK            | $2.7V \leq V_{CC} \ \leq 5.5V$ | 100  |           |      | ns              |

| t <sub>DIH</sub>         |                     | Relative to SR            | $1.8V \le V_{CC} \ \le 5.5V$   | 400  |           |      | ns              |

| ÷                        | Output Delay to 1   | AC Test                   | $2.7V \leq V_{CC} \ \leq 5.5V$ |      |           | 250  | ns              |

| t <sub>PD1</sub>         |                     | AC TESI                   | $1.8V \le V_{CC} \ \le 5.5V$   |      |           | 1000 | ns              |

| +                        | Output Delay to 0   | AC Test                   | $2.7V \leq V_{CC} \ \leq 5.5V$ |      |           | 250  | ns              |

| t <sub>PD0</sub>         | Output Delay to 0   | AC TESI                   | $1.8V \leq V_{CC} \ \leq 5.5V$ |      |           | 1000 | ns              |

| +                        | CS to Status Valid  | AC Test                   | $2.7V \leq V_{CC} \ \leq 5.5V$ |      |           | 250  | ns              |

| t <sub>sv</sub>          |                     | AC TESI                   | $1.8V \leq V_{CC} \ \leq 5.5V$ |      |           | 1000 | ns              |

| t                        | CS to DO in         | AC Test                   | $2.7V \leq V_{CC} \ \leq 5.5V$ |      |           | 150  | ns              |

| t <sub>DF</sub>          | High-impedance      | CS = V <sub>IL</sub>      | $1.8V \leq V_{CC} \ \leq 5.5V$ |      |           | 400  | ns              |

| t <sub>WP</sub>          | Write Cycle Time    |                           | $1.8V \le V_{CC} \ \le 5.5V$   | 0.1  | 3         | 10   | ms              |

| Endurance <sup>(1)</sup> | 5.0V, 25°C          |                           |                                |      | 1,000,000 | )    | Write<br>Cycles |

Note: 1. This parameter is characterized, and is not 100% tested.

| A | tm | el |

|---|----|----|

|   |    |    |

## 5. Functional Description

The AT93C86A is accessed via a simple and versatile 3-wire serial communication interface. Device operation is controlled by seven instructions issued by the Host processor. A valid instruction starts with a rising edge of CS and consists of a Start bit (Logic 1), followed by the appropriate opcode, and the desired memory address location.

|             |    |        | Addr                             | ess                       | Da          | ata                              |                                                                                                  |

|-------------|----|--------|----------------------------------|---------------------------|-------------|----------------------------------|--------------------------------------------------------------------------------------------------|

| Instruction | SB | Opcode | <b>x8</b> <sup>(1)</sup>         | <b>x16</b> <sup>(1)</sup> | <b>x</b> 8  | x16                              | Comments                                                                                         |

| READ        | 1  | 10     | A <sub>10</sub> - A <sub>0</sub> | $A_{9} - A_{0}$           |             |                                  | Reads data stored in memory at specified address.                                                |

| EWEN        | 1  | 00     | 11XXXXXXX                        | 11XXXXXX                  |             |                                  | Write Enable must precede all programming modes.                                                 |

| ERASE       | 1  | 11     | A <sub>10</sub> – A <sub>0</sub> | $A_{9} - A_{0}$           |             |                                  | Erases memory location $A_N - A_0$ .                                                             |

| WRITE       | 1  | 01     | A <sub>10</sub> - A <sub>0</sub> | $A_{9} - A_{0}$           | $D_7 - D_0$ | D <sub>15</sub> – D <sub>0</sub> | Writes memory location $A_N - A_0$ .                                                             |

| ERAL        | 1  | 00     | 10XXXXXXX                        | 10XXXXXX                  |             |                                  | Erases all memory locations. Valid only at $V_{CC}$ = 4.5V to 5.5V.                              |

| WRAL        | 1  | 00     | 01XXXXXXX                        | 01XXXXXX                  | $D_7 - D_0$ | D <sub>15</sub> – D <sub>0</sub> | Writes all memory locations. Valid only at $V_{CC}$ = 4.5V to 5.5V and Disable Register cleared. |

| EWDS        | 1  | 00     | 00XXXXXXX                        | 00XXXXXX                  |             |                                  | Disables all programming instructions.                                                           |

| Table 5-1. | AT93C86A Instruction | Set |

|------------|----------------------|-----|

|            |                      |     |

Note: 1. The 'X' in the address field represent don't care values, and must be clocked.

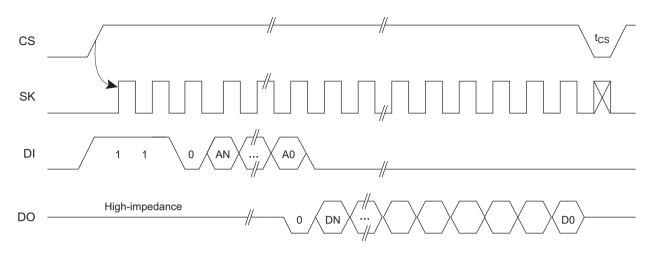

**READ:** The READ instruction contains the address code for the memory location to be read. After the instruction and address are decoded, data from the selected memory location is available at the Serial Output pin, DO. Output data changes are synchronized with the rising edges of the Serial Clock pin, SK. It should be noted that a dummy bit (Logic 0) precedes the 8-bit or 16-bit data output string. The AT93C86A supports sequential Read operations. The device will automatically increment the internal address pointer and clock out the next memory location as long as Chip Select (CS) is held high. In this case, the dummy bit (Logic 0) will not be clocked out between memory locations, thus allowing for a continuous stream of data to be read.

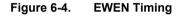

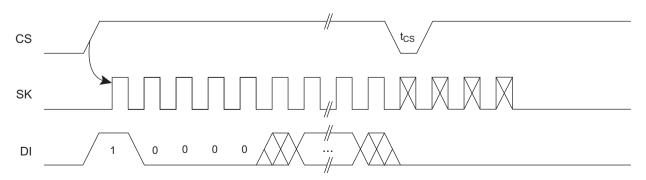

**Erase/Write Enable (EWEN):** To ensure data integrity, the part automatically goes into the Erase/Write Disable (EWDS) state when power is first applied. An Erase/Write Enable (EWEN) instruction must be executed first before any programming instructions can be carried out.

Note: Once in the EWEN state, programming remains enabled until an EWDS instruction is executed, or V<sub>CC</sub> power is removed from the part.

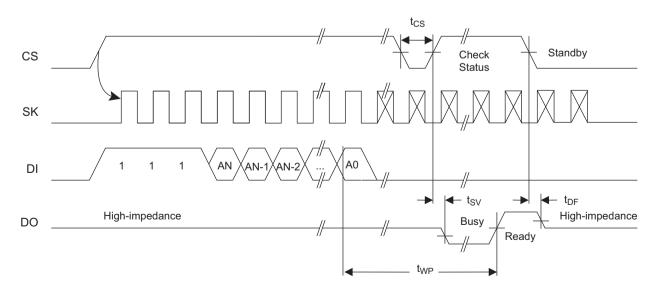

**ERASE:** The ERASE instruction programs all bits in the specified memory location to the Logic 1 state. The self-timed erase cycle starts once the ERASE instruction and address are decoded. The DO pin outputs the Ready/Busy status of the part if CS is brought high after being kept low for a minimum of  $t_{CS}$ . A Logic 1 at the DO pin indicates that the selected memory location has been erased, and the part is ready for another instruction.

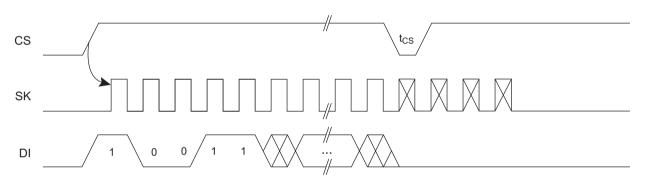

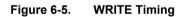

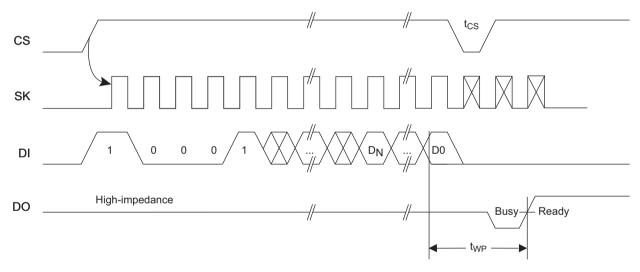

**WRITE:** The WRITE instruction contains the 8-bits or 16-bits of data to be written into the specified memory location. The self-timed programming cycle,  $t_{WP}$ , starts after the last bit of data is received at Serial Data Input pin DI. The DO pin outputs the Ready/Busy status of the part if CS is brought high after being kept low for a minimum of  $t_{CS}$ . A Logic 0 at DO indicates that programming is still in progress. A Logic 1 indicates that the memory location at the specified address has been written with the data pattern contained in the instruction, and the part is ready for further instructions. A Ready/Busy status cannot be obtained if CS is brought high after the end of the self-timed programming cycle,  $t_{WP}$ .

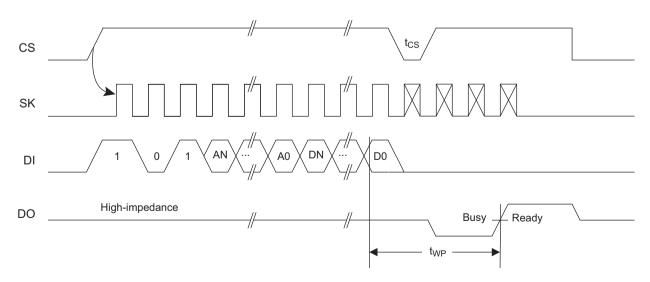

**Erase All (ERAL):** The Erase All (ERAL) instruction programs every bit in the Memory Array to the Logic 1 state and is primarily used for testing purposes. The DO pin outputs the ready/busy status of the part if CS is brought high after being kept low for a minimum of  $t_{CS}$ . The ERAL instruction is valid only at  $V_{CC} = 5.0V \pm 10\%$ .

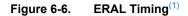

**Write All (WRAL):** The Write All (WRAL) instruction programs all memory locations with the data patterns specified in the instruction. The DO pin outputs the Ready/Busy status of the part if CS is brought high after being kept low for a minimum of  $t_{CS}$ . The WRAL instruction is valid only at  $V_{CC} = 5.0V \pm 10\%$ .

**Erase/Write Disable (EWDS):** To protect against accidental data disturbance, the Erase/Write Disable (EWDS) instruction disables all programming modes and should be executed after all programming operations. The operation of the Read instruction is independent of both the EWEN and EWDS instructions and can be executed at any time.

# 6. Timing Diagrams

Note: 1. This is the minimum SK period.

#### Table 6-1. Organization Key for Timing Diagrams

|                | AT93C8          | 6A (16K)        |

|----------------|-----------------|-----------------|

| I/O            | x8              | x16             |

| A <sub>N</sub> | A <sub>10</sub> | A <sub>9</sub>  |

| D <sub>N</sub> | D <sub>7</sub>  | D <sub>15</sub> |

Figure 6-3. READ Timing

Note: 1.  $V_{CC} = 4.5V$  to 5.5V.

Note: 1. Valid only at  $V_{CC}$  = 4.5V to 5.5V.

Atmel

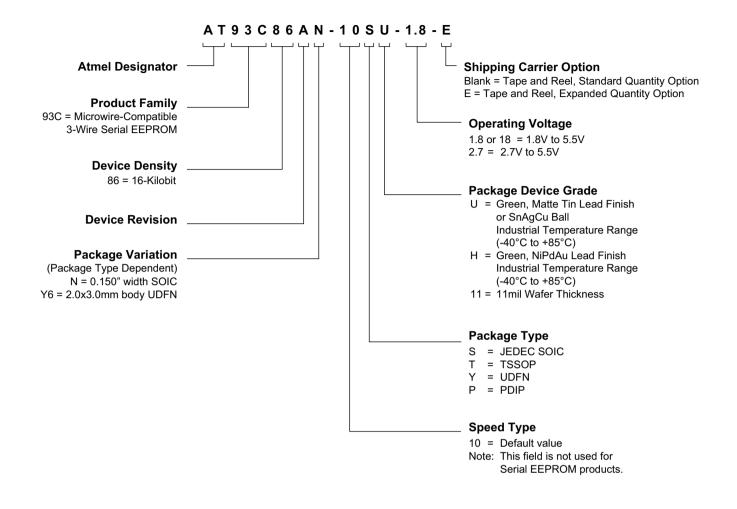

## 7. Ordering Code Detail

# 8. Part Markings

|                                                                                                                                                                                                                                                                                                                                      | 8-lead SOI                                                                      | С                                                                                                        | 8-lead TSSOP                                                                                          |                                                                                                                                           |                                                                                                                                       |                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                      | Note: Lot Numbe                                                                 | IELYWW<br>86A<br>86A<br>r and location of assembly<br>m side of the package.                             | U%<br>AT # # #<br>Note: Lot Number, location of assemt<br>YWW date code on the bottom<br>the package. | I A A A A A A A A A A A A A A A A A A A                                                                                                   |                                                                                                                                       |                                                                     |

|                                                                                                                                                                                                                                                                                                                                      | 8-pad UDF                                                                       |                                                                                                          | 8-lead PDIP                                                                                           |                                                                                                                                           |                                                                                                                                       |                                                                     |

|                                                                                                                                                                                                                                                                                                                                      | E F                                                                             | dy<br># # #<br>18<br>CXX                                                                                 | ATMLUYWW<br>93C86A<br>PU%%<br>C C C C C C                                                             | iembly                                                                                                                                    |                                                                                                                                       |                                                                     |

|                                                                                                                                                                                                                                                                                                                                      | Note 1: • designates p<br>Note 2: Package drawin                                |                                                                                                          | on the bottom side of the packa                                                                       |                                                                                                                                           |                                                                                                                                       |                                                                     |

| Catalog Number Trunca<br>AT93C86A<br>Date Codes                                                                                                                                                                                                                                                                                      | Note 2: Package drawin                                                          | gs are not to scale                                                                                      | on the bottom side of the pace                                                                        |                                                                                                                                           | s                                                                                                                                     |                                                                     |

|                                                                                                                                                                                                                                                                                                                                      | Note 2: Package drawin                                                          | gs are not to scale<br>Truncatior                                                                        |                                                                                                       | Voltage                                                                                                                                   |                                                                                                                                       | m Voltage                                                           |

| AT93C86A<br>Date Codes                                                                                                                                                                                                                                                                                                               | Note 2: Package drawin                                                          | gs are not to scale<br>Truncatior                                                                        | n Code ###: 86A<br>ork Week of Assembly<br>2<br>4                                                     | Voltage:<br>% =<br>3 or 27:                                                                                                               |                                                                                                                                       |                                                                     |

| AT93C86A           Date Codes           Y = Year           4: 2014         8: 2018           5: 2015         9: 2019           6: 2016         0: 2020                                                                                                                                                                               | M = Month<br>A: January<br>B: February<br><br>L: December                       | Truncatior<br>WW = Wo<br>02: Week<br>04: Week<br>                                                        | n Code ###: 86A<br>ork Week of Assembly<br>2<br>4                                                     | Voltage:<br>% =<br>3 or 27:<br>1 or 18:                                                                                                   | = Minimur<br>2.7V mi<br>1.8V mi                                                                                                       | in                                                                  |

| AT93C86A           Date Codes           Y = Year           4: 2014         8: 2018           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021                                                                                                                                             | M = Month<br>A: January<br>B: February<br>L: December<br>Lot                    | Truncation<br>Truncation<br>WW = Wc<br>02: Week<br>04: Week<br><br>52: Week<br>t Number                  | n Code ###: 86A<br>ork Week of Assembly<br>2<br>4                                                     | Voltage:<br>% =<br>3 or 27:<br>1 or 18:<br>Grade/L<br>H:                                                                                  | = Minimur<br>2.7V mi<br>1.8V mi<br><b>.ead Fini</b> s                                                                                 | in<br>in                                                            |

| AT93C86A           Date Codes           Y = Year           4: 2014         8: 2018           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021           Country of Assembly                                                                                                               | M = Month<br>A: January<br>B: February<br>L: December<br>Lot                    | Truncation<br>Truncation<br>WW = Wc<br>02: Week<br>04: Week<br><br>52: Week<br>t Number                  | n Code ###: 86A<br>ork Week of Assembly<br>2<br>4<br>52                                               | Voltage:<br>% =<br>3 or 27:<br>1 or 18:<br>Grade/L<br>H:<br>U:                                                                            | = Minimur<br>2.7V mi<br>1.8V mi<br><b>.ead Fini</b> s                                                                                 | in<br>is <b>h Material</b><br>al/NiPdAu<br>al/Matte Tin/Sn <i>i</i> |

| AT93C86A           Date Codes           Y = Year           4: 2014         8: 2018           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021           Country of Assembly         @ = Country of Assembly                                                                               | M = Month<br>A: January<br>B: February<br><br>L: December<br>Lot Numbers Corres | Truncation<br>Truncation<br>WW = Wc<br>02: Week<br>04: Week<br><br>52: Week<br>t Number<br>AA = Atmel Wa | n Code ###: 86A<br>ork Week of Assembly<br>2<br>4<br>52                                               | Voltages           % =           3 or 27:           1 or 18:           Grade/L           H:           U:           Atmel T           AT:  | Minimur     2.7V mi     1.8V mi     .ead Finis     Industria     Industria     runcation     Atmel     Atmel                          | in<br>is <b>h Material</b><br>al/NiPdAu<br>al/Matte Tin/Sn <i>i</i> |

| AT93C86A         Date Codes         Y = Year         4: 2014       8: 2018         5: 2015       9: 2019         6: 2016       0: 2020         7: 2017       1: 2021         Country of Assembly       @ = Country of Assembly         @ = Country of Assembly       Trace Code         XX = Trace Code (Atmel       XX = Trace Code | M = Month<br>A: January<br>B: February<br><br>L: December<br>Lot Numbers Corres | Truncation<br>Truncation<br>WW = Wc<br>02: Week<br>04: Week<br><br>52: Week<br>t Number<br>AA = Atmel Wa | n Code ###: 86A<br>ork Week of Assembly<br>2<br>4<br>52                                               | Voltage:           % =           3 or 27:           1 or 18:           Grade/L           H:           U:           Atmel T           ATM: | Minimur<br>2.7V mi<br>1.8V mi<br>1.8V mi<br><b>ead Finis</b><br>Industria<br>Industria<br><b>fruncatio</b><br>Atmel<br>Atmel<br>Atmel | in<br>is <b>h Material</b><br>al/NiPdAu<br>al/Matte Tin/Sn <i>i</i> |

**Atmel**

# 9. Ordering Information

|                                    | Lead                      |                                           |                             | Delivery I    | nformation      | Operation                                    |

|------------------------------------|---------------------------|-------------------------------------------|-----------------------------|---------------|-----------------|----------------------------------------------|

| Atmel Ordering Code <sup>(1)</sup> | Finish                    | Package                                   | Voltage                     | Form          | Quantity        | Range                                        |

| AT93C86A-10SU-1.8                  |                           | NiPdAu<br>Lead-free<br>Halogen-free<br>8X | 1.8V to 5.5V                | Tape and Reel | 4,000 per Reel  |                                              |

| AT93C86A-10SU-2.7                  | Lead-free                 |                                           | 2.7V to 5.5V <sup>(1)</sup> | Tape and Reel | 4,000 per Reel  |                                              |

| AT93C86A-10TU-1.8                  |                           |                                           | 1.8V to 5.5V                | Tape and Reel | 5,000 per Reel  |                                              |

| AT93C86A-10TU-2.7                  | -                         |                                           | 2.7V to 5.5V <sup>(1)</sup> | Tape and Reel | 5,000 per Reel  |                                              |

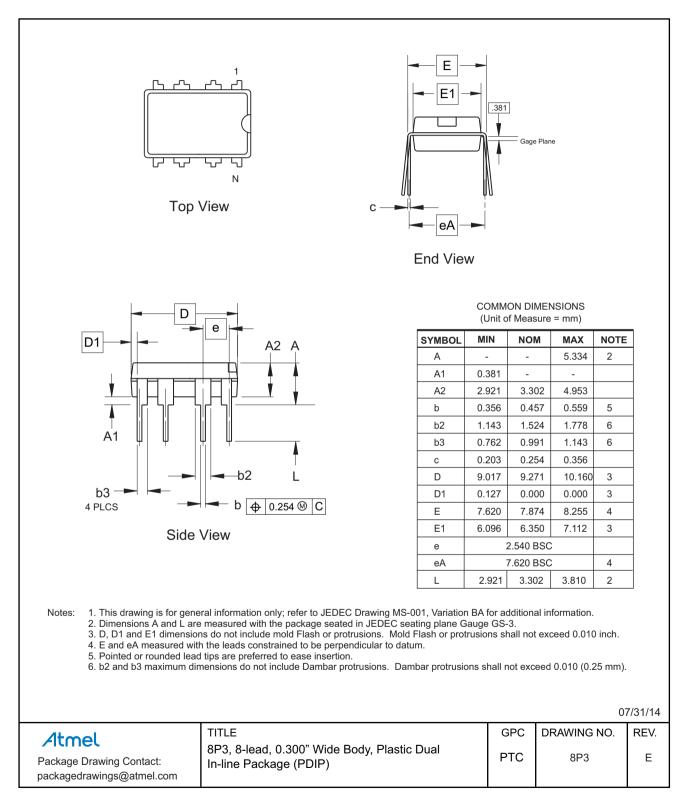

| AT93C86A-10PU-1.8                  | Matte Tin                 | 8P3                                       | 1.8V to 5.5V                | Tape and Reel | 4,000 per Reel  | Industrial<br>Temperature<br>(-40°C to 85°C) |

| AT93C86A-10PU-2.7                  | Lead-free<br>Halogen-free | 053                                       | 2.7V to 5.5V <sup>(1)</sup> | Tape and Reel | 4,000 per Reel  |                                              |

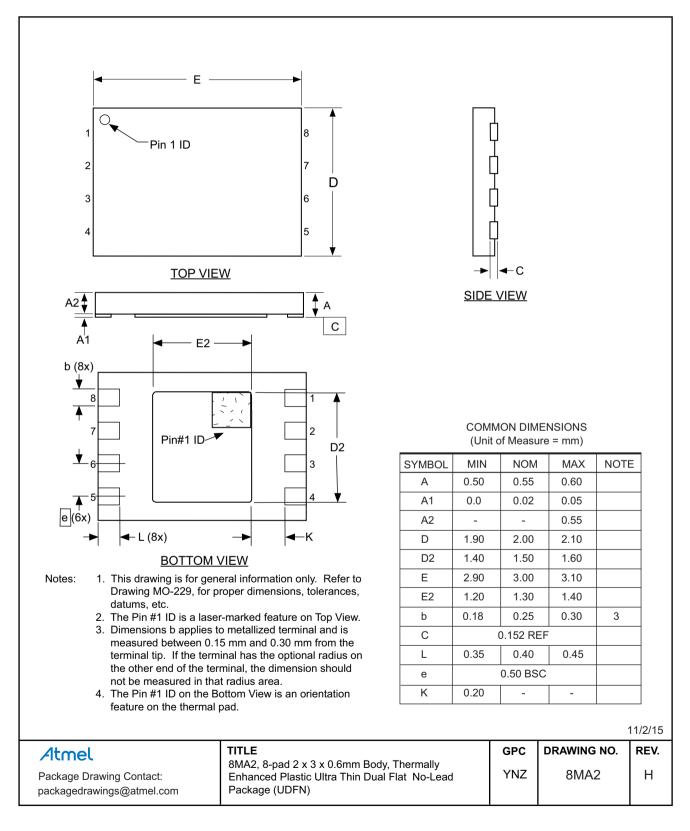

| AT93C86AY6-10YH-1.8                | NiPdAu                    | 8MA2                                      | (1,0)/(10,E,E)/(10,0)       | Tape and Reel | 5,000 per Reel  |                                              |

| AT93C86AY6-10YH-18-E               | Lead-free<br>Halogen-free | OIVIAZ                                    | 1.8V to 5.5V                | Tape and Reel | 15,000 per Reel |                                              |

| AT93C86A-W1.8-11 <sup>(2)</sup>    | N/A                       | Wafer Sale                                | 1.8V to 5.5V                | Nc            | ote 2           |                                              |

Notes: 1. For 2.7V devices used in a 4.5V to 5.5V range, please refer to performance values in Section 4.2, "DC Characteristics" and 4.3, "AC Characteristics" on page 5.

2. For Waffle pack and Wafer form; order as SL788 for inkless Wafer form. Bumped die available upon request. Please contact Atmel sales.

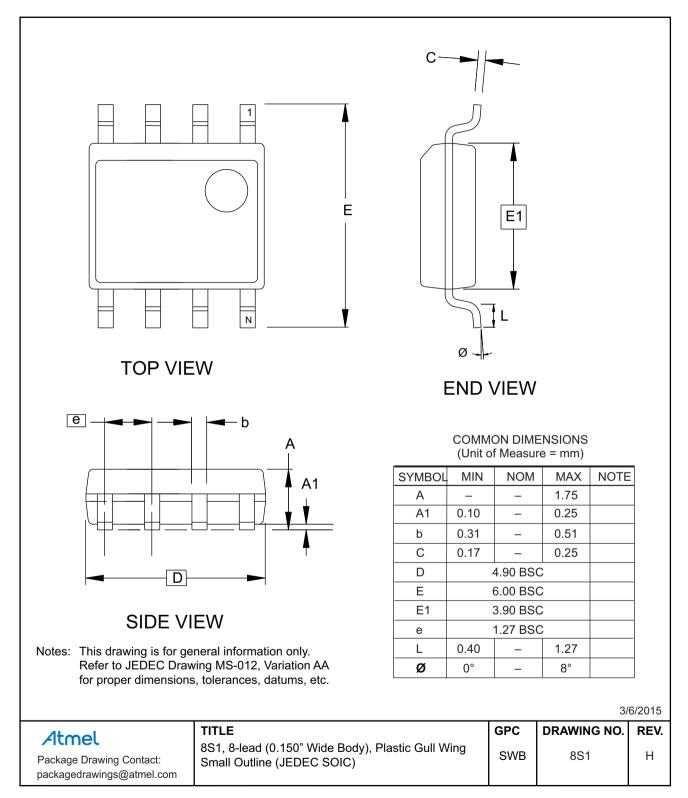

|      | Package Type                                                              |

|------|---------------------------------------------------------------------------|

| 8S1  | 8-lead, 0.150" wide, Plastic Gull Wing, Small Outline (JEDEC SOIC)        |

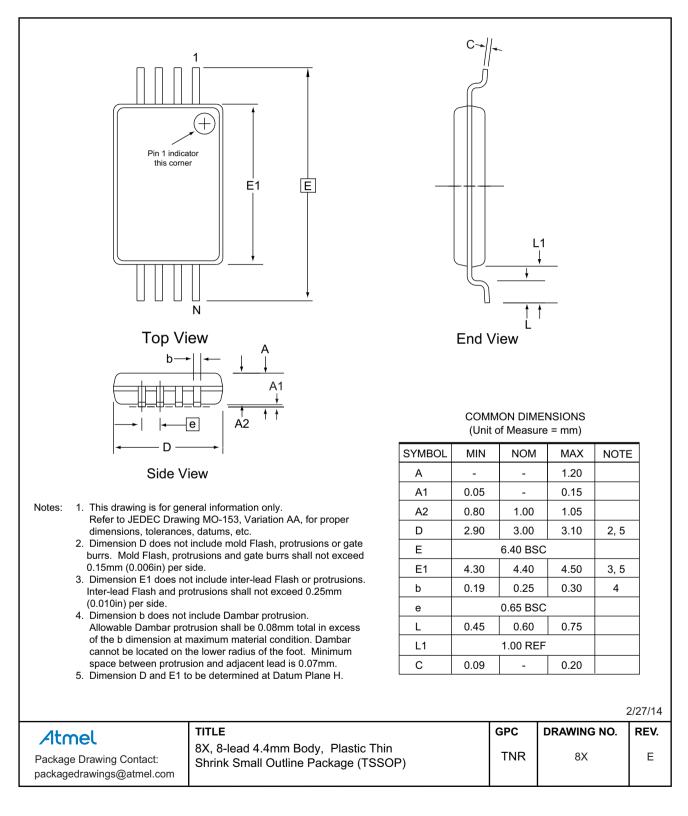

| 8X   | 8-lead, 0.170" wide, Thin Shrink Small Outline (TSSOP)                    |

| 8P3  | 8-lead, 0.300" wide body, Plastic Dual In-line Package (PDIP)             |

| 8MA2 | 8-pad, 2.00mm x 3.00mm body, 0.50mm pitch, Ultra Thin Dual No Lead (UDFN) |

# 10. Packaging Information

#### 10.1 8S1 — 8-lead JEDEC SOIC

#### 10.2 8X — 8-lead TSSOP

Atmel

# 11. Revision History

| Revision No. | Date    | Comments                                                                                                                                                                                                                            |

|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3408K        | 12/2015 | Correct Ordering Code Detail and update the 8S1 and 8MA2 package drawings.                                                                                                                                                          |

| 3408J        | 01/2015 | Add the UDFN extended quantity option and update the ordering information section.<br>Update the 8MA2 and 8P3 package drawings.                                                                                                     |

| 34081        | 08/2014 | Update pinouts, 8MA2 package drawing, grammatical changes, document template, logos, and disclaimer page. No changes to functional specification.                                                                                   |

| 3408H        | 01/2007 | Add "Bottom View" to page 1 Ultra Thin MiniMap package drawing page 4 revise Note 1 added "ensured by characterization".                                                                                                            |

| 3408G        | 07/2006 | Revision history implemented.<br>Delete 'Preliminary' status from datasheet; Add 'Ultra Thin' description to MLP 2x3<br>package; Delete '1.8V not available' on Figure 1 Note; Add 1.8V range on Table 4 under<br>Write Cycle Time. |

# Atmel Enabling Unlimited Possibilities®

T

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(40

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-3408K-SEEPROM-AT93C86A-Datasheet\_122015.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for EEPROM category:

Click to view products by Microchip manufacturer:

Other Similar products are found below :

M29F040-70K6 718278CB 718620G AT28C256-15PU-ND 444358RB 444362FB BR93C46-WMN7TP 442652G 701986CB TC58NVG0S3HBAI4 5962-8751413XA TC58BVG0S3HBAI4 TH58NYG3S0HBAI6 CAT25320YIGT-KK CAT25320DWF LE24C162-R-E 5962-8751417YA 5962-8751409YA CAT25M01LI-G DS28E11P+ BR9016AF-WE2 LE2464DXATBG CAS93C66VP2I-GT3 DS28E25+T DS28EL15Q+T M95320-DFDW6TP DS28E05GB+T AT25320B-SSPDGV-T HE24C64WLCSPD BL24SA128B-CSRC 24FC16T-I/OT 24FC08T-I/OT M24128-BFMN6TP S-24CS04AFM-TFH-U M24C04-FMC5TG M24C16-DRMN3TPK M24C64-DFMN6TP 34AA02-EMS M95080-RMC6TG M95128-DFCS6TP/K M95128-DFDW6TP M95256-DFMN6TP M95320-RDW6TP M95640-RDW6TP AT17LV010-10CU AT24C01C-SSHM-B AT24C01D-MAHM-T AT24C04D-MAHM-T AT24C04D-SSHM-T AT24C08C-SSHM-B