# Wide V<sub>IN</sub> Dual Standard Buck Regulator With 3A/3A Continuous Output Current

## ISL85033

The ISL85033 is a dual standard buck regulator capable of 3A per channel continuous output current. With an input range of 4.5V to 28V, it provides a high frequency power solution for a variety of point of load applications.

The PWM controller in the ISL85033 drives an internal switching N-Channel power MOSFET and requires an external Schottky diode to generate the output voltage. The integrated power switch is optimized for excellent thermal performance up to 3A of output current. The PWM regulator switches at a default frequency of 500kHz and it can be user programmed or synchronized from 300kHz to 2MHz. The ISL85033 utilizes peak current mode control to provide flexibility in component selection and minimize solution size. The protection features include overcurrent, UVLO and thermal overload protection.

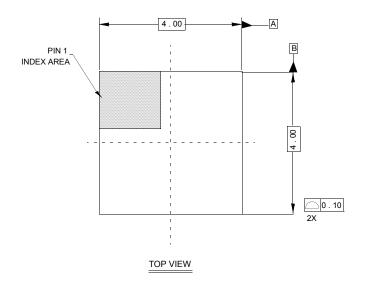

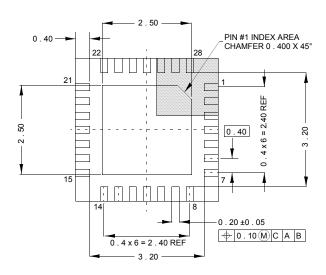

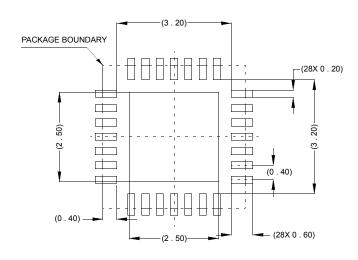

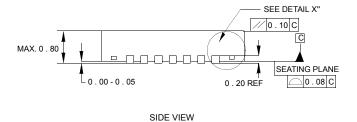

The ISL85033 is available in a small 4mmx4mm Thin Quad Flat Pb-free (TQFN) package.

### **Related Literature**

See AN1574 "ISL85033DUALEVAL1Z Wide VIN Dual Standard Buck Regulator With 3A/3A Output Current"

#### **Features**

- Wide Input Voltage Range from 4.5V to 28V

- Adjustable Output Voltage with Continuous Output Current up to 3A

- Current Mode Control

- Adjustable Switching Frequency from 300kHz to 2MHz

- Independent Power-Good Detection

- Selectable In-Phase or Out-of-Phase PWM Operation

- Independent, Sequential, Ratiometric or Absolute Tracking Between Outputs

- Internal 2ms Soft-start Time

- Overcurrent/Short Circuit Protection, Thermal Overload Protection, UVLO

- Boot Undervoltage Detection

- Pb-Free (RoHS Compliant)

## **Applications**

- General Purpose Point of Load DC/DC Power Conversion

- · Set-top Boxes

- FPGA Power and STB Power

- DVD and HDD Drives

- · LCD Panels, TV Power

- · Cable Modems

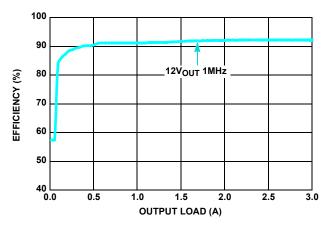

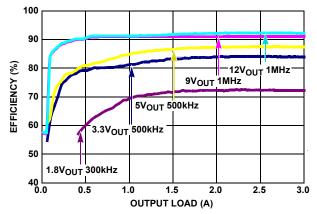

FIGURE 1. EFFICIENCY vs LOAD,  $V_{IN}$  = 28V,  $T_A$  = +25 °C

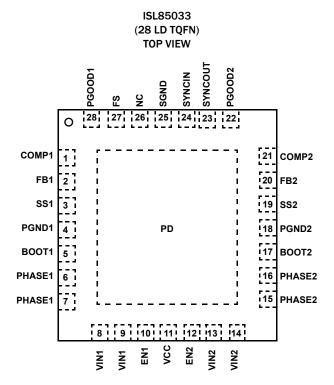

# **Pin Configuration**

# **Pin Descriptions**

| PIN NUMBER   | SYMBOL         | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 21        | COMP1, COMP2   | COMP1/COMP2 is the output of the error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2, 20        | FB1, FB2       | Feedback pin for the regulator. FB is the negative input to the voltage loop error amplifier. COMP is the output of the error amplifier. The output voltage is set by an external resistor divider connected to FB. In addition, the PWM regulator's power-good and undervoltage protection circuits use FB1/2 to monitor the regulator output voltage.                                                                                                    |

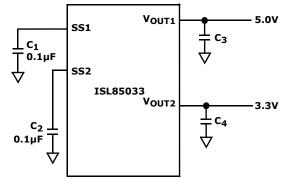

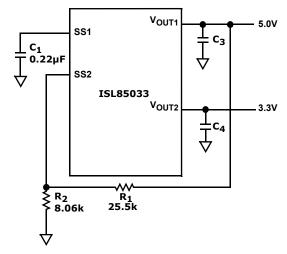

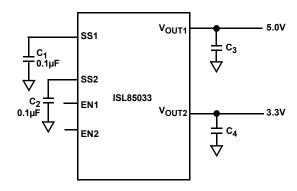

| 3, 19        | SS1, SS2       | Soft-Start pins for each controller. The SS1/2 pins control the soft-start and sequence of their respective outputs. A single capacitor from the SS pin to ground determines the output ramp rate. See the "Output Tracking and Sequencing" on page 16 for soft-start and output tracking/sequencing details. If SS pins are tied to VCC, an internal soft-start of 2ms will be used. Maximum C <sub>SS</sub> value is 50nF.                               |

| 4, 18        | PGND1, PGND2   | Power ground connections. Connect directly to the system GND plane.                                                                                                                                                                                                                                                                                                                                                                                        |

| 5, 17        | B00T1, B00T2   | Floating bootstrap supply pin for the power MOSFET gate driver. The bootstrap capacitor provides the necessary charge to turn on the internal N-Channel MOSFET. Connect an external capacitor from this pin to PHASE.                                                                                                                                                                                                                                      |

| 6, 7, 15, 16 | PHASE1, PHASE2 | Switch node output. It connects the source of the internal power MOSFET with the external output inductor and with the cathode of the external diode.                                                                                                                                                                                                                                                                                                      |

| 8, 9, 13, 14 | VIN1, VIN2     | The input supply for the power stage of the PWM regulator and the source for the internal linear regulator that provides bias for the IC. Place a minimum of 10µF ceramic capacitance from each VIN to GND and close to the IC for decoupling.                                                                                                                                                                                                             |

| 10, 12       | EN1, EN2       | PWM controller's enable inputs. The PWM controllers are held off when the pin is pulled to ground. When the voltage on this pin rises above 2V, the PWM controller is enabled. If EN1, EN2 pins are driven by an external signal, the minimum off-time for EN1, EN2 should be: $EN\_T\_off \ (\mu s) = 10 \mu s \bullet C_{SS}/2.2nF$ where $C_{SS}$ is the soft-start pin capacitor (nF). ISL85033 does not have debouncing to EN1, EN2 external signals. |

| 11           | VCC            | Output of the internal 5V linear regulator. Decouple to PGND with a minimum of 4.7µF ceramic capacitor. This pin is provided only for internal bias of ISL85033 (not to be loaded with current over 10mA).                                                                                                                                                                                                                                                 |

# Pin Descriptions (Continued)

| PIN NUMBER | SYMBOL         | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23         | SYNCOUT        | Synchronization output. Provides a signal that is the inverse of the SYNCIN signal.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24         | SYNCIN         | Connect to an external signal for synchronization from 300kHz to 2MHz (negative edge trigger). SYNCIN is not allowed to be floating.  When SYNCIN = logic 0, PHASE1 and PHASE2 are running at 180° out-of-phase.  When SYNCIN = logic 1, PHASE1 and PHASE2 are running at 0° in-phase.  When SYNCIN = an external clock, PHASE1 and PHASE2 are running at 180° out-of-phase.  External SYNC frequency applied to the SYNCIN pin should be at least 2.4 times the internal switching frequency setting. |

| 25         | SGND           | Signal ground connections. The exposed pad must be connected to SGND and soldered to the PCB. All voltage levels are measured with respect to this pin.                                                                                                                                                                                                                                                                                                                                                |

| 26         | NC             | This is a no connection pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

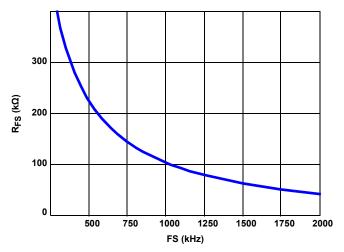

| 27         | FS             | Frequency selection pin. Tie to VCC for 500kHz switching frequency. Connect a resistor to GND for adjustable frequency from 300kHz to 2MHz.                                                                                                                                                                                                                                                                                                                                                            |

| 22, 28     | PGOOD1, PGOOD2 | Open drain power-good output that is pulled to ground when the output voltage is below regulation limits or during the soft-start interval. There is an internal $5M\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                 |

| -          | PD             | The exposed pad must be connected to the system GND plane with as many vias as possible for proper electrical and thermal performance.                                                                                                                                                                                                                                                                                                                                                                 |

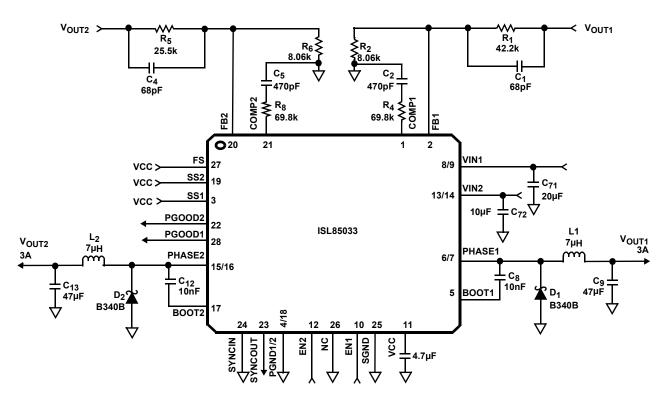

# **Typical Application Schematics**

FIGURE 2. DUAL 3A OUTPUT (VIN RANGE FROM 4.5V TO 28V)

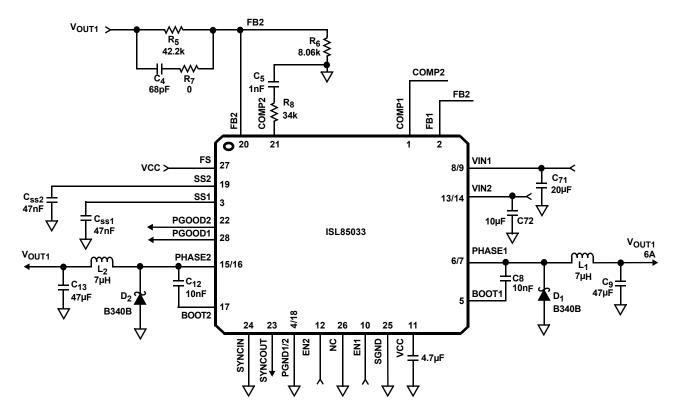

# Typical Application Schematics (Continued)

FIGURE 3. SINGLE 6A OUTPUT (VIN RANGE FROM 4.5V TO 28V) CURRENT SHARING

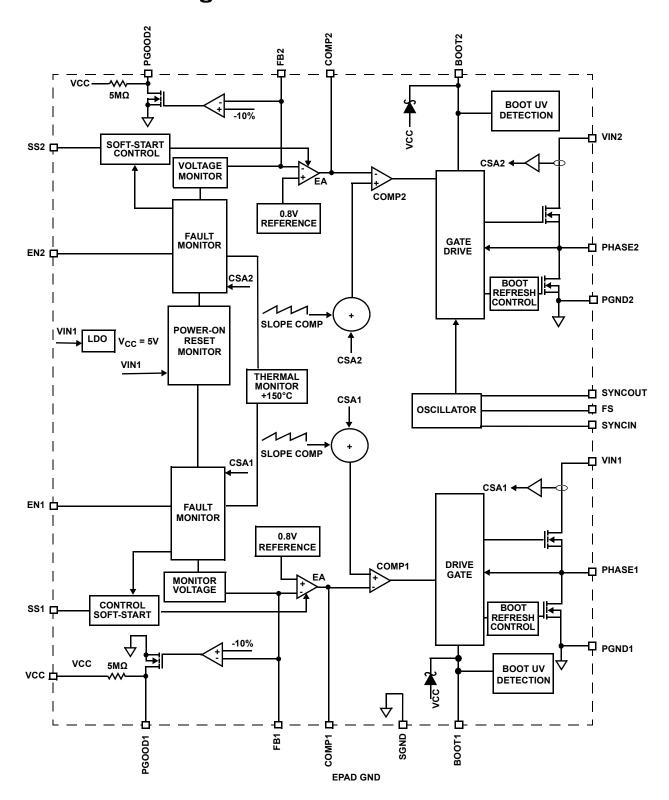

# **Functional Block Diagram**

## ISL85033

# **Ordering Information**

| PART NUMBER             | PART    | TEMP. RANGE | PACKAGE    | PKG.    |

|-------------------------|---------|-------------|------------|---------|

| (Notes 1, 2, 3)         | MARKING | (°C)        | (Pb-Free)  | DWG. #  |

| ISL85033IRTZ 850 33IRTZ |         | -40 to +85  | 28 Ld TQFN | L28.4x4 |

#### NOTES:

- 1. Add "-T\*" suffix for Tape and Reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL85033. For more information on MSL please see techbrief TB363.

## ISL85033

# **Table of Contents**

| Absolute Maximum Ratings                  | 8    |

|-------------------------------------------|------|

| Thermal Information                       | 8    |

| Recommended Operating Conditions          | 8    |

| Electrical Specifications                 | 8    |

| Detailed Description                      | . 16 |

| Operation Initialization                  | . 16 |

| Power-On Reset and Undervoltage Lockout   | 16   |

| Enable and Disable                        |      |

| Power Good                                | 16   |

| Output Voltage Selection                  | 16   |

| Output Tracking and Sequencing            | . 16 |

| Protection Features                       | . 17 |

| Buck Regulator Overcurrent Protection     |      |

| Thermal Overload Protection               |      |

| BOOT Undervoltage Protection.             |      |

| Application Guidelines                    |      |

| Operating Frequency                       |      |

| Synchronization Control                   |      |

| Output Inductor Selection                 |      |

| Buck Regulator Output Capacitor Selection |      |

| Current Sharing Configuration             |      |

| Input Capacitor Selection                 |      |

| Loop Compensation Design                  | 19   |

| Theory of Compensation                    | 20   |

| PWM Comparator Gain Fm                    |      |

| Power Stage Transfer Functions            | 20   |

| Rectifier Selection                       |      |

| Power Derating Characteristics            |      |

| Layout Considerations                     | 22   |

| Revision History                          | 24   |

|                                           | . 24 |

| Products                                  |      |

## **Absolute Maximum Ratings**

| VIN1/2 to GND                          | 0.3V to +30V                   |

|----------------------------------------|--------------------------------|

| PHASE1/2 to GND                        | 7V (<10ns) /-0.3V (DC) to +33V |

| BOOT1/2 to PHASE1/2                    | 0.3V to +5.9V                  |

| FS to GND                              | 0.3V to +5.9V                  |

| SYNCIN to GND                          | 0.3V to +5.9V                  |

| FB1/2 to GND                           | 0.3V to +2.95V                 |

| EN1/2 to GND                           | 0.3V to +5.9V                  |

| PG00D1/2 to GND                        | 0.3V to +5.9V                  |

| COMP1/2 to GND                         | 0.3V to +5.9V                  |

| VCC to GND Short Maximum Duration      |                                |

| SYNCOUT to GND                         | 0.3V to +5.9V                  |

| SS1/2 to GND                           | 0.3V to +5.9V                  |

| ESD Rating                             |                                |

| Human Body Model (Tested per JESD      | 22-A114)                       |

| Charged Device Model (Tested per JE    | SD22-C101E)2.2kV               |

| Machine Model (Tested per JESD22-A     | 115)                           |

| Latch Up (Tested per JESD-78A; Class 2 | , Level A) 100mA               |

|                                        |                                |

#### **Thermal Information**

| Thermal Resistance                        | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-------------------------------------------|----------------------|----------------------|

| QFN Package (Notes 4, 5)                  | 38                   | 3                    |

| Maximum Junction Temperature (Plastic Pac | kage)                | +150°C               |

| Maximum Storage Temperature Range         | 6!                   | 5°C to +150°C        |

| Ambient Temperature Range                 |                      | 40°C to +85°C        |

| Junction Temperature Range                | 5!                   | 5°C to +150°C        |

| Operating Temperature Range               |                      | 40°C to +85°C        |

| Pb-Free Reflow Profile                    |                      | see link below       |

| http://www.intersil.com/pbfree/Pb-FreeRe  | eflow.asp            |                      |

#### **Recommended Operating Conditions**

| Temperature    | °C to +85°C |

|----------------|-------------|

| Supply Voltage | 4.5V to 28V |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379 for details.

- 5. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications**  $T_A = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ,  $V_{\text{IN}} = 4.5 \text{V}$  to 28V, unless otherwise noted. Typical values are at  $T_A = +25 \,^{\circ}\text{C}$ . Boldface limits apply over the operating temperature range, -40  $^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$

| PARAMETER                                | SYMBOL           | TEST CONDITIONS                               | MIN<br>(Note 8) | TYP  | MAX<br>(Note 8) | UNITS |

|------------------------------------------|------------------|-----------------------------------------------|-----------------|------|-----------------|-------|

| SUPPLY VOLTAGE                           | <u>'</u>         |                                               | -               | 1    |                 |       |

| V <sub>IN</sub> Voltage Range            | VIN              |                                               | 4.5             |      | 28              | ٧     |

| V <sub>IN</sub> Quiescent Supply Current | IQ               |                                               |                 | 1.2  | 2.2             | mA    |

| V <sub>IN</sub> Shutdown Supply Current  | I <sub>SD</sub>  | EN1/2 = 0V                                    |                 | 20   | 45              | μΑ    |

| V <sub>CC</sub> Voltage                  | V <sub>CC</sub>  | V <sub>IN</sub> = 12V; I <sub>OUT</sub> = 0mA | 4.5             | 5.1  | 5.6             | ٧     |

| POWER-ON RESET                           |                  |                                               |                 |      |                 |       |

| VIN POR Threshold                        |                  | Rising Edge                                   |                 | 3.9  | 4.4             | ٧     |

|                                          |                  | Falling Edge                                  | 3.2             | 3.7  |                 | V     |

| OSCILLATOR                               | 1                |                                               |                 | 11   |                 |       |

| Nominal Switching Frequency              | F <sub>SW</sub>  | FS = VCC                                      | 420             | 500  | 580             | kHz   |

|                                          |                  | Resistor from FS to GND = $383$ k $\Omega$    |                 | 300  |                 | kHz   |

|                                          |                  | Resistor from FS to GND = $40.2$ k $\Omega$   |                 | 2000 |                 | kHz   |

| FS Voltage                               | V <sub>FS</sub>  | FS = 100kΩ                                    | 780             | 800  | 820             | mV    |

| Switching Frequency                      |                  | SYNCIN = 600kHz                               |                 | 300  |                 | kHz   |

|                                          |                  | 1.2MHz ≤ SYNCIN ≤ 4MHz                        | 600             |      | 2000            | kHz   |

| Minimum Off-Time                         | t <sub>OFF</sub> |                                               |                 | 130  |                 | ns    |

| ERROR AMPLIFIER                          |                  |                                               |                 |      |                 |       |

| Error Amplifier Transconductance Gain    | gm               |                                               | 125             | 205  | 285             | μA/V  |

| FB1, FB2 Leakage Current                 |                  | VFB = 0.8V                                    |                 | 10   | 100             | nA    |

| Current Sense Amplifier Gain             | R <sub>T</sub>   |                                               | 0.18            | 0.21 | 0.24            | V/A   |

| Reference Voltage                        |                  |                                               | 0.792           | 0.8  | 0.808           | V     |

| Soft-Start Ramp Time                     |                  | SS1/2 = VDD                                   | 1.5             | 2.5  | 3.5             | ms    |

| Soft-Start Charging Current              | I <sub>SS</sub>  |                                               | 1.4             | 2    | 2.6             | μΑ    |

## ISL85033

**Electrical Specifications**  $T_A = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ,  $V_{\text{IN}} = 4.5 \text{V}$  to 28V, unless otherwise noted. Typical values are at  $T_A = +25 \,^{\circ}\text{C}$ . Boldface limits apply over the operating temperature range, -40  $^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  (Continued)

| PARAMETER                             | SYMBOL            | TEST CONDITIONS                                                | MIN<br>(Note 8)       | TYP                   | MAX<br>(Note 8) | UNITS |

|---------------------------------------|-------------------|----------------------------------------------------------------|-----------------------|-----------------------|-----------------|-------|

| POWER-GOOD                            |                   |                                                                |                       |                       |                 |       |

| PG1, PG2 Trip Level PG to PG00D1,     |                   | Rise                                                           |                       | 91                    | 94              | %     |

| PGOOD2                                |                   | Fall                                                           | 82.5                  | 85.5                  |                 | %     |

| PG1, PG2 Propagation Delay            |                   | Percentage of the soft-start time                              |                       | 10                    |                 | %     |

| PG1, PG2 Low Voltage                  |                   | ISINK = 3mA                                                    |                       | 100                   | 300             | m۷    |

| ENABLE INPUT                          | 1                 |                                                                |                       | I .                   | I.              |       |

| EN1, EN2 Leakage Current              |                   | EN1/2 = 0V/5V                                                  | -1                    |                       | 1               | μΑ    |

| EN1, EN2 Input Threshold Voltage      |                   | Low Level                                                      |                       |                       | 0.8             | V     |

|                                       |                   | Float Level                                                    | 1.0                   |                       | 1.4             | V     |

|                                       |                   | High Level                                                     | 2                     |                       |                 | V     |

| SYNC INPUT/OUTPUT                     |                   | 1                                                              |                       |                       |                 |       |

| SYNCIN Input Threshold                |                   | Falling Edge                                                   | 1.1                   | 1.4                   |                 | V     |

|                                       |                   | Rising Edge                                                    |                       | 1.6                   | 1.9             | V     |

|                                       |                   | Hysteresis                                                     |                       | 200                   |                 | m۷    |

| SYNCIN Leakage Current                |                   | SYNCIN = 0V/5V                                                 |                       | 10                    | 1000            | nA    |

| SYNCIN Pulse Width                    |                   |                                                                | 100                   |                       |                 | ns    |

| SYNCOUT Phase-shift to SYNCIN         |                   | Measured from rising edge to rising edge, if duty cycle is 50% |                       | 180                   |                 | ٥     |

| SYNCOUT Frequency Range               |                   |                                                                | 600                   |                       | 4000            | kHz   |

| SYNCOUT Output Voltage High           |                   | ISYNCOUT = 3mA                                                 | V <sub>CC</sub> - 0.3 | V <sub>CC</sub> -0.08 |                 | V     |

| SYNCOUT Output Voltage Low            |                   |                                                                |                       | 0.08                  | 0.3             | V     |

| FAULT PROTECTION                      | 1                 |                                                                | "                     | i.                    |                 |       |

| Thermal Shutdown Temperature          | T <sub>SD</sub>   | Rising Threshold                                               |                       | 150                   |                 | °C    |

|                                       | T <sub>HYS</sub>  | Hysteresis                                                     |                       | 20                    |                 | °C    |

| Overcurrent Protection Threshold      |                   | (Note 7)                                                       | 4.1                   | 5.1                   | 6.1             | Α     |

| OCP Blanking Time                     |                   |                                                                |                       | 60                    |                 | ns    |

| POWER MOSFET                          | I                 | ,                                                              | 1                     | II.                   | I.              |       |

| Highside                              | R <sub>HDS</sub>  | I <sub>PHASE</sub> = 100mA                                     |                       | 75                    | 150             | mΩ    |

| Internal BOOT1, BOOT2 Refresh Lowside | R <sub>LDS</sub>  | I <sub>PHASE</sub> = 100mA                                     |                       | 1                     |                 | Ω     |

| PHASE Leakage Current                 |                   | EN1/2 = PHASE1/2 = 0V                                          |                       |                       | 300             | nA    |

| PHASE Rise Time                       | t <sub>RISE</sub> | V <sub>IN</sub> = 25V                                          |                       | 10                    |                 | ns    |

#### NOTES:

- 6. Test Condition: V<sub>IN</sub> = 28V, FB forced above regulation point (0.8V), no switching, and power MOSFET gate charging current not included.

- 7. Established by both current sense amplifier gain test and current sense amplifier output test @  $I_L$  = 0A.

- 8. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

#

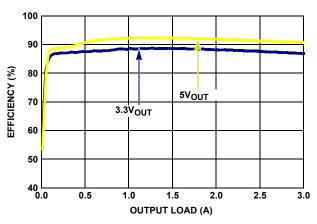

FIGURE 4. EFFICIENCY vs LOAD, T<sub>A</sub> = +25°C, V<sub>IN</sub> = 28V

FIGURE 5. EFFICIENCY vs LOAD,  $T_A = +25 \,^{\circ}$  C,  $F_{SW} = 500 \, \text{kHz}$ ,  $V_{IN} = 12 \,^{\circ}$

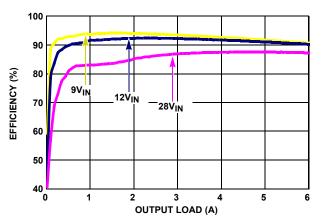

FIGURE 6. EFFICIENCY vs LOAD,  $T_A$  = +25 ° C, CURRENT SHARING 5V<sub>OUT</sub>,  $F_{SW}$  = 500kHz

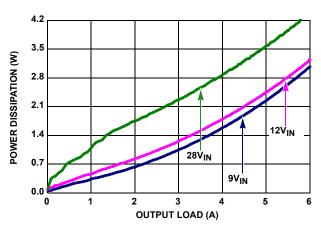

FIGURE 7. POWER DISSIPATION vs LOAD,  $T_A = +25$  °C, CURRENT SHARING 5V<sub>OUT</sub>,  $F_{SW} = 500 \text{kHz}$

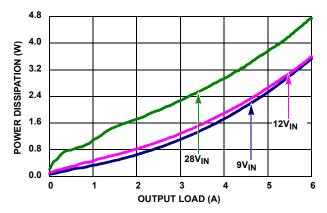

FIGURE 8. POWER DISSIPATION vs LOAD,  $T_A = +85^{\circ}$  C, CURRENT SHARING 5V<sub>OUT</sub>,  $F_{SW} = 500$ kHz

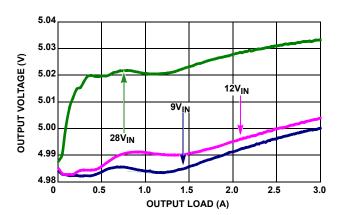

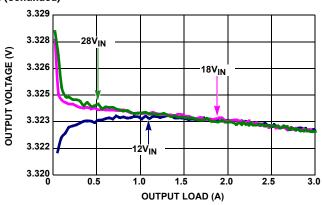

FIGURE 9.  $V_{OUT}$  REGULATION vs LOAD, CHANNEL 1,  $T_A = +25\,^{\circ}$ C,  $5V_{OUT}$ ,  $F_{SW} = 500$ kHz

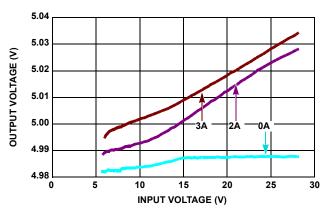

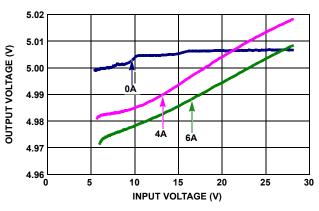

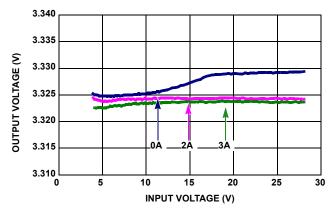

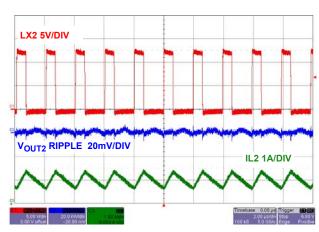

**Typical Performance Curves** Circuit of Figure 2.  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$ ,  $I_{OUT1} = 3A$ ,  $I_{OUT2} = 3A$ ,  $I_{A} = -40$  °C to +85 °C, unless otherwise noted. Typical values are at  $I_{A} = +25$  °C. (Continued)

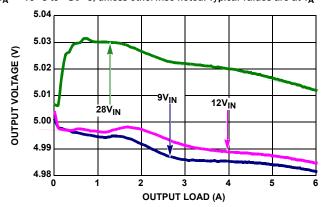

FIGURE 10.  $V_{OUT}$  REGULATION vs LOAD, CURRENT SHARING,  $T_A = +25\,^{\circ}\text{C}$ ,  $5V_{OUT}$ ,  $F_{SW} = 500\text{kHz}$

FIGURE 11.  $V_{OUT}$  REGULATION vs LOAD, CHANNEL 2,  $T_A$  = +25°C, 3.3 $V_{OUT}$ ,  $F_{SW}$  = 500kHz

FIGURE 12. OUTPUT VOLTAGE REGULATION vs  $V_{IN}$ , CHANNEL 1,  $T_A = +25\,^{\circ}\text{C}$ ,  $5V_{OUT}$ ,  $F_{SW} = 500\text{kHz}$

FIGURE 13. OUTPUT VOLTAGE REGULATION vs  $V_{IN}$ , CURRENT SHARING,  $T_A = +25\,^{\circ}$ C,  $5V_{OUT}$ ,  $F_{SW} = 500$ kHz

FIGURE 14. OUTPUT VOLTAGE REGULATION vs  $V_{IN}$ , CHANNEL 2,  $T_A = +25\,^{\circ}\text{C}$ , 3.3 $V_{OUT}$ ,  $F_{SW} = 500\text{kHz}$

FIGURE 15. STEADY STATE OPERATION AT NO LOAD CHANNEL 1

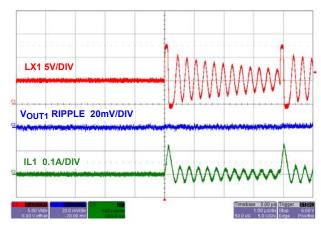

**Typical Performance Curves** Circuit of Figure 2.  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$ ,  $I_{OUT1} = 3A$ ,  $I_{OUT2} = 3A$ ,  $I_{OUT3} = 3A$ ,  $I_{OUT3} = 3A$ ,  $I_{OUT4} = 3A$ ,  $I_{OUT5} = 3A$ ,  $I_{O$

FIGURE 16. STEADY STATE OPERATION AT NO LOAD CHANNEL 1 ( $V_{\rm IN}=9V$ )

FIGURE 17. STEADY STATE OPERATION AT NO LOAD CHANNEL 2

FIGURE 18. STEADY STATE OPERATION WITH FULL LOAD CHANNEL 1

FIGURE 19. STEADY STATE OPERATION WITH FULL LOAD CHANNEL 2

FIGURE 20. STEADY STATE OPERATION WITH FULL LOAD CURRENT SHARING

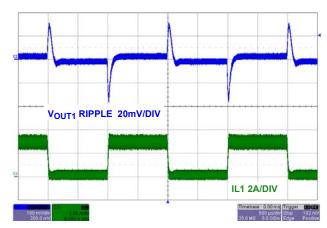

FIGURE 21. LOAD TRANSIENT CHANNEL 1

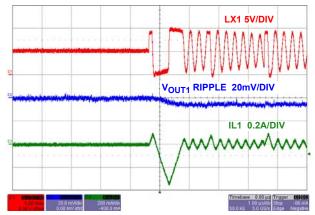

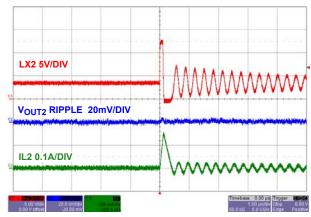

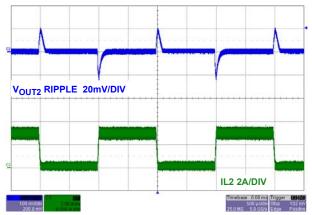

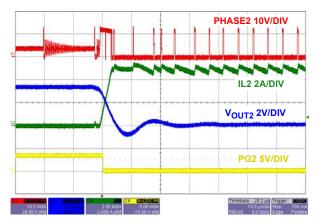

**Typical Performance Curves** Circuit of Figure 2.  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$ ,  $I_{OUT1} = 3A$ ,  $I_{OUT2} = 3A$ ,  $I_{A} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $I_{A} = +25$ °C. (Continued)

FIGURE 22. LOAD TRANSIENT CHANNEL 2

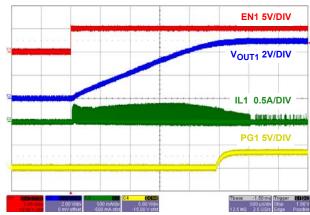

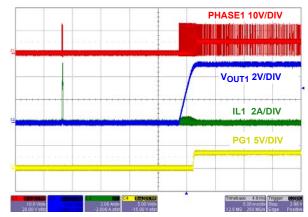

FIGURE 23. SOFT-START WITH NO LOAD CHANNEL 1

FIGURE 24. SOFT-START WITH NO LOAD CHANNEL 2

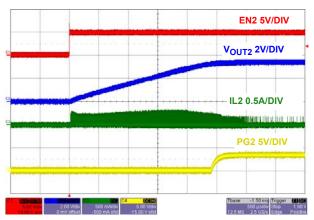

FIGURE 25. SOFT-START AT FULL LOAD CHANNEL 1

FIGURE 26. SOFT-START AT FULL LOAD CHANNEL 2

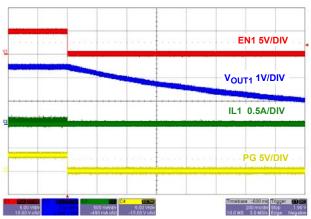

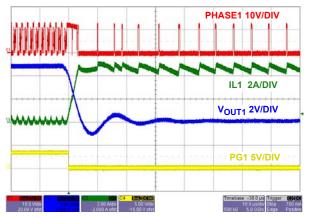

FIGURE 27. SOFT-DISCHARGE SHUTDOWN CHANNEL 1

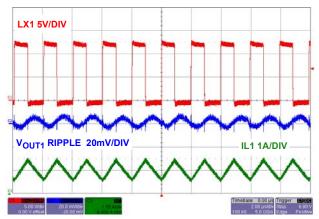

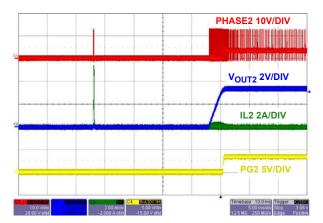

**Typical Performance Curves** Circuit of Figure 2.  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$ ,  $I_{OUT1} = 3A$ ,  $I_{OUT2} = 3A$ ,  $I_{OUT3} = 3A$ ,  $I_{OUT3} = 3A$ ,  $I_{OUT4} = 3A$ ,  $I_{OUT5} = 3A$ ,  $I_{O$

FIGURE 28. SOFT-DISCHARGE SHUTDOWN CHANNEL 2

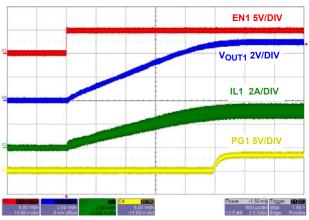

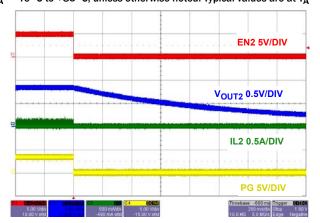

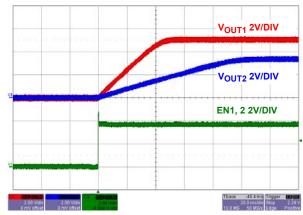

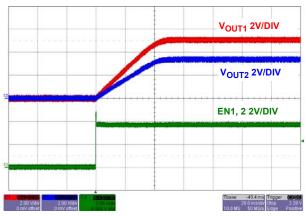

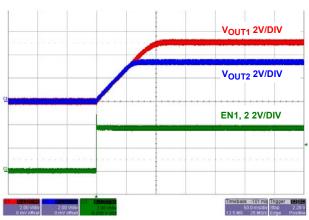

FIGURE 29. INDEPENDENT START-UP SEQUENCING AT NO LOAD

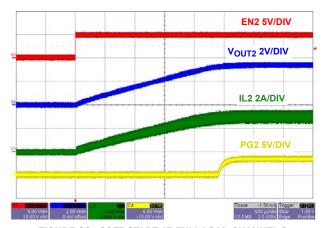

FIGURE 30. RATIOMETRIC START-UP SEQUENCING AT NO LOAD

FIGURE 31. ABSOLUTE START-UP SEQUENCING AT NO LOAD

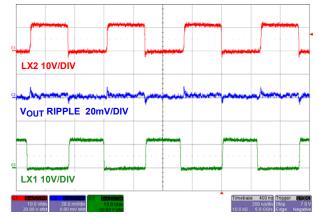

FIGURE 32. STEADY STATE OPERATION CHANNEL 1 AT FULL LOAD WITH SYNC FREQUENCY = 4MHz

FIGURE 33. STEADY STATE OPERATION CHANNEL 2 AT FULL LOAD WITH SYNC FREQUENCY = 4MHz

**Typical Performance Curves** Circuit of Figure 2.  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$ ,  $I_{OUT1} = 3A$ ,  $I_{OUT2} = 3A$ ,  $I_{A} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $I_{A} = +25$ °C. (Continued)

FIGURE 34. OUTPUT SHORT CIRCUIT CHANNEL 1

FIGURE 35. OUTPUT SHORT CIRCUIT HICCUP AND RECOVERY FOR CHANNEL 1

FIGURE 36. OUTPUT SHORT CIRCUIT CHANNEL 2

FIGURE 37. OUTPUT SHORT CIRCUIT HICCUP AND RECOVERY FOR CHANNEL 2

## **Detailed Description**

The ISL85033 combines a standard buck PWM controller with an integrated switching MOSFET. The buck controller drives an internal N-Channel MOSFET and requires an external diode to deliver load current up to 3A. A Schottky diode is recommended for improved efficiency and performance over a standard diode. The standard buck regulator can operate from an unregulated DC source, such as a battery, with a voltage ranging from +4.5V to +28V. The converter output can be regulated to as low as 0.8V. These features make the ISL85033 ideally suited for FPGA, set-top boxes, LCD panels, DVD drives, and wireless chipset power applications.

The ISL85033 employs a peak current mode control loop which simplifies feedback loop compensation and rejects input voltage variation. External feedback loop compensation allows flexibility in output filter component selection. The regulator switches at a default 500kHz and it can be adjusted from 300kHz to 2MHz with a resistor from FS to GND. The ISL85033 is also synchronizable from 300kHz to 2MHz.

## **Operation Initialization**

The power-ON reset circuitry and enable inputs prevent false start-up of the PWM regulator output. Once all input criteria are met, the controller soft-starts the output voltage to the programmed level.

### **Power-On Reset and Undervoltage Lockout**

The ISL85033 automatically initializes upon receipt of input power supply. The power-on reset (POR) function continually monitors VIN1 voltage. While below the POR threshold, the controller inhibits switching of the internal power MOSFET. Once exceeded, the controller initializes the internal soft-start circuitry. If VIN1 supply drops below their falling POR threshold during soft-start or operation, the buck regulator is disabled until the input voltage returns.

#### **Enable and Disable**

When EN1 and EN2 are pulled low, the device enters shutdown mode and the supply current drops to a typical value of  $20\mu A$ . All internal power devices are held in a high-impedance state while in shutdown mode.

The EN pin enables the controller of the ISL85033. When the voltage on the EN pin exceeds its logic rising threshold, the controller initiates the 2ms soft-start function for the PWM regulator. If the voltage on the EN pin drops below the falling threshold, the buck regulator shuts down.

If EN1, EN2 pins are driven by an external signal, the minimum off-time for EN1, EN2 should be:

$$\label{eq:en_to_sol_energy} \text{EN\_T\_off } (\mu \text{s}) \, = \, 10\,\mu \text{s} \bullet \text{C}_{\text{SS}} / 2.2 \text{nF} \tag{EQ. 1}$$

where  $C_{SS}$  is the soft-start pin capacitor (nF). ISL85033 does not have debouncing to EN1, EN2 external signals.

#### **Power Good**

PG is the open-drain output of a window comparator that continuously monitors the buck regulator output voltage via the FB pin. PG is actively held low when EN is low and during the buck

regulator soft-start period. After the soft-start period terminates, PG becomes high impedance as long as the output voltage (monitored on the FB pin) is above 90% of the nominal regulation voltage set by FB. When  $V_{OUT}$  drops 10% below the nominal regulation voltage, the ISL85033 pulls PG low. Any fault condition forces PG low until the fault condition is cleared by attempts to soft-start. There is an internal  $5 \mathrm{M}\Omega$  internal pull-up resistor.

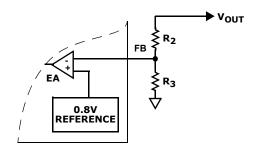

#### **Output Voltage Selection**

The regulator output voltages is easily programmed using an external resistor divider to scale V<sub>OUT</sub> relative to the internal reference voltage. The scaled voltage is applied to the inverting input of the error amplifier; refer to Figure 38.

The output voltage programming resistor,  $R_2$ , depends on the value chosen for the feedback resistor,  $R_3$ , and the desired output voltage,  $V_{OUT}$ , of the regulator. Equation 2 describes the relationship between  $V_{OUT}$  and resistor values.  $R_3$  is often chosen to be in the  $1 \text{k}\Omega$  to  $10 \text{k}\Omega$  range.

$$R_2 = (V_{OUT} - 0.8) \cdot R_3 / 0.8$$

(EQ. 2)

If the desired output voltage is 0.8V, then  $R_3$  is left unpopulated and  $R_2$  is zero ohm.

FIGURE 38. EXTERNAL RESISTOR DIVIDER

# **Output Tracking and Sequencing**

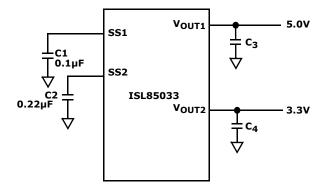

Output tracking and sequencing between channels can be implemented by using the SS1 and SS2 pins. Figures 39, 40 and 41 show several configurations for output tracking/sequencing for a 2.5V and 1.8V application. Independent soft-start for each channel is shown in Figure 39 and measured in Figure 29. The output ramp-time for each channel ( $t_{SS}$ ) is set by the soft-start capacitor ( $t_{SS}$ ).

$$c_{SS}[\mu F] = 2.5 * t_{SS}(s)$$

(EQ. 3)

Maximum C<sub>SS</sub> value is 50nF.

Ratiometric tracking is achieved in Figure 40 by using the same value for the soft-start capacitor on each channel; it is measured in Figure 30.

By connecting a feedback network from  $V_{OUT1}$  to the SS2 pin with the same ratio that sets  $V_{OUT2}$  voltage, absolute tracking shown in Figure 41 is implemented. The measurement is shown in Figure 31. If the output of Channel 1 is shorted to GND, it will enter overcurrent hiccup mode, SS2 will be pulled low through the added resistor between VOUT1 and SS2 and this will force Channel 2 into hiccup as well. If the output of Channel 2 is

shorted to GND with VOUT1 in regulation, it will enter overcurrent hiccup mode with a very short hiccup waiting time. The reason is that VOUT1 is still in regulation and can pull-up SS2 very quickly via the resistor added between VOUT1 and SS2.

Figure 42 illustrates output sequencing. When EN1 is high and EN2 is floating, OUT1 comes up first and OUT2 won't start until OUT1 > 90% of its regulation point. If EN1 is floating and EN2 is high, OUT2 comes up first and OUT1 won't start until OUT2 > 90% of its regulation point. If EN1 = EN2 = high, OUT1 and OUT2 come up at the same time. Please refer to Table 1 for conditions related to Figure 42 (Output Sequencing).

**TABLE 1. OUTPUT SEQUENCING**

| EN1      | EN2      | V <sub>OUT1</sub> V <sub>OUT2</sub> |                                   | NOTE           |

|----------|----------|-------------------------------------|-----------------------------------|----------------|

| High     | Floating | First After V <sub>OUT1</sub> > 90% |                                   |                |

| Floating | High     | After V <sub>OUT2</sub> > 90%       | First                             |                |

| High     | High     | Same time<br>as V <sub>OUT2</sub>   | Same time<br>as V <sub>OUT1</sub> |                |

| Floating | Floating |                                     |                                   | Not<br>Allowed |

FIGURE 39. INDEPENDENT START-UP

FIGURE 40. RATIOMETRIC START-UP

FIGURE 41. ABSOLUTE START-UP

FIGURE 42. OUTPUT SEQUENCING

## **Protection Features**

The ISL85033 limits the current in all on-chip power devices. Overcurrent protection limits the current on the two buck regulators and internal LDO for  $V_{CC}$ .

### **Buck Regulator Overcurrent Protection**

During the PWM on-time, the current through the internal switching MOSFET is sampled and scaled through an internal pilot device. The sampled current is compared to a nominal 5A overcurrent limit. If the sampled current exceeds the overcurrent limit reference level, an internal overcurrent fault counter is set to 1 and an internal flag is set. The internal power MOSFET is immediately turned off and will not be turned on again until the next switching cycle.

The protection circuitry continues to monitor the current and turns off the internal MOSFET as described. If the overcurrent condition persists for 17 sequential clock cycles, the overcurrent fault counter overflows indicating an overcurrent fault condition exists. The regulator is shut down and power-good goes low.

The buck controller attempts to recover from the overcurrent condition after waiting 8 soft-start cycles. The internal overcurrent flag and counter are reset. A normal soft-start cycle is attempted and normal operation continues if the fault

condition has cleared. If the overcurrent fault counter overflows during soft-start, the converter shuts down and this hiccup mode operation repeats.

#### **Thermal Overload Protection**

Thermal overload protection limits maximum junction temperature in the ISL85033. When the junction temperature  $(T_J)$  exceeds  $+150\,^{\circ}$  C, a thermal sensor sends a signal to the fault monitor.

The fault monitor commands the buck regulator to shut down. When the junction temperature has decreased by 20 °C, the regulator will attempt a normal soft-start sequence and return to normal operation. For continuous operation, the +125 °C junction temperature rating should not be exceeded.

### **BOOT Undervoltage Protection**

If the BOOT capacitor voltage falls below 2.5V, the BOOT undervoltage protection circuit will pull the phase pin low through a  $1\Omega$  switch for 400ns to recharge the capacitor. This operation may arise during long periods of no switching as in no load situations.

## **Application Guidelines**

#### **Operating Frequency**

The ISL85033 operates at a default switching frequency of 500kHz if FS is tied to VCC. Tie a resistor from FS to GND to program the switching frequency from 300kHz to 2MHz, as shown in Equation 4.

$$R_{\text{FS}}[k\Omega] = 122k\Omega^*(t - 0.17\mu\text{s}) \tag{EQ. 4}$$

#### Where:

t is the switching period in µs.

FIGURE 43. R<sub>FS</sub> SELECTION vs FS

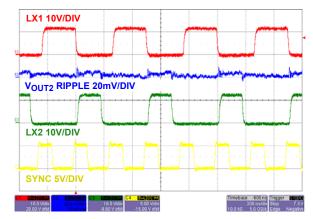

#### **Synchronization Control**

The frequency of operation can be synchronized up to 2MHz by an external signal applied to the SYNCIN pin. The falling edge on the SYNCIN triggers the rising edge of PHASE1/2. The switching frequency for each output is half of the SYNCIN frequency.

#### **Output Inductor Selection**

The inductor value determines the converter's ripple current. Choosing an inductor current requires a somewhat arbitrary choice of ripple current,  $\Delta I$ . A reasonable starting point is 30% of total load current. The inductor value can then be calculated using Equation 5:

$$L = \frac{V_{IN} - V_{OUT}}{Fs \times \Delta I} \times \frac{V_{OUT}}{V_{IN}}$$

(EQ. 5)

Increasing the value of inductance reduces the ripple current and thus ripple voltage. However, the larger inductance value may reduce the converter's response time to a load transient. The inductor current rating should be such that it will not saturate in overcurrent conditions.

#### **Buck Regulator Output Capacitor Selection**

An output capacitor is required to filter the inductor current. Output ripple voltage and transient response are 2 critical factors when considering output capacitance choice. The current mode control loop allows the usage of low ESR ceramic capacitors and thus smaller board layout. Electrolytic and polymer capacitors may also be used.

Additional consideration applies to ceramic capacitors. While they offer excellent overall performance and reliability, the actual in-circuit capacitance must be considered. Ceramic capacitors are rated using large peak-to-peak voltage swings and with no DC bias. In the DC/DC converter application, these conditions do not reflect reality. As a result, the actual capacitance may be considerably lower than the advertised value. Consult the manufacturers data sheet to determine the actual in-application capacitance. Most manufacturers publish capacitance vs DC bias so that this effect can be easily accommodated. The effects of AC voltage are not frequently published, but an assumption of ~20% further reduction will generally suffice. The result of these considerations can easily result in an effective capacitance 50% lower than the rated value. Nonetheless, they are a very good choice in many applications due to their reliability and extremely low ESR.

The following equations allow calculation of the required capacitance to meet a desired ripple voltage level. Additional capacitance may be used.

For the ceramic capacitors (low ESR): =

$$V_{OUTripple} = \frac{\Delta I}{8*F_{SW}*C_{OUT}}$$

(EQ. 6)

where  $\Delta I$  is the inductor's peak to peak ripple current,  $F_{SW}$  is the switching frequency and  $C_{OUT}$  is the output capacitor.

If using electrolytic capacitors then:

$$V_{OUTripple} = \Delta I * ESR$$

(EQ. 7)

Regarding transient response needs, a good starting point is to determine the allowable overshoot in  $V_{OUT}$  if the load is suddenly removed. In this case, energy stored in the inductor will be transferred to  $C_{OUT}$  causing its voltage to rise. After calculating capacitance required for both ripple and transient needs, choose the larger of the calculated values. The following equation determines the required output capacitor value in order to achieve a desired overshoot relative to the regulated voltage.

$$c_{\text{OUT}} = \frac{I_{\text{OUT}}^2 * L}{V_{\text{OUT}}^2 * (V_{\text{OUTMAX}} / V_{\text{OUT}})^2 - 1)}$$

(EQ. 8)

where  $V_{OUTMAX}/V_{OUT}$  is the relative maximum overshoot allowed during the removal of the load. For an overshoot of 5%, the equation becomes:

$$c_{OUT} = \frac{I_{OUT}^2 * L}{V_{OUT}^2 * (1.05^2 - 1)}$$

(EQ. 9)

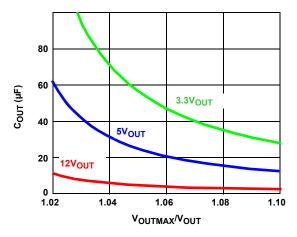

The graph in Figure 44 shows the relationship of  $C_{OUT}$  and % overshoot at 3 different output voltages. L is assumed to be  $7\mu H$  and  $I_{OUT}$  is 3A.

FIGURE 44. C<sub>OUT</sub> vs OVERSHOOT V<sub>OUTMAX</sub>/V<sub>OUT</sub>

#### **Current Sharing Configuration**

In current sharing configuration, FB1 is connected to FB2, EN1 to EN2, COMP1 to COMP2 and VOUT1 to VOUT2 as shown in Figure 3. As a result, the equivalent gm doubles its single channel value. Since the two channels are out-of-phase, the frequency will be 2X the channel switching frequency. Ripple current cancellation will reduce the ripple current seen by the output capacitors and thus lower the ripple voltage. This results in the ability to use less capacitance than would be required by a single phase design of similar rating. Ripple current cancellation also reduces the ripple current seen at the input capacitors.

#### **Input Capacitor Selection**

To reduce the resulting input voltage ripple and to minimize EMI by forcing the very high frequency switching current into a tight local loop, an input capacitor is required. The input capacitor must have adequate ripple current rating which can be approximated by the Equation 10.

If capacitors other than MLCC are used, attention must be paid to ripple and surge current ratings.

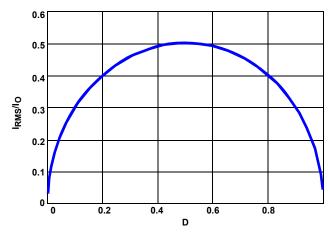

$$\frac{I_{RMS}}{I_0} = \sqrt{D - D^2}$$

(EQ. 10)

where D =  $V_0/V_{IN}$

The input ripple current is graphically represented in Figure 45.

FIGURE 45. IRMS/IO vs DUTY CYCLE

A minimum of  $10\mu F$  ceramic capacitance is required on each VIN pin. The capacitors must be as close to the IC as physically possible. Additional capacitance may be used.

#### **Loop Compensation Design**

ISL85033 uses a constant frequency current mode control architecture to achieve simplified loop compensation and fast loop transient response.

The compensator schematic is shown in Figure 47. As mentioned in the COUT selection, ISL85033 allows the usage of low ESR output capacitor. Choice of the loop bandwidth  $f_{\rm C}$  is somewhat arbitrary but should not exceed 1/4 of the switching frequency. As a starting point, the lower of 100kHz or 1/6 of the switching frequency is reasonable. The following equations determine initial component values for the compensation, allowing the designer to make the selection with minimal effort. Further detail is provided in "Theory of Compensation" on page 20 to allow fine tuning of the compensator.

Compensation resistor R1 is given by Equation 11:

$$R_{1} = \frac{2\pi f_{c}V_{o}C_{o}R_{T}}{g_{m}V_{FB}}$$

(EQ. 11)

which when applied to ISL85033 becomes:

$$R_{1}[k\Omega] = 0.008247*f_{c}*V_{o}*C_{o}$$

(EQ. 12)

where  $C_0$  is the output capacitor value [ $\mu$ F],  $f_C$  = loop bandwidth [kHz] and  $V_0$  is the output voltage [V].

Compensation capacitors C1 [nF], C2 [pF] are given by Equation 13:

$$C_{1} = \frac{C_{0} \times V_{0} \times (10)^{3}}{I_{0} \times R_{1}}, C_{2} = \frac{C_{0} \times R_{c} \times (10)^{6}}{R_{1}}$$

(EQ. 13)

where Io [A] is the output load current,  $R_1(\Omega)$  and  $Rc(\Omega)$  is the ESR of the output capacitor Co.

Example: V<sub>0</sub> = 5V, I<sub>0</sub> = 3A, f<sub>S</sub> = 500kHz, f<sub>C</sub> = 50kHz, C<sub>0</sub> =  $47\mu F/R_C$  =  $5m\Omega$ , then the compensation resistance R<sub>1</sub> =  $96k\Omega$ .

The compensation capacitors are:

$C_1$  = 815pF,  $C_2$  = 2.5pF (There is approximately 3pF parasitic capacitance from  $V_{COMP}$  to GND; therefore,  $C_2$  is optional).

#### **Theory of Compensation**

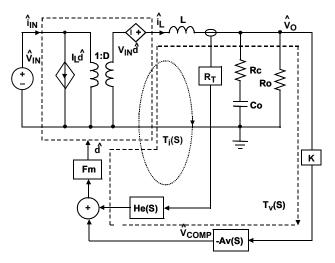

The sensed current signal is injected into the voltage loop to achieve current mode control to simplify the loop compensation design. The inductor is not considered as a state variable for current mode control and the system becomes a single order system. It is much easier to design a compensator to stabilize the voltage loop than voltage mode control. Figure 46 shows the small signal model of the synchronous buck regulator.

FIGURE 46. SMALL SIGNAL MODEL OF SYNCHRONOUS BUCK REGULATOR

#### **PWM Comparator Gain F<sub>m</sub>**

The PWM comparator gain  $\mathbf{F}_{\mathbf{m}}$  for peak current mode control is given by Equation 14:

$$F_{m} = \frac{d}{\hat{v}_{comp}} = \frac{1}{(S_{e} + S_{n})T_{s}}$$

(EQ. 14)

Where  $\mathbf{S}_{e}$  is the slew rate of the slope compensation and  $\mathbf{S}_{n}$  is given by Equation 15.

$$S_n = R_t \frac{V_{in} - V_0}{L}$$

(EQ. 15)

Where:

$R_{T}$  is trans-resistance, and is the product of the current sensing resistance and gain of the current amplifier in current loop.

#### **CURRENT SAMPLING TRANSFER FUNCTION He(S)**

In current loop, the current signal is sampled every switching cycle. Equation 16 shows the transfer function:

$$H_{e}(S) = \frac{S^{2}}{\omega_{n}^{2}} + \frac{S}{\omega_{n}Q_{n}} + 1$$

(EQ. 16)

Where  $\textbf{Q}_{\textbf{n}}$  and  $\boldsymbol{\omega}_{\textbf{n}}$  are given by  $\,\textbf{Q}_{\textbf{n}} = -\frac{2}{\pi}, = \, \boldsymbol{\omega}_{\textbf{n}} = \, \pi \textbf{f}_{\textbf{s}} \, .$

#### **Power Stage Transfer Functions**

Transfer function  $F_1(S)$  from control to output voltage is calculated in Equation 17:

$$F_{1}(S) = \frac{\hat{v}_{0}}{\hat{d}} = V_{in} \frac{1 + \frac{S}{\omega_{esr}}}{\frac{S^{2}}{\omega_{0}^{2}} + \frac{S}{\omega_{0}Q_{p}} + 1}$$

(EQ. 17)

$$\label{eq:west_estimate} \text{Where} \quad \boldsymbol{\omega}_{\text{esr}} = \frac{\textbf{1}}{\textbf{R}_{\text{c}}\textbf{C}_{\text{o}}}, \boldsymbol{Q}_{\text{p}} \approx \textbf{R}_{\text{o}} \sqrt{\frac{\textbf{C}_{\text{o}}}{L}} \quad , \boldsymbol{\omega}_{\text{o}} = \frac{\textbf{1}}{\sqrt{L\textbf{C}_{\text{o}}}}$$

Transfer function  $F_2(S)$  from control to inductor current is given by Equation 18:

$$F_{2}(S) = \frac{\hat{I}_{o}}{\hat{d}} = \frac{V_{in}}{R_{o} + R_{L}} \frac{1 + \frac{S}{\omega_{z}}}{\frac{S^{2}}{\omega_{o}^{2}} + \frac{S}{\omega_{o}Q_{p}} + 1}$$

(EQ. 18)

Where

$$\omega_z = \frac{1}{R_o C_o}$$

.

Current loop gain T<sub>i</sub>(S) is expressed as Equation 19:

$$T_{i}(S) = R_{T}F_{m}F_{2}(S)H_{e}(S)$$

(EQ. 19)

The voltage loop gain with open current loop is calculated in Equation 20:

$$T_{v}(S) = KF_{m}F_{1}(S)A_{v}(S)$$

(EQ. 20)

The voltage loop gain with current loop closed is given by Equation 21:

$$L_{\nu}(S) = \frac{T_{\nu}(S)}{\textbf{1} + T_{i}(S)} \tag{EQ. 21} \label{eq:equation:equation:equation}$$

Where  $K = \frac{V_{FB}}{V_o}$ ,  $V_{FB}$  is the feedback voltage of the voltage error amplifier. If  $T_i(S) >> 1$ , then Equation 21 can be simplified as shown in Equation 22:

$$L_{v}(S) = \frac{V_{FB}}{V_{o}} \frac{R_{o} + R_{L}}{R_{T}} \frac{1 + \frac{S}{\omega_{esr}}}{1 + \frac{S}{\omega_{o}}} \frac{A_{v}(S)}{H_{e}(S)}, \ \omega_{p} \approx \frac{1}{R_{o}C_{o}} \tag{EQ. 22} \label{eq:equation_loss}$$

From Equation 22, it is shown that the system is a single order system, which has a single pole located at  $\omega_{\text{P}}$  before the half switching frequency. Therefore, a simple type II compensator can be easily used to stabilize the system.

FN6676.6 February 23, 2012

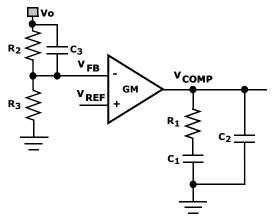

FIGURE 47. TYPE II COMPENSATOR

Figure 47 shows the type II compensator and its transfer function is expressed as Equation 23:

$$A_{v}(S) = \frac{\hat{v}_{comp}}{\hat{v}_{FB}} = \frac{g_{m}}{c_{1} + c_{2}} \frac{\left(1 + \frac{S}{\omega_{cz1}}\right)\left(1 + \frac{S}{\omega_{cz2}}\right)}{S\left(1 + \frac{S}{\omega_{cp}}\right)}$$

(EQ. 23)

Where:

$$\omega_{\text{cz1}} = \frac{1}{R_1 C_1}, \quad \omega_{\text{cz2}} = \frac{1}{R_2 C_3}, \quad \omega_{\text{cp}} = \frac{C_1 + C_2}{R_1 C_1 C_2}$$

(EQ. 24)

the compensator design goal is:

High DC gain

Loop bandwidth  $f_c$ :  $(\frac{1}{4}to\frac{1}{10})f_s$

Gain margin: >10dB

Phase margin: 40°

The compensator design procedure is shown in Equation 25:

Put compensator zero

$$\omega_{cz1} = (1to3)\frac{1}{R_0C_0}$$

(EQ. 25)

Put one compensator pole at zero frequency to achieve high DC gain, and put another compensator pole at either ESR zero frequency or half switching frequency, whichever is lower.

The loop gain  $T_V(S)$  at crossover frequency of  $f_C$  has unity gain. Therefore, the compensator resistance  $R_1$  is determined by Equation 26:

$$R_{1} = \frac{2\pi f_{c} V_{o} C_{o} R_{T}}{g_{m} V_{FB}}$$

(EQ. 26)

where  $g_m$  is the trans-conductance of the voltage error amplifier, typically 200 $\mu$ A/V. Compensator capacitor  $C_1$  is then given by Equation 27:

$$c_1 = \frac{1}{R_1 \omega_{cz}}, c_2 = \frac{1}{2\pi R_1 f_{esr}}$$

(EQ. 27)

Example: V<sub>IN</sub> = 12V, V<sub>0</sub> = 5V, I<sub>0</sub> = 3A, f<sub>s</sub> = 500kHz, C<sub>0</sub> = 220 µF/5mΩ, L = 5.6 µH, g<sub>m</sub> = 200 µs, R<sub>T</sub> = 0.21, V<sub>FB</sub> = 0.8V, S<sub>e</sub> = 1.1×10<sup>5</sup>V/s, S<sub>n</sub> = 3.4×10<sup>5</sup>V/s, f<sub>c</sub> = 80kHz, then compensator resistance R<sub>1</sub> = 72kΩ.

Put the compensator zero at 6.6kHz ( $\sim$ 1.5x C<sub>0</sub>R<sub>0</sub>), and put the compensator pole at ESR zero, which is 1.45MHz. The compensator capacitors are:

$C_1$  = 470pF,  $C_2$  = 3pF (There is approximately 3pF parasitic capacitance from  $V_{COMP}$  to GND; therefore,  $C_2$  is optional).

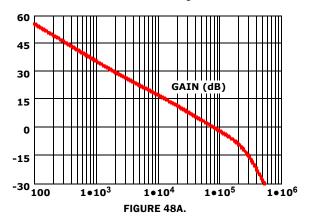

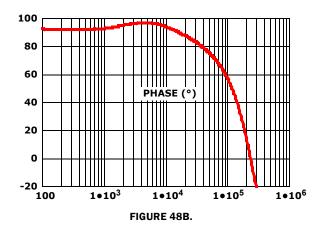

Figure 48A shows the simulated voltage loop gain. It is shown that it has 80kHz loop bandwidth with  $69^{\circ}$  phase margin and 15dB gain margin. Optional addition phase boost can be added to the overall loop response by using  $C_3$ .

#### **Rectifier Selection**

Current circulates from ground to the junction of the external Schottky diode and the inductor when the high-side switch is off. As a consequence, the polarity of the switching node is negative with respect to ground. This voltage is approximately -0.5V (a Schottky diode drop) during the off-time. The rectifier's rated reverse breakdown voltage must be at least equal to the maximum input voltage, preferably with a 20% derating factor. The power dissipation when the Schottky diode conducts is expressed in Equation 28:

$$P_{D}[W] = I_{OUT} \cdot V_{D} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(EQ. 28)

Where:

$V_{D}$  is the voltage drop of the Schottky diode. Selection of the Schottky diode is critical in terms of the high temperature reverse bias leakage current which is very dependent on VIN and

exponentially increasing with temperature. Due to the nature of reverse bias leakage vs temperature, the diode should be carefully selected to operate in the worst case circuit conditions. Catastrophic failure is possible if the diode chosen experiences thermal runaway at elevated temperatures. Please refer to Application Note for diode selection.

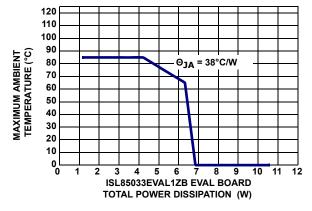

#### **Power Derating Characteristics**

To prevent the ISL85033 from exceeding the maximum junction temperature, some thermal analysis is required. The temperature rise is given by Equation 29:

$$T_{RISE}^{=} (PD)(\theta_{JA})$$

(EQ. 29)

where PD is the power dissipated by the regulator and  $\theta_{JA}$  is the thermal resistance from the junction of the die to the ambient temperature. The junction temperature,  $T_J$ , is given by Equation 30:

$$T_{J} = (T_{A} + T_{RISE})$$

(EQ. 30)

where  $T_A$  is the ambient temperature. For the QFN package, the  $\theta_{JA}$  is +38  $^{\circ}$  C/W.

The actual junction temperature should not exceed the absolute maximum junction temperature of +125°C When considering the thermal design, remember to consider the thermal needs of the rectifier diode.

The ISL85033 delivers full current at ambient temperatures up to +85°C if the thermal impedance from the thermal pad maintains the junction temperature below the thermal shutdown level, depending on the Input Voltage/Output Voltage combination and the switching frequency. The device power dissipation must be reduced to maintain the junction temperature at or below the thermal shutdown level. Figure 49 illustrates the power derating versus ambient temperature for the ISL85033 EVAL kit. Note that the EVAL kit derating curve is based on total circuit dissipation, not IC dissipation alone.

FIGURE 49. POWER DERATING CURVE

#### **Layout Considerations**

Layout is very important in high frequency switching converter design. With power devices switching efficiently between 100kHz and 600kHz, the resulting current transitions from one device to another cause voltage spikes across the interconnecting impedances and parasitic circuit elements. These voltage spikes

can degrade efficiency, radiate noise into the circuit, and lead to device overvoltage stress. Careful component layout and printed circuit board design minimizes these voltage spikes.

As an example, consider the turn-off transition of the upper MOSFET. Prior to turn-off, the MOSFET is carrying the full load current. During turn-off, current stops flowing in the MOSFET and is picked up by the Schottky diode. Any parasitic inductance in the switched current path generates a large voltage spike during the switching interval. Careful component selection, tight layout of the critical components, and short, wide traces minimizes the magnitude of voltage spikes.

There are two sets of critical components in the ISL85033 switching converter. The switching components are the most critical because they switch large amounts of energy, and therefore tend to generate large amounts of noise. Next, are the small signal components which connect to sensitive nodes or supply critical bypass current and signal coupling.

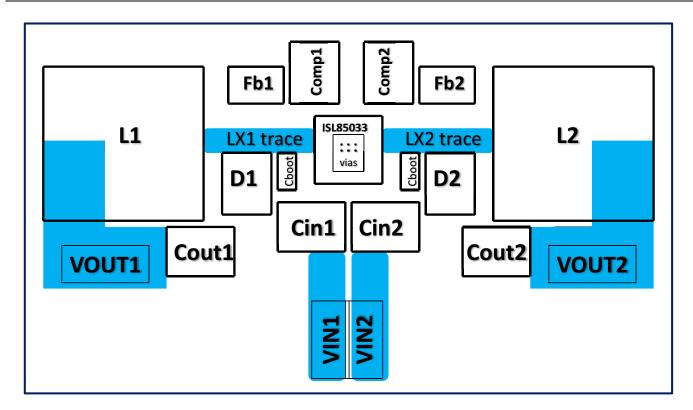

A multi-layer printed circuit board is recommended. Figure 50 shows the connections of the critical components in the converter. Note that capacitors C<sub>IN</sub> and C<sub>OUT</sub> could each represent numerous physical capacitors. Dedicate one solid layer, usually a middle layer of the PC board, for a ground plane and make all critical component ground connections with vias to this layer. Dedicate another solid layer as a power plane and break this plane into smaller islands of common voltage levels. Keep the metal runs from the PHASE terminals to the output inductor short. The power plane should support the input power and output power nodes. Use copper filled polygons on the top and bottom circuit layers for the phase nodes. Use the remaining printed circuit layers for small signal wiring.

In order to dissipate heat generated by the internal LDO and MOSFET, the ground pad should be connected to the internal ground plane through at least four vias. This allows the heat to move away from the IC and also ties the pad to the ground plane through a low impedance path.

The switching components should be placed close to the ISL85033 first. Minimize the length of the connections between the input capacitors,  $C_{\text{IN}}$ , and the power switches by placing them nearby. Position both the ceramic and bulk input capacitors as close to the upper MOSFET drain as possible. Position the output inductor and output capacitors between the upper and Schottky diode and the load.

The critical small signal components include any bypass capacitors, feedback components, and compensation components. Place the PWM converter compensation components close to the FB and COMP pins. The feedback resistors should be located as close as possible to the FB pin with vias tied straight to the ground plane as required.

FIGURE 50. PRINTED CIRCUIT BOARD POWER PLANES AND ISLANDS

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE     | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                 |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/2/11  | FN6676.6 | In the "Pin Descriptions" on page 2, added the following to end of EN1, EN2 description:                                                                                                                                                                                                                                               |

|          |          | "If EN1, EN2 pins are driven by an external signal, the minimum off-time for EN1, EN2 should be:                                                                                                                                                                                                                                       |

|          |          | EN_T_off ( $\mu$ s) = 10 $\mu$ s • C <sub>SS</sub> /2.2nF where CSS is the soft-start pin capacitor (nF). ISL85033 does not have debouncing to EN1, EN2 external signals."                                                                                                                                                             |

|          |          | In "Enable and Disable" on page 16, adding the following:                                                                                                                                                                                                                                                                              |

|          |          | "If EN1, EN2 pins are driven by an external signal, the minimum off-time for EN1, EN2 should be:                                                                                                                                                                                                                                       |

|          |          | EN_T_off ( $\mu$ s) = 10 $\mu$ s • C <sub>SS</sub> /2.2nF where CSS is the soft-start pin capacitor (nF). ISL85033 does not have debouncing to EN1, EN2 external signals."                                                                                                                                                             |

|          |          | Adding the following after Equation 3 on page 16:                                                                                                                                                                                                                                                                                      |

|          |          | "Maximum Css value is 50nF".                                                                                                                                                                                                                                                                                                           |

|          |          | In the "Pin Descriptions" on page 2, added the following to the end of SS1, SS2 description:                                                                                                                                                                                                                                           |

|          |          | "Maximum Css value is 50nF".                                                                                                                                                                                                                                                                                                           |

| 10/7/11  | FN6676.5 | In "Absolute Maximum Ratings" on page 8, changed:                                                                                                                                                                                                                                                                                      |

|          |          | PHASE1/2 to GND0.3V to +33V                                                                                                                                                                                                                                                                                                            |

|          |          | to:                                                                                                                                                                                                                                                                                                                                    |

|          |          | PHASE1/2 to GND7V (<10ns) /-0.3V (DC) to +33V                                                                                                                                                                                                                                                                                          |

| 9/14/11  | FN6676.4 | In the "Pin Descriptions" on page 3, for "SYNCIN", replaced "Set the internal switching frequency 20% lower than the external SYNC frequency applied to the SYNCIN pin" with "External SYNC frequency applied to the SYNCIN pin should be at least 2.4                                                                                 |

|          |          | times the internal switching frequency setting"                                                                                                                                                                                                                                                                                        |

| 8/9/11   |          | On page 8, changed parameter name from "Syncronization Frequency" to "Switching Frequency".                                                                                                                                                                                                                                            |

| 4/5/11   | FN6676.3 | Converted to new template                                                                                                                                                                                                                                                                                                              |

|          |          | Updated Intersil Trademark statement at bottom of page 1 per directive from Legal.                                                                                                                                                                                                                                                     |

|          |          | Page 2 in the pin table definition, please add the following sentence to the Pin 11 (VCC) description after "Output of the internal                                                                                                                                                                                                    |

|          |          | 5V linear regulator. Decouple to PGND with a minimum of 4.7μF ceramic capacitor."                                                                                                                                                                                                                                                      |

|          |          | "This pin is provided only for internal bias of ISL85033 (not to be loaded with current over 10mA)."                                                                                                                                                                                                                                   |

|          |          | Page 8 all Absolute Max Ratings that are "5.5" should be changed to "5.9"                                                                                                                                                                                                                                                              |

| 10/15/10 | FN6676.2 | Added the following sentence to the "SYNCIN" description in the "Pin Descriptions" table on page 3: "Set the internal switching frequency 20% lower than the external SYNC frequency applied to the SYNCIN pin."                                                                                                                       |

|          |          | Added the following sentence to "Synchronization Control" on page 18: "The switching frequency for each output is half of the SYNCIN frequency."                                                                                                                                                                                       |

|          |          | Revised tape and reel note in "Ordering Information" on page 6 from: "Add "-T" suffix for Tape and Reel. Please refer to TB347 for details on reel specifications"                                                                                                                                                                     |

|          |          | to:                                                                                                                                                                                                                                                                                                                                    |

|          |          | "Add "-T*" suffix for Tape and Reel. Please refer to <u>TB347</u> for details on reel specifications"  This is in order to delineate all tape and reel options.                                                                                                                                                                        |

| 9/14/10  |          | Corrected Eq. 2 on page 16 from:                                                                                                                                                                                                                                                                                                       |

|          |          |                                                                                                                                                                                                                                                                                                                                        |

|          |          | $R_3 = \frac{R_2 \times 0.8 \text{V}}{V_{\text{OUT}} - 0.8 \text{V}}$                                                                                                                                                                                                                                                                  |

|          |          | to:                                                                                                                                                                                                                                                                                                                                    |

|          |          | $R_2 = (V_{OUT} - 0.8) \bullet R_3 / 0.8$                                                                                                                                                                                                                                                                                              |

|          |          | Revised preceding paragraph from:                                                                                                                                                                                                                                                                                                      |

|          |          | "The output voltage programming resistor, $R_3$ , depends on the value chosen for the feedback resistor, $R_2$ , and the desired output voltage, $V_{OUT}$ , of the regulator. Equation 2 describes the relationship between $V_{OUT}$ and resistor values. $R_2$ is often chosen to be in the $1 k\Omega$ to $10 k\Omega$ range." to: |

|          |          | "The output voltage programming resistor, $R_2$ , depends on the value chosen for the feedback resistor, $R_3$ , and the desired output voltage, $V_{OUT}$ , of the regulator. Equation 2 describes the relationship between $V_{OUT}$ and resistor values. $R_3$ is often chosen to be in the $1$ kΩ to $1$ 0kΩ range."               |

| 6/21/10  | FN6676.1 | Changed MIN/MAX for "Soft-Start Charging Current" on page 8 from 1.5/2.5µA to 1.4/2.6µA                                                                                                                                                                                                                                                |

| 6/18/10  | FN6676.0 | Initial Release.                                                                                                                                                                                                                                                                                                                       |

| -,,      | 20.0.0   |                                                                                                                                                                                                                                                                                                                                        |

intersil

## ISL85033

## **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families.