# Phase Synchronizing Clock Generator

#### **Product Description**

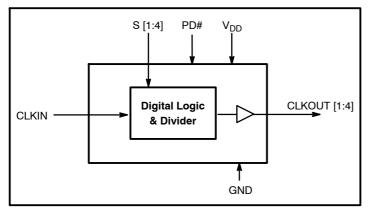

P1P3800A is a Phase Synchronizing clock generator that generates four outputs from an input clock. Output frequency will be a divide by two of the input clock. The phase of the output clocks is selectable through four select signals S1, S2, S3 and S4. Refer to *Output Clock Selection Table*. The outputs will go 'low' when all the select signals are 'low'. The transition to a new state of the output will be 'glitch free' when the select inputs change state. A Power Down signal enables the device to be driven to a power save mode, when active. The device works over a supply voltage range of 3.8 V - 5.5 V. The device is available in a 12–Lead 3mmx3mm WQFN package and operates over -40°C to +85°C.

#### Features

- Input Clock Frequency:

- 120 Hz 240 Hz (External Reference Clock)

- Output Clock Frequency: 60 Hz – 120 Hz

- 4 Clock Outputs

- 4 Two Level Controls to Select Sets of Clock Outputs

- Output Buffer Drive Strength: 8 mA

- Supply Voltage: 3.8 V 5.5 V

- Power Down for Power Save

- 12–Lead 3mmx3mm WQFN Package

- Operating Temperature Range: -40°C to +85°C

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

## Application

• P1P3800A can be used in applications where Phase Synchronization is needed.

Figure 1. Block Diagram

# **ON Semiconductor®**

http://onsemi.com

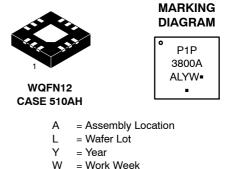

= Pb-Free Package

(Note: Microdot may be in either location)

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 6 of this data sheet.

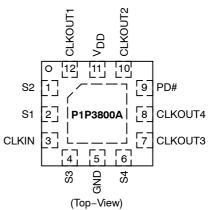

#### Table 1. PIN DESCRIPTION

| Pin# | Pin Name        | Туре | Description                                                                                                                         |

|------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1    | S2              | I    | Output clock select. Refer Output Clock selection table. Has NO default state                                                       |

| 2    | S1              | I    | Output clock select. Refer Output Clock selection table. Has NO default state.                                                      |

| 3    | CLKIN           | I    | External Reference Clock Input                                                                                                      |

| 4    | S3              | I    | Output clock select. Refer Output Clock selection table. Has NO default state.                                                      |

| 5    | GND             | Р    | Ground to entire chip                                                                                                               |

| 6    | S4              | I    | Output clock select. Refer Output Clock selection table. Has NO default state.                                                      |

| 7    | CLKOUT3         | 0    | Buffered clock output. Refer CLKOUT Diagram                                                                                         |

| 8    | CLKOUT4         | 0    | Buffered clock output. Refer CLKOUT Diagram                                                                                         |

| 9    | PD#             | I    | Power Down. Powers down the entire chip when pulled LOW. CLKOUT [1:4] will be LOW when power down is enabled. Has NO default state. |

| 10   | CLKOUT2         | 0    | Buffered clock output. Refer CLKOUT Diagram                                                                                         |

| 11   | V <sub>DD</sub> | Р    | Supply Voltage                                                                                                                      |

| 12   | CLKOUT1         | 0    | Buffered clock output. Refer CLKOUT Diagram                                                                                         |

### Table 2. OUTPUT CLOCK SELECTION TABLE

| S4 | S3 | S2 | S1 | CLKOUT4 | CLKOUT3 | CLKOUT2 | CLKOUT1 |

|----|----|----|----|---------|---------|---------|---------|

| 0  | 0  | 0  | 0  | Low     | Low     | Low     | Low     |

| 0  | 0  | 0  | 1  | CLK#    | CLK#    | CLK#    | CLK     |

| 0  | 0  | 1  | 0  | CLK#    | CLK#    | CLK     | CLK#    |

| 0  | 0  | 1  | 1  | CLK#    | CLK#    | CLK     | CLK     |

| 0  | 1  | 0  | 0  | CLK#    | CLK     | CLK#    | CLK#    |

| 0  | 1  | 0  | 1  | CLK#    | CLK     | CLK#    | CLK     |

| 0  | 1  | 1  | 0  | CLK#    | CLK     | CLK     | CLK#    |

| 0  | 1  | 1  | 1  | CLK#    | CLK     | CLK     | CLK     |

| 1  | 0  | 0  | 0  | CLK     | CLK#    | CLK#    | CLK#    |

| 1  | 0  | 0  | 1  | CLK     | CLK#    | CLK#    | CLK     |

| 1  | 0  | 1  | 0  | CLK     | CLK#    | CLK     | CLK#    |

| 1  | 0  | 1  | 1  | CLK     | CLK#    | CLK     | CLK     |

| 1  | 1  | 0  | 0  | CLK     | CLK     | CLK#    | CLK#    |

| 1  | 1  | 0  | 1  | CLK     | CLK     | CLK#    | CLK     |

| 1  | 1  | 1  | 0  | CLK     | CLK     | CLK     | CLK#    |

| 1  | 1  | 1  | 1  | CLK     | CLK     | CLK     | CLK     |

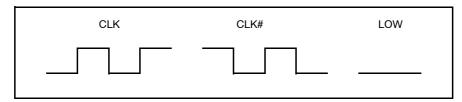

### **CLKOUT Diagram**

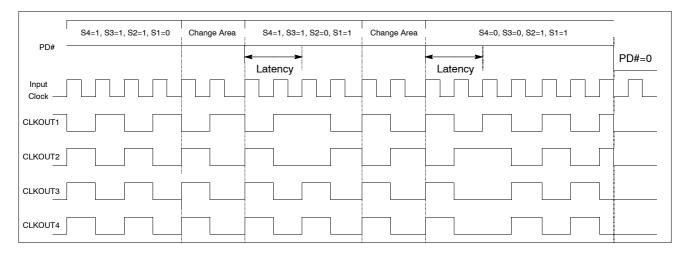

#### TIMING Diagram For Glitch Free Operation (For Reference)

(Transition of outputs from any state to any other state)

Note: Transition to new state will happen after a latency of one output clock cycle after completing the present output clock cycle Transition to new state will happen after a latency of up to 3 input clock cycles excluding the input cycle where the transition has occured.

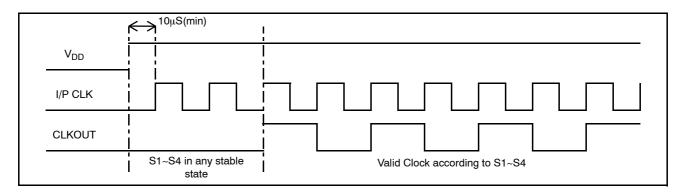

#### **Power Up**

Note: Transition to new state will happen after a latency of up to 2 input clock cycles excluding the input cycle where the transition has occured.

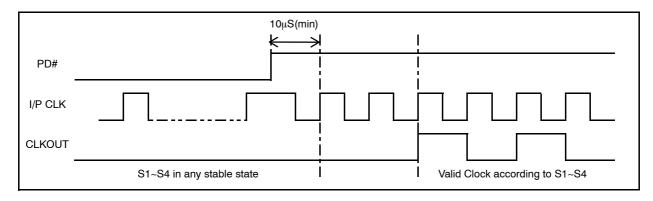

## PD# Operation

Note: Transition to new state will happen after a latency of up to 2 input clock cycles excluding the input cycle where the transition has occured.

#### **Table 3. OPERATING CONDITIONS**

| Symbol          | Parameter             | Min | Max | Unit |

|-----------------|-----------------------|-----|-----|------|

| V <sub>DD</sub> | Supply Voltage        | 3.8 | 5.5 | V    |

| T <sub>A</sub>  | Operating Temperature | -40 | +85 | °C   |

| CL              | Load Capacitance      |     | 15  | pF   |

| C <sub>IN</sub> | Input Capacitance     |     | 7.0 | pF   |

#### Table 4. ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                                             | Rating       | Unit |

|------------------|-------------------------------------------------------|--------------|------|

| V <sub>DD</sub>  | Voltage on V <sub>DD</sub> pin with respect to Ground | -0.5 to +7.0 | V    |

| V <sub>IN</sub>  | Voltage on any input pin with respect to Ground       | -0.5 to +4.0 | V    |

| T <sub>STG</sub> | Storage Temperature                                   | –65 to +125  | °C   |

| Ts               | Max. Soldering Temperature (10 sec)                   | 260          | °C   |

| TJ               | Junction Temperature                                  | 150          | °C   |

| T <sub>DV</sub>  | Static Discharge Voltage (As per JEDEC STD22-A114-B)  | 2.0          | kV   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Table 5. DC ELECTRICAL CHARACTERISTICS**

| Symbol          | Parameter                                                                                                                                                          | Min                     | Тур                    | Max | Unit |    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|-----|------|----|

| V <sub>DD</sub> | Operating Voltage                                                                                                                                                  | 3.8                     | 5.0                    | 5.5 | V    |    |

| V <sub>IL</sub> | Input Low Voltage (Note 1)                                                                                                                                         |                         | GND – 0.3              |     | 0.8  | V  |

| V <sub>IH</sub> | Input High Voltage (Note 1)                                                                                                                                        |                         | 1.6                    |     | 3.0  | V  |

| ۱ <sub>IL</sub> | Input Low Current                                                                                                                                                  |                         |                        | 10  | μΑ   |    |

| I <sub>IH</sub> | Input High Current                                                                                                                                                 |                         |                        |     | 10   | μΑ |

| V <sub>OL</sub> | Output Low Voltage                                                                                                                                                 | I <sub>OL</sub> = 8 mA  |                        |     | 0.4  | V  |

| V <sub>OH</sub> | Output High Voltage                                                                                                                                                | I <sub>OH</sub> = -8 mA | V <sub>DD</sub> - 0.6* |     |      | V  |

| I <sub>CC</sub> | Power Down Current (PD# pulled to GND)                                                                                                                             |                         |                        | 1.0 |      | μΑ |

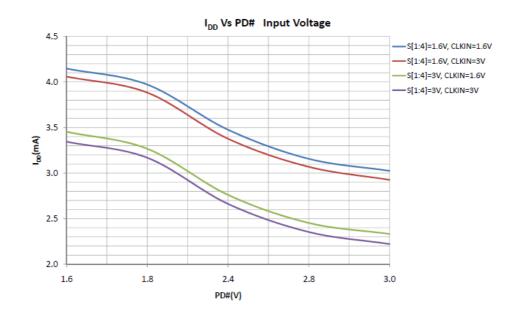

| I <sub>DD</sub> | **Dynamic Supply Current,<br>PD# = 5.5 V; S[1:4] = 5.5 V/GND; CLKIN Swing<br>$V_{DD}$ = 5.5 V                                                                      | = 0 to 5.5 V;           |                        |     | 1.8  | mA |

|                 | Dynamic Supply Current,<br>PD# = 3 V; S[1:4] = 3 V/GND; CLKIN Swing = 0 to 3.0 V<br>Dynamic Supply Current,<br>PD# = 3 V; S[1:4] = 1.6 V; CLKIN Swing = 0 to 1.6 V |                         |                        |     | 3.0  |    |

|                 |                                                                                                                                                                    |                         |                        |     | 4.0  | 1  |

|                 | Dynamic Supply Current,<br>PD# = S[1:4] = 1.6 V; CLKIN Swing = 0 to 1.6 V                                                                                          |                         |                        |     | 5.0  | ]  |

\*For  $V_{DD}$  = 5 V,  $V_{OH}$  =  $V_{DD}$  – 0.4 V. \*\*Indicative value, not a recommended operating condition.

1. Parameter is guaranteed by design and characterization. Not tested in production.

| Symbol                            | Parameter                                                                         | Min | Тур | Max | Unit |

|-----------------------------------|-----------------------------------------------------------------------------------|-----|-----|-----|------|

| CLKIN                             | Input Clock Frequency                                                             | 120 |     | 240 | Hz   |

| CLKOUT                            | Output Clock Frequency                                                            | 60  |     | 120 | Hz   |

| t <sub>LH</sub> , t <sub>HL</sub> | Output Rise / Fall time (Measured from 20% to 80%) (Notes 1, 2)                   |     |     | 10  | μs   |

| t <sub>LH</sub> , t <sub>HL</sub> | Input Rise / Fall time (Measured from 20% to 80%)                                 |     |     | 50  | μs   |

| t <sub>DOUT</sub>                 | Output Duty Cycle (Measured at V <sub>DD</sub> /2) (Notes 1, 2)                   | 49  | 50  | 51  | %    |

| t <sub>DIN</sub>                  | Input Duty Cycle                                                                  | 49  | 50  | 51  | %    |

| t <sub>su</sub>                   | Set up time for control signals, S[1:4], PD# to input clock rising edge (Note 1)  | 60  |     |     | μs   |

| t <sub>h</sub>                    | Hold up time for control signals, S[1:4], PD# to input clock rising edge (Note 1) | 60  |     |     | μs   |

| t <sub>skew</sub>                 | Output-Output Clock Skew (Note 1)                                                 |     |     | 10  | μs   |

#### Table 6. AC ELECTRICAL CHARACTERISTICS

2. All parameters are specified with 15 pF loaded output.

#### Typical I<sub>DD</sub> Vs PD# Input Voltage Plot

#### **ORDERING INFORMATION**

| Part Number      | Package                   | Shipping <sup>†</sup> |

|------------------|---------------------------|-----------------------|

| P1P3800AG12CRTWG | 12 pin (3 mm x 3 mm) WQFN | 3000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

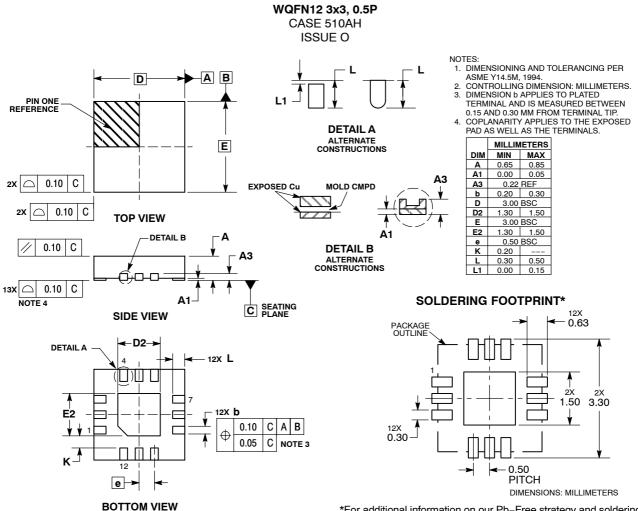

#### PACKAGE DIMENSIONS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer applications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product culd create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death agosociated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Dance: 401-92-700-0010

#### Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050

## ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Generators & Support Products category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

5P49V5901A748NLGI 5P49V5901B680NLGI 5P49V5901B744NLGI 5P49V5929B502NLGI 5P49V5935B520LTGI 5V49EE903-116NLGI CV183-2TPAG 82P33814ANLG/W 8T49N004A-002NLGI 8T49N004A-039NLGI 9FGV0631CKLF 9FGV0641AKLFT 9LRS3197AKLF 9UMS9633BFILF 9VRS4450AKLF NB3N51132DTR2G 8N3Q001EG-0035CDI 932SQ426AKLF 950810CGLF 9DBV0531AKILF 9DBV0741AKILF 9FGV0641AKLF 9UMS9633BKLF 9VRS4420DKILF 9VRS4420DKLF 9VRS4420DKLFT CY25404ZXI226 CY25422SXI-004 5P49V5901B712NLGI NB3H5150-01MNTXG 6INT61041NDG PL602-20-K52TC PL613-51QC 8N3Q001FG-1114CDI 9FGV0641AKILF ZL30314GKG2 ZL30253LDG1 ZL30251LDG1 ZL30250LDG1 ZL30169LDG1 ZL30142GGG2 9UMS9633BKILFT 9FGV0631CKLFT 9FGV0631CKILF 5P49V5935B536LTGI PI6LC48P0101LIE DS1099U-ST+ MAX24305EXG+ PI6LC48H02-01LIE 82P33814ANLG