# Poly-Phase High-Performance Wide-Span Energy Metering IC 90E32A

Version 1.0 April 2, 2013

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2013 Atmel Corporation. All rights reserved. / Rev.: Atmel-Meter-ATM90E32A-Eng-Datasheet-Eng\_042013

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL MEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND ISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.

### **Table of Contents**

|    |     |        | V                                           |     |

|----|-----|--------|---------------------------------------------|-----|

| GE | NEF | RAL DE | SCRIPTION                                   | 7   |

| BL | OCK | ( DIAG | RAM                                         | . 8 |

| 1  | PIN | ASSIG  | NMENT                                       | . 9 |

|    |     |        | RIPTION                                     |     |

|    |     |        | I DESCRIPTION                               | _   |

| J  |     |        | R SUPPLY                                    |     |

|    |     |        | (                                           |     |

|    |     |        |                                             |     |

|    | 0.0 |        | RESET Pin                                   |     |

|    |     |        | Power On Reset (POR)                        |     |

|    |     |        | Software Reset                              |     |

|    | 3.4 |        | RING FUNCTION                               |     |

|    |     | 3.4.1  | Theory of Energy Registers                  | 13  |

|    |     | 3.4.2  | Energy Registers                            | 15  |

|    |     | 3.4.3  | Energy Pulse Output                         | 15  |

|    |     |        | Startup and No-load Power                   |     |

|    | 3.5 |        | JREMENT FUNCTION                            |     |

|    |     |        | Active/ Reactive/ Apparent Power            |     |

|    |     |        | Fundamental / Harmonic Active Power         |     |

|    |     |        | Mean Power Factor (PF)                      |     |

|    |     |        | Voltage / Current RMS                       |     |

|    |     |        | Phase Angle                                 |     |

|    |     |        | Frequency                                   |     |

|    |     |        | Temperature                                 |     |

|    | 3.6 |        | R MODE                                      |     |

|    | 3.0 | 3.6.1  | Normal Mode (N Mode)                        |     |

|    |     |        | Idle Mode (I Mode)                          |     |

|    |     |        | Detection Mode (D Mode)                     |     |

|    |     |        | Partial Measurement mode (M Mode)           |     |

|    |     |        | Transition of Power Modes                   |     |

|    | 3.7 |        | DETECTION                                   |     |

|    |     |        | Zero-Crossing Detection                     |     |

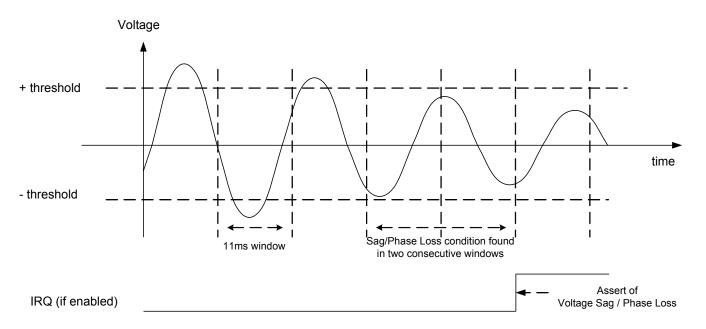

|    |     | 3.7.2  | Sag Detection                               | 25  |

|    |     | 3.7.3  | Phase Loss Detection                        | 25  |

|    |     | 3.7.4  | Computed Neutral Line Overcurrent Detection | 25  |

|    |     |        | Phase Sequence Error Detection              |     |

|    |     |        | D CURRENT RMS ESTIMATION                    |     |

| 4  | SPI | INTER  | FACE                                        | 26  |

|    | 4.1 | INTER  | FACE DESCRIPTION                            | 26  |

|    | 4.2 |        | TERFACE                                     |     |

|    |     |        | SPI Slave Interface Format                  |     |

| _  |     |        | Reliability Enhancement Feature             |     |

| 5  | CAL |        | TION METHOD                                 |     |

|    | 5.1 | NORM   | AL MODE OPERATION CALIBRATION               | 28  |

|    | 5.2 | PARTIAL MEASUREMENT MODE CALIBRATION                                 | . 28 |

|----|-----|----------------------------------------------------------------------|------|

| 6  | REG | GISTER                                                               | 29   |

|    | 6.1 | REGISTER LIST                                                        | . 29 |

|    | 6.2 | SPECIAL REGISTERS                                                    | . 36 |

|    |     | 6.2.1 Soft Reset Register                                            | 36   |

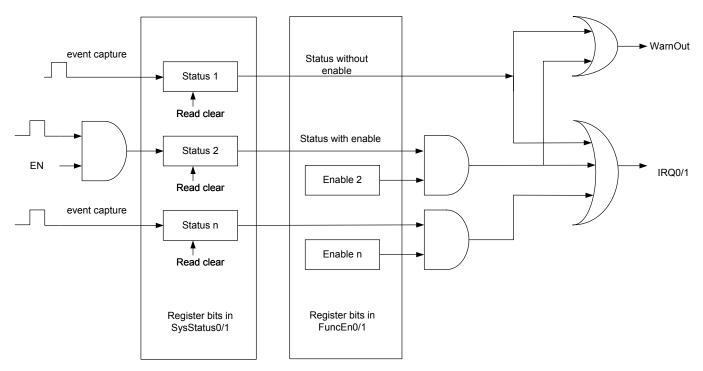

|    |     | 6.2.2 IRQ and WarnOut Signal Generation                              | 37   |

|    |     | 6.2.3 Special Configuration Registers                                |      |

|    |     | 6.2.4 Last SPI Data Register                                         |      |

|    | 6.3 | LOW-POWER MODES REGISTERS                                            | . 44 |

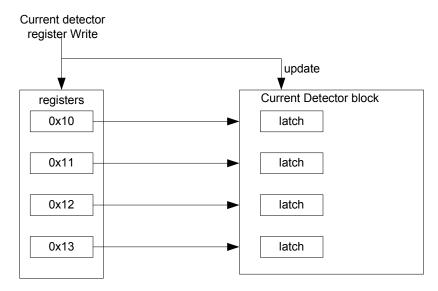

|    |     | 6.3.1 Detection Mode Registers                                       | 44   |

|    |     | 6.3.2 Partial Measurement mode Registers                             | 46   |

|    | 6.4 | CONFIGURATION AND CALIBRATION REGISTERS                              | . 49 |

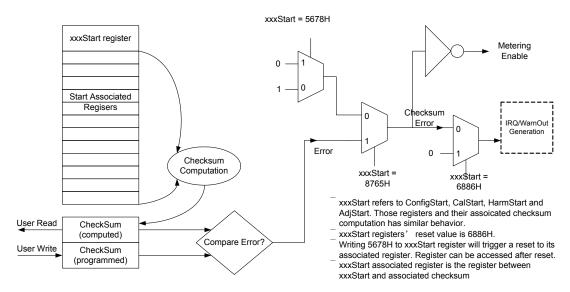

|    |     | 6.4.1 Start Registers and Associated Checksum Operation Scheme       | 49   |

|    |     | 6.4.2 Configuration Registers                                        | 49   |

|    |     | 6.4.3 Energy Calibration Registers                                   | 53   |

|    |     | 6.4.4 Fundamental/Harmonic Energy Calibration registers              | 55   |

|    |     | 6.4.5 Measurement Calibration                                        | 55   |

|    | 6.5 | ENERGY REGISTER                                                      | . 56 |

|    |     | 6.5.1 Regular Energy Registers                                       |      |

|    |     | 6.5.2 Fundamental / Harmonic Energy Register                         | 57   |

|    | 6.6 | MEASUREMENT REGISTERS                                                |      |

|    |     | 6.6.1 Power and Power Factor Registers                               |      |

|    |     | 6.6.2 Fundamental/ Harmonic Power and Voltage/ Current RMS Registers |      |

|    |     | 6.6.3 THD+N, Frequency, Angle and Temperature Registers              |      |

| 7  | ELE | ECTRICAL SPECIFICATION                                               | 61   |

|    | 7.1 | ELECTRICAL SPECIFICATION                                             | . 61 |

|    | 7.2 | METERING/ MEASUREMENT ACCURACY                                       | . 63 |

|    |     | 7.2.1 Metering Accuracy                                              | 63   |

|    |     | 7.2.2 Measurement Accuracy                                           | 64   |

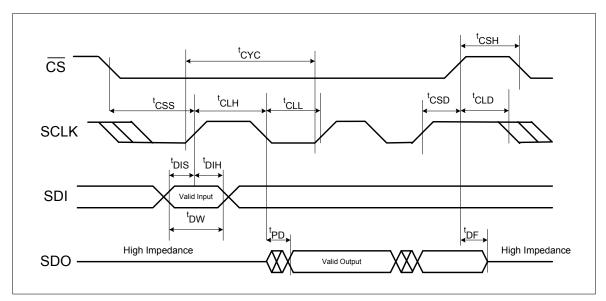

|    | 7.3 | INTERFACE TIMING                                                     | . 65 |

|    |     | 7.3.1 SPI Interface Timing (Slave Mode)                              | 65   |

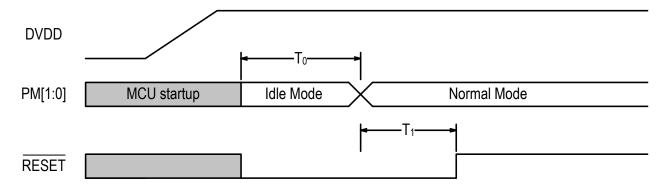

|    | 7.4 | POWER ON RESET TIMING                                                | . 66 |

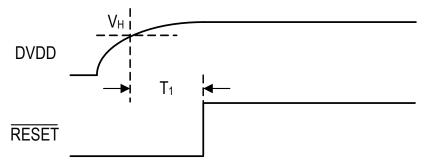

|    |     | ZERO-CROSSING TIMING                                                 |      |

|    |     | VOLTAGE SAG AND PHASE LOSS TIMING                                    |      |

|    |     | ABSOLUTE MAXIMUM RATING                                              |      |

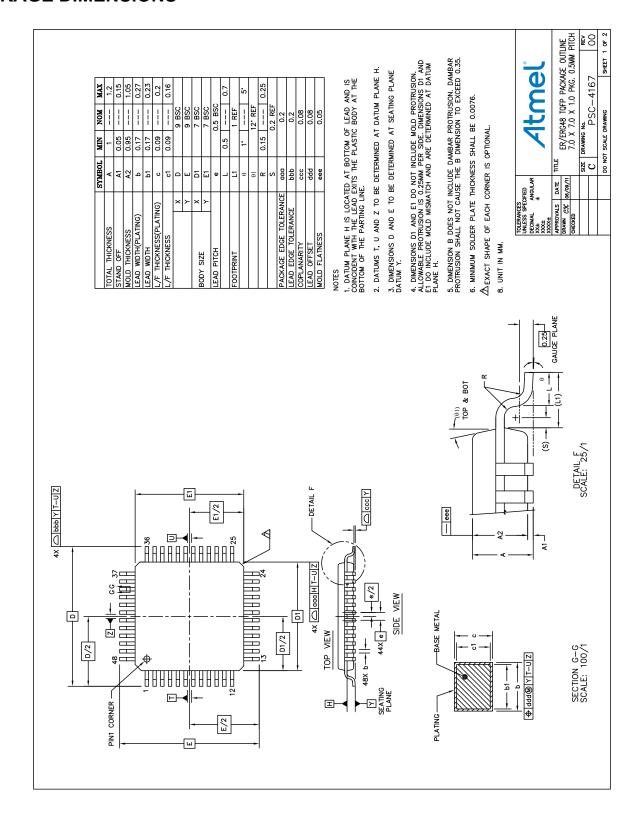

| PA | CKA | AGE DIMENSIONS                                                       | 70   |

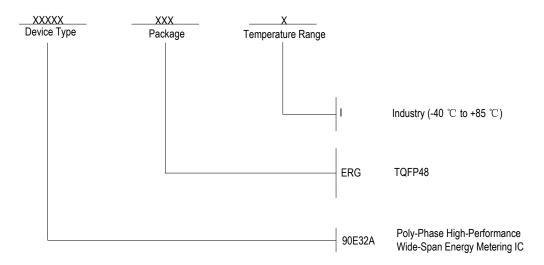

| OR | DER | RING INFORMATION                                                     | 71   |

| DA | TAS | SHEET DOCUMENT HISTORY                                               | 71   |

# **List of Tables**

| Table-1  | Pin Description                                                 | 10 |

|----------|-----------------------------------------------------------------|----|

| Table-2  | Pin Description                                                 | 19 |

| Table-3  | Digital I/O and Power Pin States in Idle Mode                   |    |

| Table-4  | Register List                                                   | 29 |

| Table-5  | Configuration Registers                                         | 49 |

| Table-6  | Calibration Registers                                           | 53 |

| Table-7  | Fundamental/Harmonic Energy Calibration Registers               | 55 |

| Table-8  | Measurement Calibration Registers                               | 55 |

| Table-9  | Regular Energy Registers                                        | 56 |

| Table-10 | Fundamental / Harmonic Energy Register                          | 57 |

| Table-11 | Power and Power Factor Register                                 | 57 |

| Table-12 | Fundamental/ Harmonic Power and Voltage/ Current RMS Registers  | 58 |

| Table-13 | THD+N, Frequency, Angle and Temperature Registers               | 59 |

| Table-14 | Metering Accuracy for Different Energy within the Dynamic Range | 63 |

| Table-15 | Measurement Parameter Range and Format                          | 64 |

| Table-16 | SPI Timing Specification                                        | 65 |

| Table-17 | Power On Reset Specification                                    | 66 |

| Table-18 | Zero-Crossing Specification                                     | 67 |

# **List of Figures**

| Figure-1  | 90E32A Block Diagram                                                 | 8  |

|-----------|----------------------------------------------------------------------|----|

| Figure-2  | 90E32A Block Diagram Pin Assignment (Top View)                       | 9  |

|           | Energy Register Operation Diagram                                    |    |

|           |                                                                      |    |

|           | Metering Startup Handling                                            |    |

| Figure-6  | Block Diagram in Normal Mode                                         | 19 |

| Figure-7  | Block Diagram in Idle Mode                                           | 20 |

| Figure-8  | Block Diagram in Detection Mode                                      | 22 |

| Figure-9  | Block Diagram in Partial Measurement mode                            | 23 |

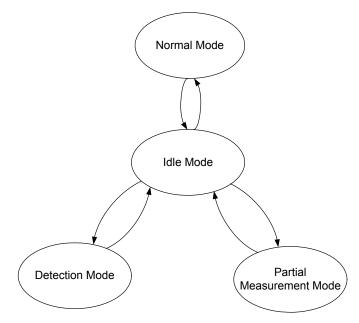

| Figure-10 | Power Mode Transition                                                | 24 |

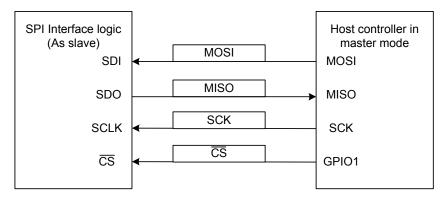

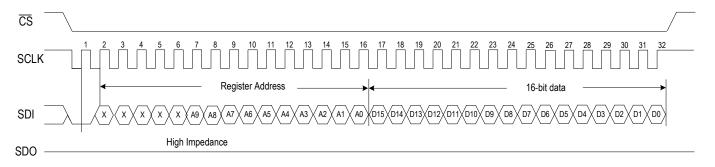

| Figure-11 | Slave Mode                                                           | 26 |

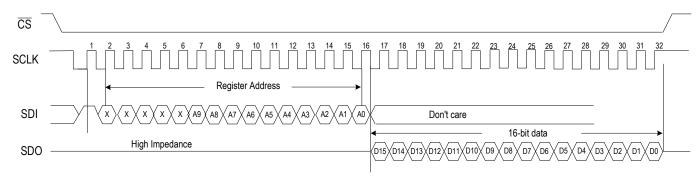

| Figure-12 | Read Sequence                                                        | 27 |

| Figure-13 | Write Sequence                                                       | 27 |

| Figure-14 | IRQ and WarnOut Generation                                           | 37 |

| Figure-15 | Current Detection Register Latching Scheme                           | 44 |

| Figure-16 | Start and Checksum Register Operation Scheme                         | 49 |

| Figure-17 | SPI Timing Diagram                                                   | 65 |

| Figure-18 | Power On Reset Timing (90E32A and MCU are Powered on Simultaneously) | 66 |

| Figure-19 | Power On Reset Timing in Normal & Partial Measurement Mode           | 66 |

| Figure-20 | Zero-Crossing Timing Diagram (per phase)                             | 67 |

| Figure-21 | Voltage Sag and Phase Loss Timing Diagram                            | 68 |

# Poly-Phase High-Performance Wide-Span Energy Metering IC

90E32A

Preliminary Information\*

#### **FEATURES**

#### **Metering Features**

- Metering features fully in compliance with the requirements of IEC62052-11, IEC62053-22 and IEC62053-23, ANSI C12.1 and ANSI C12.20; applicable in class 0.5S or class 1 poly-phase watt-hour meter or class 2 poly-phase var-hour meter.

- Accuracy of  $\pm 0.1\%$  for active energy and  $\pm 0.2\%$  for reactive energy over the dynamic range of 5000:1.

- Temperature coefficient is 6 ppm/ °C (typical) for on-chip reference voltage.

- Single-point calibration on each phase over the whole dynamic range for active energy; no calibration needed for reactive/ apparent energy.

- $\pm 1$  °C (typical) temperature sensor accuracy.

- Electrical parameters measurement: less than  $\pm 0.5\%$  fiducial error for Vrms, Irms, mean active/ reactive/ apparent power, frequency, power factor and phase angle.

- Active (forward/reverse), reactive (forward/reverse), apparent energy with independent energy registers. Active/ reactive/ apparent energy can be output by pulse or read through energy registers to adapt to different applications.

- Programmable startup and no-load power threshold, special designed of startup and no-load circuits to eliminate crosstalk among phases achieving better accuracy especially at low power conditions.

- Dedicated ADC and different gains for phase A/B/C current sampling circuits. Current sampled over current transformer (CT) or Rogowski coil (di/dt coil); phase A/B/C voltage sampled over resistor divider network or potential transformer (PT).

- Programmable power modes: Normal mode (N mode), Idle mode (I mode), Detection mode (D mode) and Partial Measurement mode (M mode).

- Fundamental (CF3, 0.2%) and harmonic (CF4, 1%) active energy with dedicated energy and power registers.

- Event detection: sag, phase loss, reverse voltage/ current phase sequence, reverse flow, calculated neutral line current I<sub>NC</sub> overcurrent and THD+N over-threshold.

#### Other Features

- 3.3V single power supply. Operating voltage range: 2.8V~3.6V.

Metering accuracy guaranteed within 3.0V~3.6V.

- · Four-wire SPI interface.

- Parameter diagnosis function and programmable interrupt output of the IRQ interrupt signals and the WarnOut signal.

- · Programmable voltage sag detection and zero-crossing output.

- CF1/CF2/CF3/CF4 output active/ reactive/ apparent energy pulses and fundamental/ harmonic energy pulses respectively.

- Crystal oscillator frequency: 16.384 MHz. On-chip two capacitors and no need of external capacitors.

- TQFP48 package.

- Operating temperature: -40  $^{\circ}$ C  $^{\sim}$  +85  $^{\circ}$ C .

#### **APPLICATION**

- Poly-phase energy meters of class 0.5S and class 1 which are used in three-phase four-wire (3P4W, Y0) or three-phase threewire (3P3W, Y or Δ) systems.

- Power monitoring instruments which need to measure voltage, current, mean power, etc.

#### GENERAL DESCRIPTION

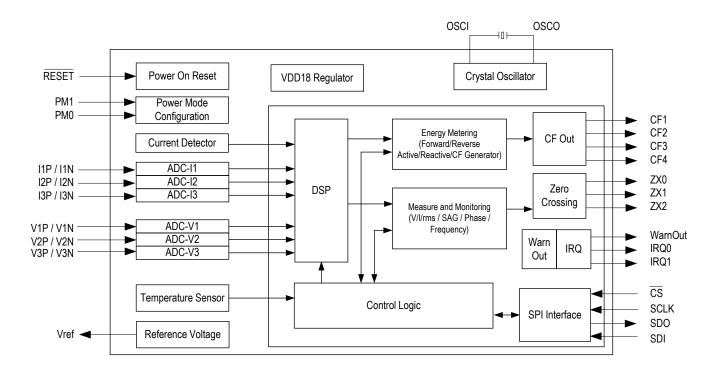

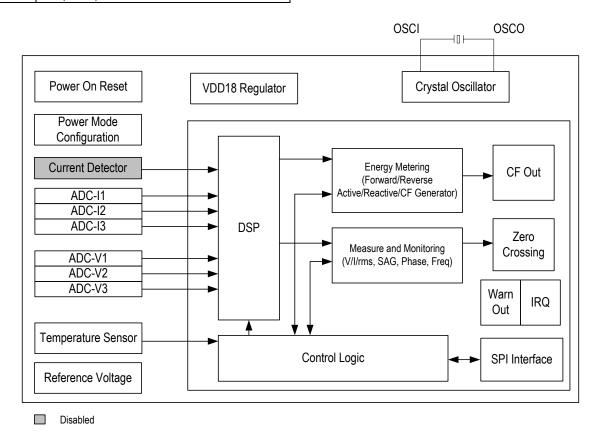

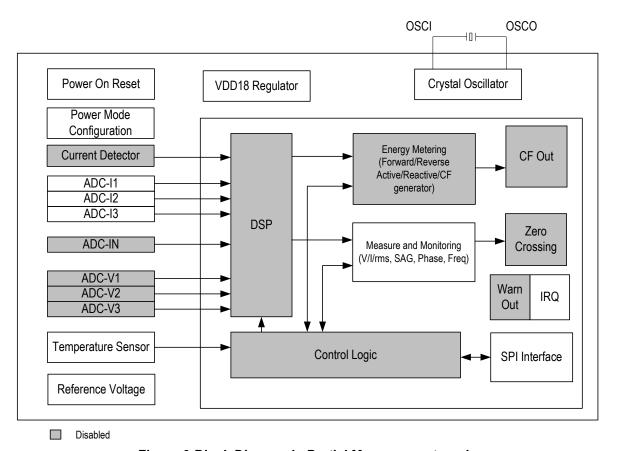

The 90E32A is a poly-phase high performance wide-dynamic range metering IC. The 90E32A incorporates 6 independent 2nd order sigmadelta ADCs, which could be employed in three voltage channels (phase A, B and C) and three current channels (phase A, B, C) in a typical three-phase four-wire system.

The 90E32A has an embedded DSP which executes calculation of active energy, reactive energy, apparent energy, fundamental and harmonic active energy over ADC signal and on-chip reference voltage. The DSP also calculates measurement parameters such as voltage and current RMS value as well as mean active/reactive/apparent power.

A four-wire SPI interface is provided between the 90E32A and the external microcontroller.

The 90E32A is suitable for poly-phase multi-function meters which could measure active/reactive/apparent energy and fundamental/harmonic energy either through four independent energy pulse outputs CF1/CF2/CF3/CF4 or through the corresponding registers.

The ADC and auto-temperature compensation technology for reference voltage ensure the 90E32A's long-term stability over variations in grid and ambient environment conditions.

April 2, 2013

#### **BLOCK DIAGRAM**

Figure-1 90E32A Block Diagram

#### 1 PIN ASSIGNMENT

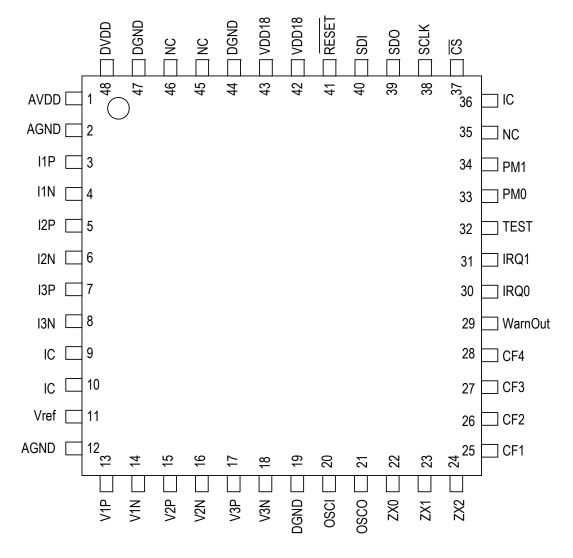

Figure-2 Pin Assignment (Top View)

#### 2 PIN DESCRIPTION

Table-1 Pin Description

| Name              | Pin No.        | I/O | Туре   | Description                                                                                                                                                                                                                                         |

|-------------------|----------------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset             | 41             | I   | LVTTL  | Reset: Reset Pin (active low) This pin should connect to ground through a 0.1 μF filter capacitor and a $10k\Omega$ resistor to VDD. In application it can also directly connect to one output pin from microcontroller (MCU).                      |

| AVDD              | 1              | I   | Power  | AVDD: Analog Power Supply This pin provides power supply to the analog part. This pin should connect to DVDD and be decoupled with a 0.1μF capacitor.                                                                                               |

| DVDD              | 48             | ı   | Power  | DVDD: Digital Power Supply This pin provides power supply to the digital part. It should be decoupled with a $10\mu F$ capacitor and a $0.1\mu F$ capacitor.                                                                                        |

| VDD18             | 42, 43         | Р   | Power  | VDD18: Digital Power Supply (1.8 V) These two pins should be connected together and connected to ground through a $10\mu F$ capacitor.                                                                                                              |

| DGND              | 19, 44, 47     | ı   | Power  | DGND: Digital Ground                                                                                                                                                                                                                                |

| AGND              | 2, 12          | 1   | Power  | AGND: Analog Ground                                                                                                                                                                                                                                 |

| I1P<br>I1N        | 3<br>4         | I   | Analog | I1P: Positive Input for Phase A Current I1N: Negative Input for Phase A Current These pins are differential inputs for phase A current. Note: I1 to phase A and I3 to phase C mapping can be swapped by configuring the I1I3Swap bit (b13, MMode0). |

| 12P<br>12N        | 5<br>6         | I   | Analog | I2P: Positive Input for Phase B Current I2N: Negative Input for Phase B Current These pins are differential inputs for phase B current.                                                                                                             |

| 13P<br>13N        | 7<br>8         | I   | Analog | I3P: Positive Input for Phase C Current I3N: Negative Input for Phase C Current These pins are differential inputs for phase C current. Note: I1 to phase A and I3 to phase C mapping can be swapped by configuring the I1I3Swap bit (b13, MMode0). |

| Vref              | 11             | 0   | Analog | Vref: Output Pin for Reference Voltage This pin should be decoupled with a $10\mu F$ capacitor, possibly a $0.1\mu F$ ceramic capacitor and a $1nF$ ceramic capacitor.                                                                              |

| V1P<br>V1N        | 13<br>14       | I   | Analog | V1P: Positive Input for Phase A Voltage V1N: Negative Input for Phase A Voltage These pins are differential inputs for phase A voltage.                                                                                                             |

| V2P<br>V2N        | 15<br>16       | ı   | Analog | V2P: Positive Input for Phase B Voltage V2N: Negative Input for Phase B Voltage These pins are differential inputs for phase B voltage.                                                                                                             |

| V3P<br>V3N        | 17<br>18       | ı   | Analog | V3P: Positive Input for Phase C Voltage V3N: Negative Input for Phase C Voltage These pins are differential inputs for phase C voltage.                                                                                                             |

| OSCI              | 20             | 1   | OSC    | OSCI: External Crystal Input                                                                                                                                                                                                                        |

| OSCO              | 21             | 0   | OSC    | OSCO: External Crystal Output A 16.384 MHz crystal is connected between OSCI and OSCO. There are two on-chip capacitor, therefore no need of external capacitors.                                                                                   |

| ZX0<br>ZX1<br>ZX2 | 22<br>23<br>24 | 0   | LVTTL  | ZX2/ZX1/ZX0:Zero-Crossing Output These pins are asserted when voltage or current crosses zero. Zero-crossing mode can be configured by the ZXConfig register (07H).                                                                                 |

| CF1               | 25             | 0   | LVTTL  | CF1: (all-phase-sum total) Active Energy Pulse Output                                                                                                                                                                                               |

| CF2               | 26             | 0   | LVTTL  | CF2: (all-phase-sum total) Reactive/ Apparent Energy Pulse Output The output of this pin is determined by the CF2varh bit (b7, MMode0) and the CF2ESV bit (b8, MMode0).                                                                             |

Table-1 Pin Description (Continued)

| Name          | Pin No.    | I/O | Туре  | Description                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CF3           | 27         | 0   | LVTTL | CF3: (all-phase-sum total) Active Fundamental Energy Pulse Output                                                                                                                                                                                                                                                                              |

| CF4           | 28         | 0   | LVTTL | CF4: (all-phase-sum total) Active Harmonic Energy Pulse Output                                                                                                                                                                                                                                                                                 |

| WarnOut       | 29         | 0   | LVTTL | WarnOut: Fatal Error Warning This pin is asserted high when there is metering related parameter checksum error. Otherwise this pin stays low. Refer to 6.2.2 IRQ and WarnOut Signal Generation.                                                                                                                                                |

| IRQ0          | 30         | 0   | LVTTL | IRQ0: Interrupt Output 0 This pin is asserted when one or more events in the SysStatus0 register (01H) occur. It is deasserted when there is no bit set in the SysStatus0 register (01H). In Detection mode, the IRQ0 is used to indicate the output of current detector. The IRQ0 state is cleared when entering or exiting Detection mode.   |

| IRQ1          | 31         | 0   | LVTTL | IRQ1: Interrupt Output 1  This pin is asserted when one or more events in the SysStatus1 register (02H) occur. It is deasserted when there is no bit set in the SysStatus1 register (02H).  In Detection mode, the IRQ1 is used to indicate the output of current detector. The IRQ1 state is cleared when entering or exiting Detection mode. |

| PM0<br>PM1    | 33<br>34   | I   | LVTTL | PM1/0: Power Mode Configuration These two pins define the power mode of 90E32A. Refer to Table-2.                                                                                                                                                                                                                                              |

| <del>CS</del> | 37         | I   | LVTTL | CS: Chip Select (Active Low) In SPI mode, this pin must be driven from high to low for each read/ write operation, and maintain low for the entire operation.                                                                                                                                                                                  |

| SCLK          | 38         | I   | LVTTL | SCLK: Serial Clock This pin is used as the clock for the SPI interface. Refer to 4 SPI Interface.                                                                                                                                                                                                                                              |

| SDO           | 39         | 0   | LVTTL | SDO: Serial Data Output This pin is used as the data output for the SPI mode. Refer to 4 SPI Interface.                                                                                                                                                                                                                                        |

| SDI           | 40         | I   | LVTTL | SDI: Serial Data Input This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.                                                                                                                                                                                                                                          |

| TEST          | 32         | I   | LVTTL | This pin should be always connected to DGND in system application.                                                                                                                                                                                                                                                                             |

| IC            | 9, 10, 36  |     | LVTTL | These pins should be always connected to DGND in system application.                                                                                                                                                                                                                                                                           |

| NC            | 35, 45, 46 |     |       | NC: These pins should be left open.                                                                                                                                                                                                                                                                                                            |

Pin Description 11 April 2, 2013

#### 3 FUNCTION DESCRIPTION

#### 3.1 POWER SUPPLY

The 90E32A works with single power rail 3.3V. An on-chip voltage regulator regulates the 1.8V voltage for the digital logic.

The regulated 1.8V power is connected to the VDD18 pin. It needs to be bypassed by an external capacitor.

The 90E32A has multiple power modes, in Idle and Detection modes the 1.8V power regulator is not turned on and the digital logic is not powered. When the logic is not powered, all the configured register values are not kept (all context lost) except for Detection mode related registers (10H~13H) for Detection mode configuration.

User has to re-configure the registers in Partial Measurement mode or Normal mode when transiting from Idle or Detection mode. Refer to 3.6 Power Mode for power mode details.

#### 3.2 CLOCK

The 90E32A has an on-chip oscillator and can directly connect to an external crystal.

The OSCI pin can also be driven with a clock source.

The oscillator will be powered down in Idle and Detection power modes, as described in 3.6 Power Mode.

#### 3.3 RESET

There are three reset sources for the 90E32A:

- RESET pin

- On-chip Power On Reset circuit

- Software Reset generated by the Software Reset register

#### 3.3.1 RESET PIN

The  $\overline{\text{RESET}}$  pin can be asserted to reset the 90E32A. The  $\overline{\text{RESET}}$  pin has RC filter with typical time constant of  $2\mu s$  in the I/O, as well as a  $2\mu s$  (typical) de-glitch filter.

Any reset pulse that is shorter than 2µs can not reset the 90E32A.

#### 3.3.2 POWER ON RESET (POR)

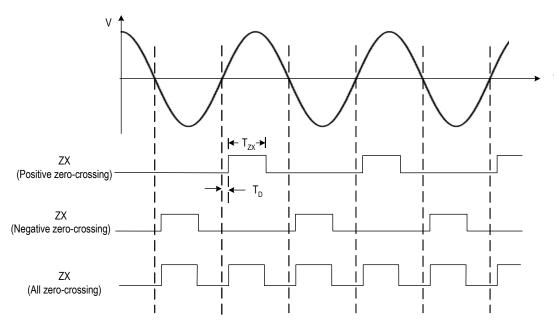

The POR circuit resets the 90E32A at power up.

POR circuit triggers reset when:

- DVDD power up, crossing the power-up threshold. Refer to Figure-19.

- VDD18 regulator changing from disable to enable, i.e. from Idle or Detection mode to Partial Measurement mode or Normal mode. Refer to Figure-18.

#### 3.3.3 SOFTWARE RESET

Chip reset can be triggered by writing to the SoftReset register in Normal mode. The software reset is the same as the reset scope generated from the RESET pin or POR.

These three reset sources have the same reset scope.

All digital logics and registers, except for the Harmonic Ratio registers will be subject to reset.

- · Interface logic: clock dividers

- Digital core/ logic: All registers except for some other special registers, refer to 6.3.1 Detection Mode Registers.

#### 3.4 METERING FUNCTION

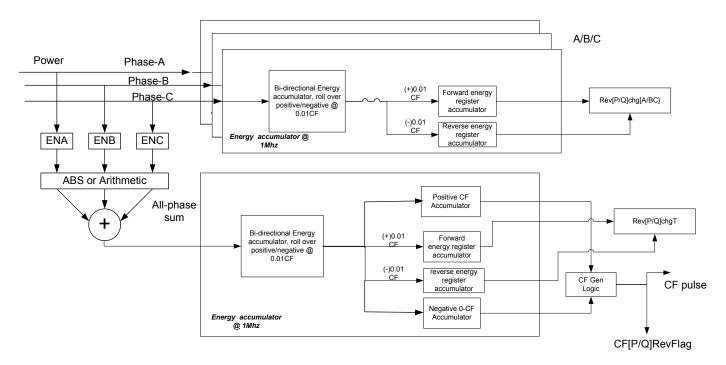

The accumulated energy is converted to pulse frequency on the CF pins and stored in the corresponding energy registers. The 90E32A provides energy accumulation registers with 0.1 or 0.01 CF resolution. 0.01CF / 0.1CF setting is defined by the 001LSB bit (b9, MMode0).

#### 3.4.1 THEORY OF ENERGY REGISTERS

The energy accumulation runs at 1 MHz clock rate, by accumulating the power value calculated by the DSP processor.

The power accumulation process is equivalent to digitally integrating the instantaneous power with a delta-time of about 1us. The accumulated energy is used to calculate the CF pulses and the corresponding internal energy registers.

The accumulated energy is converted to frequency of the CF pulses. One CF usually corresponds to 1KWh / MC (MC is Meter Constant, e.g. 3200 imp/kWh), and is usually referenced as an energy unit in this data-

sheet. The internal energy resolution for accumulation and conversion is 0.01 CF.

The 0.01 CF pulse energy constant is referenced as 'PL\_constant'.

Within 0.01 CF, forward and reverse energy are counteracted. When energy exceeds 0.01 pulse, the respective forward/ reverse energy is increased.

Take the example of active energy, suppose:

T0: Forward energy register is 12.34 pulses and reverse energy register is 1.23 pulses.

From t0 to t1: 0.005 forward pulses appeared.

From t1 to t2: 0.004 reverse pulses appeared.

From t2 to t3: 0.005 reverse pulses appeared.

From t3 to t4: 0.007 reverse pulses appeared.

The following table illustrates the process of energy accumulation process:

|                                  | t0      | t1     | t2     | t3     | t4    |

|----------------------------------|---------|--------|--------|--------|-------|

| Input energy                     | + 0.005 | -0.004 | -0.005 | -0.007 |       |

| Bidirectional energy accumulator | 0.005   | 0.001  | -0.004 | -0.001 |       |

| Forward 0.01 CF                  | 0       | 0      | 0      | 0      |       |

| Reverse 0.01CF                   | 0       | 0      | 0      | 1      |       |

| Forward energy register          | 12.34   | 12.34  | 12.34  | 12.34  | 12.34 |

| Reverse energy register          | 1.23    | 1.23   | 1.23   | 1.23   | 1.24  |

When forward/reverse energy reaches 0.1/0.01 pulse, the respective register is updated. When forward or reverse energy reaches 1 pulse,

CFx pins output pulse and the REVP/REVQ bits (b7~0, SysStatus1) are updated. Refer to Figure-3.

Figure-3 Energy Register Operation Diagram

For all-phase-sum total of active, reactive and (arithmetic sum) apparent energy, the associated power is obtained by summing the power of the three phases. The accumulation method of all-phase-sum

energy is determined by the EnPC/EnPB/EnPA/ABSEnP/ABSEnQ bits (b0~b4, MMode0).

Note that the direction of all-phase-sum power and single-phase power might be different.

#### 3.4.2 ENERGY REGISTERS

The 90E32A meters non-decomposed total active, reactive and apparent energy, as well as decomposed active fundamental and harmonic energy. The registers are listed as below.

#### 3.4.2.1 Total Energy Registers

Each phase and all-phase-sum has the following registers:

- Active forward/ reverse

- Reactive forward/ reverse

- Apparent energy

Altogether there are 20 energy registers. Those registers are defined in 6.5.1 Regular Energy Registers.

#### 3.4.2.2 Fundamental and Harmonic Energy Registers

The 90E32A counts decomposed active fundamental and harmonic energy. Reactive energy is not decomposed to fundamental and harmonic.

The fundamental/harmonic energy is accumulated in the same way as active energy accumulation method described above.

#### Registers:

- Fundamental / harmonic

- all-phase-sum / phase A / phase B / phase C

- Forward / reverse

Altogether there are 16 energy registers. Refer to 3.4.2.2 Fundamental and Harmonic Energy Registers.

#### 3.4.3 ENERGY PULSE OUTPUT

CF1 is fixed to be total active energy output (all-phase-sum). Both forward and reverse energy registers can generate the CF pulse (change of forward/ reverse direction can generate an interrupt if enabled).

CF2 is reactive energy output (all-phase-sum) by default. It can also be configured to be arithmetic sum apparent energy output (all-phase-sum)

CF3 is fixed to be active fundamental energy output (all-phase-sum).

CF4 is fixed to be active harmonic energy output (all-phase-sum).

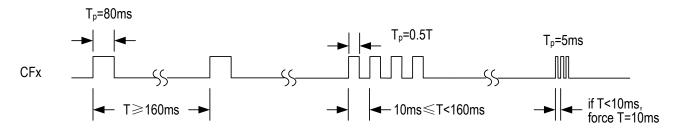

Figure-4 CFx Pulse Output Regulation

For CFx pulse width regulation, refer to Figure-4.

Case1 T>=160ms, Tp=80ms

Case 2 10ms<=T<160ms, Tp=T/2

Case 3 If Calculated T < 10ms, force T=10ms, Tp=5ms

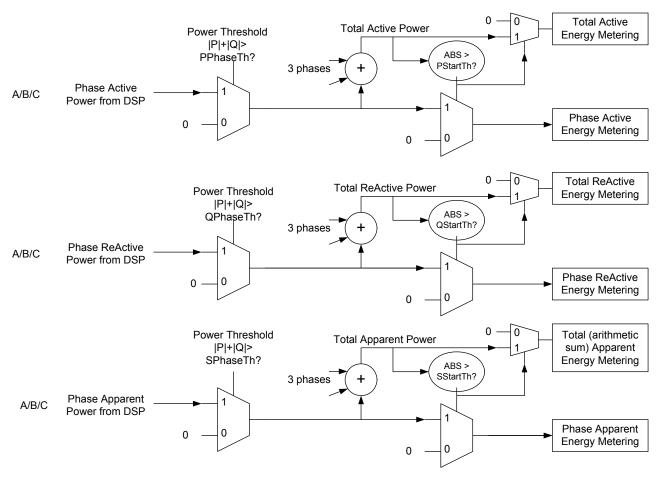

#### 3.4.4 STARTUP AND NO-LOAD POWER

There are startup power threshold registers (e.g. PStartTh(35H)). Refer to 6.4 Configuration and Calibration Registers. The power threshold registers are defined for all-phase-sum active, reactive and apparent power. The 90E32A starts metering when the corresponding all-phase-sum power is greater than the startup threshold. When the power value

is lower than the startup threshold, energy is not accumulated and it is assumed as in no-load status. Refer to Figure-5.

There are also no-load Current Threshold registers for Active, Reactive and Apparent energy metering participation for each of the 3 phases. If |P|+|Q| is lower than the corresponding power threshold, that particular phase will not be accumulated. Refer to the PStartTh register and other threshold registers.

There are also no-load status bits (the TPnoload/TQnoload bits (b14~15, EnStatus0)) defined to reflect the no-load status. The 90E32A does not output any pulse in no-load status. The power-on state is of no-load status.

Figure-5 Metering Startup Handling

#### 3.5 MEASUREMENT FUNCTION

Measured parameters can be divided to 7 types as follows:

- Active/ Reactive/ Apparent Power

- Fundamental/ Harmonic Power

- RMS for Voltage and Current

- Power Factor

- Phase Angle

- Frequency

- Temperature

Measured parameters are average values that are averaged among 16 phase-voltage cycles (about 320ms at 50Hz) except for the temperature. The measured parameter update frequency is approximately 3Hz. Refer to Table-15.

#### 3.5.1 ACTIVE/ REACTIVE/ APPARENT POWER

Active/ Reactive/ Apparent Power measurement registers can be divided as below:

- active, reactive, apparent power

- all-phase-sum / phase A / phase B / phase C

Altogether there are 12 power registers. Refer to 6.6.1 Power and Power Factor Registers and the SVmeanT register (98H).

Per-phase apparent power is defined as the product of measured Vrms and Irms of that phase.

All-phase-sum power is measured by arithmetically summing the per-phase measured power. The summing of phases can be configured by the MMode0 register.

#### 3.5.2 FUNDAMENTAL / HARMONIC ACTIVE POWER

Fundamental / harmonic active power measurement registers can be divided as below:

- fundamental and harmonic power

- all-phase-sum / phase A / phase B / phase C

Altogether there are 8 power registers. Refer to 6.6.2 Fundamental/ Harmonic Power and Voltage/ Current RMS Registers.

#### 3.5.3 MEAN POWER FACTOR (PF)

Power Factor is defined for those cases: all-phase-sum / phase A / phase B / phase C.

Altogether there are 4 power factor registers. Refer to 6.6.1 Power and Power Factor Registers.

For all-phase:

For each of the phase::

$$PF\_phase = \frac{active\_pow er}{apparent\_p ower}$$

#### 3.5.4 VOLTAGE / CURRENT RMS

Voltage/current RMS registers can be divided as follows:

#### Per-phase: Phase A / Phase B / Phase C

Voltage / Current

Altogether there are 6 RMS registers.

#### **Neutral Line Current RMS:**

Neutral line current can be calculated by instantaneous value

$$i_N = i_A + i_B + i_C.$$

Refer to 6.6.2 Fundamental/ Harmonic Power and Voltage/ Current RMS Registers.

#### 3.5.5 PHASE ANGLE

Phase Angle measurement registers can be divided as below:

- phase A / phase B / phase C

- voltage / current

Altogether there are 6 phase angle registers. Refer to 6.6.3 THD+N, Frequency, Angle and Temperature Registers.

Note: Calculation of phase angle is based on zero-crossing interval and frequency. There might be big error when voltage/current at low value.

#### 3.5.6 FREQUENCY

Frequency is measured using phase A voltage by default. When phase A has voltage sag, phase C is used, and phase B is used when both phase A and C have voltage sag.

Refer to 6.6.3 THD+N, Frequency, Angle and Temperature Registers.

#### 3.5.7 TEMPERATURE

Chip Junction-Temperature is measured roughly every 100 ms by onchip temperature sensor. Refer to 6.6.3 THD+N, Frequency, Angle and Temperature Registers.

#### 3.5.8 THD+N FOR VOLTAGE AND CURRENT

Voltage THD+N is defined as:

$$\frac{\sqrt{\left(V_{\text{rms\_total}}^{2} - V_{\text{rms\_fundam ental}}^{2}\right)}}{V_{\text{rms_fundam ental}}}$$

Current THD+N's definition is similar to that of voltage.

#### Registers:

- voltage and current

- phase A / phase B / phase C

Altogether there are 6 THD+N registers. Refer to 6.6.3 THD+N, Frequency, Angle and Temperature Registers.

The THD+N measurement is mainly used to monitor the percentage of harmonics in the system. Accuracy is not guaranteed when THD+N is lower than 10%.

#### 3.6 POWER MODE

The 90E32A has four power modes. The power mode is solely defined by the PM1 and PM0 pins.

#### **Table-2 Power Mode Mapping**

| PM1:PM0 Value | Power Mode                   |

|---------------|------------------------------|

| 11            | Normal (N mode)              |

| 10            | Partial Measurement (M mode) |

| 01            | Detection (D mode)           |

| 00            | Idle (I mode)                |

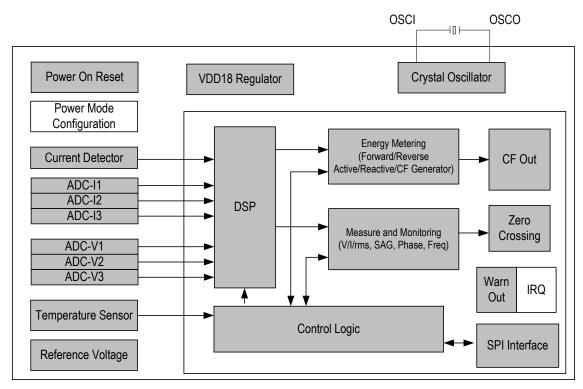

#### 3.6.1 NORMAL MODE (N MODE)

In Normal mode, all function blocks are active except for current detector block. Refer to Figure-6.

Figure-6 Block Diagram in Normal Mode

#### 3.6.2 IDLE MODE (I MODE)

In Idle mode, all functions are shut off.

The analog blocks' power supply is powered but circuits are set into power-down mode, i.e, power supply applied but all current paths are shut off. There is very low current since only very low device leakage could exist in this mode.

The digital I/Os' supply is powered.

In I/O and analog interface, the input signals from digital core (which is not powered) will be set to known state as described in Table-3. The PM1 and PM0 pins which are controlled by external MCU are active and can configure the 90E32A to other modes.

Figure-7 Block Diagram in Idle Mode

Please note that since the digital I/O is not shut off, the I/O circuit is active in the Idle mode. The application shall make sure that valid logic levels are applied to the I/O.

Table-3 lists digital I/O and power pins' states in Idle mode. It lists the requirements for inputs and the output level for output.

Table-3 Digital I/O and Power Pin States in Idle Mode

| Name         | I/O type | Туре  | Pin State in Idle Mode                                    |

|--------------|----------|-------|-----------------------------------------------------------|

| Reset        | I        | LVTTL | Input level shall be VDD33.                               |

| CS           | I        | LVTTL | I/O set in input mode. Input level shall be VDD33 or VSS. |

| SCLK         | K I      |       | I/O set in input mode. Input level shall be VDD33 or VSS. |

| SDO          | 0        | LVTTL | I/O set in input mode. Input level shall be VDD33 or VSS. |

| SDI          | I        | LVTTL | I/O set in input mode. Input level shall be VDD33 or VSS. |

| PM1<br>PM0   | I        | LVTTL | As defined in Table-2                                     |

| OSCI<br>OSCO | I<br>0   | OSC   | Oscillator powered down. OSCO stays at fixed (low) level. |

Table-3 Digital I/O and Power Pin States in Idle Mode

| Name                     | I/O type | Туре  | Pin State in Idle Mode                     |

|--------------------------|----------|-------|--------------------------------------------|

| ZX0<br>ZX1<br>ZX2        | 0        | LVTTL | 0                                          |

| CF1<br>CF2<br>CF3<br>CF4 | 0        | LVTTL | 0                                          |

| WarnOut                  | 0        | LVTTL | 0                                          |

| IRQ0<br>IRQ1             | 0        | LVTTL | 0                                          |

| VDD18                    | I        | Power | Regulated 1.8V: high impedance             |

| DVDD                     | I        | Power | Digital Power Supply: powered by system    |

| AVDD                     | I        | Power | Analog Power Supply: powered by system     |

| Test                     | I        | Input | Always tie to ground in system application |

#### 3.6.3 DETECTION MODE (D MODE)

In Detection mode, the current detector is active. The current detector compares whether any phase current exceeds the configured threshold using low-power comparators.

When the current of one phase or multiple phases exceeds the configured threshold, the 90E32A asserts the IRQ0 pin to high and hold it until power mode change. The IRQ0 state is cleared when entering or exiting Detection mode.

When the current of all three current channels exceed the configured threshold, the 90E32A asserts the IRQ1 pin to high and hold it until power mode change. The IRQ1 state is cleared when entering or exiting Detection mode.

The threshold registers need to be programmed in Normal mode before entering Detection mode.

The digital I/O state is the same as that in Idle state (except for IRQ0/IRQ1 and PM1/PM0).

The 90E32A has two comparators for detecting each phase's positive and negative current. Each comparator's threshold can be set individually. The two comparators are both active by default, which called 'double-side detection'. User also can enable one comparator only to save power consumption, which called 'single-side detection'.

Double-side detection has faster response and can detect 'half-wave' current. But it consumes nearly twice as much power as single-side detection.

Comparators can be power-down by configuring the DetectCtrl register.

Figure-8 Block Diagram in Detection Mode

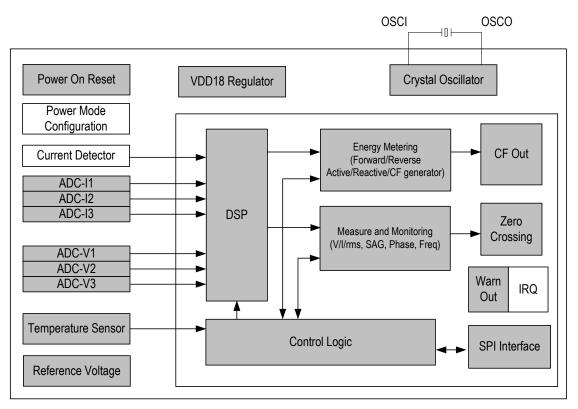

#### 3.6.4 PARTIAL MEASUREMENT MODE (M MODE)

In this mode, Voltage ADCs and digital circuits are inactive.

The 90E32A measures the current RMS of one line cycle.

When the measurement is done, the 90E32A asserts the IRQ0 pin high until the Partial Measurement mode exits.

In this mode, the user needs to program the related registers (including PGA gain, channel gain, offset, etc.) to make the current RMS measurement accurate. Refer to 5.2 Partial Measurement mode Calibration. Please note that not all registers in this mode is accessible. Only the Partial Measurement related registers (14H~1DH) and some special registers (00H, 01H, 03H, 07H,0EH, 0FH) can be accessed.

Figure-9 Block Diagram in Partial Measurement mode

#### 3.6.5 TRANSITION OF POWER MODES

The above power modes are controlled by the PM0 and PM1 pins. In application, the PM0 and PM1 pins are connected to external MCU. The PM0 and PM1 pins have internal RC- filters.

Generally, the 90E32A stays in Idle mode most of the time while outage. It enters Detection mode at a certain interval (for example 5s) as controlled by the MCU. It informs the MCU if the current exceeds the configured threshold. The MCU then commands the 90E32A to enter Partial Measurement mode at a certain interval (e.g. 60s) to read related current. After current reading, the 90E32A gets back to the Idle mode.

The measured current may be used to count energy according to some metering model (like current RMS multiplying the rated voltage to compute the power).

Any power mode transition goes through the Idle mode, as shown in Figure-10.

Figure-10 Power Mode Transition

#### 3.7 EVENT DETECTION

#### 3.7.1 ZERO-CROSSING DETECTION

Zero-crossing detector detects the zero-crossing point of the fundamental component of voltage and current for each of the 3 phases.

Zero-crossing signal can be independently configured and output. Refer to the definition of the ZXConfig register.

#### 3.7.2 SAG DETECTION

Usually in the application the Sag threshold is set to be 78% of the reference voltage. The 90E32A generates Sag event when there are less than three 8KHz samples (absolute value) greater than the sag threshold during two continuous 11ms time-window.

For the computation of Sag threshold register value, refer to AN-644.

The Sag event is captured by the SagWarn bit (b3, SysStatus0). If the corresponding IRQ enable bit the SagWnEn bit (b3, FuncEn0) is set, IRQ can be generated. Refer to Figure-21.

#### 3.7.3 PHASE LOSS DETECTION

The phase loss detection detects if there is one or more phases' voltage is less than the phase-loss threshold voltage.

The processing and handling is similar to sag detection, only the threshold is different. The threshold computation flow is also similar. The typical threshold setting could be 10% Un or less.

If any phase line is detected as in phase-loss mode, that phase's zero-crossing detection function (both voltage and current) is disabled.

# 3.7.4 COMPUTED NEUTRAL LINE OVERCURRENT DETECTION

The neutral line computed current (calculated) RMS is checked with the threshold defined in the INWarnTh0 register. If the N Line current is

greater than the threshold, the INOv0 bit (b14, SysStatus1) bit is set. IRQ1 is generated if the corresponding Enable bit the INOv0En bit (b14, FuncEn1) is set.

#### 3.7.5 PHASE SEQUENCE ERROR DETECTION

The phase sequence is detected in two cases: 3P4W and 3P3W, which is defined by the 3P3W bit (b8, MMode0).

#### 3P4W case:

Correct sequence: Voltage/current zero-crossing sequence: phase-A, phase-B and phase-C.

#### 3P3W case:

Correct sequence: Voltage/current zero-crossing between phase-A and phase-C is greater than 180 degree.

If the above mentioned criteria are violated, it is assumed as a phase sequence error.

#### 3.8 DC AND CURRENT RMS ESTIMATION

The 90E32A has a module named 'PMS' which can estimate current channel RMS or current channel arithmetic average (DC component). The measurement type is defined in the PMConfig register. It can be used to estimate current RMS in Partial Measurement mode. Since the PMS block only consume very small power, it can be also used to estimate current RMS in Normal mode. The PMS module is turned on in both Partial Measurement mode and Normal mode.

The result is in different format and different scale for the RMS and average respectively. The RMS result is unsigned; while current average is signed.

Refer to 6.3.2 Partial Measurement mode Registers for associated register definition.

#### 4 SPI INTERFACE

#### 4.1 INTERFACE DESCRIPTION

Four pins are associated with the interface as below:

- SDI Data pin, input.

- SDO Data pin, output.

- SCLK Clock input pin.

- $\overline{\text{CS}}$  Chip select pin Input.

Figure-11 Slave Mode

#### 4.2 SPI INTERFACE

The interface works in slave mode as shown in Figure-11.

#### 4.2.1 SPI SLAVE INTERFACE FORMAT

In the SPI mode, data on SDI is shifted into the chip on the rising edge of SCLK while data on SDO is shifted out of the chip on the falling edge of SCLK.

Refer to Figure-12 and Figure-13 below for the timing diagram.

#### Access type:

The first bit on SDI defines the access type as below:

| Instruction | Description         | Instruction Format |

|-------------|---------------------|--------------------|

| Read        | read from registers | 1                  |

| Write       | write to registers  | 0                  |

#### Address:

Fixed 15-bit, following the access type bits. The lower 10-bit is decoded as address; the higher 5 bits are 'Don't Care'.

#### Read/Write data:

Fixed as 16 bits.

#### Read Sequence:

Figure-12 Read Sequence

#### **Write Sequence:**

Figure-13 Write Sequence

#### 4.2.2 RELIABILITY ENHANCEMENT FEATURE

The SPI read/write transaction is  $\overline{\text{CS}}$ -low defined. Each transaction can only access one register.

Within each CS-low defined transaction:

Write: access occurs only when  $\overline{CS}$  goes from low to high and there are exactly 32 SCLK cycles received during  $\overline{CS}$  low period.

Read: if SCLK>=16 (full address received), data is read out from internal registers and gets to the SDO pin; and the LastSPIData register is updated. The R/C registers can only be cleared after the LastSPIData register is updated.

#### 5 CALIBRATION METHOD

#### 5.1 NORMAL MODE OPERATION CALIBRATION

Calibration is done per phase and there is no need to calibrate for the all-phase-sum (total) parameters. The calibration method is as follows:

#### Step-1: Register configuration for calibration

- Start to configure the System configuration Registers by writing 5678H to the ConfigStart register.

- The 90E32A automatically reset the configuration registers to their default value.

- Program all the system configuration registers.

- Calculate and write the checksum to the CS0 register.

- Write 8765H to the ConfigStart register (enable checksum checking).

- System may check the WarnOut pin to see if there is a checksum error.

The start register and checksum handling scheme is the same throughout the calibration process, so the following section does not describe the start and checksum operation.

#### Step-2: Measurement calibration (per-phase)

- First calibrate offset at I = 0, U = 0 for current or/and voltage;

- Configure calculated channel Gain (The user needs to program the PGA gain and DPGA gain properly in order to get the calculated gain within 0 to 2 in step-1).

- · Read Irms/ Urms value.

- · Calculate the compensation value.

- Write the calculated value to the offset register.

- Then calibrate gain at I = In (Ib), U = Un for current and voltage;

- · Read Irms/ Urms value.

- · Calculate the compensation value.

- · Write the calculated value to the Gain register.

#### Step-3: Metering calibration (per phase)

- First calibrate the Power/ Energy offset.

- U = Un, I = 0.

- · Read full 32 bits (or lower 16 bits) Active and Reactive Power

- · Calculate the compensation values

- Write the calculated values to the offset registers respectively.

- Then calibrate Energy gain at unity power factor:

- PF=1.0, U = Un, I = In (Ib).

- · Connect CF1 to the calibration bench;

- User/ PC calculate the energy gain according to the data got from calibration bench

- Write the calculated value to the Energy Gain register.

- Then calibrate the phase angle compensation at 0.5 inductive power factor.

- PF=0.5L, U = Un, I = In (Ib), Rated frequency = 50Hz, or 60Hz according to the application;

- · CF1 connected to the calibration bench;

- User/ PC calculate the phase angle according to the data got from calibration bench;

- · Write the calculated value to the Phase angle register.

#### 5.2 PARTIAL MEASUREMENT MODE CALIBRA-TION

The calibration method is as follows:

**Step-1:** Set the input current to zero and measure the current mean value (set MeasureType = 1, write 1 to the ReMeasure bit (b14, PMConfig) to trigger the measurement. Refer to the PMIrmsA register). Negate the result register (the PMIrmsA/PMIrmsB/PMIrmsC registers) reading (16-bit) and then write the result to the offset register.

**Step-2:** The output of Partial Measurement result = ADC\_input\_voltage \*PGA\_gain\*DPGA\_gain\*65536 / 1.2. For instance, a 150 mVrms signal (from CT) with PGA = 1 gets 8192 in the RMS result register.

**Step-3:** The user needs to do its own conversion to get meaningful result. The scaling factor in user's software could be calibrated device per device.

#### 6 REGISTER

#### 6.1 REGISTER LIST

#### Table-4 Register List

| Register<br>Address | Register Name | Read/Write<br>Type | Functional Description                                      | Comment                                                        | Page |

|---------------------|---------------|--------------------|-------------------------------------------------------------|----------------------------------------------------------------|------|

|                     |               |                    | Status and Special Register                                 | 1                                                              |      |

| 00H                 | SoftReset     | W                  | Software Reset                                              |                                                                | P 36 |

| 01H                 | SysStatus0    | R/C                | System Status 0                                             |                                                                | P 38 |

| 02H                 | SysStatus1    | R/C                | System Status 1                                             |                                                                | P 38 |

| 03H                 | FuncEn0       | R/W                | Function Enable 0                                           |                                                                | P 40 |

| 04H                 | FuncEn1       | R/W                | Function Enable 1                                           |                                                                | P 40 |

| 07H                 | ZXConfig      | R/W                | Zero-Crossing Configuration                                 | Configuration of ZX0/1/2 pins' source                          | P 41 |

| 08H                 | SagTh         | R/W                | Voltage Sag Threshold                                       |                                                                | P 42 |

| 09H                 | PhaseLossTh   | R/W                | Voltage Phase Losing Threshold                              | Similar to Voltage Sag Threshold register                      | P 42 |

| 0AH                 | INWarnTh0     | R/W                | Threshold for calculated (la + lb +lc) N line rms current   | Check SysStatus0/1 register.                                   | P 42 |

| 0CH                 | THDNUTh       | R/W                | Voltage THD Warning Threshold                               | Check SysStatus0/1 register.                                   | P 42 |

| 0DH                 | THDNITh       | R/W                | Current THD Warning Threshold                               | Check SysStatus0/1 register.                                   | P 42 |

| 0FH                 | LastSPIData   | R                  | Last Read/ Write SPI Value                                  | Refer to 4.2.2 Reliability Enhancement Feature                 | P 43 |

|                     |               | •                  | Low Power Mode Register                                     |                                                                |      |

| 10H                 | DetectCtrl    | R/W                | Current Detect Control                                      |                                                                | P 44 |

| 11H                 | DetectTh1     | R/W                | Channel 1 current threshold in Detection mode               |                                                                | P 45 |

| 12H                 | DetectTh2     | R/W                | Channel 2 current threshold in Detection mode               |                                                                | P 45 |

| 13H                 | DetectTh3     | R/W                | Channel 3 current threshold in Detection mode               |                                                                | P 46 |

| 14H                 | PMOffsetA     | R/W                | loffset for phase A in Partial Measurement mode             |                                                                | P 46 |

| 15H                 | PMOffsetB     | R/W                | loffset for phase B in Partial Measurement mode             |                                                                | P 46 |

| 16H                 | PMOffsetC     | R/W                | loffset for phase C in Partial Measurement mode             |                                                                | P 46 |

| 17H                 | PMPGA         | R/W                | PGAgain Configuration in Partial Measurement mode           |                                                                | P 47 |

| 18H                 | PMIrmsA       | R                  | Irms for phase A in Partial Measurement mode                |                                                                | P 47 |

| 19H                 | PMIrmsB       | R                  | Irms for phase B in Partial Measurement mode                |                                                                | P 47 |

| 1AH                 | PMIrmsC       | R                  | Irms for phase C in Partial Measurement mode                |                                                                | P 47 |

| 1BH                 | PMConfig      | R/W                | Measure configuration in Partial Measurement mode           |                                                                | P 48 |

| 1CH                 | PMAvgSamples  | R/W                | Number of 8K samples to be averaged in RMS/mean computation |                                                                | P 48 |

| 1DH                 | PMIrmsLSB     | R                  | LSB bits of PMRrms[A/B/C]                                   | It returns MSB of the mean measurement data in Mean value test | P 48 |

|                     |               | l                  | Configuration Registers                                     |                                                                |      |

| 30H                 | ConfigStart   | R/W                | Calibration Start Command                                   |                                                                | P 50 |

| 31H                 | PLconstH      | R/W                | High Word of PL_Constant                                    |                                                                | P 50 |

| 32H                 | PLconstL      | R/W                | Low Word of PL_Constant                                     |                                                                | P 50 |

Register 29 April 2, 2013

Table-4 Register List (Continued)

| Register<br>Address | Register Name | Read/Write<br>Type | Functional Description                                 | Comment           | Page |

|---------------------|---------------|--------------------|--------------------------------------------------------|-------------------|------|

| 33H                 | MMode0        | R/W                | Metering method configuration                          |                   | P 51 |

| 34H                 | MMode1        | R/W                | PGA gain configuration                                 |                   | P 52 |

| 35H                 | PStartTh      | R/W                | Active Startup Power Threshold.                        |                   |      |

| 36H                 | QStartTh      | R/W                | Reactive Startup Power Threshold.                      | Refer to Table-5. |      |

| 37H                 | SStartTh      | R/W                | Apparent Startup Power Threshold.                      |                   |      |

| 38H                 | PPhaseTh      | R/W                | Startup Power Threshold (Active Energy Accumulation)   |                   |      |

| 39H                 | QPhaseTh      | R/W                | Startup Power Threshold (ReActive Energy Accumulation) |                   |      |

| ЗАН                 | SPhaseTh      | R/W                | Startup Power Threshold (Apparent Energy Accumulation) |                   |      |

| 3BH                 | CS0           | R/W                | Checksum 0                                             |                   | P 53 |

|                     |               |                    | Calibration Registers                                  |                   |      |

| 40H                 | CalStart      | R/W                | Calibration Start Command                              |                   |      |

| 41H                 | PoffsetA      | R/W                | Phase A Active Power Offset                            |                   | P 54 |

| 42H                 | QoffsetA      | R/W                | Phase A Reactive Power Offset                          |                   | P 54 |

| 43H                 | POffsetB      | R/W                | Phase B Active Power Offset                            |                   |      |

| 44H                 | QOffsetB      | R/W                | Phase B Reactive Power Offset                          |                   |      |

| 45H                 | POffsetC      | R/W                | Phase C Active Power Offset                            |                   |      |

| 46H                 | QOffsetC      | R/W                | Phase C Reactive Power Offset                          | Refer to Table-6. |      |

| 47H                 | GainA         | R/W                | Phase A calibration gain                               |                   | P 54 |

| 48H                 | PhiA          | R/W                | Phase A calibration phase angle                        |                   | P 54 |

| 49H                 | GainB         | R/W                | Phase B calibration gain                               |                   |      |

| 4AH                 | PhiB          | R/W                | Phase B calibration phase angle                        |                   |      |

| 4BH                 | GainC         | R/W                | Phase C calibration gain                               |                   |      |

| 4CH                 | PhiC          | R/W                | Phase C calibration phase angle                        | 1                 |      |

| 4DH                 | CS1           | R/W                | Checksum 1                                             |                   |      |

|                     |               | Fur                | ndamental/ Harmonic Energy Calibration regis           | sters             |      |

| 50H                 | HarmStart     | R/W                | Harmonic Calibration Startup Command                   |                   |      |

| 51H                 | POffsetAF     | R/W                | Phase A Fundamental Active Power Offset                |                   |      |

| 52H                 | POffsetBF     | R/W                | Phase B Fundamental Active Power Offset                | Refer to Table-7. |      |

| 53H                 | POffsetCF     | R/W                | Phase C Fundamental Active Power Offset                |                   |      |

| 54H                 | PGainAF       | R/W                | Phase A Fundamental Active Power Gain                  |                   |      |

| 55H                 | PGainBF       | R/W                | Phase B Fundamental Active Power Gain                  |                   |      |

| 56H                 | PGainCF       | R/W                | Phase C Fundamental Active Power Gain                  | 1                 |      |

| 57H                 | CS2           | R/W                | Checksum 2                                             |                   |      |

Table-4 Register List (Continued)

| Register | <b>5</b>      | Read/Write |                                         |                   |      |

|----------|---------------|------------|-----------------------------------------|-------------------|------|

| Address  | Register Name | Туре       | Functional Description                  | Comment           | Page |

|          |               |            | Measurement Calibration                 |                   |      |

| 60H      | AdjStart      | R/W        | Measurement Calibration Startup Command |                   |      |

| 61H      | UgainA        | R/W        | Phase A Voltage RMS Gain                |                   |      |

| 62H      | IgainA        | R/W        | Phase A Current RMS Gain                |                   |      |

| 63H      | UoffsetA      | R/W        | Phase A Voltage RMS Offset              |                   |      |

| 64H      | IoffsetA      | R/W        | Phase A Current RMS Offset              |                   |      |

| 65H      | UgainB        | R/W        | Phase B Voltage RMS Gain                |                   |      |

| 66H      | IgainB        | R/W        | Phase B Current RMS Gain                |                   |      |

| 67H      | UoffsetB      | R/W        | Phase B Voltage RMS Offset              | Refer to Table-8. |      |

| 68H      | IoffsetB      | R/W        | Phase B Current RMS Offset              | Treat to lable 0. |      |

| 69H      | UgainC        | R/W        | Phase C Voltage RMS Gain                |                   |      |

| 6AH      | IgainC        | R/W        | Phase C Current RMS Gain                |                   |      |

| 6BH      | UoffsetC      | R/W        | Phase C Voltage RMS Offset              |                   |      |

| 6CH      | IoffsetC      | R/W        | Phase C Current RMS Offset              |                   |      |

| 6FH      | CS3           | R/W        | Checksum 3                              |                   |      |

|          |               |            | Energy Register                         |                   |      |

| 80H      | APenergyT     | R/C        | Total Forward Active Energy             |                   |      |

| 81H      | APenergyA     | R/C        | Phase A Forward Active Energy           | 1                 |      |

| 82H      | APenergyB     | R/C        | Phase B Forward Active Energy           |                   |      |

| 83H      | APenergyC     | R/C        | Phase C Forward Active Energy           |                   |      |

| 84H      | ANenergyT     | R/C        | Total Reverse Active Energy             |                   |      |

| 85H      | ANenergyA     | R/C        | Phase A Reverse Active Energy           |                   |      |

| 86H      | ANenergyB     | R/C        | Phase B Reverse Active Energy           |                   |      |

| 87H      | ANenergyC     | R/C        | Phase C Reverse Active Energy           |                   |      |

| 88H      | RPenergyT     | R/C        | Total Forward Reactive Energy           |                   |      |

| 89H      | RPenergyA     | R/C        | Phase A Forward Reactive Energy         |                   |      |

| 8AH      | RPenergyB     | R/C        | Phase B Forward Reactive Energy         |                   |      |

| 8BH      | RPenergyC     | R/C        | Phase C Forward Reactive Energy         |                   |      |

| 8CH      | RNenergyT     | R/C        | Total Reverse Reactive Energy           | Refer to Table-9. |      |

| 8DH      | RNenergyA     | R/C        | Phase A Reverse Reactive Energy         | 1                 |      |

| 8EH      | RNenergyB     | R/C        | Phase B Reverse Reactive Energy         | 7                 |      |

| 8FH      | RNenergyC     | R/C        | Phase C Reverse Reactive Energy         | 7                 |      |

| 90H      | SAenergyT     | R/C        | Total (Arithmetic Sum) Apparent Energy  |                   |      |

| 91H      | SenergyA      | R/C        | Phase A Apparent Energy                 | 7                 |      |

| 92H      | SenergyB      | R/C        | Phase B Apparent Energy                 |                   |      |

| 93H      | SenergyC      | R/C        | Phase C Apparent Energy                 | 1                 |      |

| 95H      | EnStatus0     | R          | Metering Status 0                       | 1                 | P 56 |

| 96H      | EnStatus1     | R          | Metering Status 1                       | 7                 | P 57 |

Register 31 April 2, 2013

#### Table-4 Register List (Continued)

| Register<br>Address | Register Name | Read/Write<br>Type | Functional Description                    | Comment            | Page |

|---------------------|---------------|--------------------|-------------------------------------------|--------------------|------|

| <u> </u>            |               | <b>'</b>           | Fundamental / Harmonic Energy Register    |                    | •    |

| A0H                 | APenergyTF    | R/C                | Total Forward Active Fundamental Energy   |                    | P 57 |

| A1H                 | APenergyAF    | R/C                | Phase A Forward Active Fundamental Energy |                    |      |

| A2H                 | APenergyBF    | R/C                | Phase B Forward Active Fundamental Energy |                    |      |

| АЗН                 | APenergyCF    | R/C                | Phase C Forward Active Fundamental Energy |                    |      |

| A4H                 | ANenergyTF    | R/C                | Total Reverse Active Fundamental Energy   |                    |      |

| A5H                 | ANenergyAF    | R/C                | Phase A Reverse Active Fundamental Energy |                    |      |

| A6H                 | ANenergyBF    | R/C                | Phase B Reverse Active Fundamental Energy |                    |      |

| A7H                 | ANenergyCF    | R/C                | Phase C Reverse Active Fundamental Energy | Refer to Table-10. |      |

| A8H                 | APenergyTH    | R/C                | Total Forward Active Harmonic Energy      | Refer to Table-10. |      |

| A9H                 | APenergyAH    | R/C                | Phase A Forward Active Harmonic Energy    |                    |      |

| AAH                 | APenergyBH    | R/C                | Phase B Forward Active Harmonic Energy    |                    |      |

| ABH                 | APenergyCH    | R/C                | Phase C Forward Active Harmonic Energy    |                    |      |

| ACH                 | ANenergyTH    | R/C                | Total Reverse Active Harmonic Energy      |                    |      |

| ADH                 | ANenergyAH    | R/C                | Phase A Reverse Active Harmonic Energy    |                    |      |

| AEH                 | ANenergyBH    | R/C                | Phase B Reverse Active Harmonic Energy    |                    |      |

| AFH                 | ANenergyCH    | R/C                | Phase C Reverse Active Harmonic Energy    |                    |      |

Table-4 Register List (Continued)

| Register<br>Address | Register Name | Read/Write<br>Type | Functional Description                              | Comment            | Page |

|---------------------|---------------|--------------------|-----------------------------------------------------|--------------------|------|

|                     | <u> </u>      |                    | Power and Power Factor Registers                    |                    |      |

| ВОН                 | PmeanT        | R                  | Total (all-phase-sum) Active Power                  |                    | P 57 |

| B1H                 | PmeanA        | R                  | Phase A Active Power                                |                    |      |

| B2H                 | PmeanB        | R                  | Phase B Active Power                                |                    |      |

| ВЗН                 | PmeanC        | R                  | Phase C Active Power                                |                    |      |

| В4Н                 | QmeanT        | R                  | Total (all-phase-sum) Reactive Power                |                    |      |

| B5H                 | QmeanA        | R                  | Phase A Reactive Power                              |                    |      |

| В6Н                 | QmeanB        | R                  | Phase B Reactive Power                              |                    |      |

| В7Н                 | QmeanC        | R                  | Phase C Reactive Power                              |                    |      |