# High Performance CMOS Oscillator with Frequency Margining – Pin Control

#### **Features**

- Crystal oscillator with CMOS output

- Output frequency from 8 MHz to 200 MHz

- Two frequency margining control pins (FS0, FS1)

- Output enable or power-down function

- Factory configured or field programmable

- Integrated phase-locked loop (PLL)

- Supply voltage: 3.3 V or 2.5 V

- Pb-free package: 5.0 × 3.2 mm LCC

- Commercial and industrial temperature ranges

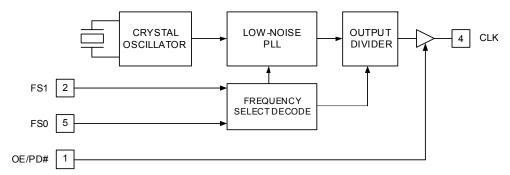

# **Functional Description**

The CY2XF32 is a high performance and high frequency crystal oscillator (XO). It uses a Cypress proprietary low noise PLL to synthesize the frequency from an integrated crystal. The output frequency can be changed via two select pins, allowing easy frequency margin testing in applications.

The CY2XF32 is available as a factory configured device or as a field programmable device.

For a complete list of related documentation, click here.

# **Logic Block Diagram**

# Contents

| Pinouts                                         | 3 |

|-------------------------------------------------|---|

| Pin Definitions                                 | 3 |

| Functional Overview                             | 3 |

| Programming Description                         |   |

| Field Programmable CY2XF32F                     | 4 |

| Factory Configured CY2XF32                      |   |

| Programming Variables                           |   |

| Output Frequencies                              |   |

| Pin 1: Output Enable or Power-down (OE/PD#)     |   |

| Supply Voltage                                  |   |

| Industrial versus Commercial Device Performance |   |

| Absolute Maximum Conditions                     |   |

| Operating Conditions                            |   |

| DC Electrical Characteristics                   |   |

| AC Electrical Characteristics                   |   |

|                                                 |   |

| Switching waveforms                     | 8  |

|-----------------------------------------|----|

| Ordering Information                    | 9  |

| Possible Configurations                 |    |

| Ordering Code Definitions               |    |

| Package Diagram                         | 10 |

| Acronyms                                | 11 |

| Document Conventions                    |    |

| Units of Measure                        | 11 |

| Document History Page                   | 12 |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      |    |

| Products                                |    |

| PSoC® Solutions                         | 13 |

| Cypress Developer Community             |    |

| Technical Support                       |    |

#### **Pinouts**

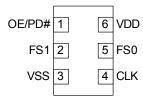

Figure 1. 6-pin Ceramic LCC pinout

#### **Pin Definitions**

6-pin Ceramic LCC

| Pin No. | Pin Name | I/O Type    | Description                                                                                              |

|---------|----------|-------------|----------------------------------------------------------------------------------------------------------|

| 1       | OE/PD#   |             | Output Enable or Power-down: Functionality is a programming option; see Table 2 and Table 3 for details. |

| 2, 5    | FS1, FS0 | CMOS Input  | Frequency Select.                                                                                        |

| 4       | CLK      | CMOS Output | Clock Output.                                                                                            |

| 6       | VDD      | Power       | Supply Voltage: 2.5 V or 3.3 V.                                                                          |

| 3       | VSS      | Power       | Ground.                                                                                                  |

#### **Functional Overview**

The FS0 and FS1 pins select between four different output frequencies, as shown in Table 1. Frequency margining is a common application for this feature. One frequency is used for the standard operating mode of the device, while the other frequencies are available for margin testing, either during product development or in system manufacturing test.

**Table 1. Frequency Select**

| FS1 | FS0 | Output Frequency |  |

|-----|-----|------------------|--|

| 0   | 0   | Frequency 0      |  |

| 0   | 1   | Frequency 1      |  |

| 1   | 0   | Frequency 2      |  |

| 1   | 1   | Frequency 3      |  |

When changing the output frequency, the frequency transition is not guaranteed to be smooth. There can be frequency excursions beyond the start frequency and the new frequency. Glitches and runt pulses are possible, and time must be allowed for the PLL to relock.

Pin 1 is programmed to function as either OE (output enable) or PD# (power-down, active low). The OE function is used to enable or disable the CLK output very quickly, but it does not reduce core power consumption. The PD# function puts the device into a low power state, but the wake up takes longer because the PLL must reacquire lock. Details are shown in Table 2 and Table 3.

**Table 2. Output Enable Operation**

| OE | PLL & Xtal Oscillator | Output Buffer |

|----|-----------------------|---------------|

| 0  | Active                | Off           |

| 1  | Active                | On            |

Table 3. Power-down Operation

| PD# | PLL & Xtal Oscillator | Output Buffer |

|-----|-----------------------|---------------|

| 0   | Off                   | Off           |

| 1   | Active                | On            |

# **Programming Description**

The CY2XF32 is a programmable device. Before being used in an application, it must be programmed with the output frequencies and other variables described in a later section. Two different device types are available, each with its own programming flow. They are described below.

### Field Programmable CY2XF32F

Field programmable devices are shipped unprogrammed and must be programmed before being installed on a printed circuit board (PCB). Customers use CyberClocks™ Online Software to specify the device configuration and generate a JEDEC (extension .jed) programming file. Programming of samples and prototype quantities is available using a Cypress programmer. Third party vendors manufacture programmers for small to large volume applications. Cypress's value added distribution partners also provide programming services. Field programmable devices are designated with an "F" in the part number. They are intended for quick prototyping and inventory reduction. The CY2XF32 is one time programmable (OTP).

The software is located at www.cyberclocksonline.com.

#### **Factory Configured CY2XF32**

For ready-to-use devices, the CY2XF32 is available with no field programming required. All requests are submitted to the local Cypress Field Application Engineer (FAE) or sales representative. After the request is processed, the user receives a new part number, samples, and data sheet with the programmed values. This part number is used for additional sample requests and production orders.

# **Programming Variables**

### **Output Frequencies**

The CY2XF32 is programmed with up to four independent output frequencies, which are then selected using the FS0 and FS1 pins. The device can synthesize frequencies to a resolution of one part per million (ppm), but the actual accuracy of the output frequency is limited by the accuracy of the integrated reference crystal.

### Pin 1: Output Enable or Power-down (OE/PD#)

Pin 1 is programmed as either Output Enable (OE) or Power-down (PD#).

#### **Supply Voltage**

A programming option optimizes the CY2XF32 for either 2.5 V or 3.3 V supply voltage. A device programmed for a particular supply voltage is not guaranteed to meet specifications when operated at the other voltage.

#### **Industrial versus Commercial Device Performance**

Industrial and commercial devices have different internal crystals. This has a potentially significant impact on performance levels for applications requiring the lowest possible phase noise. CyberClocks Online Software displays expected performance for both options.

**Table 4. Device Programming Variables**

| Variable                                     |

|----------------------------------------------|

| Output Frequency 0 (Power on default)        |

| Output Frequency 1                           |

| Output Frequency 2                           |

| Output Frequency 3                           |

| Pin 1 Functionality (OE or PD#)              |

| Supply Voltage (2.5 V or 3.3 V)              |

| Temperature Range (Commercial or Industrial) |

# **Absolute Maximum Conditions**

| Parameter                      | Description                             | Condition                   | Min         | Max                   | Unit |

|--------------------------------|-----------------------------------------|-----------------------------|-------------|-----------------------|------|

| $V_{DD}$                       | Supply Voltage                          |                             | -0.5        | 4.4                   | V    |

| V <sub>IN</sub> <sup>[1]</sup> | Input Voltage, DC                       | Relative to V <sub>SS</sub> | -0.5        | V <sub>DD</sub> + 0.5 | V    |

| T <sub>S</sub>                 | Temperature, Storage                    | Non operating               | <b>–</b> 55 | 135                   | °C   |

| T <sub>J</sub>                 | Temperature, Junction                   |                             | -40         | 135                   | °C   |

| ESD <sub>HBM</sub>             | ESD Protection (Human Body Model)       | JEDEC STD 22-A114-B         | 2000        | _                     | V    |

| <sub>⊙JA</sub> <sup>[2]</sup>  | Thermal Resistance, Junction to Ambient | 0 m/s airflow               | 6           | 4                     | °C/W |

# **Operating Conditions**

| Parameter         | Description                                                                             |       | Тур | Max   | Unit |

|-------------------|-----------------------------------------------------------------------------------------|-------|-----|-------|------|

| $V_{DD}$          | D 3.3 V Supply Voltage Range                                                            |       | 3.3 | 3.465 | V    |

|                   | 2.5 V Supply Voltage Range                                                              | 2.375 | 2.5 | 2.625 | V    |

| T <sub>PU</sub>   | Power-up Time for $V_{DD}$ to Reach Minimum Specified Voltage (Power Ramp is Monotonic) |       | _   | 500   | ms   |

| T <sub>A</sub>    | Ambient Temperature, Commercial                                                         | 0     | -   | 70    | °C   |

|                   | Ambient Temperature, Industrial                                                         | -40   | -   | 85    | °C   |

| C <sub>LOAD</sub> | Load Capacitance at CLK (>100 MHz)                                                      | -     | -   | 10    | pF   |

|                   | Load Capacitance at CLK (≤100 MHz)                                                      | _     | _   | 15    | pF   |

Document Number: 001-53147 Rev. \*F Page 5 of 13

The voltage on any input or I/O pin cannot exceed the power pin during power-up.

Simulated. The board is derived from the JEDEC multilayer standard. It measures 76 x 114 x 1.6 mm and has four layers of copper (2/1/1/2 oz.). The internal layers are 100% copper planes, while the top and bottom layers have 50% metalization. No vias are included in the model.

# **DC Electrical Characteristics**

| Parameter            | Description                           | Condition                                               | Min                   | Тур | Max                   | Unit |

|----------------------|---------------------------------------|---------------------------------------------------------|-----------------------|-----|-----------------------|------|

| I <sub>DD</sub>      | Operating Supply Current              | $V_{DD}$ = 3.465 V, OE/PD# = $V_{DD}$ , output unloaded | -                     | _   | 110                   | mA   |

| I <sub>SB</sub>      | Standby Supply Current                | PD# = V <sub>SS</sub>                                   | -                     | -   | 200                   | μΑ   |

| V <sub>OH</sub>      | Output High Voltage                   | V <sub>DD</sub> = min, I <sub>OH</sub> = –4 mA          | 0.9 × V <sub>DD</sub> | -   | _                     | V    |

| V <sub>OL</sub>      | Output Low Voltage                    | V <sub>DD</sub> = max, I <sub>OL</sub> = 4 mA           | -                     | -   | 0.1 × V <sub>DD</sub> | V    |

| I <sub>OZ</sub>      | Output Leakage Current                | OE/PD# = V <sub>SS</sub>                                | -35                   | -   | 35                    | μΑ   |

| V <sub>IH</sub>      | Input High Voltage                    |                                                         | 0.7 × V <sub>DD</sub> | -   | _                     | V    |

| V <sub>IL</sub>      | Input Low Voltage                     |                                                         | _                     | _   | 0.3 × V <sub>DD</sub> | V    |

| I <sub>IHO</sub>     | Input High Current, OE/PD# Pin        | Input = V <sub>DD</sub>                                 | _                     | _   | 115                   | μΑ   |

| I <sub>IH1</sub>     | Input High Current,<br>FS0 & FS1 Pins | Input = V <sub>DD</sub>                                 | _                     | _   | 10                    | μА   |

| I <sub>ILO</sub>     | Input Low Current, OE/PD# Pin         | Input = V <sub>SS</sub>                                 | -50                   | -   | _                     | μΑ   |

| I <sub>IL1</sub>     | Input Low Current, FS0 & FS1 Pin      | Input = V <sub>SS</sub>                                 | -20                   | _   | _                     | μΑ   |

| C <sub>IN0</sub> [3] | Input Capacitance, OE/PD# Pin         |                                                         | _                     | 15  | _                     | pF   |

| C <sub>IN1</sub> [3] | Input Capacitance,<br>FS0 & FS1 Pin   |                                                         | -                     | 4   | -                     | pF   |

Note

3. Not 100% tested, guaranteed by design and characterization.

# **AC Electrical Characteristics**

| Parameter [4]     | Description                                            | Condition                                                                                                     | Min | Тур | Max | Unit |

|-------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| F <sub>OUT</sub>  | Output Frequency <sup>[5]</sup>                        |                                                                                                               | 8   | _   | 200 | MHz  |

| FSC               | Frequency Stability, Commercial Devices <sup>[6]</sup> | T <sub>A</sub> = 0 °C to 70 °C                                                                                | -   | -   | ±35 | ppm  |

| FSI               | Frequency Stability, Industrial Devices <sup>[6]</sup> | $T_A = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C}$                                                  | -   | -   | ±55 | ppm  |

| AG                | Aging, 10 Years                                        |                                                                                                               | -   | -   | ±15 | ppm  |

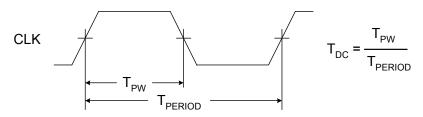

| T <sub>DC</sub>   | Output Duty Cycle                                      | Measured at V <sub>DD</sub> /2; see Figure 2                                                                  | 45  | 50  | 55  | %    |

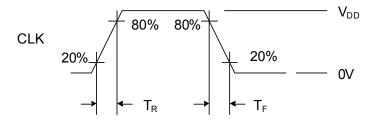

| T <sub>R</sub>    | Output Rise Time                                       | 20% to 80% of $V_{DD}$ , $C_{LOAD}$ = 15 pF                                                                   | -   | 0.7 | 1.5 | ns   |

| T <sub>F</sub>    | Output Fall Time                                       | 80% to 20% of $V_{DD}$ , $C_{LOAD}$ = 15 pF                                                                   | -   | 0.8 | 1.5 | ns   |

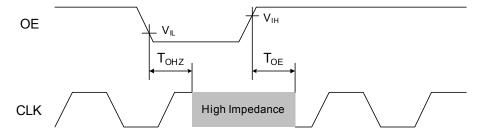

| T <sub>OHZ</sub>  | Output Disable Time                                    | Time from falling edge on OE to stopped outputs (Asynchronous)                                                | -   | -   | 100 | ns   |

| T <sub>OE</sub>   | Output Enable Time                                     | Time from rising edge on OE to outputs at a valid frequency (Asynchronous)                                    | -   | _   | 100 | ns   |

| T <sub>LOCK</sub> | Startup Time                                           | Time for CLK to reach valid frequency measured from the time $V_{DD} = V_{DD}$ (min.) or from PD# rising edge | -   | _   | 5   | ms   |

| T <sub>LFS</sub>  | Relock Time                                            | Time for CLK to reach valid frequency from FS0 or FS1 pin change                                              | -   | _   | 1   | ms   |

<sup>Notes

4. Not 100% tested, guaranteed by design and characterization.

5. This parameter is specified in CyberClocks Online software.

6. Frequency stability is the maximum variation in frequency from F<sub>0</sub>. It includes initial accuracy, plus variation from temperature and supply voltage.</sup>

# **Switching Waveforms**

Figure 2. Duty Cycle Timing

Figure 3. Output Rise and Fall Time

Figure 4. Output Enable and Disable Timing

# **Ordering Information**

The following table contains only the parts that are currently available. If you do not see what you are looking for, contact your local sales representative. For more information, visit the Cypress website at <a href="http://www.cypress.com/products">www.cypress.com/products</a>.

http://www.cypress.com/products.

| Part Number [7] | Configuration      | Package Description               | Product Flow                |  |  |  |

|-----------------|--------------------|-----------------------------------|-----------------------------|--|--|--|

| Pb-free         |                    |                                   |                             |  |  |  |

| CY2XF32FLXIT    | Field Programmable | 6-pin Ceramic LCC – Tape and Reel | Industrial, –40 °C to 85 °C |  |  |  |

Some product offerings are factory programmed customer specific devices with customized part numbers. The Possible Configurations table shows the available device types, but not complete part numbers. Contact your local Cypress FAE of Sales Representative for more information.

### **Possible Configurations**

| Part Number [7] | Configuration      | Package Description               | Product Flow                |

|-----------------|--------------------|-----------------------------------|-----------------------------|

| Pb-free         |                    |                                   |                             |

| CY2XF32LXCxxxT  | Factory Configured | 6-pin Ceramic LCC – Tape and Reel | Commercial, 0 °C to 70 °C   |

| CY2XF32LXIxxxT  | Factory Configured | 6-pin Ceramic LCC – Tape and Reel | Industrial, –40 °C to 85 °C |

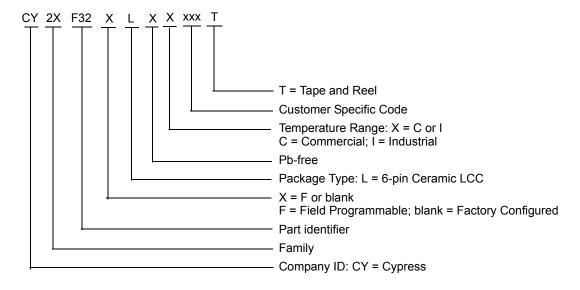

# **Ordering Code Definitions**

#### Note

Document Number: 001-53147 Rev. \*F

<sup>7. &</sup>quot;xxx" is a factory assigned code that identifies the programming option.

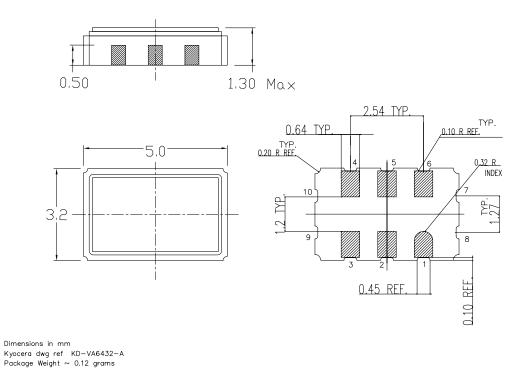

# **Package Diagram**

Figure 5. 6-pin Ceramic LCC (5.0 × 3.2 × 1.3 mm) LZ06A Package Outline, 001-10044

001-10044 \*C

# Acronyms

| Acronym | Description                             |  |  |

|---------|-----------------------------------------|--|--|

| CLKOUT  | Clock Output                            |  |  |

| CMOS    | Complementary Metal Oxide Semiconductor |  |  |

| DPM     | Die Pick Map                            |  |  |

| EPROM   | Erasable Programmable Read Only Memory  |  |  |

| LVDS    | Low-Voltage Differential Signaling      |  |  |

| NTSC    | National Television System Committee    |  |  |

| OE      | Output Enable                           |  |  |

| PAL     | Phase Alternate Line                    |  |  |

| PD      | Power-Down                              |  |  |

| PLL     | Phase Locked Loop                       |  |  |

| TTL     | Transistor-Transistor Logic             |  |  |

# **Document Conventions**

# **Units of Measure**

| Symbol | Unit of Measure             |  |  |

|--------|-----------------------------|--|--|

| °C     | degree Celsius              |  |  |

| kHz    | kilohertz                   |  |  |

| kΩ     | kilohm                      |  |  |

| MHz    | megahertz                   |  |  |

| ΜΩ     | megaohm                     |  |  |

| μΑ     | microampere                 |  |  |

| μs     | microsecond                 |  |  |

| μV     | microvolt                   |  |  |

| μVrms  | microvolts root-mean-square |  |  |

| mA     | milliampere                 |  |  |

| mm     | millimeter                  |  |  |

| ms     | millisecond                 |  |  |

| mV     | millivolt                   |  |  |

| nA     | nanoampere                  |  |  |

| ns     | nanosecond                  |  |  |

| nV     | nanovolt                    |  |  |

| Ω      | ohm                         |  |  |

| ppm    | parts per million           |  |  |

| W      | watt                        |  |  |

# **Document History Page**

| Document Title: CY2XF32, High Performance CMOS Oscillator with Frequency Margining – Pin Control Document Number: 001-53147 |         |                    |                    |                                                                                                                                                                                     |  |

|-----------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision                                                                                                                    | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                               |  |

| **                                                                                                                          | 2705753 | 05/13/09           | KVM /<br>PYRS      | New data sheet.                                                                                                                                                                     |  |

| *A                                                                                                                          | 2734005 | 07/09/2009         | WWZ                | Post to external web.                                                                                                                                                               |  |

| *B                                                                                                                          | 2764787 | 09/19/2009         | KVM                | Change $I_{SB}$ max from 250 $\mu$ A to 200 $\mu$ A Add max limit for $T_R$ , $T_F$ : 1.5 ns Change $T_{LOCK}$ max from 10 ms to 5 ms Change $T_{LFS}$ max from 10 ms to 1 ms       |  |

| *C                                                                                                                          | 2958629 | 06/22/10           | KVM                | Updated Ordering Information. Updated Package Diagram.                                                                                                                              |  |

| *D                                                                                                                          | 3169028 | 05/06/10           | BASH               | Changed status from Preliminary to Final. Added Ordering Code Definitions. Added Acronyms and Units of Measure. Updated template as per current Cypress standards.                  |  |

| *E                                                                                                                          | 4398514 | 06/04/2014         | AJU                | Updated Package Diagram: spec 001-10044 – Changed revision from *A to *B. Updated in new template. Completing Sunset Review.                                                        |  |

| *F                                                                                                                          | 4570063 | 11/14/2014         | AJU                | Added related documentation hyperlink in page 1. Removed the prune part number CY2XF32FLXCT in Ordering Information. Updated Figure 5 in Package Diagram (spec 001-10044 *B to *C). |  |

# Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Automotive Clocks & Buffers Interface

Lighting & Power Control

Memory

PSoC

Touch Sensing

USB Controllers

Wireless/RF

cypress.com/go/automotive cypress.com/go/clocks cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/plc cypress.com/go/memory cypress.com/go/psoc cypress.com/go/touch cypress.com/go/USB cypress.com/go/wireless

# PSoC® Solutions

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

# **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

# **Technical Support**

cypress.com/go/support

© Cypress Semiconductor Corporation, 2009-2014. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Phase Locked Loops - PLL category:

Click to view products by Cypress manufacturer:

Other Similar products are found below:

ADF4152HVBCPZ-RL7 HMC440QS16GTR LC72135MA-Q-AE SL28EB725ALI HMC698LP5ETR HMC699LP5ETR HMC700LP4TR LC7185-8750-E MB15E07SLPFV1-G-BND-6E1 XRT8001ID-F ATA8404C-6DQY-66 PI6C2409-1HWE ATA8405C-6DQY-66 MAX2870ETJ+T PI6C2409-1HWEX CYW170-01SXC HMC764LP6CETR HMC767LP6CETR HMC820LP6CETR HMC828LP6CETR HMC834LP6GETR ispPAC-CLK5410D-01SN64C SI4113-D-GM 82V3002APVG PI6C2405A-1WE CY22050KFI CY25200KFZXC CY29973AXI CY2XP22ZXI W232ZXC-10 CDCE937QPWRQ1 CY2077FZXI CY2546FC CY2XF23FLXIT CYISM560BSXC LMX2430TMX/NOPB HMC837LP6CETR HMC831LP6CETR ATA8404C-6DQY-66 ADF4155BCPZ-RL7 MB15E07SRPFT-G-BNDE1 NB3N5573DTG MAX2660EUT+T SI4123-D-GT SI4112-D-GM NB4N441MNR2G 9DB433AGILFT ADF4116BRUZ-REEL7 ADF4153ABCPZ MAX2682EUT+T