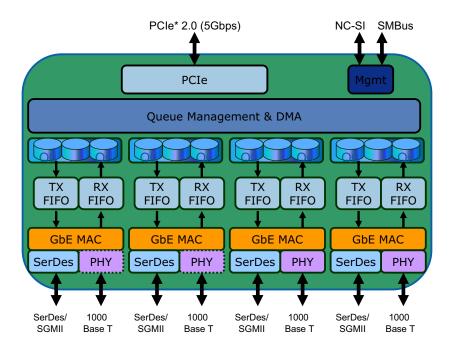

# Intel® 82580EB/82580DB Gigabit Ethernet Controller

# **Networking Division (ND)**

#### **FEATURES**

#### **External Interfaces Provided:**

- PCIe v2.0 (5Gbps and 2.5Gbps) x4/x2/x1; called PCIe in this document.

- MDI (Copper) standard IEEE 802.3 Ethernet interface for 1000BASE-T, 100BASE-TX, and 10BASE-T applications (802.3, 802.3u, and 802.3ab)

- Serializer-Deserializer (SERDES) to support 1000Base-SX/ LX (optical fiber)

- Serializer-Deserializer (SERDES) to support 1000BASE-KX and 1000BASE-BX for Gigabit backplane applications

- SGMII interface for SFP/external PHY connections

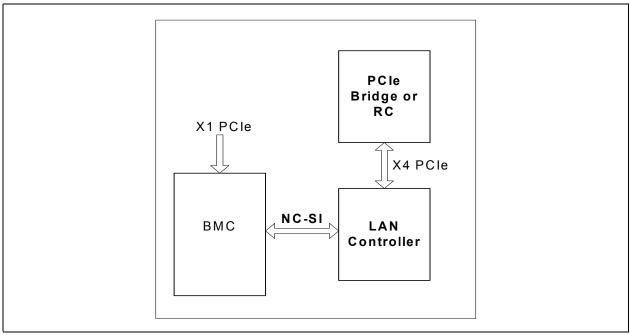

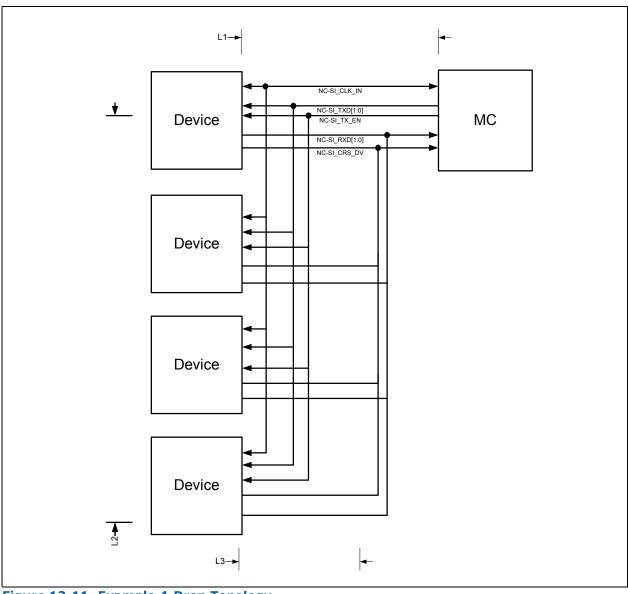

- NC-SI or SMBus for Manageability connection to MC

- IEEE 1149.6 JTAG

#### **Performance Enhancements:**

- Intel® I/O Acceleration Technology v3.0 supported:

- Stateless offloads (Header split, RSS)

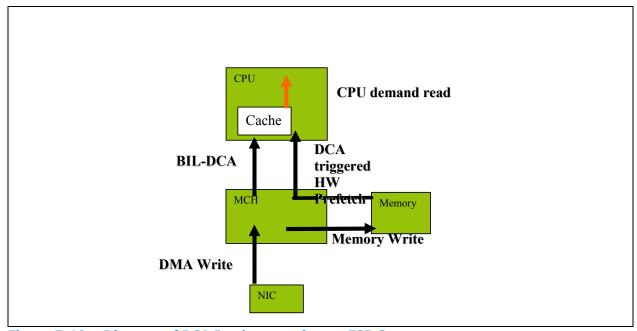

- Direct Cache Access

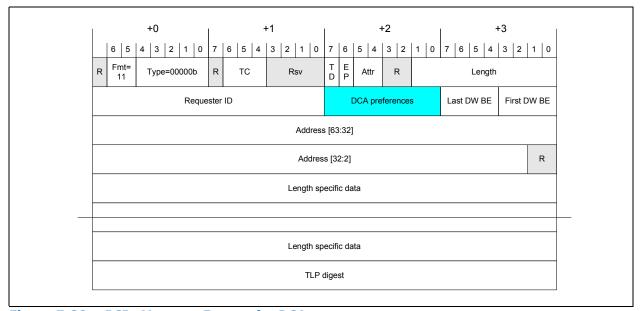

- PCIe v2.1 TLP Processing Hints (TPH)

- UDP, TCP and IP Checksum offload

- UDP and TCP Transmit Segmentation Offload (TSO)

- · SCTP receive and transmit checksum offload

#### Virtualization Ready:

- Enhanced VMDq1 support:

- Queues per port: 8 TX and 8 RX queues

- Support of up to 8 VMs per port (1 queue allocated to each VM)

#### iSCSI\*, PXE\* and UEFI\* Preboot Support

- iSCSI SerDes, Fiber and Copper in Windows/Linux. SGMII is not currently supported.

- PXE SerDes, Fiber, Copper, SGMII in Windows /Linux.

- UEFI SerDes, Fiber, Copper, SGMII in Windows/Linux.

#### **Power Saving Features:**

- Advanced Configuration and Power Interface (ACPI) power management states and wake-up capability

- · Advanced Power Management (APM) wake-up functionality

- Low power link-disconnect state

- PCIe v2.1 LTR (Latency Tolerance Reporting)

- DMA Coalescing for improved system power management

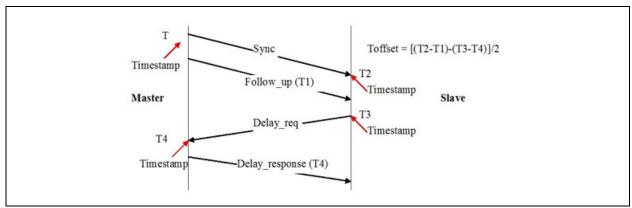

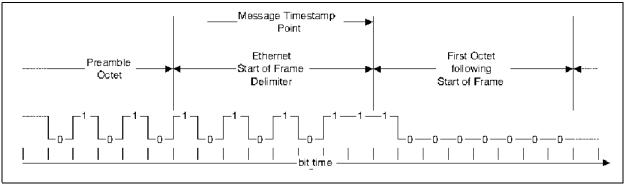

#### **IEEE802.1AS - Timing and Synchronization:**

- IEEE 1588 Precision Time Protocol support

- Per-packet timestamp

#### **Total Cost Of Ownership (TCO):**

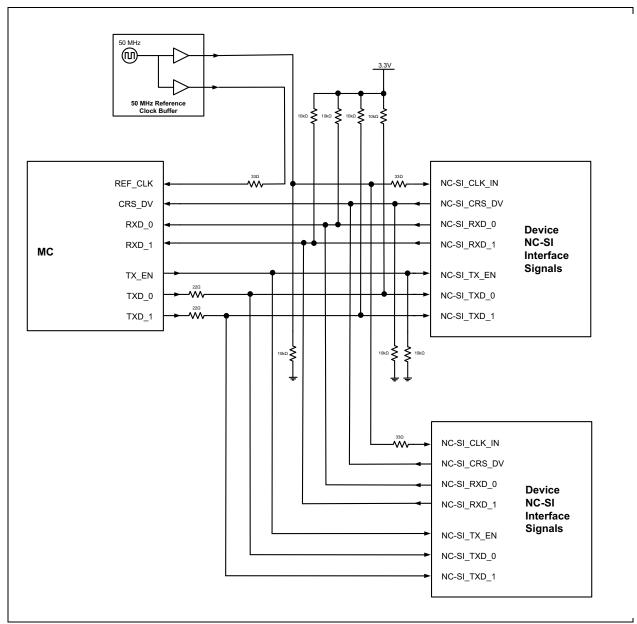

• IPMI MC pass-thru; multi-drop NC-SI

#### **Additional Product Details:**

- 17x17 PBGA package

- Estimated power: 2.8W (max) in dual port mode and 4.2W (max) in quad port mode

- Full data path Parity or ECC protection

Order # 333167-001 Revision: 2.7 September 2015

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

The products and services described may contain defects or errors which may cause deviations from published specifications. Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting www.intel.com/design/literature.htm.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

$\ensuremath{^{*}}$  Other names and brands may be claimed as the property of others.

© 2015 Intel Corporation.

# Revisions

| Rev  | Date         | Notes                                                                                                                                |

|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0.30 | Dec 2008     | Initial public release of early materials.                                                                                           |

| 0.31 | Jan 2009     | Chapter 2.0. Signals connected to the E14, F14, N12, R1, R2 and T1 corrected according to the latest ballout.                        |

|      |              | Section 11.4. Updated power consumption estimates.                                                                                   |

|      |              | Table 11-21. Corrected packaging information in the table. Now listed consistently as 17x17 PBGA package.                            |

| 0.5  | 2 April 2009 | Updated EAS source used as base.                                                                                                     |

| 1.0  | 12 June 2009 | Updated design information chapter added; supports Samples.                                                                          |

| 1.1  | 1 Oct 2009   | Editorial Changes.                                                                                                                   |

| 1.2  | 23 Oct 2009  | Chapter 12.0, Design Guidelines - 1.9V is no longer needed at the center tap. Language expressing that requirement has been removed. |

|      |              | Figure 11-1 and Table 11-3 updated to correct errors.                                                                                |

| 1.3  | 5 Jan 2010   | New EAS core added to Datasheet text.                                                                                                |

|      |              | Datasheet title updated to reflect dual and quad core capabilities.                                                                  |

|      |              | Datasheet title changed to cover. `Dual' added.                                                                                      |

|      |              | Section 1.0, Introduction language updated to indicate dual core support.                                                            |

|      |              | Table 2-7, SERDES/SGMII Pins updated; now includes dual port exclusions. See asterisks.                                              |

|      |              | Table 2-8, SFP Pins updated; now includes dual port exclusions. See asterisks.                                                       |

|      |              | Table 2-9, LED Output Pins updated; now includes dual port exclusions. See asterisks.                                                |

|      |              | Table 2-10, Analog Pins updated; now includes dual port exclusions. See asterisks.                                                   |

|      |              | Table 2-11, Testability Pins updated; now includes dual port exclusions. See asterisks.                                              |

|      |              | Table 2-15, Pin List in Alphabetical Order updated; now summarizes all dual port exclusions. See asterisks.                          |

|      |              | Table 4-4, PCI Functions Mapping (Legacy Mode) updated; information expanded.                                                        |

|      |              | Table 6-1, EEPROM Top Level Partitioning updated; now includes dual port exclusions. See asterisks.                                  |

| 2.0  | 15 Jan 2010  | Section 7.8.2.4, Size Filtering added.                                                                                               |

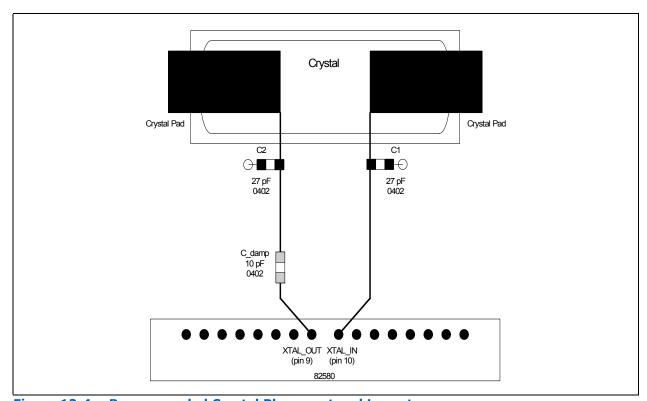

|      |              | Figure 12-4, Recommended Crystal Placement and Layout on page 697 updated.                                                           |

|      |              | Chapter 13.0, Thermal Management - Thermal management chapter added.                                                                 |

| 2.1  | 15 Jan 2010  | Test data updated.                                                                                                                   |

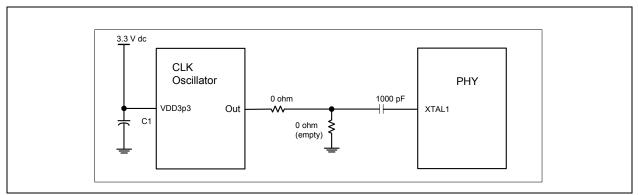

| 2.2  | 26 Feb 2010  | Figure 12-5, Oscillator Solution on page 698 updated.                                                                                |

|      |              | Table 12-3, Oscillator Manufacturers and Part Numbers updated.                                                                       |

|      |              | Confidential stamp removed from document for posting on Developer.                                                                   |

| 2.3  | 5 Mar 2010   | • In Section 13.4.4, Package Thermal Characteristics; Table 13-3 and Table 13-3 have been provided with updated data.                |

|      |              | Appendix C., Changes from the 82576; this appendix was added to the Datasheet.                                                       |

| Rev  | Date        | Notes                                                                                                                                                                                                   |

|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.4  | 29 Mar 2010 | In Section 6.2.5, Device ID (LAN Base Address + Offset 0x0D), the device ID was indicated as TBD because of a poorly set build variable. That has been corrected (Device ID = 1509).                    |

|      |             | <ul> <li>In Section 10.3.2.1.2, Request Status Command, the descriptive<br/>paragraph has been updated for clarity.</li> </ul>                                                                          |

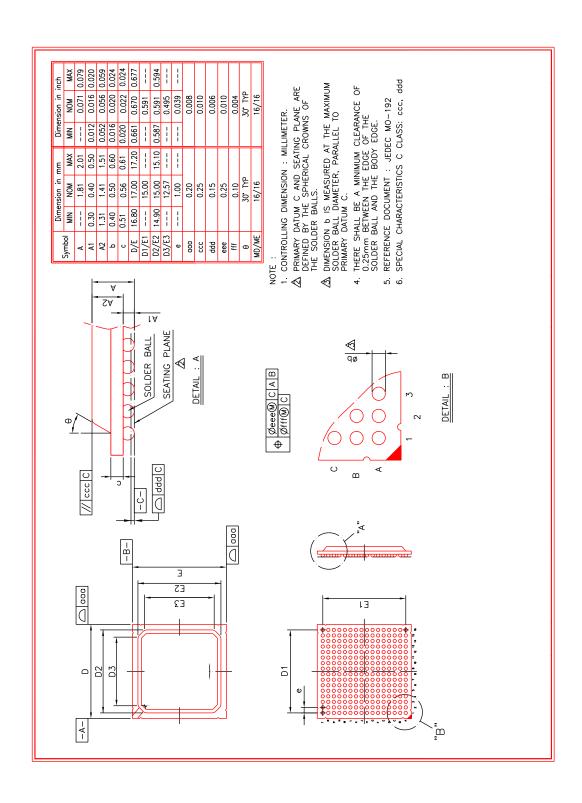

|      |             | • In Section 11.7.1, Mechanical; ball, solder, and pad information has been added to the section.                                                                                                       |

| 2.41 | 25 Jun 2010 | New sections:                                                                                                                                                                                           |

|      |             | Section 10.3.2.4, Filtering Over SMBus                                                                                                                                                                  |

|      |             | Section 10.3.2.4.5, SMBus Troubleshooting                                                                                                                                                               |

|      |             | Updated.                                                                                                                                                                                                |

|      |             | <ul> <li>Section 7.2.5.3, SCTP CRC Offloading updated. Note added: "Software<br/>must initialize the SCTP CRC field to zero (0x00000000) prior to<br/>requesting a CRC calculation offload."</li> </ul> |

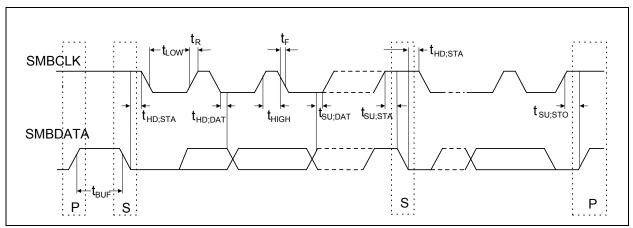

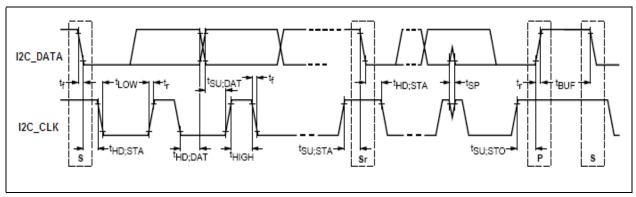

|      |             | Table 11-14, I <sup>2</sup> C Timing Parameters updated. See T <sub>HD:DAT</sub> .                                                                                                                      |

| 2.42 | 7 Jul 2010  | The PCIe PHY Auto Configuration Pointer is not supported. The discussion of this capability has been removed from the datasheet.                                                                        |

|      |             | Two EEPROM registers exposed:                                                                                                                                                                           |

|      |             | Section 6.2.14, PCIe Init Configuration 1 (Word 0x18)                                                                                                                                                   |

|      |             | Section 6.2.15, PCIe Init Configuration 2 Word (Word 0x19)                                                                                                                                              |

|      |             | Section 6.2.16, PCIe Init Configuration 3 Word (Word 0x1A)                                                                                                                                              |

| 2.43 | 20 Aug 2010 | Updated:                                                                                                                                                                                                |

|      |             | Table 2-13, Pull-Up Resistors. For NCSI_CRS_DV change Note 2 to Note 1. For NCSI_TXD[1:0] changed PD to PU.                                                                                             |

|      |             | <ul> <li>Section 6.11.5, PBA Number Module (Word 0x08, 0x09). This field has<br/>been updated. Its format has been changed.</li> </ul>                                                                  |

|      |             | <ul> <li>Section 11.3.1, Power Supply Specification. Value for Max Decoupling<br/>Capacitance changed to N/A</li> </ul>                                                                                 |

|      |             | Section 11.6.6, Oscillator Support. Information on this topic is now in Section 12.5.                                                                                                                   |

| 2.44 | 9/16/2010   | Updated:                                                                                                                                                                                                |

|      |             | • Section 6.11.5, PBA Number Module (Word 0x08, 0x09). Language updated to address questions about final format.                                                                                        |

| 2.45 | 10/13/2010  | In the 2.44 build, the link to the Appendix did not appear in the PDF. This build fixes the issue. Also updated legal section.                                                                          |

| Rev  | Date      | Notes                                                                                                                                                                                                            |         |

|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 2.46 | 3/23/2011 | Updated document title to better reflect brand string.                                                                                                                                                           |         |

|      |           | Table 3-9, Allocation of FC Credits. First row cell text changed. Cha<br>to: "Sixteen credit units to support tail write at wire speed."                                                                         | nged    |

|      |           | Section 6.11.1, Compatibility (Word 0x03). Word description updat                                                                                                                                                | ed.     |

|      |           | Section 6.11.2, Port Identification LED blinking (Word 0x04). Word description updated.                                                                                                                          |         |

|      |           | Section 6.11.6.1, Setup Options PCI Function 0 (Word 0x30). Bits a redefined.                                                                                                                                    | 2:0     |

|      |           | Section 7.2.2.3.9, PAYLEN (18). Note text updated.                                                                                                                                                               |         |

|      |           | Section 8.12.16, Tx Descriptor Completion Write–Back Address Lov TDWBAL (0xE038 + 0x40*n [n=07]; R/W). 32:2 bit description updated.                                                                             | V -     |

|      |           | Section 8.22.4, Management Control Register - MANC (0x5820; RV expression (20:2019) a typo. Corrected to 20:19.                                                                                                  | V). Bit |

|      |           | Table 11-24, Discrete/Integrated Magnetics Specifications. Added t section with complete information on magnetics.                                                                                               | able,   |

|      |           | Section 12.4.1.6, Load Capacitance. Text updated (formula correct                                                                                                                                                | ed).    |

| 2.47 | 4/6/2011  | Section 11.7.4, Package Schematics. Figure updated. Extraneous c removed.                                                                                                                                        | ircle   |

| 2.48 | 5/10/2011 | Section 6.11.2, Port Identification LED blinking (Word 0x04). Text i section updated to better describe behavior.                                                                                                | n       |

| 2.49 | 8/22/2011 | Table 6-2; 0x23 link fixed.                                                                                                                                                                                      |         |

|      |           | • Section 8.5.5, Flow Control Receive Threshold Low - FCRTL0 (0x21 W). Phrase changed: "1b (at least 16 bytes)" to "3b (at least 48 by                                                                           |         |

|      |           | • Table 10-2: In third row, existing text the existing text: "Supports of 2 and also supports the following counters only when the OS is down 6, 7" has been changed to: "Supports the following counters: 1, 2, | vn: 1,  |

|      |           | Section 13.2, Note added at end of section: "For the 82580EB/DB, is calculated at 123° C."                                                                                                                       | Tjmax   |

| Rev  | Date                 | Notes                                                                                                                                                                                                                                                                         |

|------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.50 | 10/20/2011           | More Preboot data added to feature summary on page 1.                                                                                                                                                                                                                         |

|      |                      | Section 1.4.2, Network Interfaces. Note added. States that old MDI flip-<br>chip option not supported.                                                                                                                                                                        |

|      |                      | Section 1.4.3, EEPROM Interface. Note on EEPROMless support added.<br>States clearly that EEPROMless mode is not supported.                                                                                                                                                   |

|      |                      | Section 1.4.5, SMBus Interface. Statement added. Makes performance requirement clear: "For best performance, each 82580EB/DB should have its own dedicated SMBus link to the SMBus master device."                                                                            |

|      |                      | Section 1.6.12.2, Time SYNC (IEEE1588 and IEEE 802.1AS). Statement added. Clearly defines the limited nature of 1588 support.                                                                                                                                                 |

|      |                      | Table 2-6, Miscellaneous Pins. Note added to TSENSP; Note states limits of TSENSP/Z use. Refers to thermal chapter.                                                                                                                                                           |

|      |                      | Table 2-10, Analog Pins. Error corrected. RSVD_TX_TCLK clock speed indicated as 125 MHz instead of 1.25 MHz.                                                                                                                                                                  |

|      |                      | Section 2.5, Pin List (Alphabetical), Section 2.6, Ball-Out. Note added.     Makes clear statement about proper handling for 'unused pins'.                                                                                                                                   |

|      |                      | Section 6.2.15, PCIe Init Configuration 2 Word (Word 0x19). Note added to IO_Sup, bit14. The note defines 'disable I/O mode'.                                                                                                                                                 |

|      |                      | • Section 6.2.22, Functions Control (Word 0x21), bit 9 description; Section 9.4.11.2, 64-bit BARs Mode Mapping, bit 3 description. Description has been changed. New text for both: "This bit should be set only on systems that do not generate prefetchable cycles."        |

|      |                      | Table 8-10, Usable FLASH Size and CSR Mapping Window Size. Table added to Datasheet.                                                                                                                                                                                          |

|      |                      | • Section 11.3, Power Delivery. Sentence added. Makes the following clear statement about power delivery: "The device requires the following power supplies: 3.3v, 1.8v, 1.0v. All 82580EB/DB power should be derived from AUX power."                                        |

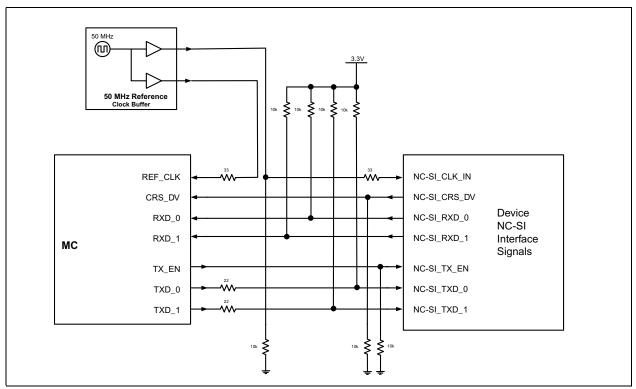

| 2.51 | September 7,<br>2012 | Section 2.1.4, NC-SI Interface Pins. Notes added. They specify pull-ups/<br>downs used when NC-SI is disconnected.                                                                                                                                                            |

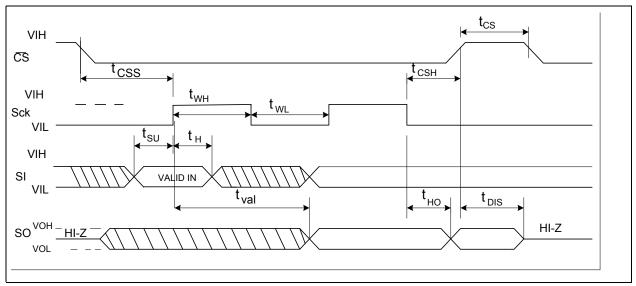

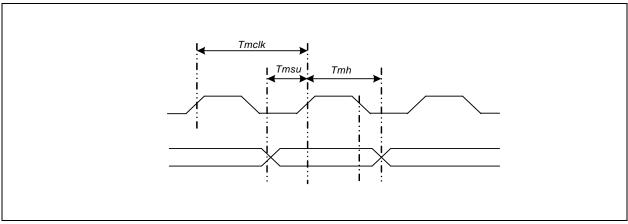

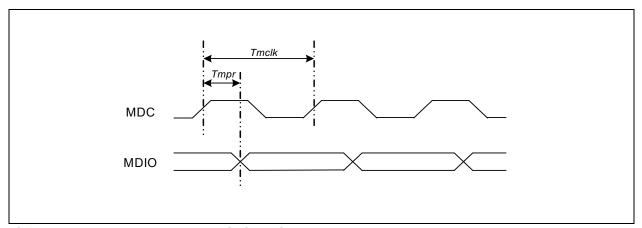

|      |                      | Section 5.5.5, Timing Requirements, Section 5.5.6, Timing Guarantees; both added to the datasheet.                                                                                                                                                                            |

|      |                      | • Section 8.8.10, Interrupt Cause Set Register - ICS (0x1504; WO), Section 8.8.11, Interrupt Mask Set/Read Register - IMS (0x1508; R/W), Section 8.8.12, Interrupt Mask Clear Register - IMC (0x150C; WO); Time Sync Bit [19] added to the datasheet for all three registers. |

|      |                      | • Section 9.6.4.2, LTR Capabilities (0x1C4; RW). Description of Bits 15:13 and 31:29 corrected to RO.                                                                                                                                                                         |

| 2.6  | June 2014            | <ul> <li>Revised sections:</li> <li>6.2.17</li> <li>3.2.1.1.4</li> <li>3.5.6.3.1</li> <li>7.8.9</li> <li>3.5.6.4 (new)</li> <li>Revised tables:</li> <li>2-15</li> </ul>                                                                                                      |

| 2.7  | September 2015       | 7-6  • Revised sections 6.11.7                                                                                                                                                                                                                                                |

|      |                      | Revised Table 11-22                                                                                                                                                                                                                                                           |

# Contents

| 1.0            |                 | on                                                            |            |

|----------------|-----------------|---------------------------------------------------------------|------------|

| 1.1            | Scope           |                                                               | 20         |

| 1.2            | Terminolog      | y and Acronyms<br>External Specification and Documents        | 20         |

| 1.3            | 1.2.1           | erviewerview                                                  |            |

| 1.4            | External Int    | terface                                                       | 22         |

| 1.4            | 1.4.1           | PCIe Interface                                                | 23         |

|                | 1.4.2           | Network Interfaces                                            | 23         |

|                | 1.4.3           | EEPROM Interface                                              | 23         |

|                | 1.4.4           | Serial Flash Interface                                        | 23         |

|                |                 | SMBus Interface                                               |            |

|                | 1.4.6           | NC-SI Interface                                               | 24         |

|                | 1.4.7           | MDIO/I <sup>2</sup> C 2 wires Interfaces                      | 24         |

|                | 1.4.8           | Software-Definable Pins (SDP) Interface (General-Purpose I/O) | . 24       |

| 1 5            | 1.4.9           | LEDs Interface                                                | 25         |

| 1.5<br>1.6     | Overview of     | f Changes Compared to the 82576                               | 23         |

| 1.0            | 1.6.1           | Network Interface                                             | 28         |

|                | 1.6.2           | HOST Interface                                                | 29         |

|                | 1.6.3           | Boundary Scan                                                 | 30         |

|                | 1.6.4           | Performance Features                                          | 30         |

|                | 1.6.5           | Receive and Transmit Queues                                   | 30         |

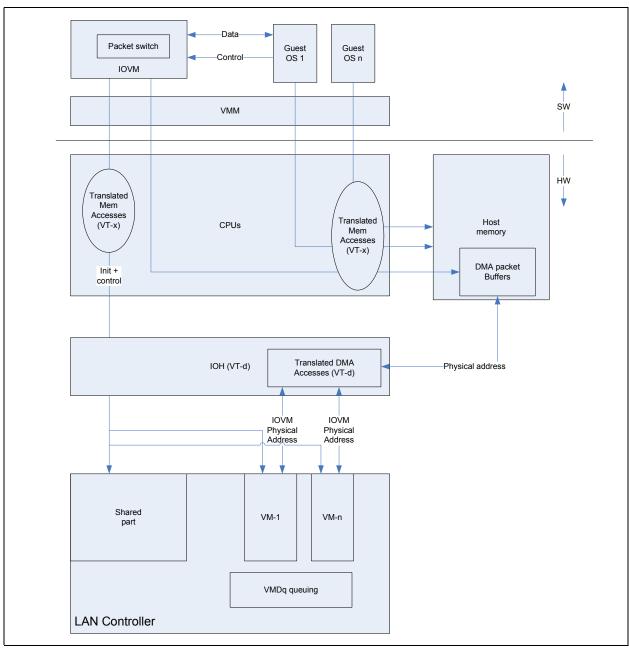

|                | 1.6.6           | Virtualization                                                | 31         |

|                | 1.6.7           | Malicious Driver Detection                                    | 31         |

|                | 1.6.8           | 2-tuple filtering                                             | 31<br>21   |

|                | 1.6.9<br>1.6.10 | Quality of Service                                            | 21         |

|                | 1.6.11          | Manageability                                                 | 32         |

|                |                 | Embedded Features                                             |            |

|                | 1.6.13          | Power Saving                                                  | 34         |

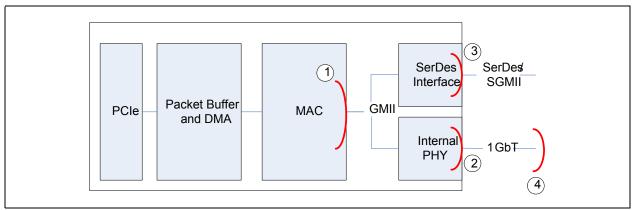

| 1.7            | Device Data     | a Flows                                                       | 35         |

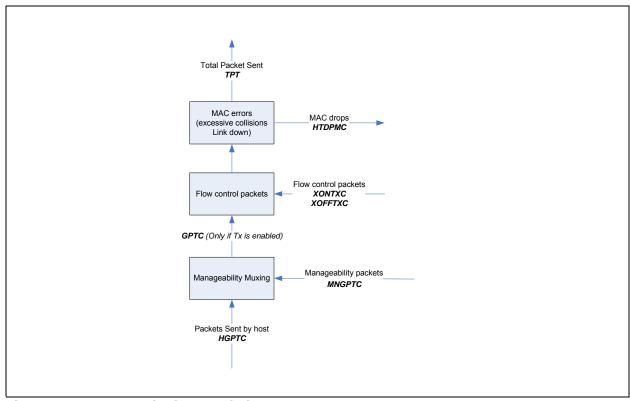

|                | 1.7.1           | Transmit Data Flow                                            | . 35       |

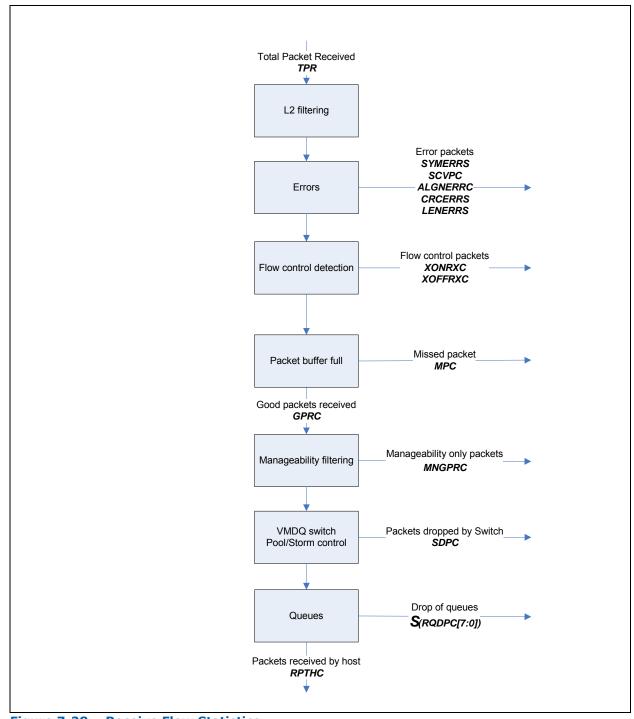

|                | 1.7.2           | Receive Data Flow                                             | 35         |

| 2.0            | Pin Interfa     | ace                                                           | .37        |

| <b>2.0</b> 2.1 |                 | nent                                                          |            |

|                | 2.1.1           | PCIe                                                          | 37         |

|                | 2.1.2           | Flash and EEPROM Ports System Management Bus (SMB) Interface  | 38         |

|                | 2.1.3           | System Management Bus (SMB) Interface                         | . 39       |

|                | 2.1.4           | NC-SI Interface Pins                                          | 39         |

|                | 2.1.5           | Miscellaneous Pins                                            | 40         |

|                | 2.1.6<br>2.1.7  | SERDES/SGMIT PINS                                             | 41         |

|                | 2.1.8           | PHY Pins                                                      | 43         |

|                | 2.1.9           | Testability Pins                                              | 48         |

|                | 2.1.10          | Testability Pins Power Supply and Ground Pins                 | . 50       |

| 2.2            | Pullups/Pull    | downs                                                         | . 50       |

| 2.2<br>2.3     | Strapping       |                                                               | 53         |

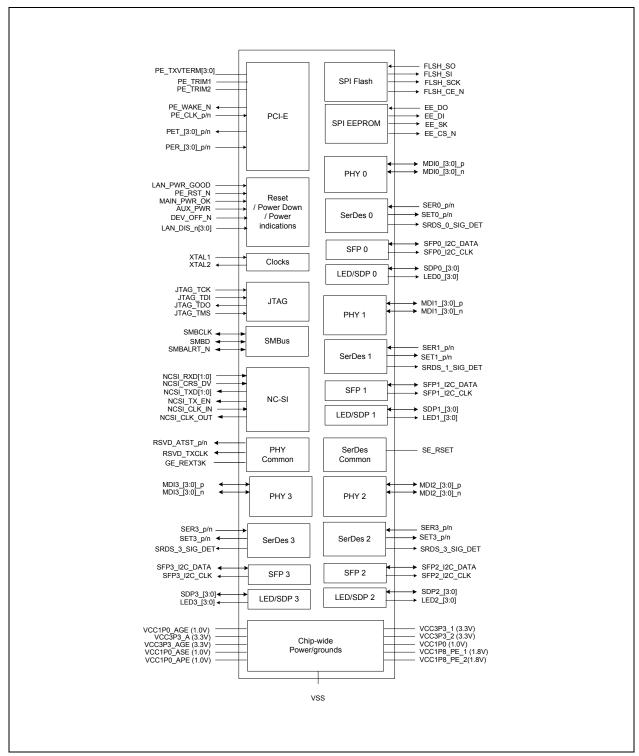

| 2.4            | Interface D     | iagram                                                        | 54         |

| 2.5            | Pin List (Alp   | phabetical)                                                   | <u> 55</u> |

| 2.6            |                 |                                                               |            |

| 3.0            | Interconn       | ects                                                          | .59        |

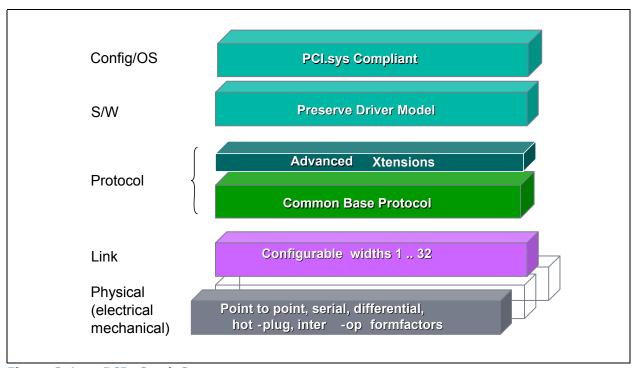

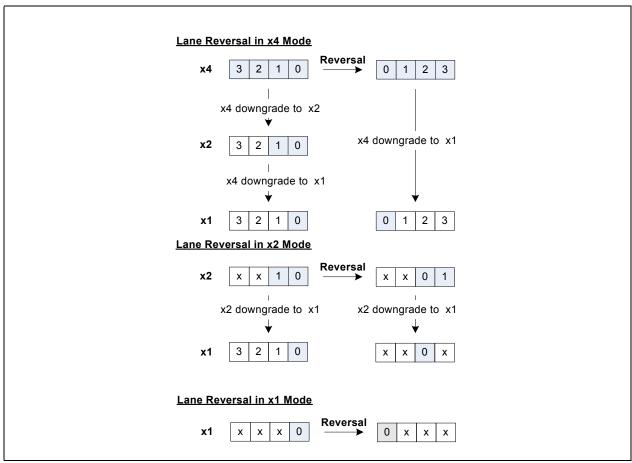

| 3.1            | PCIe            |                                                               | 59         |

|                | 3.1.1           | PCIe Overview                                                 | . 59       |

|                | 3.1.2           | Functionality - General                                       | 61         |

|                |                 | Host Interface                                                |            |

|                |                 | Transaction Layer                                             |            |

|                |                 | Physical Layer                                                |            |

|                |                 | Error Events and Error Reporting                              |            |

|                | 3.1.8           | PCIe Power Management                                         | 81         |

|                | 3.1.9           | PCIe Programming Interface                                    | 81         |

| 3.2            | Managemer       | nt Interfaces                                                 | 82         |

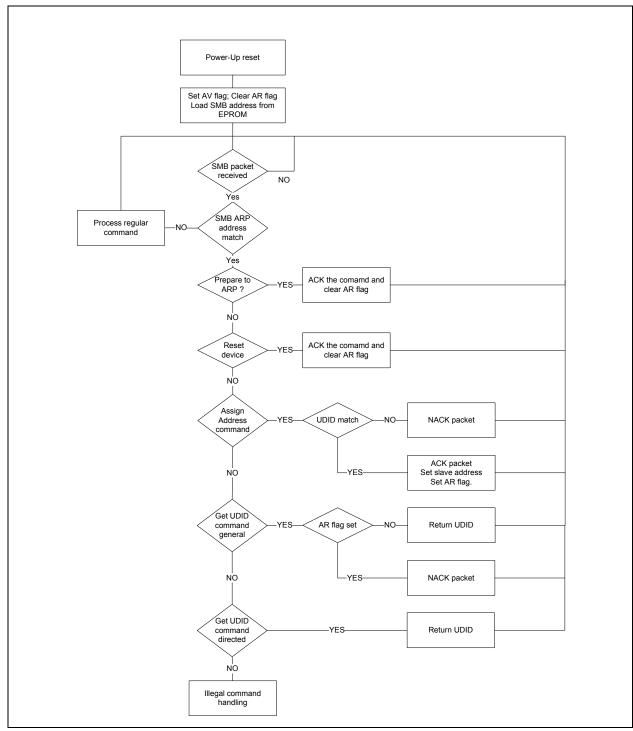

|                | 3.2.1           | SMBus                                                         | 82         |

|                |                 | NC-SI                                                         |            |

| 3.3            |                 | ROM                                                           |            |

|                |                 | EEPROM Interface                                              |            |

|                | 3.3.2           | Shared EEPROM                                                 | 1 U 1      |

|                |                 | Flash Interface                                               |            |

|                |                 |                                                               | 104        |

| 3.4        | Configurab       | le I/O Pins                                                 | 105                    |

|------------|------------------|-------------------------------------------------------------|------------------------|

|            | 3.4.1            | General-Purpose I/O (Software-Definable Pins)               | 10                     |

|            | 3.4.2            | Software Watchdog                                           | 10                     |

|            |                  | LEDs                                                        | 100                    |

| 3.5        |                  | terfaces                                                    |                        |

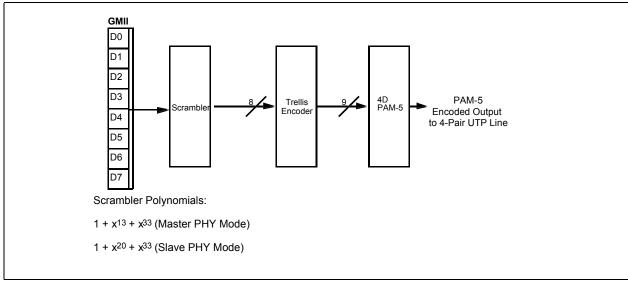

| 3.3        | 3.5.1            | Overview                                                    |                        |

|            |                  | WAC Functionality                                           | 109                    |

|            | 3.5.3            | MAC Functionality                                           | 11                     |

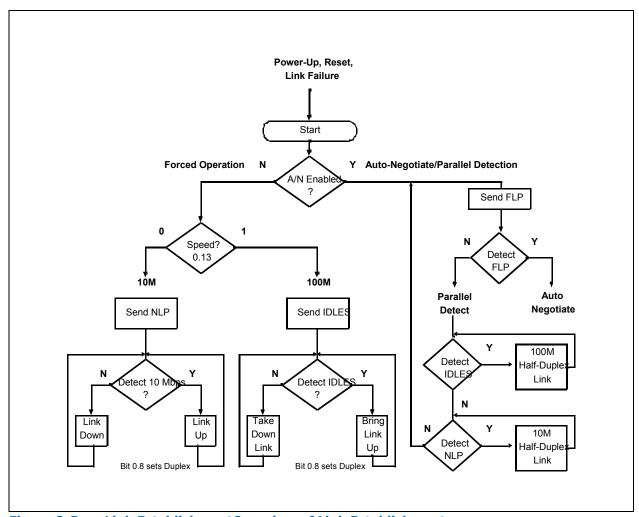

|            | 3.5.4            | Auto-Negotiation and Link Setup Features                    | 117                    |

|            | 3.5.5            | Ethernet Flow Control (FC)                                  | 120                    |

|            | 3.5.6            | Loopback Support                                            | 12                     |

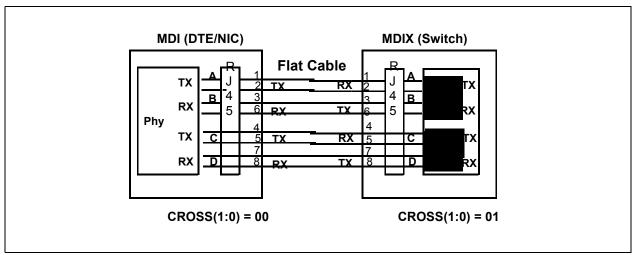

|            | 3.5.7            | Integrated Copper PHY Functionality                         | 12                     |

|            | 3.5.8            | Media Auto Sense                                            | 1/1                    |

|            | 0.0.0            |                                                             |                        |

| 4.0        | Initializat      | ion                                                         | 149                    |

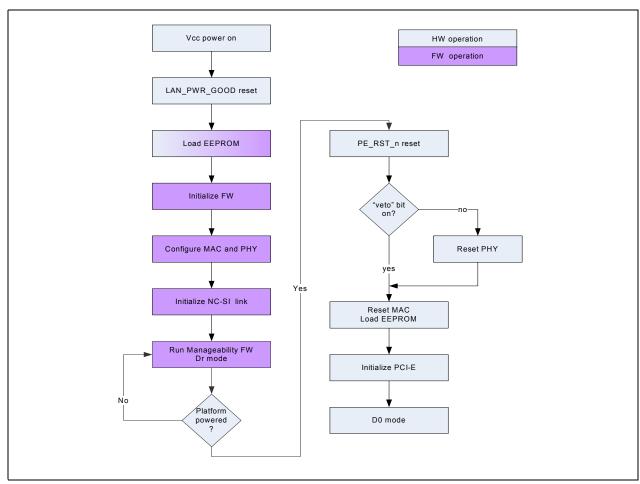

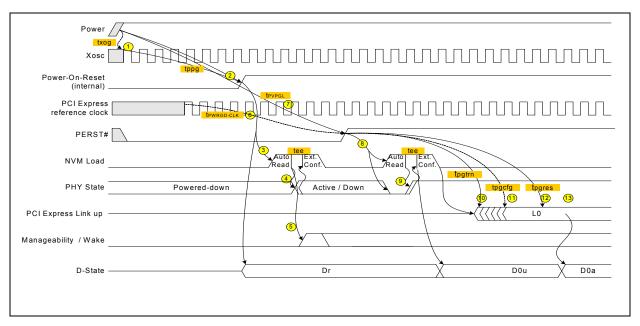

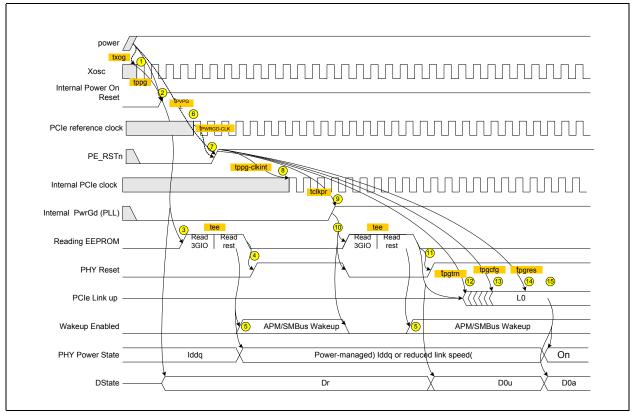

| 4.1        | Power Up         |                                                             | 149                    |

|            | 4.1.1            | Power-Up Sequence                                           | 149                    |

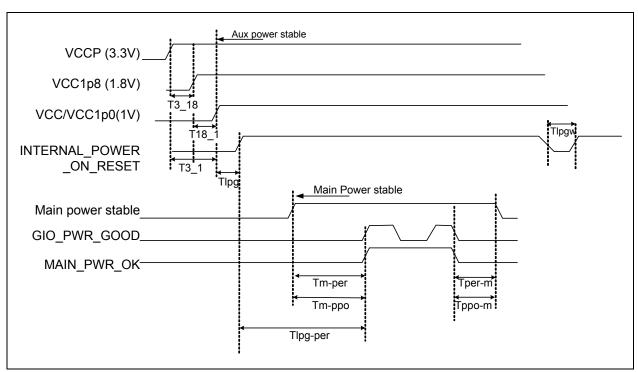

|            | 4.1.2            | Power-Up Timing Diagram                                     | 150                    |

| 4.2        | Reset Oper       | ation                                                       | 15                     |

|            | 4.2.1            | Reset Sources                                               | 15                     |

| 4.3        |                  | eset                                                        |                        |

| 1.5        | 4.3.1            | Port Software Reset (RST)                                   |                        |

|            | 4.3.2            | Device Software Reset (DEV_RST)                             | 15                     |

|            | 4.3.3            | Reset Effects                                               | 156                    |

|            | 4.3.4            | PHY Behavior During a Manageability Session                 | 160                    |

| 4.4        |                  | isable                                                      | 16                     |

| т. т       | 4.4.1            | General                                                     |                        |

|            | 4.4.2            | Overview                                                    | 10.                    |

|            |                  | Overview Ontions                                            | 10.                    |

|            |                  | Control Options                                             | 10.                    |

| <b>4</b> F | 4.4.4            | EVENT Flow for Enable/Disable Functions                     | 104                    |

| 4.5        | Device Disa      | able                                                        | 103                    |

|            | 4.5.1            | BIOS Handling of Device Disable                             | 100                    |

| 4.6        |                  | nitialization and Diagnostics                               | 100                    |

|            | 4.6.1            | Introduction                                                | 100                    |

|            |                  | Power Up State                                              |                        |

|            | 4.6.3            | Initialization Sequence                                     | 16                     |

|            | 4.6.4            | Interrupts During Initialization                            | 167                    |

|            | 4.6.5            | Global Reset and General Configuration                      |                        |

|            | 4.6.6            | Flow Control Setup                                          | 167                    |

|            | 4.6.7            | Link Setup Mechanisms and Control/Status Bit Summary        | 168                    |

|            | 4.6.8            | Initialization of Statistics                                | 172                    |

|            | 4.6.9            | Receive Initialization                                      | 173                    |

|            | 4.6.10           | Transmit Initialization                                     | 174                    |

|            | 4.6.11           | Virtualization Initialization Flow                          | 175                    |

| 4.7        | Access to s      | hared resources                                             | 176                    |

| ,          | 4.7.1            | Acquiring ownership over a shared resource                  | 17                     |

|            | 4.7.2            | Releasing ownership over a shared resource                  | 17                     |

|            | 4.7.3            | Software to Software Mailbox                                | 170                    |

|            |                  |                                                             |                        |

| 5.0        | Power Ma         | nagement                                                    | 18:                    |

| 5.1        |                  | wer State Information                                       |                        |

|            | 5.1.1            | PCI Device Power States                                     |                        |

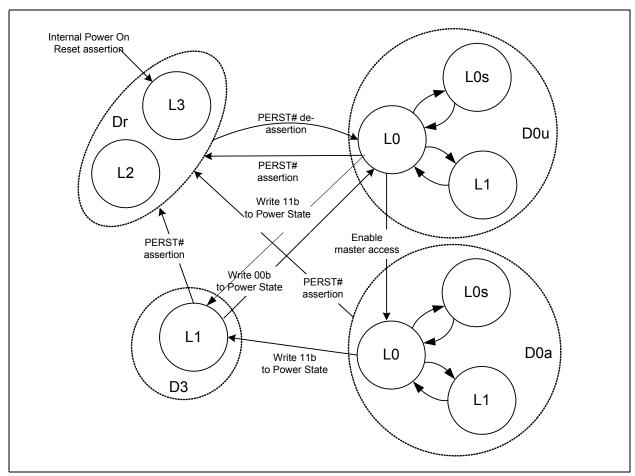

|            | 5.1.2            | PCIe Link Power States                                      |                        |

| 5.2        | Power State      | es                                                          | 182                    |

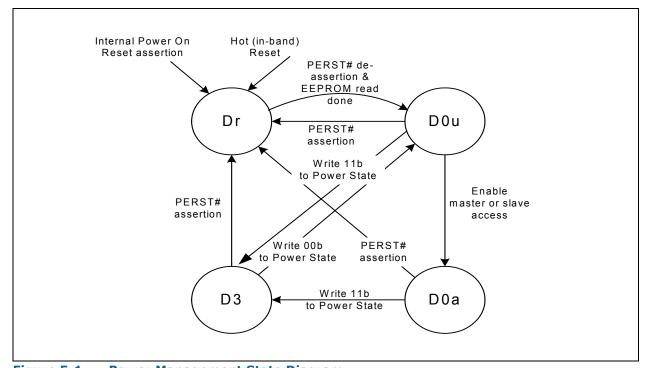

|            | 5.2.1            | D0 Uninitialized State (D0u)                                | 183                    |

|            | 5.2.2            | D0active State                                              | 184                    |

|            | 5.2.3            | D3 State (PCI-PM D3hot)                                     | 184                    |

|            | 5.2.4            | Dr State (D3cold)                                           |                        |

|            | 5.2.5            | Link Disconnect                                             |                        |

|            | 5.2.6            | Device Power-Down State                                     |                        |

| 5.3        | Power Limit      | ts by Certain Form Factors                                  |                        |

| 5.4        | Interconne       | cts Power Management                                        | 189                    |

|            | 5.4.1            | PCIe Link Power Management                                  | 180                    |

|            | 5.4.2            | NC-SI Clock Control                                         |                        |

|            |                  | Internal PHY Power-Management                               |                        |

| 5.5        |                  | Ower-State Transitions                                      |                        |

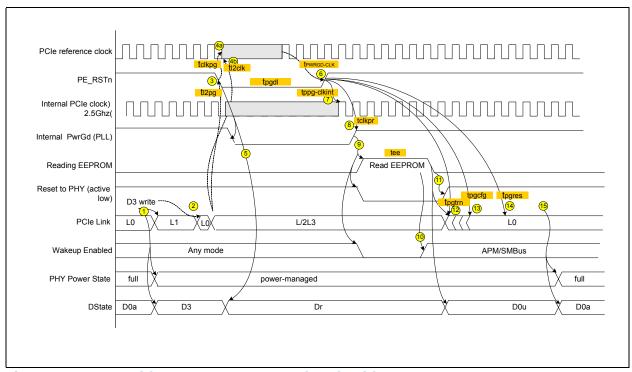

| J.J        | 551              | Power Un (Off to Dun to Duy to Dua                          | 191                    |

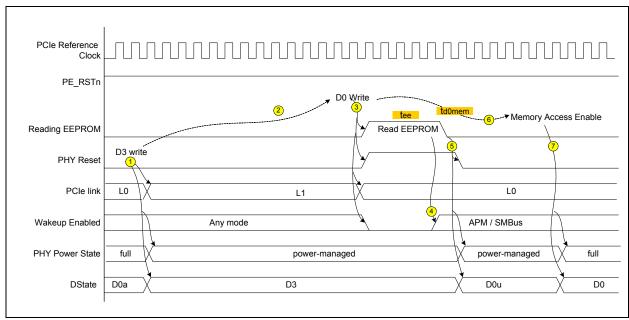

|            | 5.5.2            | Transition from D0a to D3 and Back Without PE_RST_N         | 10                     |

|            | 5.5.2<br>5.5.3   | Transition From D0a to D3 and Back WithOut PE_RST_N         | 10                     |

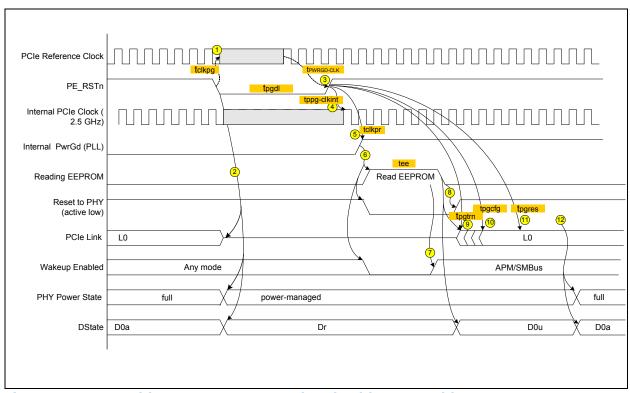

|            | 5.5.3<br>5.5.4   | Transition From D0a to D7 and Back Without Transition to D3 | 101                    |

| 5.6        | J.J.4<br>Maka Ua | Transition From Dua to Dr and Dack Without Hallstron to D3  | 10,                    |

| ٥.٥        | wake up          | Advanced Power Management Wake Up                           | 136                    |

|            | 5.6.1            | AUVAILEU TOWER MANAGEMENT WAKE UP                           | 126                    |

|            | 5.6.2            | PCIe Power Management Wake Up                               | 19                     |

| _ ¬        |                  | Wake-Up Packets                                             |                        |

| 5.7        |                  | scing                                                       | 203                    |

|            | 5.7.1            | LITTER IN DISTA COMESCING OPERALING MODE                    | <b>ZU</b> <sup>2</sup> |

|     | 5.7.2            | Conditions to Exit DMA Coalescing                                                                                     | 205        |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------|------------|

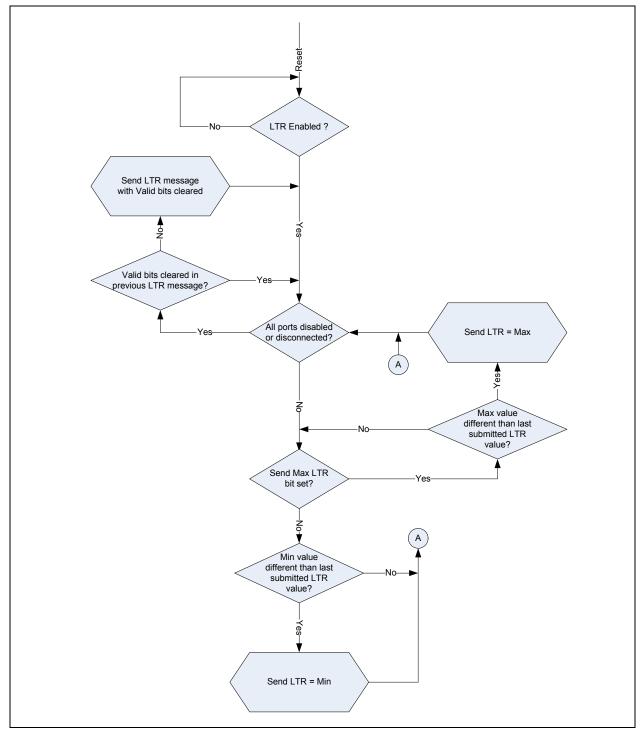

| 5.8 |                  | olerance Reporting (LTR)                                                                                              | 205        |

|     | 5.8.1            | Latency Tolerance Reporting Per Function                                                                              |            |

| 6.0 | Non-Vola         | atile Memory Map - EEPROM                                                                                             | 211        |

| 6.1 | EEPROM (         | General Map                                                                                                           | 211        |

| 6.2 |                  | Accessed Words                                                                                                        | 214        |

|     | 6.2.1            | Ethernet Address (LAN Base Address + Offsets 0x00-0x02)                                                               | 214        |

|     | 6.2.2<br>6.2.3   | Initialization Control Word 1 (word 0x0A)Subsystem ID (Word 0x0B)                                                     | 215        |

|     | 6.2.4            | Subsystem ID (Word 0x0B)                                                                                              | 216        |

|     | 6.2.5            | Subsystem Vendor ID (Word 0x0C)                                                                                       | 216        |

|     | 6.2.6            | Vendor ID (Word 0x0F)                                                                                                 | 216        |

|     | 6.2.7            | Dummy Device ID (Word 0x1D)                                                                                           | 216        |

|     | 6.2.8            | Initialization Control Word 2 (Word 0x0F)                                                                             | 216        |

|     | 6.2.9            | EEPROM Sizing and Protected Fields (Word 0x12). Initialization Control 4 (LAN Base Address + Offset 0x13)             | 217        |

|     | 6.2.10<br>6.2.11 | Initialization Control 4 (LAN Base Address + Offset UX13)                                                             | 219        |

|     | 6.2.11           | PCIe L1 Exit latencies (Word 0x14) PCIe Completion Timeout Configuration (Word 0x15)                                  | 220        |

|     | 6.2.13           | MSI-X Configuration (LAN Base Address + Offset 0x16)                                                                  | 221        |

|     | 6.2.14           | PCIe Init Configuration 1 (Word 0x18)                                                                                 | 221        |

|     | 6.2.15           | PCIe Init Configuration 2 Word (Word 0x19)                                                                            | 222        |

|     | 6.2.16           | PCIe Init Configuration 3 Word (Word 0x1A)                                                                            | 222        |

|     | 6.2.17           | PCIe Control 1 (Word 0x1B)<br>LED 1,3 Configuration Defaults (LAN Base Address + Offset 0x1C)                         | 223        |

|     | 6.2.18           | LED 1,3 Configuration Defaults (LAN Base Address + Offset 0x1C)                                                       | 223        |

|     | 6.2.19<br>6.2.20 | Device Rev ID (Word 0x1E)                                                                                             | 224        |

|     | 6.2.21           | LED 0,2 Configuration Defaults (LAN Base Address + Offset 0x1F)                                                       | 226        |

|     | 6.2.22           | Functions Control (Word 0x21)                                                                                         | 227        |

|     | 6.2.23           | LAN Power Consumption (Word 0x22) Initialization Control 3 (LAN Base Address + Offset 0x24)                           | 229        |

|     | 6.2.24           | Initialization Control 3 (LÀN Base Address + Offset 0x24)                                                             | 229        |

|     | 6.2.25           | PCIe Control 2 (Word 0x28) PCIe Control 3 (Word 0x29)                                                                 | 230        |

|     | 6.2.26           | PCIe Control 3 (Word 0x29)                                                                                            | 231        |

|     | 6.2.27           | End of Read-Only (RO) Area (Word 0x2C)<br>Start of RO Area (Word 0x2D)                                                | 231        |

|     | 6.2.28<br>6.2.29 | Watchdog Configuration (Word 0x2E)                                                                                    | 23         |

|     | 6.2.30           | VPD Pointer (Word 0x2F)                                                                                               | 232        |

| 6.3 | CCD Auto         | Configuration Dointor                                                                                                 |            |

|     | (LAN Base        | Collingulation Foliate e Address + Offset 0x17) CSR Configuration Section Length - Offset 0x0 Block CRC8 (Offset 0x1) | 232        |

|     | 6.3.1            | CSR Configuration Section Length - Offset 0x0                                                                         | 233        |

|     | 6.3.2            | Block CRC8 (Offset 0x1)                                                                                               | 233        |

|     | 6.3.3            | CSR Address - (Offset 3*n - 1; [n = 1 Section Length])                                                                | 233        |

|     | 6.3.4<br>6.3.5   | CSR Address - (Offset 3*n - 1; [n = 1 Section Length])                                                                | 233        |

| 6.4 | CCD Auto         | Configuration Dowor-Un Dointor                                                                                        |            |

| 0.4 | (LAN Base        | e Address + Offset 0x27)  CSR Configuration Power-Up Section Length - Offset 0x0                                      | 233        |

|     | 6.4.1            | CSR Configuration Power-Up Section Length - Offset 0x0                                                                | 234        |

|     | 6.4.2            | BIOCK ( BL & LOTTS OF LIV I )                                                                                         | 732        |

|     | 6.4.3            | CSR Address - (Offset 3*n - 1; [n = 1 Section Length]) CSR Data LSB - (Offset 3*n; [n = 1 Section Length])            | 234        |

|     | 6.4.4            | CSR Data LSB - (Offset 3*n; [n = 1 Section Length])                                                                   | 234        |

| 6.5 | 6.4.5            | CSR Data MSB - (Offset 3*n + 1; [n = 1 Section Length])                                                               | 235        |

| 6.6 | Firmware         | (Word 0x10) Pointers and Control Words                                                                                | 235        |

| 0.0 | 6.6.1            | Pace Through LAN Configuration Pointer                                                                                |            |

|     |                  | (LAN Base Address + Offset 0x11) Management HW Config Control (Word 0x23)                                             | 235        |

|     | 6.6.2            | Management HW Config Control (Word 0x23)                                                                              | 235        |

|     | 6.6.3            | PHY Configuration Pointer (Word 0x50)                                                                                 |            |

|     | 6.6.4            | Firmware Patch Pointer (Word 0x51)                                                                                    | 236        |

|     | 6.6.5<br>6.6.6   | Sideband Configuration Pointer (Word 0x57)                                                                            | 230        |

|     | 6.6.7            | Reserved (Word 0x5E)                                                                                                  |            |

| 6.7 | Firmware         | Patch Structure                                                                                                       | 237        |

| 0., | 6.7.1            | Firmware Patch Data Size (Offset 0x0)                                                                                 | 237        |

|     | 6.7.2            | Block CRC8 (Offset 0x1)                                                                                               | 238        |

|     | 6.7.3            | Patch Ram Address Word (Offset 0x2)                                                                                   | 238        |

|     | 6.7.4            | Patch Version 1 Word (Offset 0x3) Patch Version 2 Word (Offset 0x4) Patch Version 3 Word (Offset 0x5)                 | 238        |

|     | 6.7.5            | Patch Version 2 Word (Offset 0x5)                                                                                     | 238        |

|     | 6.7.6<br>6.7.7   | Patch Version 3 Word (Offset 0x5)                                                                                     | 238<br>220 |

|     | 6.7.7            | Patch Data Words (Offset 0x7, Block Length)                                                                           | 230        |

| 6.8 | PT LAN C         | onfiguration Structure                                                                                                | 230        |

|     | 6.8.1            | PT LAN Configuration Structure Section Length - Offset 0x0                                                            | 239        |

|     | 6.8.2            | Block CRC8 (Offset 0x1)                                                                                               | 240        |

|     | 6.8.3            | CSR Address - (Offset 2*n; [n = 1 Section Length])                                                                    | 240        |

|     | 6.8.4            | CSR Data LSB - (Offset 0x1 + 2*n; [n = 1 Section Length])                                                             | 240        |

|     | 6.8.5            | CSK Data MSB - (Offset UXZ + ZTI); [II = 1 Section Length])                                                           | 240        |

| 6.9                      | 6.8.6                                                                                                                                                                                                                          | Manageability Filtersuration Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 240                                                                                                                        |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 0.9                      | 6.9.1                                                                                                                                                                                                                          | PHY Configuration Section Length - Offset 0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 241<br>241                                                                                                                 |

|                          | 6.9.2                                                                                                                                                                                                                          | Block CRC8 (Offset 0x1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 241                                                                                                                        |

|                          | 6.9.3                                                                                                                                                                                                                          | DLIV Number and DLIV Desister Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |

|                          |                                                                                                                                                                                                                                | (Offset 2*n; [n = 1 Section Length]) PHY data (Offset 2*n + 1; [n = 1 Section Length])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 241                                                                                                                        |

| 6.10                     | 6.9.4                                                                                                                                                                                                                          | PHY data (Offset 2*n + 1; [n = 1 Section Length])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 242                                                                                                                        |

| 0.10                     | 6.10.1                                                                                                                                                                                                                         | Section Length (Offset 0x0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 242<br>242                                                                                                                 |

|                          | 6.10.2                                                                                                                                                                                                                         | Block CRC8 (Offset 0x1) SMBus Max Fragment Size (Offset 0x2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 242                                                                                                                        |

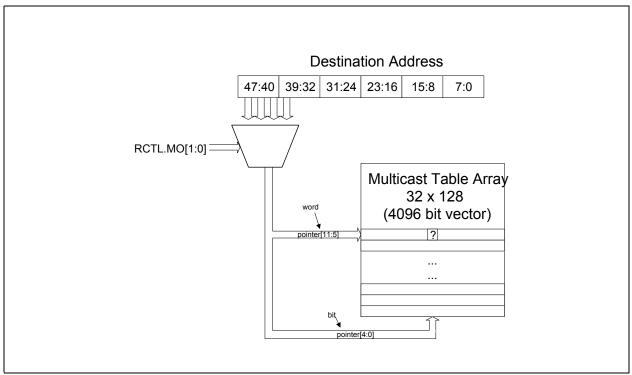

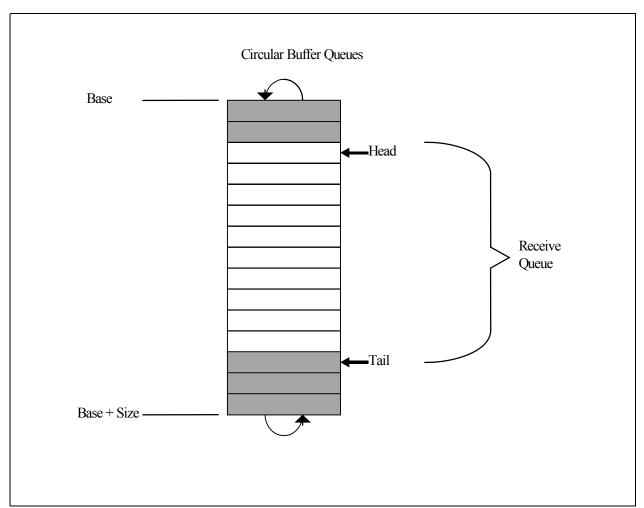

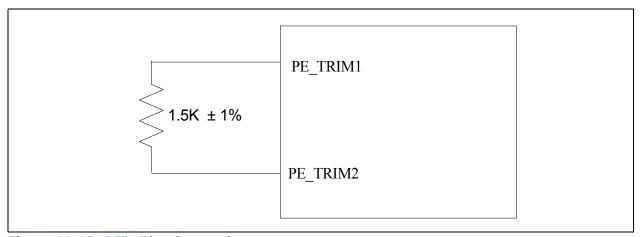

|                          | 6.10.3                                                                                                                                                                                                                         | SMBus Max Fragment Size (Offset 0x2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 242                                                                                                                        |