# ST7SCR1E4, ST7SCR1R4

# 8-bit low-power, full-speed USB MCU with 16-Kbyte Flash, 768-byte RAM, smartcard interface and timer

Datasheet - production data

#### **Features**

#### **Memories**

- Up to 16 Kbytes of ROM or High Density Flash (HDFlash) program memory with read/write protection, HDFlash In-Circuit and In-Application Programming. 100 write/erase cycles guaranteed, data retention: 40 years at 55°C

- Up to 768 bytes of RAM including up to 128 bytes stack and 256 bytes USB buffer

#### Clock, reset and supply management

- Low voltage reset

- 2 power saving modes: Halt and Wait modes

- PLL for generating 48 MHz USB clock using a 4 MHz crystal

#### Interrupt management

Nested Interrupt controller

#### **USB (Universal Serial Bus) interface**

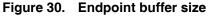

- 256-byte buffer for full speed bulk, control and interrupt transfer types compliant with USB specification (version 2.0)

- On-Chip 3.3V USB voltage regulator and transceivers with software power-down

- 7 USB endpoints:

- One 8-byte Bidirectional Control Endpoint

- One 64-byte In Endpoint,

- One 64-byte Out Endpoint

- Four 8-byte In Endpoints

#### 35 or 4 I/O ports

- Up to 4 LED outputs with software programmable constant current (3 or 7 mA).

- 2 General purpose I/Os programmable as interrupts

- Up to 8 line inputs programmable as interrupts

- Up to 20 outputs

- 1 line assigned by default as static input after reset

#### ISO7816-3 UART interface

- 4 MHz clock generation

- Synchronous/Asynchronous protocols (T=0, T=1)

- Automatic retry on parity error

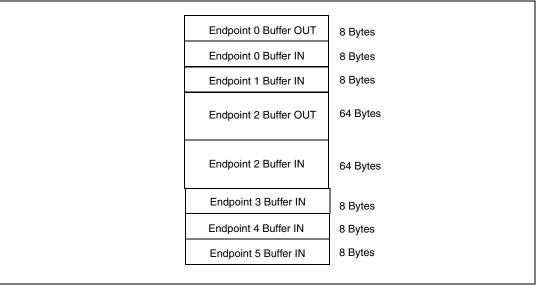

- Programmable baud rate from 372 clock pulses up to 11.625 clock pulses (D=32/F=372)

- Card Insertion/Removal Detection

#### **Smartcard power supply**

- Selectable card V<sub>CC</sub> 1.8V, 3V, and 5V

- Internal step-up converter for 5V supplied Smartcards (with a current of up to 55mA) using only two external components.

- Programmable Smartcard Internal Voltage Regulator (1.8V to 3.0V) with current overload protection and 4 KV ESD protection (Human Body Model) for all Smartcard Interface I/Os

#### One 8-bit timer

Time Base Unit (TBU) for generating periodic interrupts.

#### **Development tools**

■ Full hardware/software development package

### ECOPACK® packages

Table 1. Device summary

| Reference | Part number                         |

|-----------|-------------------------------------|

| ST7SCR1R4 | ST7FSCR1T1, ST7SCR1T1               |

| ST7SCR1E4 | ST7FSCR1M1, ST7SCR1M1,<br>ST7SCR1U1 |

# **Contents**

| 1 | Desc  | cription                           |

|---|-------|------------------------------------|

| 2 | Pin o | description10                      |

| 3 | Regi  | ister and memory map               |

| 4 | Flas  | h program memory19                 |

|   | 4.1   | Introduction                       |

|   | 4.2   | Main features 19                   |

|   | 4.3   | Structure                          |

|   | 4.4   | ICP (In-circuit programming)       |

|   | 4.5   | IAP (In-application programming)   |

|   | 4.6   | Program memory read-out protection |

|   | 4.7   | Related documentation              |

|   | 4.8   | Register description               |

| 5 | Cent  | tral processing unit               |

|   | 5.1   | Introduction                       |

|   | 5.2   | Main features                      |

|   | 5.3   | CPU registers                      |

| 6 | Sup   | ply, reset and clock management    |

|   | 6.1   | Clock system                       |

|   |       | 6.1.1 General description          |

|   |       | 6.1.2 External clock               |

|   | 6.2   | Reset sequence manager (RSM)       |

|   |       | 6.2.1 Introduction                 |

|   |       | 6.2.2 Functional description       |

| 7 | Inter | rrupts 30                          |

|   | 7.1   | Introduction                       |

|   | 7.2   | Masking and processing flow        |

|   | 7.3   | Interrupts and low power modes     |

|    | 7.4   | Concurrent and nested management | 33        |

|----|-------|----------------------------------|-----------|

|    | 7.5   | Interrupt register description   | 34        |

| 8  | Powe  | er saving modes                  | 37        |

|    | 8.1   | Introduction                     | 37        |

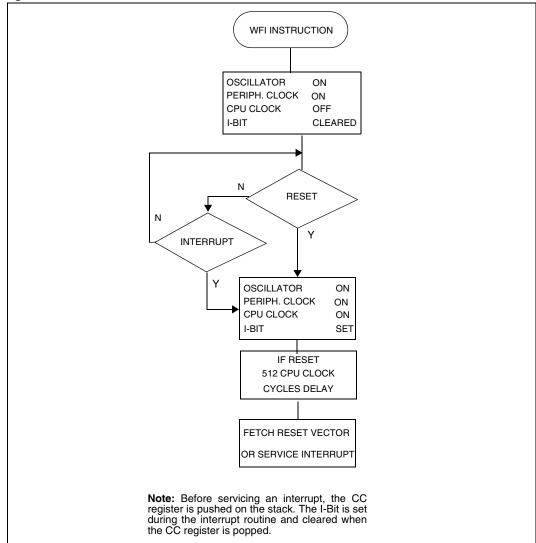

|    | 8.2   | Wait mode                        | 37        |

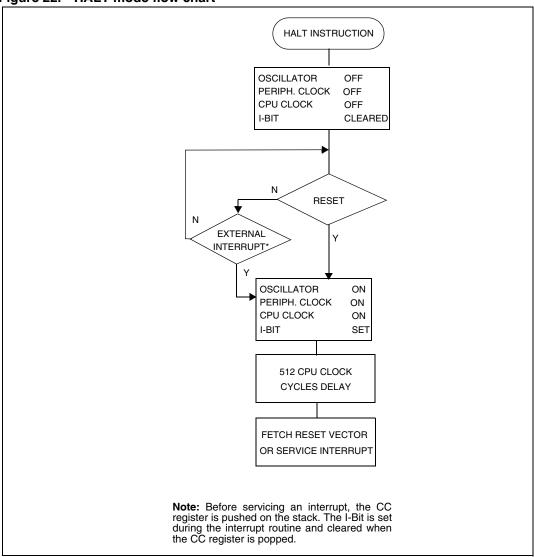

|    | 8.3   | Halt mode                        | 38        |

| 9  | I/O p | orts                             | 10        |

|    | 9.1   | Introduction                     | 40        |

|    | 9.2   | Functional description           | 40        |

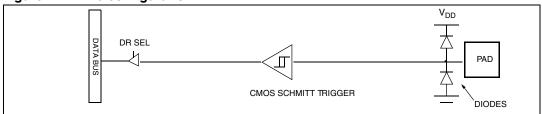

|    | 9.3   | I/O port implementation          | 41        |

|    |       | 9.3.1 Port A                     | 41        |

|    |       | 9.3.2 Ports B and D              | 42        |

|    |       | 9.3.3 Port C                     | 43        |

|    | 9.4   | Register description             | 43        |

| 10 | Misc  | ellaneous registers              | <b>ļ7</b> |

| 11 | LED   | 5                                | 50        |

| 12 | On-c  | hip peripherals                  | 51        |

|    | 12.1  | Watchdog timer (WDG)             | 51        |

|    |       | 12.1.1 Introduction              | 51        |

|    |       | 12.1.2 Main features             | 51        |

|    |       | 12.1.3 Functional description    | 51        |

|    |       | 12.1.4 Software watchdog option  | 52        |

|    |       | 12.1.5 Hardware watchdog option  | 52        |

|    |       | 12.1.6 Low power modes           | 52        |

|    |       | 12.1.7 Interrupts                | 53        |

|    |       | 12.1.8 Register description      | 53        |

|    | 12.2  | Time base unit (TBU)             | 53        |

|    |       | 12.2.1 Introduction              |           |

|    |       | 12.2.2 Main features             |           |

|    |       | 12.2.3 Functional description    |           |

|    |       | 12.2.4 Programming example       | 54        |

|    |       | 12.2.5   | Low power modes                  | 55  |

|----|-------|----------|----------------------------------|-----|

|    |       | 12.2.6   | Interrupts                       | 55  |

|    |       | 12.2.7   | Register description             | 55  |

|    | 12.3  | USB in   | terface (USB)                    | 56  |

|    |       | 12.3.1   | Introduction                     | 56  |

|    |       | 12.3.2   | Main features                    | 56  |

|    |       | 12.3.3   | Functional description           | 57  |

|    |       | 12.3.4   | Register description             | 58  |

|    | 12.4  | Smarto   | ard interface (CRD)              | 69  |

|    |       | 12.4.1   | Introduction                     | 69  |

|    |       | 12.4.2   | Main features                    | 70  |

|    |       | 12.4.3   | Functional description           | 70  |

|    |       | 12.4.4   | Register description             | 77  |

| 40 | l 4   | 4 !      | -1                               | 00  |

| 13 |       |          | set                              |     |

|    | 13.1  |          | ddressing modes                  |     |

|    |       | 13.1.1   | Inherent                         |     |

|    |       | 13.1.2   | Immediate                        |     |

|    |       | 13.1.3   | Direct                           |     |

|    |       | 13.1.4   | Indexed (No Offset, Short, Long) |     |

|    |       | 13.1.5   | Indirect (Short, Long)           |     |

|    |       | 13.1.6   | Indirect indexed (Short, Long)   |     |

|    |       | 13.1.7   | Relative mode (Direct, Indirect) |     |

|    | 13.2  | Instruct | tion groups                      | 92  |

| 14 | Flect | rical ch | aracteristics                    | 96  |

| •  | 14.1  |          | te maximum ratings               |     |

|    | 14.2  |          | mended operating conditions      |     |

|    | 14.3  |          | and reset characteristics        |     |

|    | 14.4  |          | and timing characteristics       |     |

|    | 14.4  | 14.4.1   | General timings                  |     |

|    |       | 14.4.1   | External clock source            |     |

|    |       | 14.4.2   | Crystal resonator oscillators    |     |

|    | 115   |          | •                                |     |

|    | 14.5  |          | y characteristics                |     |

|    |       | 14.5.1   | RAM and hardware registers       |     |

|    |       | 14.5.2   | FLASH memory                     | 102 |

| 17 | Revis | ion history                                                        | 20 |

|----|-------|--------------------------------------------------------------------|----|

|    |       | 16.4.3 Smart card UART automatic repetition and retry              | 19 |

|    |       | 16.4.2 Flash devices only                                          | 18 |

|    |       | 16.4.1 Unexpected reset fetch                                      | 18 |

|    | 16.4  | Important notes                                                    | 18 |

|    | 16.3  | ST7 Application notes                                              | 15 |

|    | 16.2  | Development tools                                                  | 14 |

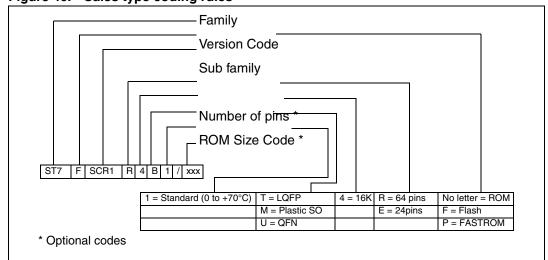

|    | 16.1  | Device ordering information and transfer of customer code 1        | 12 |

|    |       | 16.0.1 Option bytes                                                | 11 |

| 16 | Devi  | e configuration and ordering information                           | 11 |

|    | 15.2  | Recommended reflow oven profile                                    | 10 |

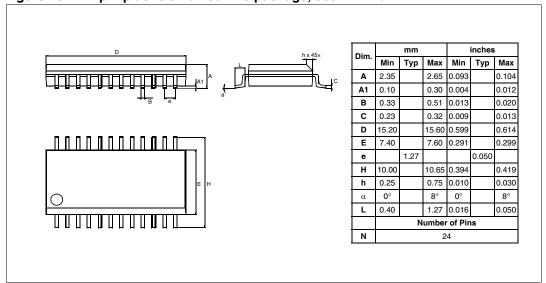

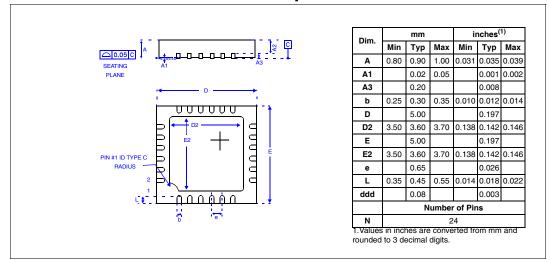

|    | 15.1  | Package mechanical data                                            | 09 |

| 15 | Pack  | age characteristics                                                | 09 |

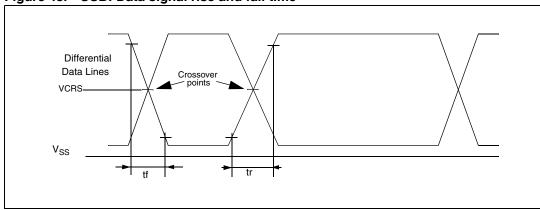

|    |       | 14.8.1 USB - Universal bus interface                               | 07 |

|    | 14.8  | Communication interface characteristics                            |    |

|    | 440   | 14.7.3 Absolute maximum ratings (electrical sensitivity)           |    |

|    |       | 14.7.2 Electro magnetic interference (EMI)                         |    |

|    |       | 14.7.1 Functional EMS (Electro magnetic susceptibility)            |    |

|    | 14.7  | EMC characteristics                                                |    |

|    | 14.6  | Smartcard supply supervisor electrical characteristics 10          |    |

|    | 11.0  | Consented and accomply accomply in an electrical above atomication | ^^ |

# List of tables

| Table 1.  | Device summary                                                                            |      |

|-----------|-------------------------------------------------------------------------------------------|------|

| Table 2.  | Detailed device summary                                                                   | 8    |

| Table 3.  | Pin description                                                                           | . 11 |

| Table 4.  | Hardware register memory map                                                              |      |

| Table 5.  | Sectors available in FLASH devices                                                        |      |

| Table 6.  | Recommended values for 4 MHz crystal resonator                                            |      |

| Table 7.  | Interrupt software priority levels                                                        |      |

| Table 8.  | Current interrupt software priority                                                       |      |

| Table 9.  | Interrupt vectors and corresponding bits                                                  |      |

| Table 10. | Dedicated interrupt instruction set                                                       |      |

| Table 11. | Interrupt mapping                                                                         | . 36 |

| Table 12. | I/O pin functions                                                                         |      |

| Table 13. | Port A description                                                                        |      |

| Table 14. | Port B and D description                                                                  |      |

| Table 15. | Port C description                                                                        |      |

| Table 16. | I/O ports register map                                                                    |      |

| Table 17. | Register map and reset values                                                             |      |

| Table 18. | Watchdog timing (fCPU = 8 MHz)                                                            |      |

| Table 19. | Transmission status encoding                                                              |      |

| Table 20. | Reception status encoding                                                                 |      |

| Table 21. | Transmission status encoding                                                              |      |

| Table 22. | Reception status encoding                                                                 |      |

| Table 23. | USB register map and reset values                                                         |      |

| Table 24. | Register map and reset values                                                             |      |

| Table 25. | CPU addressing mode overview                                                              |      |

| Table 26. | Instructions supporting direct, indexed, indirect and indirect indexed addressing modes . |      |

| Table 27. | Instruction set overview                                                                  |      |

| Table 28. | Thermal characteristics                                                                   |      |

| Table 29. | Current injection on i/o port and control pins                                            |      |

| Table 30. | I/O port pins                                                                             |      |

| Table 31. | LED pins                                                                                  |      |

| Table 32. | Low voltage detector and supervisor (LVDS)                                                |      |

| Table 33. | Typical crystal resonator                                                                 |      |

| Table 34. | Dual voltage flash memory                                                                 |      |

| Table 35. | Smartcard supply supervisor                                                               |      |

| Table 36. | Absolute maximum ratings                                                                  |      |

| Table 37. | Electrical sensitivities                                                                  |      |

| Table 38. | USB DC electrical characteristics                                                         | -    |

| Table 39. | USB: Full speed electrical characteristics                                                |      |

| Table 40. | Ordering information                                                                      |      |

| Table 41. | Development tools                                                                         |      |

| Table 42. | ST7 Application notes                                                                     |      |

| Table 43. | Device identification                                                                     |      |

| Table 44. | Document revision history                                                                 | 120  |

# List of figures

| Figure 1.  | ST7SCR block diagram                                            | 9   |

|------------|-----------------------------------------------------------------|-----|

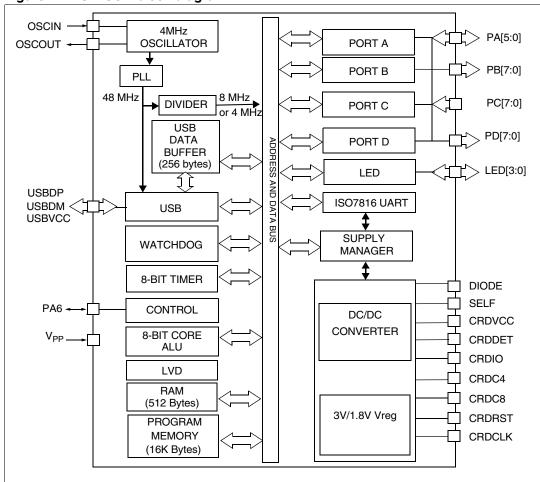

| Figure 2.  | 64-pin LQFP package pinout                                      |     |

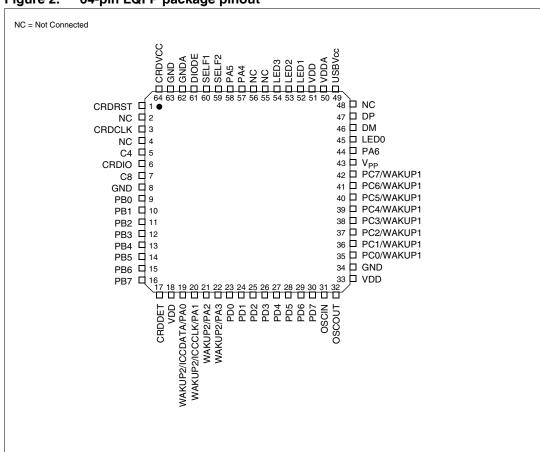

| Figure 3.  | 24-Pin SO package pinout                                        | 10  |

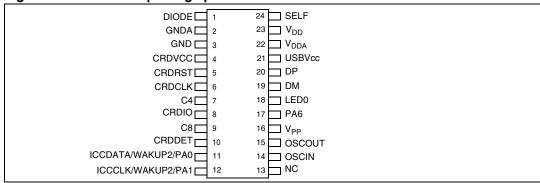

| Figure 4.  | 24-lead QFN package pinout                                      | 11  |

| Figure 5.  | Smartcard interface reference application - 24-pin SO package   | 14  |

| Figure 6.  | Smartcard interface reference application - 64-Pin LQFP package | 15  |

| Figure 7.  | Memory map                                                      |     |

| Figure 8.  | Memory map and sector address                                   | 20  |

| Figure 9.  | Typical ICP interface                                           |     |

| Figure 10. | CPU registers                                                   |     |

| Figure 11. | Stack manipulation example                                      |     |

| Figure 12. | Clock, reset and supply block diagram                           |     |

| Figure 13. | External clock source connections                               |     |

| Figure 14. | Crystal resonator                                               |     |

| Figure 15. | LVD RESET sequence                                              |     |

| Figure 16. | Watchdog RESET sequence                                         |     |

| Figure 17. | Interrupt processing flowchart                                  |     |

| Figure 18. | Priority decision process                                       |     |

| Figure 19. | Concurrent interrupt management                                 |     |

| Figure 20. | Nested interrupt management                                     |     |

| Figure 21. | WAIT mode flow chart                                            |     |

| Figure 22. | HALT mode flow chart                                            |     |

| Figure 23. | PA0, PA1, PA2, PA3, PA4, PA5 configuration                      |     |

| Figure 24. | PA6 configuration                                               |     |

| Figure 25. | Port B and D configuration                                      |     |

| Figure 26. | Port C configuration                                            |     |

| Figure 27. | Watchdog block diagram                                          |     |

| Figure 28. | TBU block diagram                                               |     |

| Figure 29. | USB block diagram                                               |     |

| Figure 30. | Endpoint buffer size                                            |     |

| Figure 31. | Smartcard interface block diagram                               |     |

| Figure 31. | Compensation mode                                               |     |

| Figure 32. | Waiting time counter example                                    |     |

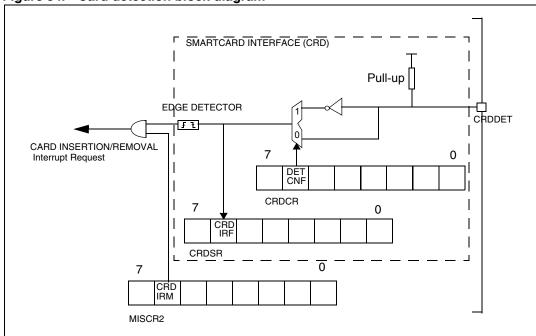

| -          | Card detection block diagram                                    |     |

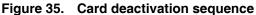

| Figure 34. | Card deactivation sequence                                      |     |

| Figure 35. |                                                                 |     |

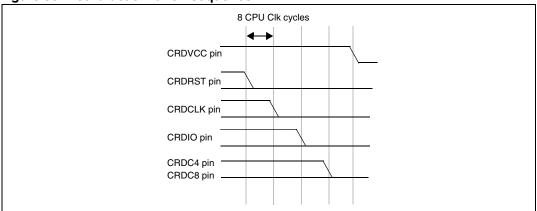

| Figure 36. | Card voltage selection and power OFF block diagram              |     |

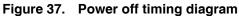

| Figure 37. | Power off timing diagram                                        |     |

| Figure 38. | Card clock selection block diagram                              |     |

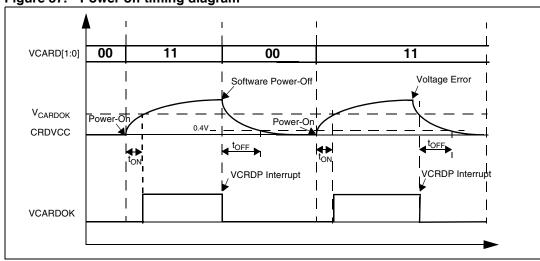

| Figure 39. | Smartcard I/O pin structure                                     |     |

| Figure 40. | Typical application with an external clock source               |     |

| Figure 41. | Typical application with a crystal resonator                    |     |

| Figure 42. | Two typical applications with VPP pin1)                         |     |

| Figure 43. | USB: Data signal rise and fall time                             |     |

| Figure 44. | 64-pin low profile quad flat package (14x14)                    |     |

| Figure 45. | 24-pin plastic small outline package, 300-mil width             |     |

| Figure 46. | Sales type coding rules                                         |     |

| Figure 47. | ST7SCR microcontroller option list                              |     |

| Figure 48. | Revision marking on box label and device marking                | 119 |

# 1 Description

The ST7SCR and ST7FSCR devices are members of the ST7 microcontroller family designed for USB applications. All devices are based on a common industry-standard 8-bit core, featuring an enhanced instruction set.

The ST7SCR ROM devices are factory-programmed and are not reprogrammable.

The ST7FSCR versions feature dual-voltage Flash memory with Flash Programming capability.

They operate at a 4 MHz external oscillator frequency.

Under software control, all devices can be placed in WAIT or HALT mode, reducing power consumption when the application is in idle or stand-by state.

The enhanced instruction set and addressing modes of the ST7 offer both power and flexibility to software developers, enabling the design of highly efficient and compact application code. In addition to standard 8-bit data management, all ST7 microcontrollers feature true bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

The devices include an ST7 core, up to 16 Kbytes of program memory, up to 512 bytes of user RAM, up to 35 I/O lines and the following on-chip peripherals:

- USB full speed interface with 7 endpoints, programmable in/out configuration and embedded 3.3V voltage regulator and transceivers (no external components are needed).

- ISO7816-3 UART interface with programmable baud rate from 372 clock pulses up to 11.625 clock pulses

- Smartcard Supply Block able to provide programmable supply voltage and I/O voltage levels to the smartcards

- Low voltage reset ensuring proper power-on or power-off of the device (selectable by option)

- Watchdog timer

- 8-bit timer (TBU)

Table 2. Detailed device summary

| Features               | ST7S0              | CR1R4              | ST7SCR1E4          |                    |               |  |  |  |  |  |  |

|------------------------|--------------------|--------------------|--------------------|--------------------|---------------|--|--|--|--|--|--|

| reatures               | ST7FSCR1T1         | ST7SCR1T1          | ST7FSCR1M1         | ST7SCR1M1          | ST7SCR1U1     |  |  |  |  |  |  |

| Program memory         | 16 Kbytes<br>FLASH | 16 Kbytes ROM      | 16 Kbytes<br>FLASH | 16 Kbytes ROM      | 16 Kbytes ROM |  |  |  |  |  |  |

| User RAM (stack) bytes | 768 (128)          |                    |                    |                    |               |  |  |  |  |  |  |

| Peripherals            | USB                | full-speed (7 Ep), | ΓBU, Watchdog tim  | ner, ISO7816-3 int | erface        |  |  |  |  |  |  |

| Operating supply       |                    |                    | 4.0 to 5.5V        |                    |               |  |  |  |  |  |  |

| CPU frequency          |                    |                    | 4 or 8 MHz         |                    |               |  |  |  |  |  |  |

| Operating temperature  |                    |                    | 0°C to +70°C       |                    |               |  |  |  |  |  |  |

| Package                | LQF                | P64                | SC                 | )24                | QFN24         |  |  |  |  |  |  |

Figure 1. ST7SCR block diagram

# 2 Pin description

Figure 2. 64-pin LQFP package pinout

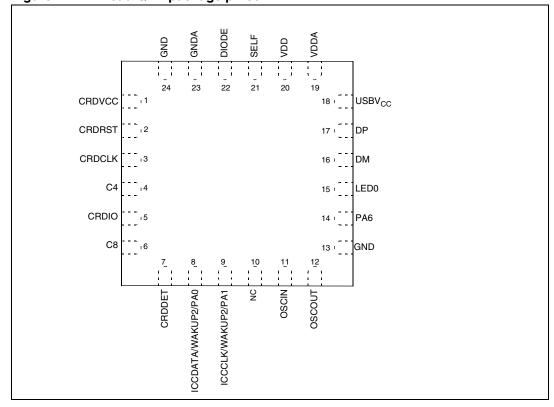

Figure 3. 24-Pin SO package pinout

10/121 Doc ID 8951 Rev 6

Figure 4. 24-lead QFN package pinout

Legend / Abbreviations:

Type: I = input, O = output, S = supply

In/Output level:  $C_T = CMOS \ 0.3V_{DD}/0.7V_{DD}$  with input trigger

Output level: HS = 10mA high sink (on N-buffer only)

Port and control configuration:

- Input:float = floating, wpu = weak pull-up, int = interrupt, ana = analog

- Output: OD = open drain, PP = push-pull

Refer to "I/O ports" on page 40 for more details on the software configuration of the I/O ports.

Table 3. Pin description

| F      | Pin n | 0    |          |      | Le    | evel           | · ·   |     | ort / | Con | trol |                 |                    |

|--------|-------|------|----------|------|-------|----------------|-------|-----|-------|-----|------|-----------------|--------------------|

| 64     | 24    | 4    | Pin name | Туре | ı     | Ħ              | ddns  | Inp | out   | Out | tput | Main function   | Alternate function |

| LQFP64 | QFN24 | S024 |          | Ė    | Input | Output         | VCARD | wpu | int   | αo  | ЬР   | (after reset)   |                    |

| 1      | 2     | 5    | CRDRST   | 0    |       | $C_{T}$        | Χ     |     |       |     | Χ    | Smartcard Reset |                    |

| 2      |       |      | NC       |      |       |                |       |     |       |     |      | Not Connected   |                    |

| 3      | 3     | 6    | CRDCLK   | 0    |       | C <sub>T</sub> | Χ     |     |       |     | Х    | Smartcard Clo   | ck                 |

Table 3. Pin description (continued)

| Pin n° |       | •    |                        | (0011 |         | vel            | led               | Po  | ort / | Con | trol |                                                                                            |                                                    |  |

|--------|-------|------|------------------------|-------|---------|----------------|-------------------|-----|-------|-----|------|--------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| 64     | 74    | 4    | Pin name               | Туре  | +       | Ħ              | supplied          | Inp | out   | Out | tput | Main<br>function                                                                           | Alternate function                                 |  |

| LQFP64 | QFN24 | 8024 |                        | Ţ     | Input   | Output         | V <sub>CARD</sub> | ndw | int   | αo  | ЬР   | (after reset)                                                                              |                                                    |  |

| 4      |       |      | NC                     |       |         |                |                   |     |       |     |      | Not Connected                                                                              | d                                                  |  |

| 5      | 4     | 7    | C4                     | 0     |         | $C_{T}$        | Χ                 |     |       |     | Х    | Smartcard C4                                                                               |                                                    |  |

| 6      | 5     | 8    | CRDIO                  | I/O   | $C_{T}$ |                | Χ                 | Χ   |       | Х   |      | Smartcard I/O                                                                              |                                                    |  |

| 7      | 6     | 9    | C8                     | 0     |         | C <sub>T</sub> | Χ                 |     |       |     | Х    | Smartcard C8                                                                               |                                                    |  |

| 8      |       | 3    | GND                    | S     |         |                |                   |     |       |     |      | Ground                                                                                     |                                                    |  |

| 9      |       |      | PB0                    | 0     |         | C <sub>T</sub> |                   |     |       | Х   | Х    | Port B0 (1)                                                                                |                                                    |  |

| 10     |       |      | PB1                    | 0     |         | C <sub>T</sub> |                   |     |       | Х   | Х    | Port B1 (1)                                                                                |                                                    |  |

| 11     |       |      | PB2                    | 0     |         | C <sub>T</sub> |                   |     |       | Х   | Х    | Port B2 (1)                                                                                |                                                    |  |

| 12     |       |      | PB3                    | 0     |         | C <sub>T</sub> |                   |     |       | Х   | Х    | Port B3 (1)                                                                                |                                                    |  |

| 13     |       |      | PB4                    | 0     |         | Ст             |                   |     |       | Х   | Х    | Port B4 (1)                                                                                |                                                    |  |

| 14     |       |      | PB5                    | 0     |         | Ст             |                   |     |       | Х   | Х    | Port B5 (1)                                                                                |                                                    |  |

| 15     |       |      | PB6                    | 0     |         | Ст             |                   |     |       | Х   | Х    | Port B6 (1)                                                                                |                                                    |  |

| 16     |       |      | PB7                    | 0     |         | Ст             |                   |     |       | Х   | Х    | Port B7 (1)                                                                                |                                                    |  |

| 17     | 7     | 10   | CRDDET                 | I     | $C_{T}$ |                |                   | Χ   |       |     |      | Smartcard Detection                                                                        |                                                    |  |

| 18     |       |      | VDD                    | S     |         |                |                   |     |       |     |      | Power Supply                                                                               | voltage 4V-5.5V                                    |  |

| 19     | 8     | 11   | PA0/WAKUP2/<br>ICCDATA | I/O   | СТ      |                |                   | Х   | Х     | X   | Х    | Port A0                                                                                    | Interrupt, In-Circuit<br>Communication Data Input  |  |

| 20     | 9     | 12   | PA1/WAKUP2/<br>ICCCLK  | I/O   | СТ      |                |                   | Х   | Х     | X   | Х    | Port A1                                                                                    | Interrupt, In-Circuit<br>Communication Clock Input |  |

| 21     |       |      | PA2/WAKUP2             | I/O   | $C_{T}$ |                |                   | Χ   | Χ     | Х   | Х    | Port A2 (1)                                                                                | Interrupt                                          |  |

| 22     |       |      | PA3/WAKUP2             | I/O   | $C_{T}$ |                |                   | Χ   | Χ     | Х   | Х    | Port A3 (1)                                                                                | Interrupt                                          |  |

| 23     |       |      | PD0                    | 0     |         | C <sub>T</sub> |                   |     |       | Х   | Х    | Port D0 (1)                                                                                |                                                    |  |

| 24     |       |      | PD1                    | 0     |         | C <sub>T</sub> |                   |     |       | Х   | Х    | Port D1 (1)                                                                                |                                                    |  |

| 25     |       |      | PD2                    | 0     |         | C <sub>T</sub> |                   |     |       | Х   | Х    | Port D2 (1)                                                                                |                                                    |  |

| 26     |       |      | PD3                    | 0     |         | C <sub>T</sub> |                   |     |       | Х   | Х    | Port D3 (1)                                                                                |                                                    |  |

| 27     |       |      | PD4                    | 0     |         | СТ             |                   |     |       | Х   | Х    | Port D4 (1)                                                                                |                                                    |  |

| 28     |       |      | PD5                    | 0     |         | Ст             |                   |     |       | Х   | Х    | Port D5 (1)                                                                                |                                                    |  |

| 29     |       |      | PD6                    | 0     |         | СТ             |                   |     |       | Х   | Х    | Port D6 (1)                                                                                |                                                    |  |

| 30     |       |      | PD7                    | 0     |         | СТ             |                   |     |       | Х   | Х    | Port D7 (1)                                                                                |                                                    |  |

| 31     | 11    | 14   | OSCIN                  |       | СТ      |                |                   |     |       |     |      |                                                                                            | Scillator pins. These pins                         |  |

| 32     | 12    | 15   | OSCOUT                 |       |         | СТ             |                   |     |       |     |      | connect a 4MHz parallel-resonant crystal, or an external source to the on-chip oscillator. |                                                    |  |

| 33     |       |      | VDD                    | S     |         |                |                   |     |       |     |      | Power Supply                                                                               | voltage 4V-5.5V                                    |  |

Table 3. Pin description (continued)

|        | Pin n | 0    | riii description |      |                | vel            | jed      | Po  | ort / | Con | trol |                                                                       |                                                                                          |  |

|--------|-------|------|------------------|------|----------------|----------------|----------|-----|-------|-----|------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|

| 94     | 4     | _    | Pin name         | Туре |                | Ħ              | supplied | Inp | out   | Ou  | tput | Main<br>function                                                      | Alternate function                                                                       |  |

| LQFP64 | QFN24 | S024 |                  | Ţ    | Input          | Output         | VCARD    | ndw | int   | ОО  | ВР   | (after reset)                                                         |                                                                                          |  |

| 34     |       |      | GND              | S    |                |                |          |     |       |     |      | Ground                                                                |                                                                                          |  |

| 35     |       |      | PC0/WAKUP1       | I    | C <sub>T</sub> |                |          | Χ   | Χ     |     |      | PC0 <sup>(1)</sup>                                                    | External interrupt                                                                       |  |

| 36     |       |      | PC1/WAKUP1       | I    | $C_{T}$        |                |          | Χ   | Χ     |     |      | PC1 <sup>(1)</sup>                                                    | External interrupt                                                                       |  |

| 37     |       |      | PC2/WAKUP1       | I    | $C_{T}$        |                |          | Χ   | Χ     |     |      | PC2 <sup>(1)</sup>                                                    | External interrupt                                                                       |  |

| 38     |       |      | PC3/WAKUP1       | I    | $C_{T}$        |                |          | Χ   | Χ     |     |      | PC3 <sup>(1)</sup>                                                    | External interrupt                                                                       |  |

| 39     |       |      | PC4/WAKUP1       | I    | $C_{T}$        |                |          | Χ   | Χ     |     |      | PC4 <sup>(1)</sup>                                                    | External interrupt                                                                       |  |

| 40     |       |      | PC5/WAKUP1       | I    | $C_{T}$        |                |          | Χ   | Χ     |     |      | PC5 <sup>(1)</sup>                                                    | External interrupt                                                                       |  |

| 41     |       |      | PC6/WAKUP1       | I    | C <sub>T</sub> |                |          | Χ   | Χ     |     |      | PC6 <sup>(1)</sup>                                                    | External interrupt                                                                       |  |

| 42     |       |      | PC7/WAKUP1       | I    | $C_{T}$        |                |          | Χ   | Χ     |     |      | PC7 <sup>(1)</sup>                                                    | External interrupt                                                                       |  |

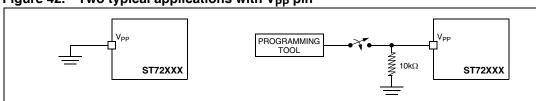

| 43     |       | 16   | V <sub>PP</sub>  | S    |                |                |          |     |       |     |      | Flash programming voltage. Must be held low in normal operating mode. |                                                                                          |  |

|        | 13    |      | GND              | S    |                |                |          |     |       |     |      | Must be held low in normal operating mode.                            |                                                                                          |  |

| 44     | 14    | 17   | PA6              | I    | $C_{T}$        |                |          |     |       |     |      | PA6                                                                   |                                                                                          |  |

| 45     | 15    | 18   | LED0             | 0    |                | HS             |          |     |       | Х   |      | Constant Current Output                                               |                                                                                          |  |

| 46     | 16    | 19   | DM               | I/O  | СТ             |                |          |     |       |     |      | USB Data Minus line                                                   |                                                                                          |  |

| 47     | 17    | 20   | DP               | I/O  | СТ             |                |          |     |       |     |      | USB Data Plu                                                          | s line                                                                                   |  |

| 48     |       |      | NC               |      |                |                |          |     |       |     |      | Not Connecte                                                          | d                                                                                        |  |

| 49     | 18    | 21   | USBVCC           | 0    |                | C <sub>T</sub> |          |     |       |     |      | 3.3 V Output f                                                        | or USB                                                                                   |  |

| 50     | 19    | 22   | $V_{DDA}$        | S    |                |                |          |     |       |     |      | power Supply                                                          | voltage 4V-5.5V                                                                          |  |

| 51     | 20    | 23   | V <sub>DD</sub>  | S    |                |                |          |     |       |     |      | power Supply                                                          | voltage 4V-5.5V                                                                          |  |

| 52     |       |      | LED1             | 0    |                | HS             |          |     |       | Х   |      | Constant Curr                                                         | ent Output                                                                               |  |

| 53     |       |      | LED2             | 0    |                | HS             |          |     |       | Х   |      | Constant Curr                                                         | ent Output                                                                               |  |

| 54     |       |      | LED3             | 0    |                | HS             |          |     |       | Х   |      | Constant Curr                                                         | ent Output                                                                               |  |

| 55     |       |      | NC               |      |                |                |          |     |       |     |      | Not Connecte                                                          | d                                                                                        |  |

| 56     |       |      | NC               |      |                |                |          |     |       |     |      | Not Connecte                                                          | d                                                                                        |  |

| 57     |       |      | PA4              | I/O  | $C_{T}$        | •              |          | Χ   | Χ     | Х   | Х    | Port A4                                                               |                                                                                          |  |

| 58     |       |      | PA5              | I/O  | $C_{T}$        |                |          | Χ   | Χ     | Х   | Х    | Port A5                                                               |                                                                                          |  |

| 59     | 21    | 24   | SELF2            | 0    |                | C <sub>T</sub> |          |     |       |     |      |                                                                       | ductance must be connected                                                               |  |

| 60     | 21    | 24   | SELF1            | 0    |                | C <sub>T</sub> |          |     |       |     |      |                                                                       | or the step up converter (refer choose the right capacitance)                            |  |

| 61     | 22    | 1    | DIODE            | S    |                | C <sub>T</sub> |          |     |       |     |      | pin for the step                                                      | ode must be connected to this p up converter (refer to <i>Figure</i> le right component) |  |

Table 3. Pin description (continued)

| F      | Pin n | 0    |          |      | Le   | vel            | el ed |     | ort / | Cont | trol |               |                    |

|--------|-------|------|----------|------|------|----------------|-------|-----|-------|------|------|---------------|--------------------|

| 64     | 24    | 4    | Pin name | Туре | ¥    | Ħ              | dns   | Inp | out   | Out  | put  | Main function | Alternate function |

| LQFP64 | QFN24 | S024 |          | Ĺ    | Indu | Output         | VCARD | wpu | int   | αо   | ЬР   | (after reset) |                    |

| 62     | 23    | 2    | GNDA     | S    |      |                |       |     |       |      |      | Ground        |                    |

| 63     | 24    | 3    | GND      | S    |      |                |       |     |       |      |      |               |                    |

| 64     | 1     | 4    | CRDVCC   | 0    |      | C <sub>T</sub> | Χ     |     |       |      |      | Smartcard Sup | oply pin           |

<sup>1.</sup> Keyboard interface

Note: It is mandatory to connect all available VDD and VDDA pins to the supply voltage and all VSS and VSSA pins to ground.

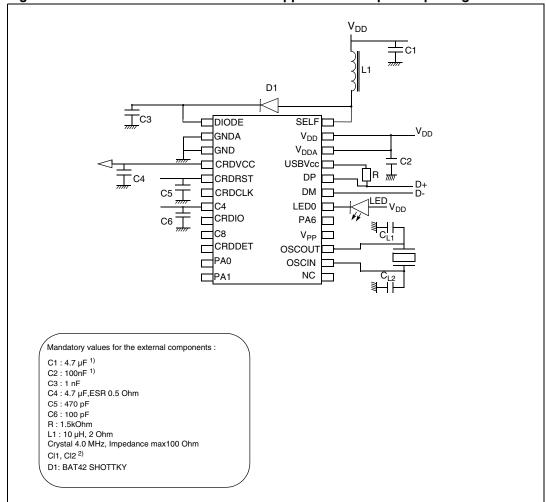

Figure 5. Smartcard interface reference application - 24-pin SO package

Note:

C1 and C2 must be located close to the chip.

Refer to Section 6: Supply, reset and clock management & Section 14.4.3 Crystal resonator oscillators.

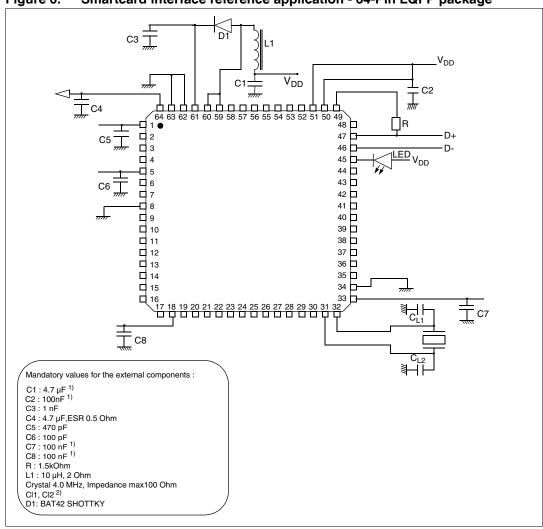

Figure 6. Smartcard interface reference application - 64-Pin LQFP package

Note:

C1, C2, C7 and C8 must be located close to the chip.

Refer to Section 6: Supply, reset and clock management and Section 14.4.3 Crystal resonator oscillators.

# 3 Register and memory map

As shown in *Figure 7*, the MCU is capable of addressing 64K bytes of memories and I/O registers.

The available memory locations consist of 40 bytes of register locations, up to 512 bytes of RAM and up to 16K bytes of user program memory. The RAM space includes up to 128 bytes for the stack from 0100h to 017Fh.

The highest address bytes contain the user reset and interrupt vectors.

**IMPORTANT**: Memory locations noted "Reserved" must never be accessed. Accessing a reserved area can have unpredictable effects on the device.

0000h **HW Registers** ∕ 0040h (see Table 4) **Short Addressing** 003Fh 0040h RAM (192 Bytes) 0100h RAM Stack (128 Bytes) 017Fh (512 Bytes) 0180h 023F 16-bit Addressing RAM 0240 ( 192 Bytes) **USB RAM** 023Fh 256 Bytes 033Fh Unused COOOL Program Memory (16K Bytes) FFDF FFE0h Interrupt & Reset Vectors (see Table 11)

Figure 7. Memory map

Table 4. Hardware register memory map

| Address | Block    | Register<br>label | Register name                        | Reset<br>status | Remarks |

|---------|----------|-------------------|--------------------------------------|-----------------|---------|

| 0000h   |          | CRDCR             | Smartcard Interface Control Register | 00h             | R/W     |

| 0001h   |          | CRDSR             | Smartcard Interface Status Register  | 80h             | R/W     |

| 0002h   |          | CRDCCR            | Smartcard Contact Control Register   | xxh             | R/W     |

| 0003h   |          | CRDETU1           | Smartcard Elementary Time Unit 1     | 01h             | R/W     |

| 0004h   |          | CRDETU0           | Smartcard Elementary Time Unit 0     | 74h             | R/W     |

| 0005h   |          | CRDGT1            | Smartcard Guard time 1               | 00h             | R/W     |

| 0006h   | CRD      | CRDGT0            | Smartcard Guard time 0               | 0Ch             | R/W     |

| 0007h   | ChD      | CRDWT2            | Smartcard Character Waiting Time 2   | 00h             | R/W     |

| 0008h   |          | CRDWT1            | Smartcard Character Waiting Time 1   | 25h             | R/W     |

| 0009h   |          | CRDWT0            | Smartcard Character Waiting Time 0   | 80h             | R/W     |

| 000Ah   |          | CRDIER            | Smartcard Interrupt Enable Register  | 00h             | R/W     |

| 000Bh   |          | CRDIPR            | Smartcard Interrupt Pending Register | 00h             | R       |

| 000Ch   |          | CRDTXB            | Smartcard Transmit Buffer Register   | 00h             | R/W     |

| 000Dh   |          | CRDRXB            | Smartcard Receive Buffer Register    | 00h             | R       |

| 000Eh   | Watchdog | WDGCR             | Watchdog Control Register            | 00h             | R/W     |

| 0011h   |          | PADR              | Port A Data Register                 | 00h             | R/W     |

| 0012h   | Port A   | PADDR             | Port A Data Direction Register       | 00h             | R/W     |

| 0013h   | POIL A   | PAOR              | Option Register                      | 00h             | R/W     |

| 0014h   |          | PAPUCR            | Pull up Control Register             | 00h             | R/W     |

| 0015h   |          | PBDR              | Port B Data Register                 | 00h             | R/W     |

| 0016h   | Port B   | PBOR              | Option Register                      | 00h             | R/W     |

| 0017h   |          | PBPUCR            | Pull up Control Register             | 00h             | R/W     |

| 0018h   | Port C   | PCDR              | Port C Data Register                 | 00h             | R/W     |

| 0019h   |          | PDDR              | Port D Data Register                 | 00h             | R/W     |

| 001Ah   | Port D   | PDOR              | Option Register                      | 00h             | R/W     |

| 001Bh   |          | PDPUCR            | Pull up Control Register             | 00h             | R/W     |

| 001Ch   |          | MISCR1            | Miscellaneous Register 1             | 00h             | R/W     |

| 001Dh   | MISC     | MISCR2            | Miscellaneous Register 2             | 00h             | R/W     |

| 001Eh   | IVIIOU   | MISCR3            | Miscellaneous Register 3             | 00h             | R/W     |

| 001Fh   |          | MISCR4            | Miscellaneous Register 4             | 00h             | R/W     |

Table 4. Hardware register memory map (continued)

|         |       | Register | lemory map (continued)                 | Reset  |         |

|---------|-------|----------|----------------------------------------|--------|---------|

| Address | Block | label    | Register name                          | status | Remarks |

| 0020h   |       | USBISTR  | USB Interrupt Status Register          | 00h    | R/W     |

| 0021h   |       | USBIMR   | USB Interrupt Mask Register            | 00h    | R/W     |

| 0022h   |       | USBCTLR  | USB Control Register                   | 06h    | R/W     |

| 0023h   |       | DADDR    | Device Address Register                | 00h    | R/W     |

| 0024h   |       | USBSR    | USB Status Register                    | 00h    | R/W     |

| 0025h   |       | EPOR     | Endpoint 0 Register                    | 0xh    | R/W     |

| 0026h   |       | CNT0RXR  | EP 0 Reception Counter Register        | 00h    | R/W     |

| 0027h   |       | CNT0TXR  | EP 0 Transmission Counter Register     | 00h    | R/W     |

| 0028h   |       | EP1TXR   | EP 1 Transmission Register             | 00h    | R/W     |

| 0029h   |       | CNT1TXR  | EP 1 Transmission Counter Register     | 00h    | R/W     |

| 002Ah   | USB   | EP2RXR   | EP 2 Reception Register                | 00h    | R/W     |

| 002Bh   |       | CNT2RXR  | EP 2 Reception Counter Register        | 0xh    | R/W     |

| 002Ch   |       | EP2TXR   | EP 2 Transmission Register             | 00h    | R/W     |

| 002Dh   |       | CNT2TXR  | EP 2 Transmission Counter Register     | 00h    | R/W     |

| 002Eh   |       | EP3TXR   | EP 3 Transmission Register             | 00h    | R/W     |

| 002Fh   |       | CNT3TXR  | EP 3 Transmission Counter Register     | 00h    | R/W     |

| 0030h   |       | EP4TXR   | EP 4 Transmission Register             | 00h    | R/W     |

| 0031h   |       | CNT4TXR  | EP 4 Transmission Counter Register     | 00h    | R/W     |

| 0032h   |       | EP5TXR   | EP 5 Transmission Register             | 00h    | R/W     |

| 0033h   |       | CNT5TXR  | EP 5 Transmission Counter Register     | 00h    | R/W     |

| 0034h   |       | ERRSR    | Error Status Register                  | 00h    | R/W     |

| 0035h   | TBU   | TBUCV    | Timer counter value                    | 00h    | R/W     |

| 0036h   | 160   | TBUCSR   | Timer control status                   | 00h    | R/W     |

| 0037h   |       | ITSPR0   | Interrupt Software Priority Register 0 | FFh    | R/W     |

| 0038h   | ITC   | ITSPR1   | Interrupt Software Priority Register 1 | FFh    | R/W     |

| 0039h   | 110   | ITSPR2   | Interrupt Software Priority Register 2 | FFh    | R/W     |

| 003Ah   |       | ITSPR3   | Interrupt Software Priority Register 3 | FFh    | R/W     |

| 003Eh   |       | LED_CTRL | LED Control Register                   | 00h    | R/W     |

# 4 Flash program memory

#### 4.1 Introduction

The ST7 dual voltage High Density Flash (HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a Byte-by-Byte basis using an external V<sub>PP</sub> supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (In-Circuit Programming) or IAP (In-Application Programming).

The array matrix organization allows each sector to be erased and reprogrammed without affecting other sectors.

### 4.2 Main features

- Three Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased.

- ICP (In-Circuit Programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (In-Application Programming) In this mode, all sectors except Sector 0, can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (In-Circuit Testing) for downloading and executing user application test patterns in RAM

- Read-out protection

- Register Access Security System (RASS) to prevent accidental programming or erasing

#### 4.3 Structure

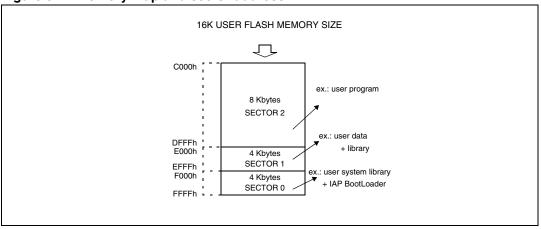

The Flash memory is organized in sectors and can be used for both code and data storage.

Depending on the overall FLASH memory size in the microcontroller device, there are up to three user sectors (see *Table 5*). Each of these sectors can be erased independently to avoid unnecessary erasing of the whole Flash memory when only a partial erasing is required.

The first two sectors have a fixed size of 4 Kbytes (see *Figure 8*). They are mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

Table 5. Sectors available in FLASH devices

| Flash Memory Size (bytes) | Available Sectors |  |  |  |

|---------------------------|-------------------|--|--|--|

| 4K                        | Sector 0          |  |  |  |

| 8K                        | Sectors 0,1       |  |  |  |

| > 8K                      | Sectors 0,1, 2    |  |  |  |

Figure 8. Memory map and sector address

# 4.4 ICP (In-circuit programming)

To perform ICP the microcontroller must be switched to ICC (In-Circuit Communication) mode by an external controller or programming tool.

Depending on the ICP code downloaded in RAM, Flash memory programming can be fully customized (number of bytes to program, program locations, or selection serial communication interface for downloading).

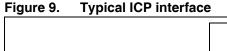

When using an STMicroelectronics or third-party programming tool that supports ICP and the specific microcontroller device, the user needs only to implement the ICP hardware interface on the application board (see *Figure 9*). For more details on the pin locations, refer to the device pinout description.

ICP needs six signals to be connected to the programming tool. These signals are:

- V<sub>SS</sub>: device power supply ground

- V<sub>DD</sub>: for reset by LVD

- OSCIN: to force the clock during power-up

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input serial data pin

- V<sub>PP</sub>: ICC mode selection and programming voltage.

If ICCCLK or ICCDATA are used for other purposes in the application, a serial resistor has to be implemented to avoid a conflict in case one of the other devices forces the signal level.

Note:

To develop a custom programming tool, refer to the ST7 FLASH Programming and ICC Reference Manual which gives full details on the ICC protocol hardware and software.

# 4.5 IAP (In-application programming)

This mode uses a BootLoader program previously stored in Sector 0 by the user (in ICP mode or by plugging the device in a programming tool).

This mode is fully controlled by user software. This allows it to be adapted to the user application, (user-defined strategy for entering programming mode, choice of communications protocol used to fetch the data to be stored, etc.). For example, it is

Figure 9.

possible to download code from the USB interface and program it in the Flash. IAP mode can be used to program any of the Flash sectors except Sector 0, which is write/erase protected to allow recovery in case errors occur during the programming operation.

Note:

If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

#### 4.6 Program memory read-out protection

The read-out protection is enabled through an option bit.

For Flash devices, when this option is selected, the program and data stored in the Flash memory are protected against read-out (including a re-write protection). When this protection is removed by reprogramming the Option Byte, the entire Flash program memory is first automatically erased and the device can be reprogrammed.

Refer to the Option Byte description for more details.

#### 4.7 **Related documentation**

For details on Flash programming and ICC protocol, refer to the ST7 Flash Programming Reference Manual and to the ST7 ICC Protocol Reference Manual.

# 4.8 Register description

### FLASH control/status register (FCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

This register is reserved for use by Programming Tool software. It controls the FLASH programming and erasing operations. For details on customizing FLASH programming methods and In-Circuit Testing, refer to the ST7 FLASH Programming and ICC Reference Manual.

# 5 Central processing unit

#### 5.1 Introduction

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

#### 5.2 Main features

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- Low power HALT and WAIT modes

- Priority maskable hardware interrupts

- Non-maskable software/hardware interrupts

### 5.3 CPU registers

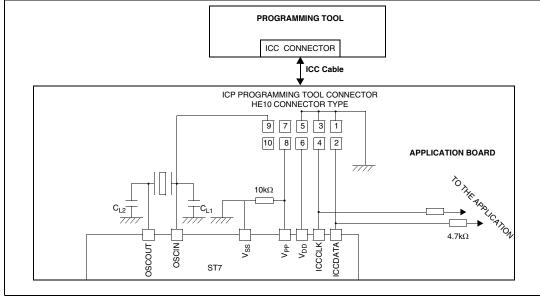

The 6 CPU registers shown in *Figure 10* are not present in the memory mapping and are accessed by specific instructions.

#### Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

#### Index registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

#### Program counter (PC)

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

#### Condition code register (CC)

Read/Write

Reset Value: 111x1xxx

| <br>7 | _ | _  | _ | _  | _ | _ | 0 |

|-------|---|----|---|----|---|---|---|

| 1     | 1 | I1 | Н | 10 | N | Z | O |

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### **Arithmetic management bits**

Bit  $4 = \mathbf{H}$  Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

- 0: No half carry has occurred.

- 1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result 7<sup>th</sup> bit.

- 0: The result of the last operation is positive or null.

- 1: The result of the last operation is negative

- (i.e. the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

57

Bit  $1 = \mathbf{Z} Zero$ .

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

0: The result of the last operation is different from zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

Bit 0 = **C** Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

Interrupt Management Bits

Bit 5,3 = **I1**, **I0** Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | I1 | 10 |

|-------------------------------|----|----|

| Level 0 (main)                | 1  | 0  |

| Level 1                       | 0  | 1  |

| Level 2                       | 0  | 0  |

| Level 3 (= interrupt disable) | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

#### Stack Pointer (SP)

Read/Write

Reset Value: 017Fh

| 15  |     |     |     |     |     |     | 8   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| 7   |     |     |     |     |     |     | 0   |

| SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 |

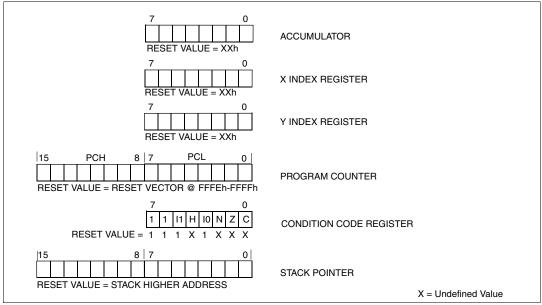

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see *Figure 11*).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

Note:

When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in *Figure 11*.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

Figure 11. Stack manipulation example

# 6 Supply, reset and clock management

### 6.1 Clock system

#### 6.1.1 General description

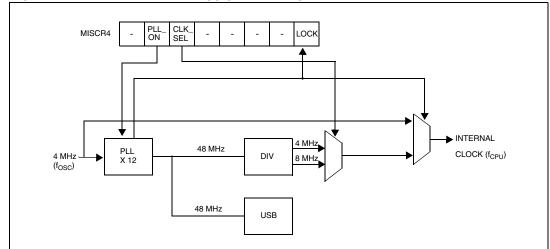

The MCU accepts either a 4 MHz crystal or an external clock signal to drive the internal oscillator. The internal clock ( $f_{CPU}$ ) is derived from the internal oscillator frequency ( $f_{OSC}$ ), which is 4 MHz.

After reset, the internal clock (f<sub>CPU</sub>) is provided by the internal oscillator (4 MHz frequency).

To activate the 48-MHz clock for the USB interface, the user must turn on the PLL by setting the PLL\_ON bit in the MISCR4 register. When the PLL is locked, the LOCK bit is set by hardware.

The user can then select an internal frequency (f<sub>CPU</sub>) of either 4 MHz or 8 MHz by programming the CLK\_SEL bit in the MISCR4 register (refer to *Section 10: Miscellaneous registers*).

The PLL provides a signal with a duty cycle of 50%.

The internal clock signal (f<sub>CPU</sub>) is also routed to the on-chip peripherals. The CPU clock signal consists of a square wave with a duty cycle of 50%.

Figure 12. Clock, reset and supply block diagram

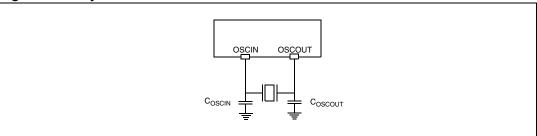

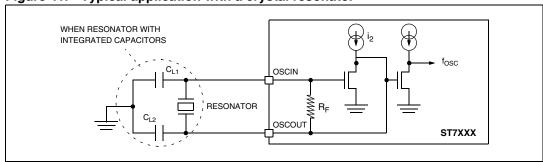

The internal oscillator is designed to operate with an AT-cut parallel resonant quartz in the frequency range specified for  $f_{\rm osc}$ . The circuit shown in *Figure 14* is recommended when using a crystal, and *Table 6* lists the recommended capacitance. The crystal and associated components should be mounted as close as possible to the input pins in order to minimize output distortion and start-up stabilization time. The LOCK bit in the MISCR4 register can also be used to generate the  $f_{CPU}$  directly from  $f_{OSC}$  if the PLL and the USB interface are not active.

Table 6. Recommended values for 4 MHz crystal resonator

| R <sub>SMAX</sub>   | 20 Ω | 25 Ω | 70 Ω |

|---------------------|------|------|------|

| C <sub>OSCIN</sub>  | 56pF | 47pF | 22pF |

| C <sub>OSCOUT</sub> | 56pF | 47pF | 22pF |

Note: R<sub>SMAX</sub> is the equivalent serial resistor of the crystal (see crystal specification).

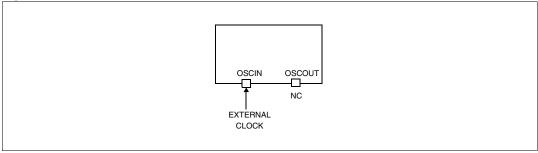

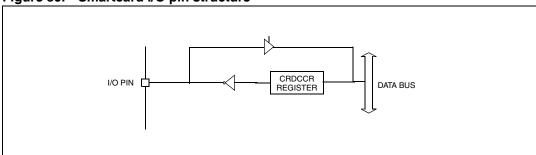

#### 6.1.2 External clock

An external clock may be applied to the OSCIN input with the OSCOUT pin not connected, as shown on *Figure 13*.

Figure 13. External clock source connections

Figure 14. Crystal resonator

# 6.2 Reset sequence manager (RSM)

#### 6.2.1 Introduction

The reset sequence manager has two reset sources:

- Internal LVD reset (Low Voltage Detection) which includes both a power-on and a voltage drop reset

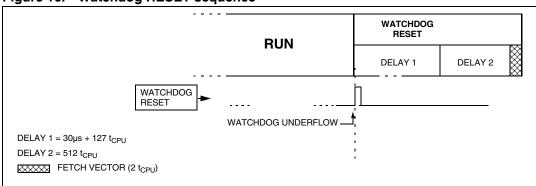

- Internal watchdog reset generated by an internal watchdog counter underflow as shown in *Figure 16*.

#### 6.2.2 Functional description

The reset service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

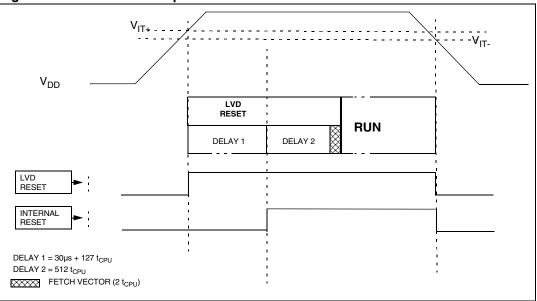

The basic reset sequence consists of 3 phases as shown in Figure 15.

28/121 Doc ID 8951 Rev 6

- 1. A first delay of  $30\mu s + 127 t_{CPU}$  cycles during which the internal reset is maintained.

- 2. A second delay of 512 t<sub>CPU</sub> cycles after the internal reset is generated. It allows the oscillator to stabilize and ensures that recovery has taken place from the Reset state.

- 3. Reset vector fetch (duration: 2 clock cycles)

#### Low voltage detector

The low voltage detector generates a reset when  $V_{DD} < V_{IT+}$  (rising edge) or  $V_{DD} < V_{IT-}$  (falling edge), as shown in *Figure 15*.

The LVD filters spikes on  $V_{DD}$  larger than  $t_{g(VDD)}$  to avoid parasitic resets. See *Section 14.3 Supply and reset characteristics*.

Note:

It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from Reset, to ensure the application functions properly.

Figure 15. LVD RESET sequence

Figure 16. Watchdog RESET sequence

# 7 Interrupts

#### 7.1 Introduction

The CPU enhanced interrupt management provides the following features:

- Hardware interrupts

- Software interrupt (TRAP)

- Nested or concurrent interrupt management with flexible interrupt priority and level management:

- Up to 4 software programmable nesting levels

- Up to 16 interrupt vectors fixed by hardware

- 3 non maskable events: RESET, TRAP, TLI

This interrupt management is based on:

- Bit 5 and bit 3 of the CPU CC register (I1:0),

- Interrupt software priority registers (ISPRx),

- Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nested) CPU interrupt controller.

# 7.2 Masking and processing flow

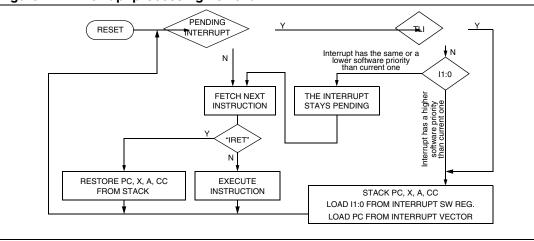

The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of each interrupt vector (see *Table 7*). The processing flow is shown in *Figure 17*.

When an interrupt request has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to "Interrupt Mapping" table for vector addresses).

The interrupt service routine should end with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

Note:

As a consequence of the IRET instruction, the I1 and I0 bits will be restored from the stack and the program in the previous level will resume.

Table 7. Interrupt software priority levels

| Interrupt software priority   | Level    | l1 | 10 |

|-------------------------------|----------|----|----|

| Level 0 (main)                | Law      | 1  | 0  |

| Level 1                       | Low<br>I | 0  | 1  |

| Level 2                       | — High   |    | 0  |

| Level 3 (= interrupt disable) | 1 11911  | 1  | 1  |

Figure 17. Interrupt processing flowchart

#### Servicing pending interrupts

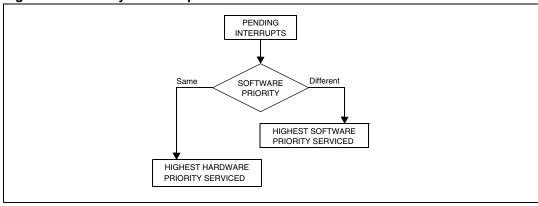

As several interrupts can be pending at the same time, the interrupt to be taken into account is determined by the following two-step process:

- the highest software priority interrupt is serviced,

- if several interrupts have the same software priority then the interrupt with the highest hardware priority is serviced first.

Figure 18 describes this decision process.

Figure 18. Priority decision process

When an interrupt request is not serviced immediately, it is latched and then processed when its software priority combined with the hardware priority becomes the highest one.

Note:

The hardware priority is exclusive while the software one is not. This allows the previous process to succeed with only one interrupt.

RESET, TRAP and TLI can be considered as having the highest software priority in the decision process.

#### Different interrupt vector sources

Two interrupt source types are managed by the CPU interrupt controller: the non-maskable type (RESET, TLI, TRAP) and the maskable type (external or from internal peripherals).

#### Non-maskable sources

These sources are processed regardless of the state of the I1 and I0 bits of the CC register (see *Figure 17*). After stacking the PC, X, A and CC registers (except for RESET), the corresponding vector is loaded in the PC register and the I1 and I0 bits of the CC are set to disable interrupts (level 3). These sources allow the processor to exit HALT mode.

TLI (Top Level Hardware Interrupt)

This hardware interrupt occurs when a specific edge is detected on the dedicated TLI pin.

Caution:

A TRAP instruction must not be used in a TLI service routine.

TRAP (Non Maskable Software Interrupt)

This software interrupt is serviced when the TRAP instruction is executed. It will be serviced according to the flowchart in *Figure 17* as a TLI.

Caution:

TRAP can be interrupted by a TLI.

RESET

The RESET source has the highest priority in the CPU. This means that the first current routine has the highest software priority (level 3) and the highest hardware priority. See the RESET chapter for more details.

#### Maskable sources

Maskable interrupt vector sources can be serviced if the corresponding interrupt is enabled and if its own interrupt software priority (in ISPRx registers) is higher than the one currently being serviced (I1 and I0 in CC register). If any of these two conditions is false, the interrupt is latched and thus remains pending.

#### External Interrupts

External interrupts allow the processor to exit from HALT low power mode.

External interrupt sensitivity is software selectable through the register.

External interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

If several input pins of a group connected to the same interrupt line are selected simultaneously, these will be logically NANDed.

#### Peripheral Interrupts

Usually the peripheral interrupts cause the Device to exit from HALT mode except those mentioned in the "Interrupt Mapping" table.

A peripheral interrupt occurs when a specific flag is set in the peripheral status registers and if the corresponding enable bit is set in the peripheral control register.

The general sequence for clearing an interrupt is based on an access to the status register followed by a read or write to an associated register.

Note:

The clearing sequence resets the internal latch. A pending interrupt (i.e. waiting for being serviced) will therefore be lost if the clear sequence is executed.

57

# 7.3 Interrupts and low power modes

All interrupts allow the processor to exit the WAIT low power mode. On the contrary, only external and other specified interrupts allow the processor to exit from the HALT modes (see column "Exit from HALT" in "Interrupt Mapping" table). When several pending interrupts are present while exiting HALT mode, the first one serviced can only be an interrupt with exit from HALT mode capability and it is selected through the same decision process shown in *Figure 18*.

Note:

If an interrupt, that is not able to Exit from HALT mode, is pending with the highest priority when exiting HALT mode, this interrupt is serviced after the first one serviced.

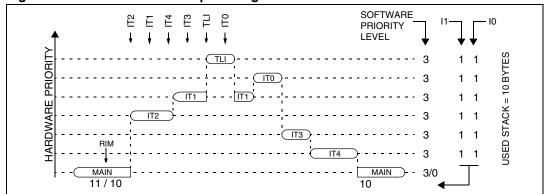

# 7.4 Concurrent and nested management

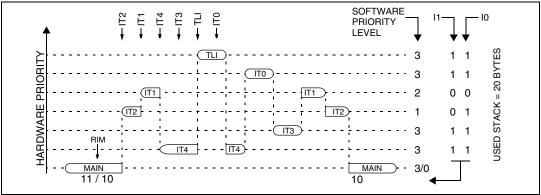

The following *Figure 19* and *Figure 20* show two different interrupt management modes. The first is called concurrent mode and does not allow an interrupt to be interrupted, unlike the nested mode in *Figure 20*. The interrupt hardware priority is given in this order from the lowest to the highest: MAIN, IT4, IT3, IT2, IT1, IT0, TLI. The software priority is given for each interrupt.

Warning: A stack overflow may occur without notifying the software of the failure.

Figure 19. Concurrent interrupt management

Figure 20. Nested interrupt management

### 7.5 Interrupt register description

#### **CPU CC register interrupt bits**

Read/Write

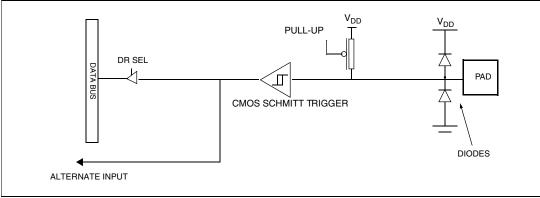

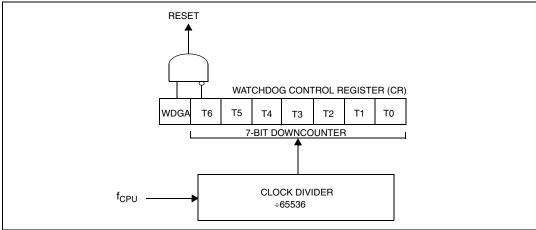

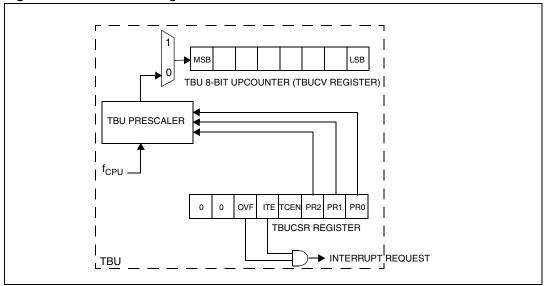

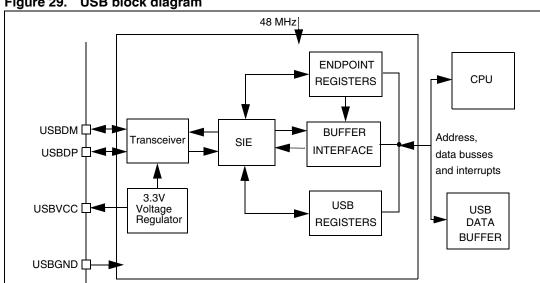

Reset Value: 111x 1010 (xAh)