# **Atmel CryptoMemory**

#### SUMMARY DATASHEET

#### **Features**

- One of a family of devices with user memories from 1-Kbit to 8-Kbit

- 1-Kbit (128-byte) EEPROM user memory

- Four 256-bit (32-byte) zones

- · Self-timed write cycle

- Single byte or 16-byte page write mode

- Programmable access rights for each zone

- 2-Kbit configuration zone

- 37-byte OTP Area for User-defined Codes

- 160-byte Area for User-defined Keys and Passwords

- High security features

- 64-bit mutual authentication protocol (under license of ELVA)

- Cryptographic Message Authentication Codes (MAC)

- Stream encryption

- Four key sets for authentication and encryption

- Eight sets of two 24-bit passwords

- Anti-tearing function

- · Voltage and frequency monitors

- Smart card features

- ISO 7816 Class B (3V) operation

- ISO 7816-3 asynchronous T=0 protocol (Gemplus<sup>®</sup> Patent) \*

- Multiple zones, key sets and passwords for multi-application use

- Synchronous 2-wire serial interface for faster device initialization \*

- Programmable 8-byte answer-to-reset register

- ISO 7816-2 compliant modules

- Embedded application features

- Low voltage supply: 2.7V 3.6V

- Secure nonvolatile storage for sensitive system or user information

- 2-wire serial interface (TWI, 5V compatible)

- 1.0MHz compatibility for fast operation

- Standard 8-lead plastic packages, green compliant (exceeds RoHS)

- Same pin configuration as Atmel<sup>®</sup> AT24CXXX Serial EEPROM in SOIC and PDIP packages

- High reliability

Endurance: 100,000 cyclesData retention: 10 yearsESD protection: 2,000V min

This is a summary document. The complete document is available on the Atmel website at www.atmel.com.

\* Note: Modules available with either T = 0 / 2-wire modes or 2-wire mode only

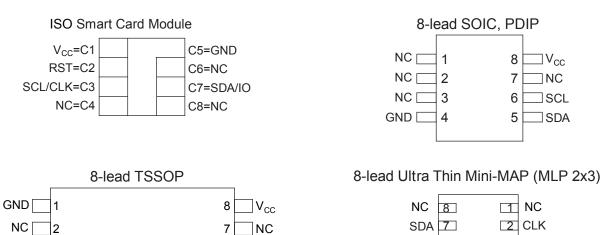

Table 1. Pin Assignments

| Pad             | Description              | ISO<br>Module | TWI<br>Module | "SOIC,<br>PDIP" | TSSOP | Mini-MAP |

|-----------------|--------------------------|---------------|---------------|-----------------|-------|----------|

| V <sub>CC</sub> | Supply Voltage           | C1            | C1            | 8               | 8     | 4        |

| GND             | Ground                   | C5            | C5            | 4               | 1     | 5        |

| SCL/CLK         | Serial Clock Input       | C3            | C3            | 6               | 6     | 2        |

| SDA/IO          | Serial Data Input/Output | C7            | C7            | 5               | 3     | 7        |

| RST             | Reset Input              | C2            | NC            | NC              | NC    | NC       |

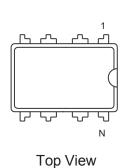

Figure 1. Pin Configuration

SDA[

NC

CLK

NC

6

5

3 NC

4 V<sub>cc</sub>

NC

GND 5

6

**Bottom View**

# 1. Description

The Atmel AT88SC0104CA member of the Atmel CryptoMemory<sup>®</sup> family is a high-performance secure memory providing 1-Kbit of user memory with advanced security and cryptographic features built in. The user memory is divided into four 32-byte zones, each of which may be individually set with different security access rights or effectively combined together to provide space for one to four data files. The AT88SC0104CA features an enhanced command set that allows direct communication with microcontroller hardware 2-wire interface thereby allowing for faster firmware development with reduced code space requirements.

### 1.1 Smart Card Applications

The AT88SC0104CA provides high security, low cost, and ease of implementation without the need for a microprocessor operating system. The embedded cryptographic engine provides for dynamic, symmetric-mutual authentication between the device and host, as well as performing stream encryption for all data and passwords exchanged between the device and host. Up to four unique key sets may be used for these operations. The AT88SC0104CA offers the ability to communicate with virtually any smart card reader using the asynchronous T = 0 protocol (Gemplus Patent) defined in ISO 7816-3.

#### 1.2 Embedded Applications

Through dynamic, symmetric-mutual authentication, data encryption, and the use of cryptographic Message Authentication Codes (MAC), the AT88SC0104CA provides a secure place for storage of sensitive information within a system. With its tamper detection circuits, this information remains safe even under attack. A 2-wire serial interface running at speeds up to 1.0MHz provides fast and efficient communications with up to 15 individually addressable devices. The AT88SC0104CA is available in industry standard 8-lead packages with the same familiar pin configuration as AT24CXXX Serial EEPROM devices.

Note: Does not apply to either the TSSOP or the ultra thin mini-map pinouts

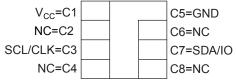

Figure 1-1. Block Diagram

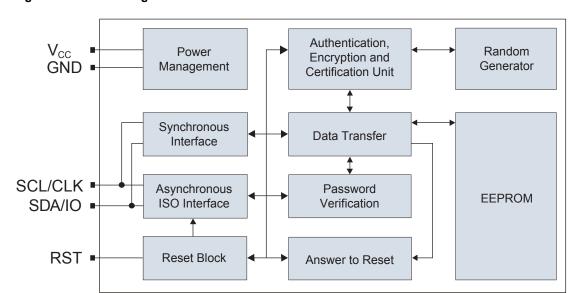

# 2. Connection Diagram

Figure 2-1. Connection Diagram

# 3. Pin Descriptions

# 3.1 Supply Voltage (V<sub>cc</sub>)

The  $V_{\text{CC}}$  input is a 2.7V to 3.6V positive voltage supplied by the host.

## 3.2 Clock (SCL/CLK)

When using the asynchronous T = 0 protocol, the CLK (SCL) input provides the device with a carrier frequency f. The nominal length of one bit emitted on I/O is defined as an "elementary time unit" (ETU) and is equal to 372/f.

When using the synchronous protocol, data clocking is done on the positive edge of the clock when writing to the device and on the negative edge of the clock when reading from the device.

#### 3.3 Reset (RST)

The AT88SC0104CA provides an ISO 7816-3 compliant asynchronous Answer-To-Reset (ATR) sequence. Upon activation of the reset sequence, the device outputs bytes contained in the 64-bit Answer-To-Reset register. An internal pull-up on the RST input pad allows the device to operate in synchronous mode without bonding RST. The AT88SC0104CA does not support an Answer-To-Reset sequence in the synchronous mode of operation.

#### 3.4 Serial Data (SDA/IO)

The SDA/IO pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wired with any number of other open-drain or open-collector devices. An external pull-up resistor should be connected between SDA/IO and  $V_{CC}$ . The value of this resistor and the system capacitance loading the SDA/IO bus will determine the rise time of SDA/IO. This rise time will determine the maximum frequency during read operations. Low value pull-up resistors will allow higher frequency operations while drawing higher average power supply current. SDA/IO information applies to both asynchronous and synchronous protocols.

# 4. Absolute Maximum Ratings\*

| Operating temperature40°C to +85°C                                     |

|------------------------------------------------------------------------|

| Storage temperature65°C to + 150°C                                     |

| Voltage on any pin with respect to ground 0.7 to V <sub>CC</sub> +0.7V |

| Maximum operating voltage 4.0V                                         |

| DC output current 5.0mA                                                |

|                                                                        |

\*Notice:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

Table 4-1. DC Characteristics

Applicable over recommended operating range from V<sub>CC</sub> = +2.7 to 3.6V, T<sub>AC</sub> = -40°C to +85°C (unless otherwise noted)

| Symbol                         | Parameter                  | Test Conditions                                           | Min                   | Тур | Max                    | Units |

|--------------------------------|----------------------------|-----------------------------------------------------------|-----------------------|-----|------------------------|-------|

| V <sub>CC</sub> <sup>(1)</sup> | Supply Voltage             |                                                           | 2.7                   |     | 3.6                    | V     |

| Icc                            | Supply Current             | Async Read at 3.57MHz                                     |                       |     | 5                      | mA    |

| Icc                            | Supply Current             | Async Write at 3.57MHz                                    |                       |     | 5                      | mA    |

| Icc                            | Supply Current             | Synch Read at 1MHz                                        |                       |     | 5                      | mA    |

| I <sub>CC</sub>                | Supply Current             | Synch Write at 1MHz                                       |                       |     | 5                      | mA    |

| I <sub>SB</sub>                | Standby Current            | $V_{IN} = V_{CC}$ or GND                                  |                       |     | 100                    | μΑ    |

| V <sub>IL</sub>                | SDA/IO Input Low Voltage   |                                                           | 0                     |     | V <sub>CC</sub> x 0.2  | V     |

| V <sub>IL</sub>                | CLK Input Low Voltage      |                                                           | 0                     |     | V <sub>CC</sub> x 0.2  | V     |

| V <sub>IL</sub>                | RST Input Low Voltage      |                                                           | 0                     |     | V <sub>CC</sub> x 0.2  | V     |

| V <sub>IH</sub> <sup>(1)</sup> | SDA/IO Input High Voltage  |                                                           | V <sub>CC</sub> x 0.7 |     | 5.5                    | V     |

| V <sub>IH</sub> <sup>(1)</sup> | SCL/CLK Input High Voltage |                                                           | V <sub>CC</sub> x 0.7 |     | 5.5                    | V     |

| V <sub>IH</sub> <sup>(1)</sup> | RST Input High Voltage     |                                                           | V <sub>CC</sub> x 0.7 |     | 5.5                    | V     |

| I <sub>IL</sub>                | SDA/IO Input Low Current   | $0 < V_{IL} < V_{CC} \times 0.15$                         |                       |     | 15                     | μΑ    |

| I <sub>IL</sub>                | SCL/CLK Input Low Current  | $0 < V_{IL} < V_{CC} \times 0.15$                         |                       |     | 15                     | μΑ    |

| I <sub>IL</sub>                | RST Input Low Current      | $0 < V_{IL} < V_{CC} \times 0.15$                         |                       |     | 50                     | μΑ    |

| I <sub>IH</sub>                | SDA/IO Input High Current  | V <sub>CC</sub> x 0.7 < V <sub>IH</sub> < V <sub>CC</sub> |                       |     | 20                     | μΑ    |

| I <sub>IH</sub>                | SCL/CLK Input High Current | $V_{CC} \times 0.7 < V_{IH} < V_{CC}$                     |                       |     | 100                    | μΑ    |

| I <sub>IH</sub>                | RST Input High Current     | $V_{CC} \times 0.7 < V_{IH} < V_{CC}$                     |                       |     | 150                    | μΑ    |

| V <sub>OH</sub>                | SDA/IO Output High Voltage | 20K ohm external pull-up                                  | V <sub>CC</sub> x 0.7 |     | Vcc                    | V     |

| V <sub>OL</sub>                | SDA/IO Output Low Voltage  | I <sub>OL</sub> = 1mA                                     | 0                     |     | V <sub>CC</sub> x 0.15 | V     |

| I <sub>OH</sub>                | SDA/IO Output High Current | V <sub>OH</sub>                                           |                       |     | 20                     | μΑ    |

| I <sub>OL</sub>                | SDA/IO Output Low Current  | V <sub>OL</sub>                                           |                       |     | 10                     | mA    |

Note: 1. To prevent latch up conditions from occurring during power up of the Atmel AT88SC0104CA,  $V_{CC}$  must be turned on before applying  $V_{IH}$ . For powering down,  $V_{IH}$  must be removed before turning  $V_{CC}$  off

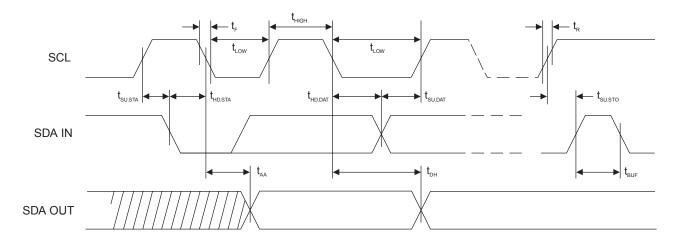

#### Table 4-2. AC Characteristics

Applicable over recommended operating range from  $V_{CC}$  = +2.7 to 3.6V,  $T_{AC}$  = -40°C to +85°C, CL = 30pF (unless otherwise noted)

| Symbol              | Parameter                   | Min | Max         | Units |

|---------------------|-----------------------------|-----|-------------|-------|

| f <sub>CLK</sub>    | Async Clock Frequency       | 1   | 4           | MHz   |

| f <sub>CLK</sub>    | Synch Clock Frequency       | 0   | 1           | MHz   |

|                     | Clock Duty cycle            | 40  | 60          | %     |

| t <sub>R</sub>      | "Rise Time - SDA/IO, RST"   |     | 1           | μS    |

| t <sub>F</sub>      | "Fall Time - SDA/IO, RST"   |     | 1           | μS    |

| t <sub>R</sub>      | Rise Time - SCL/CLK         |     | 9% x period | μS    |

| t <sub>F</sub>      | Fall Time - SCL/CLK         |     | 9% x period | μS    |

| t <sub>AA</sub>     | Clock Low to Data Out Valid |     | 250         | nS    |

| t <sub>HD.STA</sub> | Start Hold Time             | 200 |             | nS    |

| t <sub>SU.STA</sub> | Start Set-up Time           | 200 |             | nS    |

| t <sub>HD.DAT</sub> | Data In Hold Time           | 10  |             | nS    |

| t <sub>SU.DAT</sub> | Data In Set-up Time         | 100 |             | nS    |

| t <sub>SU.STO</sub> | Stop Set-up Time            | 200 |             | nS    |

| t <sub>DH</sub>     | Data Out Hold Time          | 20  |             | nS    |

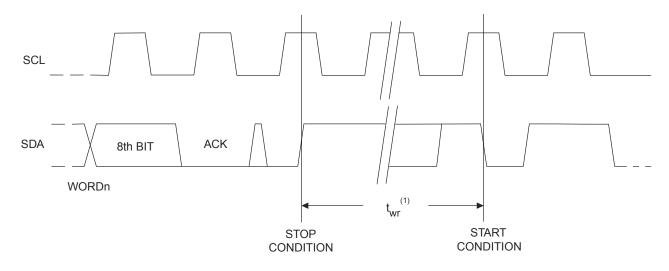

| t <sub>WR</sub>     | Write Cycle Time            |     | 5           | mS    |

# 5. Device Operations for Synchronous Protocols

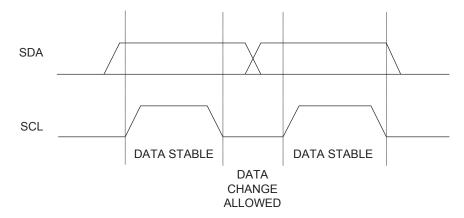

#### 5.1 Clock and Data Transitions

The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see Figure 5-3 on page 8). Data changes during SCL high periods will indicate a start or stop condition as defined below.

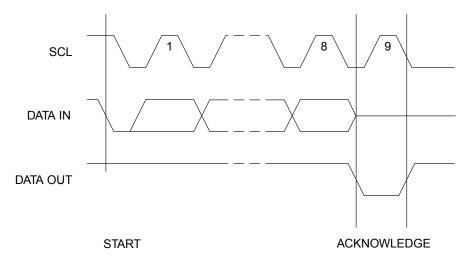

#### 5.1.1 Start Condition

A high-to-low transition of SDA with SCL high defines a start condition which must precede all commands (see Figure 5-4 on page 8).

#### 5.1.2 Stop Condition

A low-to-high transition of SDA with SCL high defines a stop condition. After a read sequence, the stop condition will place the EEPROM in a standby power mode (see Figure 5-4 on page 8).

#### 5.1.3 Acknowledge

All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle (see Figure 5-5 on page 8).

# 5.2 Memory Reset

After an interruption in communication due protocol errors, power loss or any reason, perform "Acknowledge Polling" to properly recover from the condition. Acknowledge polling consists of sending a start condition followed by a valid CryptoMemory command byte and determining if the device responded with an acknowledge.

Figure 5-1. Bus Time for 2-wire Serial Communications

#### SCL: Serial Clock, SDA: Serial Data I/O

Figure 5-2. Write Cycle Timing

SCL: Serial Clock, SDA: Serial Data I/O

Note: The write cycle time t<sub>wr</sub> is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle

Figure 5-3. Data Validity

Figure 5-4. Start and Stop Definitions

Figure 5-5. Output Acknowledge

#### 6. Device Architecture

#### 6.1 User Zones

The EEPROM user memory is divided into four zones of 256 bits each. Multiple zones allow for storage of different types of data or files in different zones. Access to user zones is permitted only after meeting proper security requirements. These security requirements are user definable in the configuration memory during device personalization. If the same security requirements are selected for multiple zones, then these zones may effectively be accessed as one larger zone.

Figure 6-1. User Zones

| Zone   |      | \$0      | \$1      | \$2 | \$3  | \$4  | \$5 | \$6 | \$7 |  |  |  |

|--------|------|----------|----------|-----|------|------|-----|-----|-----|--|--|--|

| User 0 | \$00 |          |          |     |      |      |     |     |     |  |  |  |

|        | -    |          |          |     | 32 b | ytes |     |     |     |  |  |  |

|        | -    |          |          |     |      |      |     |     |     |  |  |  |

|        | \$18 |          |          |     |      |      |     |     |     |  |  |  |

| User 1 | \$00 |          |          |     |      |      |     |     |     |  |  |  |

|        | -    |          | 32 bytes |     |      |      |     |     |     |  |  |  |

|        | -    |          |          |     |      |      |     |     |     |  |  |  |

|        | \$18 |          |          |     |      |      |     |     |     |  |  |  |

| User 2 | \$00 |          |          |     |      |      |     |     |     |  |  |  |

|        | -    | 32 bytes |          |     |      |      |     |     |     |  |  |  |

|        | -    |          |          |     |      |      |     |     |     |  |  |  |

|        | \$18 |          |          |     |      |      |     |     |     |  |  |  |

| User 3 | \$00 |          |          |     |      |      |     |     |     |  |  |  |

|        | -    |          |          |     | 32 b | ytes |     |     |     |  |  |  |

|        | -    |          |          |     |      |      |     |     |     |  |  |  |

|        | \$18 |          |          |     |      |      |     |     |     |  |  |  |

# 7. Control Logic

Access to the user zones occur only through the control logic built into the device. This logic is configurable through access registers, key registers and keys programmed into the configuration memory during device personalization. Also implemented in the control logic is a cryptographic engine for performing the various higher-level security functions of the device.

# 8. Configuration Memory

The configuration memory consists of 2048 bits of EEPROM memory used for storage of passwords, keys, codes, and also used for definition of security access rights for the user zones. Access rights to the configuration memory are defined in the control logic and are not alterable by the user after completion of personalization.

Figure 8-1. Configuration Memory

|      | \$0                                 | \$1 | \$2      | \$3         | \$4       | \$5       | \$6    | \$7             |                      |

|------|-------------------------------------|-----|----------|-------------|-----------|-----------|--------|-----------------|----------------------|

| \$00 | Answer To Reset                     |     |          |             |           |           |        |                 | l do ntifito ati a n |

| \$08 | Fab Code MTZ Card Manufacturer Code |     |          |             |           |           |        | Identifitcation |                      |

| \$10 |                                     |     |          | Lot Histo   | ory Code  |           |        |                 | Read Only            |

| \$18 | DCR Identification Number Nc        |     |          |             |           |           |        |                 |                      |

| \$20 | AR0                                 | PR0 | AR1      | PR1         | AR2       | PR2       | AR3    | PR3             |                      |

| \$28 |                                     |     |          |             |           |           |        |                 |                      |

| \$30 | Reserved  Issuer Code               |     |          |             |           |           |        |                 | Access Control       |

| \$38 |                                     |     |          |             |           |           |        |                 |                      |

| \$40 |                                     |     |          |             |           |           |        |                 |                      |

| \$48 |                                     |     |          | issuei      | Code      |           |        |                 |                      |

| \$50 |                                     |     |          |             |           |           |        |                 |                      |

| \$58 |                                     |     |          |             |           |           |        |                 |                      |

| \$60 |                                     |     |          |             |           |           |        |                 |                      |

| \$68 |                                     |     | C A 41   | 4: 4:       |           | .4:       |        |                 |                      |

| \$70 |                                     |     | For Autr | nentication | and Encry | otion use |        |                 | Cryptography         |

| \$78 |                                     |     |          |             |           |           |        |                 |                      |

| \$80 |                                     |     |          |             |           |           |        |                 |                      |

| \$88 |                                     |     |          |             |           |           |        |                 |                      |

| \$90 |                                     |     |          |             |           |           |        |                 |                      |

| \$98 |                                     |     | C A 41   | 4: 4:       |           | .4:       |        |                 | 0                    |

| \$A0 |                                     |     | For Autr | nentication | and Encry | otion use |        |                 | Secret               |

| \$A8 |                                     |     |          |             |           |           |        |                 |                      |

| \$B0 | PAC                                 |     | Write 0  |             | PAC       |           | Read 0 |                 |                      |

| \$B8 | PAC                                 |     | Write 1  |             | PAC       |           | Read 1 |                 |                      |

| \$C0 | PAC                                 |     | Write 2  |             | PAC       |           | Read 2 |                 |                      |

| \$C8 | PAC                                 |     | Write 3  |             | PAC       |           | Read 3 |                 | Description          |

| \$D0 | PAC                                 |     | Write 4  |             | PAC       |           | Read 4 |                 | Password             |

| \$D8 | PAC                                 |     | Write 5  |             | PAC       |           | Read 5 |                 |                      |

| \$E0 | PAC                                 |     | Write 6  |             | PAC       |           | Read 6 |                 |                      |

| \$E8 | PAC                                 |     | Write 7  |             | PAC       |           | Read 7 |                 |                      |

| \$F0 |                                     |     |          | Dose        | anuad     |           |        |                 | Forbiddon            |

| \$F8 |                                     |     |          | Rese        | erved     |           |        |                 | Forbidden            |

### 8.2 Security Fuses

There are three fuses on the device that must be blown during the device personalization process. Each fuse locks certain portions of the configuration zone as OTP (One-Time Programmable) memory. Fuses are designed for the module manufacturer, card manufacturer and card issuer and should be blown in sequence, although all programming of the device and blowing of the fuses may be performed at one final step.

# 9. Communication Security Modes

Communications between the device and host operate in three basic modes. Standard mode is the default mode for the device after power-up. Authentication mode is activated by a successful authentication sequence. Encryption mode is activated by a successful encryption activation following a successful authentication.

Table 9-1. Communication Security Modes<sup>(1)</sup>

| Mode           | Configuration Data | User Data | Passwords | Data Integrity Check |

|----------------|--------------------|-----------|-----------|----------------------|

| Standard       | Clear              | Clear     | Clear     | MDC <sup>(1)</sup>   |

| Authentication | Clear              | Clear     | Encrypted | MAC <sup>(1)</sup>   |

| Encryption     | Clear              | Encrypted | Encrypted | MAC <sup>(1)</sup>   |

Note: 1. Configuration data include viewable areas of the configuration zone except the passwords:

- MDC (Modification Detection Code)

- MAC (Message Authentication Code)

# 10. Security Options

#### 10.1 Anti-Tearing

In the event of a power loss during a write cycle, the integrity of the device's stored data is recoverable. This function is optional – the host may choose to activate the anti-tearing function, depending on application requirements. When anti-tearing is active, write commands take longer to execute, since more write cycles are required to complete them, and data is limited to a maximum of eight bytes for each write request.

Data is written first into a buffer zone in EEPROM instead of the intended destination address, but with the same access conditions. The data is then written in the required location. If this second write cycle is interrupted due to a power loss, the device will automatically recover the data from the system buffer zone at the next power-up. Non-volatile buffering of the data is done automatically by the device.

During power-up in applications using anti-tearing, the host is required to perform ACK polling in the event that the device needs to carry out the data recovery process.

#### 10.2 Write Lock

If a user zone is configured in the write lock mode, the lowest address byte of an 8-byte page constitutes a write access byte for the bytes of that page.

Example: For example, the write lock byte at \$080 controls the bytes from \$081 to \$087.

Figure 10-1. Write Lock Example

| Address | \$0      | \$1       | \$2       | \$3       | \$4       | \$5       | \$6       | \$7       |

|---------|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| \$080   | 11011001 | xxxx xxxx |

|         |          | locked    | locked    |           |           | locked    |           |           |

The Write-Lock byte itself may be locked by writing its least significant (rightmost) bit to "0". Moreover, when write lock mode is activated, the write lock byte can only be programmed – that is, bits written to "0" cannot return to "1".

In the write lock configuration, write operations are limited to writing only one byte at a time. Attempts to write more than one byte will result in writing of just the first byte into the device.

#### 10.3 Password Verification

Passwords may be used to protect read and/or write access of any user zone. When a valid password is presented, it is memorized and active until power is turned off, unless a new password is presented or RST becomes active. There are eight password sets that may be used to protect any user zone. Only one password is active at a time.

Presenting the correct write password also grants read access privileges.

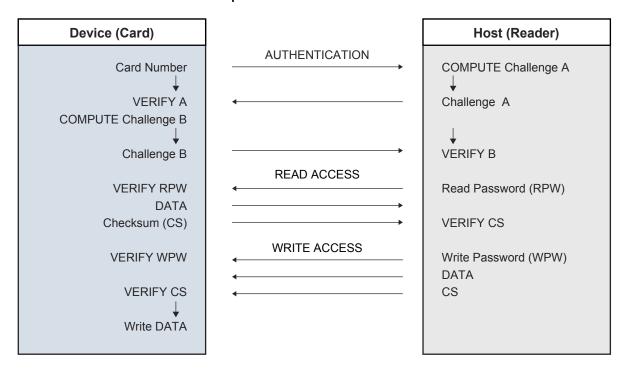

#### 10.4 Authentication Protocol

The access to a user zone may be protected by an authentication protocol. Any one of four keys may be selected to use with a user zone.

Authentication success is memorized and active as long as the chip is powered, unless a new authentication is initialized or RST becomes active. If the new authentication request is not validated, the card loses its previous authentication which must be presented again to gain access. Only the latest request is memorized.

Figure 10-2. Password and Authentication Operations

Note:

Authentication and password verification may be attempted at any time and in any order. Exceeding corresponding authentication or password attempts trial limit renders subsequent authentication or password verification attempts futile.

#### 10.5 Cryptographic Message Authentication Codes

AT88SC0104CA implements a data validity check function in the standard, authentication or encryption modes of operation.

In the standard mode, data validity check is done through a Modification Detection Code (MDC), in which the host may read an MDC from the device in order to verify that the data sent was received correctly.

In authentication and encryption modes, the data validity check becomes more powerful since it provides a bidirectional data integrity check and data origin authentication capability in the form of a Message Authentication Codes (MAC). Only the host/device that carried out a valid authentication is capable of computing a valid MAC. While operating in the authentication or encryption modes, the use of MAC is required. For an ingoing command, if the device calculates a MAC different from the MAC transmitted by the host, not only is the command abandoned but the security privilege is revoked. A new authentication and/or encryption activation will be required to reactivate the MAC.

#### 10.6 Encryption

The data exchanged between the device and the host during read, write and verify password commands may be encrypted to ensure data confidentiality.

The issuer may choose to require encryption for a user zone by settings made in the configuration memory. Any one of four keys may be selected for use with a user zone. In this case, activation of the encryption mode is required in order to read/write data in the zone and only encrypted data will be transmitted. Even if not required, the host may still elect to activate encryption provided the proper keys are known.

#### 10.7 Supervisor Mode

Enabling this feature allows the holder of one specific password to gain full access to all eight password sets, including the ability to change passwords.

# 10.8 Modify Forbidden

No write access is allowed in a user zone protected with this feature at any time. The user zone must be written during device personalization prior to blowing the security fuses.

#### 10.9 Program Only

For a user zones protected by this feature, data can only be programmed (bits change from a "1" to a "0"), but not erased (bits change from a "0" to a "1").

#### 11. Protocol Selection

The AT88SC0104CA supports two different communication protocols.

#### Smartcard Applications:

Smartcard applications use ISO 7816-B protocol in asynchronous T = 0 mode for compatibility and interoperability with industry standard smartcard readers.

#### Embedded Applications:

A 2-wire serial interface provides fast and efficient connectivity with other logic devices or microcontrollers.

The power-up sequence determines establishes the communication protocol for use within that power cycle. Protocol selection is allowed only during power-up.

# 11.1 Synchronous 2-wire Serial Interface

The synchronous mode is the default mode after power up. This is due to the presence of an internal pull-up on RST. For embedded applications using CryptoMemory in standard plastic packages, this is the only available communication protocol.

- Power-up V<sub>CC</sub>, RST goes high also

- After stable V<sub>CC</sub>, SCL(CLK) and SDA(I/O) may be driven

- Once synchronous mode has been selected, it is not possible to switch to asynchronous mode without first powering

off the device

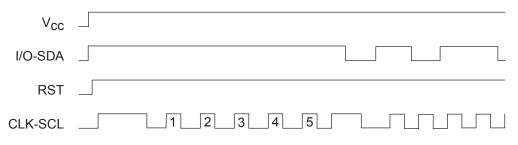

#### Figure 11-1. Synchronous 2-wire Protocol

Note: Five clock pulses must be sent before the first command is issued

#### 11.2 Asynchronous T = 0 Protocol

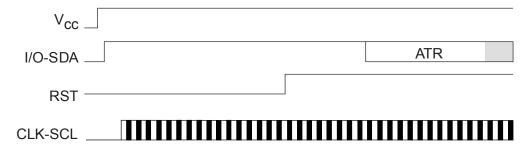

This power-up sequence complies to ISO 7816-3 for a cold reset in smart card applications.

- V<sub>CC</sub> goes high; RST, I/O (SDA) and CLK (SCL) are low

- Set I/O (SDA) in receive mode

- Provide a clock signal to CLK (SCL)

- RST goes high after 400 clock cycles

The device will respond with a 64-bit ATR code, including historical bytes to indicate the memory density within the CryptoMemory family.

Once asynchronous mode has been selected, it is not possible to switch to synchronous mode without first powering off the device.

Figure 11-2. Asynchronous T = 0 Protocol (Gemplus Patent)

# 12. Initial Device Programming

Enabling the security features of CryptoMemory requires prior personalization. Personalization entails setting up of desired access rights by zones, passwords and key values, programming these values into the configuration memory with verification using simple write and read commands, and then blowing fuses to lock this information in place.

Gaining access to the configuration memory requires successful presentation of a secure (or transport) code. The initial signature of the secure (transport) code for the AT88SC0104CA device is \$DD 42 97. This is the same as the write seven password. The user may elect to change the signature of the secure code anytime after successful presentation.

After writing and verifying data in the configuration memory, the security fuses *must* be blown to lock this information in the device. For additional information on personalizing CryptoMemory, please see the application notes *Programming CryptoMemory for Embedded Applications and Initializing CryptoMemory for Smart Card Applications* from the product page at www.atmel.com/products/securemem.

# 13. Ordering Information

| Atmel Ordering Code                                                         | Package                                                                                | Voltage Range | Temperature Range                                               |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------|

| AT88SC0104CA-MJ AT88SC0104CA-MP AT88SC0104CA-MJTG AT88SC0104CA-MPTG         | M2 – J Module - ISO<br>M2 – P Module - ISO<br>M2 – J Module -TWI<br>M2 – P Module -TWI | 2.7V-3.6V     | Commercial (0°C to 70°C)                                        |

| AT88SC0104CA-PU<br>AT88SC0104CA-SH<br>AT88SC0104CA-TH<br>AT88SC0104CA-Y6H-T | 8P3<br>8S1<br>8X<br>8MA2                                                               | 2.7V-3.6V     | Green Compliant<br>(exceeds RoHS)/Industrial<br>(-40°C to 85°C) |

| AT88SC0104CA-WI                                                             | 7 mil wafer                                                                            | 2.7V-3.6V     | Industrial (-40°C to 85°C)                                      |

| Package Type <sup>(1) ( 2)</sup> |                                                                                            |  |  |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| M2 - J Module : ISO or TWI       | M2 ISO 7816 Smart Card Module                                                              |  |  |  |  |  |  |

| M2 - P Module: ISO or TWI        | M2 ISO 7816 Smart Card Module with Atmel <sup>®</sup> logo                                 |  |  |  |  |  |  |

| 8P3                              | 8-lead, 0.300" wide, Plastic Dual Inline (PDIP)                                            |  |  |  |  |  |  |

| 8S1                              | 8-lead, 0.150" wide, Plastic Gull Wing Small Outline (JEDEC SOIC)                          |  |  |  |  |  |  |

| 8X                               | 8-lead, 4.4mm body, Plastic Thin Shrink Small Outline (TSSOP)                              |  |  |  |  |  |  |

| 8MA2                             | 8-lead, 2.0 x 3.0mm body, 0.50mm pitch, Ultra Thin Mini-map, Dual No Lead (DFN), (MLP 2x3) |  |  |  |  |  |  |

Note:

- 1. Formal drawings may be obtained from an Atmel sales office

- 2. Both the J and P module packages are used for either ISO (T=0 / 2-wire mode) or TWI (2-wire mode only)

# 14. Package Information

# Ordering Code: MJ or MJTG

Module size: M2

Dimension\*: 12.6 x 11.4 [mm] Glob top: round – Æ 8.5 [mm]

Thickness: 0.58 [mm] Pitch: 14.25 mm

## **Ordering Code: MP or MPTG**

Module size: M2

Dimension\*: 12.6 x 11.4 [mm] Glob top: square – 8.8 x 8.8 [mm]

Thickness: 0.58 [mm] Pitch: 14.25 mm

Note:

\*The module dimensions listed refer to the dimensions of the exposed metal contact area. The actual dimensions of the module after excise or punching from the carrier tape are generally 0.4mm greater in both directions (i.e., a punched M2 module will yield 13.0 x 11.8mm).

# 14.1 Atmel AT88SC0104CA Package Marking Information

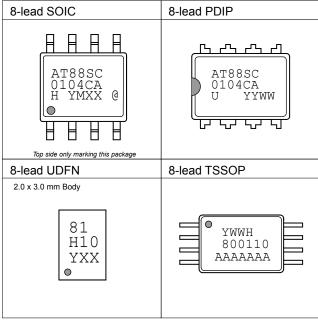

# AT88SC0104CA: Package Marking Information

Note 1: designates pin 1

Note 2: Package drawings are not to scale

| AT88SC01                   | 04CA                            |                                             | Truncation C                     | ode #####: 0104 | CA ##: 1                                  | 1 #: 1               |

|----------------------------|---------------------------------|---------------------------------------------|----------------------------------|-----------------|-------------------------------------------|----------------------|

| Date Code                  | s                               |                                             |                                  |                 |                                           |                      |

| Y = Year                   |                                 | M = Month                                   | YY = Year                        |                 | WW = W                                    | ork Week of Assembly |

| 2: 2012                    | 6: 2016                         | A = January                                 | 12: 2014                         | 16: 2016        | 02:                                       | Week 2               |

| 3: 2013                    | 7: 2017                         | B = February                                | 13: 2013                         | 17: 2017        | 04:                                       | Week 4               |

| 4: 2014                    | 8: 2018                         |                                             | 14: 2014                         | 18: 2018        |                                           |                      |

| 5: 2015                    | 9: 2019                         | L = December                                | 15: 2015                         | 19: 2019        | 52:                                       | Week 52              |

| Country of Assembly Lot Nu |                                 | ot Number                                   |                                  | Grade/L         | ead Finish Material                       |                      |

| , ,                        |                                 | AAAA = Atmel Wafe<br>Marked on<br>PDIP only | er Lot Number<br>Bottom side for | U:<br>H:        | Industrial/Matte Tin<br>Industrial/NiPdAu |                      |

| Trace Cod                  | е                               |                                             |                                  |                 | Atmel T                                   | runcation            |

|                            | e Code (Atmel L<br>nple: AA, AB | ot Numbers to Co                            | rrespond to Code)                |                 | AT:                                       | Atmel                |

3/6/12

| Atmel                                           | TITLE                                                  | DRAWING NO.  | REV. |

|-------------------------------------------------|--------------------------------------------------------|--------------|------|

| Package Mark Contact: DL-CSO-Assy_eng@atmel.com | 88SC0104CASM, AT88SC0104CA Package Marking Information | 88SC0104CASM | Α    |

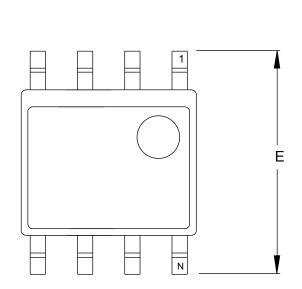

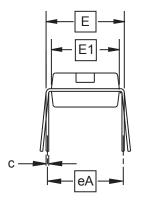

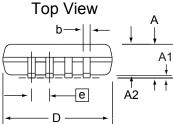

# 14.2 Ordering Code: SH 8S1 – 8-lead JEDEC SOIC

**TOP VIEW**

# SIDE VIEW

Notes: This drawing is for general information only. Refer to JEDEC Drawing MS-012, Variation AA for proper dimensions, tolerances, datums, etc.

**END VIEW**

# COMMON DIMENSIONS (Unit of Measure = mm)

| SYMBOL | MIN      | NOM | MAX  | NOTE |

|--------|----------|-----|------|------|

| Α      | 1.35     | _   | 1.75 |      |

| A1     | 0.10     | _   | 0.25 |      |

| b      | 0.31     | _   | 0.51 |      |

| С      | 0.17     | _   | 0.25 |      |

| D      | 4.80     | _   | 5.05 |      |

| E1     | 3.81     | _   | 3.99 |      |

| E      | 5.79     | _   | 6.20 |      |

| е      | 1.27 BSC |     |      |      |

| L      | 0.40     | _   | 1.27 |      |

| Ø      | 0°       | _   | 8°   |      |

6/22/11 **REV.**

G

# **Atmel**

Package Drawing Contact: packagedrawings@atmel.com

TITLE

8S1, 8-lead (0.150" Wide Body), Plastic Gull Wing Small Outline (JEDEC SOIC)

GPC SWB

DRAWING NO.

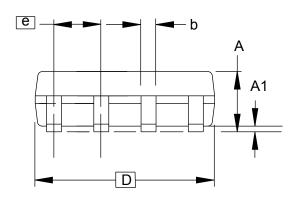

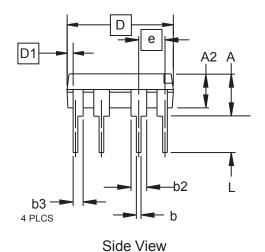

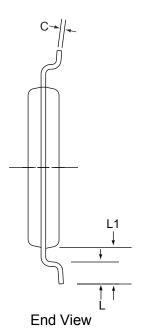

#### 14.3 **Ordering Code: PU** 8P3 - 8-lead PDIP

**End View**

COMMON DIMENSIONS (Unit of Measure = inches)

| SYMBOL | MIN       | NOM   | MAX   | NOTE |

|--------|-----------|-------|-------|------|

| Α      |           |       | 0.210 | 2    |

| A2     | 0.115     | 0.130 | 0.195 |      |

| b      | 0.014     | 0.018 | 0.022 | 5    |

| b2     | 0.045     | 0.060 | 0.070 | 6    |

| b3     | 0.030     | 0.039 | 0.045 | 6    |

| С      | 0.008     | 0.010 | 0.014 |      |

| D      | 0.355     | 0.365 | 0.400 | 3    |

| D1     | 0.005     |       |       | 3    |

| E      | 0.300     | 0.310 | 0.325 | 4    |

| E1     | 0.240     | 0.250 | 0.280 | 3    |

| е      | 0.100 BSC |       |       |      |

| eA     | 0.300 BSC |       | 4     |      |

| L      | 0.115     | 0.130 | 0.150 | 2    |

- 1. This drawing is for general information only; refer to JEDEC Drawing MS-001, Variation BA for additional information.

- Dimensions A and L are measured with the package seated in JEDEC seating plane Gauge GS-3.

D, D1 and E1 dimensions do not include mold Flash or protrusions. Mold Flash or protrusions shall not exceed 0.010 inch.

- 5. By Briant ET difficulties of the leads constrained to be perpendicular to datum.

4. E and eA measured with the leads constrained to be perpendicular to datum.

5. Pointed or rounded lead tips are preferred to ease insertion.

6. b2 and b3 maximum dimensions do not include Dambar protrusions. Dambar protrusions shall not exceed 0.010 (0.25 mm).

06/21/11

| ∕Itmel                                                | TITLE                                                              | GPC | DRAWING NO. | REV. |

|-------------------------------------------------------|--------------------------------------------------------------------|-----|-------------|------|

| Package Drawing Contact:<br>packagedrawings@atmel.com | 8P3, 8-lead, 0.300" Wide Body, Plastic Dual In-line Package (PDIP) | PTC | 8P3         | D    |

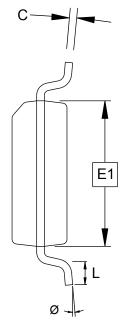

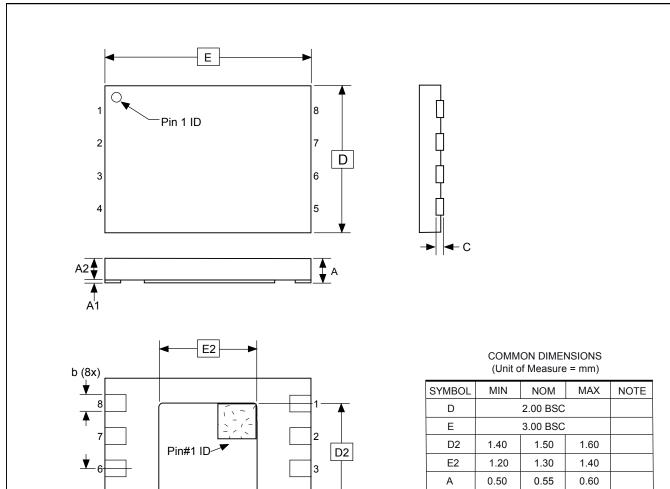

#### 14.4 **Ordering Code: TH** 8X - 8-lead TSSOP

Side View

- Notes: 1. This drawing is for general information only. Refer to JEDEC Drawing MO-153, Variation AA, for proper dimensions, tolerances, datums, etc.

- 2. Dimension D does not include mold Flash, protrusions or gate burrs. Mold Flash, protrusions and gate burrs shall not exceed 0.15mm (0.006in) per side.

- 3. Dimension E1 does not include inter-lead Flash or protrusions. Inter-lead Flash and protrusions shall not exceed 0.25mm (0.010in) per side.

- 4. Dimension b does not include Dambar protrusion. Allowable Dambar protrusion shall be 0.08mm total in excess of the b dimension at maximum material condition. Dambar cannot be located on the lower radius of the foot. Minimum space between protrusion and adjacent lead is 0.07mm.

- 5. Dimension D and E1 to be determined at Datum Plane H.

COMMON DIMENSIONS (Unit of Measure = mm)

| SYMBOL | MIN      | NOM  | MAX  | NOTE |

|--------|----------|------|------|------|

| Α      | -        | -    | 1.20 |      |

| A1     | 0.05     | -    | 0.15 |      |

| A2     | 0.80     | 1.00 | 1.05 |      |

| D      | 2.90     | 3.00 | 3.10 | 2, 5 |

| Е      | 6.40 BSC |      |      |      |

| E1     | 4.30     | 4.40 | 4.50 | 3, 5 |

| b      | 0.19     | _    | 0.30 | 4    |

| е      | 0.65 BSC |      |      |      |

| L      | 0.45     | 0.60 | 0.75 |      |

| L1     | 1.00 REF |      |      |      |

| С      |          | 0.09 | -    | 0.20 |

|        |          |      |      |      |

6/22/11

| Atmel                     | TITLE                                | GPC | DRAWING NO. | REV. |

|---------------------------|--------------------------------------|-----|-------------|------|

| Package Drawing Contact:  | 8X, 8-lead 4.4mm Body, Plastic Thin  | TNR | 8X          | D    |

| packagedrawings@atmel.com | Shrink Small Outline Package (TSSOP) |     |             |      |

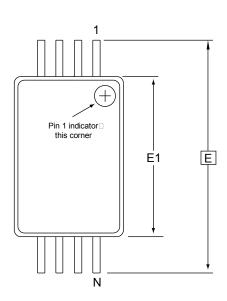

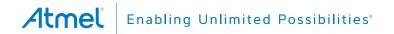

# 14.5 Ordering Code: Y6H-T

# 8MA2 - 8-pad Ultra Thin Mini-MAP

Notes: 1. This drawing is for general information only. Refer to JEDEC Drawing MO-229, for proper dimensions, tolerances, datums, etc.

2. The terminal #1 ID is a laser-marked feature.

**←** L (8x)

e (6x)

3. Dimension b applies to metallized terminal and is measured between 0.15 mm and 0.30 mm from the terminal tip. If the terminal has the optional radius on the other end of the terminal, the dimension should not be measured in that radius area.

| SYMBOL | MIN  | NOM      | MAX  | NOTE |

|--------|------|----------|------|------|

| D      |      | 2.00 BSC | ;    |      |

| Е      |      | 3.00 BSC | ;    |      |

| D2     | 1.40 | 1.50     | 1.60 |      |

| E2     | 1.20 | 1.30     | 1.40 |      |

| Α      | 0.50 | 0.55     | 0.60 |      |

| A1     | 0.0  | 0.02     | 0.05 |      |

| A2     | _    | _        | 0.55 |      |

| С      |      | 0.152 RE | F    |      |

| L      | 0.30 | 0.35     | 0.40 |      |

| е      |      | 0.50 BSC | ;    |      |

| b      | 0.18 | 0.25     | 0.30 | 3    |

| K      | 0.20 | _        | -    |      |

|        |      |          |      |      |

7/15/11

| 1tmal                     | TITLE                                       | GPC | DRAWING NO. | REV. |

|---------------------------|---------------------------------------------|-----|-------------|------|

| Atmel                     | 8MA2, 8-pad, 2 x 3 x 0.6 mm Body, Thermally |     |             |      |

| Package Drawing Contact:  | Enhanced Plastic Ultra Thin Dual Flat No    | YNZ | 8MA2        | В    |

| packagedrawings@atmel.com | Lead Package (UDFN)                         |     |             |      |

# 15. Revision History

| Doc. Rev. | Date    | Comments                                                                                                                    |

|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------|

| 5200GS    | 12/2013 | Add package marking information.  Update Atmel logos and disclaimer page.                                                   |

| 5200FS    | 12/2011 | Update template. Update package drawings, replace 8A2 with 8X and 8T6 with 8MA2. Change AT88SC0104CA-SU to AT88SC0104CA-SH. |

| 5200ES    | 08/2009 | Minor edits and TWI module updates.                                                                                         |

| 5200DS    | 07/2009 | Minor updates to package drawing information and ordering information.                                                      |

| 5200CS    | 05/2009 | Added Mini-MAP column to Table 1-1 and Mini-MAP pin-out drawing.                                                            |

| 5200BS    | 02/2009 | Connection diagram inserted; DC characteristics table updated.                                                              |

| 5200AS    | 07/2008 | Initial document release.                                                                                                   |

**Atmel Corporation**

1600 Technology Drive, San Jose, CA 95110 USA

**T:** (+1)(408) 441.0311

**F:** (+1)(408) 436.4200

www.atmel.com

© 2013 Atmel Corporation. / Rev.: Atmel-2022MS-CryptoMem-AT88SC0204C-Datasheet-Summary\_122013.

Atmel®, Atmel logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM®, ARM Connected® logo, and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.