# DUAL IO-LINK MASTER TRANSCEIVER WITH UARTS PRODUCTION DATA - NOV 27, 2013

E981.12

## **Features**

- 2-port IO-Link Master

- Integrated UART-Interface for each port

- Output drivers with typical 1 Ω

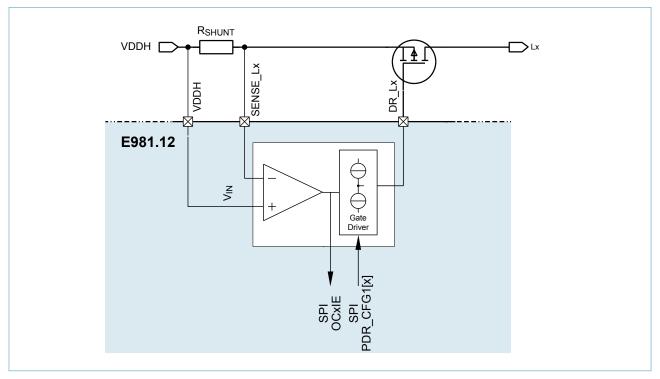

- Supporting external PMOS switches for IO-Link supply (L+) with current limitation

- Wake-up generation support

- ► Supply voltage range V<sub>VDDH</sub>: 8V − 32V / V<sub>VDD</sub>: 3.15V - 3.45V

- Over-current & short-circuit protection at output stages with configurable thresholds

- Digital inputs configurable for IO-LINK or IEC 61131-2 compatible interface

- SPI for communication, configuration, and diagnosis

- Under voltage monitor for all supplies

- Over temperature protection

# **Applications**

- IO-Link Master application in modular SPS

- Gateway applications

## **General Description**

This device comes with two independently operating IO-Link MASTER PHYs which make it a perfect fit for 2/4/8/16-port Master applications. Especially for multiport applications the integrated UARTs offer you high flexibility regarding scalability of Master ports and the choice of the  $\mu$ C used for the application. As the E981.12 allows the support of external MOSFETs for sensor supply, it enables cost-effective and power dissipation optimized system concepts.

The dual IO-Link Master is also available as SIP at RENE-SAS with embedded microcontroller for protocol handling.

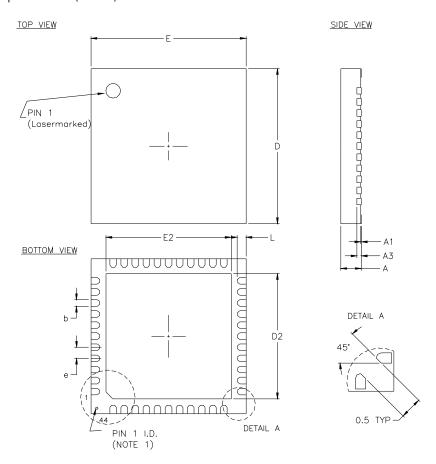

## **Ordering Information**

| Ordering No.: | Ambient Temp. Range | Package |

|---------------|---------------------|---------|

| E98112A39B    | -40°C to +105°C     | QFN44L7 |

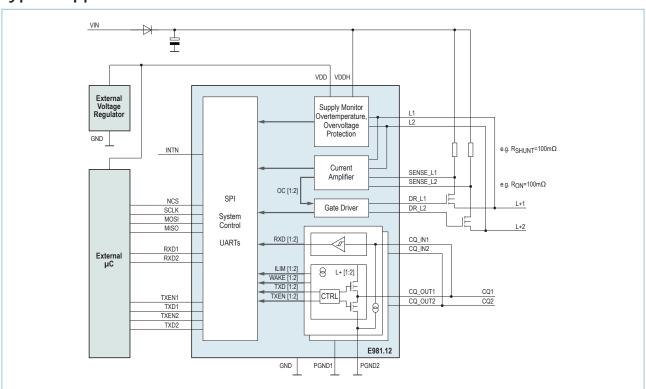

# **Typical Application Circuit**

$Elmos \ Semiconductor \ AG \ reserves \ the \ right \ to \ change \ the \ detail \ specifications \ as \ may \ be \ required \ to \ permit \ improvements \ in \ the \ design \ of \ its \ products$

Elmos Semiconductor AG Data Sheet QM-No.: 25DS0069E.02

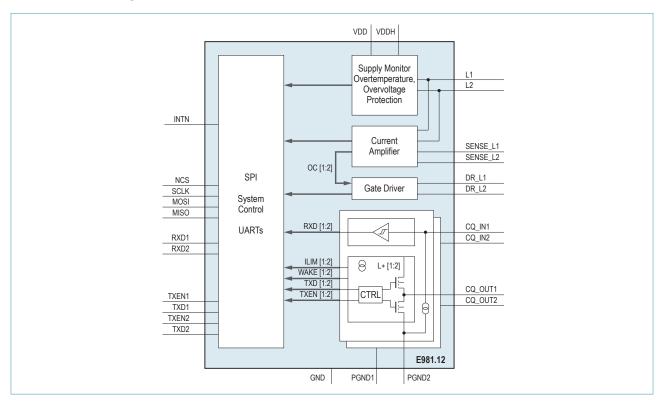

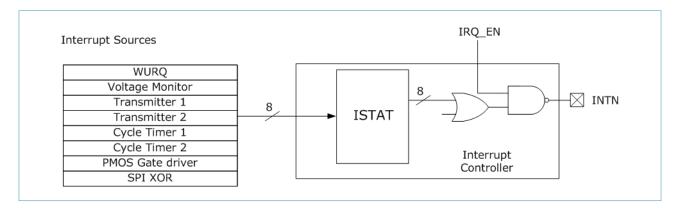

# **Functional Diagram**

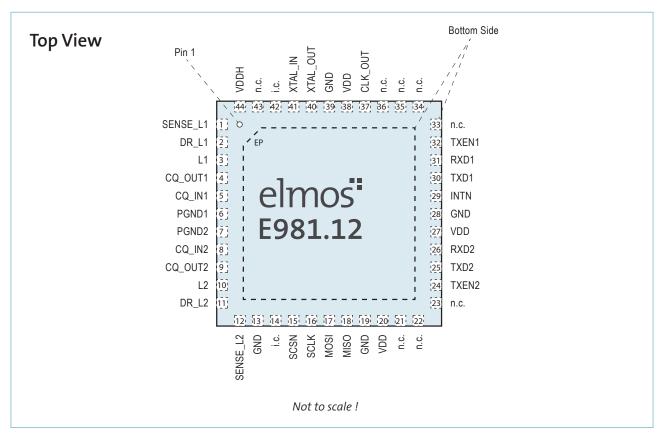

# **Pin Configuration**

# **Pin Description**

| Pin | Name     | Type 1) | Description                                                               |

|-----|----------|---------|---------------------------------------------------------------------------|

| 1   | SENSE_L1 | HV_A_I  | Supply current sense input channel 1                                      |

| 2   | DR_L1    | HV_A_O  | PMOS Gate control output channel 1                                        |

| 3   | L1       | HV_S    | Transceiver supply input channel 1                                        |

| 4   | CQ_OUT1  | HV_A_O  | Transmitter output channel 1                                              |

| 5   | CQ_IN1   | HV_A_I  | Receiver / general purpose input channel 1                                |

| 6   | PGND1    | HV_S    | Power ground channel 1                                                    |

| 7   | PGND 2   | HV_S    | Power ground channel 2                                                    |

| 8   | CQ_IN2   | HV_A_I  | Receiver / general purpose input channel 2                                |

| 9   | CQ_OUT2  | HV_A_O  | Transmitter output channel 2                                              |

| 10  | L2       | HV_S    | Transceiver supply input channel 2                                        |

| 11  | DR_L2    | HV_A_O  | PMOS Gate control output channel 2                                        |

| 12  | SENSE_L2 | HV_A_I  | Supply current sense input channel 2                                      |

| 13  | GND      | S       | System ground                                                             |

| 14  | i.c.     |         | Internally connected. For factory use only. Connect to GND in application |

| 15  | SCSN     | D_I     | SPI chip select input                                                     |

| 16  | SCLK     | D_I     | SPI serial clock input                                                    |

| 17  | MOSI     | D_I     | SPI master output slave input (data input)                                |

| 18  | MISO     | D_O     | SPI master input slave output (data output)                               |

| 19  | GND      | S       | System ground                                                             |

| 20  | VDD      | S       | 3.3V voltage supply                                                       |

| 21  | n.c.     |         | not connected                                                             |

| 22  | n.c.     |         | not connected                                                             |

| 23  | n.c.     |         | not connected                                                             |

| 24  | TXEN2    | D_I     | Transmitter enable channel 2                                              |

| 25  | TXD2     | D_I     | Transmitter input channel 2                                               |

| 26  | RXD2     | D_O     | Receiver output channel 2                                                 |

| 27  | VDD      | S       | 3.3V voltage supply                                                       |

| 28  | GND      | S       | System ground                                                             |

| 29  | INTN     | D_O     | Interrupt output (low active)                                             |

| 30  | TXD1     | D_I     | Transmitter input channel 1                                               |

| 31  | RXD1     | D_0     | Receiver output channel 1                                                 |

| 32  | TXEN1    | D_I     | Transmitter enable channel 1                                              |

| 33  | n.c.     |         | not connected                                                             |

| 34  | n.c.     |         | not connected                                                             |

| 35  | n.c.     |         | not connected                                                             |

| 36  | n.c.     |         | not connected                                                             |

| 37  | CLK_OUT  | D_O     | Clock output port                                                         |

| 38  | VDD      | S       | 3.3V voltage supply                                                       |

| 39  | GND      | S       | System ground                                                             |

1) A = Analog, D = Digital, S = Supply, I = Input, O = Output, B = Bidirectional, HV = High Voltage

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

Elmos Semiconductor AG

Data Sheet

| Pin | Name     | Type 1) | Description                                                                |

|-----|----------|---------|----------------------------------------------------------------------------|

| 40  | XTAL_OUT | D_O     | External quartz                                                            |

| 41  | XTAL_IN  | D_I     | External quartz                                                            |

| 42  | i.c.     |         | Internally connected. For factory use only. To be left open in application |

| 43  | n.c.     |         | not connected                                                              |

| 44  | VDDH     | S       | High-voltage supply input                                                  |

| -   | EP       | S       | Exposed Die Pad                                                            |

<sup>1)</sup> A = Analog, D = Digital, S = Supply, I = Input, O = Output, B = Bidirectional, HV = High Voltage

# 1 Absolute Maximum Ratings

Stresses beyond these absolute maximum ratings listed below may cause permanent damage to the device. These are stress ratings only; operation of the device at these or any other conditions beyond those listed in the operational sections of this document is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. All voltages with respect to ground. Currents flowing into terminals are positive, those drawn out of a terminal are negative. PGND1, PGND2, GND1 and the package exposed pad must be soldered to the same GND potential.

| Description                                                                                    | Condition                                           | Symbol                    | Min  | Max                   | Unit |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------|------|-----------------------|------|

| DC voltage at pin VDDH                                                                         | continuous                                          | V <sub>SUP</sub>          | -0.3 | 40                    | V    |

| Transient voltage at pin VDDH (ESD, burst, surge)                                              | t < 500μs                                           | V <sub>SUP,trans</sub>    | -0.3 | 60                    | V    |

| DC input voltage at pins CQ_INx                                                                | continuous                                          | V <sub>CO_IN_dc</sub>     | -5   | 40                    | V    |

| DC input voltage at pins CQ_OUTx                                                               | continuous                                          | V <sub>CO_OUT_dc</sub>    | -0.3 | V <sub>DDH</sub> +0.3 | V    |

| DC voltage at pins Lx, SENSE_Lx, DR_Lx                                                         | continuous                                          | V <sub>L_CTRL</sub>       | -0.3 | V+0.3                 | V    |

| Synchronous transient voltage at pins CQ_OUTx and Lx                                           | t < 500μs                                           | V <sub>L_CTRL,trans</sub> | -0.3 | 60                    | V    |

| Continuous DC voltage at VDD                                                                   | continuous                                          | V <sub>VDD</sub>          | -0.3 | 3.6                   | V    |

| Voltage range for digital interface pins<br>RXDx, TXDx, TXENx, INTN, MISO, MOSI,<br>SCLK, SCSN | continuous                                          | V <sub>IF</sub>           | -0.3 | V <sub>DD</sub> +0.3  | V    |

| Maximum IO current at each pin, if not specified otherwise                                     |                                                     | I <sub>IO_LUP</sub>       | -10  | 10                    | mA   |

| Junction temperature                                                                           | continuous                                          | T <sub>J</sub>            |      | 150                   | °C   |

| Storage temperature                                                                            |                                                     | T <sub>STG</sub>          | -40  | 150                   | °C   |

| ESD protection at pins CQ_OUTx and CQ_INx                                                      | AEC-Q100-002<br>R=1.5kΩ, C=100pF<br>chip level test | V <sub>CQ_ESD_HBM</sub>   | 6    |                       | kV   |

| ESD protection at pin VDDH                                                                     | AEC-Q100-002<br>R=1.5kΩ, C=100pF<br>chip level test | V <sub>VDDH_ESD_</sub>    | 6    |                       | kV   |

| ESD protection at pins CQ_OUTx and CQ_INx                                                      | IEC 61000-4-2<br>R=330Ω, C=150pF                    | V <sub>CQ_ESD</sub>       | 6    |                       | kV   |

| ESD protection at pin VDDH                                                                     | IEC 61000-4-2<br>R=330Ω, C=150pF                    | V <sub>VDDH_ESD</sub>     | 6    |                       | kV   |

| ESD protection at all other pins                                                               | AEC-Q100-002<br>R=1.5kΩ, C=100pF<br>chip level test | $V_{pin\_ESD\_HBM}$       | 2    |                       | kV   |

$Elmos \ Semiconductor \ AG \ reserves \ the \ right \ to \ change \ the \ detail \ specifications \ as \ may \ be \ required \ to \ permit \ improvements \ in \ the \ design \ of \ its \ products.$

PRODUCTION DATA - NOV 27, 2013

# **2 Recommended Operating Conditions**

Parameters are guaranteed within the range of recommended operating conditions unless otherwise specified. All voltages are referred to ground (0V).

Currents flowing into the circuit have positive values.

The first electrical potential connected to the IC must be GND.

| Description                                         | Condition    | Symbol            | Min  | Тур | Max  | Unit |

|-----------------------------------------------------|--------------|-------------------|------|-----|------|------|

| Supply voltage at pin VDDH                          | SIO Mode     | V <sub>VDDH</sub> | 8    | 24  | 32   | ٧    |

| Supply voltage at pin VDDH for IOLINK communication | IO_Link Mode | V <sub>VDDH</sub> | 18   | 24  | 32   | ٧    |

| Supply voltage at pin VDD                           |              | V <sub>VDD</sub>  | 3.15 | 3.3 | 3.45 | V    |

| Operating ambient temperature range                 |              | T <sub>OP</sub>   | -40  |     | +105 | °C   |

## **3 Thermal Characteristics**

| Description                                               | Condition             | Symbol                    | Min | Тур | Max | Unit |

|-----------------------------------------------------------|-----------------------|---------------------------|-----|-----|-----|------|

| Thermal resistance junction to case                       | QFN44L7 <sup>1)</sup> | R <sub>TH_JC_7_ABS</sub>  |     | 5   |     | K/W  |

| Thermal resistance junction to ambient, high conductivity | QFN44L7 <sup>1)</sup> | R <sub>TH_JAH_7_ABS</sub> |     | 25  |     | K/W  |

<sup>1)</sup> Values are based on multilayer PCB according to JEDEC JESD-51-5.

#### 4 Electrical Characteristics

$(V_{VDDH}$  = +8V to +32V for SIO mode,  $V_{VDD}$  =3.15V to 3.45V,  $T_{AMB}$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $V_{VDDH}$  = +24V,  $V_{VDD}$  = +3.3V and  $T_{AMB}$  = +25°C. Positive currents flow into the device pins.)

| Description                                                                                      | Condition | Symbol                 | Min  | Тур | Max  | Unit |

|--------------------------------------------------------------------------------------------------|-----------|------------------------|------|-----|------|------|

| Power Supplies                                                                                   |           |                        |      |     |      |      |

| Supply voltage at pin VDDH for SIO mode                                                          | SIO mode  | V <sub>supSIO</sub>    | 8    | 24  | 32   | V    |

| Supply voltage at pin VDDH for IOLINK communication                                              |           | V <sub>suplOLINK</sub> | 18   | 24  | 32   | V    |

| Supply voltage at pin VDD                                                                        |           | V <sub>DD</sub>        | 3.15 | 3.3 | 3.45 | V    |

| Supply current at pin VDDH                                                                       |           | I <sub>DDH</sub>       |      | 1.0 | 2.0  | mA   |

| Supply current at pin VDD                                                                        |           | I <sub>DD</sub>        |      | 3.5 | 5.5  | mA   |

| Supply Monitors                                                                                  |           |                        |      |     |      |      |

| Under voltage threshold VDDH, L1,<br>L2 to switch-off the transmitters<br>or the external P-FETs |           | UV <sub>OFF</sub>      | 6.5  | 7   | 7.5  | V    |

| Under voltage monitor threshold at L1 and L2                                                     |           | UV <sub>IOLINK</sub>   | 16   | 17  | 18   | V    |

| Debounce time for under voltage detection at VDDH, L1 and L2                                     |           | t <sub>deb_UV</sub>    | 50   |     | 250  | μs   |

| VDD undervoltage threshold                                                                       |           | V <sub>DDUV</sub>      | 2.7  |     | 3    | V    |

| Hysteresis of VDDUV threshold                                                                    |           | V <sub>DDUVhyst</sub>  |      | 0.1 |      | V    |

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

Elmos Semiconductor AG Data Sheet QM-No.: 25DS0069E.02

$(V_{VDDH}$  = +8V to +32V for SIO mode,  $V_{VDD}$  =3.15V to 3.45V,  $T_{AMB}$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $V_{VDDH}$  = +24V,  $V_{VDD}$  = +3.3V and  $T_{AMB}$  = +25°C. Positive currents flow into the device pins.)

| Description                                                                     | Condition                                                                                   | Symbol                                                           | Min   | Тур  | Max  | Unit |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|------|------|------|

| Debounce time for VDDUV                                                         |                                                                                             | t <sub>deb_VDDUV</sub>                                           | 50    |      | 250  | μs   |

| Hysteresis of VDDPOR signal                                                     |                                                                                             | V <sub>DDPORhyst</sub>                                           |       | 0.1  |      | V    |

| VDDPOR threshold                                                                |                                                                                             | V <sub>DDPOR</sub>                                               | 2.2   |      | 2.7  | V    |

| voltage difference between VD-<br>DUV threshold and POR                         |                                                                                             | $\begin{pmatrix} \Delta(V_{DDUV^{-}} \\ V_{DDPOR} \end{pmatrix}$ |       | 0.3  |      | V    |

| IO-Link Transmitter                                                             |                                                                                             |                                                                  |       |      |      |      |

| Driver ON resistance                                                            | V(Lx) >14V<br>tested at  lout  =<br>200mA                                                   | R <sub>on</sub>                                                  |       | 1    | 2    | Ω    |

| Driver ON resistance at low supply voltage                                      | 8V < V(Lx) < 14V<br>tested at  lout  =<br>200mA                                             | R <sub>ON_low_supply</sub>                                       |       | 2    | 3    | Ω    |

| Over current limitation threshold for CQ_OUT=Low                                |                                                                                             | I <sub>LIM_L</sub>                                               | 550   | 750  | 1200 | mA   |

| Over current limitation threshold for CQ_OUT=High                               |                                                                                             | I <sub>LIM_H</sub>                                               | -1200 | -750 | -550 | mA   |

| first (default) configurable over current limitation threshold for CQ_OUT=Low   |                                                                                             | I <sub>THL_OFF_CONF1</sub>                                       | 300   | 500  | 800  | mA   |

| second configurable over current limitation threshold for CQ_OUT=Low            |                                                                                             | I <sub>THL_OFF_CONF2</sub>                                       | 150   | 250  | 425  | mA   |

| third configurable over current limitation threshold for CQ=Low                 |                                                                                             | I <sub>THL_OFF_CONF3</sub>                                       | 75    | 150  | 250  | mA   |

| fourth configurable over current limitation threshold for CQ_<br>OUT=Low        |                                                                                             | I <sub>THL_OFF_CONF4</sub>                                       | 50    | 100  | 175  | mA   |

| first (default) configurable over current limitation threshold for CQ_OUT= High |                                                                                             | I <sub>THH_OFF_CONF1</sub>                                       | -800  | -500 | -300 | mA   |

| second configurable over current limitation threshold for CQ_<br>OUT=High       |                                                                                             | I <sub>THH_OFF_CONF2</sub>                                       | -425  | -250 | -150 | mA   |

| third configurable over current limitation threshold for CQ_OUT=High            |                                                                                             | I <sub>THH_OFF_CONF3</sub>                                       | -250  | -150 | -75  | mA   |

| fourth configurable over cur-<br>rent limitation threshold for CQ_<br>OUT=High  |                                                                                             | I <sub>THH_OFF_CONF4</sub>                                       | -175  | -100 | -50  | mA   |

| Output voltage rise time in fast<br>mode<br>(bit FAST="1" in CH_CFG             | $C_{load}$ = 1-5nF,<br>$R_{load}$ =20k $\Omega$ to GND,<br>C/Q H/L transition,<br>10% - 90% | t <sub>rhspeed</sub>                                             | 100   |      | 896  | ns   |

| Output voltage rise time in slow<br>mode<br>(bit FAST="0" in CH_CFG)            | $C_{load}$ = 1-5nF,<br>$R_{load}$ =20k $\Omega$ to GND,<br>C/Q H/L transition,<br>10% - 90% | t <sub>rlspeed</sub>                                             | 0.8   |      | 5.2  | μs   |

$(V_{VDDH}$  = +8V to +32V for SIO mode,  $V_{VDD}$  =3.15V to 3.45V,  $T_{AMB}$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $V_{VDDH}$  = +24V,  $V_{VDD}$  = +3.3V and  $T_{AMB}$  = +25°C. Positive currents flow into the device pins.)

| Description                                                          | Condition                                                                                   | Symbol                   | Min   | Тур                         | Max   | Unit |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------|-------|-----------------------------|-------|------|

| Output voltage fall time in fast<br>mode<br>(bit FAST="1" in CH_CFG  | $C_{load}$ = 1-5nF,<br>$R_{load}$ =20k $\Omega$ to GND,<br>C/Q L/H transition,<br>10% - 90% | t <sub>fhspeed</sub>     | 100   |                             | 896   | ns   |

| Output voltage fall time in slow<br>mode<br>(bit FAST="0" in CH_CFG) | $C_{load}$ = 1-5nF,<br>$R_{load}$ =20k $\Omega$ to GND,<br>C/Q L/H transition,<br>10% - 90% | t <sub>flspeed</sub>     | 0.8   |                             | 5.2   | μs   |

| Transmit propagation delay from TXD to CQ_OUT                        | V(Lx)= 24V<br>bit FAST="0                                                                   | t <sub>pd_Ispeed</sub>   |       | 2.5 1)                      |       | μs   |

| Transmit propagation delay from TXD to CQ_OUT                        | V(Lx)= 24V<br>bit FAST="1"                                                                  | t <sub>pd_hspeed</sub>   |       | 1.2 1)                      |       | μs   |

| Duty Cycle 1 <sup>3)</sup>                                           | VTHHs <sub>IOLINK</sub> (max),<br>VTHLs (max) <sup>2)</sup>                                 | D <sub>min,1</sub>       | 0.386 |                             |       |      |

| Duty Cycle 2 <sup>3)</sup>                                           | VTHHs <sub>IOLINK</sub> (min),<br>VTHLs(min) <sup>2)</sup>                                  | D <sub>max,2</sub>       |       |                             | 0.591 |      |

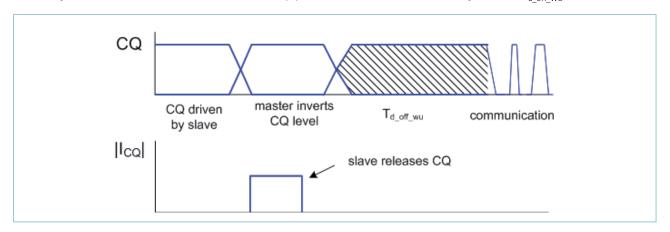

| Wake-up pulse duration                                               | Wake-up request                                                                             | t <sub>wu</sub>          | 75    | 80                          | 85    | μs   |

| OFF time after wake-up pulse                                         | Wake-up procedure                                                                           | t <sub>dOFF_WU</sub>     |       | 350                         | 400   | μs   |

| ON time with overload                                                |                                                                                             | t <sub>dON_OL</sub>      | 85    | 100                         | 115   | μs   |

| First OFF time after first ON or wake-up pulse                       |                                                                                             | t <sub>dOFF1_OL</sub>    |       | 200<br>*t <sub>dON_OL</sub> |       | μs   |

| OFF time after overload detection, default value                     | TDOFF1,2= "00"                                                                              | t <sub>dOFF2_OL_</sub>   |       | 200<br>*t <sub>dON_OL</sub> |       | μs   |

| OFF time after overload detection, configured                        | TDOFF1,2= "01"                                                                              | t <sub>dOFF2_OL_</sub>   |       | 120<br>*t <sub>don_ol</sub> |       | μs   |

| OFF time after overload detection, configured                        | TDOFF1,2= "10"                                                                              | t <sub>dOFF2_OL_</sub>   |       | 64<br>*t <sub>dON_OL</sub>  |       | μs   |

| OFF time after overload detection, configured                        | TDOFF1,2= "11"                                                                              | t <sub>dOFF2_OL_</sub>   |       | 320<br>*t <sub>dON OL</sub> |       | μs   |

| Debounce time for over current detection                             |                                                                                             | t <sub>debOL</sub>       |       | 15                          |       | μs   |

| IO-Link Receiver                                                     |                                                                                             |                          |       |                             |       |      |

| Input threshold high for IEC61131-2 type 2                           | 18V < V <sub>Lx</sub> < 30V                                                                 | V <sub>THHsIEC2</sub>    | 9     | 10                          | 11    | V    |

| Input threshold high for IOLINK and IEC61131-2 type 1                | 18V < V <sub>Lx</sub> < 30V                                                                 | V <sub>THHSIOLINK</sub>  | 11    | 12                          | 13    | V    |

| Input threshold low                                                  | 18V < V <sub>Lx</sub> < 30V                                                                 | V <sub>THLs</sub>        | 8     | 9                           | 10    | V    |

| Input threshold hysteresis for IEC61131-2 type 2                     | 18V < V <sub>Lx</sub> < 30V                                                                 | V <sub>HYSsIEC2</sub>    | 0.5   | 1                           | 1.5   | V    |

| Input threshold hysteresis for IOLINK and IEC61131-2 type 1          | 18V < V <sub>Lx</sub> < 30V                                                                 | V <sub>HYSs_IOLINK</sub> | 2     | 3                           | 4     | V    |

| Receiver input debounce filter time                                  | t <sub>BIT</sub> depends on BD1/BD0                                                         | t <sub>CQ_deb</sub>      |       | 1/9*t <sub>BIT</sub>        |       | ns   |

<sup>1)</sup> not production tested

<sup>2)</sup> tested at  $C_{Load}$  = 1-5nF;  $R_{Load,min}$  =20kOhm to GND;  $V(Lx)/R_{Load,max}$  = 15 mA

<sup>3)</sup>  $D = t_{CQH}/2*T_{Bit}$

$(V_{VDDH}$  = +8V to +32V for SIO mode,  $V_{VDD}$  =3.15V to 3.45V,  $T_{AMB}$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $V_{VDDH}$  = +24V,  $V_{VDD}$  = +3.3V and  $T_{AMB}$  = +25°C. Positive currents flow into the device pins.)

| Description                                                        | Condition                                       | Symbol                  | Min                  | Тур               | Max                  | Unit   |

|--------------------------------------------------------------------|-------------------------------------------------|-------------------------|----------------------|-------------------|----------------------|--------|

| Input pull down current 1 for input IEC61131-2 type 2              | PD-Source enabled V <sub>co_INx</sub> > 5 V     | <br>  pdown1            | 6                    | 8                 | 12                   | mA     |

| Input pull down current 2 for input IEC61131-2 type 2              | PD-Source enabled V <sub>co INx</sub> > 5 V     | l <sub>pdown2</sub>     | 2                    | 4                 | 7                    | mA     |

| UART                                                               |                                                 |                         |                      |                   |                      |        |

| UART master tolerance                                              |                                                 | UART                    |                      |                   | 0.1                  | %      |

| UART receiver detects IDLE after N <sub>BIT,IDLE</sub> * bit times | at least one byte<br>UART reception be-<br>fore | N <sub>BIT,IDLE</sub>   |                      | 5                 |                      |        |

| TRX buffer memory size                                             |                                                 | n <sub>MEM</sub>        |                      | 127               |                      | byte   |

| IO-Link Cycle Timer                                                |                                                 |                         |                      |                   |                      |        |

| IO-Link Cycle Time                                                 | UART of channel ena-<br>bled                    | T <sub>CYC</sub>        | 0.5                  |                   | 348                  | ms     |

| Granularity of TCYC                                                | depending on<br>PRSC[1:0]                       | T <sub>CYC_STEP</sub>   | 0.5                  |                   | 4                    | ms     |

| Low pulse @ pin SCSN for synchro-<br>nization event                | no SCK pulse                                    | t <sub>IOSYNC</sub>     | 10                   |                   |                      | μs     |

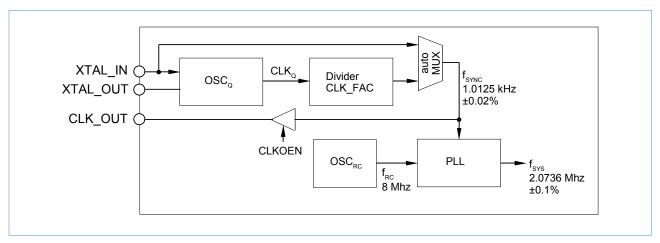

| Oscillator                                                         |                                                 |                         |                      |                   |                      |        |

| Internal oscillator frequency                                      |                                                 | f <sub>OSC,INT</sub>    | -5%                  | 8                 | +5%                  | MHz    |

| Oscillator frequency accuracy with external quarz                  | external chrystal<br>50ppm                      | f <sub>osc,Quartz</sub> | -0.01%               |                   | +0.01%               | MHz    |

| PLL                                                                |                                                 |                         |                      |                   |                      |        |

| Internal synchronization clock                                     | Quarz enabled or XTAL_IN insertion              | f                       |                      | 1.0125            |                      | kHz    |

| Synchronization clock frequency applied at pin XTAL_IN             | Quarz disabled,<br>XTAL_OUT n.c.                | f <sub>XTAL,sync</sub>  | -0.02%               | f <sub>sync</sub> | +0.02%               |        |

| Frequency of CLK_OUT port, C <sub>sync</sub>                       | Output enabled,<br>Quarz enabled                | f <sub>CLK_OUT</sub>    | -0.02%               | 1.0125            | +0.02%               | kHz    |

| Temperature Monitor                                                |                                                 |                         |                      |                   |                      |        |

| Shut off over temperature threshold                                |                                                 | Тот                     | 150                  |                   |                      | deg. C |

| Electrical hysteresis of over-tem-<br>perature shut-off            |                                                 | T <sub>OT_hyst</sub>    |                      | 12                |                      | deg. C |

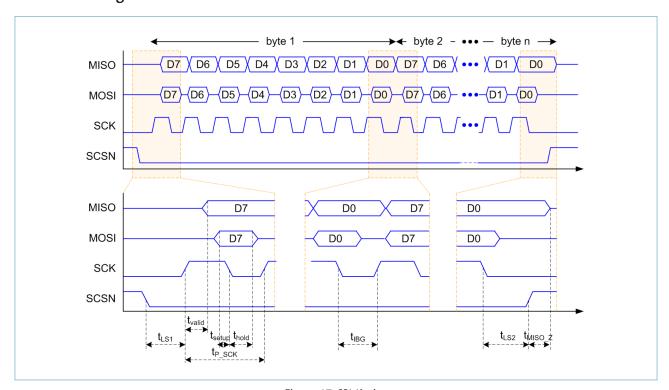

| Host Interface                                                     |                                                 |                         |                      |                   |                      |        |

| High level input voltage                                           |                                                 | V <sub>IH</sub>         | 0.7*V <sub>VDD</sub> |                   |                      | V      |

| Low level input voltage                                            |                                                 | V <sub>IL</sub>         |                      |                   | 0.3*V <sub>VDD</sub> | V      |

| High level output voltage                                          | Iload=2mA                                       | V <sub>OH</sub>         | 0.8*V <sub>VDD</sub> |                   |                      | V      |

| Low level output voltage                                           | Iload=-2mA                                      | V <sub>OL</sub>         |                      |                   | 0.2*V <sub>VDD</sub> | V      |

| Input pull-down current                                            | Vpin=V <sub>VDD</sub>                           | I <sub>pd</sub>         | 10                   |                   | 80                   | μΑ     |

| Input pull-up current                                              | Vpin=0V                                         | I <sub>pu</sub>         | -80                  |                   | -10                  | μΑ     |

| Time between rising edge of SCSN and high impedance at MISO        |                                                 | t <sub>MISO_Z</sub>     |                      |                   | 100                  | ns     |

| MISO data valid time                                               | C <sub>MISO</sub> < 20 pF                       | t <sub>valid</sub>      |                      |                   | 35                   | ns     |

| SCK pulsewidth                                                     |                                                 | t <sub>P_SCK</sub>      | 125                  |                   |                      | ns     |

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

Elmos Semiconductor AG Data Sheet QM-No.: 25DS0069E.02

$(V_{VDDH}$  = +8V to +32V for SIO mode,  $V_{VDD}$  =3.15V to 3.45V,  $T_{AMB}$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $V_{VDDH}$  = +24V,  $V_{VDD}$  = +3.3V and  $T_{AMB}$  = +25°C. Positive currents flow into the device pins.)

| Description                                                                          | Condition                                                                             | Symbol                  | Min                       | Тур                       | Max                  | Unit |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------|---------------------------|---------------------------|----------------------|------|

| Time between falling SCSN edge and first rising SCK edge                             |                                                                                       | t <sub>LS1</sub>        | 50                        |                           | 2000                 | ns   |

| Time between last falling SCK edge and rising SCSN edge                              |                                                                                       | t <sub>LS2</sub>        | 50                        |                           |                      | ns   |

| Inter byte gap relevant for two<br>byte access between address and<br>data byte only |                                                                                       | t <sub>IBG</sub>        | 550                       |                           |                      | ns   |

| MOSI data setup time                                                                 |                                                                                       | t <sub>setup</sub>      | 30                        |                           |                      | ns   |

| MOSI data hold time                                                                  |                                                                                       | t <sub>hold</sub>       | 20                        |                           |                      | ns   |

| Number of data bytes during burst access to TRX buffers                              |                                                                                       | N <sub>SPI,burst</sub>  | 1                         |                           | 127                  |      |

| IO-Link Supply Control                                                               |                                                                                       |                         |                           |                           | ·                    |      |

| Shutdown delay 1 including delay of current regulation                               | PDR_CFG1 [7:6]=00<br>Power FET dependent                                              | t <sub>d_OFF1</sub>     |                           | 1                         |                      | ms   |

| Shutdown delay 2 including delay of current regulation                               | PDR_CFG1 [7:6]=01<br>Power FET dependent                                              | t <sub>d_OFF2</sub>     |                           | 4                         |                      | ms   |

| Shutdown delay 3 including delay of current regulation                               | PDR_CFG1 [7:6]=10<br>Power FET dependent                                              | t <sub>d_OFF3</sub>     |                           | 10                        |                      | ms   |

| Shutdown duration 1                                                                  | PDR_CFG1 [5:4]=00                                                                     | t <sub>OFF1</sub>       |                           | 5                         |                      | ms   |

| Shutdown duration 2                                                                  | PDR_CFG1 [5:4]=01                                                                     | t <sub>OFF2</sub>       |                           | 20                        |                      | ms   |

| Shutdown duration 3                                                                  | PDR_CFG1 [5:4]=10                                                                     | t <sub>OFF3</sub>       |                           | 50                        |                      | ms   |

| Over current detection threshold at shunt resistor                                   |                                                                                       | V <sub>IN_OCCOMP</sub>  | 60                        | 90                        | 120                  | mV   |

| Voltage drop across shunt in over current limitation state                           |                                                                                       | V <sub>IN_OC</sub>      | 70                        | 100                       | 130                  | mV   |

| Over current debounce time                                                           |                                                                                       | t <sub>deb_OCCOMP</sub> |                           | 8                         |                      | μs   |

| Input current at pin SENSE_Lx                                                        | V <sub>SENSE_Lx</sub> =V <sub>VDDH</sub>                                              | I <sub>SENSE</sub>      | 6                         | 10                        | 20                   | μΑ   |

| Pull up resistance at Pins DR_L1 and DR_L2 in OFF state                              | $V_{VDDH} - V_{DR_Lx} < 0.8V$                                                         | R <sub>PU_OFFSW</sub>   |                           | 300                       | 500                  | Ω    |

| Output voltage at Pins DR_L1 and DR_L2 to switch external PMOS ON                    | $I_{DR_Lx} = 100 \mu A$                                                               | V <sub>GATE_min</sub>   | V <sub>VDDH</sub><br>-15  | V <sub>VDDH</sub><br>-12  | V <sub>VDDH</sub> -5 | V    |

| Output voltage at Pins DR_L1 and DR_L2 to switch external PMOS OFF                   | $I_{DR_{Lx}} = -100 \mu A$                                                            | V <sub>GATE_max</sub>   | V <sub>VDDH</sub><br>-0.4 | V <sub>VDDH</sub><br>-0.1 | V <sub>VDDH</sub>    | V    |

| Maximum switch-off current for gate of external PMOS                                 | PMOS active<br>V <sub>DR_L</sub> =V <sub>VDDH</sub> - 4V<br>V <sub>shunt</sub> =300mV | I <sub>max_OFF</sub>    | -2                        | -3.8                      | -7                   | mA   |

| Switch-on gate current for gate of external PMOS                                     | PMOS active<br>V <sub>DR_</sub> =V <sub>VDDH</sub> - 4V<br>V <sub>shunt</sub> =55mV   | I <sub>min_NORM</sub>   | 0.5                       | 1                         | 3.5                  | mA   |

| Transient response time OFF->ON                                                      | PMOS active<br>C <sub>DR_L</sub> =0.8nF                                               | t <sub>pd_ON</sub>      |                           | 10                        |                      | μs   |

| Transient response time<br>ON->OFF                                                   | PMOS active<br>C <sub>DR_L</sub> =0.8nF                                               | t <sub>pd_OFF</sub>     |                           | 10                        |                      | μs   |

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

Elmos Semiconductor AG Data Sheet QM-No.: 25DS0069E.02

## **5 Functional Description**

#### 5.1 Power Supplies

The device has got four supply input pins:

VDDH - 24V supply

L1, L2 – 24V supply for the transceivers VDD – 3.3V supply for the digital blocks

VDDH is the general high-voltage supply pin. It supplies an internal low-voltage regulator for safe power up, internal references and the voltage monitors.

Each of the transmitter supply pins L1 and L2 supplies one of the two internal transmitters. This supply can be controlled by external PMOS transis-

tors. The IC provides the gate voltage for these external transistors and a current monitor to be able to limit the maximum current. If no external current limitated switches are needed the pins L1 and L2 has to be connected to the VDDH supply.

Pin VDD has to be supplied by an external voltage supply with nominal 3.3V. VDD supplies the host interface, the logic block and various other internal blocks. The logic block is set to its initial ("reset") state by a power-on-reset signal, delivered by the VDD monitor.

## 5.2 Supply Monitor

The supply monitor provides status information of the supply voltages VDD, VDDH, L1 and L2 in SPI register VMON STAT. For each flag an interrupt enable bit (IE)

can be configured in register VMON IE. Read access to register VMON STAT will clear the interrupts.

### 5.3 VDDH, L1, L2 Monitor

If the supply voltage at L1 or L2 falls below the  $UV_{IOLINK}$  threshold this condition is set in the corresponding SPI register only and an interrupt is generated if configured. The transmitters keep active.

If the supply voltage at L1 or L2 falls below the  $UV_{\text{OFF}}$  threshold the transmitters are disabled.

If the VDDH supply voltage falls below the  ${\rm UV_{OFF}}$  threshold the external PMOS-FETs are switched-off.

#### 5.4 VDD Monitor

If the VDD supply voltage falls below the  $V_{\tiny DDUV}$  threshold a bit in the register VMON STAT is set. If VDD falls below  $V_{\tiny DDPOR}$  threshold a power-on-reset is generated.

## 5.5 Status and Control Registers

Table 1. Voltage Monitoring Register

| Register Name | Address | Description               |

|---------------|---------|---------------------------|

| VMON STAT     |         | CAN-ID [7:0]              |

| VMON IE       |         | CAN-ID [10:8] and CAN-IDE |

Table 2. VMON STAT

| VMON STAT (0x02) | MSB                                                                                                                           |   |   |   |      |      |        | LSB   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|---|---|---|------|------|--------|-------|

| Content          | -                                                                                                                             | - | - | - | L2UV | L1UV | VDDHUV | VDDUV |

| Reset Value      | 0                                                                                                                             | 0 | 0 | 0 | 1    | 1    | 1      | 1     |

| Access           | R                                                                                                                             | R | R | R | R    | R    | R      | R     |

| Bit Description  | L2UV: 1 = Under voltage at L2 L1UV: 1 = Under voltage at L1 VDDHUV: 1 = Under voltage at VDDH VDDUV: 1 = Under voltage at VDD |   |   |   |      |      |        |       |

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

Elmos Semiconductor AG Data Sheet OM-No.: 25DS0069E.02

Table 3. VMON IE

| VMON IE (0x03)  | MSB                                                                                                                           |   |   |   |      |      |        | LSB   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|---|---|---|------|------|--------|-------|

| Content         | -                                                                                                                             | - | - | - | L2IE | L1IE | VDDHIE | VDDIE |

| Reset Value     | 0                                                                                                                             | 0 | 0 | 0 | 0    | 0    | 0      | 0     |

| Access          | R                                                                                                                             | R | R | R | R/W  | R/W  | R/W    | R/W   |

| Bit Description | L2IE: 1 = Interrupt enable L2 L1IE: 1 = Interrupt enable L1 VDDHIE: 1 = Interrupt enable VDDH VDDIE: 1 = Interrupt enable VDD |   |   |   |      |      |        |       |

#### 5.6 IO-Link-Transceiver

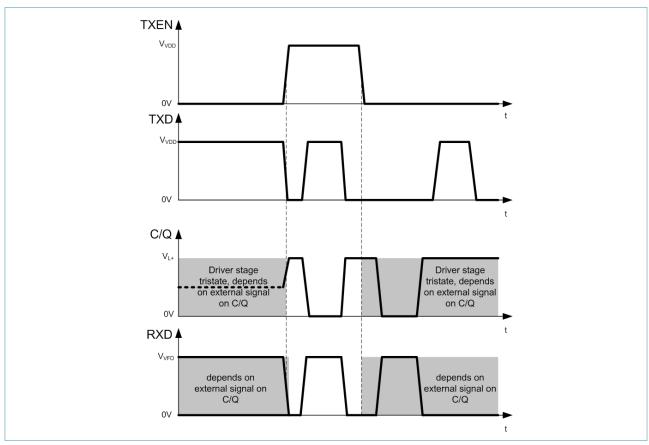

The device contains two channels with a high-voltage digital transmitter (output: CQ\_OUTx) and receiver (input: CQ\_INx). The transmitter and receiver are accessible by both — a parallel interface (TXD, TXEN, RXD) and by SPI in IO-Link or SIO mode. The digital pins are supplied by VDD voltage. The input thresholds and output levels are referenced to this voltage.

It can be used in the following ways:

- a) CQ\_OUTx is used as standard output (SIO) to drive ohmic loads, inductive loads or bulb lamps

- b) CQ\_INx is used as standard digital input type 2 according to IEC 61131-2

- c) CQ\_OUTx and CQ\_INx are used together as IO-LINK port for data transfer rates of 4.8 kBaud, 38.4 kBaud or 230.4 kBaud.

#### 5.7 IO-Link-Transmitter

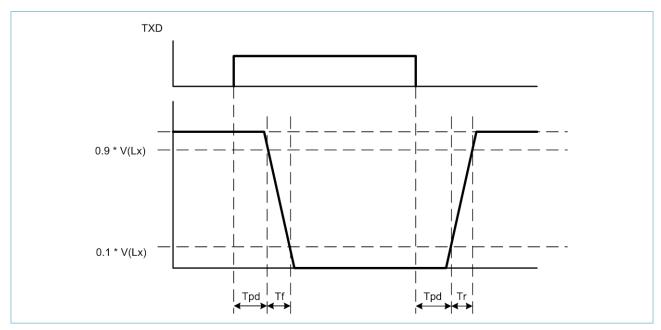

The push-pull transmitter is activated with high level on pin TXEN and drives the CQ\_OUT pin Low or High in accordance to the inverted logic level on pin TXD. A slope control limits EMC emission.

Figure 1. Transmitter polarity

$Elmos\ Semiconductor\ AG\ reserves\ the\ right\ to\ change\ the\ detail\ specifications\ as\ may\ be\ required\ to\ permit\ improvements\ in\ the\ design\ of\ its\ products.$

Elmos Semiconductor AG Data Sheet OM-No.: 25DS0069E.02

The transition times can be set for two different slope modes using register CH CFG. The transmitter is operable only if VDD, L+ and chip temperature are within their specified limits. Otherwise the transmitter is disabled.

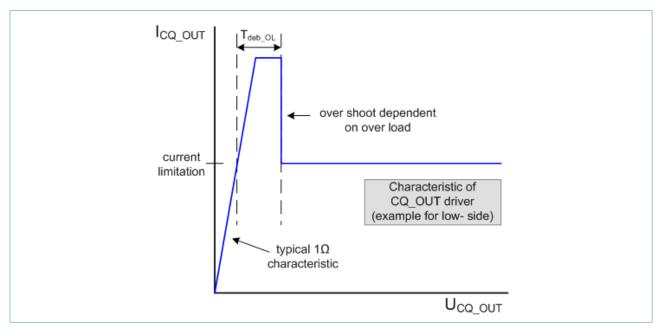

Figure 2. Transmitter characteristics

## 5.8 Transmitter Overload

In case of high power dissipation (e.g. due to short circuit of the driver) the chip temperature will increase. To protect the device, an internal over temperature sensor for each driver is implemented. In case of over temperature, the affected driver is disabled. The other output

driver can operate independently.

The transmitters are switched on after a the over temperature condition disappeared. The over temperature flag is set in CH STAT, to generate an interrupt use bit OTIE in TRX CFG

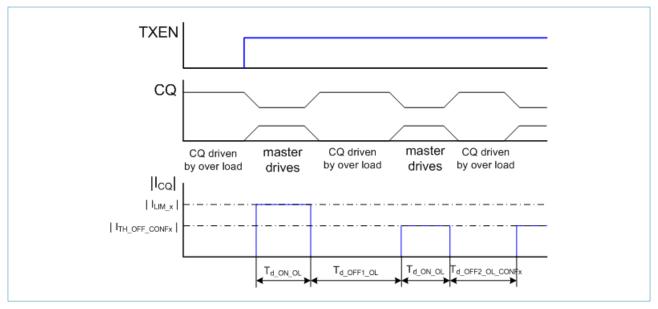

Figure 3. Transmitter characteristics at overload

PRODUCTION DATA - NOV 27, 2013

In case of an over current is detected directly after the transmitter is activated by setting the pin TXEN to high (or Bit STXEN=1), the output current is limited to an over current threshold ILIM\_x. The transmitter remains active for  $T_{doN_OI}$ . After this time the transmitter is disabled for  $T_{doPF1_OI}$ . After this first sequence a cyclic

overcurrent shutdown with a configurable current limitation ( $I_{THx\_OFF\_CONFx}$ ) and dutycycle ( $T_{don\_OL}$  /  $T_{doFF2\_OL\_CON-Fx}$ ) is implemented (see Fig. 4).

The configured dutycycle must not exceed the power dissipation limits of the device.

Figure 4. Transmitter over load sequence

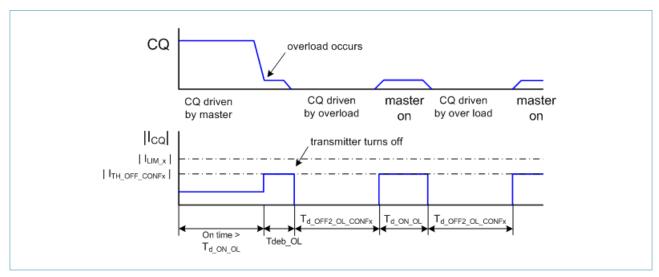

If an overload occurs while the transmitter was already active, it will turn off immediately after a debounce time  $T_{deb\ OL}$  for  $T_{d\ Off2\ OL}$  followed by the sequence described above using off times  $T_{d\ Off2\ OL}$  (see Fig. 5).

Figure 5. Over load while driver was already active

PRODUCTION DATA - NOV 27, 2013

#### 5.9 Transmitter Loads

In SIO mode the external load at CQ\_OUT may have resistive, capacitive or inductive characteristic or can be a bulb lamp. The loads can be connected between CQ\_OUTx and Lx or between CQ\_OUTx and PGNDx.

It is possible to switch the load in the following ways:

TXEN = constant High, switching with TXD

In this case CQ\_OUT is driven as push-pull output.

TXD = Low: high-side driver active TXD = High: low-side driver active In case of inductive loads the complementary driver acts as free-wheeling element.

#### TXD constant, switching with TXEN

In this case the high-side driver (if TXD = Low) or the low-side driver (if TXD = High) is used, so the load is switched either between "Active Low" and "Tristate" or between "Active High" and "Tristate".

In case of inductive loads inherent diodes of the drivers act as free-wheeling elements.

#### 5.10 IO-LINK Receiver

The receiver converts the voltage level at the CQ\_IN pin to an inverted logic receive signal which is available at pin RXD and the internal UART. The receiver filter times depends on the configured baudrate. The receiver functionality is available in the specified IO-Link supply range.

The receiver can be configured by bit IEC-2 in TRX CFG

either as standard IO-LINK / IEC61131-2 input or as standard IEC61131-1 input.

The input current source can be activated by bit PDEN in register <u>TRX CFG</u>. Setting bit PDAUTO the current source is disabled while the driver stage is active during SIO mode or communication mode (TXEN=1) in order to reduce power dissipation.

#### 5.11 SIO-Mode

Each C/Q channel can be used as an input or output, while the output can be configured to switch between high side, low side and HiZ.

SIO mode can be used by pins TXEN, TXD, RXD or by SPI

control. The mode can be configured by register CH\_CFG. If bit SIO is set to "1" the output control is done by SPI access to register TRX\_CFG bits STXD and STXEN. The receiver status can be read by register CH\_STAT bit RXD.

#### 5.12 Transceiver UART

The IO-Link Master IC has two integrated UART interfaces. The UART provides the media access and bit decoding / encoding and byte framing capabilities as well. UART timing accuracy of 0.1% depends on the oscillatior configuration described in chapter "Oscillator".

UART mode is activated by SPI register CH\_CFG bit UART. For UART mode the bit "SIO" has to be "0". The

UART baudrate has to be configured in register CH\_CFG independently for each channel.

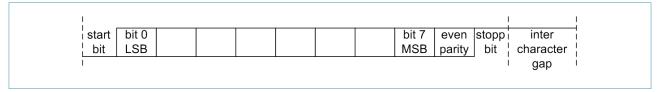

The UART byte frame consists of:

- one start bit (value "0")

- eight data bits (LSB first)

- an even parity bit and

- one stop bit (value "1").

Figure 6. Uart byte frame

Elmos Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products

Elmos Semiconductor AG Data Sheet OM-No.: 25DS0069E.02

# DUAL IO-LINK MASTER TRANSCEIVER WITH UARTS PRODUCTION DATA - NOV 27, 2013

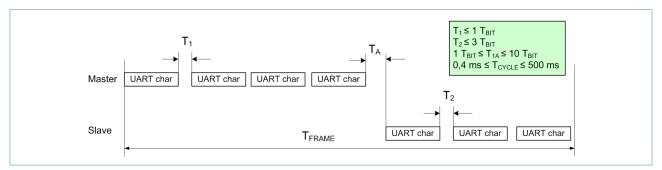

Transmission and receive is controlled by the integrated IO-Link cycle timer. For UART communication the internal cycle timer must be configured and enabled (see chapter "IO-Link cycle timer").

Each received byte is checked for correct parity and right framing (stop bit). In case of receive errors the corresponding error flags are set in register RX\_STAT and TIM STAT.

The E981.12 provides a 127 byte shared TRX buffer to store transmit and receive frames.

The number of bytes to be transmitted and received must be configured in register UART\_TXNUM and UART\_RXNUM. As soon as the configured number of bytes was successfully send and the response was received bit RDY in register TIM\_STAT is set. Optionally an interrupt can be enabled by RDYIE in register TIM IE.

Figure 7. IO-Link frame and cycle timing

If no further UART characters are observed for longer than T<sub>2</sub>, IDLE is detected. If the number of received characters differs from the value in UART\_RXNUM (as well as no reception at all was observed), the error flag

NUME will be set in register TIM\_STAT. Optionally an interrupt can be enabled by NUMIE in register TIM IE. The interrupt is cleared by read access to TIM STAT.

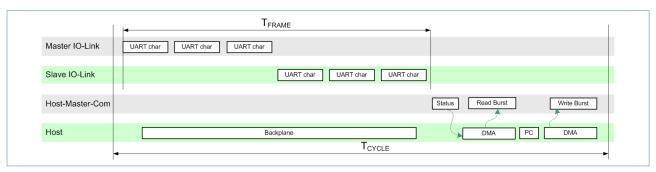

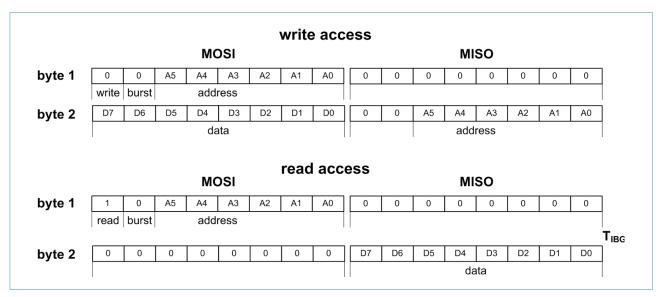

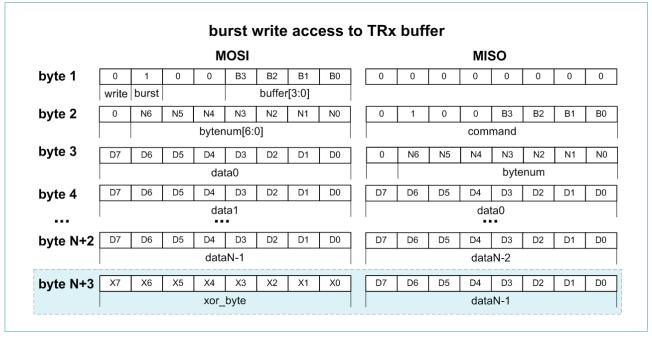

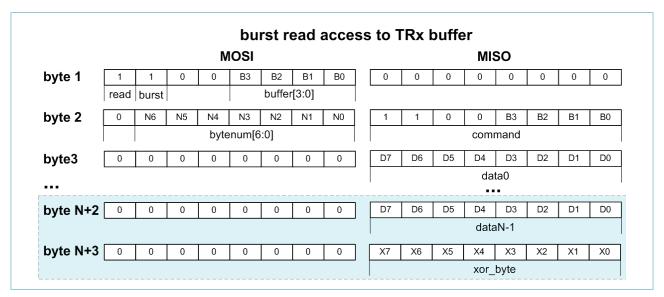

#### 5.13 Host - PHY Communication

The timing diagram in Fig. 8 shows the communication between host microcontroller and IO-Link Master TRX buffer within one cycle when using the internal UARTs.

Before writing or reading the corresponding buffer the UART hast to be enabled.

Figure 8. Host-PHY communication

After reading the response frame of the current cycle the host has to write the master frame for the next cycle to be transmitted before the current cycle has been ended. The buffered IO-Link master frame is sent by E981.12 starting with the next communication cycle (see chapter "IO-Link cycle timer"). The host microcontroller has to ensure to fill the TRX buffer with the master frame before the next cycle starts. If the TRX buffer access is not finished till the next cycle start (cy-

cle boundary violation), the transmission is started delayed.

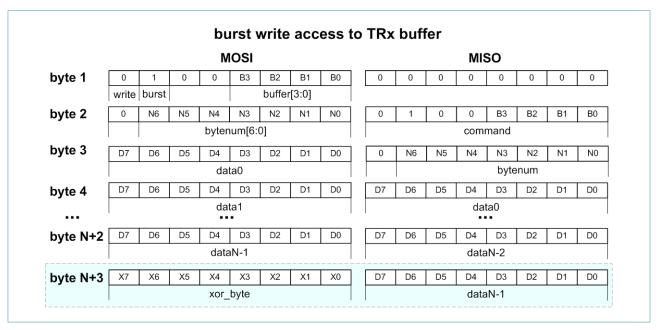

The TX bytes written to the TRX buffer by SPI are checked by XOR checksum. If the checksum fails the E981.12 does not transmit data in the next cycle.

The TRX buffer access is implemented as SPI burst access to reduce the SPI communication overhead (see Chapter 5.23 SPI Interface).

Figure 9. UART buffer burst write access

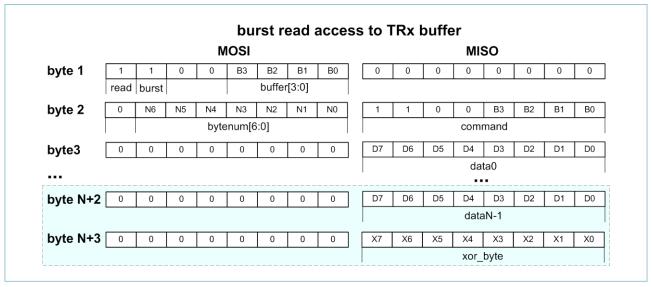

Figure 10. UART buffer burst read access

The buffer is selected by bits [B3:B0]. Channel 1 is selected by 0x5 (0101b). The buffer for channel 2 is selected by 0xA (1010b).

This buffer selection code must not be interpreted as starting address. The buffer read or write access always starts with data byte 0. It is not needed to read or write all 127 bytes. The application has to ensure that the buffer content matches to the number of bytes to be transmitted in register UART TXNUM.

For further information about SPI access see chapter 5.23 SPI Interface.

## **5.14 Channel Status and Configuration Registers**

Table 4. Transceiver Register

| Register Name | Address | Description                                               |  |  |  |

|---------------|---------|-----------------------------------------------------------|--|--|--|

| Channel 1     |         |                                                           |  |  |  |

| CH CFG        | 0x10    | Channel 1 configuration                                   |  |  |  |

| CH STAT       | 0x11    | Channel 1 status and error register                       |  |  |  |

| TRX CFG       | 0x12    | Transceiver config channel 1                              |  |  |  |

| TX OCCFG      | 0x13    | Transmitter over current configuration register channel 1 |  |  |  |

| UART TXNUM    | 0x14    | Number of Bytes for TX channel 1                          |  |  |  |

| UART RXNUM    | 0x15    | Number of Bytes for RX channel 1                          |  |  |  |

| RX STAT       | 0x1A    | Receiver status and error register channel 1              |  |  |  |

| Channel 2     |         | -                                                         |  |  |  |

| CH CFG        | 0x20    | Channel 2 configuration                                   |  |  |  |

| CH STAT       | 0x21    | Channel 2 status and error register                       |  |  |  |

| TRX CFG       | 0x22    | Transceiver config channel 2                              |  |  |  |

| TX OCCFG      | 0x23    | Transmitter over current configuration register channel 2 |  |  |  |

| UART TXNUM    | 0x24    | Number of Bytes for TX channel 2                          |  |  |  |

| UART RXNUM    | 0x25    | Number of Bytes for RX channel 2                          |  |  |  |

| RX STAT       | 0x2A    | Receiver status and error register channel 2              |  |  |  |

Table 5. Channel configuration

back to Table 4. Transceiver Register

| CH CFG<br>Channel 1 (0x10)<br>Channel 2 (0x20) | MSB         |                                                                                                |                                                                                                             |                                                          |                                    |                           |              | LSB    |

|------------------------------------------------|-------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|---------------------------|--------------|--------|

| Content                                        | -           | FAST                                                                                           | BD1                                                                                                         | BD0                                                      | -                                  | -                         | SIO          | UART   |

| Reset Value                                    | 0           | 0                                                                                              | 0                                                                                                           | 0                                                        | 0                                  | 0                         | 0            | 0      |

| Access                                         | R           | R/W                                                                                            | R/W                                                                                                         | R/W                                                      | R                                  | R                         | R/W          | R/W    |

| Bit Description                                | BD1 / BD0 : | 00 = 4.8 kE<br>01 = 38.4 k<br>10 = 230.4<br>11 = analo<br>1 = SIO N<br>0 = SIO w<br>1 = interr | opes '<br>selection ar<br>Baud<br>Baud<br>kBaud<br>g mode (TX<br>Node with r<br>vith TXEN, T<br>nal UART is | nd receiver f<br>KEN, TXD, R<br>egister valu<br>TXD, RXD | XD is used f<br>es<br>"SIO" is not | or commur<br>set to "1" ( | SIO has pric | ority) |

Table 6. Channel status and error register

back to Table 4. Transceiver Register

| CH STAT<br>Channel 1 (0x11)<br>Channel 2 (0x21) | MSB                                                                                                                                                                                     |   |   |   |      |      |   | LSB |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|------|------|---|-----|

| Content                                         | -                                                                                                                                                                                       | - | - | - | TXOC | TXOT | - | RXD |

| Reset Value                                     | 0                                                                                                                                                                                       | 0 | 0 | 0 | 0    | 0    | 0 | 0   |

| Access                                          | R                                                                                                                                                                                       | R | R | R | R    | R    | R | R   |

| Bit Description                                 | TXOC: 1 = Transmitter Overcurrent detected, cleared by read access TXOT: 1 = Transmitter Over temp. detected, cleared by read access RXD: 1 = Current value of filtered receiver status |   |   |   |      |      |   |     |

## **DUAL IO-LINK MASTER TRANSCEIVER WITH UARTS**

PRODUCTION DATA - NOV 27, 2013

Table 7. Transceiver config

## back to Table 4. Transceiver Register

| TRX CFG<br>Channel 1 (0x12)<br>Channel 2 (0x22) | MSB                                                                                                                    |                                                                                                         |                                                                                                                                                     |                                                                                                                            |                                                                                             |                          |      | LSB   |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------|------|-------|

| Content                                         | IEC-2                                                                                                                  | IPD                                                                                                     | PDAUTO                                                                                                                                              | PDEN                                                                                                                       | OCIE                                                                                        | OTIE                     | STXD | STXEN |

| Reset Value                                     | 0                                                                                                                      | 0                                                                                                       | 0                                                                                                                                                   | 0                                                                                                                          | 0                                                                                           | 0                        | 0    | 0     |

| Access                                          | R/W                                                                                                                    | R/W                                                                                                     | R/W                                                                                                                                                 | RR/W                                                                                                                       | R/W                                                                                         | R/W                      | R/W  | RR/W  |

| Bit Description                                 | 0 = IPD : 1 = 0 = PDAUTO : 1 = 0 = PDEN : 1 = 0 = OCIE : 1 = OTIE : 1 = STXD : 1 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = | Receiver che<br>Receiver che<br>Receiver che<br>Over Curre<br>Over Temp<br>LS active (i<br>HS active (i | nreshold for<br>nannel 1 pu<br>nannel 1 pu<br>nannel 1 pu<br>nannel 1 pu<br>nannel 1 pul<br>ent IRQ ena<br>o IRQ enable<br>n SIO mode<br>n SIO mode | · IO-Link cor<br>II down cur<br>II down cur<br>Receiver pu<br>II down cor<br>II down disa<br>I down disa<br>ble<br>• only) | mmunication<br>rent 1 Ipdo<br>rent 2 Ipdo<br>Il down sou<br>ntrolled by F<br>Ibled<br>Ibled | on<br>wn1<br>wn2<br>ırce |      |       |

Table 8. Transmitter over current configuration register

#### back to Table 4. Transceiver Register

| TX OCCFG<br>Channel 1 (0x13)<br>Channel 2 (0x23) | MSB       |                                                                                                                                                                     |        |        |   |         |        | LSB     |

|--------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|---|---------|--------|---------|

| Content                                          | -         | -                                                                                                                                                                   | TDOFF1 | TDOFF0 | - | DISOCTH | OCTHR1 | OCTHR0  |

| Reset Value                                      | 0         | 0                                                                                                                                                                   | 0      | 0      | 0 | 0       | 0      | 0       |

| Access                                           | R         | R                                                                                                                                                                   | R/W    | R/W    | R | R/W     | R/W    | R/W     |

| Bit Description                                  | DISOCTH : | TDOFF1 / TDOFF0 : configuration for TdOFF2_OL_CONFx $00 = T_{dOFF2\_OL\_CONF1}$ $01 = T_{dOFF2\_OL\_CONF2}$ $10 = T_{dOFF2\_OL\_CONF3}$ $11 = T_{dOFF2\_OL\_CONF4}$ |        |        |   |         |        | R[1:0], |

Table 9. Number of Bytes for TX

## back to Table 4. Transceiver Register

| UART TXNUM<br>Channel 1 (0x14)<br>Channel 2 (0x24) | MSB                                          |                         |      |      |      |      |      | LSB  |

|----------------------------------------------------|----------------------------------------------|-------------------------|------|------|------|------|------|------|

| Content                                            | -                                            | NUM6                    | NUM5 | NUM4 | NUM3 | NUM2 | NUM1 | NUM0 |

| Reset Value                                        | 0                                            | 0                       | 0    | 0    | 0    | 0    | 0    | 0    |

| Access                                             | R                                            | R/W R/W R/W R/W R/W R/W |      |      |      |      |      |      |

| Bit Description                                    | NUM6 NUM0: Number of Bytes to be transmitted |                         |      |      |      |      |      |      |

### **DUAL IO-LINK MASTER TRANSCEIVER WITH UARTS**

PRODUCTION DATA - NOV 27, 2013

Table 10. Number of Bytes for RX

back to Table 4. Transceiver Register

| UART RXNUM<br>Channel 1 (0x15)<br>Channel 2 (0x25) | MSB                                                   |                         |      |      |      |      |      | LSB  |

|----------------------------------------------------|-------------------------------------------------------|-------------------------|------|------|------|------|------|------|

| Content                                            | -                                                     | NUM6                    | NUM5 | NUM4 | NUM3 | NUM2 | NUM1 | NUM0 |

| Reset Value                                        | 0                                                     | 0                       | 0    | 0    | 0    | 0    | 0    | 0    |

| Access                                             | R                                                     | R/W R/W R/W R/W R/W R/W |      |      |      |      |      |      |

| Bit Description                                    | Description NUM6 NUM0: Number of Bytes to be received |                         |      |      |      |      |      |      |

Table 11. Receiver status and error register

back to Table 4. Transceiver Register

| RX STAT<br>Channel 1 (0x1A)<br>Channel 2 (0x2A) | MSB                                                                                                      |   |   |   |   |   |    | LSB |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------|---|---|---|---|---|----|-----|

| Content                                         | -                                                                                                        | - | - | - | - | - | FE | PE  |

| Reset Value                                     | 0                                                                                                        | 0 | 0 | 0 | 0 | 0 | 0  | 0   |

| Access                                          | R                                                                                                        | R | R | R | R | R | R  | R   |

| Bit Description                                 | FE: 1 = Framing error (no stop bit), cleared by read access PE: 1 = Parity error, cleared by read access |   |   |   |   |   |    |     |

## 5.15 IO-Link Cycle Timer

The IO-Link cycle timer generates the communication cycle. It can be configured in range of 0.4 ms up to 132.8 ms in register TIM PER. The cycle time is configured by selecting one range out of three as shown in Table 12.

Table 12. IO-Link cycle time

| PRSC[1:0] | T <sub>CYC_STEP</sub> | T <sub>CYC_OFFSET</sub> | T <sub>cyc</sub> |

|-----------|-----------------------|-------------------------|------------------|

| 00b       | 0.1 ms                | N.A.                    | 0.4 6.3 ms       |

| 01b       | 0.4 ms                | 6.4 ms Offset included  | 6.4 31.6 ms      |

| 10b       | 1.6 ms                | 32 ms Offset included   | 32 132.8 ms      |

| 11b       | not used              |                         |                  |

$$T_{CYC} = T_{CYC\_OFFSET} + T_{CYC\_STEP} \bullet TIM\_PER[5:0]$$

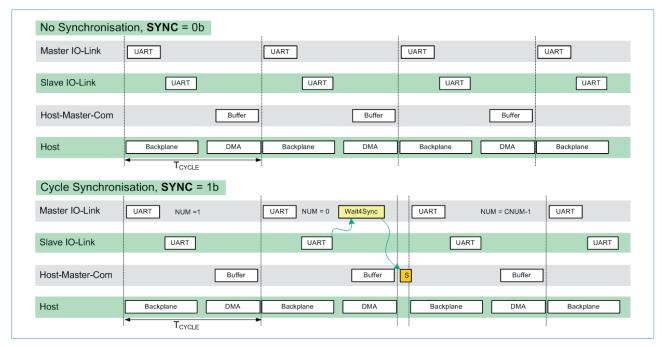

## 5.16 Cycle Synchronisation

In applications with several channels the device has implemented a cycle synchronization capability.

To enable the cycle synchronization feature set bit SYNC in register TIM CFG to "1".

Because of independent internal oscillator of several devices in multi port applications the synchronization

has to be repeated after certain period of time. This period of time depends on oscillator accuracy and application needs. The cycle timer can be configured to run for a number of cycles determined by bits CNUM[2:0] in register TIM CFG (for details see Table below).

Table 13. Number of cycles without resynchronization in SYNC mode

| CNUM[2:0] | Number of free running cycles |

|-----------|-------------------------------|

| 000b      | 0.1 ms                        |

| 001b      | 0.4 ms                        |

| 010b      | 1.6 ms                        |

| 011b      | not used                      |

| 100b      |                               |

| 101b      |                               |

| 110b      |                               |

| 111b      |                               |

$Elmos \ Semiconductor \ AG \ reserves \ the \ right \ to \ change \ the \ detail \ specifications \ as \ may \ be \ required \ to \ permit \ improvements \ in \ the \ design \ of \ its \ products.$

Elmos Semiconductor AG Data Sheet QM-No.: 25DS0069E.02

If this number of cycles is reached, the bit WAIT4S in register TIM STAT is set and the cycle timer waits for a resynchronization event from the host controller. Optionally an interrupt can be activated by bit SYNCIE in register TIM IE to indicate that the device is waiting for an resynchronization event (WAIT4S in TIM STAT). This interrupt is set after the number of free running cycles is reached under two conditions:

- the slave response frame is received (number of received characters is equal UART RXNUM)

- · idle is detected

The interrupt is cleared by reading TIM STAT.