June 2015

# FAN23SV04T 4 A Synchronous Buck Regulator for DDR Termination

#### **Features**

- V<sub>IN</sub> Range: 7 V to 18 V Using Internal Linear Regulator for Bias

- V<sub>IN</sub> Range: 4.5 V to 5.5 V with V<sub>IN</sub>/P<sub>VIN</sub>/P<sub>VCC</sub>

Connected to Bypass Internal Regulator

- High Efficiency

- Continuous Output Current: 4 A

- MOSFETs R<sub>DS,ON</sub> (Typical): HS: 9.67 mΩ, LS: 5.46 mΩ

- Internal Linear Bias Regulator

- Internal V<sub>DDQ</sub> Resistor Divider

- Excellent Line and Load Transient Response

- Output Voltage Range: 0.5 to 1.5 V

- Programmable Frequency: 200 kHz to 1.5 MHz

- Programmable Soft-Start

- Low Shutdown Current

- Adjustable Sourcing Current Limit

- Internal Boot Diode

- Thermal Shutdown

- Halogen and Lead Free, RoHS Compliant

#### **Applications**

- Bus Termination

- Servers and Desktop Computers

- NVDC Notebooks, Netbooks

- Game Consoles

#### **Description**

The FAN23SV04T is a highly efficient, synchronous buck regulator for use in tracking applications, such as DDR termination rails. The  $V_{\rm DDQ}$  input includes an internal 2:1 resistive voltage divider to reduce total circuit size and component count. The regulator operates with an input range from 7 V to 18 V and supports up to 4 A load currents. The device can operate from a 5 V rail (±10%) if  $V_{\rm IN},\,P_{\rm VIN},\,$  and  $P_{\rm VCC}$  are connected together to bypass the internal linear regulator.

This device utilizes Fairchild's constant on-time control architecture to provide excellent transient response and to maintain a relatively constant switching frequency.

Switching frequency and sourcing over-current protection can be programmed to provide a flexible solution for various applications.

Output over-current, and thermal shutdown protections help prevent damage during fault conditions. A hysteresis feature restarts the device when normal operating temperature is reached.

#### **Ordering Information**

| Part Number   | Configuration                                 | Operating<br>Temperature Range | Output<br>Current | Package                        |

|---------------|-----------------------------------------------|--------------------------------|-------------------|--------------------------------|

| FAN23SV04TMPX | PWM Mode with V <sub>DDQ</sub> Tracking Input | -40 to 125°C                   | 4 A               | 34-Lead, PQFN, 5.5 mm x 5.0 mm |

#### **Typical Application Diagrams**

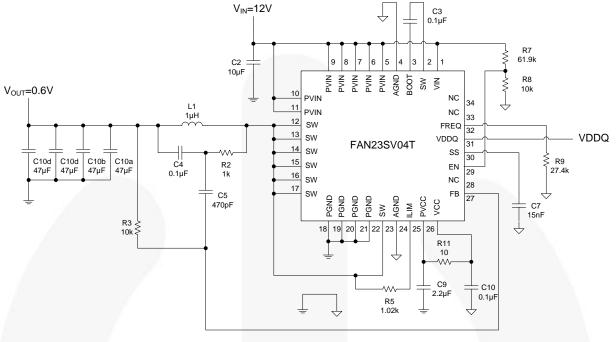

Figure 1. Typical Application with  $V_{\text{IN}} = 12 \text{ V}$

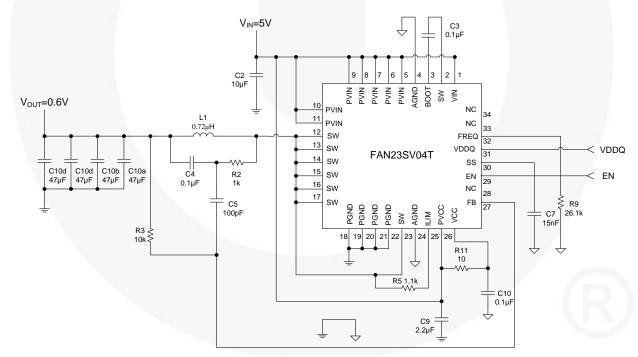

Figure 2. Typical Application with  $V_{IN} = 5 \text{ V}$

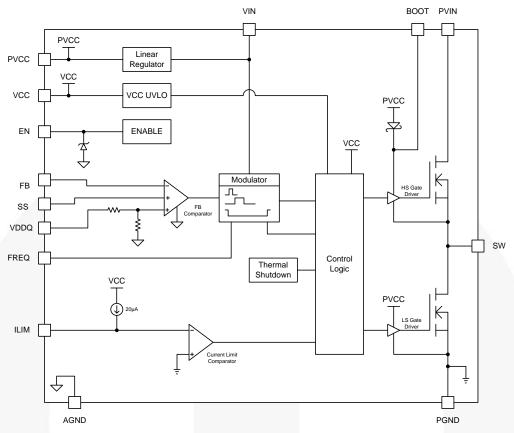

#### **Functional Block Diagram**

Figure 3. Block Diagram

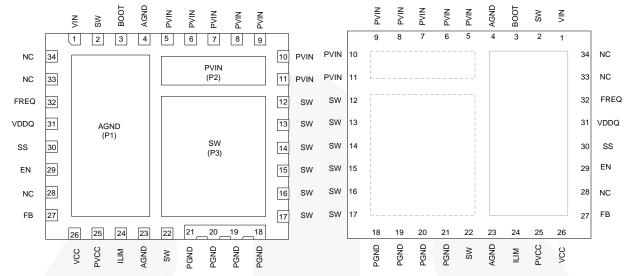

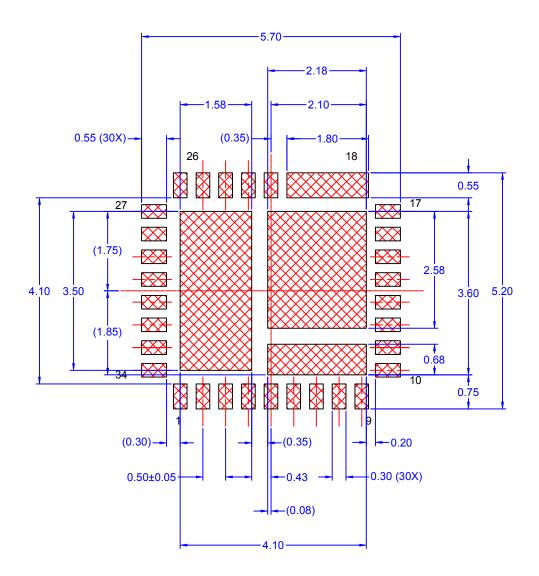

### **Pin Configuration**

Figure 4. Bottom View

Figure 5. Top View

#### **Pin Definitions**

| Name | Pad / Pin        | Description                                                                                                                                                                                                                                                             |  |  |

|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PVIN | P2; 5-11         | Power input for the power stage.                                                                                                                                                                                                                                        |  |  |

| VIN  | 1                | Power input to the linear regulator; used in the modulator for input voltage feed-forward.                                                                                                                                                                              |  |  |

| PVCC | 25               | Power output of the linear regulator; directly supplies power for the low-side gate driver and boot diode. Can be connected to VIN and PVIN for operation from 5 V rail.                                                                                                |  |  |

| VCC  | 26               | Power supply input for the controller.                                                                                                                                                                                                                                  |  |  |

| PGND | 18-21            | Power ground for the low-side power MOSFET and for the low-side gate driver.                                                                                                                                                                                            |  |  |

| AGND | P1; 4, 23        | Analog ground for the analog portions of the IC and for substrate.                                                                                                                                                                                                      |  |  |

| SW   | P3; 2, 12-17, 22 | Switching node; junction between high-and low-side MOSFETs.                                                                                                                                                                                                             |  |  |

| воот | 3                | Supply for high-side MOSFET gate driver. A capacitor from BOOT to SW supplies the charge to turn on the N-channel high-side MOSFET. During the freewheeling interval (low-side MOSFET on), the high-side capacitor is recharged by an internal diode connected to PVCC. |  |  |

| ILIM | 24               | Current limit. A resistor between ILIM and SW sets the current-limit threshold.                                                                                                                                                                                         |  |  |

| FB   | 27               | Output voltage feedback to the modulator.                                                                                                                                                                                                                               |  |  |

| EN   | 29               | Enable input to the IC. Pin must be driven logic high to enable, or logic low to disable.                                                                                                                                                                               |  |  |

| SS   | 30               | Soft-Start input to the modulator                                                                                                                                                                                                                                       |  |  |

| VDDQ | 31               | External reference input to the modulator. The modulator regulates to half of the voltage at the VDDQ pin.                                                                                                                                                              |  |  |

| FREQ | 32               | On-time and frequency programming pin. Connect a resistor between FREQ and AGND to program on-time and switching frequency.                                                                                                                                             |  |  |

| NC   | 28, 33-34        | Leave pin open or connect to AGND.                                                                                                                                                                                                                                      |  |  |

#### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            | Parameter               | Condition                                        | Min. | Max. | Unit |

|-------------------|-------------------------|--------------------------------------------------|------|------|------|

| $V_{PVIN}$        | Power Input             | Referenced to PGND                               | -0.3 | 25.0 | V    |

| V <sub>IN</sub>   | Modulator Input         | Referenced to AGND                               | -0.3 | 25.0 | V    |

| \/                | Boot Voltage            | Referenced to PVCC                               | -0.3 | 26.0 | V    |

| $V_{BOOT}$        |                         | Referenced to PVCC, <20 ns                       | -0.3 | 30.0 | V    |

| W                 | SW Voltage to GND       | Referenced to PGND, AGND                         | -1   | 25   | V    |

| $V_{\text{SW}}$   |                         | Referenced to PGND, AGND < 20 ns                 | -5   | 25   | V    |

| V                 | Boot to SW Voltage      | Referenced to SW                                 | -0.3 | 6.0  | V    |

| $V_{BOOT}$        | Boot to PGND            | Referenced to PGND                               | -0.3 | 30   | V    |

| V <sub>PVCC</sub> | Gate Drive Supply Input | Referenced to PGND, AGND                         | -0.3 | 6.0  | V    |

| V <sub>VCC</sub>  | Controller Supply Input | Referenced to PGND, AGND                         | -0.3 | 6.0  | V    |

| $V_{ILIM}$        | Current Limit Input     | Referenced to AGND                               | -0.3 | 6.0  | V    |

| $V_{FB}$          | Output Voltage Feedback | Referenced to AGND                               | -0.3 | 6.0  | V    |

| $V_{EN}$          | Enable Input            | Referenced to AGND                               | -0.3 | 6.0  | V    |

| $V_{SS}$          | Soft Start Input        | Referenced to AGND                               | -0.3 | 6.0  | V    |

| $V_{FREQ}$        | Frequency Input         | Referenced to AGND                               | -0.3 | 6.0  | V    |

| $V_{DDQ}$         | VDDQ Input              | Referenced to AGND                               | -0.3 | 6.0  | V    |

| ESD               | Floatroatatia Disabarga | Human Body Model, JESD22-A114 <sup>(1)</sup>     |      | 2000 | V    |

| E9D               | Electrostatic Discharge | Charged Device Model, JESD22-C101 <sup>(2)</sup> |      | 2500 | V    |

| TJ                | Junction Temperature    |                                                  |      | +150 | °C   |

| T <sub>STG</sub>  | Storage Temperature     |                                                  | -55  | +150 | °C   |

#### Note:

- 1. Exception for FB pin up to 350V

- 2. Exception for FB pin up to 500V

#### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                                                 | Parameter                                                           | Condition                                                                                                             | Min. | Max. | Unit |

|--------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>PVIN</sub>                                      | Power Input                                                         | Referenced to PGND                                                                                                    | 7    | 18   | V    |

| V <sub>IN</sub>                                        | Modulator Input                                                     | Referenced to AGND                                                                                                    | 7    | 18   | V    |

| TJ                                                     | Junction Temperature                                                |                                                                                                                       | -40  | +125 | °C   |

| I <sub>LOAD</sub>                                      | Load Current                                                        | T <sub>A</sub> =25°C, No Airflow                                                                                      |      | 6    | Α    |

| V <sub>PVIN,</sub> V <sub>IN</sub> , V <sub>PVCC</sub> | PV <sub>IN</sub> , V <sub>IN</sub> , and Gate Drive<br>Supply Input | V <sub>PVIN</sub> , V <sub>IN</sub> , V <sub>PVCC</sub> Connected for 5 V Rail Operation and Referenced to PGND, AGND | 4.5  | 5.5  | V    |

#### **Thermal Characteristics**

The thermal characteristics were evaluated on a 4-layer pcb structure (1 oz/1 oz/1 oz/1 oz) measuring 7 cm x 7 cm).

| Symbol        | Parameter                                                   | Тур. | Unit |

|---------------|-------------------------------------------------------------|------|------|

| $\Theta_{JA}$ | Thermal Resistance, Junction-to-Ambient                     | 35   | °C/W |

| Ψιс           | Thermal Characterization Parameter, Junction-to-Top of Case | 2.7  | °C/W |

| <b>Ψ</b> JРСВ | Thermal Characterization Parameter, Junction-to-PCB         | 2.3  | °C/W |

#### **Electrical Characteristics**

Unless otherwise noted; V  $_{IN}$  =12 V, V  $_{OUT}$  =0.6 V, T  $_{A}$  =T  $_{J}$  =-40 to +125 °C.  $^{(5)}$

| Symbol                      | Parameter                                    | Condition                                                                           | Min. | Тур. | Max. | Unit     |

|-----------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|----------|

| Supply Cur                  | rent                                         |                                                                                     | •    | •    | •    | •        |

| I <sub>VIN,SD</sub>         | Shutdown Current                             | E <sub>N</sub> =0 V                                                                 |      |      | 16   | μA       |

| $I_{VIN,Q}$                 | Quiescent Current                            | E <sub>N</sub> =5 V, Not Switching                                                  |      |      | 1.8  | mA       |

| I <sub>VIN,GateCharge</sub> | Gate Charge Current                          | E <sub>N</sub> =5 V, f <sub>SW</sub> =500 kHz                                       |      | 10   |      | mA       |

| Linear Regi                 | ulator                                       |                                                                                     |      |      |      |          |

| $V_{REG}$                   | Regulator Output Voltage                     |                                                                                     | 4.75 | 5.00 | 5.25 | V        |

| I <sub>REG</sub>            | Regulator Current Limit                      |                                                                                     | 60   |      |      | mA       |

| Reference,                  | Feedback Comparator                          |                                                                                     |      |      |      |          |

| $V_{FB}$                    | FB Voltage Threshold                         |                                                                                     | 590  | 596  | 602  | mV       |

| $V_{DDQ}$                   | V <sub>DDQ</sub> Pin Voltage Range           |                                                                                     | 0    |      | 3    | V        |

| I <sub>FB</sub>             | FB Pin Bias Current                          |                                                                                     | -100 | 0    | 100  | nA       |

| Modulator                   | // A                                         |                                                                                     |      | •    |      | •        |

| t <sub>ON</sub>             | On-Time Accuracy                             | R <sub>FREQ</sub> =56 k, V <sub>IN</sub> =10 V,<br>t <sub>ON</sub> =250 ns, No Load | -20  |      | 20   | %        |

| t <sub>OFF,MIN</sub>        | Minimum SW Off-Time                          |                                                                                     |      | 320  | 374  | ns       |

| D <sub>MIN</sub>            | Minimum Duty Cycle                           | FB=1 V                                                                              |      | 0    |      | %        |

| Soft-Start                  | 7                                            |                                                                                     |      |      | •    |          |

| I <sub>SS</sub>             | Soft-Start Current                           | SS=0 V                                                                              | 7    | 10   | 13   | μA       |

| Current Lin                 | nit                                          |                                                                                     | •    |      | •    |          |

| I <sub>LIM</sub>            | Valley Current Limit Accuracy                | T <sub>A</sub> =T <sub>J</sub> =25°C, I <sub>VALLEY</sub> =4 A                      | -10  |      | 10   | %        |

| K <sub>ILIM</sub>           | I <sub>LIM</sub> Set-Point Scale Factor      |                                                                                     |      | 233  |      |          |

| I <sub>LIMTC</sub>          | Temperature Coefficient                      |                                                                                     |      | 4000 |      | ppm/°C   |

| Enable                      |                                              |                                                                                     | 1    |      | 1    | 1        |

| V <sub>TH+</sub>            | Rising Threshold                             |                                                                                     | 1.11 | 1.26 | 1.43 | V        |

| V <sub>HYST</sub>           | Hysteresis                                   |                                                                                     |      | 122  |      | mV       |

| V <sub>TH</sub> -           | Falling Threshold                            |                                                                                     | 1.00 | 1.14 | 1.28 | V        |

| V <sub>ENCLAMP</sub>        | Enable Voltage Clamp                         | I <sub>EN</sub> =20 μA                                                              | 4.3  | 4.5  |      | V        |

| I <sub>ENCLAMP</sub>        | Clamp Current                                | E <sub>N</sub> =5 V                                                                 | 24   | A    |      | μA       |

| I <sub>ENLK</sub>           | Enable Pin Leakage                           | E <sub>N</sub> =1.2 V                                                               |      |      | 100  | nA       |

| I <sub>ENLK</sub>           | Enable Pin Leakage                           | V <sub>EN</sub> =5 V                                                                |      |      | 76   | μA       |

| UVLO                        |                                              |                                                                                     |      | I    |      |          |

| Von                         | V <sub>CC</sub> Good Threshold Rising        |                                                                                     |      |      | 4.4  | V        |

| V <sub>HYS</sub>            | Hysteresis Voltage                           |                                                                                     |      | 160  |      | mV       |

| Thermal Sh                  | -                                            |                                                                                     |      |      |      |          |

| T <sub>OFF</sub>            | Thermal Shutdown Trip Point <sup>(3)</sup>   |                                                                                     |      | 155  |      | °C       |

| T <sub>HYS</sub>            | Hysteresis <sup>(3)</sup>                    |                                                                                     |      | 15   |      | °C       |

|                             | otstrap Diode                                |                                                                                     |      |      |      |          |

| V <sub>FBOOT</sub>          | Forward Voltage                              | I <sub>F</sub> =10 mA                                                               |      |      | 0.6  | V        |

| I <sub>R</sub>              | Reverse Leakage                              | V <sub>R</sub> =5 V                                                                 |      |      | 1000 | μA       |

| MOSFETs                     | -                                            |                                                                                     | 1    |      | 1    | <u> </u> |

| R <sub>DS,ON,HS</sub>       | Drain to Source On Resistance <sup>(4)</sup> | V <sub>GS</sub> =5 V, I <sub>D</sub> =30 A, T <sub>A</sub> =25°C                    |      | 9.67 |      | mΩ       |

| R <sub>DS,ON.LS</sub>       | Drain to Source On Resistance <sup>(4)</sup> | V <sub>GS</sub> =5 V, I <sub>D</sub> =30 A, T <sub>A</sub> =25°C                    |      | 5.46 |      | mΩ       |

#### Notes:

- 3. Guaranteed by design; not production tested.

- 4. Typical R<sub>DS,ON</sub> value is provided for reference only, and is derived from discrete MOSFET data.

- 5. Device is 100% production tested at T<sub>A</sub>=25°C. Limits over that temperature are guaranteed by design.

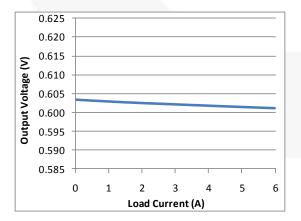

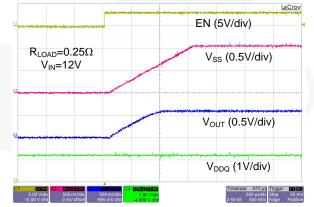

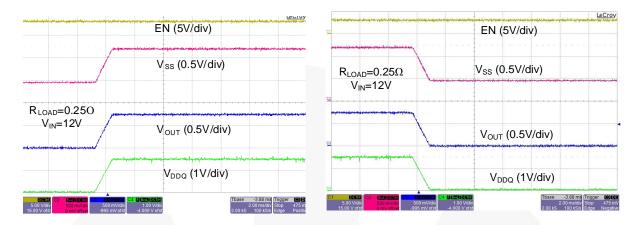

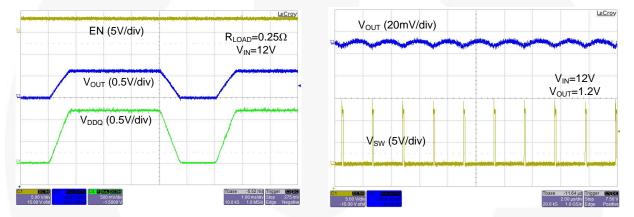

#### **Typical Performance Characteristics**

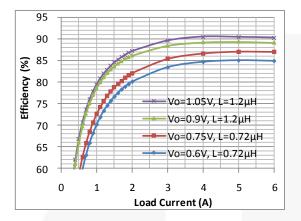

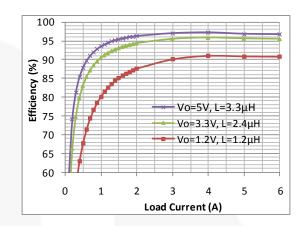

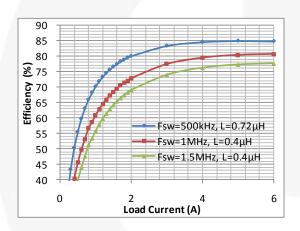

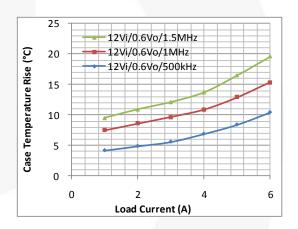

Tested using evaluation board circuit shown in Figure 1 with  $V_{IN}$ =12 V,  $V_{OUT}$ =0.6 V,  $f_{SW}$ =500 kHz,  $T_A$ =25°C, and no airflow; unless otherwise specified.

Figure 6. Efficiency vs. Load Current  $V_{IN}$ =12 V and  $f_{SW}$ =500 kHz

Figure 7. Efficiency vs. Load Current V<sub>IN</sub>=12 V and f<sub>SW</sub>=500 kHz

Figure 8. Efficiency vs. Load Current with  $V_{IN}$ =12 V and  $V_{OUT}$ =0.6 V

Figure 9. Case Temperature Rise vs. Load Current

Figure 10. Load Regulation

Figure 11. Startup Waveforms Using Soft-Start with 2.4 A Resistive Load

## **Typical Performance Characteristics** (Continued)

Figure 12. Startup Waveforms Tracking V<sub>DDQ</sub> with Figure 13. Shutdown Waveforms Tracking V<sub>DDQ</sub> with 2.4 A Resistive Load 2.4 A Resistive Load

Figure 14. Tracking Operation with Variable V<sub>DDQ</sub> Reference Input

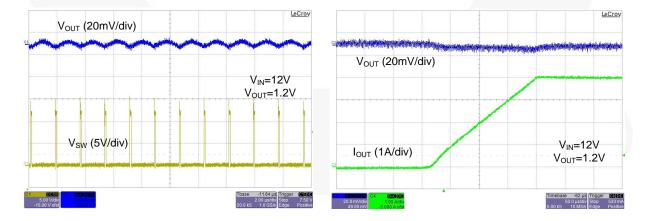

Figure 15. Static Output Ripple with No Load

Figure 16. Static Output Ripple with 4 A Load Current

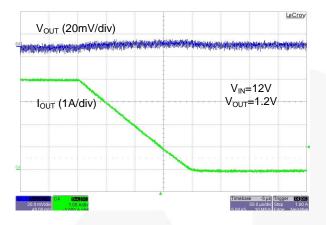

Figure 17. Operation as Load Changes from 0 A to 4 A

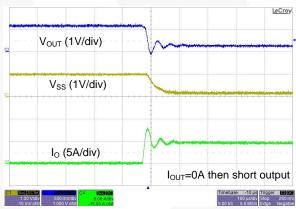

#### **Typical Performance Characteristics** (Continued)

Figure 18. Operation as Load Changes from 4 A to 0 A

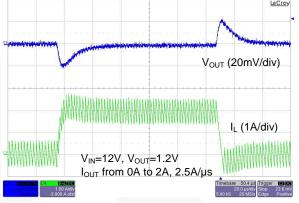

Figure 19. Load Transient from 0% to 50% Load Current

Figure 20. Load Transient from 50% to 100% Load Current

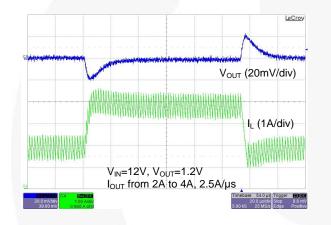

Figure 21. Over-Current Protection with Heavy Load

#### **Circuit Operation**

The FAN23SV04T uses a constant-on-time modulation architecture with a  $V_{\rm IN}$  feed-forward input to accommodate a wide  $V_{\rm IN}$  range. This method provides fixed switching frequency ( $f_{\rm SW}$ ) operation when the inductor operates in Continuous Conduction Mode (CCM). Additional benefits include excellent line and load transient response, cycle-by-cycle current limiting, and elimination of loop compensation requirements.

At the beginning of each cycle, FAN23SV04T turns on the high-side MOSFET (HS) for a fixed duration ( $t_{ON}$ ). At the end of  $t_{ON}$ , HS turns off for a duration ( $t_{OFF}$ ) determined by the operating conditions. Once the FB voltage ( $V_{FB}$ ) falls below the reference voltage ( $V_{REF}$ ), a new switching cycle begins.

The modulator provides a minimum off-time ( $t_{OFF-MIN}$ ) of 250 ns to provide a guaranteed interval for low-side MOSFET (LS) current sensing and PFM operation.  $t_{OFF-MIN}$  provides stability against multiple pulsing and limits maximum switching frequency during transient events.

#### **Enable**

The enable pin can be driven with an external logic signal, connected to a resistive divider from PVIN/Vin to ground to create an Under-Voltage Lockout (UVLO) based on the PVIN/VIN supply, or connected to PVIN/VIN through a single resistor to auto-enable while operating within the EN pin internal clamp current sink capability.

The EN pin can be directly driven by logic voltages of 5 V, 3.3 V, 2.5 V, etc. If the EN pin is driven by 5 V logic, a small current flows into the pin when the EN pin voltage exceeds the internal clamp voltage of 4.3 V. To eliminate clamp current flowing into the EN pin use a voltage divider to limit the EN pin voltage to < 4 V.

To implement the UVLO function based on PVIN/VIN voltage level, select values for R7 and R8 in Figure 1 such that the tap point reaches 1.26 V when  $V_{\text{IN}}$  reaches the desired startup level using the following equation:

$$R7 = R8\left(\frac{V_{IN,on}}{V_{EN,on}} - 1\right) \tag{1}$$

where  $V_{\text{IN},\text{on}}$  is the input voltage for startup and  $V_{\text{EN},\text{on}}$  is the EN pin rising threshold of 1.26 V. With R8 selected as 10 k $\Omega$ , and  $V_{\text{IN},\text{on}} = 9$  V the value of R7 is 61.9 k $\Omega$ .

The EN pin can be pulled high with a single resistor connected from VIN to the EN pin. With VIN > 5.5V a series resistor is required to limit the current flow into the EN pin clamp to less than 24  $\mu$ A to keep the internal clamp within normal operating range. The resistor value can be calculated from the following equation:

$$R_{EN} > \frac{V_{IN,max} - V_{EN,Clamp,min}}{22\mu A} \tag{2}$$

#### **Constant On-Time Modulation**

The FAN23SV04T uses a constant on-time modulation technique, in which the HS MOSFET is turned on for a fixed time, set by the modulator, in response to the input

voltage and the frequency-setting resistor. This on-time is proportional to the desired output voltage, divided by the input voltage. With this proportionality, the frequency is essentially constant over the load range where inductor current is continuous.

For a buck converter in Continuous-Conduction Mode (CCM), the switching frequency f<sub>SW</sub> is expressed as:

$$f_{SW} = \frac{V_{OUT}}{V_{IN} \cdot t_{ON}} \tag{3}$$

The on-time generator sets the on-time  $(t_{\text{ON}})$  for the high-side MOSFET, which results in the switching frequency of the regulator during steady-state operation. To maintain a relatively constant switching frequency over a wide range of input conditions, the input voltage information is fed into the on-time generator.

t<sub>ON</sub> is determined by:

$$t_{ON} = \frac{C_{tON}}{I_{tON}} \cdot 2V \tag{4}$$

where ItON is:

$$I_{tON} = \frac{1}{10} \cdot \frac{V_{IN}}{R_{FREO}} \tag{5}$$

where  $R_{\text{FREQ}}$  is the frequency-setting resistor described in the Setting Switching Frequency section;  $C_{\text{toN}}$  is the internal 2.2 pF capacitor; and  $I_{\text{toN}}$  is the  $V_{\text{IN}}$  feed-forward current that generates the on-time.

The FAN23SV04T implements open-circuit detection on the FREQ pin to protect the output from an infinitely long on-time. In the event the FREQ pin is left floating, switching of the regulator is disabled. The FAN23SV04T is designed for a  $V_{\rm IN}$  input range 7 to 18 V and  $f_{\rm SW}$  from 200 kHz to 1.5 MHz, resulting in an  $I_{\rm tON}$  ratio of 1 to 16.

As the ratio of  $V_{OUT}$  to  $V_{IN}$  increases,  $t_{OFF,min}$  introduces a limit on the maximum switching frequency as calculated in the following equation, where the factor 1.2 is included in the denominator to provide some headroom for transient operation:

$$f_{SW} < \frac{\left(1 - \frac{V_{OUT}}{V_{IN,min}}\right)}{1.2 \cdot t_{OFF,min}} \tag{6}$$

#### **VDDQ**

This pin is connected to the  $V_{DDQ}$  supply, which the FAN23SV04T must track during startup and produce an output  $(V_{TT})$  equal to half of  $V_{DDQ}$  in steady-state conditions. To accomplish this, the  $V_{DDQ}$  pin has an internal resistor divider to AGND that provides a reference voltage equal to  $V_{DDQ}/2$  at the positive input of the FB comparator.

#### Soft-Start (SS)

A conventional soft-start ramp is implemented to provide a controlled startup sequence of the output voltage. A current is generated on the SS pin to charge an external capacitor. The lesser of the voltage on the SS pin and the reference voltage is used for output regulation.

During normal operation, the SS voltage is clamped to 400 mV above the FB voltage. The clamp voltage drops to 40 mV during an overload condition (when  $V_{FB}$  is  $\leq$  400 mV) to allow the converter to recover using the soft-start ramp once the overload condition is removed. There is no on-time modulation during normal soft-start or when recovering from an overload condition.

The nominal startup time is programmable through an internal current source charging the external soft-start capacitor  $C_{SS}$ :

$$C_{SS} = \frac{I_{SS} \cdot t_{SS}}{V_{REF}} \tag{7}$$

where:

C<sub>SS</sub> = External soft-start programming capacitor;

I<sub>SS</sub> = Internal soft-start charging current source, 10 μA;

tss = Soft-start time; and

$V_{REF} = VDDQ/2$ .

For example; for 1 ms startup time, C<sub>SS</sub>=15 nF.

The soft-start option can be used for ratiometric tracking. When EN is LOW, the soft-start capacitor is discharged.

#### **Internal Linear Regulator**

The FAN23SV04T includes a linear regulator to facilitate single-supply operation for self-biased applications. PVCC is the linear regulator output and supplies power to the internal gate drivers. The PVCC pin should be bypassed with a 2.2  $\mu F$  ceramic capacitor. The device can operate from a 5 V rail if the V\_IN, P\_VIN, and P\_VCC pins are connected together to bypass the internal linear regulator.

#### V<sub>CC</sub> Bias Supply and UVLO

The  $V_{CC}$  rail supplies power to the controller. It is generally connected to the PVCC rail through a low-pass filter of a 10  $\Omega$  resistor and 0.1  $\mu$ F capacitor to minimize any noise sources from the driver supply.

An Under-Voltage Lockout (UVLO) circuit monitors the  $V_{CC}$  voltage to ensure proper operation. Once the  $V_{CC}$  voltage is above the UVLO threshold, the part begins operation after an initialization routine of 50  $\mu$ s. There is no UVLO circuitry on either the PVCC or  $V_{IN}$  rails.

#### **Over-Current Protection (OCP)**

The FAN23SV04T uses current information through the LS to implement valley-current limiting. While an OC event is detected, the HS is prevented from turning on and the LS is kept on until the current falls below the user-defined set point. Once the current is below the set point, the HS is allowed to turn on.

The ILIM pin has an open detection circuit to provide protection against operation without a current limit.

#### Over-Temperature Protection (OTP)

FAN23SV04T incorporates an over-temperature protection circuit that disables the converter when the die temperature reaches 155°C. The IC restarts when the die temperature falls below 140°C.

#### **Application Information**

#### **Stability**

Constant on-time stability consists of two parameters: stability criterion and sufficient signal at  $V_{\text{FB}}$ .

Stability criterion is given by:

$$R_{ESR} \cdot C_{OUT} \gg \frac{t_{ON}}{2} \tag{8}$$

Sufficient signal requirement is given by:

$$\Delta I_{IND} \cdot R_{ESR} > \Delta V_{FB} \tag{9}$$

where  $\Delta I_{IND}$  is the inductor current ripple and  $\Delta V_{FB}$  is the ripple voltage on  $V_{FB}$ , which should be  $\geq$ 12 mV.

In certain applications, especially designs utilizing only ceramic output capacitors, there may not be sufficient ripple magnitude available on the feedback pin for stable operation. In this case, an external circuit, such as R2-C4-C5 shown in Figure 1, can be added to inject ripple voltage into the FB pin.

There are some specific considerations when selecting the RCC ripple injector circuit. For typical applications, the value of C4 can be selected as  $0.1\,\mu\text{F}$  and approximate values for R2 and C5 can be determined using the following equations.

R2 must be small enough to develop 12 mV of ripple:

$$R2 < \frac{(V_{IN} - V_{OUT}) \cdot V_{OUT}}{V_{IN} \cdot 0.012V \cdot C4 \cdot f_{SW}}$$

(10)

R2 must also be selected such that the R2C4 time constant enables stable operation:

$$R2 < \frac{0.33 \cdot 2\pi \cdot f_{SW} \cdot L_{OUT} \cdot C_{OUT}}{C4} \tag{11}$$

The minimum value of C5 can be selected to minimize the capacitive component of ripple appearing on the feedback pin:

$$C5_{MIN} = \frac{L_{OUT} \cdot C_{OUT}}{R2 \cdot R3 \cdot C4}$$

(12)

Using the minimum value of C5 generally offers the best transient response, and 100 pF is a good initial value in many applications. However, under some operating conditions excessive pulse jitter may be observed. To reduce jitter and improve stability, the value of C5 can be increased:

$$C5 \ge 2 \cdot C5_{MIN} \tag{13}$$

#### 5 V PV<sub>CC</sub>

The PV<sub>CC</sub> is the output of the internal regulator that supplies power to the drivers and V<sub>CC</sub>. It is crucial to keep this pin decoupled to PGND with a  $\geq 1~\mu F$  X5R or X7R ceramic capacitor. Because V<sub>CC</sub> powers the internal analog circuit, it is filtered from PV<sub>CC</sub> with a 10  $\Omega$  resistor and 0.1  $\mu F$  X7R decoupling ceramic capacitor to AGND.

#### **Setting the Output Voltage (Vout)**

The output voltage,  $V_{OUT}$ , is regulated by initiating a high-side MOSFET on-time interval when the valley of the divided output voltage appearing at the FB pin reaches  $V_{REF}$ . Since this method regulates at the valley of the output ripple voltage, the actual DC output voltage on  $V_{OUT}$  is offset from the programmed output voltage by the average value of the output ripple voltage. The output  $V_{OUT}$  setting of the regulator can be determined using the following equation:

$$V_{OUT} = \frac{V_{DDQ}}{2} \tag{14}$$

where V<sub>DDQ</sub> is the voltage applied to pin 31.

For example; if  $V_{DDQ}$ =1.2 V then  $V_{OUT}$ =600mV.  $V_{FB}$  is trimmed to a value of 596 mV when  $V_{DDQ}$ = $V_{REF}$ =600 mV. The final output voltage, including the effect of the output ripple voltage, can be approximated by:

$$V_{OUT} = V_{FB} * \left[ \frac{V_{rip}}{2} \right] \tag{15}$$

#### Setting the Switching Frequency (fsw)

f<sub>SW</sub> is programmed through external R<sub>FREQ</sub> as follows:

$$R_{FREQ} = \frac{V_{OUT}}{20 * C_{tON} * f_{SW}} \tag{16}$$

where  $C_{tON}{=}2.2$  pF). For example; for f<sub>SW</sub>=500 kHz and V<sub>OUT</sub>=0.6 V, then select a standard resistor value for  $R_{FREQ}{=}27.4$  k $\Omega.$

#### **Inductor Selection**

The inductor is typically selected based on the ripple current ( $\Delta I_L$ ), which is approximately 25% to 45% of the maximum DC load. The inductor current rating should be selected such that the saturation and heating current ratings exceed the intended currents encountered in the application over the expected temperature range of operation. Regulators that require fast transient response use smaller inductance and higher current ripple; while regulators that require higher efficiency keep ripple current on the low side.

The inductor value is given by:

$$L = \frac{(V_{IN} - V_{OUT})}{\Delta I_L \cdot f_{SW}} \cdot \frac{V_{OUT}}{V_{IN}}$$

(17)

For example: for 12 V  $V_{IN},\,0.6$  V  $V_{OUT},\,4$  A load, 25% IL, and 500 kHz  $f_{SW};\,L$  is calculated to be 1.1  $\mu H$  and a standard value of 1  $\mu H$  is selected.

#### **Input Capacitor Selection**

Input capacitor  $C_{\text{IN}}$  is selected based on voltage rating, RMS current  $I_{\text{CIN}(\text{RMS})}$  rating, and capacitance. For capacitors with DC voltage bias derating, such as ceramic capacitors, higher rating is strongly recommended. RMS current rating is given by:

$$I_{CIN(RMS)} = I_{LOAD-MAX} \cdot \sqrt{D \cdot (1-D)}$$

(18)

where  $I_{LOAD\text{-}MAX}$  is the maximum load current and D is the duty cycle  $V_{OUT}/V_{IN}.$  The maximum  $I_{CIN(RMS)}$  occurs at 50% duty cycle.

The capacitance is given by:

$$C_{IN} = \frac{I_{LOAD-MAX} \cdot D \cdot (1 - D)}{f_{SW} \cdot \Delta V_{IN}}$$

(19)

where  $\Delta V_{IN}$  is input voltage ripple, normally 1% of  $V_{IN}$ .

For example: for V<sub>IN</sub>=12 V,  $\Delta$ V<sub>IN</sub>=120 mV, V<sub>OUT</sub>=0.6 V, 4 A load, and f<sub>SW</sub>=950 kHz; then C<sub>IN</sub> is calculated as 1.7  $\mu$ F, select a single 10  $\mu$ F, 25 V-rated ceramic capacitor with X7R or similar dielectric, recognizing that the capacitor DC bias characteristic indicates that the capacitance value falls approximately 40% at V<sub>IN</sub>=12 V.

#### **Output Capacitor Selection**

Output capacitor  $C_{\text{OUT}}$  is also selected based on voltage rating, RMS current  $I_{\text{CIN}}$  (RMS) rating, and capacitance. For capacitors with DC voltage bias derating, such as ceramic capacitors, higher rating is recommended.

When calculating  $C_{\text{OUT}}$ , usually the dominant requirement is the current load step transient. If the unloading transient requirement ( $I_{\text{OUT}}$  transitioning from HIGH to LOW), is satisfied, the load transient ( $I_{\text{OUT}}$  transitioning LOW to HIGH), is also usually satisfied. The unloading  $C_{\text{OUT}}$  calculation, assuming  $C_{\text{OUT}}$  has negligible parasitic resistance and inductance in the circuit path, is given by:

$$C_{OUT} = L \cdot \frac{I_{LEVEL1}^2 - I_{LEVEL2}^2}{(V_{OUT} + \Delta V_{OUT})^2 - V_{OUT}^2}$$

(20)

where  $I_{\text{level1}}$  and  $I_{\text{level2}}$  are current levels before and after load steps, and  $\Delta V_{\text{OUT}}$  is the voltage overshoot, usually specified at 3 to 5%.

For example: for V<sub>I</sub>=12 V, V<sub>OUT</sub>=0.6 V, I<sub>LEVEL1</sub>=3 A, I<sub>LEVEL2</sub>=2 A, f<sub>SW</sub>=500 kHz, L<sub>OUT</sub>=1  $\mu$ H, and 4.0%  $\Delta$ V<sub>OUT</sub> overshoot of 24 mV; the C<sub>OUT</sub> value is calculated to be 170  $\mu$ F, and four 47  $\mu$ F, 6.3 V-rated X5R ceramic capacitors may be used. This equation assumes that the load current rises instantaneously: with reduced current slew rate, the value for C<sub>OUT</sub> can be reduced.

#### **Setting the Current Limit**

Current limit is implemented by sensing the inductor valley current across the LS  $R_{\rm DS(ON)}$  during the LS ontime. The current-limit comparator prevents a new ontime from starting until the valley current is less than the current limit.

The set point is configured by connecting a resistor from the ILIM pin to the SW pin. A trimmed current of approximately 20  $\mu A$  is output onto the ILIM pin, which creates a voltage across the resistor. When the voltage on ILIM goes negative, an over-current condition is detected.

The current flowing out of the ILIM pin through  $R_{\text{ILIM}}$  is trimmed to compensate for both the  $R_{\text{DS(ON)}}$  of the LS MOSFET and the offset voltage of the current limit comparator.  $R_{\text{ILIM}}$  is calculated by:

$$R_{ILIM} = 1.02 * K_{ILIM} * I_{VALLEY}$$

(21)

where  $K_{ILIM}$  is the current source scale factor equal to the average  $R_{DS,ON}$  of the LS MOSFET divided by the average ILIM pin current of 20  $\mu$ A, and  $I_{VALLEY}$  is the inductor valley current when the current limit threshold is reached. The factor 1.01 accounts for the temperature offset of the LS MOSFET compared to control circuit (approximately 5°C), and the approximate increase in the  $R_{DS,on}$  of the LS MOSFET of 4000 ppm/°C.

With the constant on-time architecture, HS is always turned on for a fixed on-time. This determines the peak-to-peak inductor current.

Current ripple ∆I is given by:

$$\Delta I_L = \frac{(V_{IN} - V_{OUT}) * t_{ON}}{L} \tag{22}$$

From the equation above, the worst-case ripple occurs during an output short circuit (where  $V_{\text{OUT}}$  is 0 V). This should be taken into account when selecting the current limit set point.

The FAN23SV04T uses valley-current sensing. The current limit ( $I_{ILIM}$ ) set point is the valley ( $I_{VALLEY}$ ).

The valley current level for calculating RILIM is given by:

$$I_{VALLEY} = I_{LOAD\ (CL)} - \frac{\Delta I_L}{2}$$

(23)

where  $I_{\text{LOAD (CL)}}$  is the DC load current when the current limit threshold is reached.

For example: in a converter designed for 4 A steady-state operation and 1 A current ripple, the current-limit threshold could be selected at 120% of  $I_{LOAD,(SS)}$  to accommodate transient operation and inductor value decrease under loading. As a result;  $I_{LOAD,(SS)}$  is 4.8 A,  $I_{VALLEY}{=}4.3$  A, and  $R_{ILIM}$  is selected as the standard value of1.02  $k\Omega$ .

#### **Boot Resistor**

In some applications, especially with higher input voltage, the  $V_{\text{SW}}$  ring voltage may exceed the derating guidelines of 80% to 90% of absolute rating for  $V_{\text{SW}}$ . In this situation, a resistor can be connected in series with the boot capacitor (C3 in Figure 1) to reduce the turn-on speed of the high-side MOSFET to reduce the amplitude of the  $V_{\text{SW}}$  ring voltage.

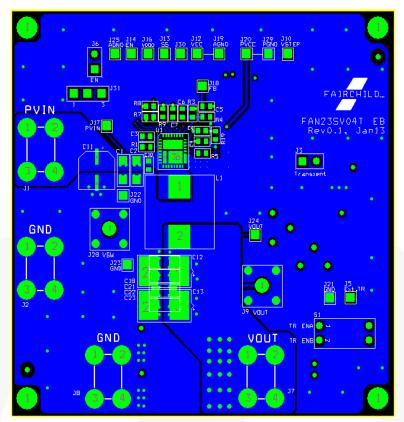

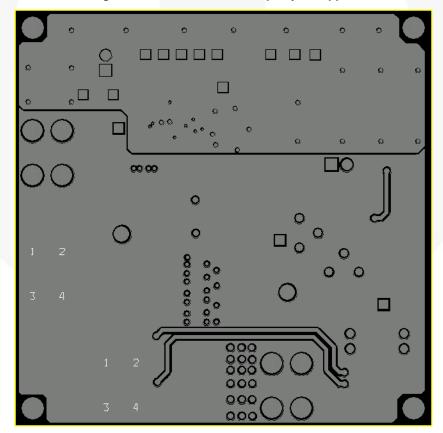

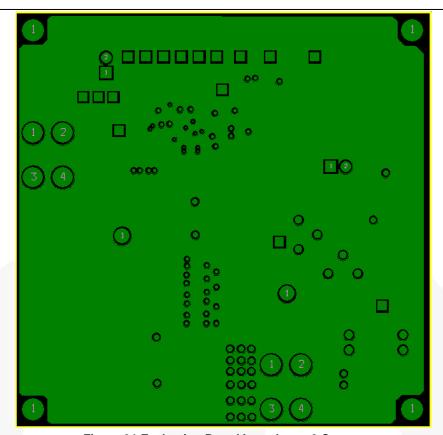

## PCB (Printed Circuit Board) Layout Guidelines

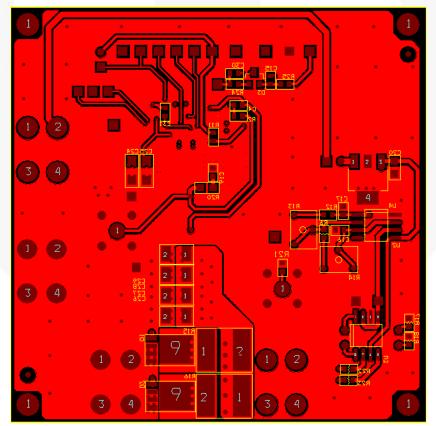

The following should be considered before beginning a PCB layout using the FAN23SV04T. A sample PCB layout from the evaluation board following the layout guidelines is shown in Figure 22 - Figure 25.

Power components consisting of the input capacitors, output capacitors, inductor, and FAN23SV04T device should be on a common side of the PCB in close proximity to each other and connected using surface copper.

Sensitive analog components; including SS, FB, ILIM, FREQ, and EN; should be placed away from the high-voltage switching circuits, such as SW and BOOT, and connected to their respective pins with short traces.

The inner PCB layer closest to the FAN23SV04T device should have Power Ground (PGND) under the power-processing portion of the device (PVIN, SW, and PGND). This inner PCB layer should have a separate Analog Ground (AGND) under the P1 pad and the associated analog components. AGND and PGND should be connected together near the IC between PGND pins 18-21 and AGND pin 23, which connects to P1 thermal pad.

The AGND thermal pad (P1) should be connected to AGND plane on the inner layer using four 0.25 mm vias spread under the pad. No vias are included under PVIN (P2) and SW (P3) to maintain the PGND plane under the power circuitry intact.

Power circuit loops that carry high currents should be arranged to minimize the loop area. Primary focus should be directed to minimize the loop for current flow from the input capacitor to PVIN, through the internal MOSFETs, and returning to the input capacitor. The input capacitor should be placed as close to the PVIN terminals as possible.

The current return path from PGND at the low-side MOSFET source to the negative terminal of the input capacitor can be routed under the inductor and also through vias that connect the input capacitor and low-side MOSFET source to the PGND region under the power portion of the IC.

The SW node trace that connects the source of the high-side MOSFET and the drain of the low-side MOSFET to the inductor should be short and wide.

To control the voltage across the output capacitor, the output voltage divider should be located close to the FB pin, with the upper FB voltage divider resistor connected to the positive side of the output capacitor, and the bottom resistor should be connected to the AGND portion of the FAN23SV04T device.

When using ceramic capacitor solutions with external ramp injection circuitry (R2, C4, C5 in Figure 1), R2 and C4 should be connected near the inductor and coupling capacitor C5 should be placed near the FB pin to minimize FB pin trace length.

Decoupling capacitors for PVCC and VCC should be located close to their respective device pins.

SW node connections to BOOT, ILIM, and ripple injection resistor R2 should be through separate traces.

Figure 22. Evaluation Board Top Layer Copper

Figure 23. Evaluation Board Inner Layer 1 Copper

Figure 24. Evaluation Board Inner Layer 2 Copper

Figure 25. Evaluation Board Bottom Layer Copper

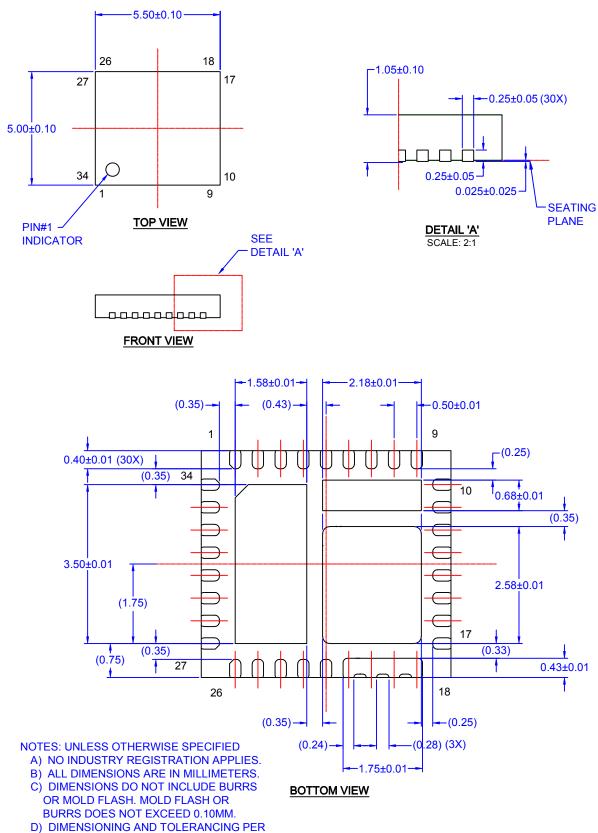

- ASME Y14.5M-2009.

- E) DRAWING FILE NAME: MKT-PQFN34AREV2

- F) FAIRCHILD SEMICONDUCTOR

LAND PATTERN RECOMMENDATION

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

AccuPower™ F-PFS™ AttitudeEngine™ FRFET®

Global Power Resource<sup>SM</sup> Awinda<sup>®</sup> AX-CAP®\*

GreenBridge™ BitSiC™ Green FPS™ Build it Now™ Green FPS™ e-Series™

CorePLUS™ Gmax™ CorePOWER™  $\mathsf{GTO}^{\mathsf{TM}}$ CROSSVOLT™ IntelliMAX™ CTL™ ISOPLANAR™

Current Transfer Logic™ Making Small Speakers Sound Louder

**DEUXPEED®** and Better™ Dual Cool™ MegaBuck™ EcoSPARK® MIČROCOUPLER™ EfficientMax™

MicroFET™ **ESBC™** MicroPak™ **■**® MicroPak2™ MillerDrive™ Fairchild®

MotionMax™ Fairchild Semiconductor® MotionGrid® FACT Quiet Series™ MTi<sup>®</sup> FACT MTx® FAST<sup>®</sup> MVN® FastvCore™ mWSaver® FETBench™ OptoHiT™ FPS™

OPTOLOGIC®

OPTOPLANAR®

Power Supply WebDesigner™ PowerTrench®

PowerXSTI

Programmable Active Droop™

OFFT QS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™

Solutions for Your Success™

SPM® STEALTH™ SuperFET® SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SyncFET™ Sync-Lock™

SYSTEM SYSTEM

TinyBoost<sup>®</sup> TinyBuck<sup>®</sup> TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO™ TinvPower™ TinyPWM™ TinyWire™ TranSiC™ TriFault Detect™ TRUECURRENT®\*

uSerDes™ UHC Ultra FRFET™

UniFET™ VCX™ VisualMax™ VoltagePlus™ XSTM. Xsens™ 仙童™

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. TO OBTAIN THE LATEST, MOST UP-TO-DATE DATASHEET AND PRODUCT INFORMATION, VISIT OUR <u>AIRCHILDSEMI.COM.</u> FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

Unless otherwise specified in this data sheet, this product is a standard commercial product and is not intended for use in applications that require extraordinary levels of quality and reliability. This product may not be used in the following applications, unless specifically approved in writing by a Fairchild officer: (1) automotive or other transportation, (2) military/aerospace, (3) any safety critical application - including life critical medical equipment - where the failure of the Fairchild product reasonably would be expected to result in personal injury, death or property damage. Customer's use of this product is subject to agreement of this Authorized Use policy. In the event of an unauthorized use of Fairchild's product, Fairchild accepts no liability in the event of product failure. In other respects, this product shall be subject to Fairchild's Worldwide Terms and Conditions of Sale, unless a separate agreement has been signed by both Parties.

#### **ANTI-COUNTERFEITING POLICY**

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com,

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Definition of Terms      |                       |                                                                                                                                                                                                     |  |  |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |  |  |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |  |  |

Rev 175

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.