# MC68340

# Integrated Processor with DMA User's Manual

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and the was registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

### **PREFACE**

The complete documentation package for the MC68340 consists of the MC68340UM/AD, MC68340 Integrated Processor with DMA User's Manual, M68000PM/AD, MC68000 Family Programmer's Reference Manual, and the MC68340P/D, MC68340 Integrated Processor with DMA Product Brief.

The MC68340 Integrated with DMA Processor User's Manual describes the programming, capabilities, registers, and operation of the MC68340; the MC68000 Family Programmer's Reference Manual provides instruction details for the MC68340; and the MC68340 Integrated Processor with DMA Product Brief provides a brief description of the MC68340 capabilities.

This user's manual is organized as follows:

| Device Overview           | Section 8                                                                               | Timer Modules                                                                                                            |

|---------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Signal Descriptions       | Section 9                                                                               | IEEE 1149.1 Test Access                                                                                                  |

| Bus Operation             |                                                                                         | Port                                                                                                                     |

| System Integration Module | Section 10                                                                              | Applications                                                                                                             |

| CPU32                     | Section 11                                                                              | Electrical Characteristics                                                                                               |

| DMA Controller Module     | Section 12                                                                              | Ordering Information and                                                                                                 |

| Serial Module             |                                                                                         | Mechanical Data                                                                                                          |

|                           | Signal Descriptions Bus Operation System Integration Module CPU32 DMA Controller Module | Signal Descriptions Bus Operation System Integration Module CPU32 DMA Controller Module Section 10 Section 11 Section 12 |

# **68K FAX-IT** FAX 512-891-8593

The Motorola High-End Technical Publication Department provides a FAX number for you to submit any questions and comments about this document. We welcome your suggestions for improving our documentation or any questions concerning our products.

Please provide the part number and revision number (located in upper right-hand corner on the cover), and the title of the document when submitting. When referring to items in the manual please reference by the page number, paragraph number, figure number, table number, and line number if needed. Reference the line number from the top of the page.

When we receive a FAX between the hours of 7:30 AM and 5:00 PM EST, Monday through Friday, we will respond within two hours. If the FAX is received after 5:00 PM or on the weekend, we will respond within two hours on the first working day following receipt of the FAX.

When sending a FAX, please provide your name, company, FAX number, and voice number including area code (so we can talk to a real person if needed).

# TABLE OF CONTENTS

| Paragraph<br>Number | Title                                            | Page<br>Number |

|---------------------|--------------------------------------------------|----------------|

|                     | Section 1                                        |                |

|                     | Device Overview                                  |                |

| 1.1                 | M68300 Family                                    | 1-2            |

| 1.1.1               | Organization                                     |                |

| 1.1.2               | Advantages                                       |                |

| 1.2                 | Central Processor Unit                           | 1-3            |

| 1.2.1               | CPU32                                            | 1-4            |

| 1.2.2               | Background Debug Mode                            | 1-4            |

| 1.3                 | On-Chip Peripherals                              |                |

| 1.3.1               | System Integration Module                        | 1-5            |

| 1.3.1.1             | External Bus Interface                           |                |

| 1.3.1.2             | System Configuration and Protection              |                |

| 1.3.1.3             | Clock Synthesizer                                |                |

| 1.3.1.4             | Chip Select and Wait State Generation            |                |

| 1.3.1.5             | Interrupt Handling                               |                |

| 1.3.1.6             | Discrete I/O Pins                                |                |

| 1.3.1.7             | IEEE 1149.1 Test Access Port                     |                |

| 1.3.2               | Direct Memory Access Module                      |                |

| 1.3.3               | Serial Module                                    |                |

| 1.3.4               | Timer Modules                                    |                |

| 1.4                 | Power Consumption Management                     |                |

| 1.5<br>1.6          | Physical                                         |                |

| 1.6                 | Compact Disc-Interactive  More Information       |                |

| 1.7                 | More information                                 | 1-10           |

|                     |                                                  |                |

|                     | Section 2 Signal Descriptions                    |                |

| 2.1                 | Signal Index                                     | 2-2            |

| 2.2                 | Address Bus                                      |                |

| 2.2.1               | Address Bus (A23–A0)                             |                |

| 2.2.2               | Address Bus (A31–A24)                            |                |

| 2.3                 | Data Bus (D15–D0)                                |                |

| 2.4                 | Function Codes (FC3–FC0)                         |                |

| 2.5                 | Chip Selects (CS3–CS0)                           |                |

| 2.6                 | Interrupt Request Level (IRQ7, IRQ6, IRQ5, IRQ3) |                |

| Paragraph<br>Number | Title                                      | Page<br>Number |

|---------------------|--------------------------------------------|----------------|

| 2.7                 | Bus Control Signals                        |                |

| 2.7.1               | Data and Size Acknowledge (DSACK1, DSACK0) | 2-6            |

| 2.7.2               | Address Strobe (AS)                        |                |

| 2.7.3               | Data Strobe (DS)                           |                |

| 2.7.4               | Transfer Size (SIZ1, SIZ0)                 |                |

| 2.7.5               | Read/Write (R/W)                           |                |

| 2.8                 | Bus Arbitration Signals                    |                |

| 2.8.1               | Bus Request (BR)                           |                |

| 2.8.2               | Bus Grant (BG)                             |                |

| 2.8.3               | Bus Grant Acknowledge (BGACK)              | 2-7            |

| 2.8.4               | Read-Modify-Write Cycle (RMC)              |                |

| 2.9                 | Exception Control Signals                  |                |

| 2.9.1               | Reset (RESET)                              |                |

| 2.9.2               | Halt (HALT)                                |                |

| 2.9.3               | Bus Èrror (BÉRR)                           |                |

| 2.10                | Clock Signals                              |                |

| 2.10.1              | System Clock (CLKOUT)                      |                |

| 2.10.2              | Crystal Oscillator (EXTAL, XTAL)           |                |

| 2.10.3              | External Filter Capacitor (XFC)            |                |

| 2.10.4              | Clock Mode Select (MODCK)                  |                |

| 2.11                | Instrumentation and Emulation Signals      |                |

| 2.11.1              | Instruction Fetch (IFETCH)                 |                |

| 2.11.2              | Instruction Pipe (IPIPE)                   |                |

| 2.11.3              | Breakpoint (BKPT)                          |                |

| 2.11.4              | Freeze (FREEZE)                            |                |

| 2.12                | DMA Module Signals                         |                |

| 2.12.1              | DMA Request (DREQ2, DREQ1)                 |                |

| 2.12.2              | DMA Acknowledge (DACK2, DACK1)             |                |

| 2.12.3              | DMA Done (DONE2, DONE1)                    |                |

| 2.13                | Serial Module Signals                      | 2-11           |

| 2.13.1              | Serial Crystal Oscillator (X2, X1)         | 2-11           |

| 2.13.2              | Serial External Clock Input (SCLK)         |                |

| 2.13.3              | Receive Data (RxDA, RxDB)                  | 2-11           |

| 2.13.4              | Transmit Data (TxDA, TxDB)                 | 2-11           |

| 2.13.5              | Clear to Send (CTSA, CTSB)                 | 2-11           |

| 2.13.6              | Request to Send (RTSA, RTSB)               | 2-11           |

| 2.13.7              | Transmitter Ready (T≈RDYA)                 | 2-11           |

| 2.13.8              | Receiver Ready (R≈RDYA)                    | 2-12           |

| 2.14                | Timer Signals                              |                |

| 2.14.1              | Timer Gate (TGATE2, TGATE1)                | 2-12           |

| 2.14.2              | Timer Input (TIN2, TIN1)                   | 2-12           |

| 2.14.3              | Timer Output (TOUT2, TOUT1)                | 2-12           |

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

| 2.15                | Test Signals                                       | 2-13           |

| 2.15.1              | Test Clock (TCK)                                   | 2-13           |

| 2.15.2              | Test Mode Select (TMS)                             |                |

| 2.15.3              | Test Data In (TDI)                                 |                |

| 2.15.4              | Test Data Out (TDO)                                |                |

| 2.16                | Synthesizer Power (V <sub>CCSYN</sub> )            |                |

| 2.17                | System Power and Ground (V <sub>CC</sub> and GND)  | 2-13           |

| 2.18                | Signal Summary                                     |                |

|                     | Section 3                                          |                |

|                     | Bus Operation                                      |                |

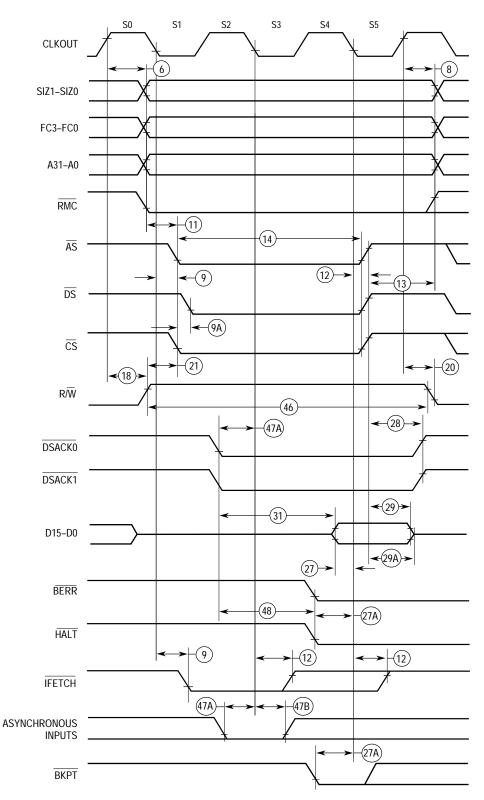

| 3.1                 | Bus Transfer Signals                               |                |

| 3.1.1               | Bus Control Signals                                |                |

| 3.1.2               | Function Code Signals                              |                |

| 3.1.3               | Address Bus (A31–A0)                               |                |

| 3.1.4               | Address Strobe (AS)                                |                |

| 3.1.5               | Data Bus (D15–D0)                                  |                |

| 3.1.6               | Data Strobe (DS)                                   |                |

| 3.1.7               | Bus Cycle Termination Signals                      | 3-4            |

| 3.1.7.1             | Data Transfer and Size Acknowledge Signals         |                |

|                     | (DSACK1 and DSACK0)                                |                |

| 3.1.7.2             | Bus Error (BERR)                                   |                |

| 3.1.7.3             | Autovector (AVEC)                                  | 3-5            |

| 3.2                 | Data Transfer Mechanism                            |                |

| 3.2.1               | Dynamic Bus Sizing                                 |                |

| 3.2.2               | Misaligned Operands                                |                |

| 3.2.3               | Operand Transfer Cases                             |                |

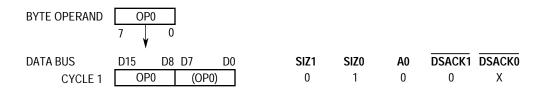

| 3.2.3.1             | Byte Operand to 8-Bit Port, Odd or Even $(A0 = X)$ |                |

| 3.2.3.2             | Byte Operand to 16-Bit Port, Even (A0 = 0)         |                |

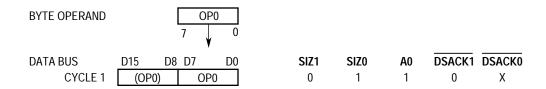

| 3.2.3.3             | Byte Operand to 16-Bit Port, Odd (A0 = 1)          |                |

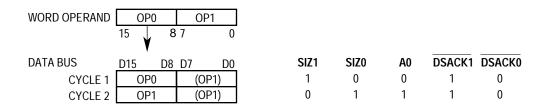

| 3.2.3.4             | Word Operand to 8-Bit Port, Aligned                |                |

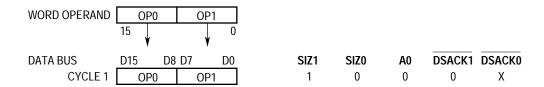

| 3.2.3.5             | Word Operand to 16-Bit Port, Aligned               |                |

| 3.2.3.6             | Long-word Operand to 8-Bit Port, Aligned           |                |

| 3.2.3.7             | Long-Word Operand to 16-Bit Port, Aligned          |                |

| 3.2.4               | Bus Operation                                      |                |

| 3.2.5               | Synchronous Operation with DSACK≈                  |                |

| 3.2.6               | Fast Termination Cycles                            |                |

| 3.3                 | Data Transfer Cycles                               |                |

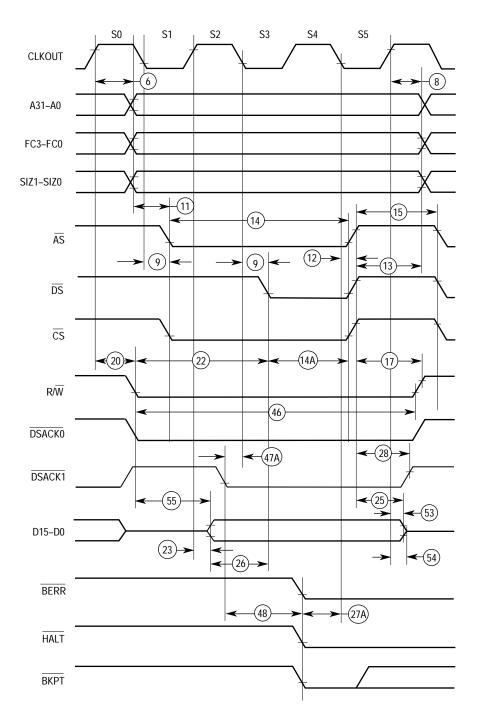

| 3.3.1               | Read Cycle                                         |                |

| 3.3.2               | Write Cycle                                        |                |

| 3.3.3               | Read-Modify-Write Cycle                            | 3-19           |

| Paragraph<br>Number | Title                                           | Page<br>Number |

|---------------------|-------------------------------------------------|----------------|

| 3.4                 | CPU Space Cycles                                | 3-21           |

| 3.4.1               | Breakpoint Acknowledge Cycle                    | 3-22           |

| 3.4.2               | LPSTOP Broadcast Cycle                          | 3-23           |

| 3.4.3               | Module Base Address Register Access             | 3-27           |

| 3.4.4               | Interrupt Acknowledge Bus Cycles                | 3-27           |

| 3.4.4.1             | Interrupt Acknowledge Cycle—Terminated Normally | 3-27           |

| 3.4.4.2             | Autovector Interrupt Acknowledge Cycle          | 3-29           |

| 3.4.4.3             | Spurious Interrupt Cycle                        | 3-30           |

| 3.5                 | Bus Exception Control Cycles                    | 3-32           |

| 3.5.1               | Bus Errors                                      |                |

| 3.5.2               | Retry Operation                                 | 3-36           |

| 3.5.3               | Halt Operation                                  | 3-38           |

| 3.5.4               | Double Bus Fault                                | 3-39           |

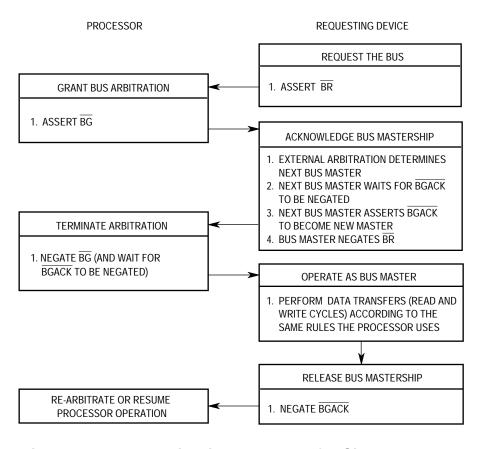

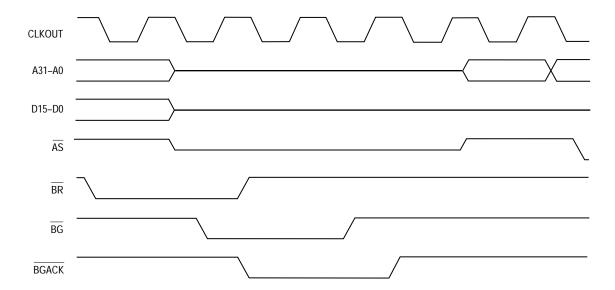

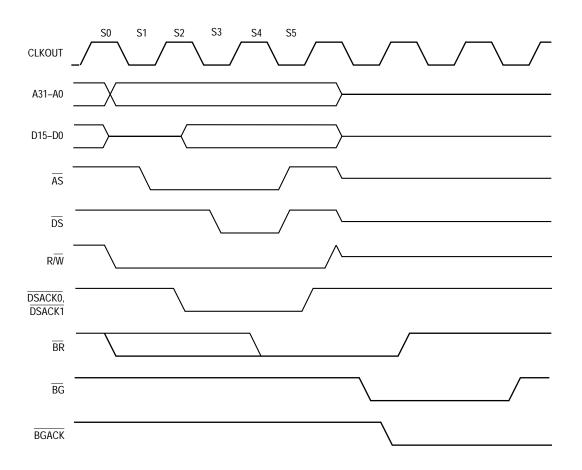

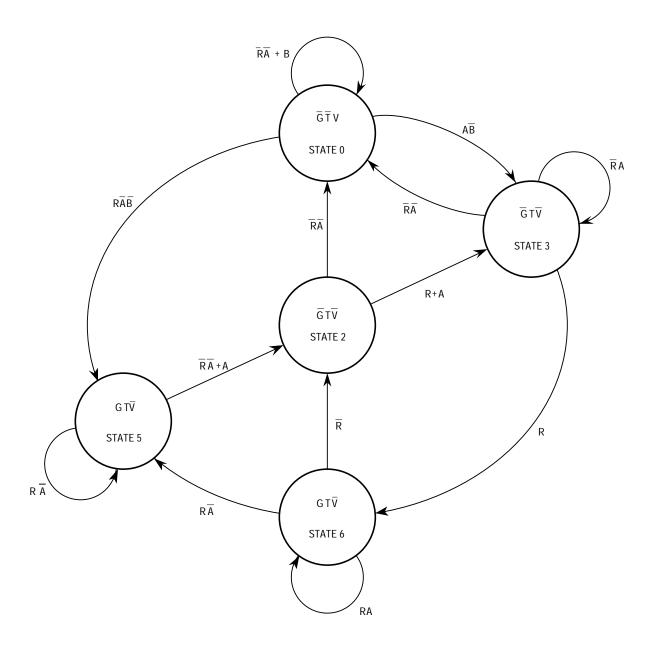

| 3.6                 | Bus Arbitration                                 | 3-40           |

| 3.6.1               | Bus Request                                     | 3-43           |

| 3.6.2               | Bus Grant                                       | 3-43           |

| 3.6.3               | Bus Grant Acknowledge                           | 3-43           |

| 3.6.4               | Bus Arbitration Control                         | 3-44           |

| 3.6.5               | Show Cycles                                     | 3-44           |

| 3.7                 | Reset Operation                                 |                |

|                     | Section 4 System Integration Module             |                |

| 4.1                 | Module Overview                                 | 4-1            |

| 4.2                 | Module Operation                                | 4-2            |

| 4.2.1               | Module Base Address Register Operation          | 4-2            |

| 4.2.2               | System Configuration and Protection Operation   | 4-3            |

| 4.2.2.1             | System Configuration                            |                |

| 4.2.2.2             | Internal Bus Monitor                            | 4-6            |

| 4.2.2.3             | Double Bus Fault Monitor                        | 4-6            |

| 4.2.2.4             | Spurious Interrupt Monitor                      | 4-6            |

| 4.2.2.5             | Software Watchdog                               | 4-6            |

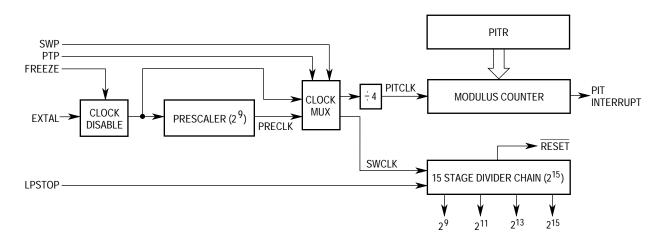

| 4.2.2.6             | Periodic Interrupt Timer                        | 4-7            |

| 4.2.2.6.1           | Periodic Timer Period Calculation               |                |

| 4.2.2.6.2           | Using the Periodic Timer as a Real-Time Clock   | 4-9            |

| 4.2.2.7             | Simultaneous Interrupts by Sources in the SIM40 |                |

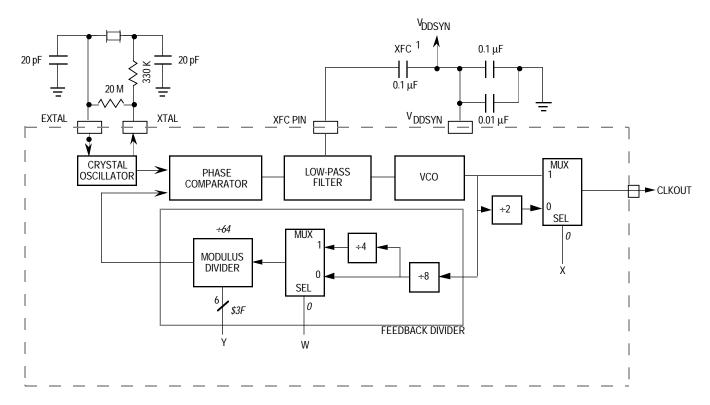

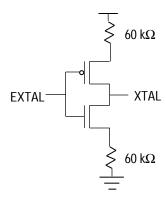

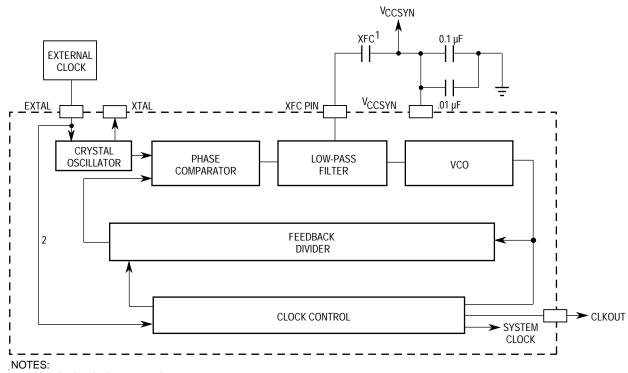

| 4.2.3               | Clock Synthesizer Operation                     | 4-9            |

| 4.2.3.1             | Phase Comparator and Filter                     |                |

| 4.2.3.2             | Frequency Divider                               |                |

| 4.2.3.3             | Clock Control                                   |                |

| 4.2.4               | Chip Select Operation                           |                |

| 4.2.4.1             | Programmable Features                           |                |

| Paragraph<br>Number | Title                                         | Page<br>Numbe |

|---------------------|-----------------------------------------------|---------------|

| 4.2.4.2             | Global Chip Select Operation                  | 4-14          |

| 4.2.5               | External Bus Interface Operation              | 4-15          |

| 4.2.5.1             | Port A                                        | 4-15          |

| 4.2.5.2             | Port B                                        | 4-16          |

| 4.2.6               | Low-Power Stop                                | 4-17          |

| 4.2.7               | Freeze                                        | 4-17          |

| 4.3                 | Programming Model                             |               |

| 4.3.1               | Module Base Address Register (MBAR)           | 4-20          |

| 4.3.2               | System Configuration and Protection Registers |               |

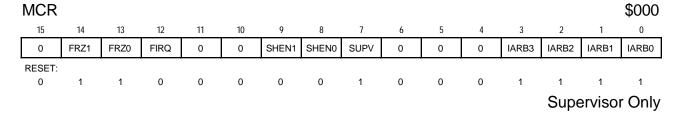

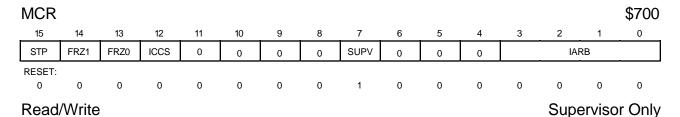

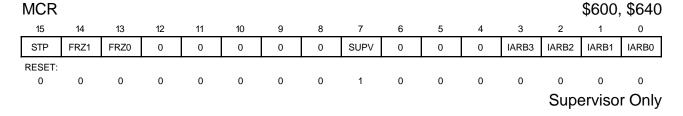

| 4.3.2.1             | Module Configuration Register (MCR)           | 4-21          |

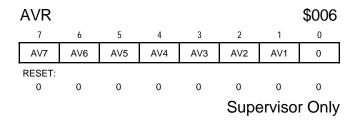

| 4.3.2.2             | Autovector Register (AVR)                     |               |

| 4.3.2.3             | Reset Status Register (RSR)                   |               |

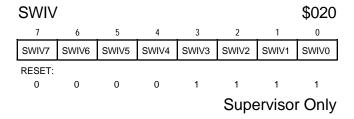

| 4.3.2.4             | Software Interrupt Vector Register (SWIV)     |               |

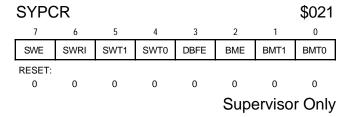

| 4.3.2.5             | System Protection Control Register (SYPCR)    |               |

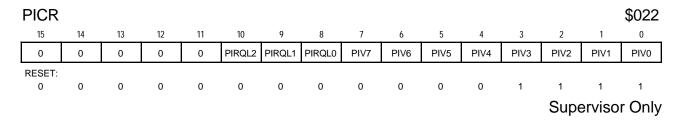

| 4.3.2.6             | Periodic Interrupt Control Register (PICR)    |               |

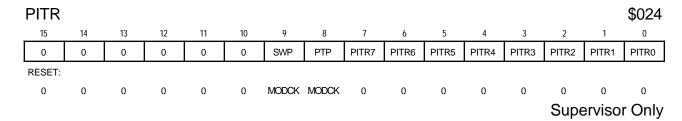

| 4.3.2.7             | Periodic Interrupt Timer Register (PITR)      |               |

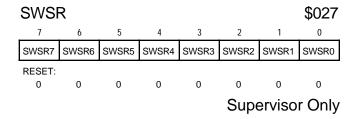

| 4.3.2.8             | Software Service Register (SWSR)              |               |

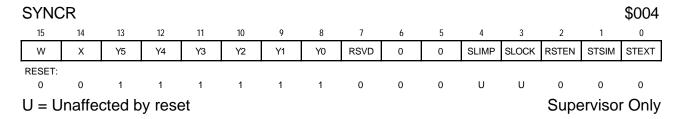

| 4.3.3               | Clock Synthesizer Control Register (SYNCR)    |               |

| 4.3.4               | Chip Select Registers                         |               |

| 4.3.4.1             | Base Address Registers                        |               |

| 4.3.4.2             | Address Mask Registers                        |               |

| 4.3.4.3             | Chip Select Registers Programming Example     |               |

| 4.3.5               | External Bus Interface Control                |               |

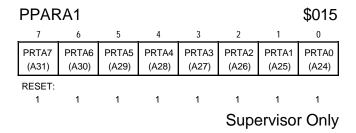

| 4.3.5.1             | Port A Pin Assignment Register 1 (PPARA1)     | 4-33          |

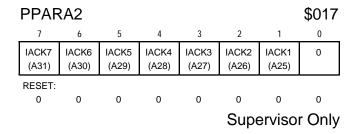

| 4.3.5.2             | Port A Pin Assignment Register 2 (PPARA2)     |               |

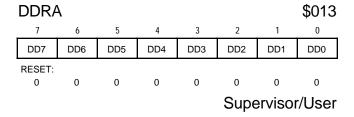

| 4.3.5.3             | Port A Data Direction Register (DDRA)         |               |

| 4.3.5.4             | Port A Data Register (PORTA)                  |               |

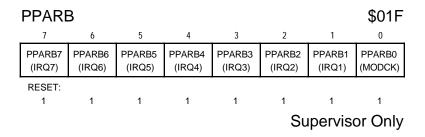

| 4.3.5.5             | Port B Pin Assignment Register (PPARB)        |               |

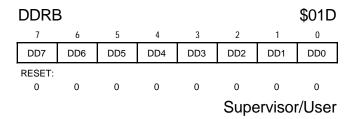

| 4.3.5.6             | Port B Data Direction Register (DDRB)         |               |

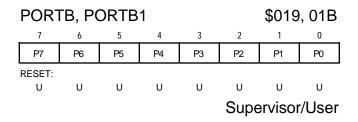

| 4.3.5.7             | Port B Data Register (PORTB, PORTB1)          |               |

| 4.4                 | MC68340 Initialization Sequence               |               |

| 4.4.1               | Startup                                       |               |

| 4.4.2               | SIM40 Module Configuration                    |               |

| 4.4.3               | SIM40 Example Configuration Code              |               |

|                     | Section 5<br>CPU32                            |               |

| 5.1                 | Overview                                      | <b>Б</b> _1   |

| 5.1.1               | Features                                      |               |

| 5.1.1               | Virtual Memory                                |               |

| 5.1.2               | Loop Mode Instruction Execution               |               |

| 0.1.0               | Loop wode instruction execution               | 3-3           |

| Paragraph<br>Number | Title                                             | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

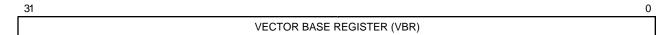

| 5.1.4               | Vector Base Register                              | 5-4            |

| 5.1.5               | Exception Handling                                | 5-4            |

| 5.1.6               | Addressing Modes                                  | 5-5            |

| 5.1.7               | Instruction Set                                   | 5-5            |

| 5.1.7.1             | Table Lookup and Interpolate Instructions         | 5-7            |

| 5.1.7.2             | Low-Power STOP Instruction                        | 5-7            |

| 5.1.8               | Processing States                                 | 5-7            |

| 5.1.9               | Privilege States                                  | 5-7            |

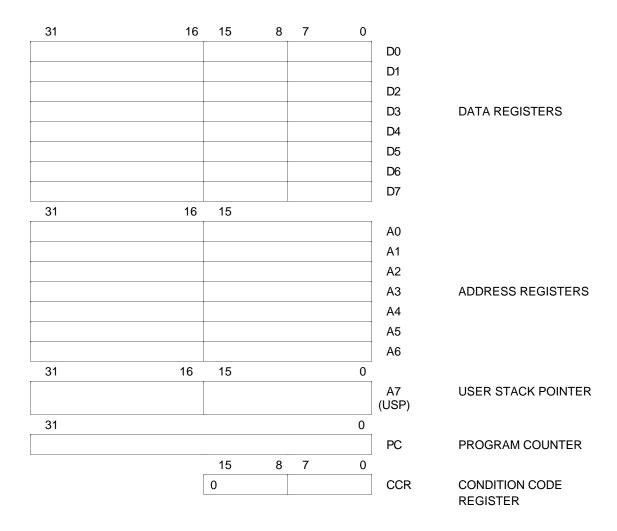

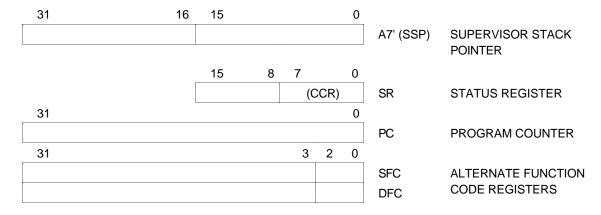

| 5.2                 | Architecture Summary                              | 5-8            |

| 5.2.1               | Programming Model                                 | 5-8            |

| 5.2.2               | Registers                                         |                |

| 5.3                 | Instruction Set                                   |                |

| 5.3.1               | M68000 Family Compatibility                       | 5-11           |

| 5.3.1.1             | New Instructions                                  |                |

| 5.3.1.1.1           | Low-Power Stop (LPSTOP)                           | 5-11           |

| 5.3.1.1.2           | Table Lookup and Interpolation (TBL)              |                |

| 5.3.1.2             | Unimplemented Instructions                        | 5-12           |

| 5.3.2               | Instruction Format and Notation                   | 5-12           |

| 5.3.3               | Instruction Summary                               | 5-15           |

| 5.3.3.1             | Condition Code Register                           | 5-20           |

| 5.3.3.2             | Data Movement Instructions                        |                |

| 5.3.3.3             | Integer Arithmetic Operations                     | 5-22           |

| 5.3.3.4             | Logic Instructions                                |                |

| 5.3.3.5             | Shift and Rotate Instructions                     | 5-24           |

| 5.3.3.6             | Bit Manipulation Instructions                     |                |

| 5.3.3.7             | Binary-Coded Decimal (BCD) Instructions           |                |

| 5.3.3.8             | Program Control Instructions                      | 5-26           |

| 5.3.3.9             | System Control Instructions                       | 5-27           |

| 5.3.3.10            | Condition Tests                                   |                |

| 5.3.4               | Using the TBL Instructions                        |                |

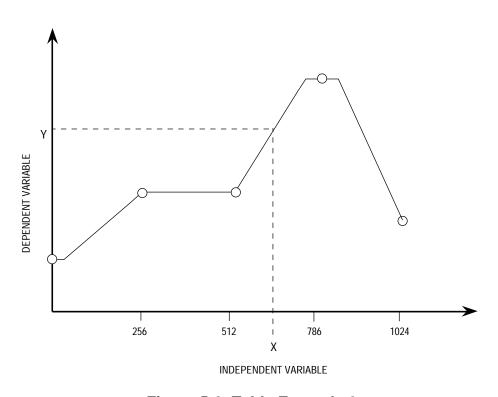

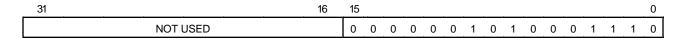

| 5.3.4.1             | Table Example 1: Standard Usage                   |                |

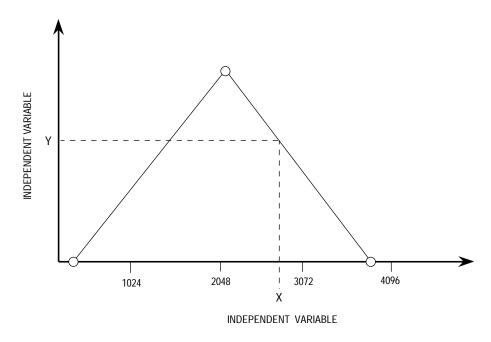

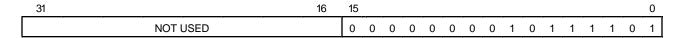

| 5.3.4.2             | Table Example 2: Compressed Table                 |                |

| 5.3.4.3             | Table Example 3: 8-Bit Independent Variable       |                |

| 5.3.4.4             | Table Example 4: Maintaining Precision            |                |

| 5.3.4.5             | Table Example 5: Surface Interpolations           | 5-36           |

| 5.3.5               | Nested Subroutine Calls                           |                |

| 5.3.6               | Pipeline Synchronization with the NOP Instruction | 5-36           |

| 5.4                 | Processing States                                 | 5-36           |

| 5.4.1               | State Transitions                                 | 5-37           |

| 5.4.2               | Privilege Levels                                  | 5-37           |

| 5.4.2.1             | Supervisor Privilege Level                        | 5-37           |

| 5.4.2.2             | User Privilege Level                              | 5-39           |

| Paragraph<br>Number | Title                                                | Page<br>Number |

|---------------------|------------------------------------------------------|----------------|

| 5.4.2.3             | Changing Privilege Level                             | 5-39           |

| 5.5                 | Exception Processing                                 | 5-39           |

| 5.5.1               | Exception Vectors                                    | 5-40           |

| 5.5.1.1             | Types of Exceptions                                  | 5-41           |

| 5.5.1.2             | Exception Processing Sequence                        | 5-41           |

| 5.5.1.3             | Exception Stack Frame                                | 5-42           |

| 5.5.1.4             | Multiple Exceptions                                  | 5-42           |

| 5.5.2               | Processing of Specific Exceptions                    | 5-44           |

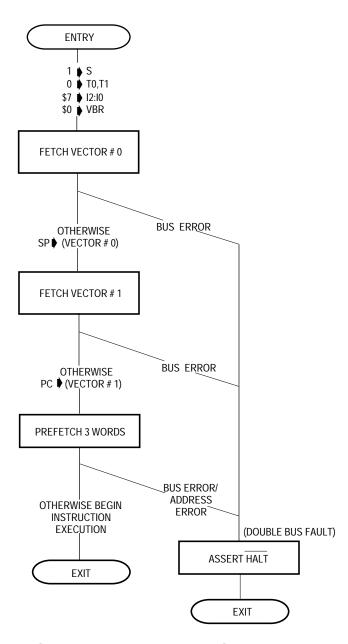

| 5.5.2.1             | Reset                                                | 5-44           |

| 5.5.2.2             | Bus Error                                            | 5-46           |

| 5.5.2.3             | Address Error                                        | 5-46           |

| 5.5.2.4             | Instruction Traps                                    | 5-47           |

| 5.5.2.5             | Software Breakpoints                                 | 5-47           |

| 5.5.2.6             | Hardware Breakpoints                                 | 5-48           |

| 5.5.2.7             | Format Error                                         | 5-48           |

| 5.5.2.8             | Illegal or Unimplemented Instructions                | 5-48           |

| 5.5.2.9             | Privilege Violations                                 | 5-49           |

| 5.5.2.10            | Tracing                                              | 5-50           |

| 5.5.2.11            | Interrupts                                           |                |

| 5.5.2.12            | Return from Exception                                | 5-52           |

| 5.5.3               | Fault Recovery                                       | 5-53           |

| 5.5.3.1             | Types of Faults                                      |                |

| 5.5.3.1.1           | Type I—Released Write Faults                         |                |

| 5.5.3.1.2           | Type II—Prefetch, Operand, RMW, and MOVEP Faults     |                |

| 5.5.3.1.3           | Type III—Faults During MOVEM Operand Transfer        |                |

| 5.5.3.1.4           | Type IV—Faults During Exception Processing           |                |

| 5.5.3.2             | Correcting a Fault                                   |                |

| 5.5.3.2.1           | Type I—Completing Released Writes via Software       |                |

| 5.5.3.2.2           | Type I—Completing Released Writes via RTE            | 5-57           |

| 5.5.3.2.3           | Type II—Correcting Faults via RTE                    |                |

| 5.5.3.2.4           | Type III—Correcting Faults via Software              |                |

| 5.5.3.2.5           | Type III—Correcting Faults by Conversion and Restart |                |

| 5.5.3.2.6           | Type III—Correcting Faults via RTE                   |                |

| 5.5.3.2.7           | Type IV—Correcting Faults via Software               |                |

| 5.5.4               | CPU32 Stack Frames                                   |                |

| 5.5.4.1             | Four-Word Stack Frame                                |                |

| 5.5.4.2             | Six-Word Stack Frame                                 |                |

| 5.5.4.3             | Bus Error Stack Frame                                | 5-60           |

| 5.6                 | Development Support                                  |                |

| 5.6.1               | CPU32 Integrated Development Support                 |                |

| 5.6.1.1             | Background Debug Mode (BDM) Overview                 | 5-64           |

| 5.6.1.2             | Deterministic Opcode Tracking Overview               | 5-64           |

| Paragraph  |                                           | Page   |

|------------|-------------------------------------------|--------|

| Number     | Title                                     | Number |

| 5.6.1.3    | On-Chip Hardware Breakpoint Overview      |        |

| 5.6.2      | Background Debug Mode                     |        |

| 5.6.2.1    | Enabling BDM                              |        |

| 5.6.2.2    | BDM Sources                               |        |

| 5.6.2.2.1  | External BKPT Signal                      |        |

| 5.6.2.2.2  | BGND Instruction                          | 5-66   |

| 5.6.2.2.3  | Double Bus Fault                          | 5-66   |

| 5.6.2.3    | Entering BDM                              | 5-66   |

| 5.6.2.4    | Command Execution                         | 5-67   |

| 5.6.2.5    | BDM Registers                             | 5-67   |

| 5.6.2.5.1  | Fault Address Register (FAR)              | 5-67   |

| 5.6.2.5.2  | Return Program Counter (RPC)              | 5-67   |

| 5.6.2.5.3  | Current Instruction Program Counter (PCC) | 5-67   |

| 5.6.2.6    | Returning from BDM                        |        |

| 5.6.2.7    | Serial Interface                          |        |

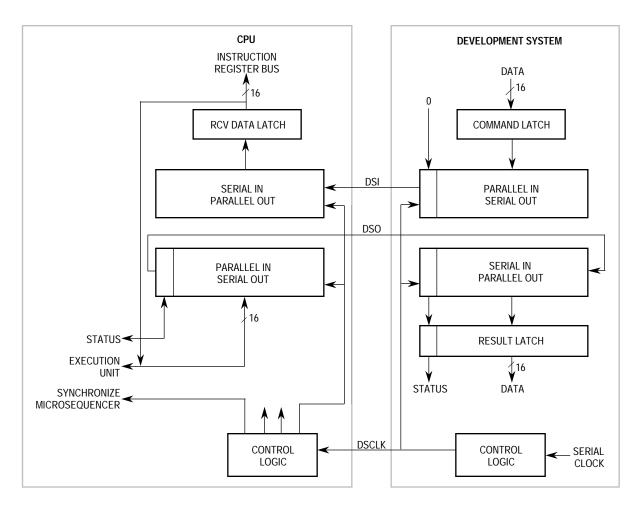

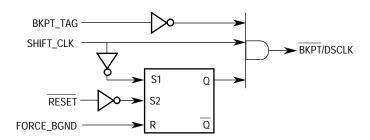

| 5.6.2.7.1  | CPU Serial Logic                          | 5-69   |

| 5.6.2.7.2  | Development System Serial Logic           |        |

| 5.6.2.8    | Command Set                               |        |

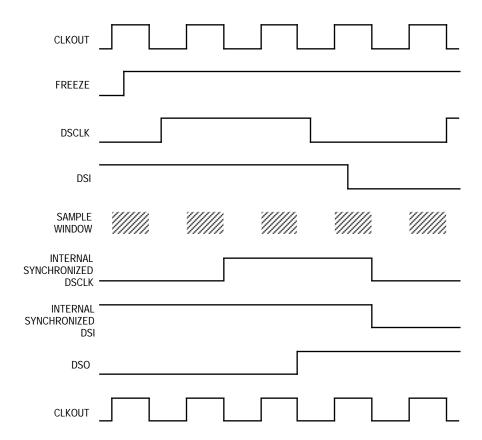

| 5.6.2.8.1  | Command Format                            | 5-73   |

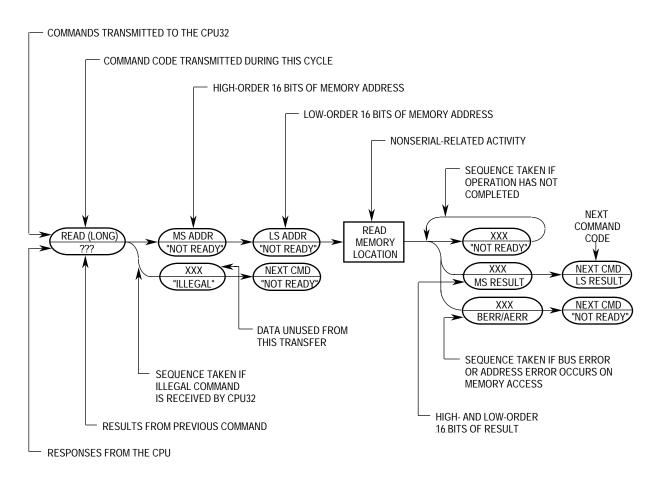

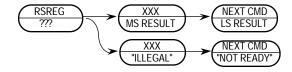

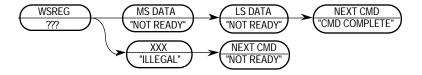

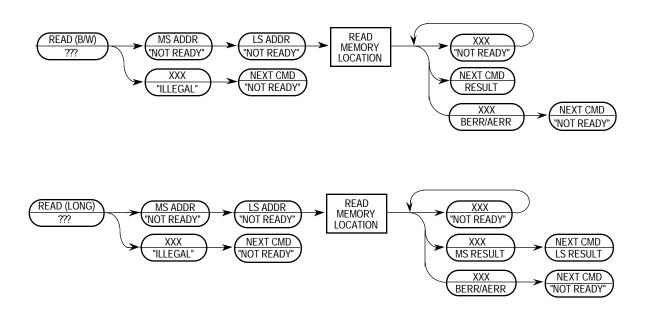

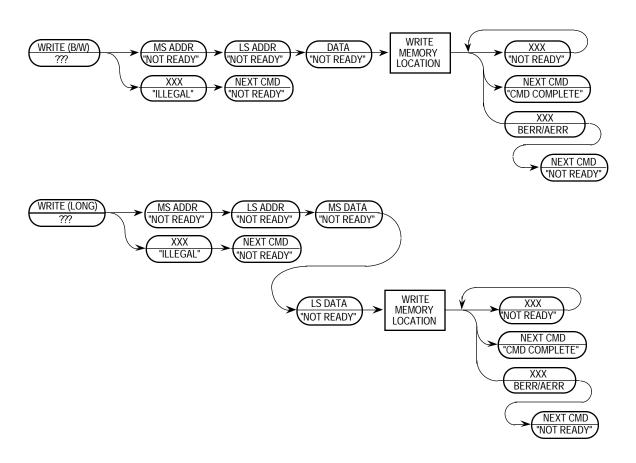

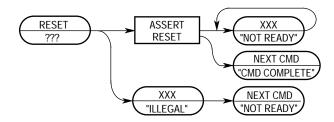

| 5.6.2.8.2  | Command Sequence Diagram                  | 5-74   |

| 5.6.2.8.3  | Command Set Summary                       |        |

| 5.6.2.8.4  | Read A/D Register (RAREG/RDREG)           | 5-76   |

| 5.6.2.8.5  | Write A/D Register (WAREG/WDREG)          |        |

| 5.6.2.8.6  | Read System Register (RSREG)              |        |

| 5.6.2.8.7  | Write System Register (WSREG)             |        |

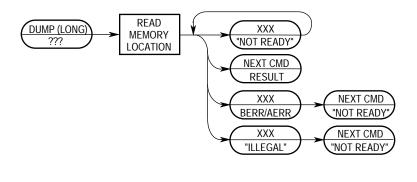

| 5.6.2.8.8  | Read Memory Location (READ)               | 5-79   |

| 5.6.2.8.9  | Write Memory Location (WRITE)             |        |

| 5.6.2.8.10 | Dump Memory Block (DUMP)                  | 5-80   |

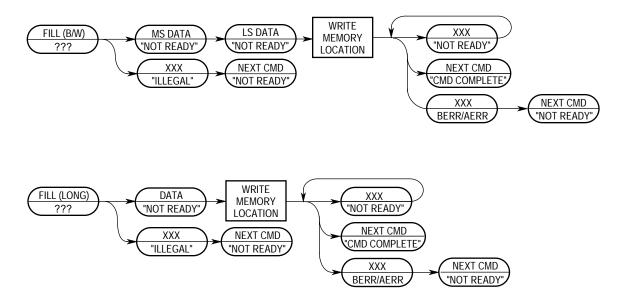

| 5.6.2.8.11 | Fill Memory Block (FILL)                  | 5-82   |

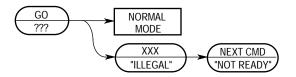

| 5.6.2.8.12 | Resume Execution (GO)                     | 5-83   |

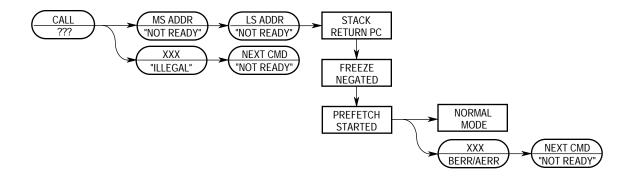

| 5.6.2.8.13 | Call User Code (CALL)                     | 5-83   |

| 5.6.2.8.14 | Reset Peripherals (RST)                   | 5-85   |

| 5.6.2.8.15 | No Operation (NOP)                        |        |

| 5.6.2.8.16 | Future Commands                           |        |

| 5.6.3      | Deterministic Opcode Tracking             |        |

| 5.6.3.1    | Instruction Fetch (IFETCH)                | 5-86   |

| 5.6.3.2    | Instruction Pipe (IPIPE)                  | 5-87   |

| 5.6.3.3    | Opcode Tracking during Loop Mode          | 5-88   |

| 5.7        | Instruction Execution Timing              |        |

| 5.7.1      | Resource Scheduling                       | 5-88   |

| 5.7.1.1    | Microsequencer                            | 5-89   |

| 5.7.1.2    | Instruction Pipeline                      |        |

| Paragraph<br>Number | Title                                          | Page<br>Number |

|---------------------|------------------------------------------------|----------------|

| 5.7.1.3             | Bus Controller Resources                       | 5-89           |

| 5.7.1.3.1           | Prefetch Controller                            |                |

| 5.7.1.3.2           | Write Pending Buffer                           |                |

| 5.7.1.3.3           | Microbus Controller                            |                |

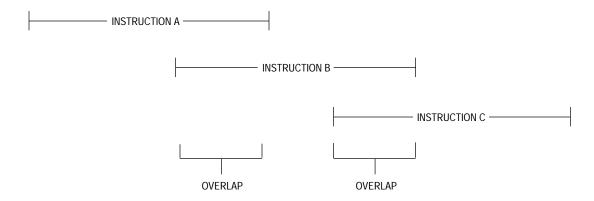

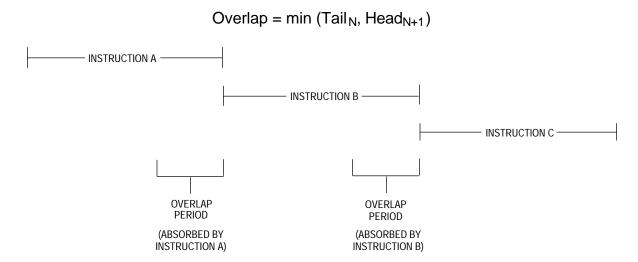

| 5.7.1.4             | Instruction Execution Overlap                  |                |

| 5.7.1.5             | Effects of Wait States                         |                |

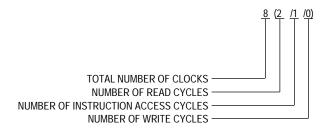

| 5.7.1.6             | Instruction Execution Time Calculation         | 5-92           |

| 5.7.1.7             | Effects of Negative Tails                      | 5-93           |

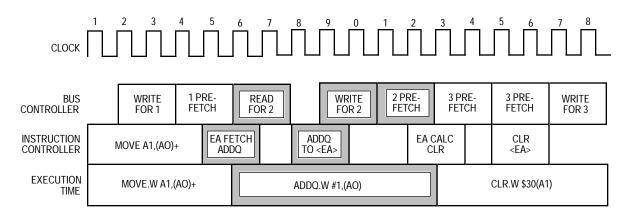

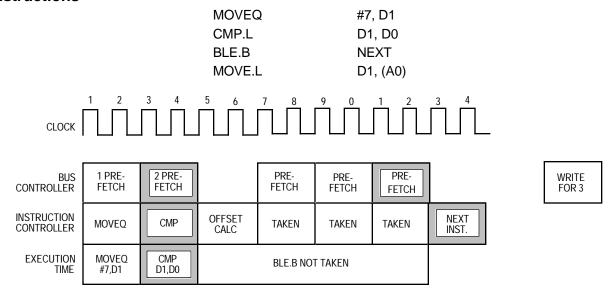

| 5.7.2               | Instruction Stream Timing Examples             | 5-94           |

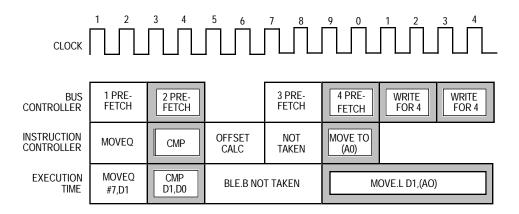

| 5.7.2.1             | Timing Example 1—Execution Overlap             | 5-94           |

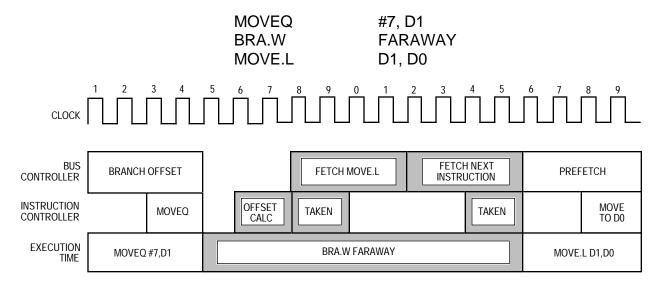

| 5.7.2.2             | Timing Example 2—Branch Instructions           | 5-95           |

| 5.7.2.3             | Timing Example 3—Negative Tails                | 5-96           |

| 5.7.3               | Instruction Timing Tables                      | 5-97           |

| 5.7.3.1             | Fetch Effective Address                        | 5-99           |

| 5.7.3.2             | Calculate Effective Address                    |                |

| 5.7.3.3             | MOVE Instruction                               |                |

| 5.7.3.4             | Special-Purpose MOVE Instruction               |                |

| 5.7.3.5             | Arithmetic/Logic Instructions                  |                |

| 5.7.3.6             | Immediate Arithmetic/Logic Instructions        |                |

| 5.7.3.7             | Binary-Coded Decimal and Extended Instructions |                |

| 5.7.3.8             | Single Operand Instructions                    |                |

| 5.7.3.9             | Shift/Rotate Instructions                      |                |

| 5.7.3.10            | Bit Manipulation Instructions                  |                |

| 5.7.3.11            | Conditional Branch Instructions                |                |

| 5.7.3.12            | Control Instructions                           |                |

| 5.7.3.13            | Exception-Related Instructions and Operations  |                |

| 5.7.3.14            | Save and Restore Operations                    | 5-111          |

|                     | Section 6                                      |                |

|                     | DMA Controller Module                          |                |

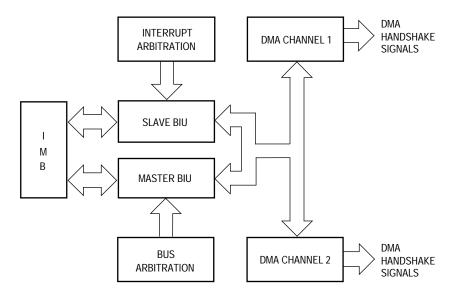

| 6.1                 | DMA Module Overview                            |                |

| 6.2                 | DMA Module Signal Definitions                  |                |

| 6.2.1               | DMA Request (DREQ≈)                            |                |

| 6.2.2               | DMA Acknowledge (DACK≈)                        |                |

| 6.2.3               | DMA Done (DONE≈)                               |                |

| 6.3                 | Transfer Request Generation                    |                |

| 6.3.1               | Internal Request Generation                    |                |

| 6.3.1.1             | Internal Request, Maximum Rate                 |                |

| 6.3.1.2             | Internal Request, Limited Rate                 |                |

| 6.3.2               | External Request Generation                    |                |

| 6.3.2.1             | External Burst Mode                            | 6-5            |

| Paragraph<br>Number                     | Title                                        | Page<br>Number    |

|-----------------------------------------|----------------------------------------------|-------------------|

| 6.3.2.2                                 | External Cycle Steal Mode                    | 6-5               |

| 6.4                                     | Data Transfer Modes                          | 6-6               |

| 6.4.1                                   | Single-Address Mode                          | 6-6               |

| 6.4.1.1                                 | Single-Address Read                          |                   |

| 6.4.1.2                                 | Single-Address Write                         | 6-9               |

| 6.4.2                                   | Dual-Address Mode                            |                   |

| 6.4.2.1                                 | Dual-Address Read                            | 6-12              |

| 6.4.2.2                                 | Dual-Address Write                           | 6-14              |

| 6.5                                     | Bus Arbitration                              | 6-18              |

| 6.6                                     | DMA Channel Operation                        | 6-18              |

| 6.6.1                                   | Channel Initialization and Startup           | 6-18              |

| 6.6.2                                   | Data Transfers                               |                   |

| 6.6.2.1                                 | Internal Request Transfers                   | 6-19              |

| 6.6.2.2                                 | External Request Transfers                   |                   |

| 6.6.3                                   | Channel Termination                          |                   |

| 6.6.3.1                                 | Channel Termination                          | 6-20              |

| 6.6.3.2                                 | Interrupt Operation                          | 6-20              |

| 6.6.3.3                                 | Fast Termination Option                      |                   |

| 6.7                                     | Register Description                         | 6-22              |

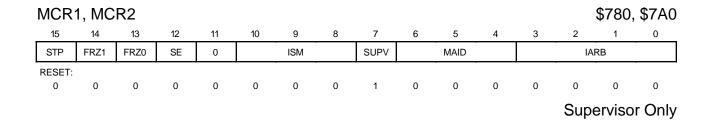

| 6.7.1                                   | Module Configuration Register (MCR)          | 6-23              |

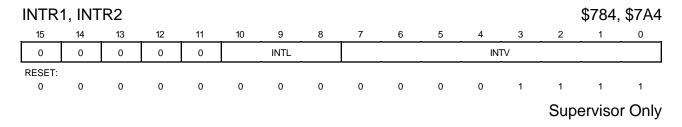

| 6.7.2                                   | Interrupt Register (INTR)                    |                   |

| 6.7.3                                   | Channel Control Register (CCR)               | 6-26              |

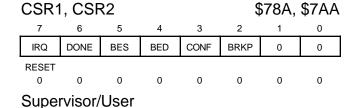

| 6.7.4                                   | Channel Status Register (CSR)                | 6-30              |

| 6.7.5                                   | Function Code Register (FCR)                 |                   |

| 6.7.6                                   | Source Address Register (SAR)                | 6-33              |

| 6.7.7                                   | Destination Address Register (DAR)           | 6-33              |

| 6.7.8                                   | Byte Transfer Counter Register (BTC)         |                   |

| 6.8                                     | Data Packing                                 |                   |

| 6.9                                     | DMA Channel Initialization Sequence          | 6-36              |

| 6.9.1                                   | DMA Channel Configuration                    | 6-36              |

| 6.9.1.1                                 | DMA Channel Operation in Single-Address Mode |                   |

| 6.9.1.2                                 | DMA Channel Operation in Dual-Address Mode   | 6-37              |

| 6.9.2                                   | DMA Channel Example Configuration Code       | 6-38              |

|                                         | Section 7<br>Serial Module                   |                   |

| 7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4 | Module Overview                              | 7-3<br>7-3<br>7-3 |

|                                         |                                              |                   |

| Paragraph<br>Number | Title                                           | Page<br>Number |

|---------------------|-------------------------------------------------|----------------|

| 7.1.5               | Comparison of Serial Module to MC68681          | 7-4            |

| 7.2                 | Serial Module Signal Definitions                |                |

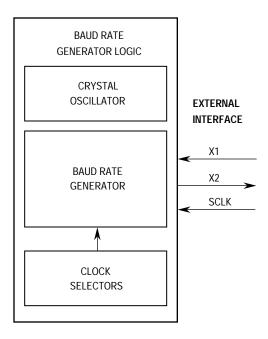

| 7.2.1               | Crystal Input or External Clock (X1)            | 7-5            |

| 7.2.2               | Crystal Output (X2)                             | 7-5            |

| 7.2.3               | External Input (SCLK)                           |                |

| 7.2.4               | Channel A Transmitter Serial Data Output (TxDA) | 7-6            |

| 7.2.5               | Channel A Receiver Serial Data Input (RxDA)     |                |

| 7.2.6               | Channel B Transmitter Serial Data Output (TxDB) | 7-6            |

| 7.2.7               | Channel B Receiver Serial Data Input (RxDB)     | 7-6            |

| 7.2.8               | Channel A Request-To-Send (RTSA)                | 7-6            |

| 7.2.8.1             | RTSA                                            | 7-6            |

| 7.2.8.2             | OP0                                             |                |

| 7.2.9               | Channel B Request-To-Send (RTSB)                | 7-6            |

| 7.2.9.1             | RTSB                                            |                |

| 7.2.9.2             | OP1                                             |                |

| 7.2.10              | Channel A Clear-To-Send (CTSA)                  |                |

| 7.2.11              | Channel B Clear-To-Send (CTSB)                  |                |

| 7.2.12              | Channel A Transmitter Ready (T≈RDYA)            |                |

| 7.2.12.1            | T≈RDYA                                          |                |

| 7.2.12.2            | OP6                                             |                |

| 7.2.13              | Channel A Receiver Ready (R≈RDYA)               |                |

| 7.2.13.1            | R≈RDYA                                          |                |

| 7.2.13.2            | FFULLA                                          |                |

| 7.2.13.3            | OP4                                             |                |

| 7.3                 | Operation                                       |                |

| 7.3.1               | Baud Rate Generator                             |                |

| 7.3.2               | Transmitter and Receiver Operating Modes        |                |

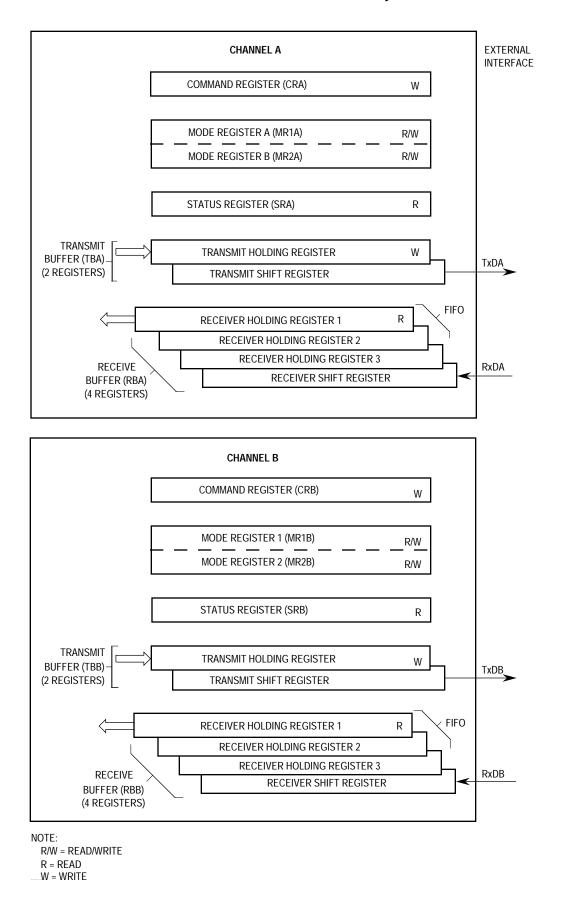

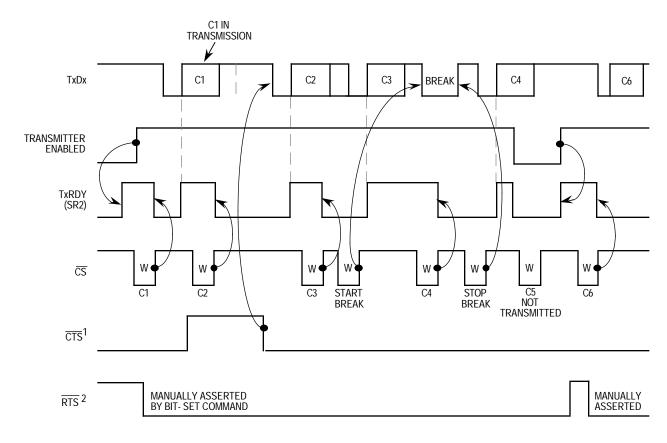

| 7.3.2.1             | Transmitter                                     |                |

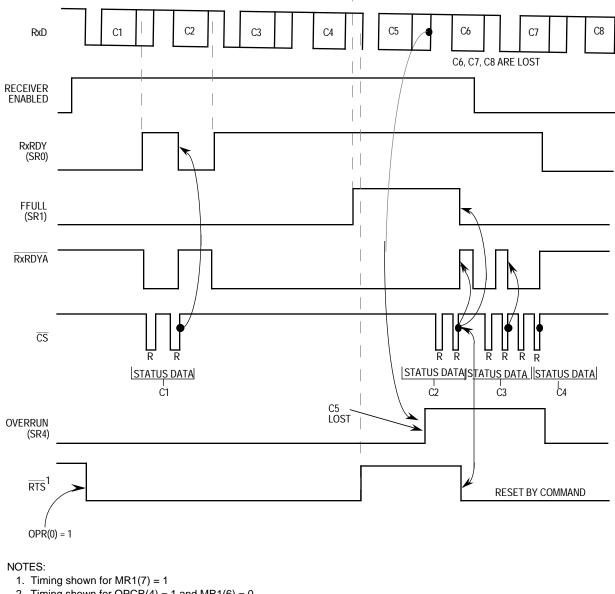

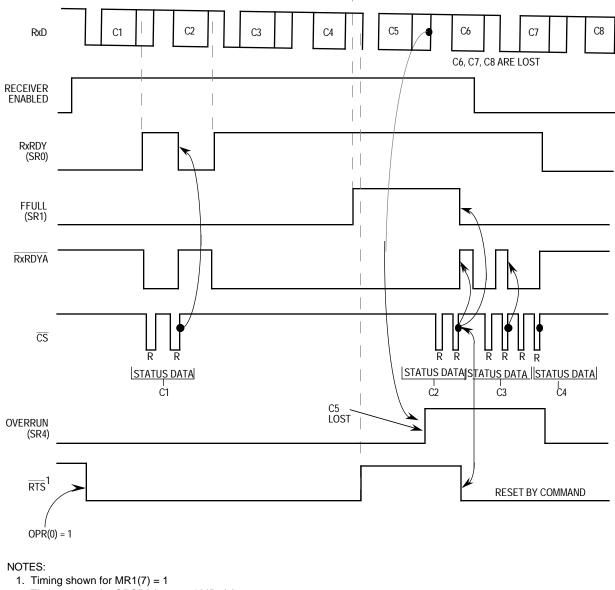

| 7.3.2.2             | Receiver                                        |                |

| 7.3.2.3             | FIFO Stack                                      |                |

| 7.3.3               | Looping Modes                                   |                |

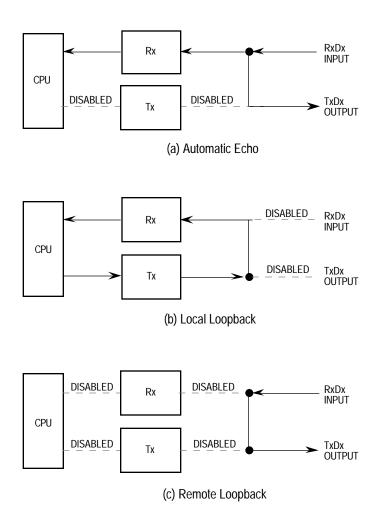

| 7.3.3.1             | Automatic Echo Mode                             |                |

| 7.3.3.2             | Local Loopback Mode                             |                |

| 7.3.3.3             | Remote Loopback Mode                            |                |

| 7.3.4               | Multidrop Mode                                  |                |

| 7.3.5               | Bus Operation                                   |                |

| 7.3.5.1             | Read Cycles                                     |                |

| 7.3.5.2             | Write Cycles                                    |                |

| 7.3.5.3             | Interrupt Acknowledge Cycles                    |                |

| 7.4                 | Register Description and Programming            |                |

| 7.4.1               | Register Description                            |                |

| 7.4.1.1             | Module Configuration Register (MCR)             | 7-19           |

| Paragraph<br>Number | Title                                    | Page<br>Number |

|---------------------|------------------------------------------|----------------|

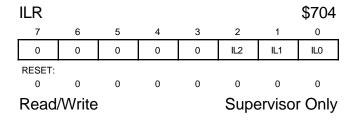

| 7.4.1.2             | Interrupt Level Register (ILR)           |                |

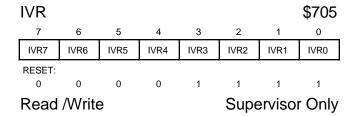

| 7.4.1.3             | Interrupt Vector Register (IVR)          |                |

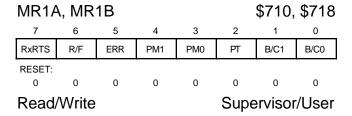

| 7.4.1.4             | Mode Register 1 (MR1)                    |                |

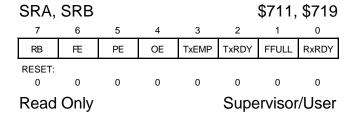

| 7.4.1.5             | Status Register (SR)                     |                |

| 7.4.1.6             | Clock-Select Register (CSR)              |                |

| 7.4.1.7             | Command Register (CR)                    |                |

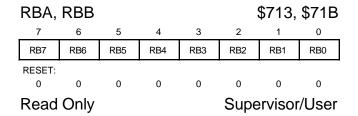

| 7.4.1.8             | Receiver Buffer (RB)                     |                |

| 7.4.1.9             | Transmitter Buffer (TB)                  |                |

| 7.4.1.10            | Input Port Change Register (IPCR)        |                |

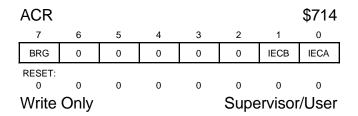

| 7.4.1.11            | Auxiliary Control Register (ACR)         |                |

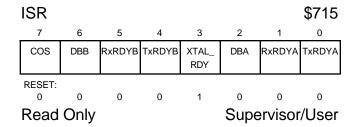

| 7.4.1.12            | Interrupt Status Register (ISR)          |                |

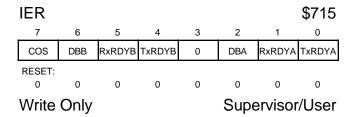

| 7.4.1.13            | Interrupt Enable Register (IER)          |                |

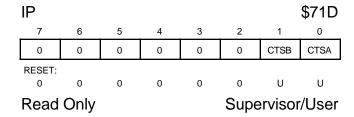

| 7.4.1.14            | Input Port (IP)                          | 7-35           |

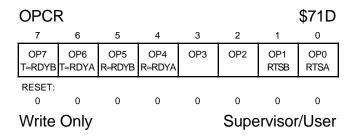

| 7.4.1.15            | Output Port Control Register (OPCR)      |                |

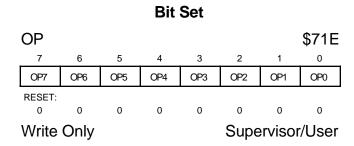

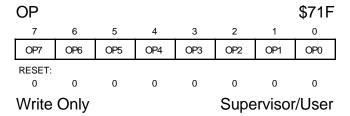

| 7.4.1.16            | Output Port Data Register (OP)           |                |

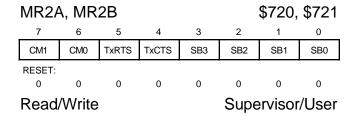

| 7.4.1.17            | Mode Register 2 (MR2)                    |                |

| 7.4.2               | Programming                              |                |

| 7.4.2.1             | Serial Module Initialization             |                |

| 7.4.2.2             | I/O Driver Example                       |                |

| 7.4.2.3             | Interrupt Handling                       |                |

| 7.5                 | Serial Module Initialization Sequence    |                |

| 7.5.1               | Serial Module Configuration              |                |

| 7.5.2               | Serial Module Example Configuration Code | 7-47           |

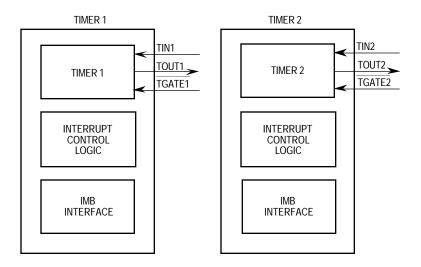

|                     | Section 8 Timer Modules                  |                |

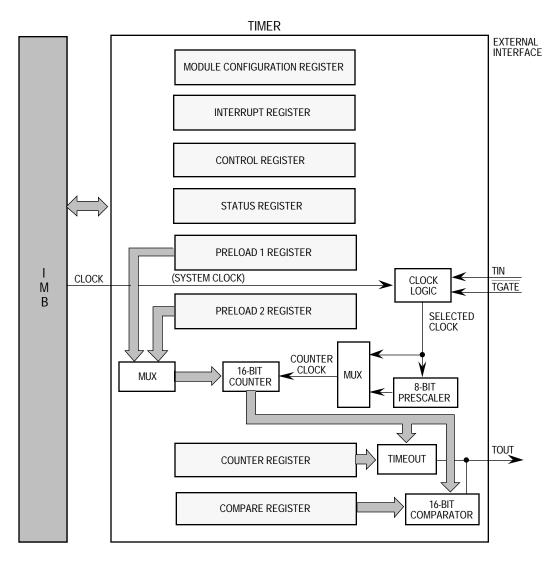

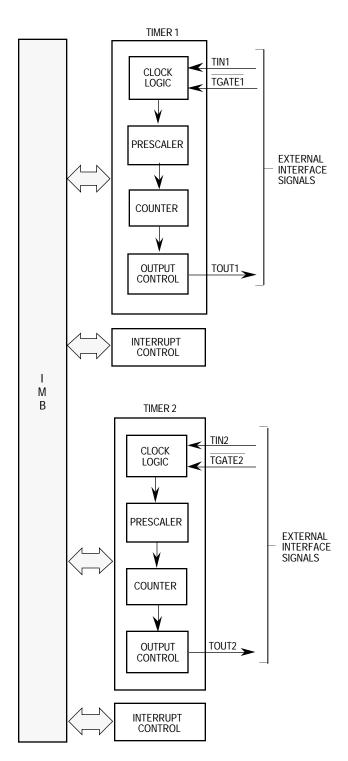

| 8.1                 | Module Overview                          | 8-1            |

| 8.1.1               | Timer and Counter Functions              |                |

| 8.1.1.1             | Prescaler and Counter                    |                |

| 8.1.1.2             | Timeout Detection                        |                |

| 8.1.1.3             | Comparator                               |                |

| 8.1.1.4             | Clock Selection Logic                    |                |

| 8.1.2               | Internal Control Logic                   |                |

| 8.1.3               | Interrupt Control Logic                  |                |

| 8.2                 | Timer Modules Signal Definitions         |                |

| 8.2.1               | Timer Input (TIN1, TIN2)                 |                |

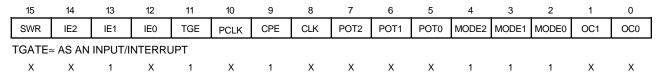

| 8.2.2               | Timer Gate (TGATE1, TGATE2)              | 8-6            |

| 8.2.3               | Timer Output (TOUT1, TOUT2)              | 8-6            |

| 8.3                 | Operating Modes                          |                |

| 8.3.1               | Input Capture/Output Compare             |                |

| 8.3.2               | Square-Wave Generator                    |                |

| Paragraph<br>Number | Title                                                             | Page<br>Number |

|---------------------|-------------------------------------------------------------------|----------------|

| 8.3.3               | Variable Duty-Cycle Square-Wave Generator                         | 8-9            |

| 8.3.4               | Variable-Width Single-Shot Pulse Generator                        |                |

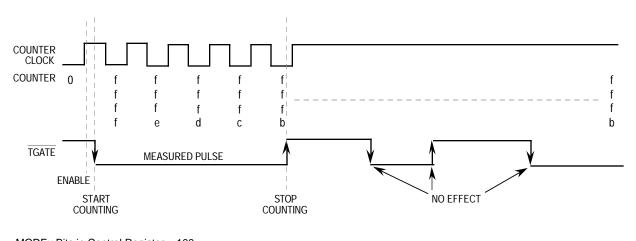

| 8.3.5               | Pulse-Width Measurement                                           | 8-12           |

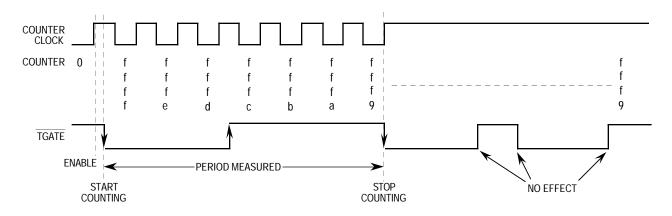

| 8.3.6               | Period Measurement                                                | 8-13           |

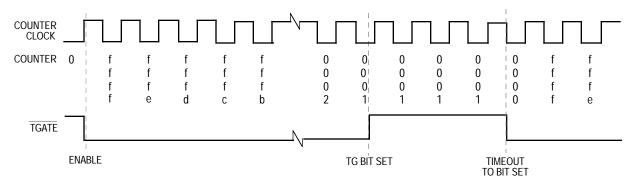

| 8.3.7               | Event Count                                                       | 8-14           |

| 8.3.8               | Timer Bypass                                                      | 8-16           |

| 8.3.9               | Bus Operation                                                     | 8-17           |

| 8.3.9.1             | Read Cycles                                                       | 8-17           |

| 8.3.9.2             | Write Cycles                                                      |                |

| 8.3.9.3             | Interrupt Acknowledge Cycles                                      |                |

| 8.4                 | Register Description                                              | 8-17           |

| 8.4.1               | Module Configuration Register (MCR)                               |                |

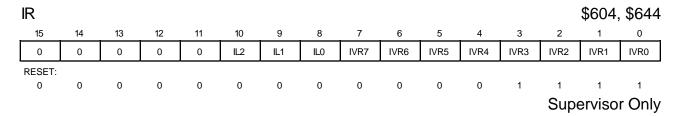

| 8.4.2               | Interrupt Register (IR)                                           |                |

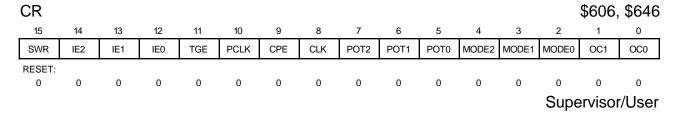

| 8.4.3               | Control Register (CR)                                             |                |

| 8.4.4               | Status Register (SR)                                              |                |

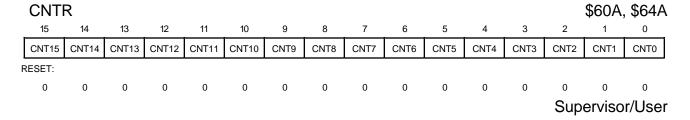

| 8.4.5               | Counter Register (CNTR)                                           |                |

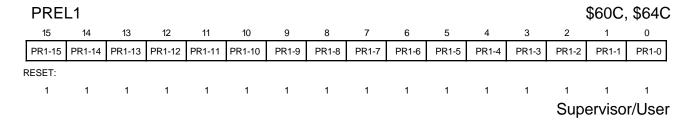

| 8.4.6               | Preload 1 Register (PREL1)                                        |                |

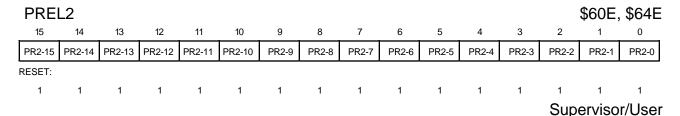

| 8.4.7               | Preload 2 Register (PREL2)                                        |                |

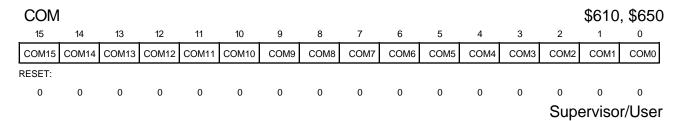

| 8.4.8               | Compare Register (COM)                                            |                |

| 8.5                 | Timer Module Initialization Sequence                              |                |

| 8.5.1<br>8.5.2      | Timer Module ConfigurationTimer Module Example Configuration Code |                |

| 0.0.2               | Section 9 IEEE 1149.1 Test Access Port                            |                |

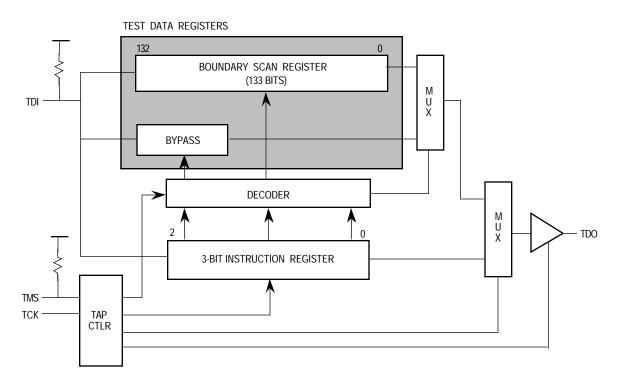

| 9.1                 | Overview                                                          | 0.1            |

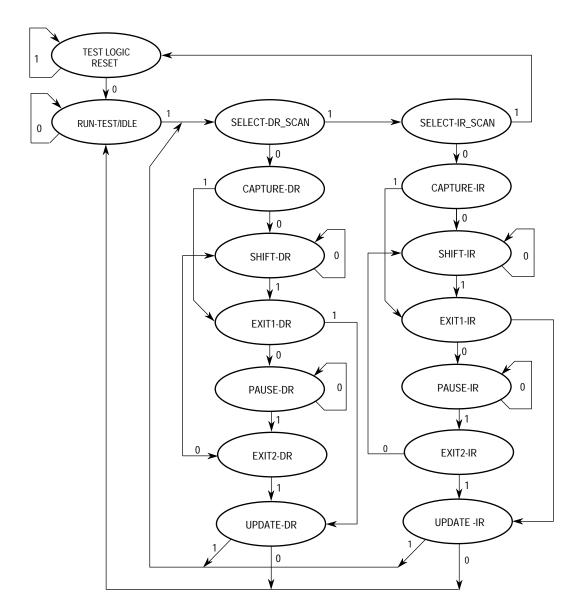

| 9.1                 | TAP Controller                                                    |                |

| 9.2                 | Boundary Scan Register                                            |                |

| 9.4                 | Instruction Register                                              |                |

| 9.4.1               | EXTEST (000)                                                      |                |

| 9.4.2               | SAMPLE/PRELOAD (001)                                              |                |

| 9.4.3               | BYPASS (X1X, 101)                                                 |                |

| 9.4.4               | HI-Z (100)                                                        |                |

| 9.5                 | MC68340 Restrictions                                              |                |

| 9.6                 | Non-IEEE 1149.1 Operation                                         |                |

|                     | Section 10 Applications                                           |                |

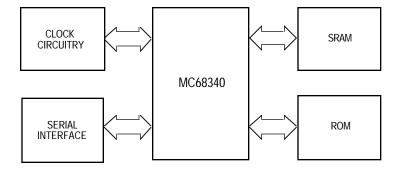

| 10.1                | Minimum System Configuration                                      |                |

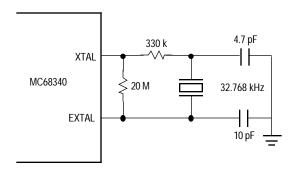

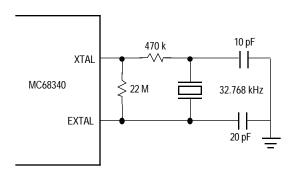

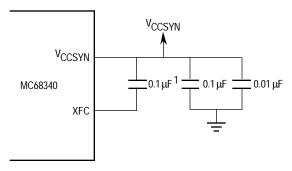

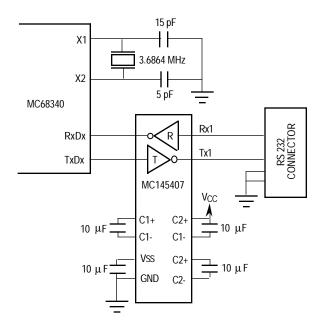

| 10.1.1              | Processor Clock Circuitry                                         | 10-1           |

# **TABLE OF CONTENTS (Concluded)**

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

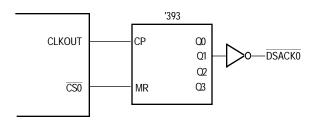

| 10.1.2              | Reset Circuitry                                    | 10-3           |

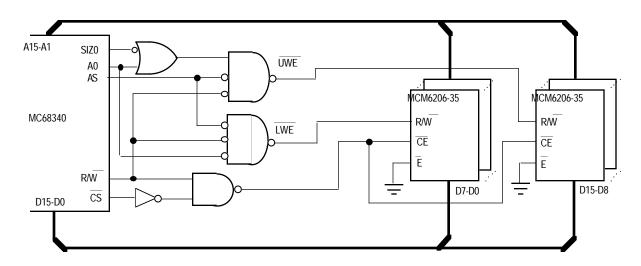

| 10.1.3              | SRAM Interface                                     |                |

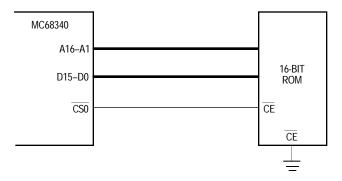

| 10.1.4              | ROM Interface                                      | 10-4           |

| 10.1.5              | Serial Interface                                   | 10-4           |

| 10.2                | Memory Interface Information                       | 10-5           |

| 10.2.1              | Using an 8-Bit Boot ROM                            | 10-5           |

| 10.2.2              | Access Time Calculations                           |                |

| 10.2.3              | Calculating Frequency-Adjusted Output              | 10-7           |

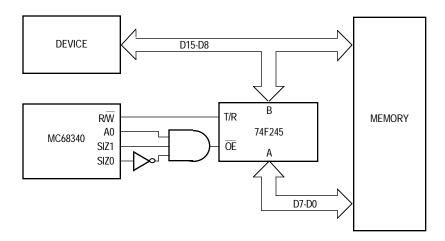

| 10.2.4              | Interfacing an 8-Bit Device to 16-Bit Memory Using | 40.40          |

| 10.0                | Single-Address DMA Mode                            |                |

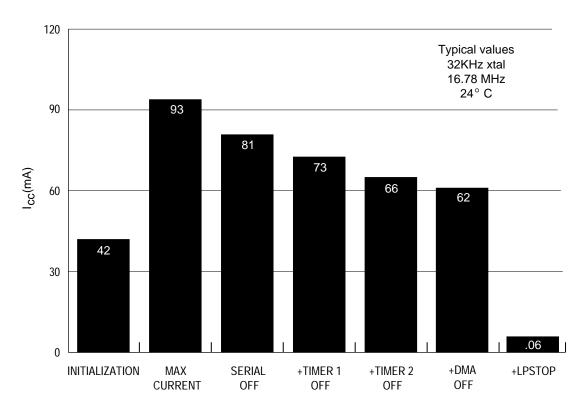

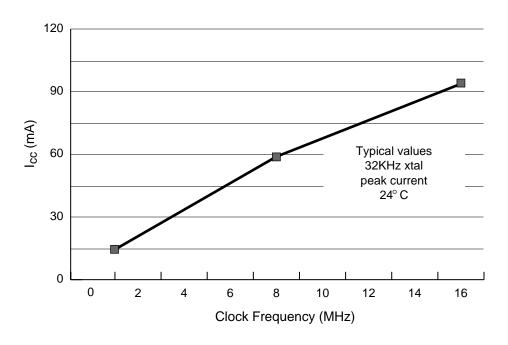

| 10.3                | Power Consumption Considerations                   |                |

| 10.3.1              | MC68340 Power Reduction at 5V                      |                |

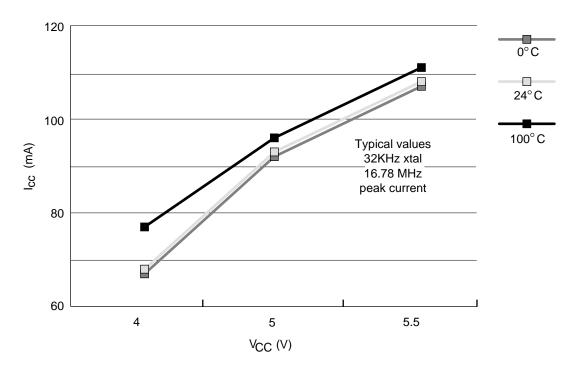

| 10.3.2              | MC68340V (3.3 V)                                   | 10-13          |

|                     | Section 11                                         |                |

| 44.4                | Electrical Characteristics                         | 44.4           |

| 11.1                | Maximum Rating                                     |                |

| 11.2                | Thermal Characteristics                            |                |

| 11.3                | Power Considerations                               |                |

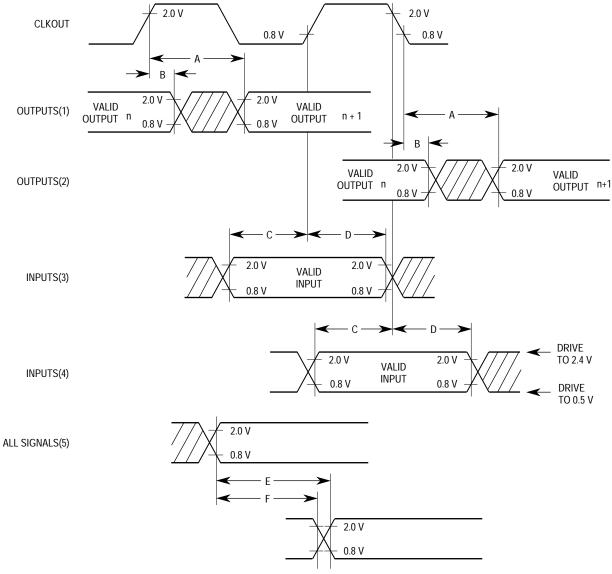

| 11.4                | AC Electrical Specification Definitions            |                |

| 11.5                | DC Electrical Specifications                       |                |

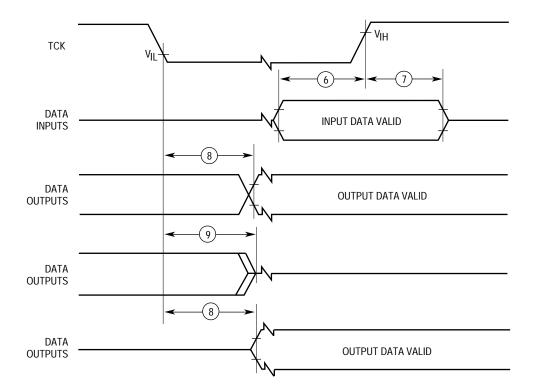

| 11.6                | AC Electrical Specifications Control Timing        | 11-0           |

| 11.7                | AC Timing Specifications                           |                |

| 11.8                | DMA Module AC Electrical Specifications            |                |

| 11.9                | Timer Module Electrical Specifications             |                |

| 11.10               | Serial Module Electrical Specifications            |                |

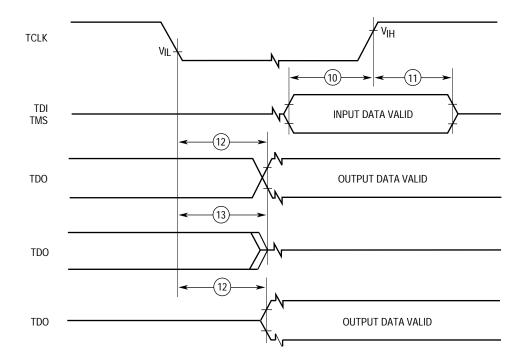

| 11.11               | IEEE 1149.1 Electrical Specifications              | 11-25          |

|                     | Section 12                                         |                |

|                     | Ordering Information and Mechanical Data           |                |

| 12.1                | Standard MC68340 Ordering Information              | 12-1           |

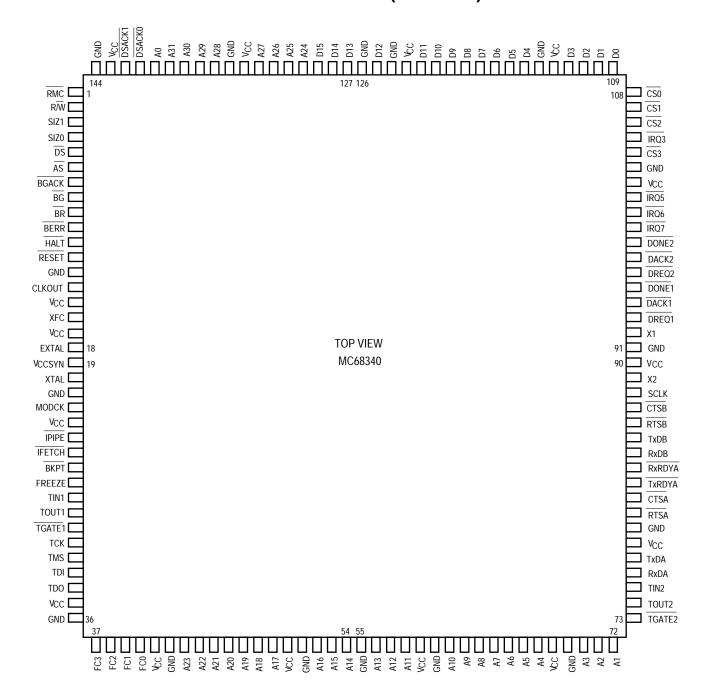

| 12.2                | Pin Assignment                                     | 12-2           |

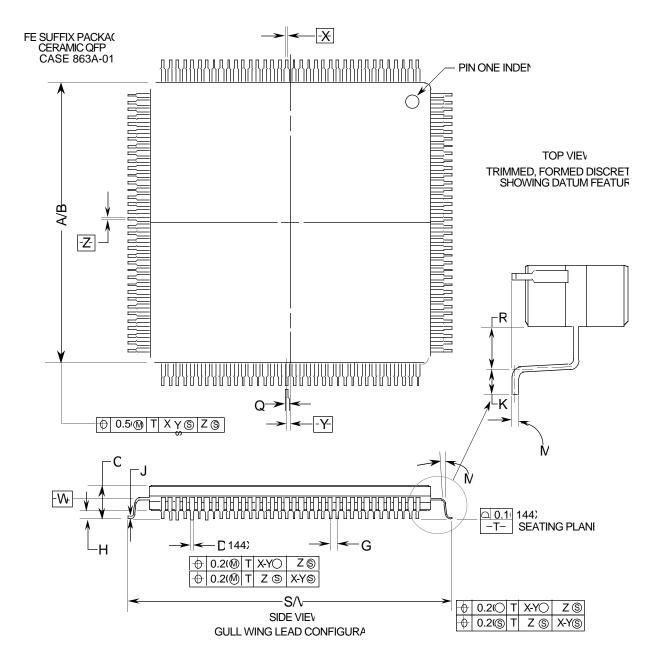

| 12.2.1              | 144-Lead Ceramic Quad Flat Pack (FE Suffix)        | 12-2           |

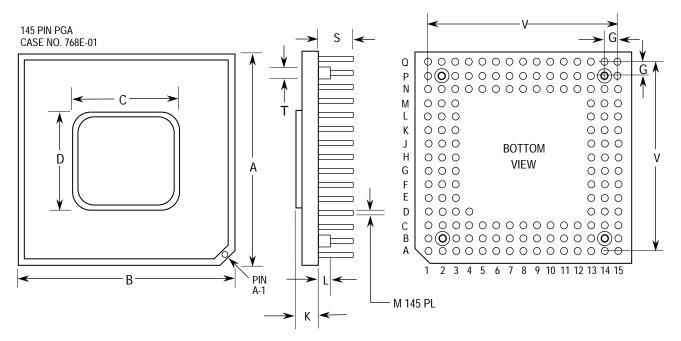

| 12.2.2              | 145-Lead Plastic Pin Grid Array (RP Suffix)        | 12-4           |

| 12.3                | Package Dimensions                                 |                |

| 12.3.1              | FE Suffix                                          | 12-6           |

| 12.3.2              | RP Suffix                                          | 12-7           |

Index

## LIST OF ILLUSTRATIONS

| Figu<br>Numl                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page<br>Numbe                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

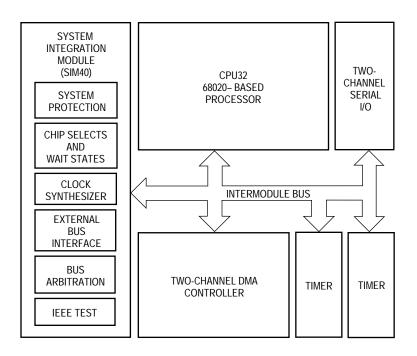

| 1-1                                                                                                                                                                                                                 | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-1                                                                                                     |

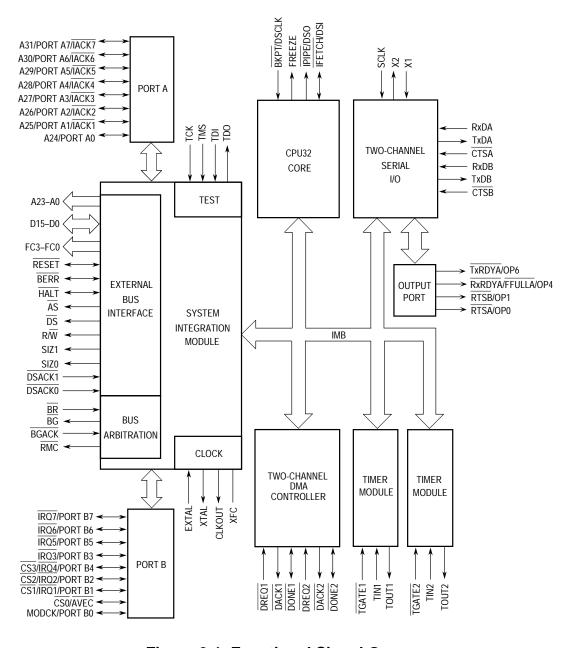

| 2-1                                                                                                                                                                                                                 | Functional Signal Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-1                                                                                                     |

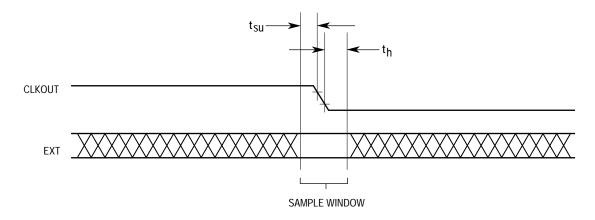

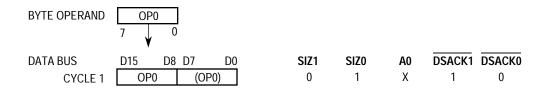

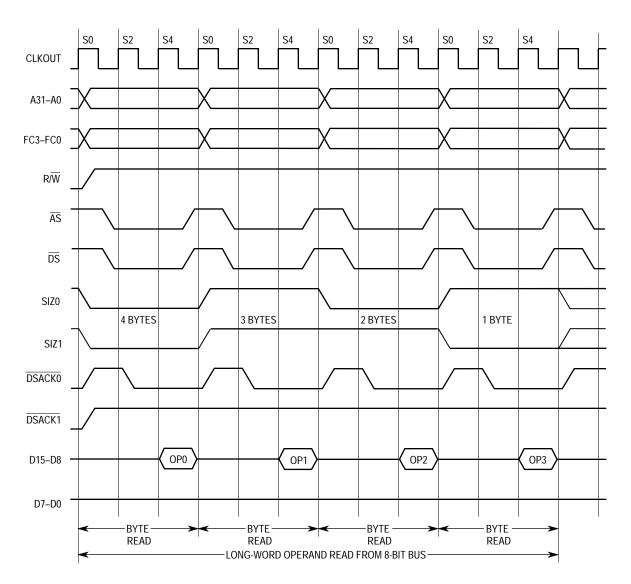

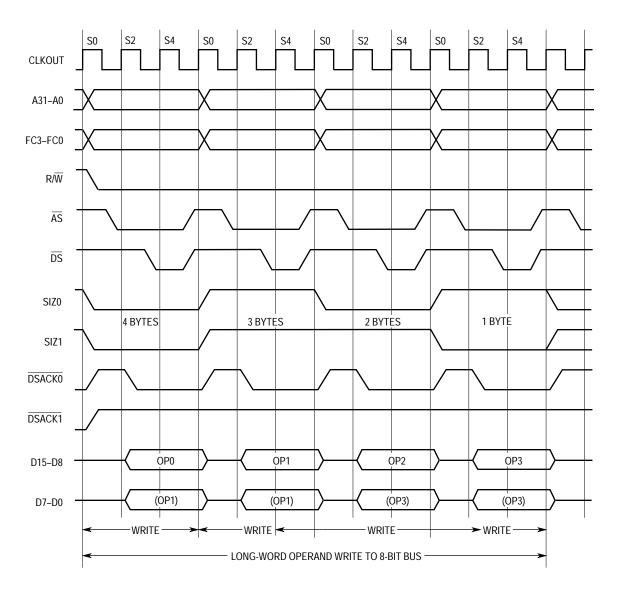

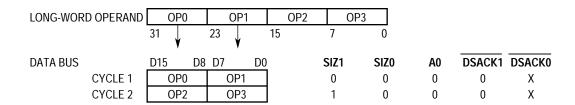

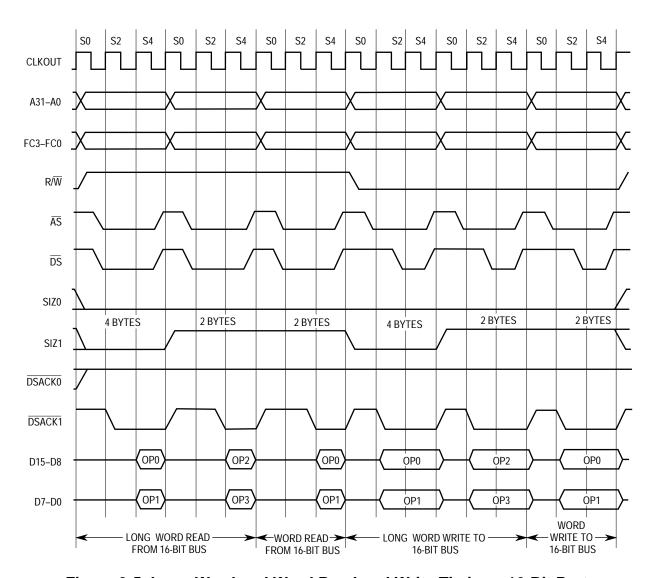

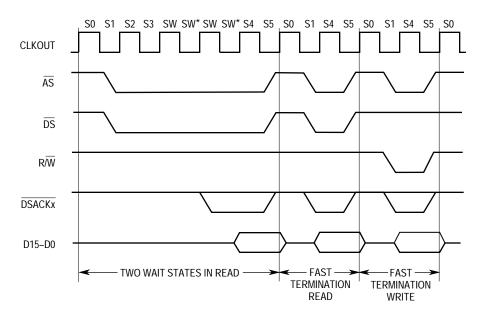

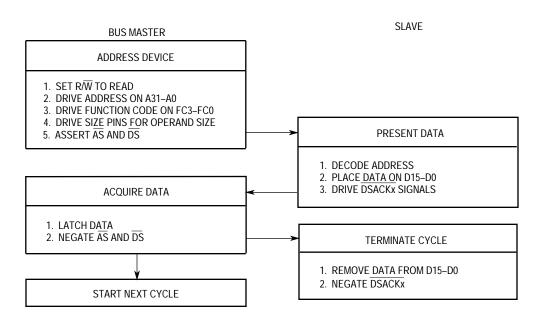

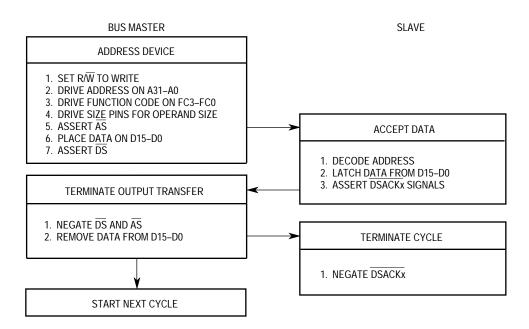

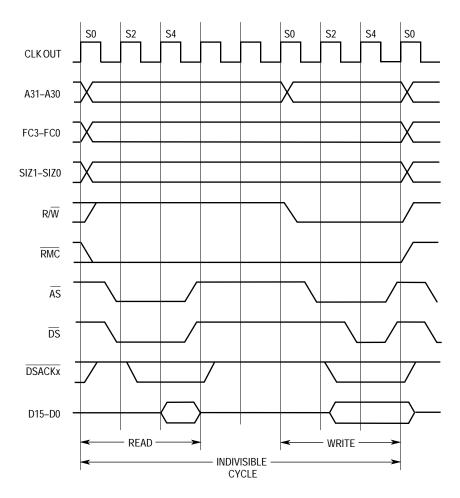

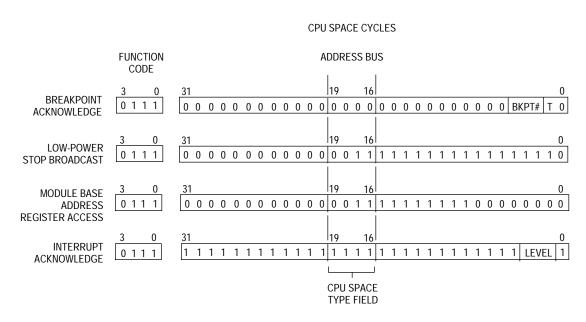

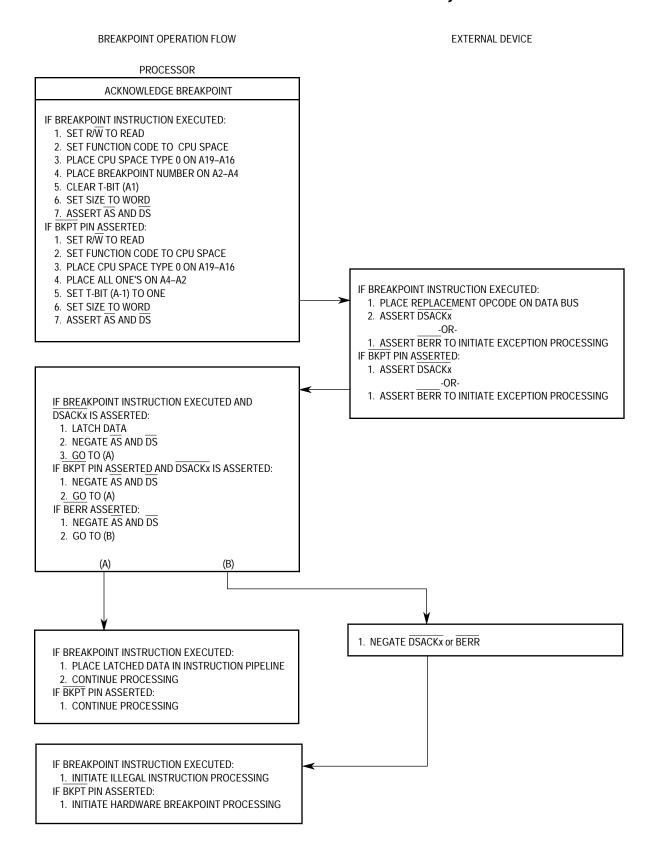

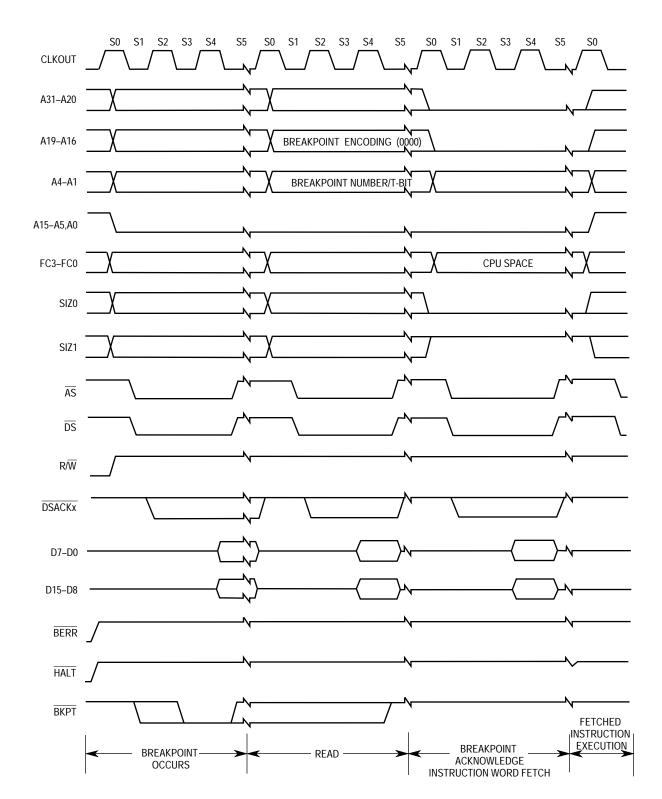

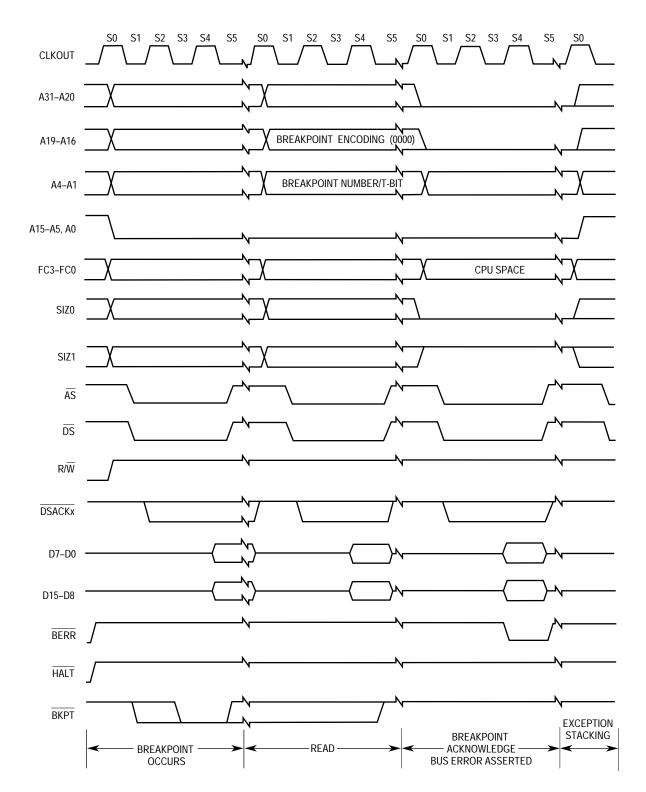

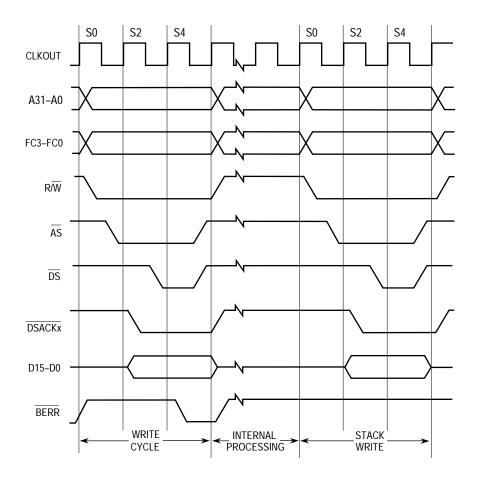

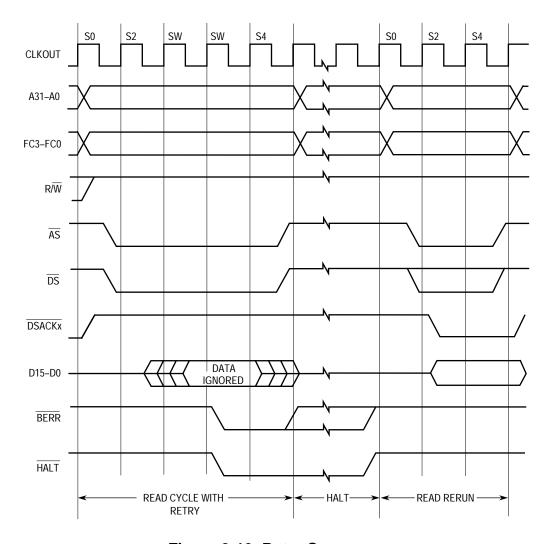

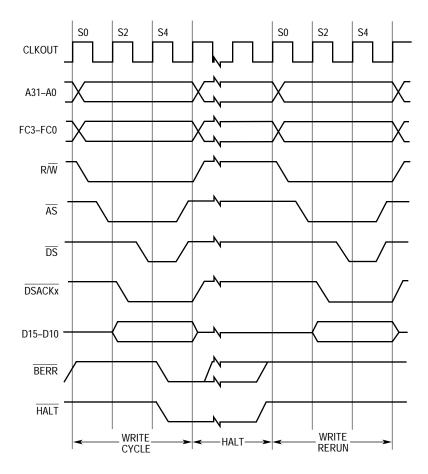

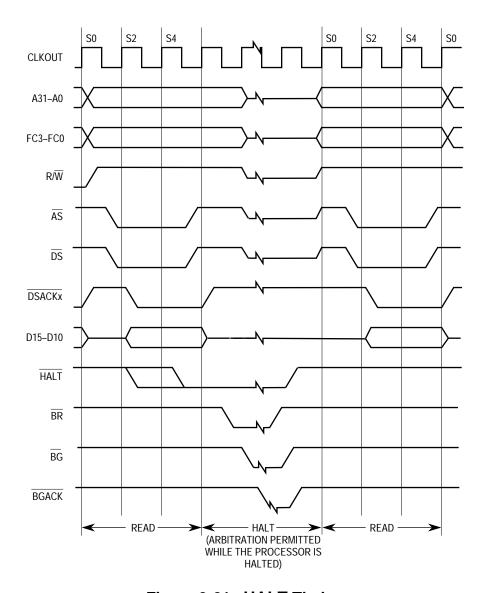

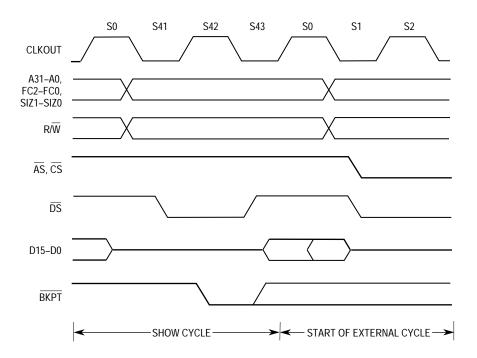

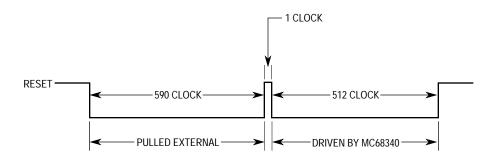

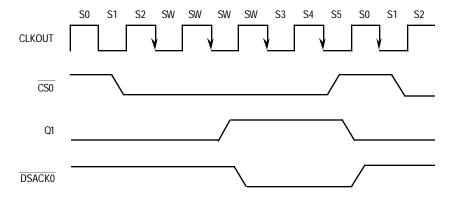

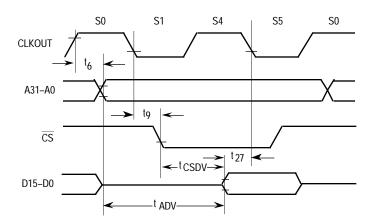

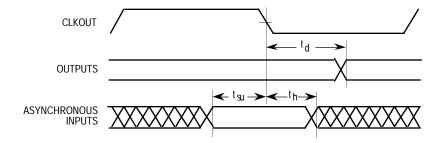

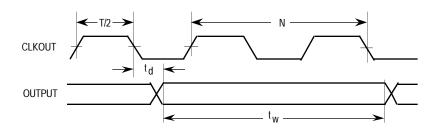

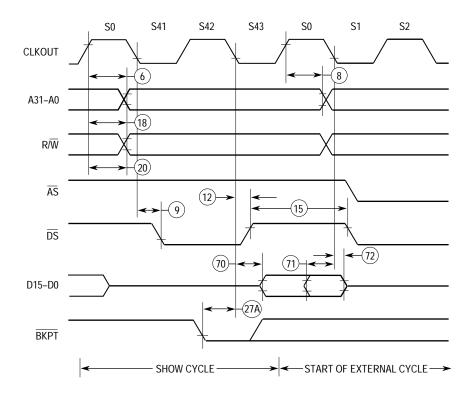

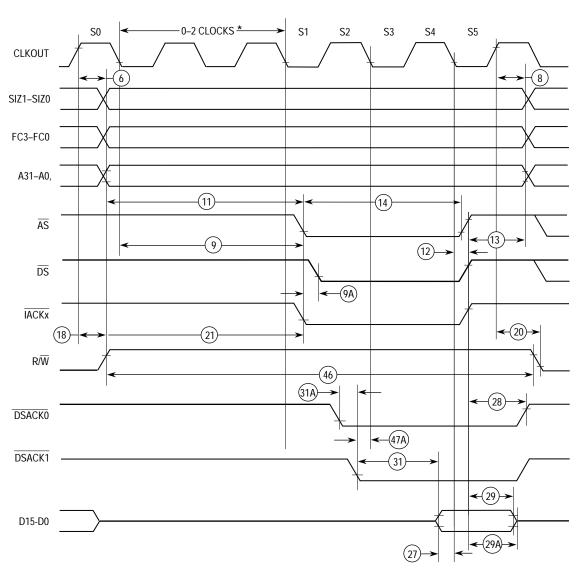

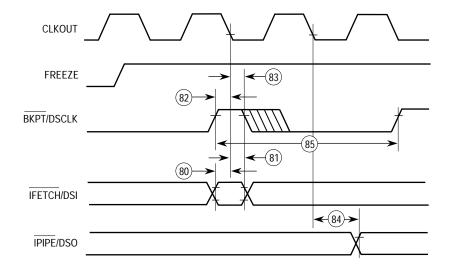

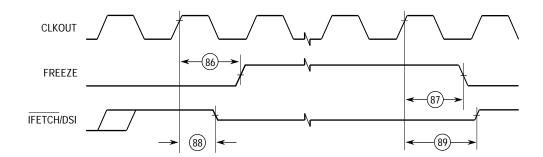

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18<br>3-19<br>3-20<br>3-21<br>3-22<br>3-23<br>3-24<br>3-25<br>3-26<br>3-27<br>3-28 | Input Sample Window  MC68340 Interface to Various Port Sizes  Long-Word Operand Read Timing from 8-Bit Port  Long-Word Operand Write Timing to 8-Bit Port  Long-Word and Word Read and Write Timing—16-Bit Port  Fast Termination Timing  Word Read Cycle Flowchart  Word Write Cycle Flowchart  Read-Modify-Write Cycle Timing  CPU Space Address Encoding  Breakpoint Operation Flowchart  Breakpoint Acknowledge Cycle Timing (Opcode Returned)  Breakpoint Acknowledge Cycle Flowchart  Interrupt Acknowledge Cycle Flowchart  Interrupt Acknowledge Cycle Flowchart  Interrupt Acknowledge Cycle Timing  Autovector Operation Timing  Bus Error without DSACK≈  Late Bus Error with DSACK≈  Retry Sequence  Late Retry Sequence  HALT Timing  Bus Arbitration Flowchart for Single Request  Bus Arbitration Timing Diagram—Idle Bus Case  Bus Arbitration Timing Diagram—Active Bus Case  Bus Arbitration State Diagram  Show Cycle Timing Diagram  Timing for External Devices Driving RESET  Power-Up Reset Timing Diagram | 3-73-113-123-133-153-163-183-193-213-243-253-263-283-283-373-353-363-373-383-393-413-423-423-453-463-47 |

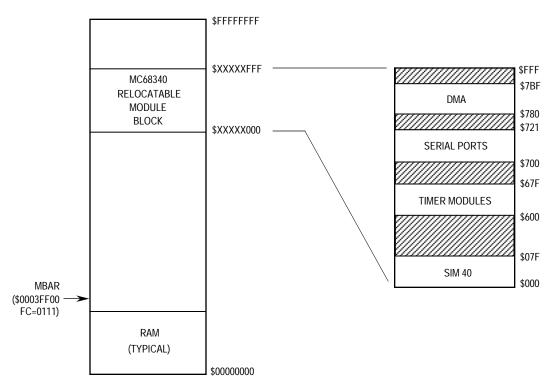

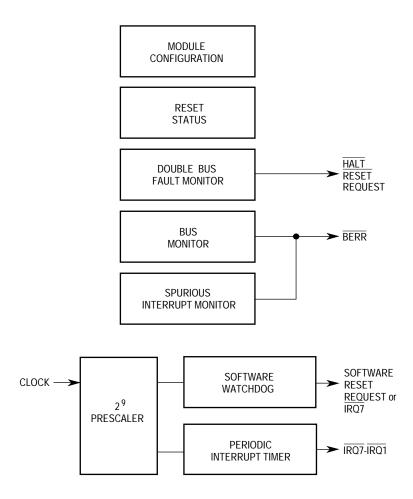

| 4-1<br>4-2<br>4-3<br>4-4                                                                                                                                                                                            | SIM40 Module Register Block  System Configuration and Protection Function  Software Watchdog Block Diagram  Clock Block Diagram for Crystal Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-5<br>4-7                                                                                              |

# LIST OF ILLUSTRATIONS (Continued)

| Figu<br>Numb |                                                       | Page<br>Number |

|--------------|-------------------------------------------------------|----------------|

| 4-5          | MC68340 Crystal Oscillator                            | 4-10           |

| 4-6          | Clock Block Diagram for External Oscillator Operation |                |

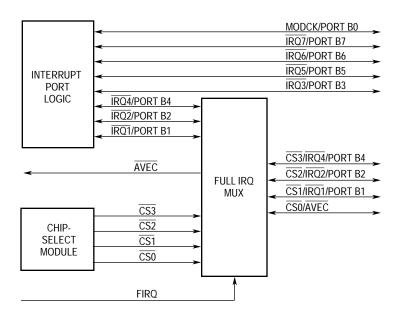

| 4-7          | Full Interrupt Request Multiplexer                    |                |

| 4-8          | SIM40 Programming Model                               |                |

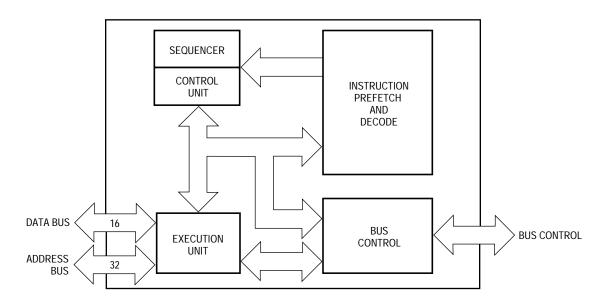

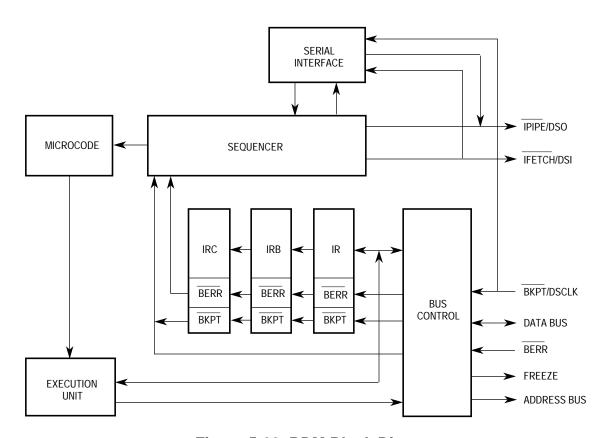

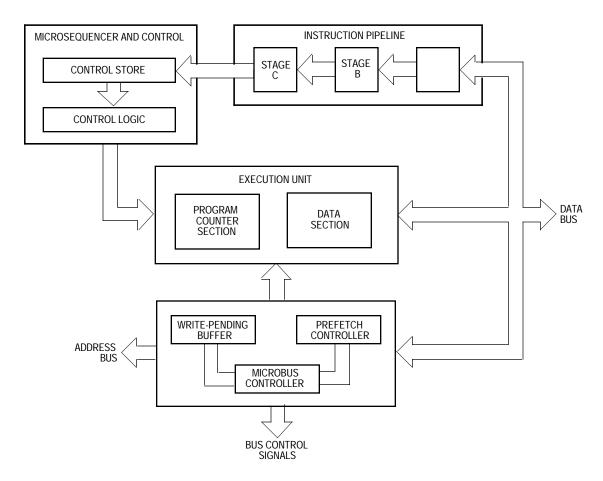

| 5-1          | CPU32 Block Diagram                                   | 5-3            |

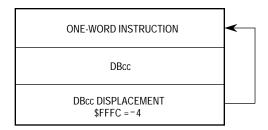

| 5-2          | Loop Mode Instruction Sequence                        | 5-3            |

| 5-3          | User Programming Model                                |                |

| 5-4          | Supervisor Programming Model Supplement               | 5-9            |

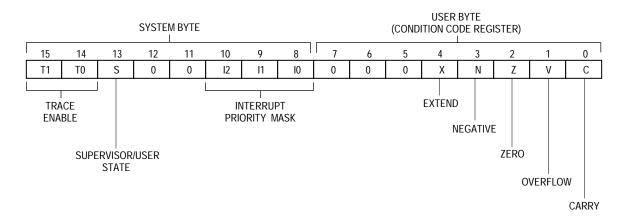

| 5-5          | Status Register                                       |                |

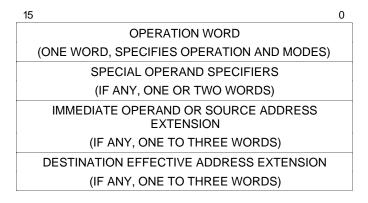

| 5-6          | Instruction Word General Format                       | 5-12           |

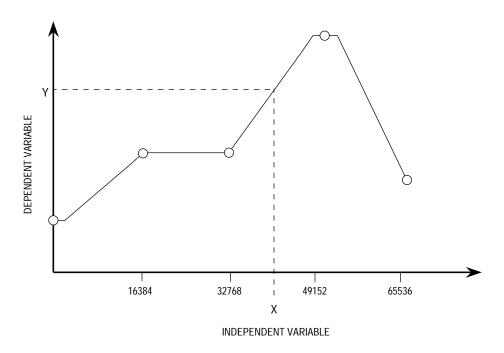

| 5-7          | Table Example 1                                       | 5-30           |

| 5-8          | Table Example 2                                       | 5-31           |

| 5-9          | Table Example 3                                       | 5-33           |

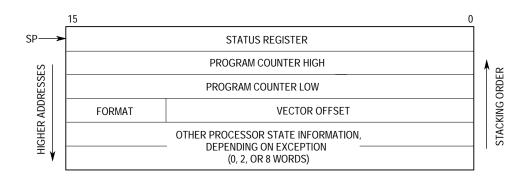

| 5-10         | Exception Stack Frame                                 |                |

| 5-11         | Reset Operation Flowchart                             | 5-45           |

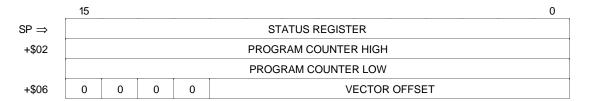

| 5-12         | Format \$0—Four-Word Stack Frame                      | 5-60           |

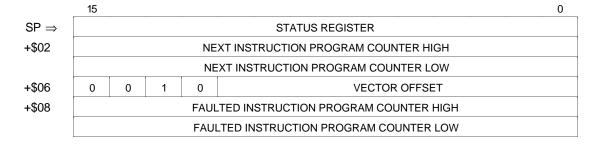

| 5-13         | Format \$2—Six-Word Stack Frame                       | 5-60           |

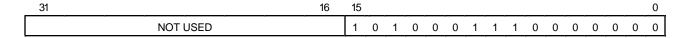

| 5-14         | Internal Transfer Count Register                      | 5-61           |

| 5-15         | Format \$C—BERR Stack for Prefetches and Operands     | 5-62           |

| 5-16         | Format \$C—BERR Stack on MOVEM Operand                | 5-62           |

| 5-17         | Format \$C—Four- and Six-Word BERR Stack              | 5-63           |

| 5-18         | In-Circuit Emulator Configuration                     | 5-64           |

| 5-19         | Bus State Analyzer Configuration                      | 5-64           |

| 5-20         | BDM Block Diagram                                     | 5-65           |

| 5-21         | BDM Command Execution Flowchart                       | 5-68           |

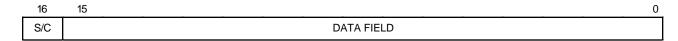

| 5-22         | Debug Serial I/O Block Diagram                        | 5-70           |

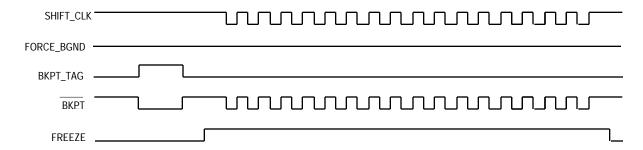

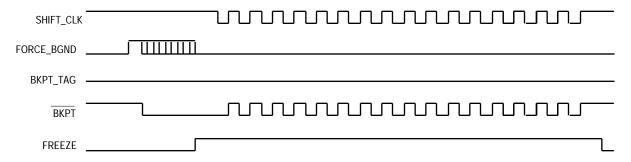

| 5-23         | Serial Interface Timing Diagram                       | 5-71           |

| 5-24         | BKPT Timing for Single Bus Cycle                      | 5-72           |

| 5-25         | BKPT Timing for Forcing BDM                           | 5-72           |

| 5-26         | BKPT/DSCLK Logic Diagram                              |                |

| 5-27         | Command-Sequence Diagram                              | 5-75           |

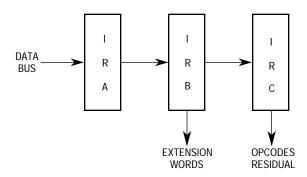

| 5-28         | Functional Model of Instruction Pipeline              | 5-87           |

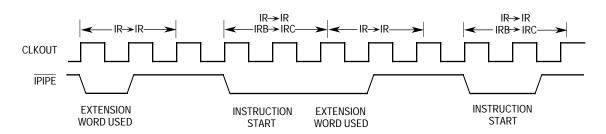

| 5-29         | Instruction Pipeline Timing Diagram                   | 5-88           |

| 5-30         | Block Diagram of Independent Resources                | 5-90           |

| 5-31         | Simultaneous Instruction Execution                    | 5-91           |

| 5-32         | Attributed Instruction Times                          | 5-92           |

| 5-33         | Example 1—Instruction Stream                          | 5-95           |

| 5-34         | Example 2—Branch Taken                                |                |

| 5-35         | Example 2—Branch Not Taken                            |                |

| 5-36         | Example 3—Branch Negative Tail                        |                |

# LIST OF ILLUSTRATIONS (Continued)

| Figui<br>Numb |                                                                   | Page<br>Number |

|---------------|-------------------------------------------------------------------|----------------|

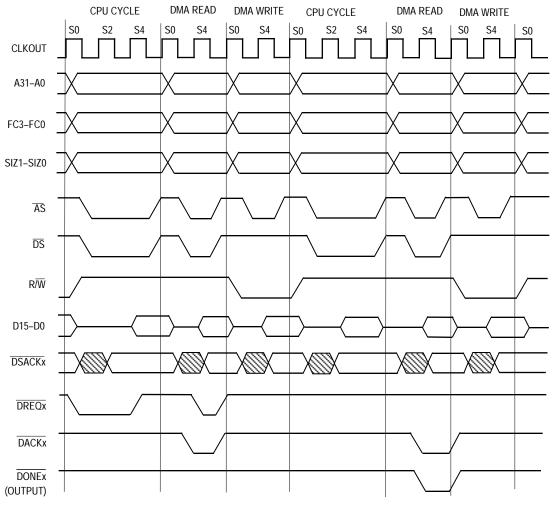

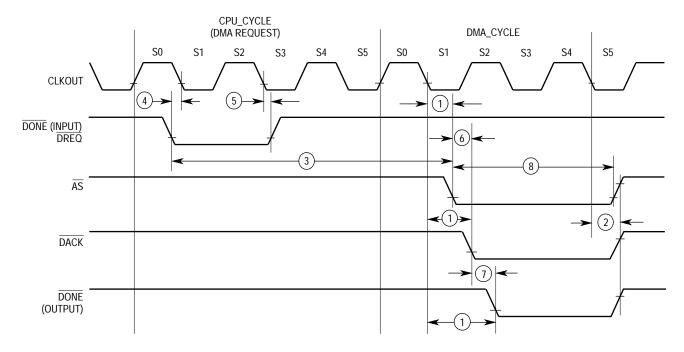

| 6-1           | DMA Block Diagram                                                 | 6-1            |

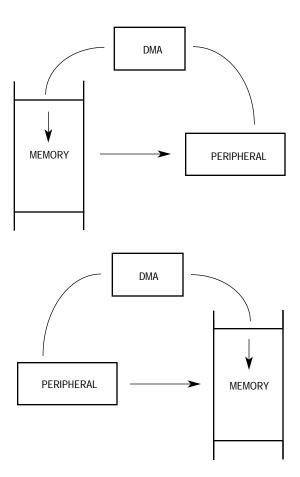

| 6-2           | Single-Address Transfers                                          |                |

| 6-3           | Dual-Address Transfer                                             |                |

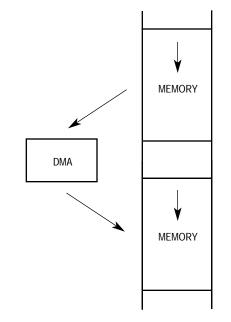

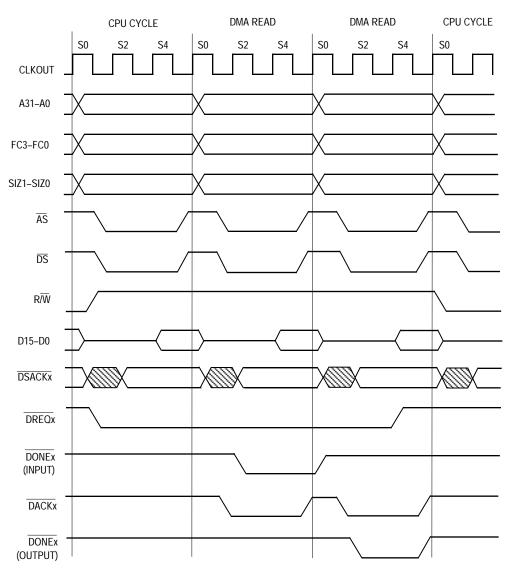

| 6-4           | DMA External Connections to Serial Module                         | 6-6            |

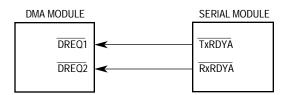

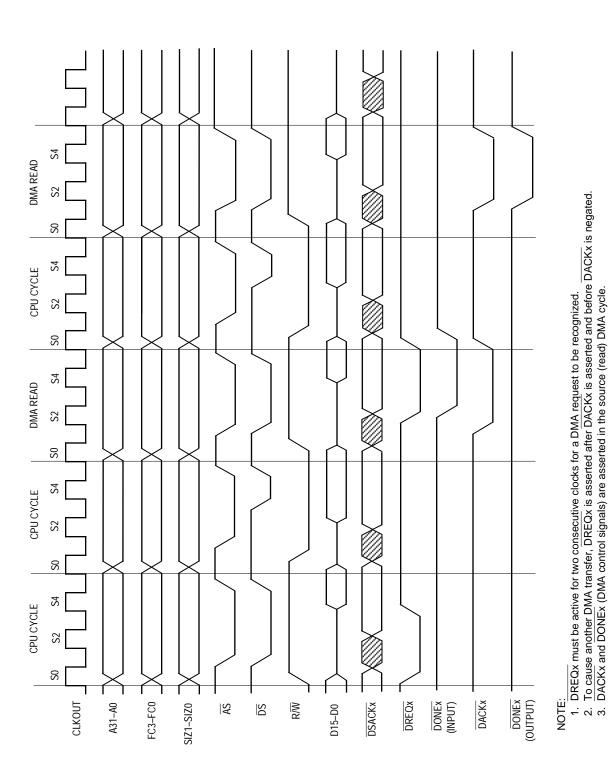

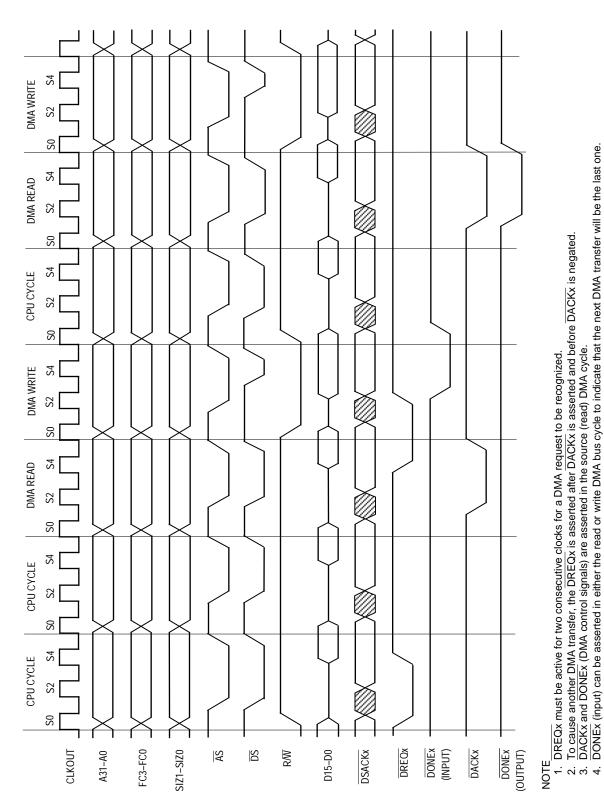

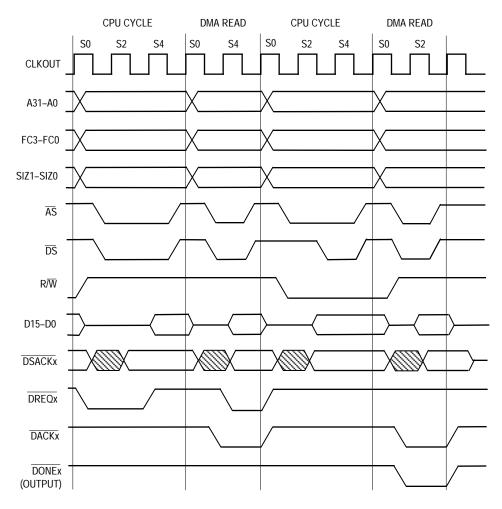

| 6-5           | Single-Address Read Timing (External Burst)                       | 6-8            |

| 6-6           | Single-Address Read Timing (Cycle Steal)                          | 6-9            |

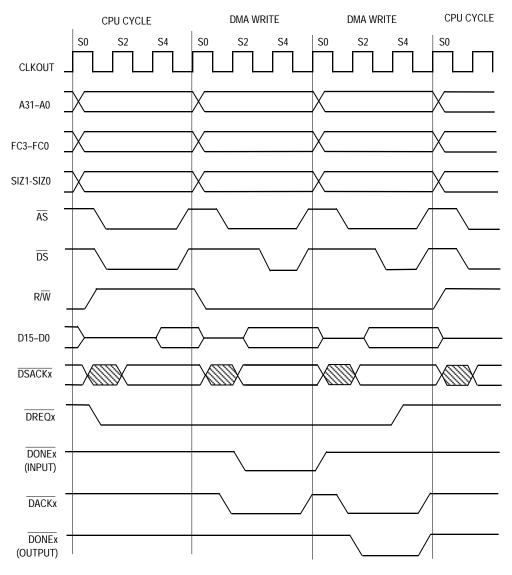

| 6-7           | Single-Address Write Timing (External Burst)                      | 6-10           |

| 6-8           | Single-Address Write Timing (Cycle Steal)                         |                |

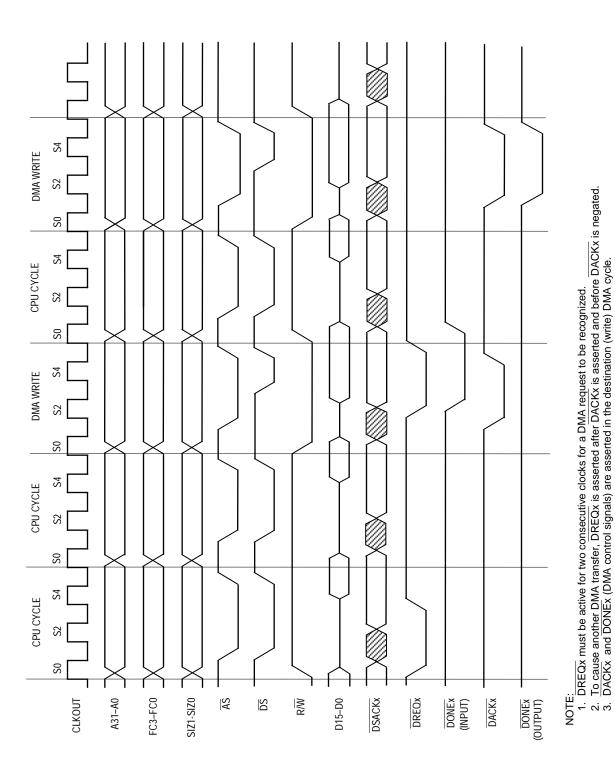

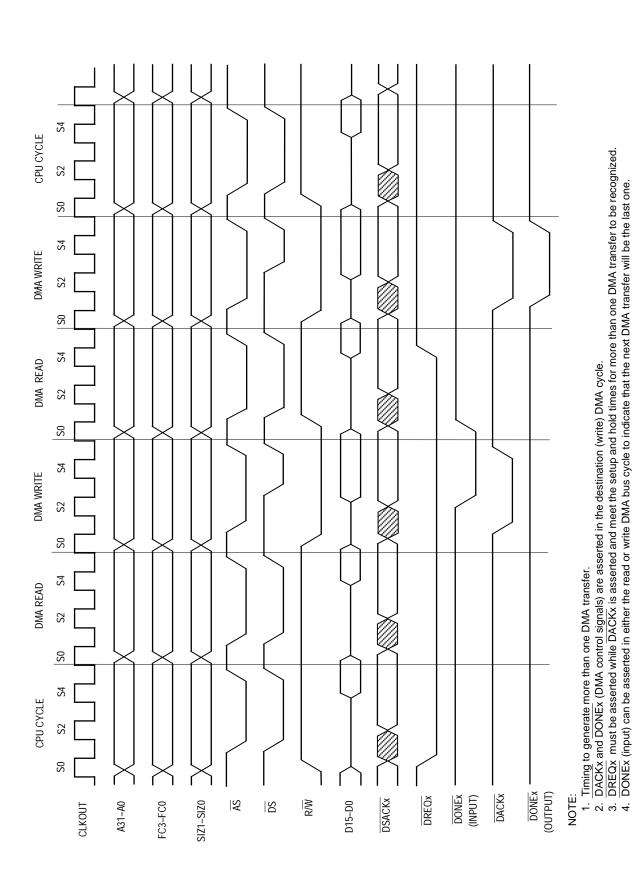

| 6-9           | Dual-Address Read Timing (External Burst—Source Requesting)       | 6-13           |

| 6-10          | Dual-Address Read Timing (Cycle Steal—Source Requesting)          |                |

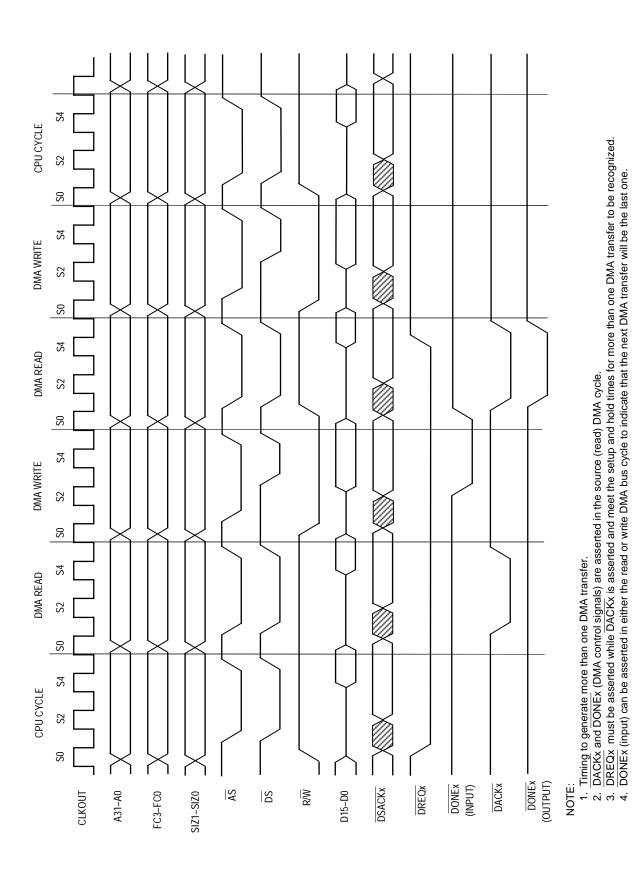

| 6-11          | Dual-Address Write Timing (External Burst—Destination Requesting) |                |

| 6-12          | Dual-Address Write Timing (Cycle Steal—Destination Requesting)    |                |

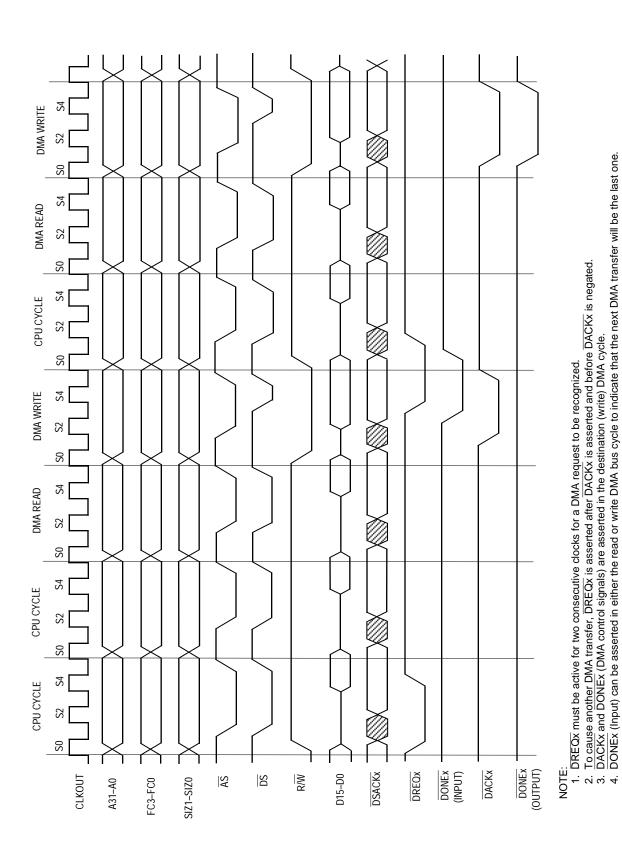

| 6-13          | Fast Termination Option (Cycle Steal)                             |                |

| 6-14          | Fast Termination Option (External Burst—Source Requesting)        |                |

| 6-15          | DMA Module Programming Model                                      |                |

| 6-16          | Packing and Unpacking of Operands                                 | 6-35           |

| 7-1           | Simplified Block Diagram                                          |                |

| 7-2           | External and Internal Interface Signals                           |                |

| 7-3           | Baud Rate Generator Block Diagram                                 |                |

| 7-4           | Transmitter and Receiver Functional Diagram                       |                |

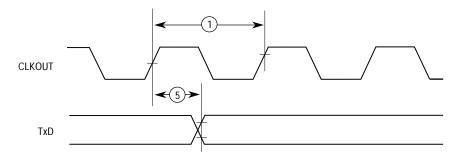

| 7-5           | Transmitter Timing Diagram                                        |                |

| 7-6           | Receiver Timing Diagram                                           |                |

| 7-7           | Looping Modes Functional Diagram                                  |                |

| 7-8           | Multidrop Mode Timing Diagram                                     |                |

| 7-9           | Serial Module Programming Model                                   |                |

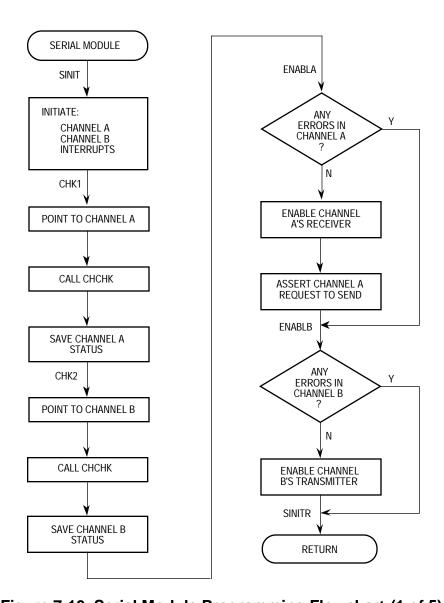

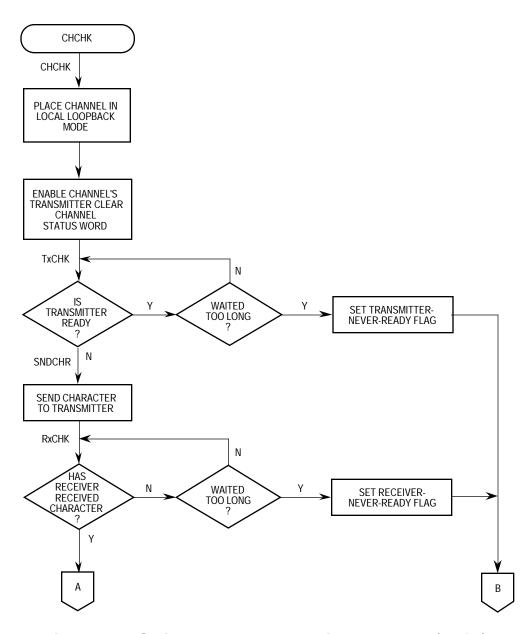

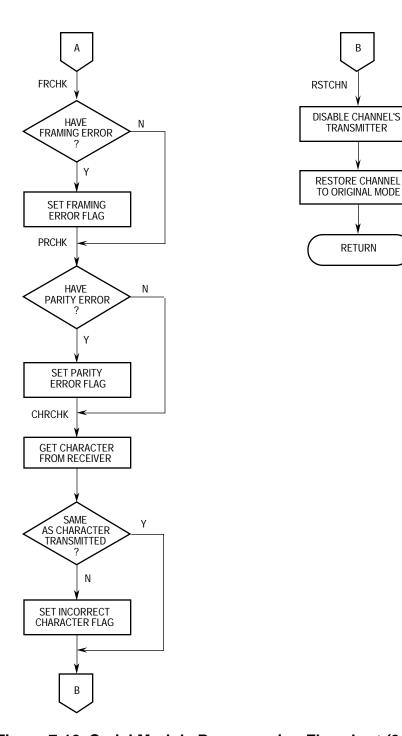

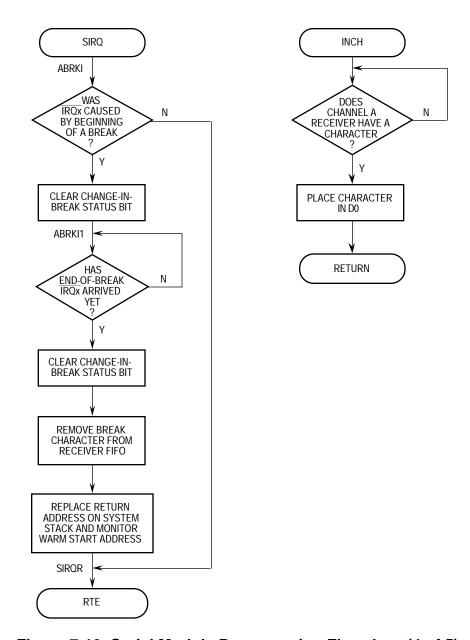

| 7-10          | Serial Module Programming Flowchart                               | 7-41           |

| 8-1           | Simplified Block Diagram                                          |                |

| 8-2           | Timer Functional Diagram                                          |                |

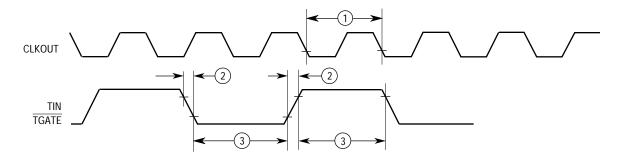

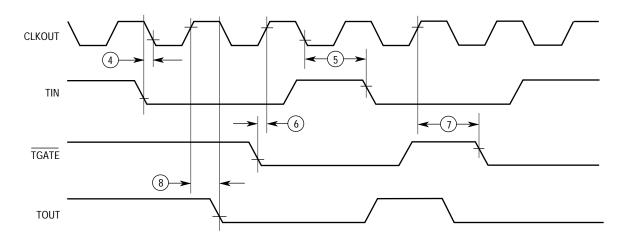

| 8-3           | External and Internal Interface Signals                           |                |

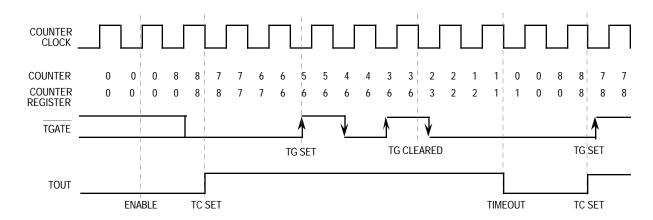

| 8-4           | Input Capture/Output Compare Mode                                 |                |

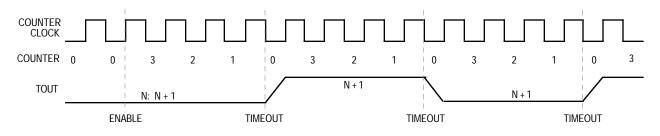

| 8-5           | Square-Wave Generator Mode                                        |                |

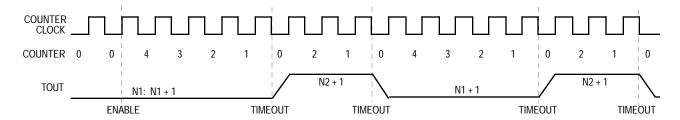

| 8-6           | Variable Duty-Cycle Square-Wave Generator Mode                    |                |

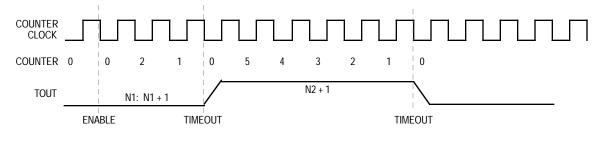

| 8-7           | Variable-Width Single-Shot Pulse Generator Mode                   |                |

| 8-8           | Pulse-Width Measurement Mode                                      |                |

| 8-9           | Period Measurement Mode                                           |                |

| 8-10          | Event Count Mode                                                  |                |

| 8-11          | Timer Module Programming Model                                    | 8-18           |

| 9-1           | Test Access Port Block Diagram                                    |                |

| 9-2           | TAP Controller State Machine                                      | 9-3            |

# LIST OF ILLUSTRATIONS (Continued)

| Figur<br>Numb |                                                            | Page<br>Number |

|---------------|------------------------------------------------------------|----------------|

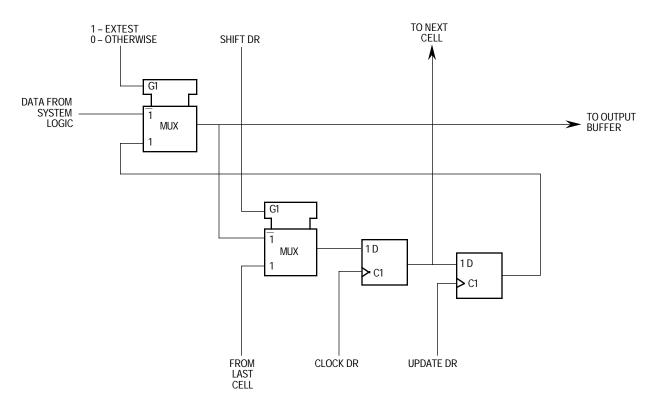

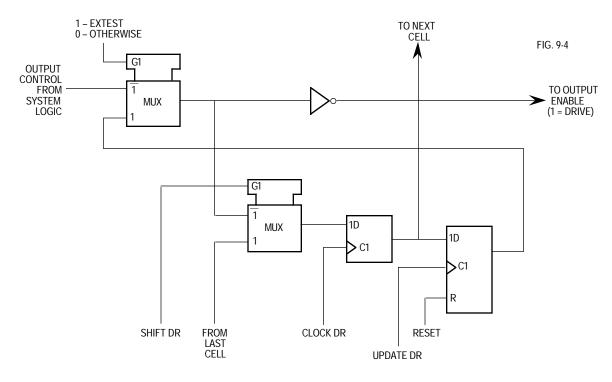

| 9-3           | Output Latch Cell (O.Latch)                                | 9-7            |

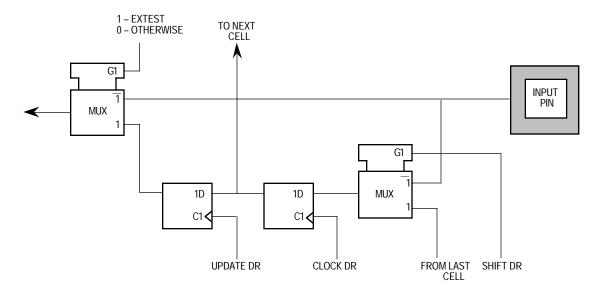

| 9-4           | Input Pin Cell (I.Pin)                                     |                |

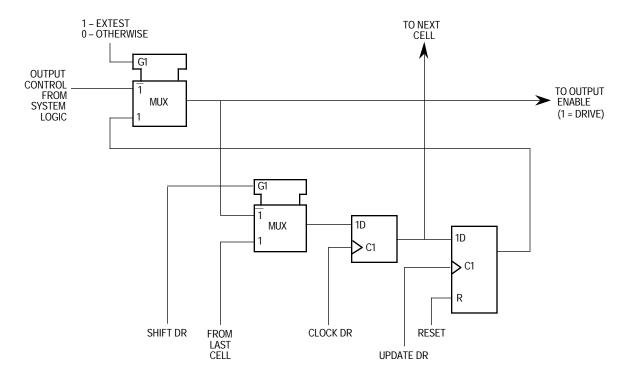

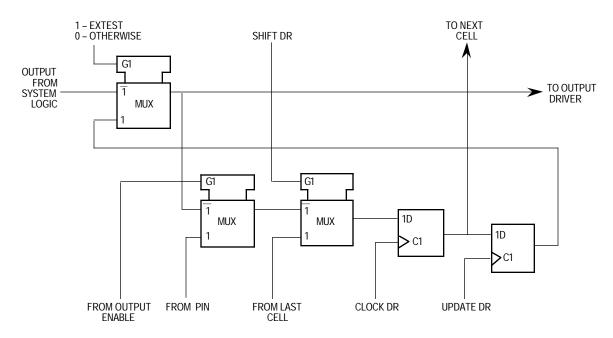

| 9-5           | Active-High Output Control Cell (IO.Ctl1)                  | 9-8            |

| 9-6           | Active-Low Output Control Cell (IO.Ctl0)                   | 9-8            |

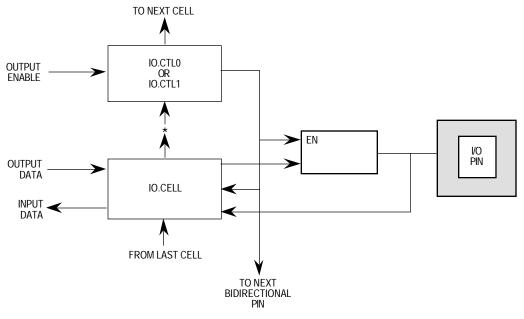

| 9-7           | Bidirectional Data Cell (IO.Cell)                          | 9-9            |

| 9-8           | General Arrangement for Bidirectional Pins                 |                |

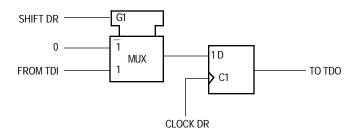

| 9-9           | Bypass Register                                            | 9-11           |

| 10-1          | Minimum System Configuration Block Diagram                 | 10-1           |

| 10-2          | Sample Crystal Circuit                                     |                |

| 10-3          | Statek Corporation Crystal Circuit                         |                |

| 10-4          | XFC and V <sub>CCSYN</sub> Capacitor Connections           |                |

| 10-5          | SRAM Interface                                             |                |

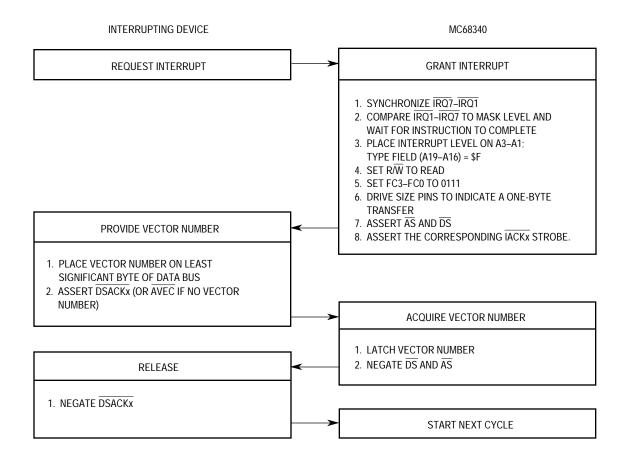

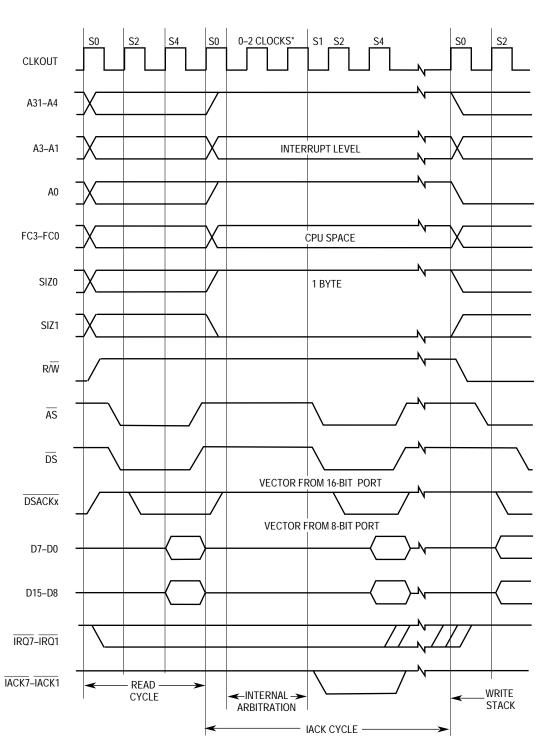

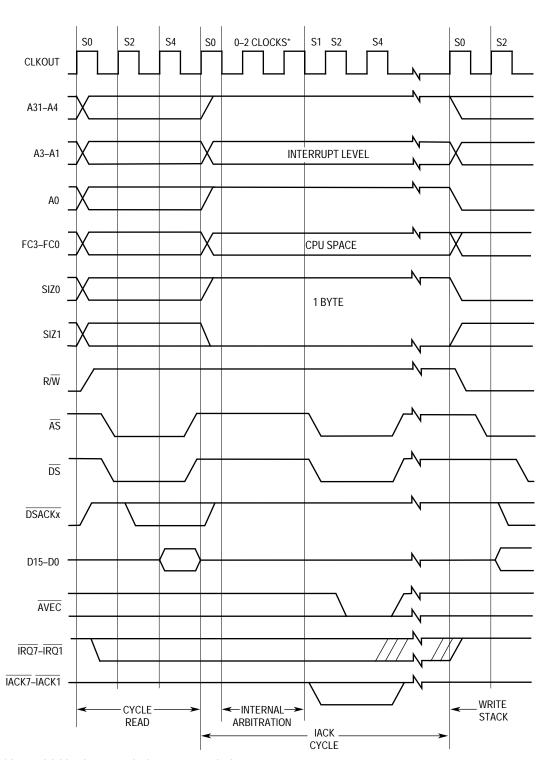

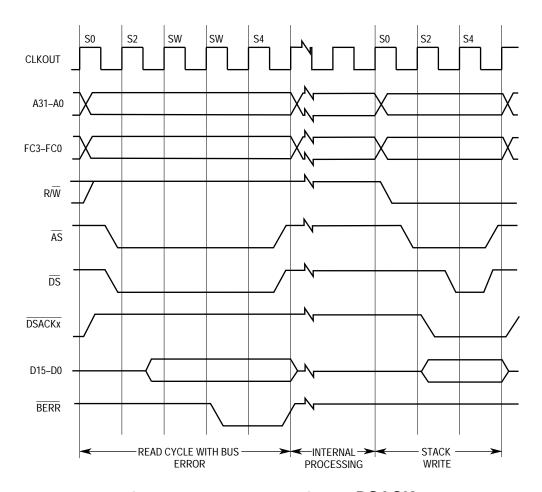

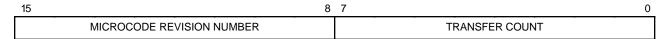

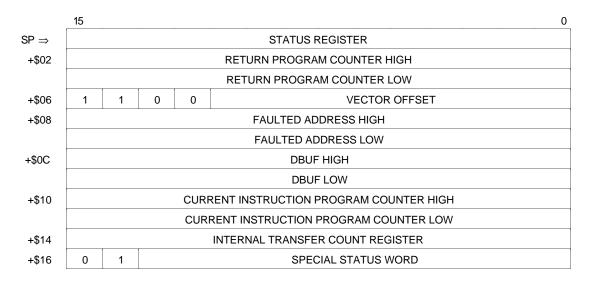

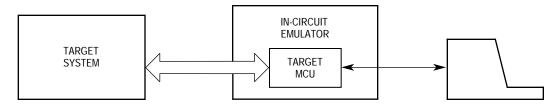

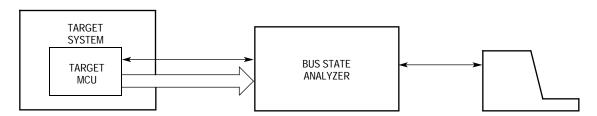

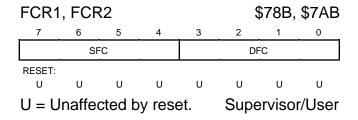

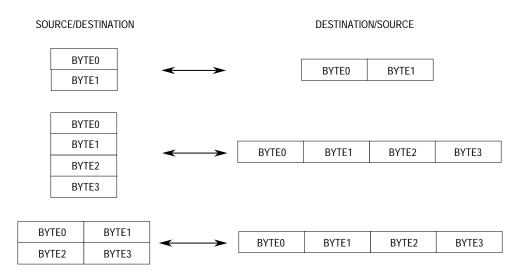

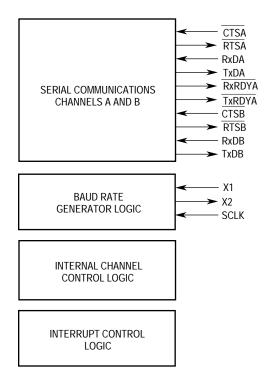

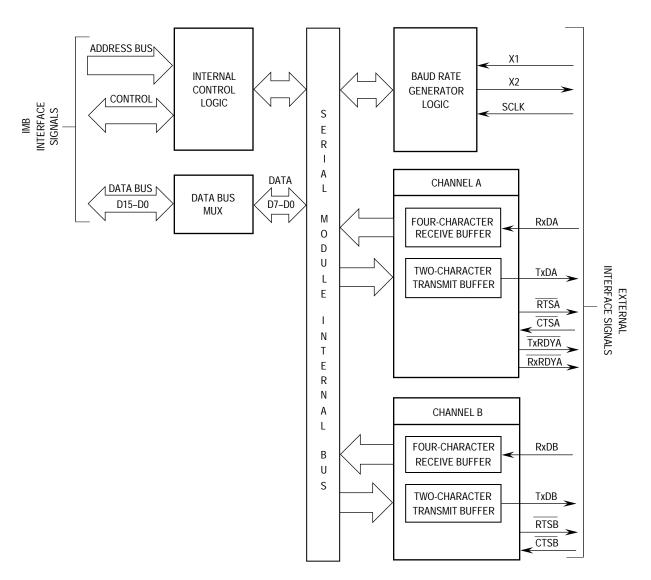

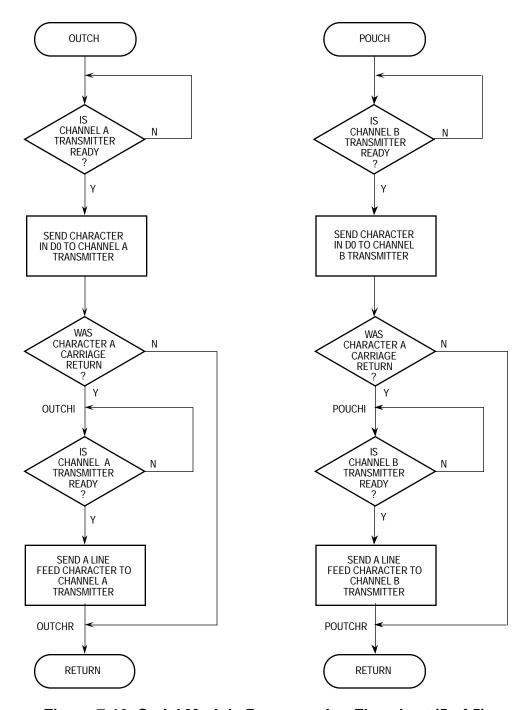

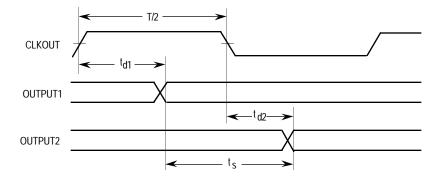

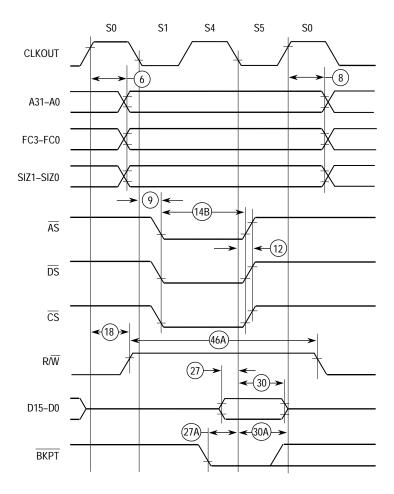

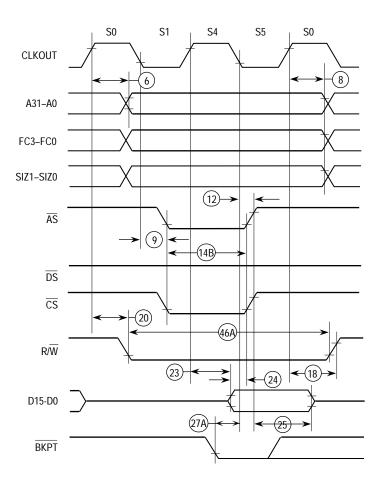

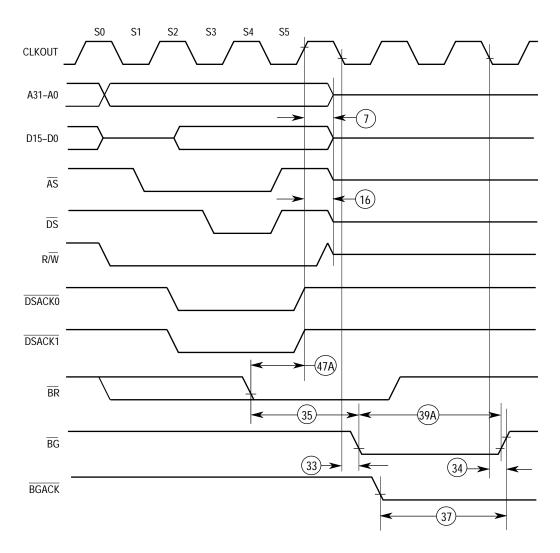

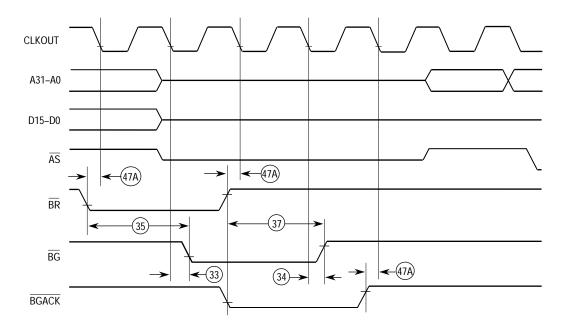

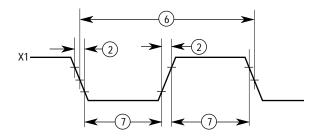

| 10-6          | ROM Interface                                              | 10-4           |