# **Freescale Semiconductor**

#### **Technical Data**

Document Number: MC1321x

Rev. 1.8 08/2009

# MC1321x

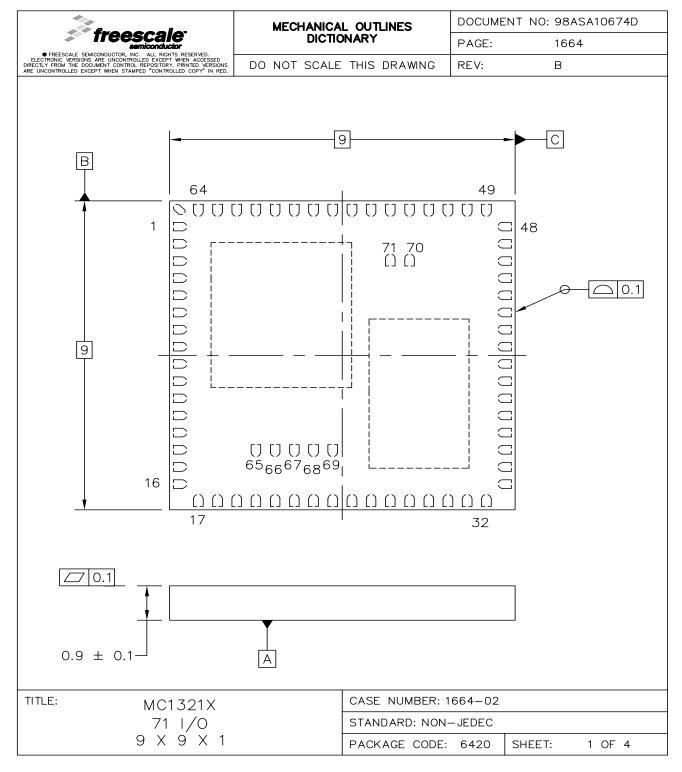

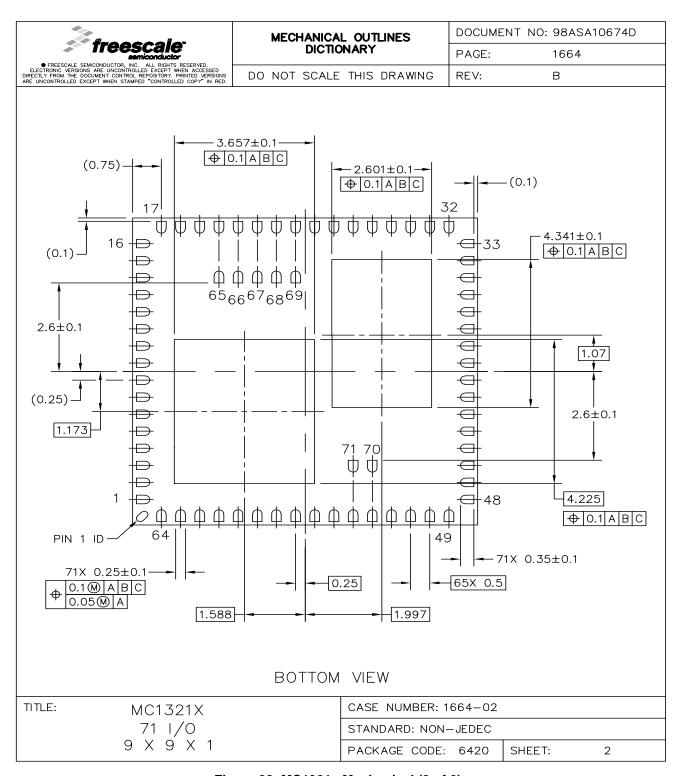

#### Package Information Case 1664-01

71-pin LGA [9x9 mm]

#### **Ordering Information**

| Device               | Device Marking | Package |

|----------------------|----------------|---------|

| MC13211 <sup>1</sup> | 13211          | LGA     |

| MC13212 <sup>1</sup> | 13212          | LGA     |

| MC13213 <sup>1</sup> | 13213          | LGA     |

See Table 1 for more details.

# MC13211/212/213

ZigBee<sup>™</sup>- Compliant Platform - 2.4 GHz Low Power Transceiver for the IEEE<sup>®</sup> 802.15.4 Standard plus Microcontroller

## 1 Introduction

The MC1321x family is Freescale's second-generation ZigBee platform which incorporates a low power 2.4 GHz radio frequency transceiver and an 8-bit microcontroller into a single 9x9x1 mm 71-pin LGA package. The MC1321x solution can be used for wireless applications from simple proprietary point-to-point connectivity to a complete ZigBee mesh network. The combination of the radio and a microcontroller in a small footprint package allows for a cost-effective solution.

The MC1321x contains an RF transceiver which is an 802.15.4 Standard compliant radio that operates in the 2.4 GHz ISM frequency band. The transceiver includes a low noise amplifier, 1mW nominal output power, PA with internal voltage controlled oscillator (VCO), integrated transmit/receive switch, on-board power supply regulation, and full spread-spectrum encoding and decoding.

The MC1321x also contains a microcontroller based on the HCS08 Family of Microcontroller Units (MCU), specifically the HCS08 Version A, and can provide up to 60KB of flash memory and 4KB of RAM. The onboard

#### **Contents**

| 1 | Introduction 1                                 |

|---|------------------------------------------------|

| 2 | MC1321x Pin Assignment and Connections 8       |

| 3 | MC1321x Serial Peripheral Interface (SPI) . 14 |

| 4 | 802.15.4 Standard Modem 16                     |

| 5 | MCU 25                                         |

| 6 | System Electrical Specification 46             |

| 7 | Application Considerations 63                  |

| 8 | Mechanical Diagrams 68                         |

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2005, 2006, 2007, 2008, 2009. All rights reserved.

MCU allows the communications stack and also the application to reside on the same system-in-package (SIP). The MC1321x family is organized as follows:

- The MC13211 has 16KB of flash and 1KB of RAM and is an ideal solution for low cost, proprietary applications that require wireless point-to-point or star network connectivity. The MC13211 combined with the Freescale Simple MAC (SMAC) provides the foundation for proprietary applications by supplying the necessary source code and application examples to get users started on implementing wireless connectivity.

- The MC13212 contains 32K of flash and 2KB of RAM and is intended for use with the Freescale fully compliant 802.15.4 MAC. Custom networks based on the 802.15.4 Standard MAC can be implemented to fit user needs. The 802.15.4 Standard supports star, mesh and cluster tree topologies as well as beaconed networks.

- The MC13213 contains 60K of flash and 4KB of RAM and is also intended for use with the Freescale fully compliant 802.15.4 MAC and the fully ZigBee compliant Freescale BeeStack.

#### WARNING

- The MC1321x now uses an updated version of the 689S08A 8-bit microprocessor to correct errata associated with the onboard FLL and reset pin. Refer to the associated errata for this new device, *Document Number MSE9S08GB60A\_4L11Y*, on the Freescale web site.

- The MC1321x also now uses an updated version of the transceiver device that is functionally fully compliant with earlier versions of the transceiver.

However, for proper performance of the radio the following modem registers must be over-programmed:

Register 0x31 to 0xA0C0

Register 0x34 to 0xFEC6

These registers must be over-programmed for MC1321x devices in which the modem Chip\_ID Register 0x2C reads 0x6800.

Applications include, but are not limited to, the following:

- Residential and commercial automation

- Lighting control

- Security

- Access control

- Heating, ventilation, air-conditioning (HVAC)

- Automated meter reading (AMR)

- Industrial Control

- Asset tracking and monitoring

- Homeland security

- Process management

- Environmental monitoring and control

- HVAC

- Automated meter reading

- Health Care

- Patient monitoring

- Fitness monitoring

- Consumer

- Human interface devices (keyboard, mice, etc.)

- Remote control

- Wireless toys

# 1.1 Ordering Information

Table 1 provides additional details about the MC1321x family.

#### **NOTE**

The device marking for silicon revision 1.1 and newer is different than version 1.0 and older. For more details about the 71-pin LGA package used for the MC1321x family, see the 802.15.4/ZigBee Hardware Design Considerations Reference Manual (ZHDCRM).

**Table 1. Orderable Parts Details**

| Device    | Operating<br>Temp Range<br>(TA.) | Package              | Memory<br>Options      | Description                                                                                                                         |

|-----------|----------------------------------|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| MC13211   | -40° to 85° C                    | LGA                  | 1KB RAM,<br>16KB Flash | Intended for proprietary applications and Freescale Simple MAC (SMAC)                                                               |

| MC13211R2 | -40° to 85° C                    | LGA<br>Tape and Reel | 1KB RAM,<br>16KB Flash | Intended for proprietary applications and Freescale Simple MAC (SMAC)                                                               |

| MC13212   | -40° to 85° C                    | LGA                  | 2KB RAM,<br>32KB Flash | Intended for 802.15.4 Standard compliant applications and Freescale 802.15.4 MAC                                                    |

| MC13212R2 | -40° to 85° C                    | LGA<br>Tape and Reel | 2KB RAM,<br>32KB Flash | Intended for 802.15.4 Standard compliant applications and Freescale 802.15.4 MAC                                                    |

| MC13213   | -40° to 85° C                    | LGA                  | 4KB RAM,<br>60KB Flash | Intended for 802.15.4 Standard compliant applications and the Freescale 802.15.4 MAC and fully ZigBee compliant Freescale BeeStack. |

| MC13213R2 | -40° to 85° C                    | LGA<br>Tape and Reel | 4KB RAM,<br>60KB Flash | Intended for 802.15.4 Standard compliant applications and Freescale 802.15.4 MAC and fully ZigBee compliant Freescale BeeStack.     |

#### 1.2 General Platform Features

- 802.15.4 Standard compliant on-chip transceiver/modem

- 2.4GHz

- 16 selectable channels

- Programmable output power

- Multiple power saving modes

- 2V to 3.4V operating voltage with on-chip voltage regulators

- -40°C to +85°C temperature range

- Low external component count

- Supports single 16 MHz crystal clock source operation or dual crystal operation

- Support for SMAC, IEEE 802.15.4 Standard-Compliant MAC, SynkroRF, BeeStack, BeeStack Consumer (ZigBee RF4CE) software solutions

- 9mm x 9mm x 1mm 71-pin LGA

#### 1.3 Microcontroller Features

- Low voltage MCU with 40 MHz low power HCS08 CPU core

- Up to 60K flash memory with block protection and security and 4K RAM

- MC13211: 16KB Flash, 1KB RAM

- MC13212: 32KB Flash, 2KB RAM

- MC13213: 60KB Flash, 4KB RAM

- Low power modes (Wait plus Stop2 and Stop3 modes)

- Dedicated serial peripheral interface (SPI) connected internally to 802.15.4 modem

- One external 4-channel (5-channel internal) 16-bit timer/pulse width modulator (TPM) module and one external 1-channel (3-channel internal) 16-bit timer/pulse width modulator module, each with selectable input capture, output capture, and PWM capability.

- 8-bit port keyboard interrupt (KBI)

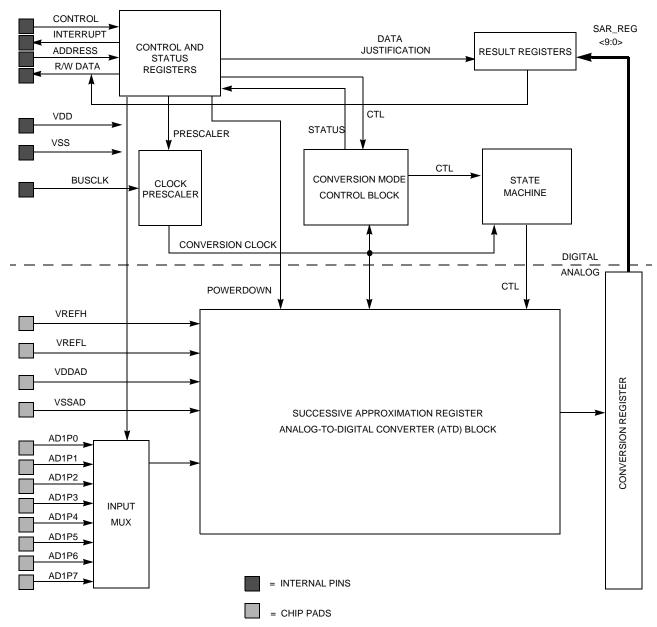

- 8-channel 8-10-bit ADC

- Two independent serial communication interfaces (SCI)

- Multiple clock source options

- Internal clock generator (ICG) with 243 kHz oscillator that has +/-0.2% trimming resolution and +/-0.5% deviation across voltage.

- Startup oscillator of approximately 8 MHz

- External crystal or resonator

- External source from modem clock for very high accuracy source or system low-cost option

- Inter-integrated circuit (IIC) interface.

- In-circuit debug and flash programming available via on-chip background debug module (BDM)

- Two comparator and 9 trigger modes

- Eight deep FIFO for storing change-of-flow addresses and event-only data

- Tag and force breakpoints

- In-circuit debugging with single breakpoint

- System protection features

- Programmable low voltage interrupt (LVI)

- Optional watchdog timer (COP)

- Illegal opcode detection

- Up to 32 MCU GPIO with programmable pullups

#### 1.4 RF Modem Features

- Fully compliant 802.15.4 Standard transceiver supports 250 kbps O-QPSK data in 5.0 MHz channels and full spread-spectrum encode and decode

- Operates on one of 16 selectable channels in the 2.4 GHz ISM band

- -1 dBm to 0 dBm nominal output power, programmable from -27 dBm to +3 dBm typical

- Receive sensitivity of <-92 dBm (typical) at 1% PER, 20-byte packet, much better than the 802.15.4 Standard of -85 dBm

- Integrated transmit/receive switch

- Dual PA ouput pairs which can be programmed for full differential single-port or dual-port operation that supports an external LNA and/or PA.

- Three low power modes for increased battery life

- Programmable frequency clock output for use by MCU

- Onboard trim capability for 16 MHz crystal reference oscillator eliminates need for external variable capacitors and allows for automated production frequency calibration

- Four internal timer comparators available to supplement MCU timer resources

- Supports both packet data mode and streaming data mode

- Seven GPIO to supplement MCU GPIO

#### 1.5 Software Features

Freescale provides a wide range of software functionality to complement the MC1321x hardware. There are three levels of application solutions:

- SMAC

- IEEE 802.15.4 Standard-Compliant MAC

- SynkroRF

- BeeStack

- BeeStack Consumer (ZigBee RF4CE)

## 1.5.1 Simple Media Access Controller (SMAC)

- Small memory footprint (about 3 Kbytes typical)

- Supports point-to-point and star network configurations

- Proprietary networks

- Source code and application examples provided

### 1.5.2 802.15.4 Standard-Compliant MAC

- Supports star, mesh and cluster tree topologies

- Supports beaconed networks

- Supports GTS for low latency

- Multiple power saving modes (idle doze, hibernate)

## 1.5.3 SynkroRF

- Based on the IEEE 802.15.4 Standard

- Bi-directional Communication

- Interference Avoidance

- Channel Agility

- Low Latency Transmission for high duty cycle interferers

- Easy Device Pairing

- Fragmentation Support

- Standardized Command Set

#### 1.5.4 BeeStack

- Based on the IEEE 802.15.4 Standard

- Supports ZigBee 2006 Specification

- Supports star, mesh and tree networks

- Advanced Encryption Standard (AES) 128-bit security

- Supports the ZigBee Home Automation Profile

- Supports the ZigBee Smart Energy Profile

## 1.5.5 BeeStack Consumer (ZigBee RF4CE)

- Based on the IEEE 802.15.4 Standard

- Supports application profiles that define standardized command sets for multi-vendor interoperability

- Supports vendor specific extensions to standard application profiles for vendor specific customizing

- Supports AES-128 bit encryption

- Provides a mechanism for secured key generation

- Specifies various power saving modes

- Provides a simple mechanism to pair devices (such as a remote to a TV)

- Ensures only authorized devices are able to communicate (a user's remote will not turn their neighbor's TV on or off)

## 1.6 System Block Diagram

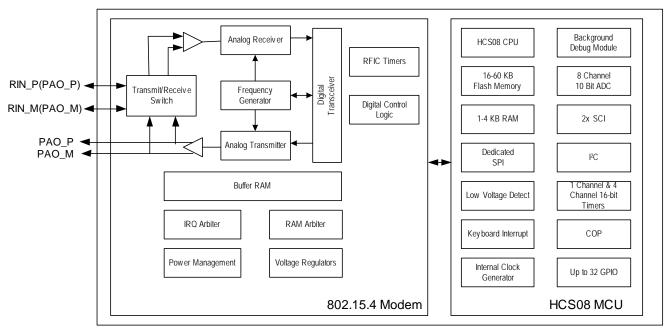

Figure 1 shows a simplified block diagram of the MC1321x solution.

Figure 1. MC1321x System Level Block Diagram

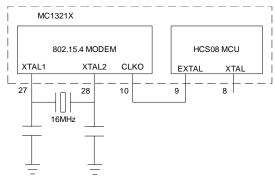

## 1.7 System Clock Configuration

The MC321x device allows for a wide array of system clock configurations:

- Pins are provided for a separate external clock source for the CPU. The external clock source can

by derived from a crystal oscillator or from an external clock source

- Pins are provided for a 16 MHz crystal for the modem clock source (required)

- The modem crystal oscillator frequency can be trimmed through programming to maintain the tight tolerances required by the 802.15.4 Standard

- The modem provides a CLKO programmable frequency clock output that can be used as an external source to the CPU. As a result, a single crystal system clock solution is possible

- Out of reset, the MCU uses an internally generated clock (approximately 8-MHz) for start-up. This allows recovery from stop or reset without a long crystal start-up delay

- The MCU contains an internal clock generator (which can be trimmed) that can be used to run the MCU for low power operation. This internal reference is approximately 243 kHz

Figure 2. MC1321x Single Crystal System Clock Structure

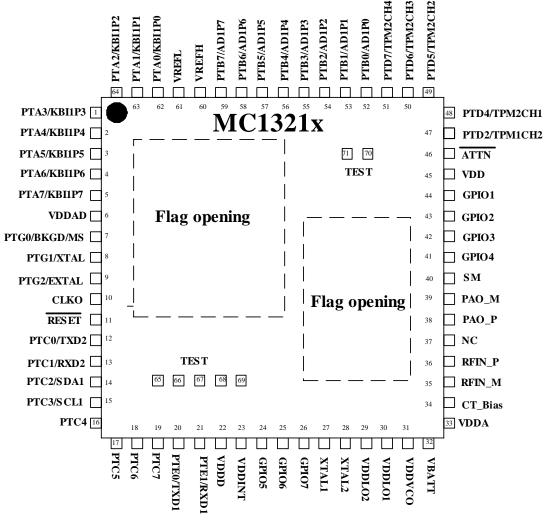

# 2 MC1321x Pin Assignment and Connections

Figure 3 shows the MC1321x pinout.

Figure 3. MC1321x Pinout (Top View)

# 2.1 Pin Definitions

Table 2 details the MC1321x pinout and functionality.

**Table 2. Pin Function Description**

| Pin # | Pin Name      | Туре                     | Description                                    | Functionality                                                                                                               |

|-------|---------------|--------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1     | PTA3/KBI1P3   | Digital<br>Input/Output  | MCU Port A Bit 3 /<br>Keyboard Input Bit 3     |                                                                                                                             |

| 2     | PTA4/KBI1P4   | Digital<br>Input/Output  | MCU Port A Bit 4 /<br>Keyboard Input Bit 4     |                                                                                                                             |

| 3     | PTA5/KBI1P5   | Digital<br>Input/Output  | MCU Port A Bit 5 /<br>Keyboard Input Bit 5     |                                                                                                                             |

| 4     | PTA6/KBI1P6   | Digital<br>Input/Output  | MCU Port A Bit 6 /<br>Keyboard Input Bit 6     |                                                                                                                             |

| 5     | PTA7/KBI1P7   | Digital<br>Input/Output  | MCU Port A Bit 7 /<br>Keyboard Input Bit 7     |                                                                                                                             |

| 6     | VDDAD         | Power Input              | MCU power supply to ATD                        | Decouple to ground.                                                                                                         |

| 7     | PTG0/BKGND/MS | Digital<br>Input/Output/ | MCU Port G Bit 0 /<br>Background / Mode Select | PTG0 is output only. Pin is I/O when used as BDM function.                                                                  |

| 8     | PTG1/XTAL     | Digital<br>Input/Output  | MCU Port G Bit 1 / Crystal oscillator output   | Full I/O when not used as clock source.                                                                                     |

| 9     | PTG2/EXTAL    | Digital<br>Input/Output/ | MCU Port G Bit 2 / Crystal oscillator input    | Full I/O when not used as clock source.                                                                                     |

| 10    | CLKO          | Digital Output           | Modem Clock Output                             | Programmable frequencies of:<br>16 MHz, 8 MHz, 4 MHz, 2 MHz, 1 MHz, 62.5 kHz,<br>32.786+ kHz (default),<br>and 16.393+ kHz. |

| 11    | RESET         | Digital<br>Input/Output  | MCU reset. Active low                          |                                                                                                                             |

| 12    | PTC0/TXD2     | Digital<br>Input/Output  | MCU Port C Bit 0 / SCI2 TX data out            |                                                                                                                             |

| 13    | PTC1/RXD2     | Digital<br>Input/Output  | MCU Port C Bit 1/ SCI2 RX data in              |                                                                                                                             |

| 14    | PTC2/SDA1     | Digital<br>Input/Output  | MCU Port C Bit 1/ IIC bus data                 |                                                                                                                             |

| 15    | PTC3/SCL1     | Digital<br>Input/Output  | MCU Port C Bit 1/ IIC bus clock                |                                                                                                                             |

| 16    | PTC4          | Digital<br>Input/Output  | MCU Port C Bit 4                               |                                                                                                                             |

| 17    | PTC5          | Digital<br>Input/Output  | MCU Port C Bit 5                               |                                                                                                                             |

| 18    | PTC6          | Digital<br>Input/Output  | MCU Port C Bit 6                               |                                                                                                                             |

**Table 2. Pin Function Description (continued)**

| Pin# | Pin Name           | Туре                    | Description                                                        | Functionality                                                                                                                                                                                           |

|------|--------------------|-------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19   | PTC7               | Digital<br>Input/Output | MCU Port C Bit 7                                                   |                                                                                                                                                                                                         |

| 20   | PTE0/TXD1          | Digital<br>Input/Output | MCU Port E Bit 0 / SCI1 TX data out                                |                                                                                                                                                                                                         |

| 21   | PTE1/RXD1          | Digital<br>Input/Output | MCU Port E Bit 1/ SCI1 RX data in                                  |                                                                                                                                                                                                         |

| 22   | VDDD               | Power Output            | Modem regulated output supply voltage                              | Decouple to ground.                                                                                                                                                                                     |

| 23   | VDDINT             | Power Input             | Modem digital interface supply                                     | 2.0 to 3.4 V. Decouple to ground. Connect to Battery.                                                                                                                                                   |

| 24   | GPIO5 <sup>1</sup> | Digital<br>Input/Output | General Purpose<br>Input/Output 5.                                 | See Footnote 1                                                                                                                                                                                          |

| 25   | GPIO6 <sup>1</sup> | Digital<br>Input/Output | Modem General Purpose Input/Output 6                               | See Footnote 1                                                                                                                                                                                          |

| 26   | GPIO7 <sup>1</sup> | Digital<br>Input/Output | Modem General Purpose Input/Output 7                               | See Footnote 1                                                                                                                                                                                          |

| 27   | XTAL1              | Input                   | Modem crystal reference oscillator input                           | Connect to 16 MHz crystal and load capacitor.                                                                                                                                                           |

| 28   | XTAL2              | Input/Output            | Modem crystal reference oscillator output                          | Connect to 16 MHz crystal and load capacitor. Do not load this pin by using it as a 16 MHz source. Measure 16 MHz output at CLKO, programmed for 16 MHz.                                                |

| 29   | VDDLO2             | Power Input             | Modem LO2 VDD supply                                               | Connect to VDDA externally.                                                                                                                                                                             |

| 30   | VDDLO1             | Power Input             | Modem LO1 VDD supply                                               | Connect to VDDA externally.                                                                                                                                                                             |

| 31   | VDDVCO             | Power Output            | Modem VCO regulated supply bypass                                  | Decouple to ground.                                                                                                                                                                                     |

| 32   | VBATT              | Power Input             | Modem voltage regulators' input                                    | Decouple to ground. Connect to Battery.                                                                                                                                                                 |

| 33   | VDDA               | Power Output            | Modem analog regulated supply output                               | Decouple to ground. Connect to directly VDDLO1 and VDDLO2 externally and to PAO_P and PAO_M through a bias network.                                                                                     |

| 34   | CT_Bias            | RF Control<br>Output    | Modem bias<br>voltage/control signal for<br>RF external components | When used with internal T/R switch, provides ground reference for RX and VDDA reference for TX. Can also be used as a control signal with external LNA, antenna switch, and/or PA (high level is VDDA). |

| 35   | RFIN_M             | RF Input<br>(Output)    | Modem RF input/output negative                                     | When used with internal T/R switch, this is a bi-directional RF port for the internal LNA and PA                                                                                                        |

| 36   | RFIN_P             | RF Input<br>(Output)    | Modem RF input/output positive                                     | When used with internal T/R switch, this is a bi-directional RF port for the internal LNA and PA                                                                                                        |

| 37   | NC                 |                         | Not used                                                           | May be grounded or left open                                                                                                                                                                            |

**Table 2. Pin Function Description (continued)**

| Pin # | Pin Name           | Туре                     | Description                                                                       | Functionality                                                                                                                |

|-------|--------------------|--------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 38    | PAO_P              | RF Output                | Modem power amplifier RF output positive                                          | Open drain. Connect to VDDA through a bias network when used with external balun. Not used when internal T/R switch is used. |

| 39    | PAO_M              | RF Output                | Modem power amplifier RF output negative                                          | Open drain. Connect to VDDA through a bias network when used with external balun. Not used when internal T/R switch is used. |

| 40    | SM                 | Input                    | Test Mode pin                                                                     | Must be grounded for normal operation                                                                                        |

| 41    | GPIO4 <sup>1</sup> | Digital Input/<br>Output | General Purpose<br>Input/Output 4.                                                | See Footnote 1                                                                                                               |

| 42    | GPIO3 <sup>1</sup> | Digital<br>Input/Output  | Modem General Purpose<br>Input/Output 3                                           | See Footnote 1                                                                                                               |

| 43    | GPIO2              | Test Point               | MCU Port E Bit 6 / Modem<br>General Purpose<br>Input/Output 2                     | Internally connected pins. When gpio_alt_en, Register 9, Bit 7 = 1, GPIO2 functions as a "CRC Valid" indicator.              |

| 44    | GPIO1              | Test Point               | MCU Port E Bit 7 / Modem<br>General Purpose<br>Input/Output 1                     | Internally connected pins. When gpio_alt_en, Register 9, Bit 7 = 1, GPIO1 functions as an "Out of Idle" indicator.           |

| 45    | VDD                | Power Input              | MCU main power supply                                                             | Decouple to ground.                                                                                                          |

| 46    | ATTN <sup>2</sup>  | Digital Input            | Active Low Attention. Transitions IC from either Hibernate or Doze Modes to Idle. | See Footnote 2                                                                                                               |

| 47    | PTD2/TPM1CH2       | Digital<br>Input/Output  | MCU Port D Bit 2 / TPM1<br>Channel 2                                              |                                                                                                                              |

| 48    | PTD4/TPM2CH1       | Digital<br>Input/Output  | MCU Port D Bit 4 / TPM2<br>Channel 1                                              |                                                                                                                              |

| 49    | PTD5/TPM2CH2       | Digital<br>Input/Output  | MCU Port D Bit 5 / TPM2<br>Channel 2                                              |                                                                                                                              |

| 50    | PTD6/TPM2CH3       | Digital<br>Input/Output  | MCU Port D Bit 6 / TPM2<br>Channel 3                                              |                                                                                                                              |

| 51    | PTD7/TPM2CH4       | Digital<br>Input/Output  | MCU Port D Bit 7 / TPM2<br>Channel 4                                              |                                                                                                                              |

| 52    | PTB0/AD1P0         | Input/Output             | MCU Port B Bit 0 / ATD analogChannel 0                                            |                                                                                                                              |

| 53    | PTB1/AD1P1         | Input/Output             | MCU Port B Bit 1 / ATD analog Channel 1                                           |                                                                                                                              |

| 54    | PTB2/AD1P2         | Input/Output             | MCU Port B Bit 2 / ATD analog Channel 2                                           |                                                                                                                              |

| 55    | PTB3/AD1P3         | Input/Output             | MCU Port B Bit 3 / ATD analog Channel 3                                           |                                                                                                                              |

| 56    | PTB4/AD1P4         | Input/Output             | MCU Port B Bit 4 / ATD analog Channel 4                                           |                                                                                                                              |

**Table 2. Pin Function Description (continued)**

| Pin # | Pin Name    | Туре                    | Description                                                                                          | Functionality                         |

|-------|-------------|-------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------|

| 57    | PTB5/AD1P5  | Input/Output            | MCU Port B Bit 5 / ATD analog Channel 5                                                              |                                       |

| 58    | PTB6/AD1P6  | Input/Output            | MCU Port B Bit 6 / ATD analog Channel 6                                                              |                                       |

| 59    | PTB7/AD1P7  | Input/Output            | MCU Port B Bit 7 / ATD analog Channel 7                                                              |                                       |

| 60    | VREFH       | Input                   | MCU high reference voltage for ATD                                                                   |                                       |

| 61    | VREFL       | Input                   | MCU low reference voltage for ATD                                                                    |                                       |

| 62    | PTA0/KBI1P0 | Digital<br>Input/Output | MCU Port A Bit 0 /<br>Keyboard Input Bit 0                                                           |                                       |

| 63    | PTA1/KBI1P1 | Digital<br>Input/Output | MCU Port A Bit 1 /<br>Keyboard Input Bit 1                                                           |                                       |

| 64    | PTA2/KBI1P2 | Digital<br>Input/Output | MCU Port A Bit 2 /<br>Keyboard Input Bit 2                                                           |                                       |

| 65    | PTE5/SPSCK1 | SPICLK                  | MCU SPI master SPI clock output drives modem SPICLK slave clock input.                               | Normally factory test. Do not connect |

| 66    | PTE4/MOSI1  | MOSI                    | MCU SPI master MOSI<br>output drives modem slave<br>MOSI input                                       | Normally factory test. Do not connect |

| 67    | PTE3/MISO1  | MISO                    | Modem SPI slave MISO output drives MCU master MISO input                                             | Normally factory test. Do not connect |

| 68    | PTE2/SS1    | CE                      | MCU SPI master SS<br>output drives modem slave<br>CE input                                           | Normally factory test. Do not connect |

| 69    | IRQ         | M_IRQ                   | Modem interrupt request M_IRQ output drives MCU IRQ input                                            | Normally factory test. Do not connect |

| 70    | PTD1        | RXTXEN                  | MCU Port D Bit 1 drives<br>the RXTXEN input to the<br>modem to enable TX or RX<br>or CCA operations. | Normally factory test. Do not connect |

| 71    | PTD3        | M_RST                   | MCU Port D Bit 3 drives the reset M_RST input to the modem.                                          | Normally factory test. Do not connect |

| FLAG  | VSS         | Power input             | External package flag.<br>Common VSS                                                                 | Connect to ground.                    |

<sup>&</sup>lt;sup>1</sup> The transceiver GPIO pins default to inputs at reset. There are no programmable pullups on these pins. Unused GPIO pins should be tied to ground if left as inputs, or if left unconnected, they should be programmed as outputs set to the low state.

<sup>&</sup>lt;sup>2</sup> During low power modes, input must remain driven by MCU.

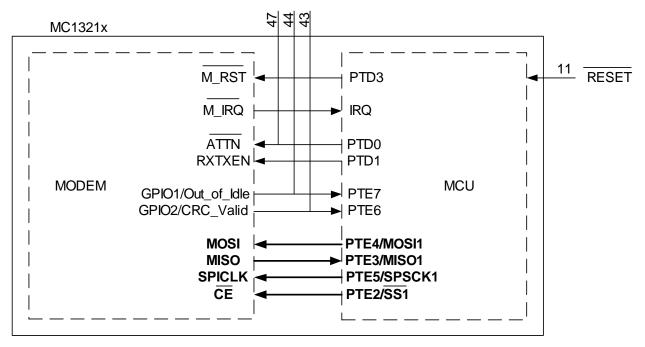

#### 2.2 Internal Functional Interconnects

The MCU provides control for the 802.15.4 modem. The required interconnects between the devices are routed onboard the SiP. In addition, the signals are brought out to external pads primarily for use as test points. These signals can be useful when writing and debugging software.

**Table 3. Internal Functional Interconnects**

| Pin # | MCU Signal  | Modem Signal        | Description                                                                                                |  |

|-------|-------------|---------------------|------------------------------------------------------------------------------------------------------------|--|

| 43    | PTE6        | GPIO2               | Modem GPIO2 output acts as "CRC Valid" status indicator for Stream Data Mode to MCU.                       |  |

| 44    | PTE7        | GPIO1               | Modem GPIO1 output acts as "Out of Idle" status indicator for Stream Data Mode to MCU.                     |  |

| 46    | PTD0        | ATTN                | MCU Port D Bit 0 drives the attention (ATTN) input of the modem to wake modem from Hibernate or Doze Mode. |  |

|       | PTE5/SPSCK1 | SPICLK <sup>1</sup> | MCU SPI master SPI clock output drives modem SPICLK slave clock input.                                     |  |

|       | PTE4/MOSI1  | MOSI <sup>1</sup>   | MCU SPI master MOSI output drives modem slave MOSI input                                                   |  |

|       | PTE3/MISO1  | MISO <sup>2</sup>   | Modem SPI slave MISO output drives MCU master MISO input                                                   |  |

|       | PTE2/SS1    | CE <sup>1</sup>     | MCU SPI master SS output drives modem slave CE input                                                       |  |

|       | IRQ         | M_IRQ               | Modem interrupt request M_IRQ output drives MCU IRQ input                                                  |  |

|       | PTD1        | RXTXEN <sup>1</sup> | MCU Port D Bit 1 drives the RXTXEN input to the modem to enable TX or RX or CCA operations.                |  |

|       | PTD3        | M_RST               | MCU Port D Bit 3 drives the reset MRST input to the modem.                                                 |  |

<sup>&</sup>lt;sup>1</sup> During low power modes, input must remain driven by MCU.

#### **NOTE**

To use the MCU and modem signals as described in Table 3, the MCU needs to be programmed appropriately for the stated function.

<sup>&</sup>lt;sup>2</sup> By default MISO is tri-stated when  $\overline{\text{CE}}$  is negated. For low power operation, miso\_hiz\_en (Bit 11, Register 07) should be set to zero so that MISO is driven low when  $\overline{\text{CE}}$  is negated.

# 3 MC1321x Serial Peripheral Interface (SPI)

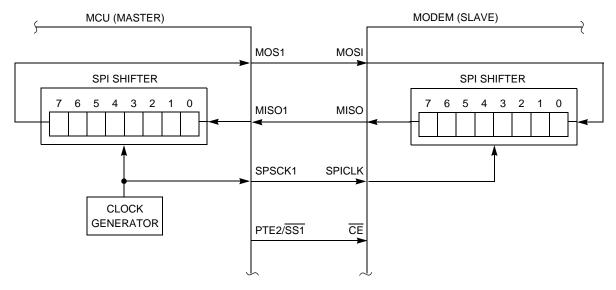

The MC1321x modem and CPU communicate primarily through the onboard SPI command channel. Figure 4 shows the SiP internal interconnects with the SPI bus highlighted. The MCU has a single SPI module that is dedicated to the modem SPI interface. The modem is a slave only and the MCU SPI must be programmed and used as a master only. Further, the SPI performance is limited by the modem constraints of 8 MHz SPI clock frequency, and use of the SPI must be programmed to meet the modem SPI protocol.

#### 3.1 SiP Level SPI Pin Connections

The SiP level SPI pin connections are all internal to the device. Figure 4 shows the SiP interconnections with the SPI bus highlighted.

Figure 4. MC1321x Internal Interconnects Highlighting SPI Bus

| MCU Signal  | Modem Signal | Description                                                            |  |

|-------------|--------------|------------------------------------------------------------------------|--|

| PTE5/SPSCK1 | SPICLK       | MCU SPI master SPI clock output drives modem SPICLK slave clock input. |  |

| PTE4/MOSI1  | MOSI         | MCU SPI master MOSI output drives modem slave MOSI input               |  |

| PTE3/MISO1  | MISO         | Modem SPI slave MISO output drives MCU master MISO input               |  |

| PTE2/SS1    | CE           | MCU SPI master SS output drives modem slave CE input                   |  |

Table 4. MC1321x Internal SPI Connections

#### 3.2 SPI Features

- MCU bus master

- Modem bus slave

- Programmable SPI clock rate; maximum rate is 8 MHz

- Double-buffered transmit and receive at MCU

- Serial clock phase and polarity must meet modem requirements (MCU control bits

- Slave select programmed to meet modem protocol

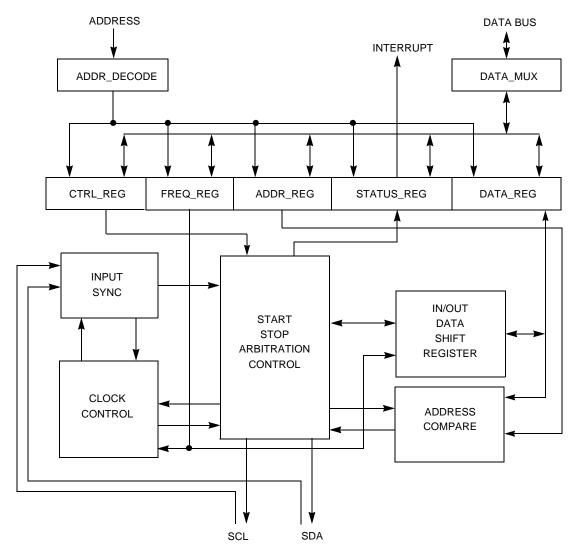

## 3.3 SPI System Block Diagram

Figure 5 shows the SPI system level diagram.

Figure 5. SPI System Block Diagram

Figure 5 shows the SPI modules of the MCU and modem in the master-slave arrangement. The MCU (master) initiates all SPI transfers. During a transfer, the master shifts data out (on the MOSI pin) to the slave while simultaneously shifting data in (on the MISO pin) from the slave. Although the SPI interface supports simultaneous data exchange between master and slave, the modem SPI protocol only uses data exchange in one direction at a time. The SPSCK signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input (SS1 pin).

# 4 802.15.4 Standard Modem

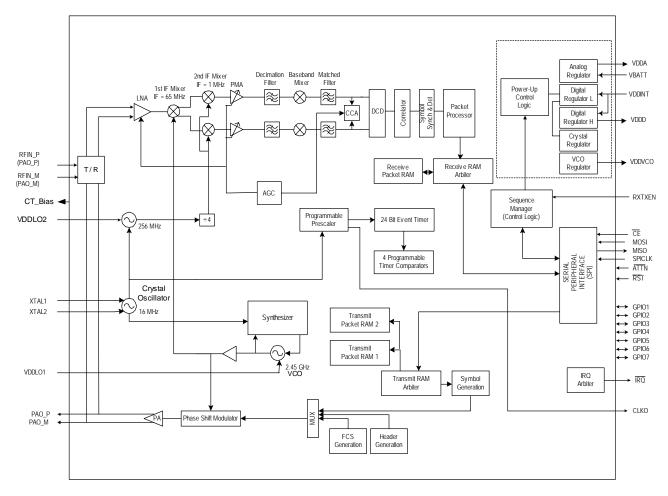

# 4.1 Block Diagram

Figure 6. 802.15.4 Standard Modem Block Diagram

#### 4.2 Data Transfer Modes

The 802.15.4 modem has two data transfer modes:

- 1. Packet Mode Data is buffered in on-chip RAM

- 2. Streaming Mode Data is processed word-by-word

The Freescale 802.15.4 MAC software only supports the streaming mode of data transfer. For proprietary applications, packet mode can be used to conserve MCU resources.

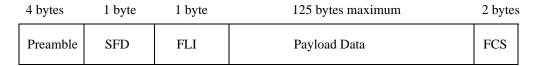

#### 4.3 Packet Structure

Figure 7 shows the packet structure of the 802.15.4 modem. Payloads of up to 125 bytes are supported. The 802.15.4 modem adds a four-byte preamble, a one-byte Start of Frame Delimiter (SFD), and a one-byte Frame Length Indicator (FLI) before the data. A Frame Check Sequence (FCS) is calculated and appended to the end of the data.

Figure 7. 802.15.4 modem Packet Structure

## 4.4 Receive Path Description

In the receive signal path, the RF input is converted to low IF In-phase and Quadrature (I & Q) signals through two down-conversion stages. A Clear Channel Assessment (CCA) can be performed based upon the baseband energy integrated over a specific time interval. The digital back end performs Differential Chip Detection (DCD), the correlator "de-spreads" the Direct Sequence Spread Spectrum (DSSS) Offset QPSK (O-QPSK) signal, determines the symbols and packets, and detects the data.

The preamble, SFD, and FLI are parsed and used to detect the payload data and FCS (which are stored in RAM in Packet Mode). A two-byte FCS is calculated on the received data and compared to the FCS value appended to the transmitted data, which generates a Cyclical Redundancy Check (CRC) result. A parameter of received energy during the reception called the Link Quality Indicator is measured over a 64 µs period after the packet preamble and stored in an SPI register.

If the 802.15.4 modem is in Packet Mode, the data is stored in RAM and processed as an entire packet. The MCU is notified that an entire packet has been received via an interrupt.

If the 802.15.4 modem is in streaming mode, the MCU is notified by a recurring interrupt on a word-by-word basis.

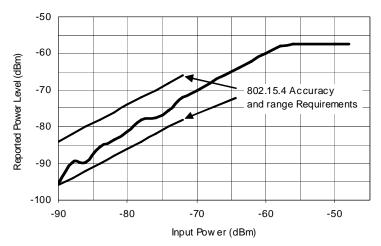

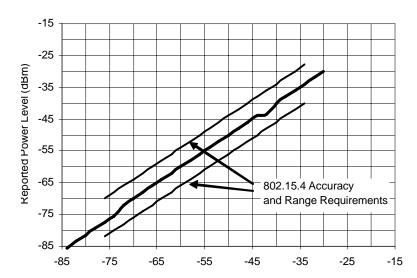

Figure 8 shows CCA reported power level versus input power. Note that CCA reported power saturates at about -57 dBm input power which is well above 802.15.4 Standard requirements.

Freescale Semiconductor

MC13211/212/213 Technical Data, Rev. 1.8

#### **NOTE**

For both graphs, the required 802.15.4 Standard accuracy and range limits are shown. A 3.5 dBm offset has been programmed into the CCA reporting level to center the level over temperature in the graphs.

Figure 8. Reported Power Level versus Input Power in Clear Channel Assessment Mode

Figure 9 shows energy detection/LQI reported level versus input power.

Figure 9. Reported Power Level Versus Input Power for Energy Detect or Link Quality Indicator

## 4.5 Transmit Path Description

For the transmit path, the TX data that was previously written to the internal RAM is retrieved (packet mode) or the TX data is clocked in via the SPI (stream mode), formed into packets per the 802.15.4 PHY, spread, and then up-converted to the transmit frequency.

If the 802.15.4 modem is in packet mode, data is processed as an entire packet. The data is first loaded into the TX buffer. The MCU then requests that the modem transmit the data. The MCU is notified via an interrupt when the whole packet has successfully been transmitted.

In streaming mode, the data is fed to the 802.15.4 modem on a word-by-word basis with an interrupt serving as a notification that the 802.15.4 modem is ready for more data. This continues until the whole packet is transmitted.

In both modes, a two-byte FCS is calculated in hardware from the payload data and appended to the packet. This done without intervention from the user.

## 4.6 Functional Description

The following sections provide a detailed description of the MC1321x functionality including the operating modes and the Serial Peripheral Interface (SPI).

#### 4.6.1 802.15.4 Modem Operational Modes

The 802.15.4 modem has a number of operational modes that allow for low-current operation. Transition from the Off to Idle mode occurs when  $\overline{M_RST}$  is negated. Once in Idle, the SPI is active and is used to control the IC. Transition to Hibernate and Doze modes is enabled via the SPI. These modes are summarized, along with the transition times, in Table 5. Current drain in the various modes is listed in Table 8, DC Electrical Characteristics.

Table 5. 802.15.4 Modem Mode Definitions and Transition Times

| Mode      | Definition                                                                                                                                                                                                                                      | Transition Time<br>To or From Idle |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Off       | All IC functions Off, Leakage only. M_RST asserted. Digital outputs are tri-stated including IRQ                                                                                                                                                | 10 - 25 ms to Idle                 |

| Hibernate | Crystal Reference Oscillator Off. (SPI not functional.) IC Responds to ATTN. Data is retained.                                                                                                                                                  | 7 - 20 ms to Idle                  |

| Doze      | Crystal Reference Oscillator On but CLKO output available only if Register 7, Bit 9 = 1 for frequencies of 1 MHz or less. (SPI not functional.) Responds to ATTN and can be programmed to enter Idle Mode through an internal timer comparator. | (300 + 1/CLKO) µs to Idle          |

| Idle      | Crystal Reference Oscillator On with CLKO output available. SPI active.                                                                                                                                                                         |                                    |

| Receive   | Crystal Reference Oscillator On. Receiver On.                                                                                                                                                                                                   | 144 µs from Idle                   |

| Transmit  | Crystal Reference Oscillator On. Transmitter On.                                                                                                                                                                                                | 144 µs from Idle                   |

## 4.6.2 Serial Peripheral Interface (SPI)

The MCU directs the 802.15.4 modem, checks its status, and reads/writes data to the device through the 4-wire SPI port. The transceiver operates as a SPI slave device only. A transaction between the host and the 802.15.4 modem occurs as multiple 8-bit bursts on the SPI. The modem SPI signals are:

- 1. Chip Enable ( $\overline{CE}$ ) A transaction on the SPI port is framed by the active low  $\overline{CE}$  input signal. A transaction is a minimum of 3 SPI bursts and can extend to a greater number of bursts.

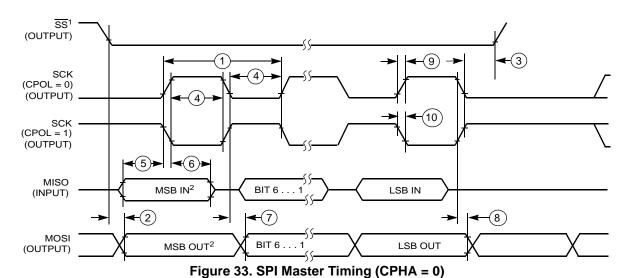

- 2. SPI Clock (SPICLK) The host drives the SPICLK input to the 802.15.4 modem. Data is clocked into the master or slave on the leading (rising) edge of the return-to-zero SPICLK and data out changes state on the trailing (falling) edge of SPICLK.

#### **NOTE**

For the MCU, the SPI clock format is the clock phase control bit CPHA = 0 and the clock polarity control bit CPOL = 0.

- 3. Master Out/Slave In (MOSI) Incoming data from the host is presented on the MOSI input.

- 4. Master In/Slave Out (MISO) The 802.15.4 modem presents data to the master on the MISO output.

Although the SPI port is fully static, internal memory, timer and interrupt arbiters require an internal clock (CLK<sub>core</sub>), derived from the crystal reference oscillator, to communicate from the SPI registers to internal registers and memory.

#### 4.6.2.1 SPI Burst Operation

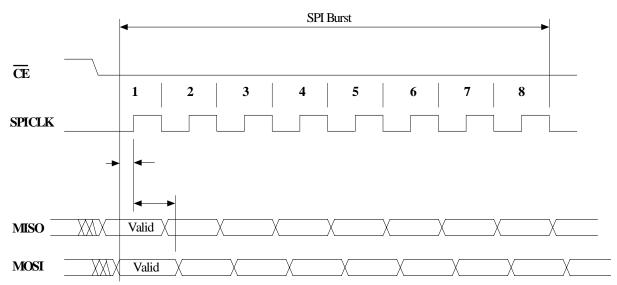

The SPI port of the MCU transfers data in bursts of 8 bits with most significant bit (MSB) first. The master (MCU) can send a byte to the slave (transceiver) on the MOSI line and the slave can send a byte to the master on the MISO line. Although an 802.15.4 modern transaction is three or more SPI bursts long, the timing of a single SPI burst is shown in Figure 10. The maximum SPI clock rate is 8 Mhz from the MCU because the modern is limited by this number.

Figure 10. SPI Single Burst Timing Diagram

MC13211/212/213 Technical Data, Rev. 1.8

#### 4.6.2.2 SPI Transaction Operation

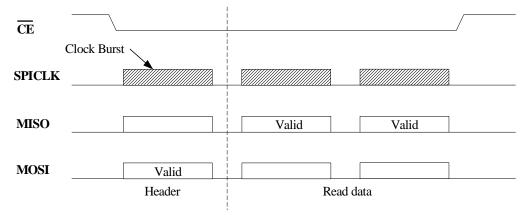

Although the SPI port of the MCU transfers data in bursts of 8 bits, the 802.15.4 modem requires that a complete SPI transaction be framed by  $\overline{\text{CE}}$ , and there will be three (3) or more bursts per transaction. The assertion of  $\overline{\text{CE}}$  to low signals the start of a transaction. The first SPI burst is a write of an 8-bit header to the transceiver (MOSI is valid) that defines a 6-bit address of the internal resource being accessed and identifies the access as being a read or write operation. In this context, a write is data written to the 802.15.4 modem and a read is data written to the SPI master. The following SPI bursts will be either the write data (MOSI is valid) to the transceiver or read data from the transceiver (MISO is valid).

Although the SPI bus is capable of sending data simultaneously between master and slave, the 802.15.4 modem never uses this mode. The number of data bytes (payload) will be a minimum of 2 bytes and can extend to a larger number depending on the type of access. After the final SPI burst,  $\overline{\text{CE}}$  is negated to high to signal the end of the transaction.

An example SPI read transaction with a 2-byte payload is shown in Figure 11.

Figure 11. SPI Read Transaction Diagram

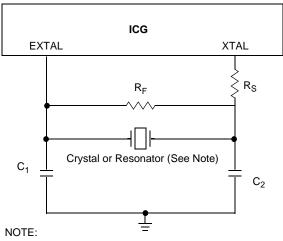

## 4.7 Modem Crystal Oscillator

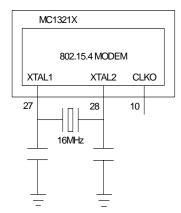

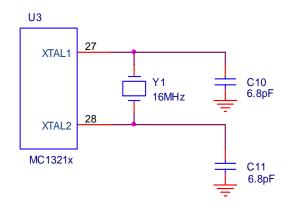

The modem crystal oscillator uses the following external pins as shown in Figure 12.

- 1. XTAL1 reference oscillator input.

- 2. XTAL2 reference oscillator output. Note that this pin should not be loaded as a reference source or to measure frequency; instead use CLKO to measure or supply 16 MHz.

Figure 12. Modem Crystal Oscillator

The 802.15.4 Standard requires that several frequency tolerances be kept within  $\pm 40$  ppm accuracy. This means that a total offset up to 80 ppm between transmitter and receiver will still result in acceptable performance. The primary determining factor in meeting the 802.15.4 Standard is the tolerance of the crystal oscillator reference frequency. A number of factors can contribute to this tolerance and a crystal specification will quantify each of them:

- 1. The initial (or make) tolerance of the crystal resonant frequency itself.

- 2. The variation of the crystal resonant frequency with temperature.

- 3. The variation of the crystal resonant frequency with time, also commonly known as aging.

- 4. The variation of the crystal resonant frequency with load capacitance, also commonly known as pulling. This is affected by:

- a) The external load capacitor values initial tolerance and variation with temperature

- b) The internal trim capacitor values initial tolerance and variation with temperature

- c) Stray capacitance on the crystal pin nodes including stray on-chip capacitance, stray package capacitance and stray board capacitance; and its initial tolerance and variation with temperature

Freescale has specified that a 16 MHz crystal with a <9 pF load capacitance is required. The 802.15.4 modem does not contain a reference divider, so 16 MHz is the only frequency that can be used. A crystal requiring higher load capacitance is prohibited because a higher load on the amplifier circuit may compromise its performance. The crystal manufacturer defines the load capacitance as that total external capacitance seen across the two terminals of the crystal. The oscillator amplifier configuration used in the 802.15.4 modem requires two balanced load capacitors from each terminal of the crystal to ground. As such, the capacitors are seen to be in series by the crystal, so each must be <18 pF for proper loading.

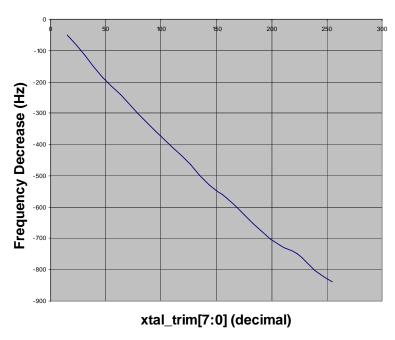

The modem uses the 16 MHz crystal oscillator as the reference oscillator for the system and a programmable warp capability is provided. It is controlled by programming CLKO\_Ctl Register 0A, Bits

15-8 (xtal\_trim[7:0]). The trimming procedure varies the frequency by a few hertz per step, depending on the type of crystal. The high end of the frequency spectrum is set when xtal\_trim[7:0] is set to zero. As xtal\_trim[7:0] is increased, the frequency is decreased. Accuracy of this feature can be observed by varying xtal\_trim[7:0] and using a spectrum analyzer or frequency counter to track the change in frequency of the crystal signal. The reference oscillator frequency can be measured at the CLKO contact by programming CLKO\_Ctl Register 0A, Bits 2-0, to value 000.

Figure 13 shows typical oscillator frequency decrease versus the value programmed in xtal\_trim[7:0].

Figure 13. Crystal Frequency Variation vs. xtal\_trim[7:0]

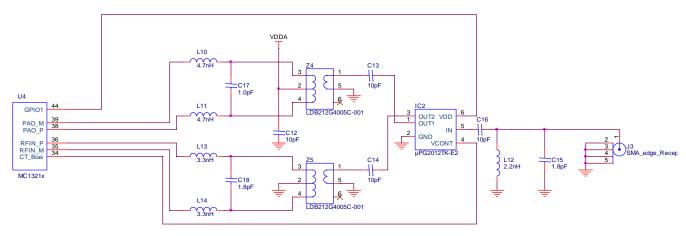

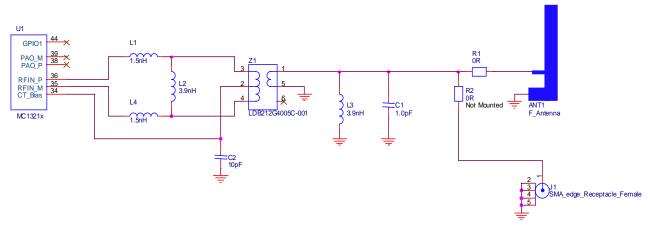

# 4.8 Radio Usage

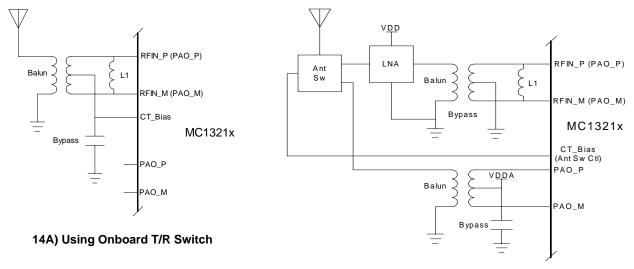

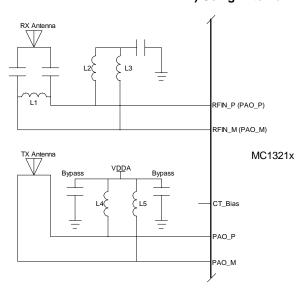

The MC1321x RF analog interface has been designed to provide maximum flexibility as well as low external part count and cost. An on-chip transmit/receive (T/R) switch with bias switch (CT\_Bias) can be used for a simple single antenna interface with a balun. Alternately, separate full differential RFIN and PAO outputs can be utilized for separate RX and TX antennae or external LNA and PA designs.

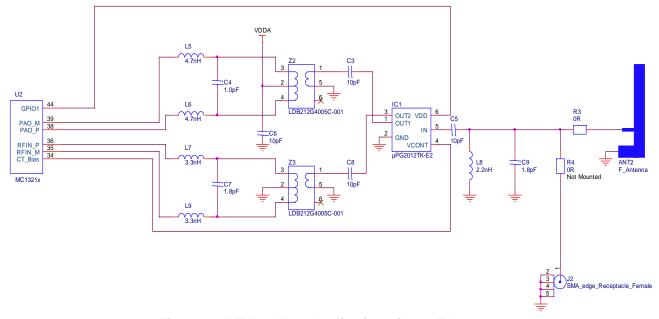

Figure 14 shows three possible configurations for the transceiver radio RF usage.

- 1. Figure 14A shows a single antenna configuration in which the MC1321x internal T/R switch is used. The balun converts the single-ended antenna to differential signals that interface to the RFIN\_x (PAO\_x) pins of the radio. The CT\_Bias pin provides the proper bias point to the balun depending on operation, that is, CT\_Bias is at VDDA voltage for transmit and is at ground for receive. The internal T/R switch enables the signal to an onboard LNA for receive and enables the onboard PAs for transmit.

- 2. Figure 14B shows a single antenna configuration with an external low noise amplifier (LNA) for greater range. An external antenna switch is used to multiplex the antenna between receive and transmit. An LNA is in the receive path to add gain for greater receive sensitivity. Two external baluns are required to convert the single-ended antenna switch signals to the differential signals

- required by the radio. Separate RFIN and PAO signals are provided for connection with the baluns, and the CT\_Bias signal is programmed to provide the external switch control. The polarity of the external switch control is selectable.

- 3. Figure 14C shows a dual antenna configuration where there is a RX antenna and a TX antenna. For the receive side, the RX antenna is ac-coupled to the differential RFIN inputs and these capacitors along with inductor L1 form a matching network. Inductors L2 and L3 are ac-coupled to ground to form a frequency trap. For the transmit side, the TX antenna is connected to the differential PAO outputs, and inductors L4 and L5 provide dc-biasing to VDDA but are ac isolated.

14B) Using External Antenna Switch With LNA

14C) Using Dual Antennae

Figure 14. Using the MC1321x with External RF Components

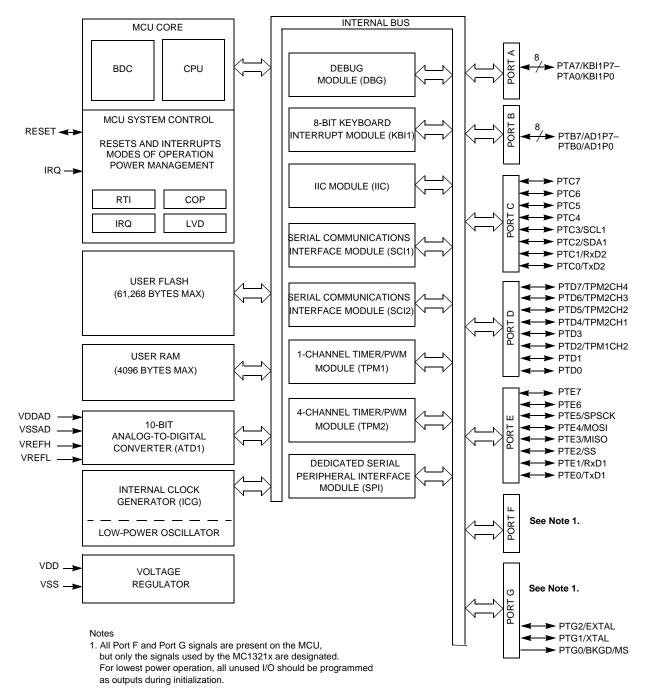

## 5 MCU

## 5.1 MCU Block Diagram

Timer channels are limited as noted due to use of Port D I/O for internal signals.

Figure 15. MCU Block Diagram (HCS08, Version A)

## 5.2 MCU Modes of Operation

The MCU has multiple operational modes to facilitate maximum system performance while also providing low-power modes. In the MC1321x, the MCU can use the following modes:

- Run

- Wait

- Stop2

- Stop3

#### **NOTE**

- The MCU can also be programmed for Stop1 mode, but this mode IS NOT USABLE. The reset to the modem function is controlled by an MCU GPIO and the GPIO state must be maintained during the MCU "stop" condition. Stop1 mode does not control I/O states as required during modem power down condition.

- To attain specified Stop2 and Stop3 currents, all unused port signals must be programmed to a known state (recommended as outputs in the low state)

#### 5.2.1 Run Mode

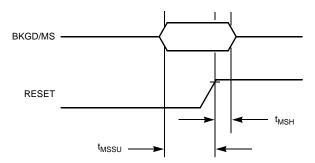

This is the normal operating mode for the HCS08. This mode is selected when the BKGD/MS pin is high at the rising edge of reset. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at \$FFFE:\$FFFF after reset.

#### 5.2.2 Wait Mode

Wait Mode is entered by executing a WAIT instruction. Upon execution of the WAIT instruction, the CPU enters a low-power state in which it is not clocked. The I bit in CCR is cleared when the CPU enters the wait mode, enabling interrupts. When an interrupt request occurs, the CPU exits the wait mode and resumes processing, beginning with the stacking operations leading to the interrupt service routine.

While the MCU is in Wait Mode, there are some restrictions on which background debug commands can be used. Only the BACKGROUND command and memory-access-with-status commands are available when the MCU is in wait mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from Wait Mode and enter active background mode.

# 5.2.3 Stop 2

The Stop2 Mode provides very low standby power consumption and maintains the contents of RAM and the current state of all of the I/O pins. Stop2 can be entered only if the LVD circuit is not enabled in Stop Modes (either LVDE or LVDSE not set).

Before entering Stop2 Mode, the user must save the contents of the I/O port registers, as well as any other memory-mapped registers they want to restore after exit of Stop2, to locations in RAM. Upon exit of Stop2, these values can be restored by user software before pin latches are opened.

When the MCU is in Stop2 Mode, all internal circuits that are powered from the voltage regulator are turned off, except for the RAM. The voltage regulator is in a low-power standby state, as is the ATD. Upon entry into Stop2, the states of the I/O pins are latched. The states are held while in Stop2 Mode and after exiting Stop2 Mode until a 1 is written to PPDACK in SPMSC2.

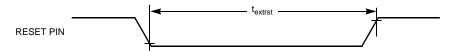

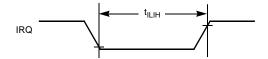

Exit from Stop2 is performed by asserting either of the wake-up pins:  $\overline{RESET}$  or IRQ, or by an RTI interrupt. IRQ is always an active low input when the MCU is in Stop2, regardless of how it was configured before entering Stop2.

Upon wake-up from Stop2 Mode, the MCU will start up as from a power-on reset (POR) except pin states remain latched. The CPU will take the reset vector. The system and all peripherals will be in their default reset states and must be initialized.

After waking up from Stop2, the PPDF bit in SPMSC2 is set. This flag may be used to direct user code to go to a Stop2 recovery routine. PPDF remains set and the I/O pin states remain latched until a 1 is written to PPDACK in SPMSC2.

To maintain I/O state for pins that were configured as general-purpose I/O, the user must restore the contents of the I/O port registers, which have been saved in RAM, to the port registers before writing to the PPDACK bit. If the port registers are not restored from RAM before writing to PPDACK, then the register bits will assume their reset states when the I/O pin latches are opened and the I/O pins will switch to their reset states.

For pins that were configured as peripheral I/O, the user must reconfigure the peripheral module that interfaces to the pin before writing to the PPDACK bit. If the peripheral module is not enabled before writing to PPDACK, the pins will be controlled by their associated port control registers when the I/O latches are opened.

A separate self-clocked source (approximately 1 kHz) for the real-time interrupt allows a walk-up from Stop2 or Stop3 Modes with no external components. When RTIS2:RTIS1:RTIS0 = 0:0:0, the real-time interrupt function and this 1-kHz source are disabled. Power consumption is lower when the 1-kHz source is disabled, but in that case the real-time interrupt cannot wake the MCU from stop.

# 5.2.4 Stop3

Upon entering the Stop3 Mode, all of the clocks in the MCU, including the oscillator itself, are halted. The ICG is turned off, the ATD is disabled, and the voltage regulator is put in standby. The states of all of the internal registers and logic, as well as the RAM content, are maintained. The I/O pin states are not latched at the pin as in Stop2. Instead they are maintained by virtue of the states of the internal logic driving the pins being maintained.

Exit from Stop3 is performed by asserting  $\overline{RESET}$ , an asynchronous interrupt pin, or through the real-time interrupt. The asynchronous interrupt pins are the IRQ or KBI pins.

If Stop3 is exited by means of the RESET pin, then the MCU will be reset and operation will resume after taking the reset vector. Exit by means of an asynchronous interrupt or the real-time interrupt will result in the MCU taking the appropriate interrupt vector.

A separate self-clocked source (approximately 1 kHz) for the real-time interrupt allows a wake up from Stop2 or Stop3 Modes with no external components. When RTIS2:RTIS1:RTIS0 = 0:0:0, the real-time interrupt function and this 1-kHz source are disabled. Power consumption is lower when the 1-kHz source is disabled, but in that case the real-time interrupt cannot wake the MCU from stop.

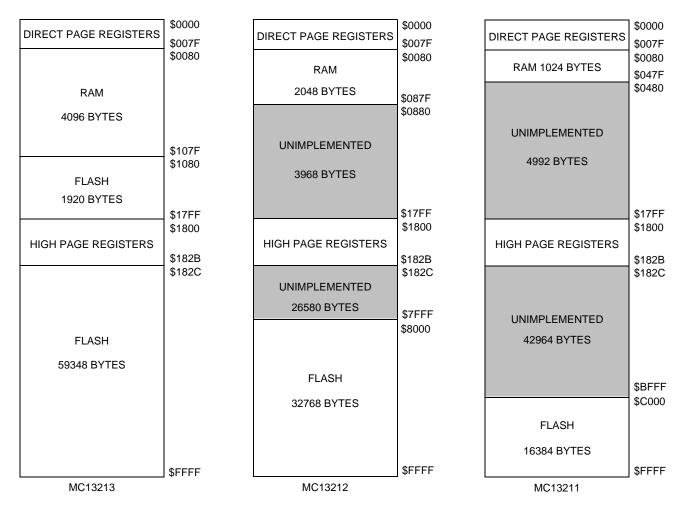

## 5.3 MCU Memory

As shown in Figure 16, on-chip memory in the MC1321x series of MCUs consists of RAM, FLASH program memory for non-volatile data storage, plus I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (\$0000 through \$007F)

- High-page registers (\$1800 through \$182B)

- Nonvolatile registers (\$FFB0 through \$FFBF)

Figure 16. MC1321X Memory Maps

MC13211/212/213 Technical Data, Rev. 1.8

## 5.4 MCU Internal Clock Generator (ICG)

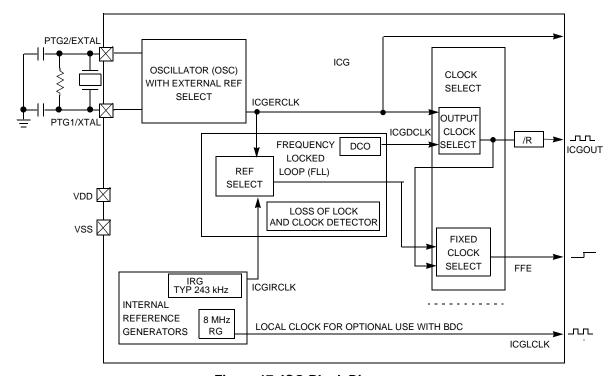

The ICG provides multiple options for MCU clock sources. This block along with the ability to provide the MCU clock form the modem offers a user great flexibility when making choices between cost, precision, current draw, and performance. As seen in Figure 17, the ICG consists of four functional blocks.

- Oscillator Block The Oscillator Block provides means for connecting an external crystal or

resonator. Two frequency ranges are software selectable to allow optimal start-up and stability.

Alternatively, the oscillator block can be used to route an external square wave to the MCU system

clock. External sources such as the modem CLKO output can provide a low cost source or a very

precise clock source. The oscillator is capable of being configured for low power mode or high

amplitude mode as selected by HGO.

- Internal Reference Generator The Internal Reference Generator consists of two controlled clock sources. One is designed to be approximately 8 MHz and can be selected as a local clock for the background debug controller. The other internal reference clock source is typically 243 kHz and can be trimmed for finer accuracy via software when a precise timed event is input to the MCU. This provides a highly reliable, low-cost clock source.

- **Frequency-Locked Loop** A Frequency-Locked Loop (FLL) stage takes either the internal or external clock source and multiplies it to a higher frequency. Status bits provide information when the circuit has achieved lock and when it falls out of lock. Additionally, this block can monitor the external reference clock and signals whether the clock is valid or not.

- Clock Select Block The Clock Select Block provides several switch options for connecting different clock sources to the system clock tree. ICGDCLK is the multiplied clock frequency out of the FLL, ICGERCLK is the reference clock frequency from the crystal or external clock source, and FFE (fixed frequency enable) is a control signal used to control the system fixed frequency clock (XCLK). ICGLCLK is the clock source for the background debug controller (BDC).

The module is intended to be very user friendly with many of the features occurring automatically without user intervention.

#### 5.4.1 Features

Features of the ICG and clock distribution system:

- Several options for the MCU primary clock source allow a wide range of cost, frequency, and precision choices:

- 32 kHz–100 kHz crystal or resonator

- 1 MHz–16 MHz crystal or resonator

- External clock supplied by modem CLKO or other source

- Internal reference generator

- Defaults to self-clocked mode to minimize startup delays

- Frequency-locked loop (FLL) generates 8 MHz to 40 MHz (for bus rates up to 20 MHz). When using modem CLKO as external source, maximum FLL frequency is 32 MHz (16 MHz bus rate) with CLKO = 16 MHz or maximum FLL frequency is 40 MHz (20 MHz bus rate) with CLKO = 4 MHz.

- Uses external or internal clock as reference frequency

- Automatic lockout of non-running clock sources

- Reset or interrupt on loss of clock or loss of FLL lock

- Digitally-controlled oscillator (DCO) preserves previous frequency settings, allowing fast frequency lock when recovering from stop3 mode

- DCO will maintain operating frequency during a loss or removal of reference clock. When FLL is

engaged (FEE or FEI) loss of lock or loss of clock adds a divide-by-2 to ICG to prevent

over-clocking of the system.

- Post-FLL divider selects 1 of 8 bus rate divisors (/1 through /128)

- Separate self-clocked source for real-time interrupt

- Trimmable internal clock source supports SCI communications without additional external components

- Automatic FLL engagement after lock is acquired

- Selectable low-power/high-gain oscillator modes

#### 5.4.2 Modes of Operation

This section provides a high-level description only.

- Mode 1 Off

- The output clock, ICGOUT, is static. This mode may be entered when the STOP instruction is executed.

- Mode 2 Self-clocked (SCM)

- Default mode of operation that is entered out of reset. The ICG's FLL is open loop and the digitally controlled oscillator (DCO) is free running at a frequency set by the filter bits.

- Mode 3 FLL engaged internal (FEI)

- In this mode, the ICG's FLL is used to create frequencies that are programmable multiples of the internal reference clock.

- FLL engaged internal unlocked is a transition state which occurs while the FLL is attempting to lock. The FLL DCO frequency is off target and the FLL is adjusting the DCO to match the target frequency.

- FLL engaged internal locked is a state which occurs when the FLL detects that the DCO is locked to a multiple of the internal reference.

- Mode 4 FLL bypassed external (FBE)

- In this mode, the ICG is configured to bypass the FLL and use an external clock as the clock source.

- Mode 5 FLL engaged external (FEE)

- The ICG's FLL is used to generate frequencies that are programmable multiples of the external clock reference.

- FLL engaged external unlocked is a transition state which occurs while the FLL is attempting to lock. The FLL DCO frequency is off target and the FLL is adjusting the DCO to match the target frequency.

— FLL engaged external locked is a state which occurs when the FLL detects that the DCO is locked to a multiple of the internal reference.

Figure 17 is a top-level diagram that shows the functional organization of the internal clock generation (ICG) module.

Figure 17. ICG Block Diagram

# 5.5 Central Processing Unit (CPU)

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

#### 5.5.1 CPU Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

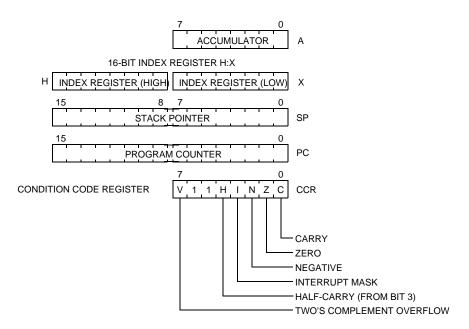

# 5.5.2 Programmer's Model and CPU Registers

Figure 18 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 18. CPU Registers

## 5.6 Parallel Input/Output

The MC1321x HCS08 has seven I/O ports which include a total of 56 general-purpose I/O signals (one of these pins, PTG0, is output only). The MC1321x family does not use all the these signals as denoted in Figure 15. Port F and part of port G are not utilized. The MC1321x family makes use of the remaining I/O as pinned-out I/O or as internally dedicated signal for communication with the 802.15.4 modem.

As stated above port F and part of port G are not utilized. These signals and any unused IO should be programmed as outputs during initialization for lowest power operation. Many of these pins are shared with on-chip peripherals such as timer systems, various communication ports, or keyboard interrupts. When these other modules are not controlling the port pins, they revert to general-purpose I/O control. For each I/O pin, a port data bit provides access to input (read) and output (write) data, a data direction bit controls the direction of the pin, and a pullup enable bit enables an internal pullup device (provided the pin is configured as an input), and a slew rate control bit controls the rise and fall times of the pins. Parallel I/O features include:

- A total of 32 general-purpose I/O pins in seven ports (PTG0 is output only)

- High-current drivers on port C

- Hysteresis input buffers

- Software-controlled pullups on each input pin

- Software-controlled slew rate output buffers

- Eight port A pins shared with KBI1

- Eight port B pins shared with ATD1

- Eight high-current port C pins shared with SCI2 and IIC1

- Eight port D pins shared with TPM1 and TPM2

- Eight port E pins shared with SCI1 and SPI1

- Eight port G pins shared with EXTAL, XTAL, and BKGD/MS

#### **NOTE**

Not all port G signals and no port F signals are bonded out, but are present in the MCU hardware (see Figure 15). These port I/O signals should be programmed as outputs set to the low state.

# 5.7 MCU Peripherals

## 5.7.1 Modem Dedicated Serial Peripheral Interface (SPI) Module

The HCS08 provides one serial peripheral interface (SPI) module which is connected within the SiP to the modem SPI port. The four pins associated with SPI functionality are shared with port E pins 2–5. When the SPI is enabled, the direction of pins is controlled by module configuration.

The MCU SPI port is used only in master mode on the MC1321x family. The user must program the SPI module for the proper characteristics as listed in the features below and also program the  $\overline{SS}$  signal to have the proper use to support the modem transaction protocol for the modem  $\overline{CE}$  signal.

#### **5.7.1.1 SPI Features**

Features of the SPI module use include:

- Used in master mode only

- Programmable transmit bit rate (maximum usable rate is 8 MHz with modem)

- Double-buffered transmit and receive

- Serial clock phase and polarity option must be programmed to CPHA = 0 and CPOL = 0

- Programmable slave select output to support modem SPI protocol

- MSB-first data transfer

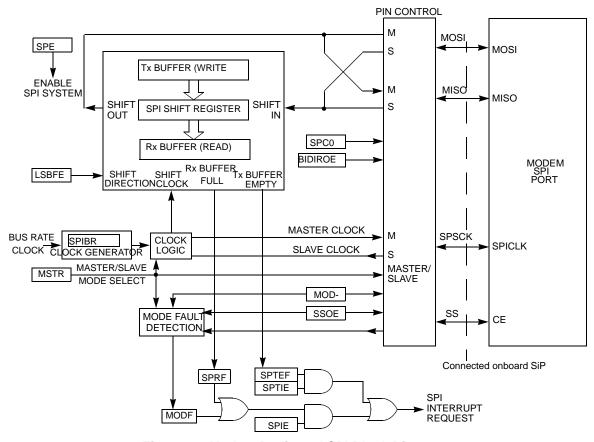

#### 5.7.1.2 SPI Module Block Diagram

Figure 19 is a block diagram of the SPI module. The central element of the SPI is the SPI shift register. Data is written to the double-buffered transmitter (write to SPI1D) and gets transferred to the SPI shift register at the start of a data transfer. After shifting in a byte of data, the data is transferred into the double-buffered receiver where it can be read (read from SPI1D). Pin multiplexing logic controls connections between MCU pins and the SPI module.

When the SPI is configured as a master, the clock output is routed to the SPSCK pin, the shifter output is routed to MOSI, and the shifter input is routed from the MISO pin.

Figure 19. Modem Dedicated SPI Block Diagram

MC13211/212/213 Technical Data, Rev. 1.8

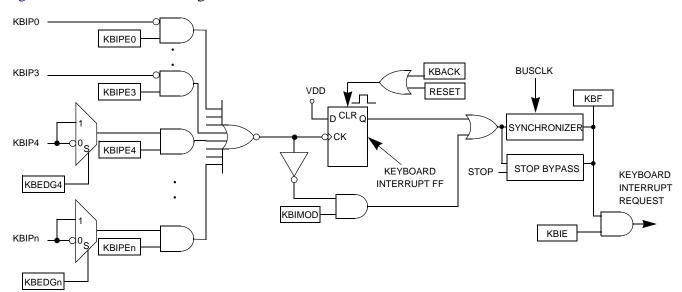

### 5.7.2 Keyboard Interrupt (KBI) Module

The HCS08 has one KBI module with eight keyboard interrupt inputs that share port A pins.

The KBI module allows up to eight pins to act as additional interrupt sources. Four of these pins allow falling-edge sensing while the other four can be configured for either rising-edge sensing or falling-edge sensing. The sensing mode for all eight pins can also be modified to detect edges and levels instead of only edges.

This on-chip peripheral module is called a keyboard interrupt (KBI) module because originally it was designed to simplify the connection and use of row-column matrices of keyboard switches. However, these inputs are also useful as extra external interrupt inputs and as an external means of waking up the MCU from stop or wait low-power modes.

#### 5.7.3 KBI Features

The keyboard interrupt (KBI) module features include:

- Keyboard interrupts selectable on eight port pins:

- Four falling-edge/low-level sensitive

- Four falling-edge/low-level or rising-edge/high-level sensitive

- Choice of edge-only or edge-and-level sensitivity

- Common interrupt flag and interrupt enable control

- Capable of waking up the MCU from stop3 or wait mode

### 5.7.3.1 KBI Block Diagram

Figure 20 shows the block diagram for the KBI module.

Figure 20. KBI Block Diagram

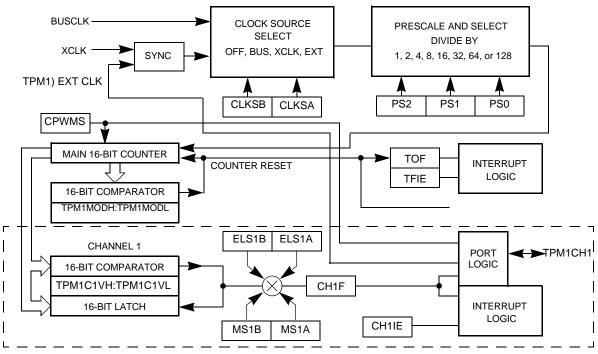

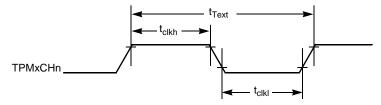

#### 5.7.4 Timer/PWM (TPM) Module Introduction

The HCS08 includes two independent Timer/PWM (TPM) modules which support traditional input capture, output compare, or buffered edge-aligned pulse-width modulation (PWM) on each channel. A control bit in each TPM configures all channels in that timer to operate as center-aligned PWM functions. In each of these two TPMs, timing functions are based on a separate 16-bit counter with prescaler and modulo features to control frequency and range (period between overflows) of the time reference. This timing system is ideally suited for a wide range of control applications, and the center-aligned PWM capability on the 3-channel TPM extends the field of applications to motor control in small appliances.

The use of the fixed system clock, XCLK, as the clock source for either of the TPM modules allows the TPM prescaler to run using the oscillator rate divided by two (ICGERCLK/2). This clock source must be selected only if the ICG is configured in either FBE or FEE mode. In FBE mode, this selection is redundant because the BUSCLK frequency is the same as XCLK. In FEE mode, the proper conditions must be met for XCLK to equal ICGERCLK/2. Selecting XCLK as the clock source with the ICG in either FEI or SCM mode will result in the TPM being non-functional.

#### 5.7.4.1 TPM Features

The timer system in the MC1321x family MCU includes a one external 4-channel (5-channel internal) TPM1 and one external 1-channel (3-channel internal) TPM2. Timer system features include

- A total of 5 external channels:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

- Each TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on all channels

- Clock source to prescaler for each TPM is independently selectable as bus clock, fixed system clock, or an external pin

- Prescale taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- 16-bit free-running or up/down (CPWM) count operation

- 16-bit modulus register to control counter range

- Timer system enable

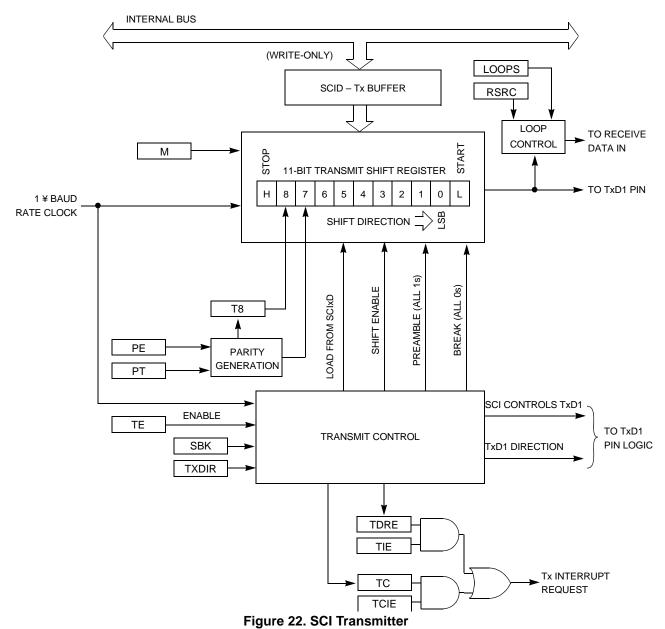

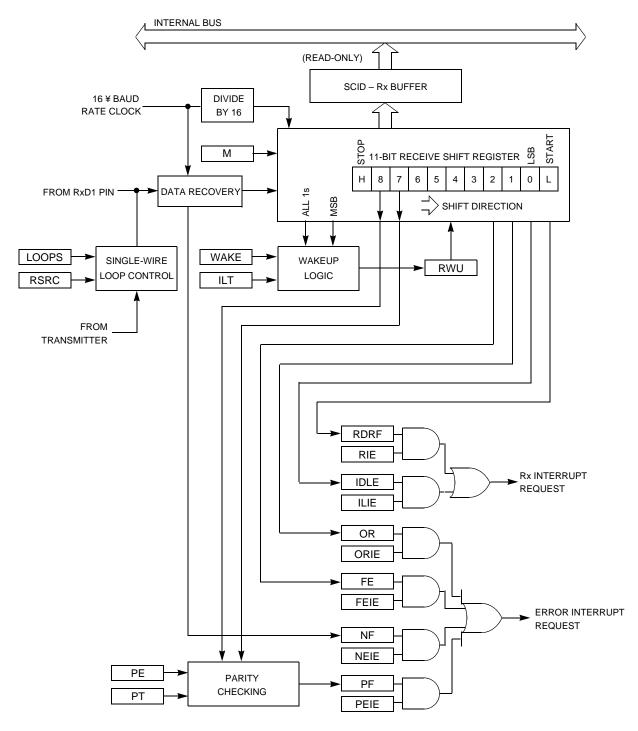

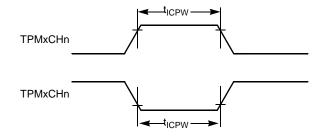

- One interrupt per channel plus terminal count interrupt