## LatticeSC/M Family flexiPCS Data Sheet

DS1005 Version 02.0, June 2011

# Table of Contents LatticeSC/M Family flexiPCS Data Sheet

| June | 2011 |

|------|------|

|      |      |

| Introduction to flexiPCS                    |      |

|---------------------------------------------|------|

| flexiPCS™ Features                          | 1-1  |

| flexiPCS Introduction                       | 1-2  |

| Architecture Overview                       | 1-2  |

| flexiPCS Quad                               | 1-2  |

| flexiPCS Channel                            | 1-3  |

| Per Channel PCS/FPGA Interface Ports        | 1-4  |

| Using this Data Sheet                       |      |

| SERDES Functionality/Electrical & Timing    | 2-1  |

| Introduction                                | 2-1  |

| LatticeSC flexiPCS Quad Module              | 2-1  |

| Quad and Channel Option Control             | 2-1  |

| Register Map Addressing                     | 2-1  |

| Auto-Configuration                          | 2-3  |

| SERDES Functionality                        | 2-4  |

| SERDES Port Description                     | 2-6  |

| SERDES Functionality Detailed Description   | 2-8  |

| SERDES Powerup                              | 2-8  |

| Clocks & Resets                             | 2-9  |

| Rate Mode Registers                         | 2-12 |

| Locked Reference and Transmit Clocks        | 2-17 |

| Transmit Clocks                             | 2-18 |

| Receive Clocks                              | 2-18 |

| Transmit Data                               | 2-22 |

| Transmit Data Skew                          | 2-23 |

| Receive Data                                |      |

| Low Speed SERDES Receiver Operation         |      |

| Status Interrupt Registers                  |      |

| Receive CDR Loss of Lock Interrupt Usage    |      |

| flexiPCS Reset Sequences                    |      |

| flexiPCS Power Down Control Signals         |      |

| SERDES Electrical & Timing Characteristics  |      |

| SERDES Performance                          | 2-31 |

| SERDES High Speed Data Transmitter          |      |

| SERDES High Speed Data Receiver             |      |

| Interfacing to Reference Clock CML Buffers  |      |

| SERDES Power                                |      |

| SERDES Power Supply Sequencing Requirements |      |

| SERDES Power Supply Requirements            |      |

| SERDES Power Supply Package Requirements    |      |

| Power-Down/Power-Up Specification           | 2-38 |

| 8-bit and 10-bit SERDES Only Modes          | 3-1  |

| Introduction                                |      |

| LatticeSC flexiPCS Quad Module              | 3-1  |

| Quad and Channel Option Control             | 3-1  |

| Register Map Addressing                     |      |

| Auto-Configuration                          |      |

| 8-bit SERDES Only Register Settings         | 3-4  |

| 8-bit SERDES Only Auto-Configuration Example               | 3-4 |

|------------------------------------------------------------|-----|

| 10-bit SERDES Only Register Settings                       |     |

| 10-bit SERDES Only Auto-Configuration Example              | 3-6 |

| 8-bit SERDES Only Mode                                     |     |

| 8-bit SERDES Only Mode Pin Description                     | 3-8 |

| 8-bit SERDES Only Mode Detailed Description                |     |

| Clocks & Resets                                            |     |

| Transmit Data                                              |     |

| Receive Data                                               |     |

| Control & Status                                           |     |

| 10-bit SERDES Only Mode                                    |     |

| 10-bit SERDES Only Mode Pin Description                    |     |

| 10-bit SERDES Only Mode Detailed Description               |     |

| Clocks & Resets                                            |     |

| Transmit Data                                              |     |

| Receive Data                                               |     |

| Control & Status                                           |     |

| Generic 8b10b Mode                                         |     |

| Introduction                                               |     |

| LatticeSC flexiPCS Quad Module                             |     |

| Quad and Channel Option Control                            |     |

| Register Map Addressing                                    |     |

| Auto-Configuration                                         |     |

| Generic 8b10b Register Settings                            |     |

| Generic 8b10b Auto-Configuration Example                   |     |

| Generic 8b10b Mode                                         |     |

| Generic 8b10b Mode Pin Description                         |     |

| Generic 8b10b Mode Detailed Description                    |     |

| Clocks & Resets                                            |     |

| Transmit Data                                              |     |

| Receive Data                                               |     |

| Control & Status                                           |     |

| Status Interrupt Registers                                 |     |

| Gigabit Ethernet Mode                                      |     |

| Introduction                                               |     |

| LatticeSC flexiPCS Quad Module                             |     |

| Quad and Channel Option Control                            |     |

| Register Map Addressing                                    |     |

| Auto-Configuration                                         |     |

| Gigabit Ethernet Register Settings                         |     |

| Gigabit Ethernet Auto-Configuration                        |     |

| Gigabit Ethernet ModeGigabit Ethernet Mode Pin Description |     |

| Gigabit Ethernet Mode Detailed Description                 |     |

| Clocks & Resets                                            |     |

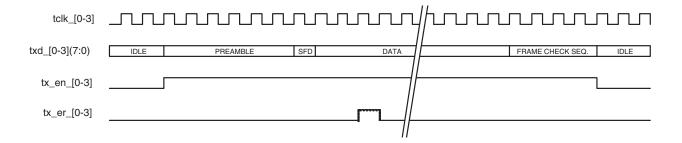

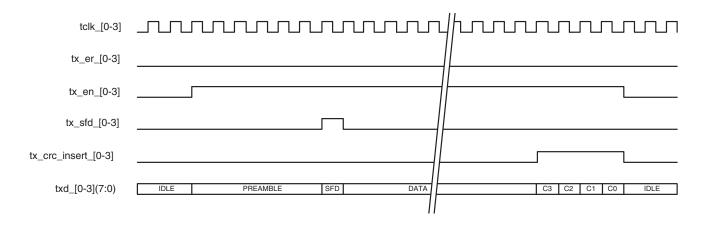

| Transmit Data                                              |     |

| Receive Data                                               |     |

| Auto-Negotiation                                           |     |

| Control & Status                                           |     |

| Status Interrupt Registers                                 |     |

| Fibre Channel Mode                                         |     |

| Introduction                                               |     |

| LatticeSC flexiPCS Quad Module                             |     |

| Quad and Channel Option Control                            |     |

|                                                            |     |

| Register Map Addressing                       |      |

|-----------------------------------------------|------|

| Auto-Configuration                            |      |

| Fibre Channel Register Settings               |      |

| Fibre Channel Auto-Configuration Example      |      |

| Fibre Channel Mode                            |      |

| Fibre Channel Mode Pin Description            |      |

| Fibre Channel Mode Detailed Description       |      |

| Clocks & Resets                               |      |

| Transmit Data                                 |      |

| Receive Data                                  |      |

| Control & Status                              |      |

| Status Interrupt Registers                    |      |

| XAUI Mode                                     |      |

| Introduction                                  |      |

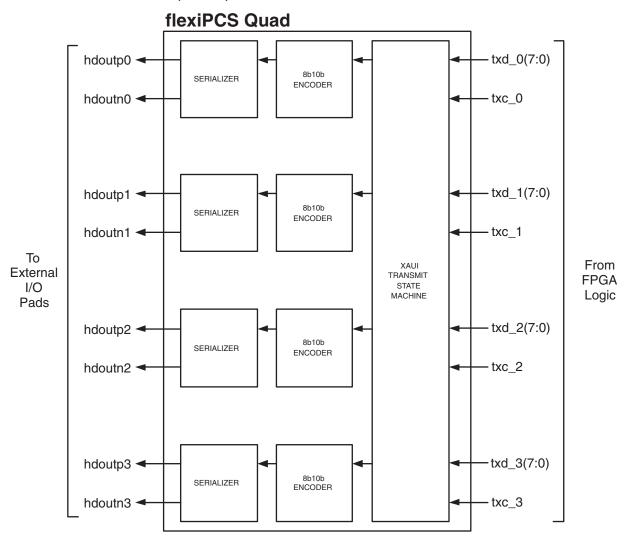

| LatticeSC flexiPCS Quad Module                |      |

| Quad and Channel Option Control               |      |

| Register Map Addressing                       |      |

| Auto-Configuration                            |      |

| XAUI Register Settings                        |      |

| XAUI Auto-Configuration Example               |      |

| XAUI Mode                                     |      |

| XAUI Mode Pin Descriptions                    |      |

| XAUI Mode Detailed Description                |      |

| Clocks & Resets                               |      |

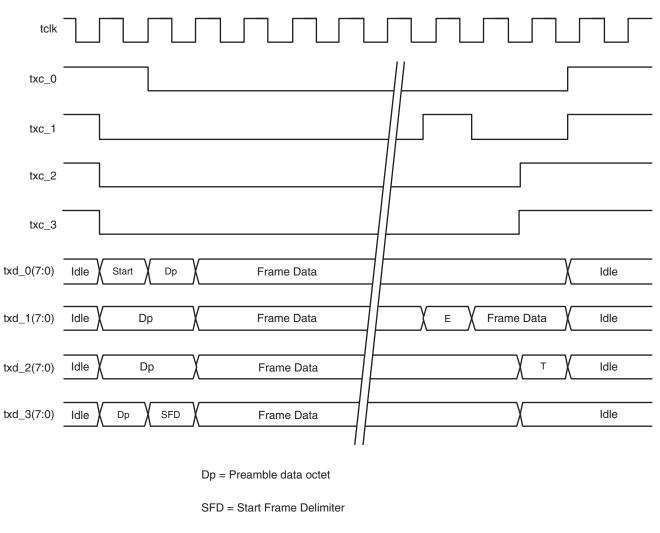

| Transmit Data                                 |      |

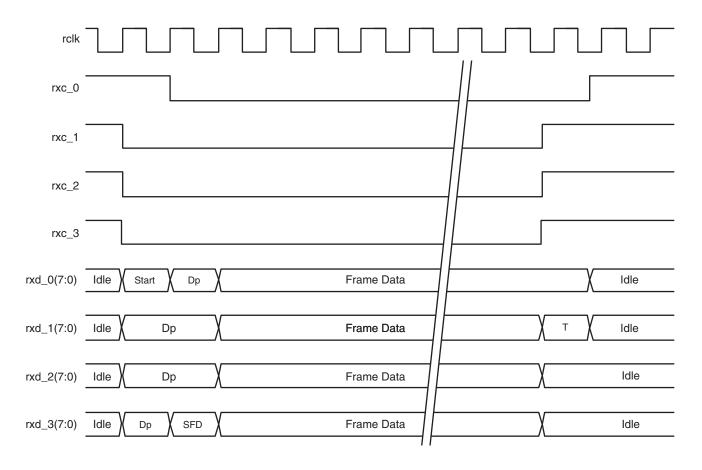

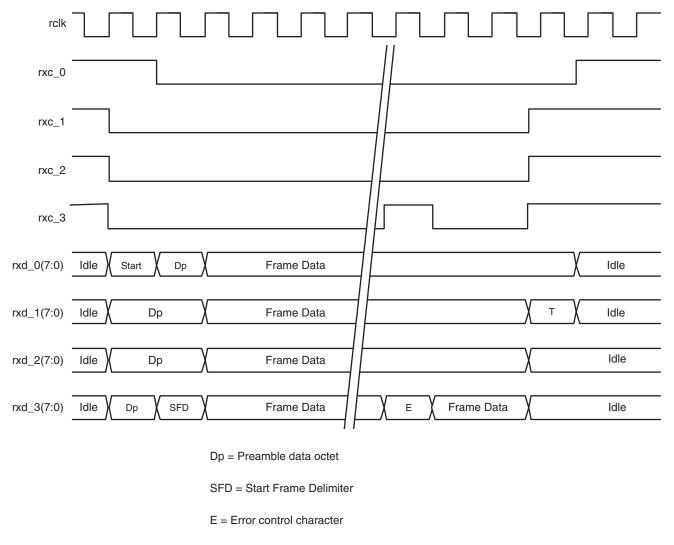

| Receive Data                                  |      |

| Control & Status                              |      |

| Status Interrupt Registers                    |      |

| PCI Express Mode                              |      |

| Introduction                                  |      |

| LatticeSC flexiPCS Quad Module                |      |

| Quad and Channel Option Control               |      |

| Register Map Addressing                       |      |

| Auto-Configuration                            |      |

| PCI Express Register Settings                 |      |

| x4 PCI Express Auto-Configuration Example     |      |

| PCI Express Mode                              |      |

| PCI Express Mode Pin Description              |      |

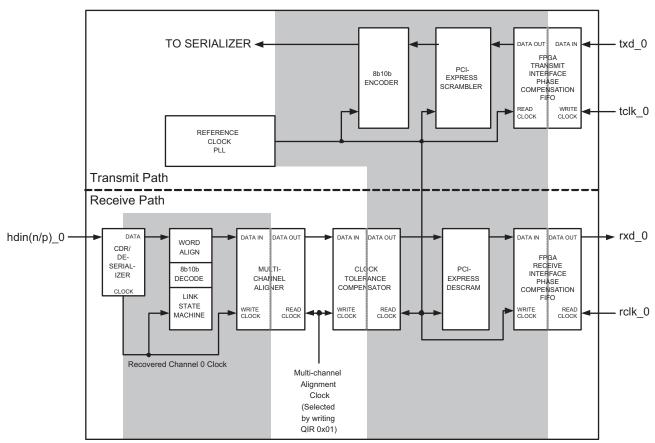

| PCI Express Mode Detailed Description         |      |

| Clocks & Resets                               |      |

| Transmit Data                                 |      |

| Receive Data                                  |      |

| Control & Status                              |      |

| x2 PCI Express Operation                      |      |

| x4 PCI Express Operation                      |      |

| x4 PCI Express Operation Pin Description      |      |

| x4 PCI Express Operation Detailed Description |      |

| Clocks & Resets                               |      |

| Transmit Data                                 |      |

| Receive Data                                  |      |

| x8 PCI Express Operation                      |      |

| Control & Status                              |      |

| Status Interrupt Registers                    | 8-38 |

| Serial RapidIO Mode                                    |      |

|--------------------------------------------------------|------|

| Introduction                                           |      |

| LatticeSC flexiPCS Quad Module                         |      |

| Quad and Channel Option Control                        |      |

| Register Map Addressing                                |      |

| Auto-Configuration                                     |      |

| Serial RapidIO Register Settings                       |      |

| Serial RapidIO Auto-Configuration Example              |      |

| Serial RapidIO Mode                                    |      |

| 1x Serial RapidIO Mode Pin Descriptions                |      |

| Serial RapidIO Mode Detailed Description               |      |

| Clocks & Resets                                        |      |

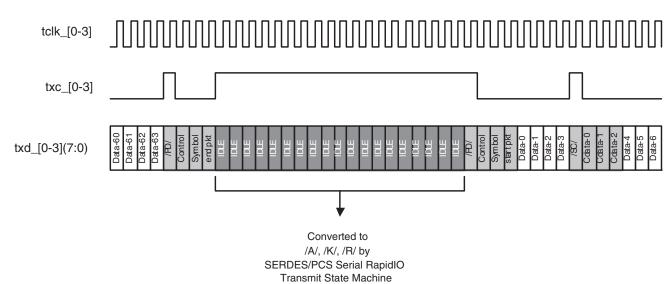

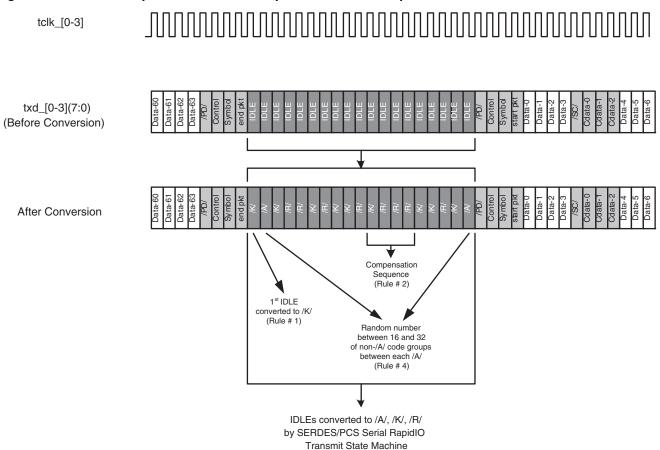

| Transmit Data                                          |      |

| Receive Data                                           |      |

| Control & Status                                       |      |

| 4x Serial RapidIO Operation                            |      |

| 4x Serial RapidIO Operation Pin Description            |      |

| 4x Serial RapidIO Operation Detailed Description       |      |

| Clocks & Resets                                        |      |

| Transmit Data                                          |      |

| Receive Data                                           |      |

| Control & Status                                       |      |

| Status Interrupt Registers                             |      |

| SONET Mode                                             |      |

| Introduction                                           |      |

| LatticeSC flexiPCS Quad Module                         |      |

| Quad and Channel Option Control                        |      |

| Register Map Addressing                                |      |

| Auto-Configuration                                     |      |

| SONET Register Settings                                |      |

| SONET Auto-Configuration                               |      |

| SONET Mode                                             |      |

| SONET Mode Pin Description                             |      |

| SONET Mode Detailed Description                        |      |

| Clocks & Resets                                        |      |

| Transmit Data                                          |      |

| Receive Data                                           |      |

| Control & Status                                       |      |

| Status Interrupt Registers                             |      |

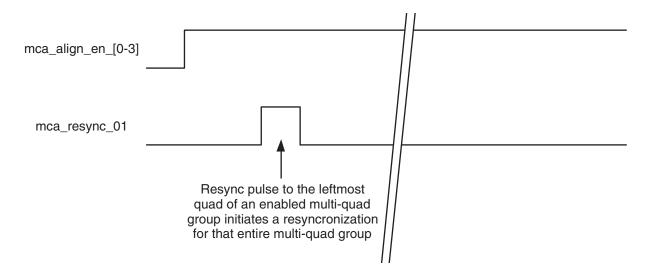

| Multi-Channel Alignment                                |      |

| Introduction                                           |      |

| Supported Protocols                                    |      |

| Alignment Within A Quad                                |      |

| Alignment Between Quads                                |      |

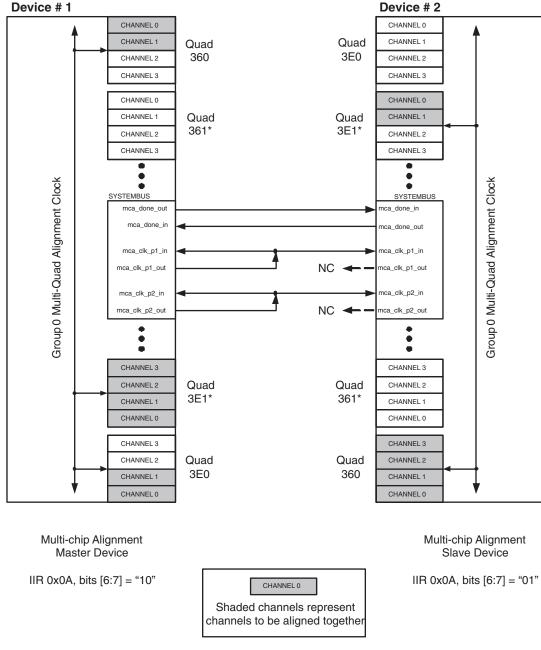

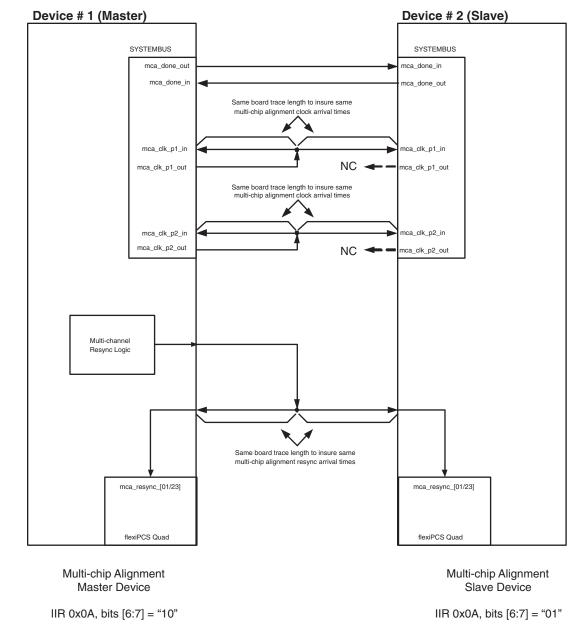

| Alignment Between Two Devices                          |      |

| Synchronization of Aligned Channels Across Two Devices |      |

| Status Interrupt Registers                             |      |

| flexiPCS Testing                                       |      |

| Introduction                                           |      |

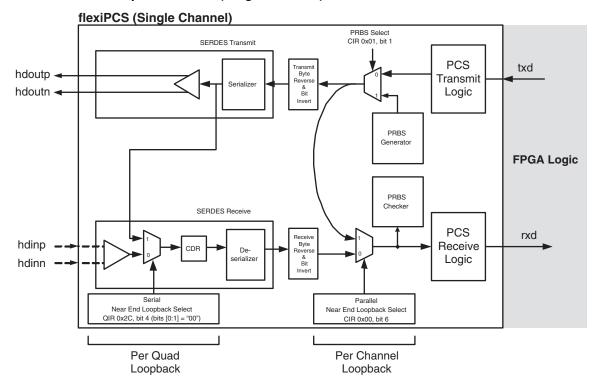

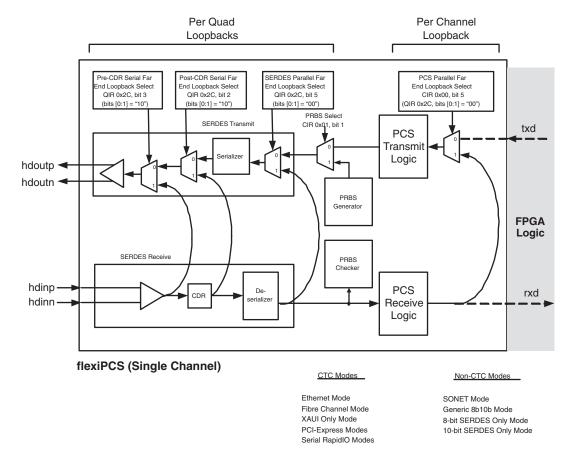

| Near-End Loopback Modes                                |      |

| Far-End Loopback Modes                                 |      |

| PRBS Generator and Checker                             |      |

| Memory Map                                             |      |

| LatticeSC flexiPCS Memory Map                          | 13-1 |

|                                                        |      |

| Revision History | 14 |  |

|------------------|----|--|

|                  |    |  |

# Introduction to flexiPCS LatticeSC/M flexiPCS Family Data Sheet

August 2007 Data Sheet DS1005

## flexiPCS™ Features

## n Up to 32 Channels of High-Speed SERDES

- 600 Mbps to 3.8 Gbps per channel

- Out-of-band signal interface allows same pin operation down to DC rates

- Low TX jitter (0.25 UI typical at 3.125Gbps)

- High RX jitter tolerance (0.8 UI at 3.125Gbps)

- Low Power (105mW per channel typical)

- SERDES Only mode allows direct 8- or 10-bit interface to FPGA logic

## n Other Key Features

- Four levels of pre-emphasis up to 48%

- Two levels of equalization up to 12dB

- Four TX programmable amplitude levels

- Three programmable termination levels (TX)

- Four programmable termination levels (RX)

- · Hot-plug capable

- AC or DC coupled receiver

## Full Function Embedded Physical Coding Sublayer (PCS) Logic Supporting Industry Standard Protocols

- Up to 32 Channels of full-duplex data supported per device

- Multiple protocol support on one chip

- Supports popular 8b10b based packet protocols

- Supports SONET based payloads

## n Gigabit Ethernet

- IEEE 1000BASE-X compliant

- 8b10b encoding/decoding

- Access Clause 22 PHY registers in Auto-negotiation mode

- Comma character word alignment

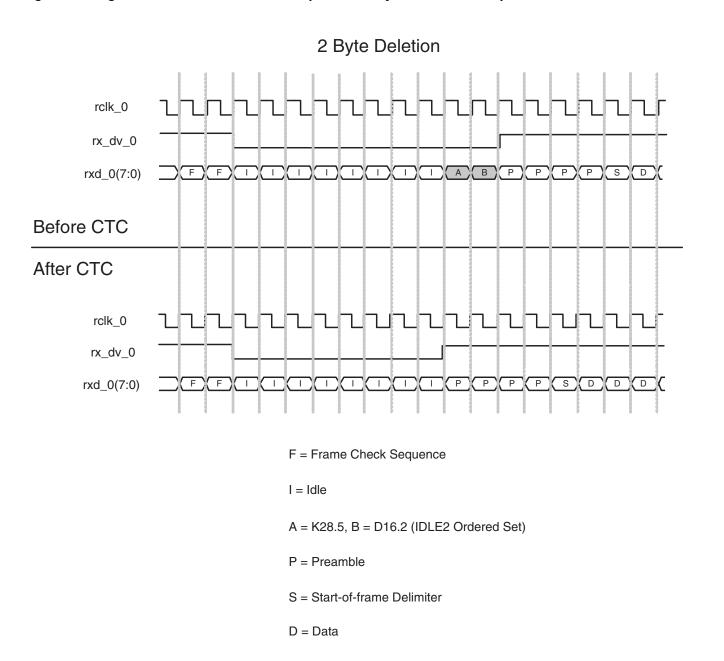

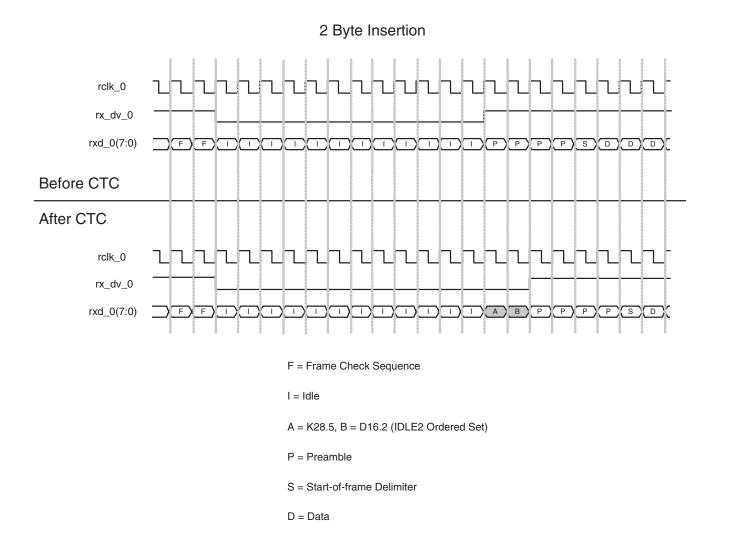

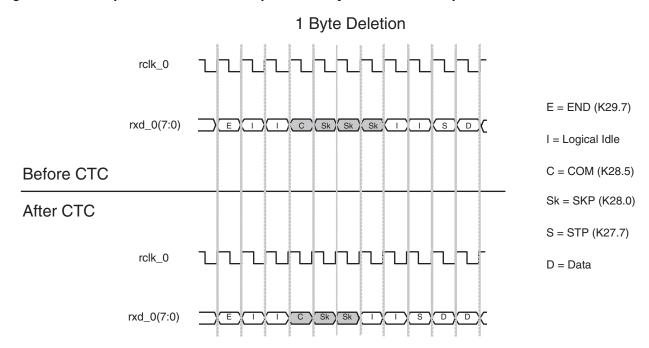

- Clock Tolerance Compensation circuit

- CRC generation/checking

- Provides 1G Ethernet link to GMII compliant FPGA logic interface

#### n 10Gb Ethernet

- 10GbE /A/K/R/ idle insertion and removal

- 10GbE synchronization state machine controls comma alignment

- 10GbE XAUI deskew state machine controls multichannel alignment and monitors alignment status

- Clock Tolerance Compensation logic performs idle insertion and removal

- Provides 10G Ethernet link to XGMII compliant FPGA logic interface

## n Fibre Channel

Fibre Channel link state machine to report link status

- Fibre Channel EOF ordered set conversion to correct disparity

- 1.02/2.04 Gbps Fibre Channel support (single channel) and 10G Fibre Channel support (4 channels)

## PCI Express

- Word aligner

- 8b10b encoding/decoding

- Clock Tolerance Compensation circuit

- PCI Express data scrambling and descrambling (Both D1.0 and D1.0a polynomials)

- Multi-channel alignment for support of x1 to x32 PCI Express on one device

- Electrical Idle and Receiver Detection support

## Serial RapidIO

- Word Aligner

- 8b10b encoding/decoding

- Clock Tolerance Compensation circuit

- Random /A/K/R/ insertion in transmit path and idle replacement in receive path

- Multi-channel alignment for support of 1x to 32x RapidIO on one device

## n SONET Based Functionality

- STS-48 and STS-12 Framers

- Supports any length of concatenation within an STS-12/STS-12c or STS-48/STS-48c frame

- TOH byte insertion of A1, A2, and Section B1 bytes into transmitted data frames

- SONET compliant scrambling and descrambling

- B1 checking, AIS insertion/checking and RDI-L insertion and checking

- STS-48/STS-12 pointer interpreter function with STS-1 granularity

- TFI-5 Link Layer support

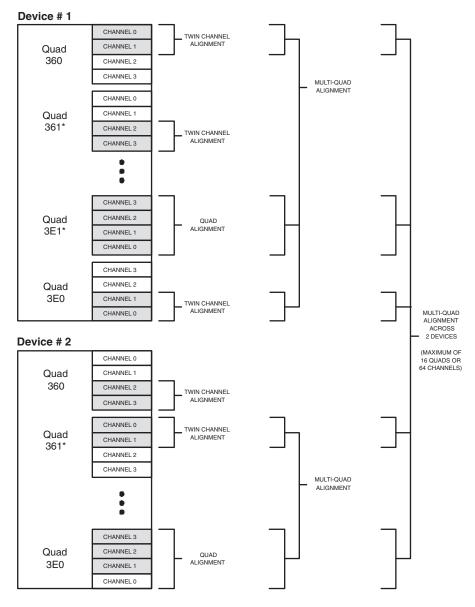

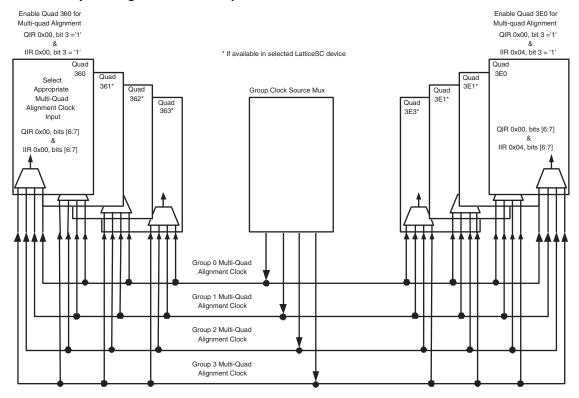

## Multiple Protocol Compliant Multi-Channel Aligner

- Supports simultaneous alignment of four independent alignment groups on one device

- Provides up to 32 channel alignment on one device and 64 channel alignment across two devices

## Integrated Loopback Modes for System Debugging

- Far End Loopback (RX to TX) provided for testing line connections to and from LatticeSC device

- Near End Loopback (TX to RX) provided to test connections across PCS/FPGA logic interface

- Integrated 2^7 and 2^31 PRBS generator/check-

© 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## flexiPCS Introduction

The LatticeSC family of FPGA combines a high-performance FPGA fabric, high-performance I/Os and large embedded RAM in a single industry leading architecture. All LatticeSC devices also feature up to 32 channels of embedded SERDES with associated Physical Coding Sublayer (PCS) logic. The flexiPCS logic can be configured to support numerous industry standard high-speed data transfer protocols.

Each channel of flexiPCS logic contains dedicated transmit and receive SERDES for high-speed full-duplex serial data transfers at data rates up to 3.8 Gbps. The PCS logic in each channel can be configured to support an array of popular data protocols including SONET (STS-12/STS-12c, STS-48/STS-48c, and TFI-5 support of 10 Gbps or above), Gigabit Ethernet (compliant to the IEEE 1000BASE-X specification), 1.02 or 2.04 Gbps Fibre Channel, PCI Express, and Serial RapidIO. In addition, the protocol based logic can be fully or partially bypassed in a number of configurations to allow users flexibility in designing their own high-speed data interface.

Protocols requiring data rates above 3.8 Gbps can be accommodated by dedicating either one pair or all 4 channels in one PCS quad block to one data link. One quad can support full-duplex serial data transfers at data rates up to 15.2 Gbps. A single PCS quad can be configured to support 10Gb Ethernet (with a fully compliant XAUI interface), 10Gb Fibre Channel, and x4 PCI Express and 4x RapidIO.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. Each SERDES pin can also be independently DC coupled and can allow for both high-speed and low-speed operation on the same SERDES pin for such applications as Serial Digital Video.

## **Architecture Overview**

The flexiPCS logic is arranged in quads containing logic for four independent full-duplex data channels. Each device in the LatticeSC family has up to 8 quads of flexiPCS logic. The table on the cover page of the <a href="LatticeSC/M">LatticeSC/M</a> Family Data Sheet contains the number of flexiPCS channels present on the chip. Note that in some packages (particularly lower pin count packages), not all channels from all quads on a given device may be bonded to package pins.

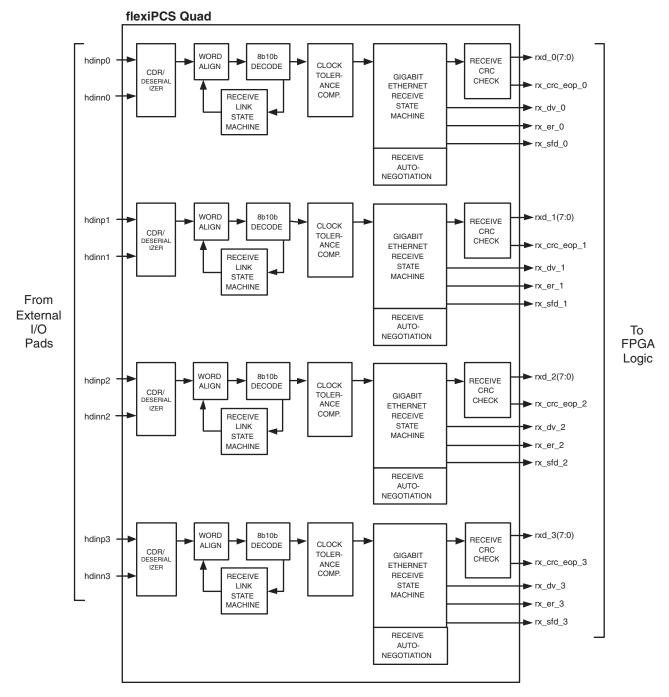

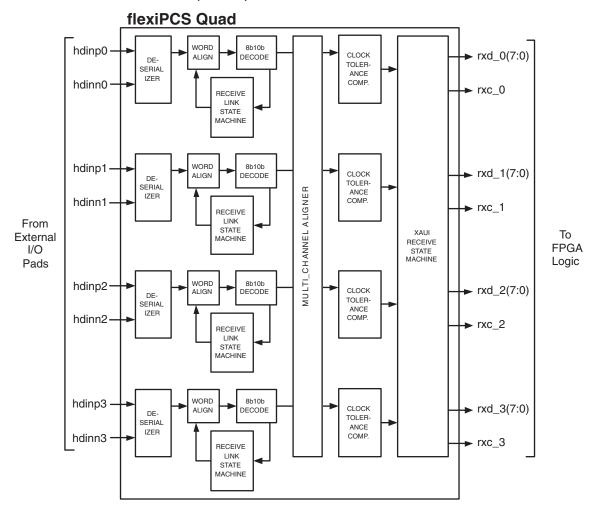

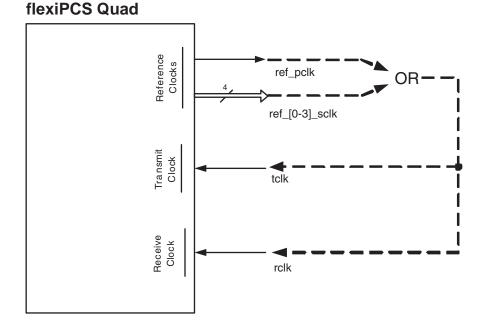

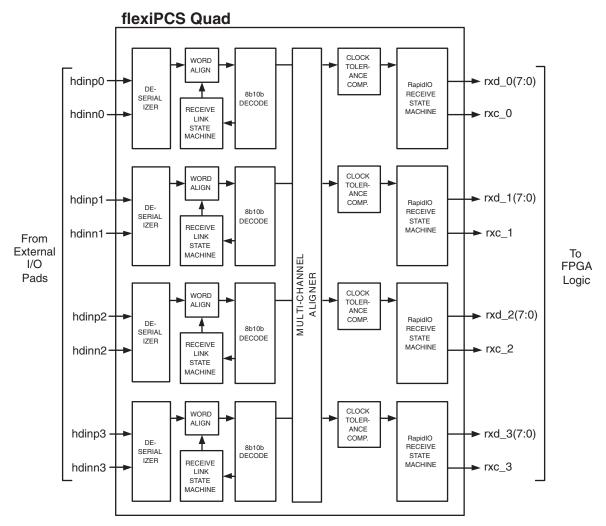

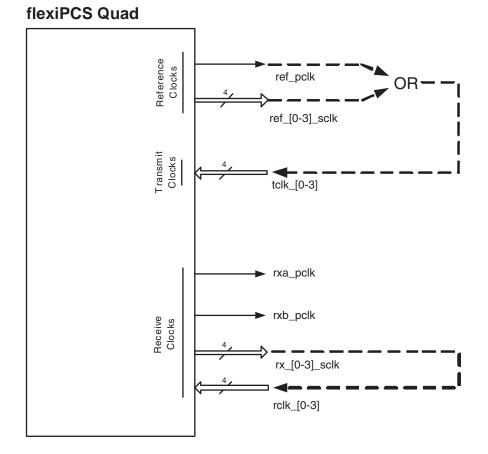

## flexiPCS Quad

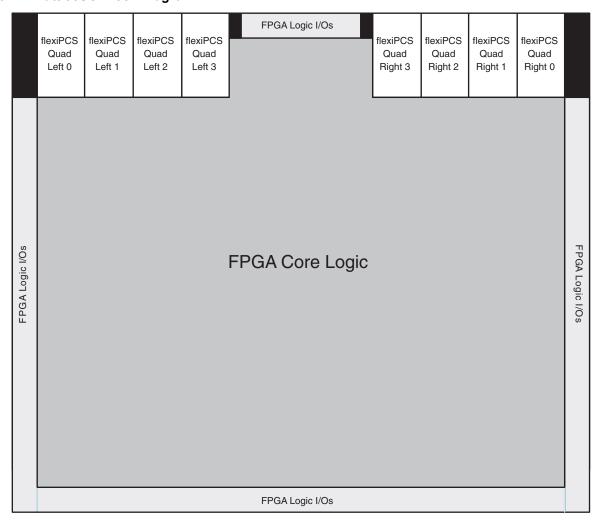

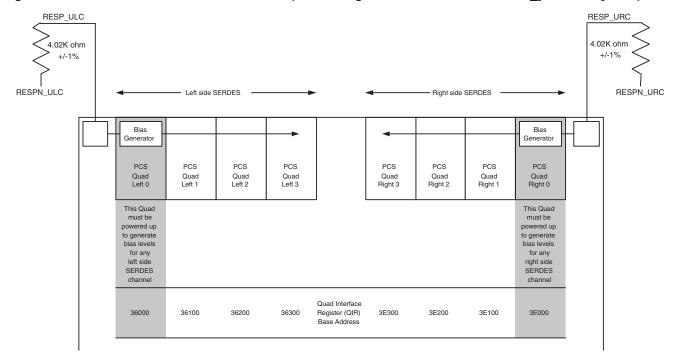

Figure 1-1 is a layout of a LatticeSC device showing the arrangement of flexiPCS quads on the device (the largest array containing 8 quads is shown. Other devices have fewer quads).

Figure 1-1. LatticeSC Block Diagram

Every quad can be programmed into one of several protocol based modes. Each quad requires its own reference clock which can be sourced externally from package pins or internally from the FPGA logic.

Since each quad has its own reference clock, different quads can support different standards on the same chip. This feature makes the LatticeSC family of devices ideal for bridging between different standards.

flexiPCS quads are not dedicated solely to industry standard protocols. Each quad (and each channel within a quad) can be programmed for many user defined data manipulation modes. For example, modes governing user-defined word alignment, and multi-channel alignment can be programmed for non-protocol operation.

## flexiPCS Channel

Each quad on a device supports up to four channels of full-duplex data. The user can utilize anywhere from one to four channels in a quad depending on the application. Many options can be set by the user for each channel independently within a given quad.

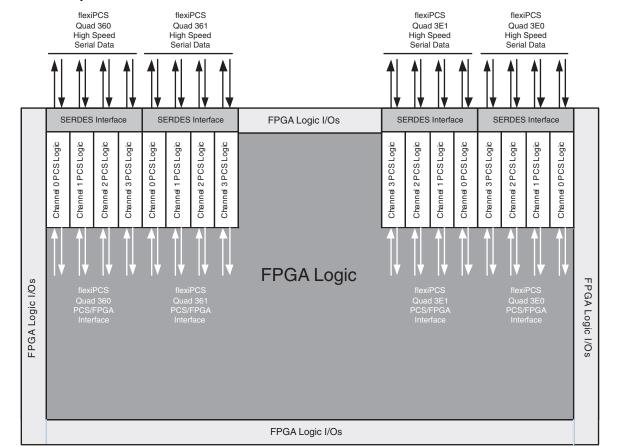

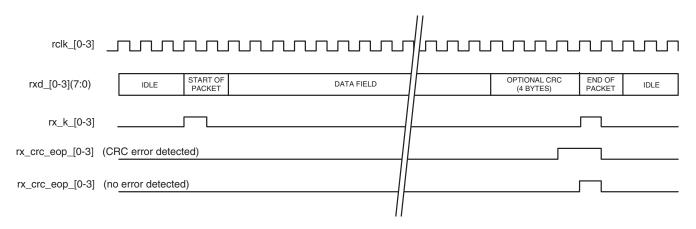

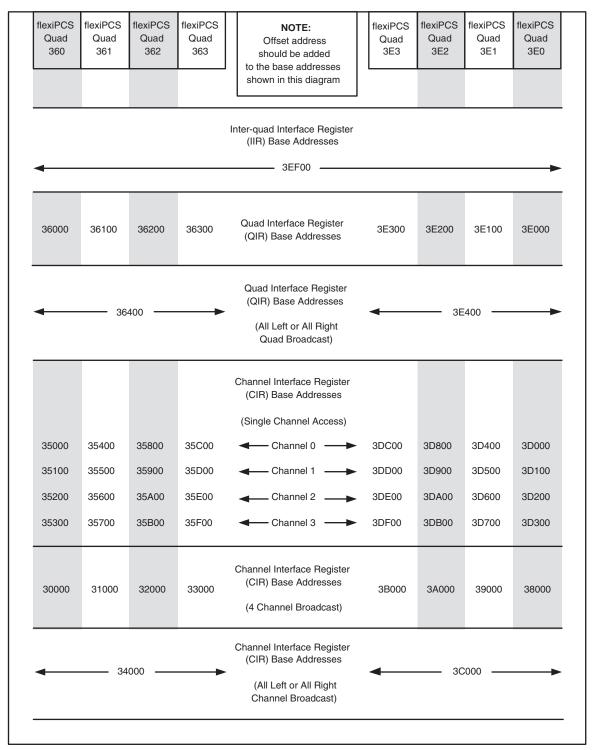

Figure 1-2 shows an example of a device with four flexiPCS quads which contain a total of 16 flexiPCS channels. Quad are named according to the base address of their control and status registers: Quad 360, Quad 361, Quad 362, Quad 363, Quad 3E0, Quad 3E1, Quad 3E2, and Quad 3E3. LatticeSC devices with less than 8 quads have quads with the lowest trailing numbers. For example, a device with two quads has quads 360 and 3E0. A device with four quads has quads 360, 3E0, 361, and 3E1.

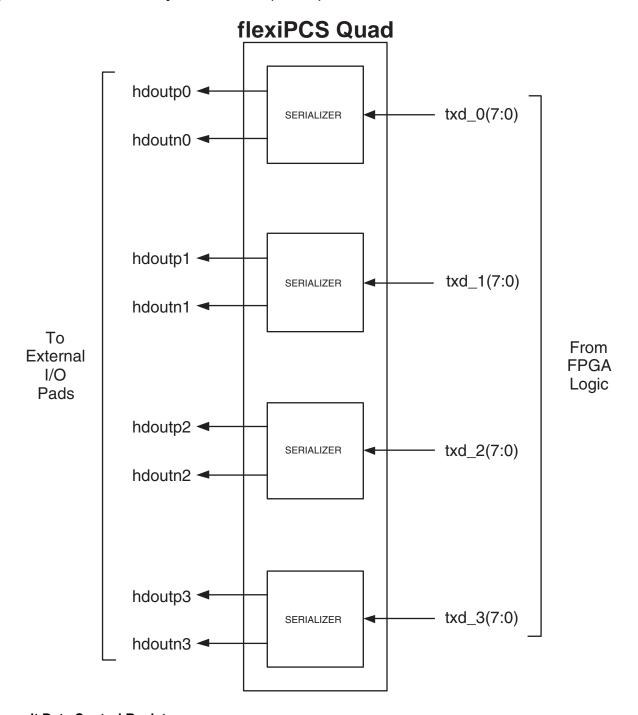

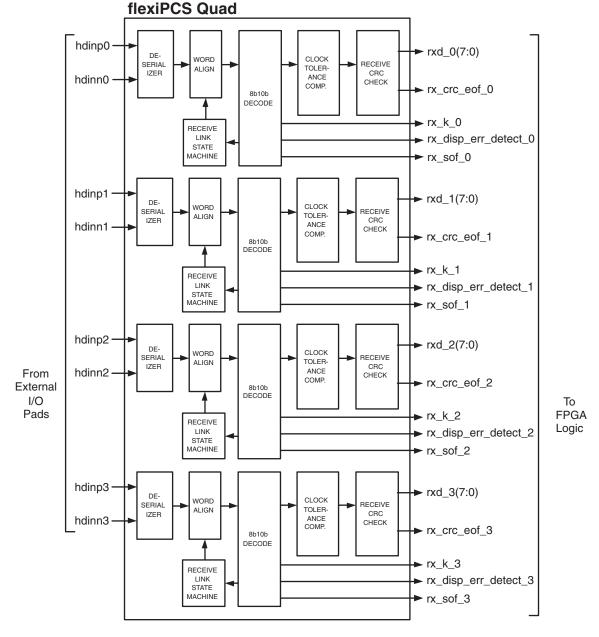

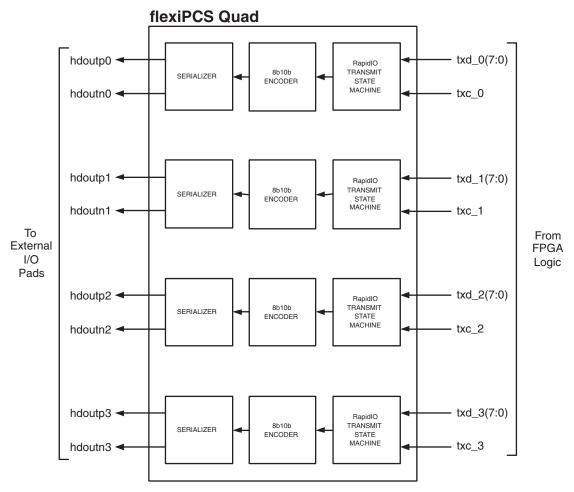

Figure 1-2. Example of LatticeSC Device with four flexiPCS Quads

## Per Channel PCS/FPGA Interface Ports

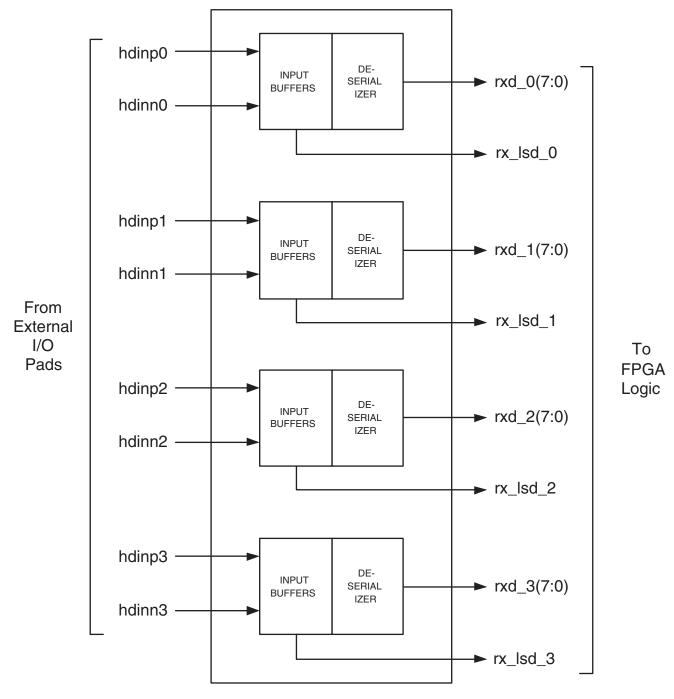

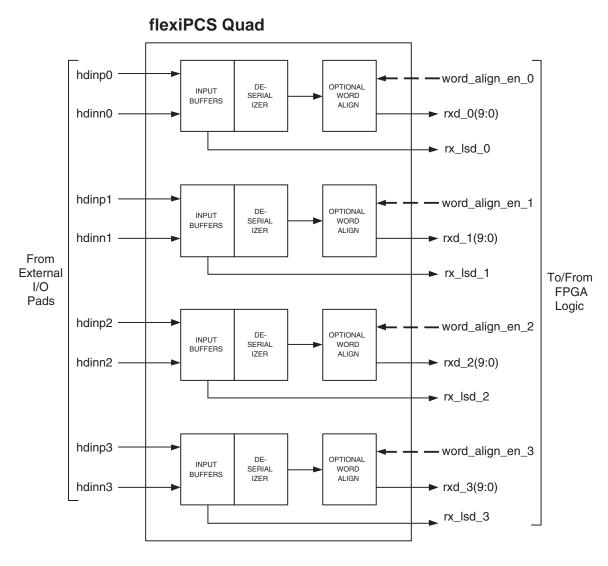

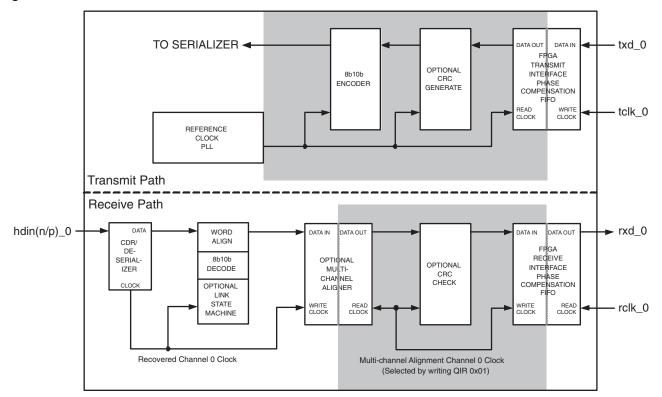

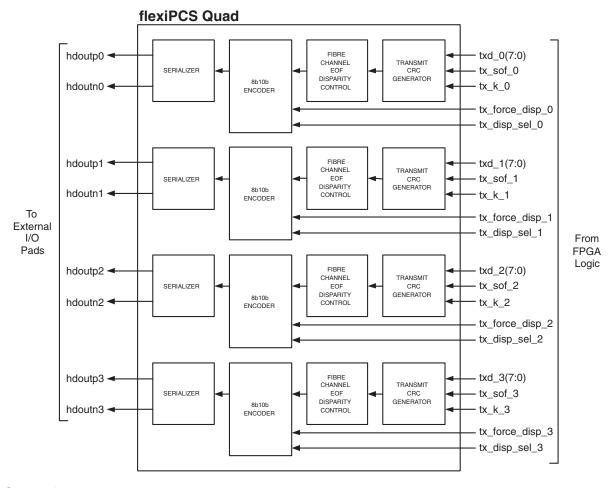

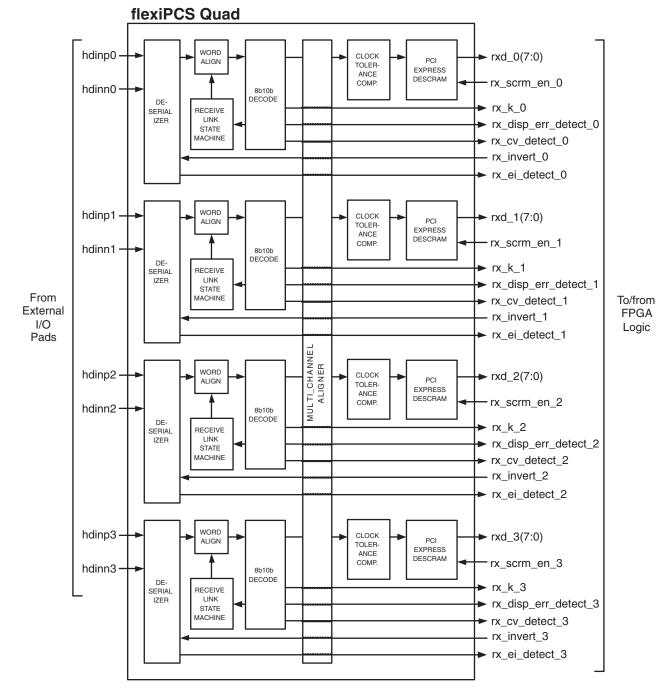

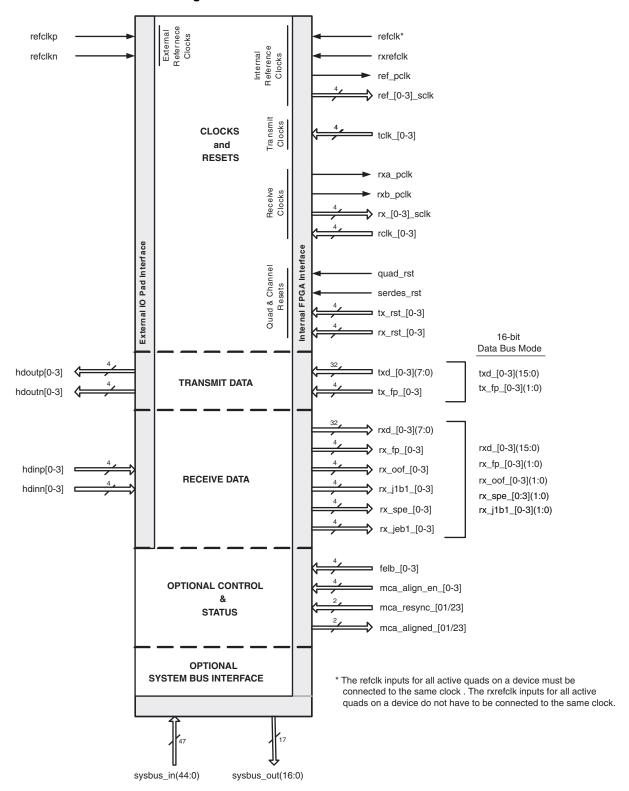

All flexiPCS quads regardless of chosen mode have the same external high speed serial interface at the package pins. However, every flexiPCS mode has its own unique list of input/output ports from/to the FPGA logic appropriate to the protocol chosen for the quad. A detailed description of the quad input/output signals for each mode is provided in the corresponding mode description section of the flexiPCS Data Sheet. A simplified diagram showing the channels within a single quad is shown in Figure 1-3.

High speed serial interface HDINP\_0 HDOUTP\_0. HDINP\_2 HDINN\_2 HDINP\_3 HDINN\_3 HDOUTP\_3. HDINP\_1 HDINN\_1 HDOUTP\_ HDOUTP\_ Same signals for all flexiPCS Modes High Speed SERDES Interface CHANNEL 1 CHANNEL 0 **CHANNEL 2** CHANNEL 3 Transmit Data

Receive Data

CONTROL

STATUS CONTROL STATUS Transmit Data

Receive Data CONTROL STATUS Transmit Data

Receive Data CONTROL STATUS Transmit Data

Receive Data **CLOCKS & RESETS CLOCKS & RESETS CLOCKS & RESETS** CLOCKS & RESETS Mode specific port list at PCS/ FPGA interface **FPGA Logic** Interface

Figure 1-3. flexiPCS Quad External and Internal FPGA Interfaces

A general description of the FPGA interface signals follows:

## **Clocks & Resets**

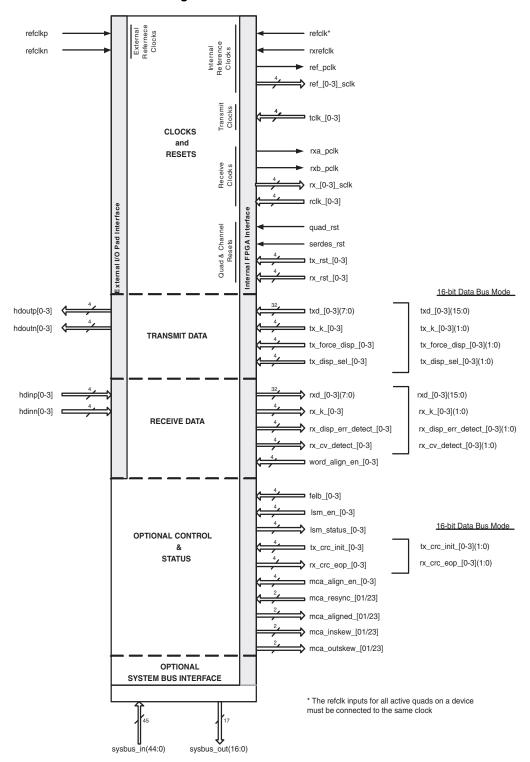

A flexiPCS quad supplies per channel locked reference clocks and per channel recovered receive clocks to the FPGA logic interface. Each flexiPCS quad provides these clocks on both primary and general FPGA clock routing. The PCS/FPGA interface also has ports for the transmit and receive clocks supplied from the FPGA fabric for all four channels in each quad.

Each quad has reset inputs to force reset of both the SERDES and PCS logic in a quad or the just the SERDES. In addition, separate resets dedicated for the PCS logic are provided for each channel for both the transmit and receive directions.

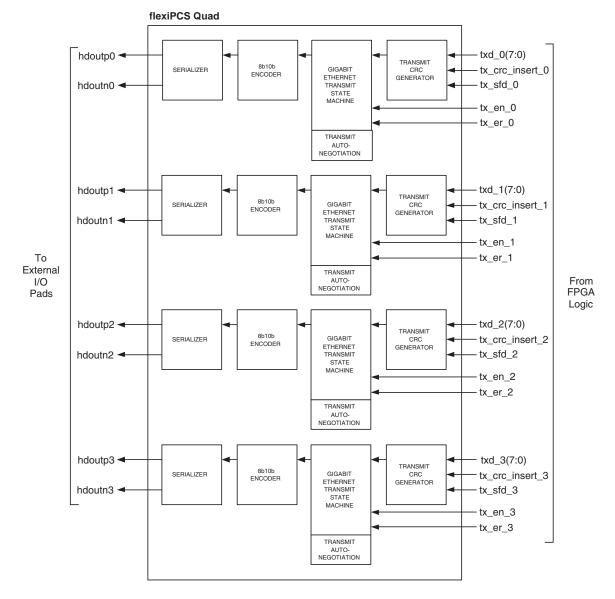

## **Transmit Data**

For each channel in the quad, 8-bit or 10-bit (depending on mode) transmit data from the FPGA is supplied to the PCS, where it is serialized, and sent off chip by the SERDES. A gearing option per channel is provided for a 16 or 20-bit FPGA transmit data interface which runs at one half the nominal rate.

Data is synchronized to the quad reference clock supplied either from external pins or the FPGA logic.

#### **Receive Data**

For each channel in the quad, serial data and clock is supplied by an external source to the SERDES pins. The data is descrialized and manipulated by the PCS logic and passed as 8-bit or 10-bit (depending on mode) data to the FPGA logic. A gearing option per channel is provided for a 16 or 20-bit FPGA receive data interface which would run at half the nominal rate. Clocks are recovered for each channel and made available at the internal FPGA logic interface.

#### Control

Each mode has its own set of control signals which allows direct control of various PCS features from the FPGA logic. In general, each of these control inputs duplicate the effect of writing to a corresponding control register bit or bits. The ispLEVER design tools give the user the option to bring these ports out to the FPGA interface.

## Status

Each mode has its own set of status or alarm signals that can be monitored by the FPGA logic. In general, each of these status outputs correspond to a specific status register bit or bits. The ispLEVER design tools give the user the option to bring these port out to the PCS FPGA interface.

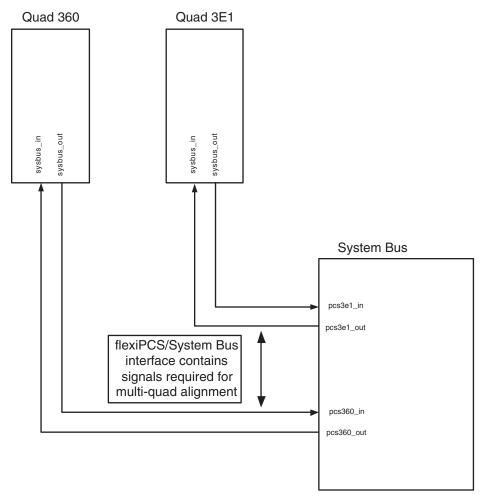

#### System Bus Control and Monitoring

Dedicated registers accessible through the System Bus interface are provided to control a wide range of options in the SERDES and PCS. Similarly, System Bus registers are provided for monitoring status and alarm conditions. Register maps are provided at the end of the flexiPCS Data Sheet for all the control and status registers common to all the PCS quads on a device. Registers are provided which cover multi-quad and channel control and status. The System Bus addressing scheme for each of these register types is provided at the beginning of each mode section. For more information on the System Bus, refer to the TN1085, <u>LatticeSC MPI/System Bus</u>.

## **Using this Data Sheet**

The ispLEVER design tools from Lattice support all modes of the flexiPCS. Most modes are dedicated to applications for a specific industry standard data protocol. Other modes are more general purpose modes which allow a user to define their own custom application settings. ispLEVER design tools allow the user to define the mode for each quad in their design. Nine quad modes are currently supported by the ispLEVER design flow:

## **Quad flexiPCS Modes:**

- 8-bit SERDES Only

- 10-bit SERDES Only

- SONET (STS-12/STS-48)

- Gigabit Ethernet

- Fibre Channel (Single SERDES)

- XAUI

- Serial RapidIO

- PCI Express

- · Generic 8b10b

The LatticeSC/M Family flexiPCS Data Sheet has been written in a modular fashion and is organized along the lines of the modes selectable in the ispLEVER design flow. Nine sub-sections are each dedicated to one of the above modes. In addition, several sections covering information common to all modes, including SERDES Functionality/Electrical & Timing Characteristics, Multi-channel Alignment, flexiPCS Testing and the flexiPCS Memory Map, may be of interest to users.

The ispLEVER design flow for the LatticeSC family allows the user to define the operation of the PCS on a per quad basis. Therefore, the flexiPCS Data Sheet describes the operation of each mode on a per quad basis as well. Each of the nine subsections describes the operation of a single quad. In general, the operation of a quad does not affect the choice of operation of any of the other quads on a device. The major exception is when several quads are configured to the same protocol and multi-channel alignment is required between channels on separate quads. The Multi-Channel Alignment section of this document describes how a LatticeSC device can be configured for alignment of a pair of channels, all channels within a quad, channels across multiple quads on the same device, and channels across multiple quads on two devices.

A user who is interested in the application of the flexiPCS for a specific protocol need only refer to the sub-section describing the mode dedicated to that protocol. A recommended list of sections might include:

- · Introduction to flexiPCS

- SERDES Functionality/Electrical & Timing Characteristics (Contains extra detail on the SERDES functionality which is applicable to all modes)

- Specific Mode of interest (Gigabit Ethernet Mode, SONET Mode, XAUI Mode, etc.)

- Multi-Channel Alignment (If needed)

- flexiPCS Testing (If needed)

- flexiPCS Memory Map

The flexiPCS Data Sheet provides a thorough description of the complete functionality of the embedded SERDES and associated PCS logic. Electrical and Timing Characteristics of the embedded SERDES are provided in the SERDES Functionality/Electrical & Timing Characteristics section of this document. Package pinout information is provided in the Architecture section of the <u>LatticeSC/M Family Data Sheet</u>.

# SERDES Functionality/Electrical & Timing LatticeSC/M flexiPCS Family Data Sheet

June 2011 Data Sheet DS1005

## Introduction

e a high speed SERDES serial data interface. This section describes the operation of the LatticeSC SERDES for all modes of the SEREDES/PCS block.

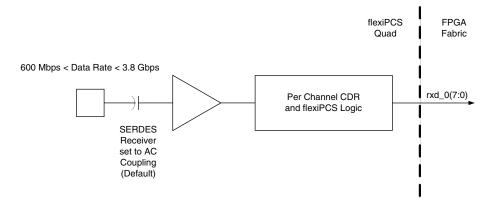

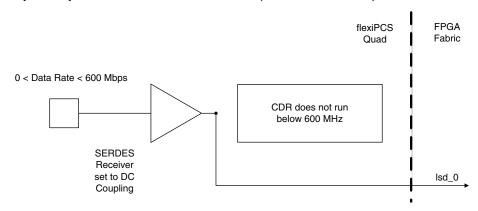

The embedded SERDES PLLs support serial data rates from 600 Mbps to 3.8 Gbps which covers a wide range of industry standard protocol data transmission rates. For applications which require a lower input data rate to the SERDES buffers, low speed connections from the SERDES input buffers to the FPGA logic are also available (see the 8-bit and 10-bit SERDES Only Modes section of the LatticeSC/M Family flexiPCS Data Sheet).

## LatticeSC flexiPCS Quad Module

Devices in the LatticeSC family may have up to 8 quads of embedded flexiPCS logic. Each quad in turn supports 4 independent full duplex data channels. Therefore, each quad in a LatticeSC device is capable of supporting 4 transmit and 4 receive SERDES serial data links. This section describes the operation of a single quad of flexiPCS logic.

Operation of the SERDES requires the user to provide a reference clock or clocks to each active quad to provide a synchronization reference for the SERDES PLLs. Reference clocks are shared among all four channels of a quad. If the transmit and receive frequencies are within the specified ppm tolerance for the LatticeSC SERDES (See the SERDES Electrical &Timing Characteristics section), only one reference clock is needed for both transmit and receive directions. If the receive frequency is not within the specified ppm tolerance, then separate reference clocks for the transmit and receive directions must be provided.

Simultaneous support of non-synchronous high-speed data rates on one device is possible with the use of multiple quads.

## **Quad and Channel Option Control**

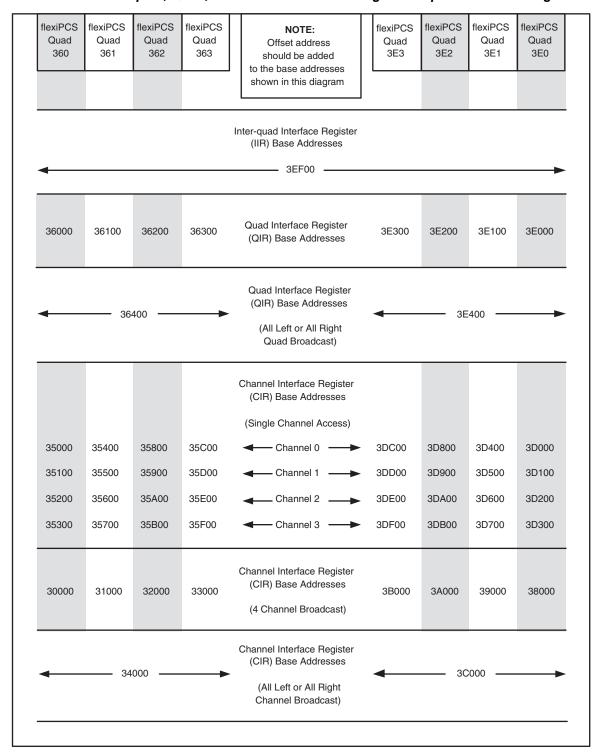

Although the mode selection and reference frequency covers an entire quad, many options covering clocking and data formatting are available on a per channel basis. Options are available only through dedicated registers that can be written and read via the embedded System Bus Interface (see the System Bus section for more details on the operation of the System Bus), or during device configuration. Depending on the specific option, a register may affect operation of multiple quads, a single quad or an individual channel in a quad. Registers dedicated to multiple quads are listed in the Inter-quad Interface Register Map in the LatticeSC flexiPCS Memory Map section of the flexiPCS Data Sheet. Registers dedicated to one quad are listed in the Quad Interface Register Map. Registers dedicated to a single channel are listed in the Channel Interface Register Map.

## **Register Map Addressing**

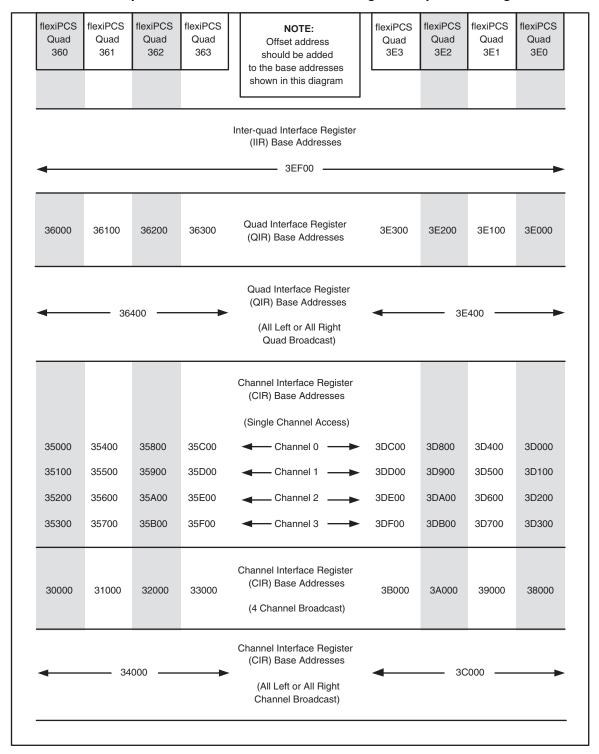

Figure 2-1 provides a map of base register addresses for any of the flexiPCS quads on a LatticeSC device. Note that different devices may have different numbers of available quads up to a total of 8 quads (or 32 channels) maximum.

Inter-quad Interface, Quad Interface, and Channel Interface Registers are listed by Offset Address. Each Inter-quad Interface Register, Quad Interface Register, and Channel Interface Register has a unique 18-bit address determined by the specific quad or channel targeted. The addressing of Inter-quad Interface Registers, Quad Interface Registers, and Channel Interface Registers is shown Figure 2-1.

Base addresses are dependant on the physical location of a given quad or channel on a LatticeSC device. Each quad and channel has an associated set of control and status registers. These registers are referred throughout this data sheet by their offset addresses. The unique 18-bit address of a control or status register for a specific

© 2011 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

www.latticesemi.com 2-1 DS1005 SERDES 02.0

# SERDES Functionality/Electrical & Timing Characteristics LatticeSC/M Family flexiPCS Data Sheet

## **Lattice Semiconductor**

quad or channel is simply the offset address of that register added to the base address for that specific quad or channel as shown in Figure 2-1.

Channel Interface Registers can be written in one of three methods. One method is to write to one specific register corresponding to one specific channel. The other two methods involve writing to multiple channel registers with just one write operation. This is referred to as a Broadcast write. A Broadcast write is useful when multiple channel registers are to be written with the same value. The first method of Broadcast writing involves writing to all four channel registers in a quad at one time. A second method of Broadcast writing involves writing to all channel registers for all quads on the left or right side of the device at one time. Therefore, a specific Channel Interface Register may be accessed through any one of three channel addresses, depending on the number of channel registers being written to at any one time.

A broadcast write to multiple quads cannot be used to power on SERDES in any device-package combination that does not have all SERDES guads bonded because of excess power on the board and jitter is also affected.

Throughout this document, the byte-wide data at each offset address is listed with a hexadecimal value with bit 0 as the MSB and bit 7 as the LSB as per the PowerPC convention. For example if the value for Quad Interface Register Offset Address 0x02 is stated to be 0x15, the bit pattern defined is as shown in Table 2-1:

Table 2-1. Control/Status Register Bit Order Example

| Quad Interface Register Offset Address 0x02 = 0x15 |              |               |               |               |               |               |               |

|----------------------------------------------------|--------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Data<br>Bit 0                                      | Data<br>Bit1 | Data<br>Bit 2 | Data<br>Bit 3 | Data<br>Bit 4 | Data<br>Bit 5 | Data<br>Bit 6 | Data<br>Bit 7 |

| 0                                                  | 0            | 0             | 1             | 0             | 1             | 0             | 1             |

| 1 5                                                |              |               |               |               |               |               |               |

A full list of register Offset Addresses is provided in the **LatticeSC flexiPCS Memory Map** section of the flexiPCS Data Sheet.

flexiPCS flexiPCS flexiPCS flexiPCS flexiPCS flexiPCS flexiPCS flexiPCS NOTE: Quad Quad Quad Quad Quad Quad Quad Quad Offset address 3E2 3E0 360 361 362 363 3E3 3E1 should be added to the base addresses shown in this diagram Inter-quad Interface Register (IIR) Base Addresses 3EF00 Quad Interface Register 36000 36100 36200 36300 3E300 3E200 3E100 3E000 (QIR) Base Addresses Quad Interface Register (QIR) Base Addresses 36400 3E400 (All Left or All Right Quad Broadcast) Channel Interface Register (CIR) Base Addresses (Single Channel Access) 35C00 35000 35400 35800 — Channel 0 — 3DC00 3D800 3D400 3D000 35100 35500 35900 35D00 Channel 1 -3DD00 3D900 3D500 3D100 35200 35600 35A00 35E00 3DE00 3DA00 3D600 3D200 Channel 2 . 35700 3D700 3D300 35300 35B00 35F00 - Channel 3 -3DF00 3DB00 Channel Interface Register (CIR) Base Addresses 30000 31000 32000 33000 3B000 3A000 39000 38000 (4 Channel Broadcast) Channel Interface Register (CIR) Base Addresses 34000 3C000 (All Left or All Right Channel Broadcast)

Figure 2-1. flexiPCS Inter-quad, Quad, and Channel Interface Register Map Base Addressing

## **Auto-Configuration**

Initial register setup for each flexiPCS mode can be performed without accessing the system bus by using the auto-configuration tool, IPexpress. IPexpress generates an auto-configuration file which contains the quad and channel register settings for the chosen mode. This file can be referred to for front-end simulation and also can be integrated into the bitstream. When an auto-configuration file is integrated into the bitstream all the quad and channel

## SERDES Functionality/Electrical & Timing Characteristics LatticeSC/M Family flexiPCS Data Sheet

## **Lattice Semiconductor**

registers will be set upon reset to values defined in the auto-configuration file. The system bus is therefore not needed if all quads are to be set via auto-configuration files. However, the system bus will still need to be included in a design if the user wants to change control registers or monitor status registers during operation.

## **SERDES Functionality**

IPexpress allows the designer to choose the protocol for each flexiPCS quad used in a given design. All PCS modes share a common list of SERDES pins. Control of the SERDES is the same regardless of PCS protocol chosen. The specific choice of SERDES options may be constrained by the particular application corresponding to the PCS protocol chosen. This section details the control of a single quad of SERDES common to any PCS mode. For more specific information about the setup of the SERDES for a particular protocol mode, refer to the appropriate section of the LatticeSC/M Family flexiPCS Data Sheet.

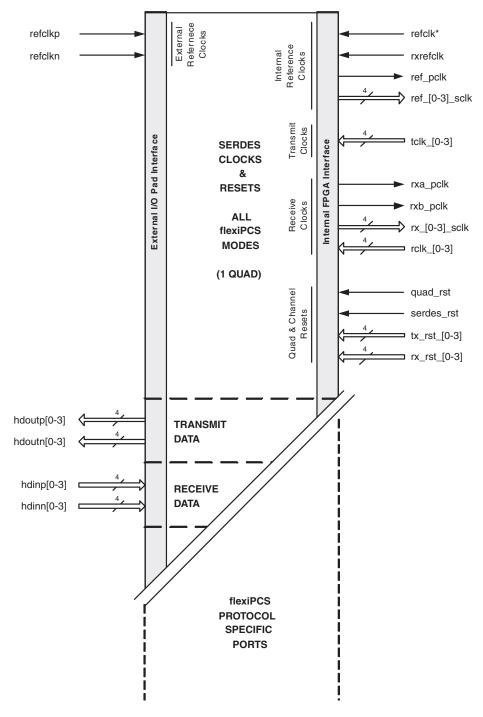

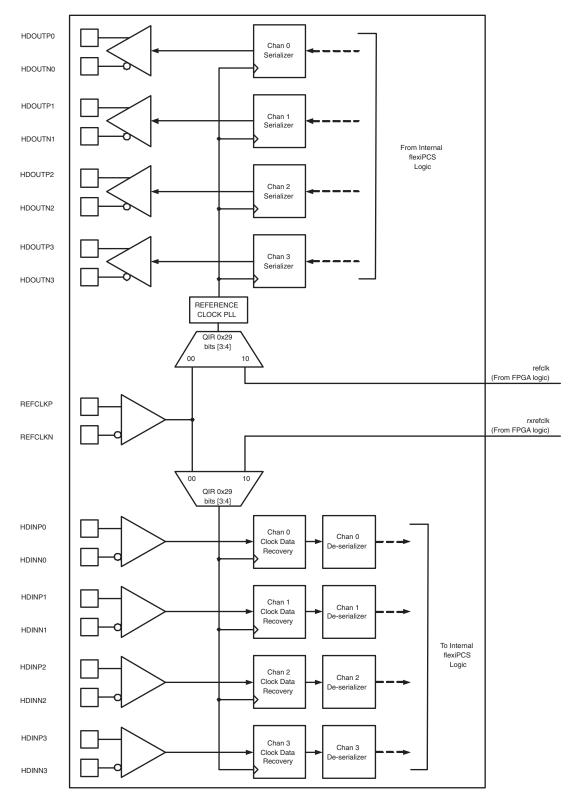

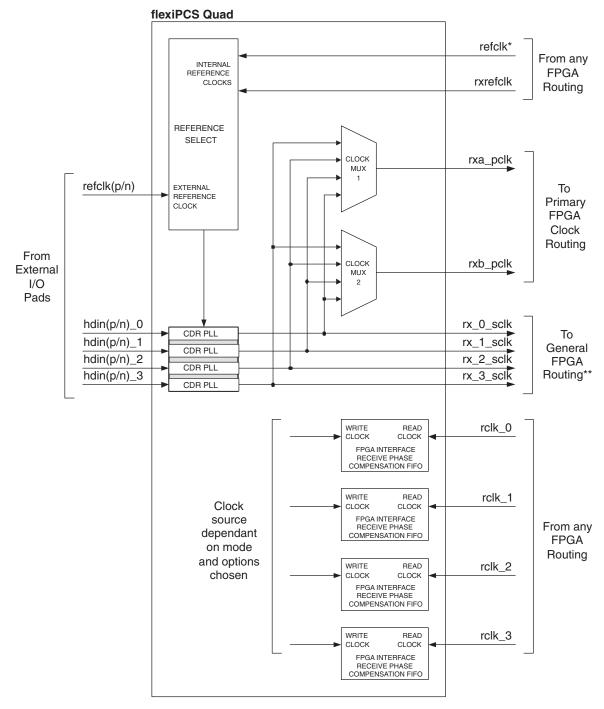

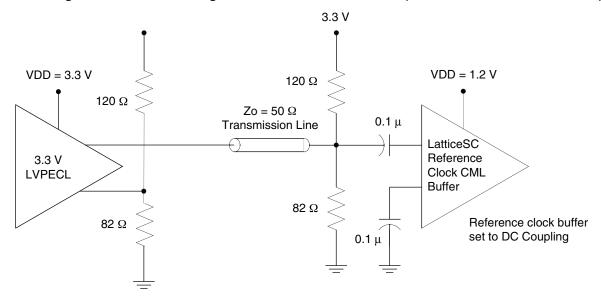

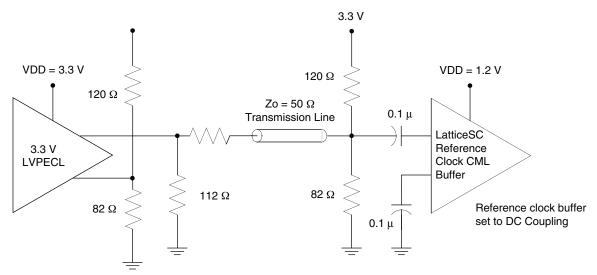

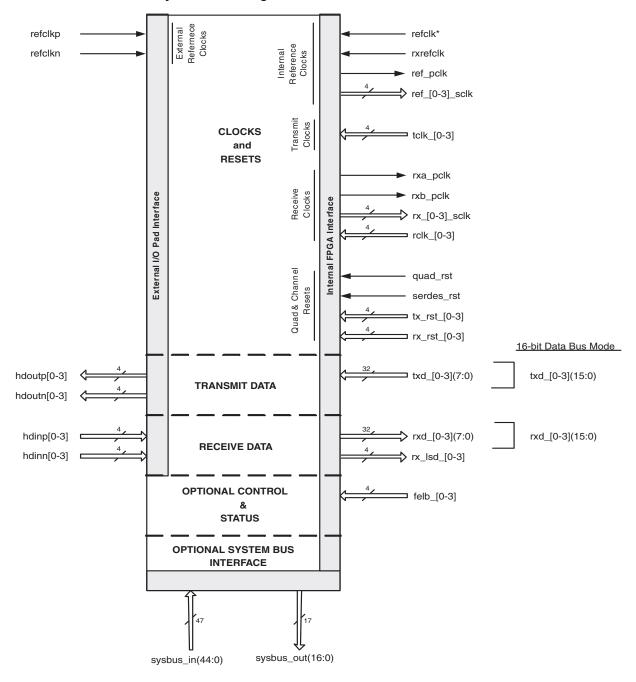

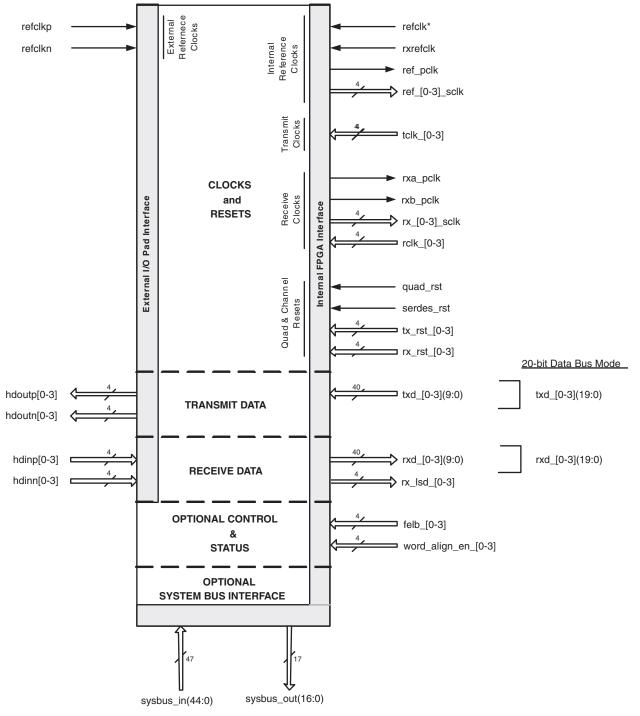

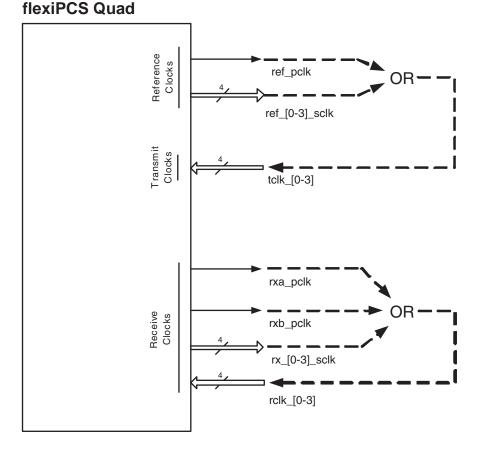

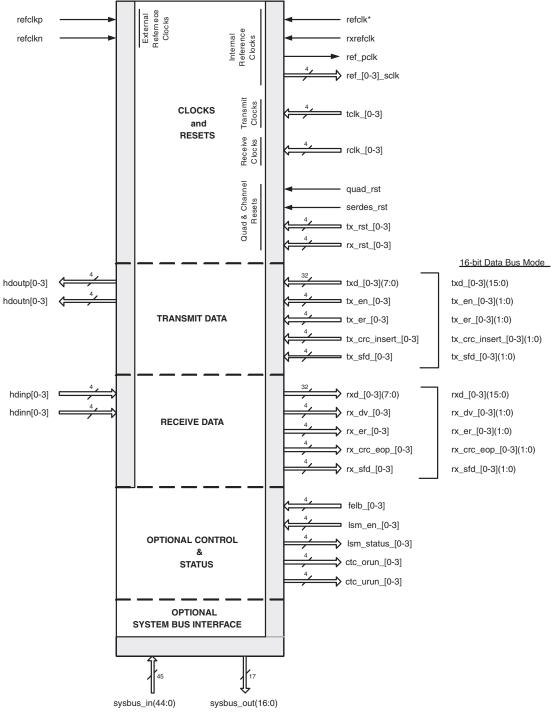

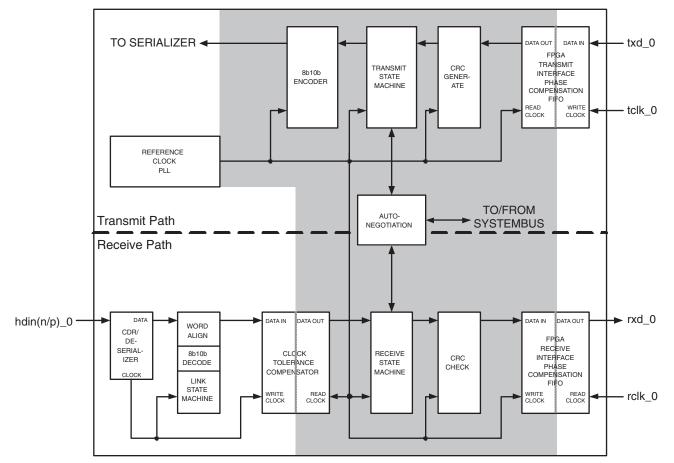

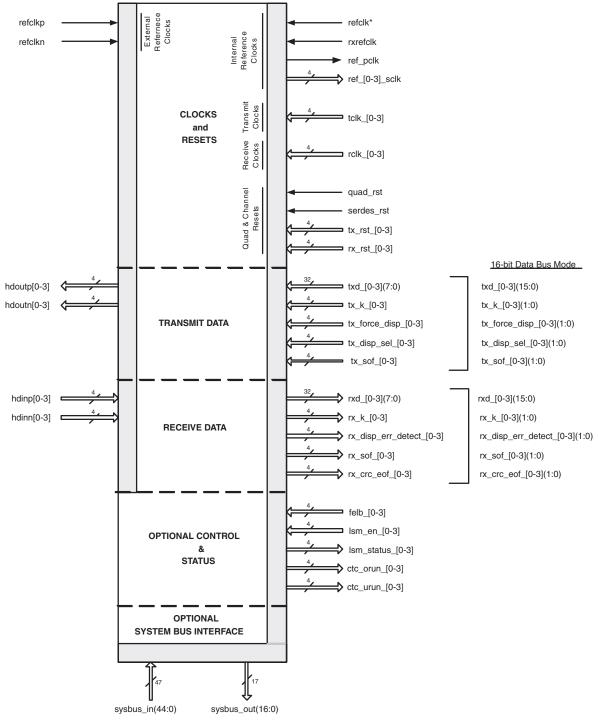

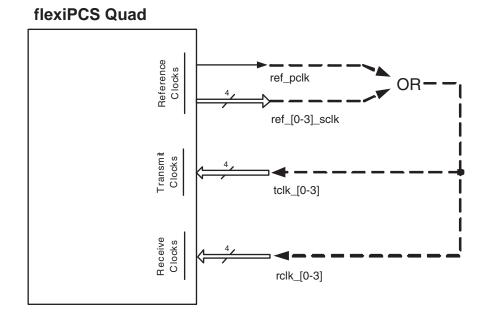

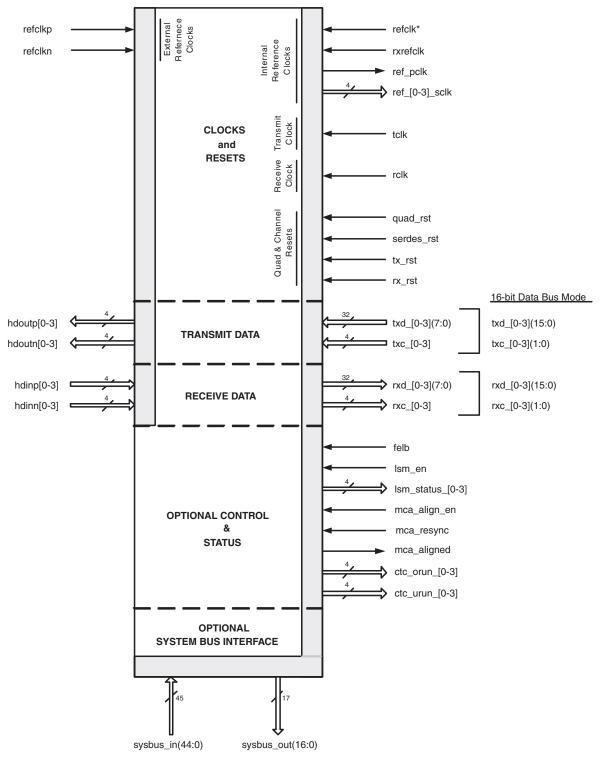

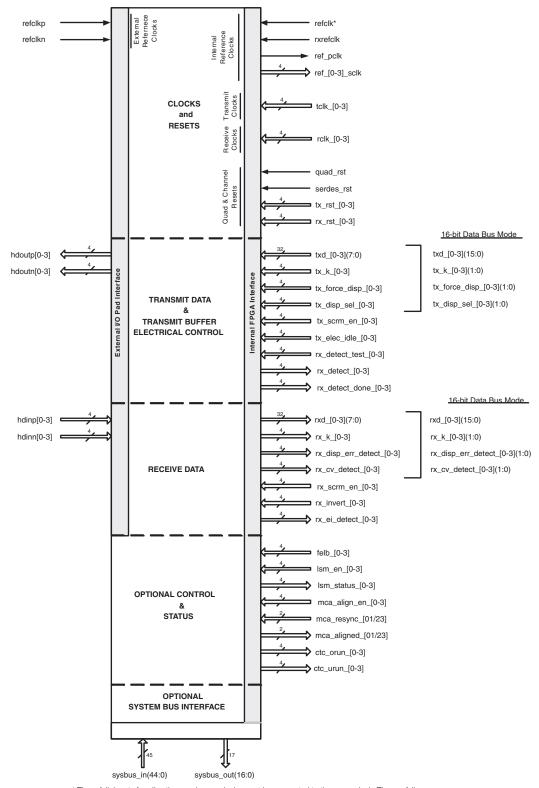

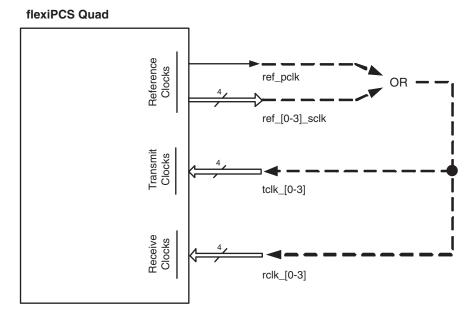

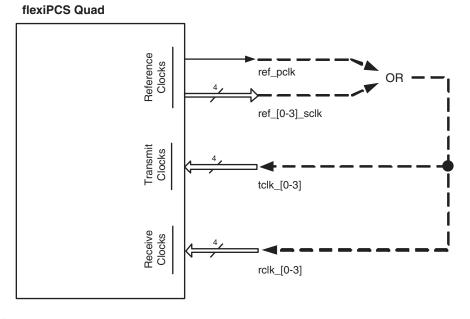

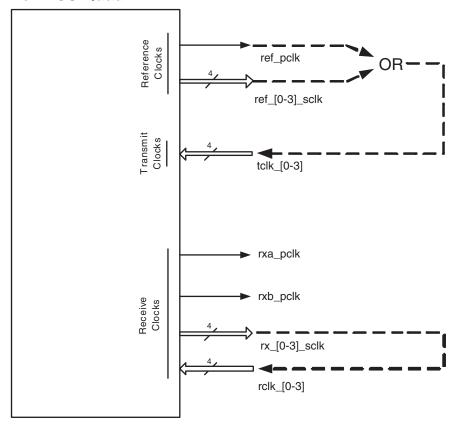

Figure 2-2 displays the common list of SERDES clock and reset pins for one PCS quad. In addition to these pins, each PCS mode will also have data, control, and status ports specific to the protocol mode chosen. The functionality of these additional ports is discussed in the appropriate **LatticeSC/M Family flexiPCS Data Sheet** section.

Figure 2-2. Common SERDES Port Pin Diagram

<sup>\*</sup> The refclk inputs for all active quads on a device must be connected to the same clock. The rxrefclk inputs for all active quads on a device do not have to be connected to the same clock.

## **SERDES Port Description**

Table 2-2 lists all the common ports to/from a PCS quad for the SERDES logic. A brief description for each port is given in the table. A detailed description of the function of each port is given in the **SERDES Functionality Detailed Description** section.

Table 2-2. SERDES Common Ports

| Symbol         | Direction/<br>Interface | Clock | Description                                                                                                                                                                                                                                                                                                                                |

|----------------|-------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reference Cloc | ks                      |       |                                                                                                                                                                                                                                                                                                                                            |

| refclkp        | In from I/O pad         | N/A   | Reference clock input, positive. Dedicated CML input.                                                                                                                                                                                                                                                                                      |

| refclkn        | In from I/O pad         | N/A   | Reference clock input, negative. Dedicated CML input                                                                                                                                                                                                                                                                                       |

| refclk         | In from FPGA            | N/A   | Optional transmit reference clock input from FPGA logic. Can be used instead of I/O pin reference clock.                                                                                                                                                                                                                                   |

|                |                         |       | The Tx refclk inputs for all active quads on a device must be connected to the same clock.                                                                                                                                                                                                                                                 |

| rxrefclk       | In from FPGA            | N/A   | Optional receive reference clock input from FPGA logic. Can be used instead of I/O pin reference clock. The rxrefclk inputs for all active quads do not have to be connected to the same clock.                                                                                                                                            |

| ref_pclk       | Out to FPGA             | N/A   | Locked reference clock selection from one of the four channels. Selection made through register setting. Output to primary clock routing.                                                                                                                                                                                                  |

| ref_[0-3]_sclk | Out to FPGA             | N/A   | Per channel locked reference clocks. Each channel's locked reference clock is connected to FPGA general routing. Clocks connected to general FPGA routing can route to either primary or secondary clocks with a larger clock injection delay than clock ports dedicated solely to primary clock routing.                                  |

| Transmit Clock | S                       |       |                                                                                                                                                                                                                                                                                                                                            |

| tclk_[0-3]     | In from FPGA            | N/A   | Per channel transmit clock inputs from FPGA. Used to clock the TX data phase compensation FIFO with clock synchronous to the reference clock. May also be used to clock the RX data phase compensation FIFO with a clock synchronous to the reference clock. May not be created from a DLL to PLL combination or a PLL to PLL combination. |

| Receive Clocks | ,                       |       |                                                                                                                                                                                                                                                                                                                                            |

| rxa_pclk       | Out to FPGA             | N/A   | Recovered receive clock selection from one of the four channels. Selection made through register setting. Output to primary clock routing.                                                                                                                                                                                                 |

| rxb_pclk       | Out to FPGA             | N/A   | Recovered receive clock selection from one of the four channels. Selection made through register setting. Output to primary clock routing.                                                                                                                                                                                                 |

| rx_[0-3]_sclk  | Out to FPGA             | N/A   | Per channel recovered receive clocks. Each channel's locked reference clock is connected to FPGA general routing. Clocks connected to general FPGA routing can route to either primary or secondary clocks with a larger clock injection delay than clock ports dedicated solely to primary clock routing.                                 |

| rclk_[0-3]     | In from FPGA            | N/A   | Per channel receive clock inputs from FPGA. May be used to clock the RX data phase compensation FIFO with a clock synchronous to the reference and/or receive reference clock. May not be created from a DLL to PLL combination or a PLL to PLL combination.                                                                               |

| Resets         | <b>!</b>                | I     |                                                                                                                                                                                                                                                                                                                                            |

| quad_rst       | In from FPGA            | ASYNC | Active high, asynchronous reset for all channels of SERDES and PCS logic.                                                                                                                                                                                                                                                                  |

| serdes_rst     | In from FPGA            | ASYNC | Active high, asynchronous reset for all channels of the SERDES.                                                                                                                                                                                                                                                                            |

| tx_rst_[0-3]   | In from FPGA            | ASYNC | Per channel active high, asynchronous reset of individual transmit channel of PCS logic.                                                                                                                                                                                                                                                   |

| rx_rst_[0-3]   | In from FPGA            | ASYNC | Per channel active high, asynchronous reset of individual receive channel of PCS logic.                                                                                                                                                                                                                                                    |

| Transmit Data  | •                       |       |                                                                                                                                                                                                                                                                                                                                            |

| hdoutp[0-3]    | Out to I/O pad          | N/A   | High-speed CML serial output, positive.                                                                                                                                                                                                                                                                                                    |

| hdoutn[0-3]    | Out to I/O pad          | N/A   | High-speed CML serial output, negative.                                                                                                                                                                                                                                                                                                    |

Table 2-2. SERDES Common Ports

| Symbol       | Direction/<br>Interface | Clock | Description                            |

|--------------|-------------------------|-------|----------------------------------------|

| Receive Data |                         |       |                                        |

| hdinp[0-3]   | In from I/O pad         | N/A   | High-speed CML serial input, positive. |

| hdinn[0-3]   | In from I/O pad         | N/A   | High-speed CML serial input, negative. |

## **SERDES Functionality Detailed Description**

The following section provides a description of the operation of the SERDES for all PCS modes. The functional description is organized according to the port listing shown in Figure 2-2. The System Bus Offset Addresses for any control and status registers relevant to a given function are provided with the description of the operation of that function.

## **SERDES Powerup**

By default, the SERDES logic in all quads is powered down. The SERDES logic must be powered up in order to access any channel in a specific SERDES/PCS quad, regardless of the quad mode chosen. The SERDES logic in a SERDES/PCS quad is powered up by writing the appropriate Quad Interface Register Offset Address 0x28, bit 1 to a '1'. For more information regarding hot socketing requirements, see the Architecture section and DC and Switching Characteristics section of the LatticeSC/M Family Data Sheet.

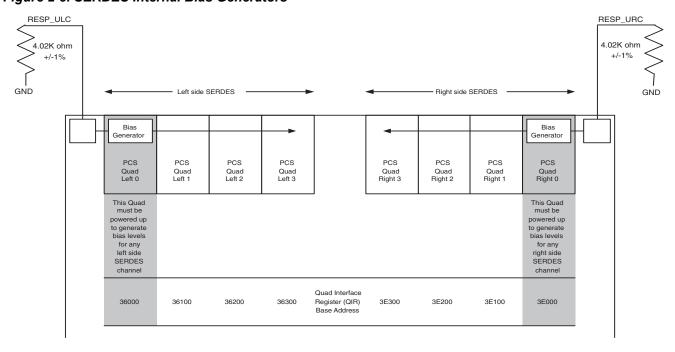

The bias levels for all SERDES channels on one side of a LatticeSC device (either left side or right side) are set by tying that side's external bias resistor to ground. Figure 2-3 shows the bias resistor connections for the SERDES/PCS quads on each side of the device. The bias resistor value must be 4.02K ohm +/- 1%. Note the bias levels for all left side SERDES channels are set in the leftmost quad (Quad Base Address 36000). This means that the leftmost quad SERDES must be powered up for proper operation of any SERDES channel on the left side (meaning Quad Interface Register 36028, bit 1 must be set to a '1'). Likewise, the bias levels for all right side SERDES channels are set in the rightmost quad (Quad Base Address 3E000). This means that the rightmost quad SERDES must be powered up for proper operation of any SERDES channel on the right side (meaning Quad Interface Register 3E028, bit 1 must be set to a '1').

Figure 2-3. SERDES Internal Bias Generators

Figure 2-4. SERDES Internal Bias Generators (for Packages that Include the RESPN [ULC/URC] Pins)

## Clocks & Resets

Every LatticeSC PCS quad regardless of selected mode has the same basic clocking and reset architecture. The choice of reference clock frequencies and the selection of PCS/FPGA interface clocks will be determined by the particular application. The following is a description of the functions of the clock and reset ports. For a specific explanation of the clocking strategy for a particular data protocol, refer to the relevant section of the **flexiPCS Data Sheet**.

## **Reference Clocks**

A reference clock or clocks must be provided to each active quad to provide a synchronization reference for the SERDES PLLs. Reference clock(s) are shared among all four channels of each quad. Reference clocks must be supplied for each active quad in the device. The LatticeSC SERDES provides two options for choosing the source of the reference clock(s) as shown in Table 2-3.

Table 2-3. Reference Clock Source Selection

| Quad Interface Register Offset Address = 0x29 |   | Reference Clock Source Selection                                                                                                                                                                  |

|-----------------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 3 Bit 4                                   |   | Description                                                                                                                                                                                       |

| 0                                             | 0 | Single external reference clock supplied to <b>ref- clkn/refclkp</b> pins. Reference clock used for both transmit and receive directions. (Default mode).                                         |

| 1                                             | 0 | Internal (from FPGA logic) reference clocks supplied to refclk (transmit) and rxrefclk (receive). refclk and rxrefclk can be tied together or connected to separate clocks at the FPGA interface. |

In the default reference clock mode (QIR 0x29, bits [3:4] = "00"), one external reference clock needs to be supplied to pins **refclkn/refclkp**. In this mode, the **refclkn/refclkp** clock supplies the reference frequency for both transmit and receive data paths. This is appropriate for any applications where the transmit and receive frequencies are

# SERDES Functionality/Electrical & Timing Characteristics LatticeSC/M Family flexiPCS Data Sheet

## **Lattice Semiconductor**

within the specified ppm tolerance for the LatticeSC SERDES (See the **SERDES Electrical & Timing Characteristics** section).

For applications where the transmit and receive frequencies are not the same, two internal reference clocks can be supplied. This mode can be selected by setting the Quad Interface Offset Register 0x29, bits [3:4] = "10". The transmit reference clock is then supplied to the refclk port at the flexiPCS/FPGA interface. Note that the refclk inputs for all active quads on a device must be connected to the same clock internally. The receive reference clock is supplied to the rxrefclk port at the PCS/FPGA interface. The rxrefclk inputs for all active quads on a device does not have to be connected to the same clock internally. The refclk and rxrefclk reference clock inputs can be tied to the same clock or can be tied to different clocks. In modes which utilize a Clock Tolerance Compensation (CTC) block, these clocks must be the same frequency to within the given protocol's clock tolerance specification. In non-CTC modes (SERDES Only, Generic 8b10b, and SONET modes) there is no such restriction.

A diagram illustrating the reference clock options for the SERDES is shown in Figure 2-5:

Figure 2-5. SERDES Reference Clock Selections

## **Reference Clock Control Registers**

Quad Interface Register bits can be used to control other options relevant when using an external reference clock.

By default, the external reference clock inputs **refclkn/refclkp** are AC coupled. These reference clock pins can be set to DC coupling by setting Quad Interface Register Offset Address 0x29, bit 1 to '1'.

## **Loss of Lock Alarm Registers**

Both the transmit PLL and the individual channel CDRs have counter-based loss-of-lock detectors. If the transmit PLL loses lock, the loss-of-lock for the PLL is asserted and remains asserted until the PLL reaguires lock.

If a CDR loses lock to the incoming data on the **hdin** inputs, the loss-of-lock for that channel is asserted and the CDR attempts to lock to the reference clock instead. After successfully locking to the reference clock, loss-of-lock for that channel is deasserted and the CDR then attempts to relock to the incoming channel's data. If successful, the CDR will then remain locked to the data. If the CDR cannot relock to the incoming data, then it will once again report an out of lock condition and repeat the training cycle.

The loss of lock alarm for the quad TX PLL can be read at Quad Interface Register Offset Address 0x86, bit 7. The loss of lock alarm for each channel's receive CDR can be read at the appropriate Channel Interface Register Offset Address 0x94, bit 6.

The receiver CDR loss of lock alarm for each channel's receiver input can be read at Channel Interface Register Offset Address 0x94, bit 6.

The time to detect both lock and loss-of-lock for the transmit reference clock PLLs or the individual CDR, when QIR0x2A[7:6]=00 (+/- 600 ppm), is shown in Table 2-4

Table 2-4. Time to Lock and Loss-of-Lock for TX PLL and CDRs

| Description                                               | Min. | Тур.    | Max. | Units |

|-----------------------------------------------------------|------|---------|------|-------|

| Time to detect locked/unlocked condition for x1 CDR modes |      | 655360  |      | UI    |

| Time to detect locked/unlocked condition for x2 CDR modes |      | 1310720 |      | UI    |

## **Rate Mode Registers**

The following section describes how to change the SERDES generated clock rates through register settings. These settings are to be set via an auto-configuration file generated within IPexpress. Reference clock and output clock frequencies can by set by the user in the GUI and the optimal register settings will be calculated and written to the auto-configuration file.

Note: There are also frequency dependent SERDES performance control bits that are not writable via the Systembus. These control bits are set in the auto-configuration file created within IPexpress and passed into the bitstream through the normal FPGA design flow (map, par, bitgen). To change the bit rate for a SERDES, specify the proper values for the affected flexiPCS quad in IPexpress and regenerate the auto-configuration file. Failure to regenerate the auto-configuration file with the proper value may result in non-optimal SERDES operation.

The following information is provided for reference. If the registers described in the **Full Rate and Half Rate Modes** section are changed via the Systembus after a bitstream has been loaded, non-optimal SERDES performance may result for the reasons described above.

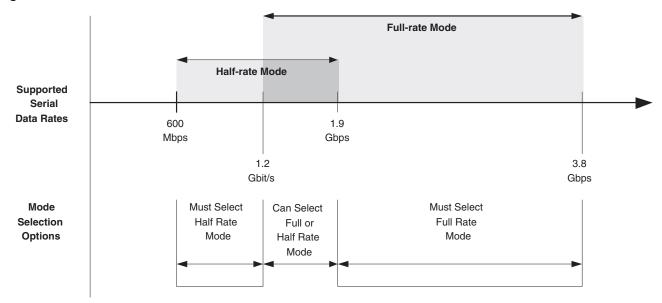

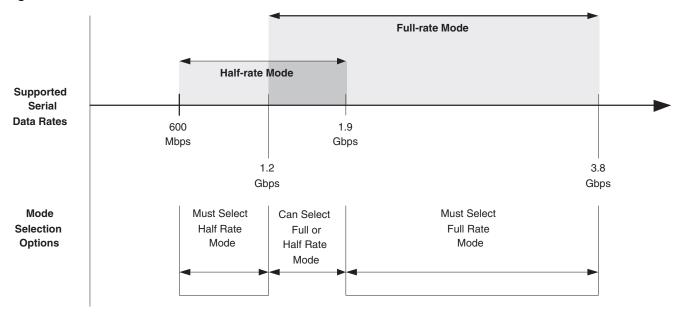

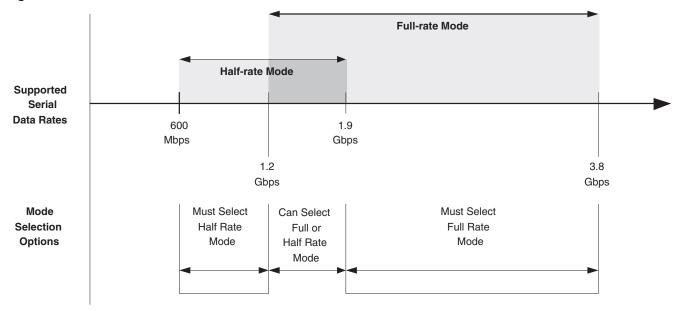

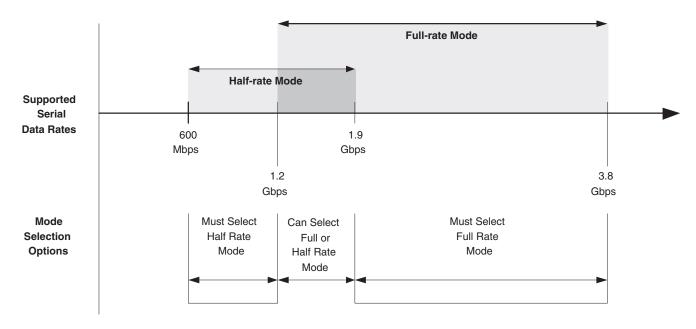

## **Full-Rate and Half-Rate Modes**

The SERDES PLLs support data rates from 1.2 Gbps to 3.8 Gbps. A half-rate mode is available to permit operation of the SERDES at industry standard protocol data rates lower than 1.2 Gbps. The combination of half-rate and full-rate modes allow operation of a single SERDES channel at any data rate from 600 Mbps to 3.8 Gbps as shown in Figure 2-6.

Figure 2-6. Full-Rate and Half-Rate Mode Selection

Each of the four receive channels can be independently configured to receive data at either full-rate or half-rate. Similarly each of the four transmit channels can be independently configured to transmit data at either full-rate or half-rate. The truth table shown in Table 2-5 for a transmit channel describes the reference clock and data rate relationship during full and half-rate operation. The same relationship applies to each receive channel as well.

Note that the internal serial (bit) clock multiplier is shown for both 8-bit and 10-bit modes in Table 2-5. The choice of 8-bit or 10-bit mode is made by the user depending on the particular application of the PCS. The control for 8-bit or 10-bit mode is described in each LatticeSC/M Family flexiPCS Data Sheet section.

The FPGA interface clock multiplier value applies to all PCS/FPGA interface locked reference, transmit and receive clocks.

| Table 2-5. Full-Rate and Half-Rate Mode | Operations |

|-----------------------------------------|------------|

|                                         |            |

| Rate Mode                           | Reference Clock Mode               |                                                              | FPGA Interface Clock Multiplier  Quad Interface Register  Offset Address 0x191 |                             |

|-------------------------------------|------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------|

| Channel Interface<br>Register       | Quad Interface                     | Internal<br>Serial (bit)<br>Clock<br>Multiplier <sup>1</sup> |                                                                                |                             |

| Offset Address<br>= 0x13            | Register<br>Offset Address = 0x28, |                                                              | 8/10 Bit Data Bus<br>Width                                                     | 16/20 Bit Data Bus<br>Width |

| Transmit - Bit 5<br>Receive - Bit 4 | Bits [2:3]                         |                                                              | Transmit - Bit 4 = '0'<br>Receive - Bit 5 = '0'                                |                             |

| 0                                   | 00                                 | 16X or 20X                                                   | 2X                                                                             | 1X                          |

| Full rate                           | 01                                 | 8X or 10X                                                    | 1X                                                                             | (1/2)X                      |

| (1.2 Gbps - 3.8 Gbps)               | 10                                 | 4X or 5X                                                     | (1/2)X                                                                         | (1/4)X                      |

| 1                                   | 00                                 | 8X or 10X                                                    | 1X                                                                             | (1/2)X                      |

| Half rate                           | 01                                 | 4X or 5X                                                     | (1/2)X                                                                         | (1/4)X                      |

| (600 Mbps - 1.9 Gbps)               | 10                                 | 2X or (5/2)X                                                 | (1/4)X                                                                         | (1/8)X                      |

<sup>1.</sup> All clock multiplier values are with respect to supplied reference clock frequency.

Note: There are frequency dependent SERDES performance control bits that are not writable via the Systembus. These control bits are set in the auto-configuration file created within IPexpress and passed into the bitstream through the normal FPGA design flow (map, par, bitgen). To change the PLL rate for a SERDES specify the proper

value for the affected flexiPCS quad in IPexpress and regenerate the auto-configuration file. Failure to do this may result in non-optimal SERDES operation. These settings do not need to be changed when selecting between full-rate and half-rate operation.

The registers which change the PLL rate for the transmit direction are: the Reference Clock Mode (QIR 0x28, bits [2:3]). The Rate Mode register (CIR 0x13, bit 5) and the FPGA Interface Clock Multiplier register (QIR0x19, bit 4) for the transmit direction do not affect the transmit PLL rate and can be changed after configuration.

The registers which change the PLL rate for the receive direction are: the Reference Clock Mode (QIR 0x28, bits [2:3]) and the Rate Mode register (CIR 0x13, bit 4). The FPGA Interface Clock Multiplier register (QIR0x19, bit 5) for the receive direction does not affect the receive PLL rate and can be changed after configuration.

## **Full Rate Timing**

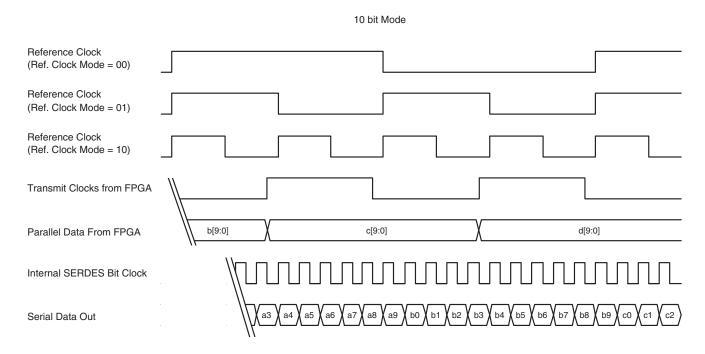

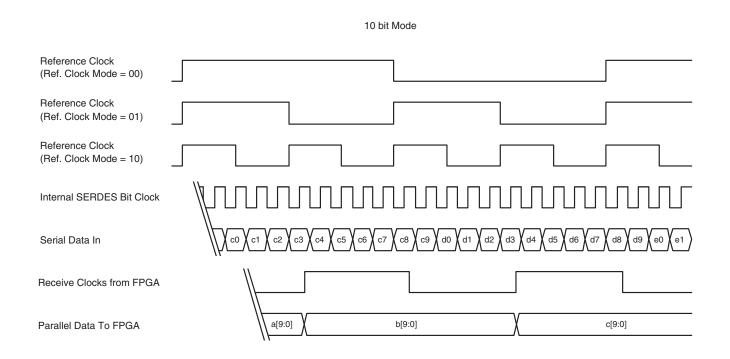

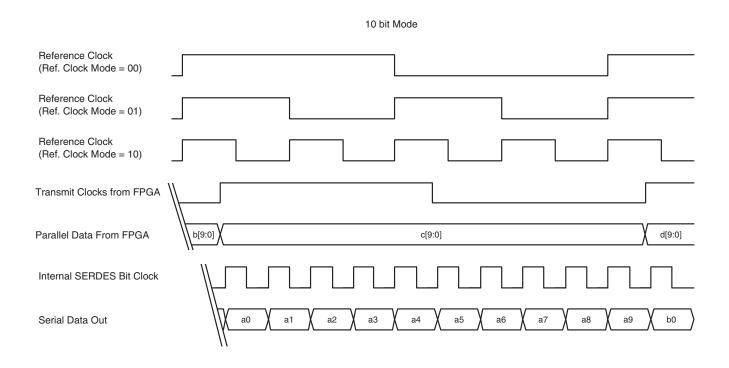

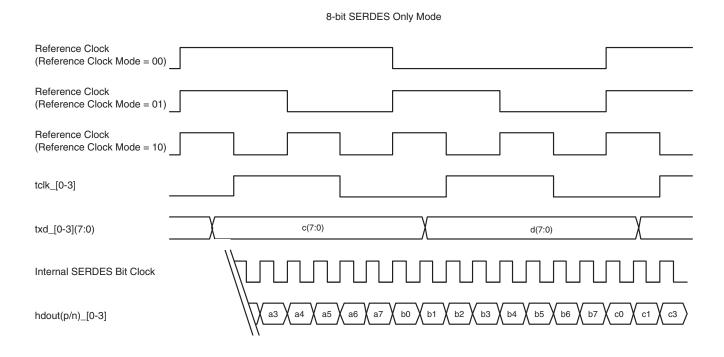

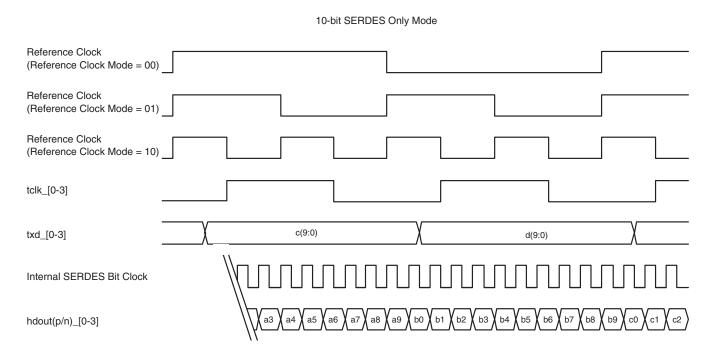

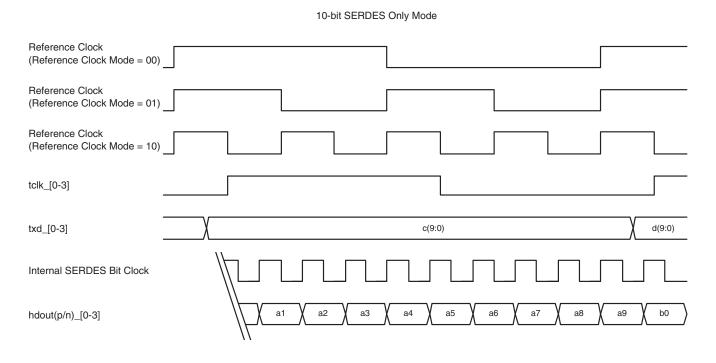

The relationships between the reference clock, the internal SERDES serial (bit) clock, and the PCS/FPGA interface clocks for a channel set to full rate are shown in the following diagrams. Figure 2-7 shows the timing for a transmit channel and Figure 2-8 shows the timing for a receive channel. Note that each channel in a quad can be independently set to full or half rate mode (although all channels in a given quad share the same reference clock).

Each diagram shows the relationship for all three possible reference clock modes which can be chosen. Note that the reference clock mode applies to all channels of a given quad.

Figure 2-7. Full-Rate Transmit Path Timing Diagram

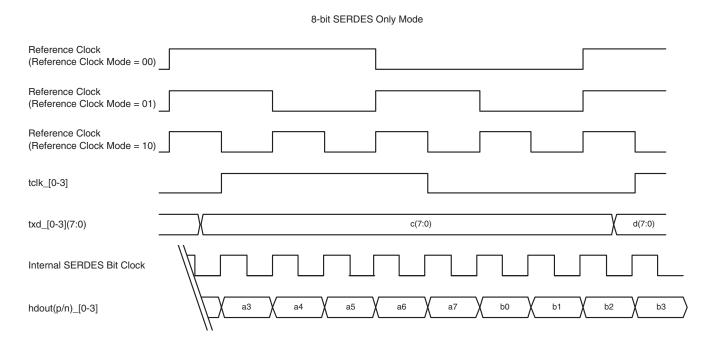

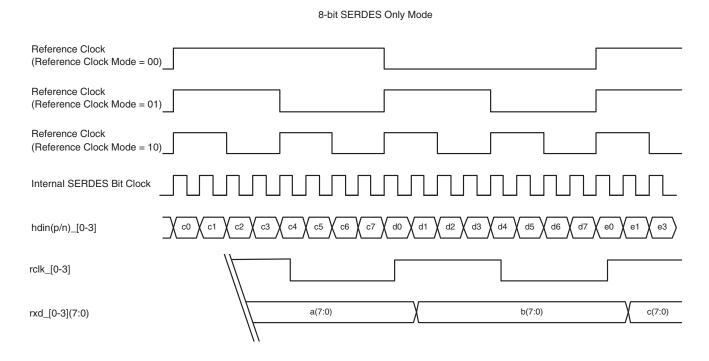

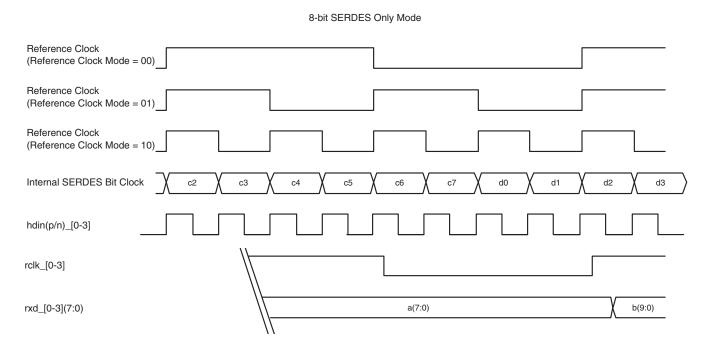

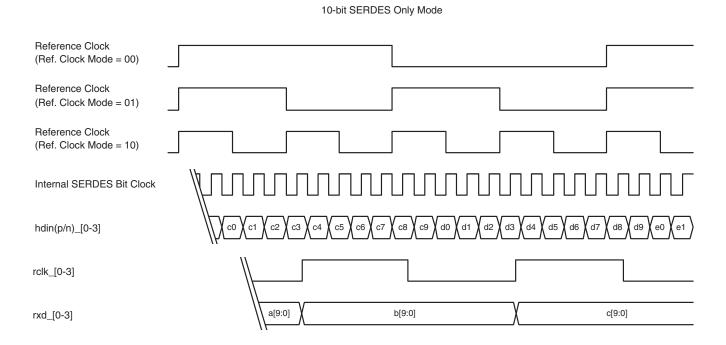

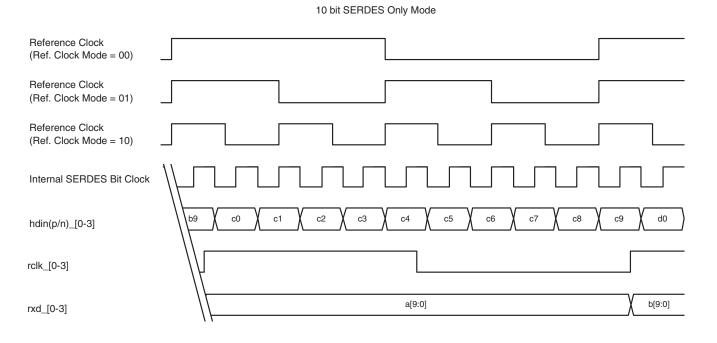

Figure 2-8. Full-Rate Receive Path Timing Diagram

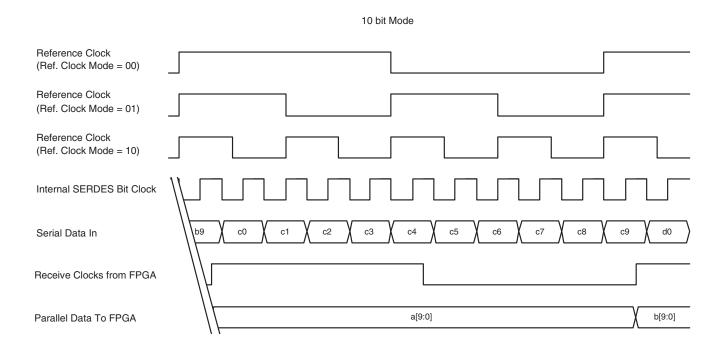

## **Half Rate Timing**

The relationships between the reference clock, the internal SERDES serial (bit) clock, and the PCS/FPGA interface clocks for a channel set to halfrate are shown in the following diagrams. Figure 2-9 shows the timing for a transmit channel and Figure 2-10 shows the timing for a receive channel. Note that each channel in a quad can be independently set to full or half rate mode (although all channels in a given quad share the same reference clock).

Each diagram shows the relationship for all three possible reference clock modes which can be chosen. Note that the reference clock mode applies to all channels of a given quad.

Figure 2-9. Half-Rate Transmit Path Timing Diagram

Figure 2-10. Half-Rate Receive Path Timing Diagram

## **Locked Reference and Transmit Clocks**

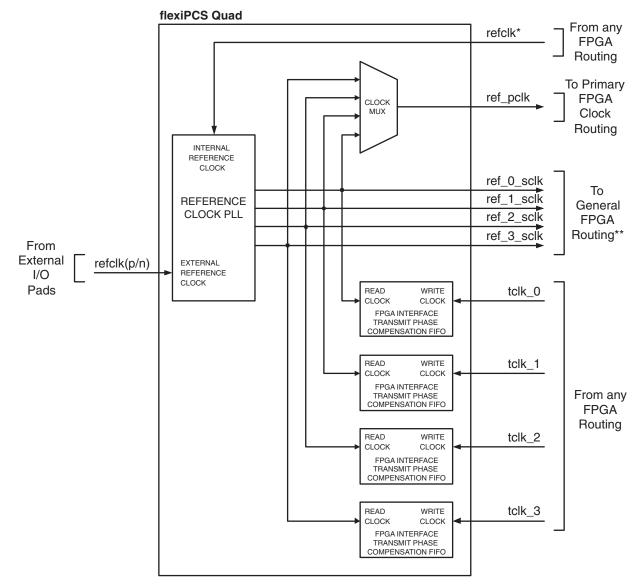

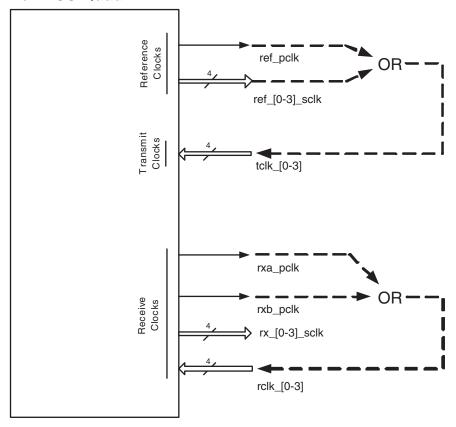

Figure 2-11 illustrates the relationships between the various PCS/FPGA interface locked reference and transmit clocks.

Figure 2-11. Locked Reference and Transmit Clocks

<sup>\*</sup> The refclk inputs for all active quads on a device must be connected to the same clock. The rxrefclk inputs for all active quads on a device do not have to be connected to the same clock.

The reference clock PLL in the SERDES is able to lock to either an external reference clock, or a reference clock provided from the FPGA core.

## **Locked Reference Clocks to FPGA Logic**

The PCS provides one locked reference clock per channel (ref\_[0-3]\_sclk) to the FPGA. Each channel's locked reference clock is connected to FPGA general routing. Clocks connected to general FPGA routing can route to either primary or secondary clocks with a larger clock injection delay than clock ports dedicated solely to primary

<sup>\*\*</sup> Clocks connected to general FPGA routing can route to either primary or secondary clocks with a larger clock injection delay than clock ports dedicated solely to primary clock routing.

clock routing. A four-way mux of all locked reference channel clocks (**ref\_pclk**) is provided on a primary clock. The clock selection for **ref\_pclk** is controlled by writing to Quad Interface Register Offset Address 0x02, bits 2 and 3 as shown in Table 2-6. All locked reference clocks are generated from a single PLL.

Table 2-6. Locked Reference Clock Selection for ref pclk

| Quad Interface Register Offset Address = 0x02 |       | Locked Reference Clock Selection         |

|-----------------------------------------------|-------|------------------------------------------|

| Bit 2                                         | Bit 3 | Description                              |

| 0                                             | 0     | Selects locked reference clock channel 0 |

| 0                                             | 1     | Selects locked reference clock channel 1 |

| 1                                             | 0     | Selects locked reference clock channel 2 |

| 1                                             | 1     | Selects locked reference clock channel 3 |

## **Transmit Clocks**

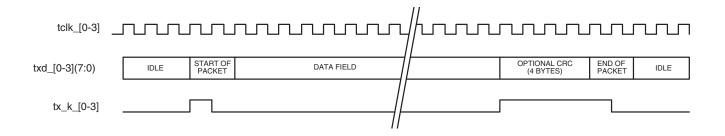

Each respective channel's input transmit clock can be driven from the FPGA logic on pins tclk\_[0-3]. These clocks serve as the write clocks to FPGA interface phase compensation FIFOs embedded in the quad PCS logic as shown in Table 2-9.

## **Transmit Clocks from FPGA Logic**

The FPGA interface phase compensation FIFOs are intended only to provide a clean timing interface to the PCS logic and cannot be used to arbitrate between different clock frequencies. Therefore the tclk[0-3] ports must be connected to clocks which are frequency locked to the reference clock. Typically, they are fed from the locked reference clock outputs from the PCS to the FPGA (ref\_pclk or the appropriate ref\_[0-3]\_sclk). The phase compensation FIFOs are designed to handle any phase shift of these clocks due to internal clock routing delays. The clocks connected to the tclk[0-3] ports may not be created from a DLL to PLL combination or a PLL to PLL combination as these combinations may create short term frequency deviations that may overflow or underflow the FPGA interface phase compensation FIFOs.

## 16/20 Bit Data Bus Mode Transmit Clock Rates

The above description of locked reference and transmit clock rates assumes that the quad transmit data path is set to "8/10 bit data bus" mode. In this case, one byte of data is to be presented to the PCS every clock cycle at the FPGA interface clock rate shown in Table 2-5 This is the default mode. The transmit data path for a quad can be set to "16/20 bit data bus" mode by writing Quad Interface Register Offset Address 0x19 bit 4 to a "1". In this mode, two bytes of data are to be presented to the PCS from the FPGA logic at 1/2 of the FPGA interface clock rate as shown in Table 2-5. In "16/20 bit data bus" mode, the byte on the lower bits at the PCS/FPGA interface is transmitted first, then the byte on the upper bits is transmitted second.

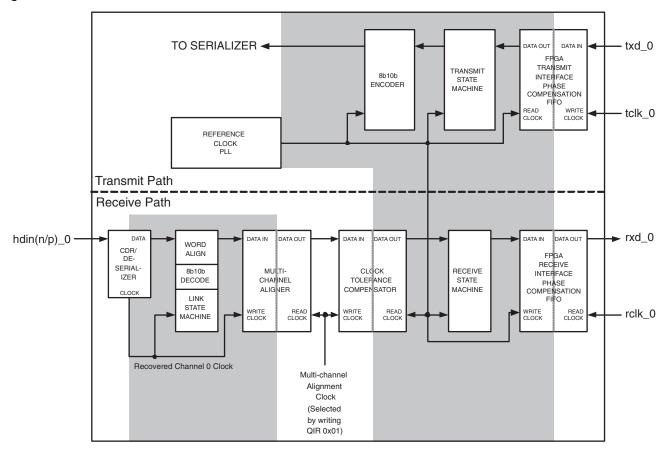

## **Receive Clocks**

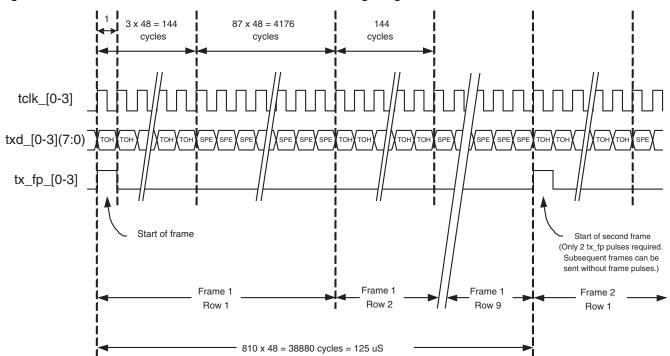

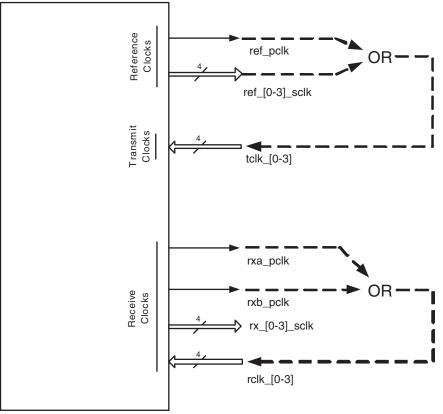

Figure 2-12 illustrates the relationships between the various PCS/FPGA interface receive clocks.

Figure 2-12. Receive Clocks

<sup>\*</sup> The refclk inputs for all active quads on a device must be connected to the same clock. The rxrefclk inputs for all active quads on a device do not have to be connected to the same clock.

<sup>\*\*</sup> Clocks connected to general FPGA routing can route to either primary or secondary clocks with a larger clock injection delay than clock ports dedicated solely to primary clock routing.

## **Receive Clocks to FPGA Logic**

Each of the four receive SERDES in a quad recovers a clock from the incoming data that is then used to clock the associated receive channel flexiPCS logic. The PCS provides a recovered clock per channel (rx\_[0-3]\_sclk) to the FPGA. Each channel's locked reference clock is connected to FPGA general routing. Clocks connected to general FPGA routing can route to either primary or secondary clocks with a larger clock injection delay than clock ports dedicated solely to primary clock routing. Two clocks are provided to the FPGA which are both a four-way mux of all receive channel clocks (rxa pclk and rxb pclk). These two clocks are provided on primary clocks.

The clock selection for **rxa\_pclk** is controlled by writing to Quad Interface Register Offset Address 0x02, bits 4 and 5 as shown in Table 2-7.

Table 2-7. Receive Clock Selection for rxa\_pclk

| Quad Interface Register Offset Address = 0x02 |       | Receive Clock Selection         |

|-----------------------------------------------|-------|---------------------------------|

| Bit 4                                         | Bit 5 | Description                     |

| 0                                             | 0     | Selects receive clock channel 0 |

| 0                                             | 1     | Selects receive clock channel 1 |

| 1                                             | 0     | Selects receive clock channel 2 |

| 1                                             | 1     | Selects receive clock channel 3 |

Note: Relevant only when multi-channel alignment not selected.

The clock selection for **rxb\_pclk** is controlled by writing to Quad Interface Register Offset Address 0x02, bits 6 and 7 as shown in Table 2-8.

Table 2-8. Receive Clock Selection for rxb\_pclk

| Quad Interface Register<br>Offset Address<br>= 0x02 |       | Receive Clock Selection         |  |

|-----------------------------------------------------|-------|---------------------------------|--|

| Bit 6                                               | Bit 7 | Description                     |  |

| 0                                                   | 0     | Selects receive clock channel 0 |  |

| 0                                                   | 1     | Selects receive clock channel 1 |  |

| 1                                                   | 0     | Selects receive clock channel 2 |  |

| 1                                                   | 1     | Selects receive clock channel 3 |  |

Note: Relevant only when multi-channel alignment not selected.

Recovered Clocks are sourced from the VCO of the CDR. During a loss of lock to data, these clocks will be unstable and produce high frequency clocks. Care must be taken when using these clocks that any downstream elements using these clocks can accept a clock with variable frequency and pulse widths.

## **Receive Clocks from FPGA Logic**

Each respective channel's input receive clock can be driven from the FPGA logic on pins **rclk[0-3]**. These clocks serve as the read clocks to FPGA interface phase compensation FIFOs embedded in the quad PCS logic as shown in Figure 2-12.

The FPGA interface phase compensation FIFOs are intended only to provide a clean timing interface to the PCS logic and cannot be used to arbitrate between different clock frequencies. Therefore the rclk[0-3] ports must be connected to clocks which are frequency locked to the respective channel's FPGA interface receive phase compensation FIFO write clock.

In modes where Multi-channel alignment and Clock Tolerance Compensation features are unused, the input receive clocks to the FPGA Interface Receive phase compensation FIFOs shown in Figure 2-12 are typically fed from the receive clock outputs from the PCS to the FPGA (rxa\_pclk, rxb\_pclk, or the appropriate rx\_[0-3]\_sclk). The phase compensation FIFOs are designed to handle any phase shift of these clocks due to internal clock rout-

## SERDES Functionality/Electrical & Timing Characteristics LatticeSC/M Family flexiPCS Data Sheet

## **Lattice Semiconductor**

ing delays. The clocks connected to the rclk[0-3] ports may not be created from a DLL to PLL combination or a PLL to PLL combination as these combinations may create short term frequency deviations that may overflow or underflow the FPGA interface phase compensation FIFOs.

When Multi-channel alignment is active, the write clock to the FPGA interface receive phase compensation FIFOs will be driven from a selection of one of the individual channel CDR clocks. For more information on control and timing issues for Multi-channel alignment, refer to the Multi-channel Alignment section of the LatticeSC/M Family flexiPCS Data Sheet.

When Clock Tolerance Compensation is active, the write clock to the FPGA interface receive phase compensation FIFOs will be driven from the PCS locked reference clock. In this case, the rclk[0-3] must be connected to clocks which are frequency locked to the locked reference clock, specifically the **ref\_pclk** or **ref\_[0-3]\_sclk** ports shown in Figure 2-11. For more information on control and timing issues for Clock Tolerance Compensation, refer to the Detailed Functionality section for each PCS mode.

#### 16/20 Bit Data Bus Mode Receive Clock Rates

The above description of receive clock rates assumes that the quad receive data path is set to "8/10 bit data bus" mode. In this case, one byte of data passed from the PCS to the FPGA logic every clock cycle at the FPGA interface clock rate shown in Figure 2-5. This is the default mode. The receive data path for a quad can be set to "16/20 bit data bus" mode by writing Quad Interface Register Offset Address 0x19 bit 5 to a "1". In this mode, two bytes of data are to provided by the PCS to the FPGA logic at 1/2 of the FPGA interface clock rate as shown in Table 2-5. In "16/20 bit data bus" mode, the first received byte is placed on the lower bits, and the second received byte is placed on the upper bits at the FPGA interface.

#### **Quad & Channel Resets**

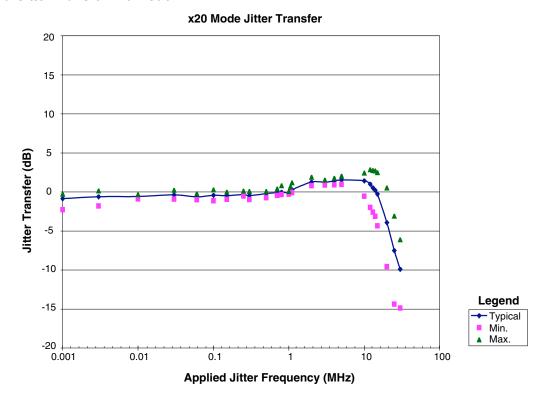

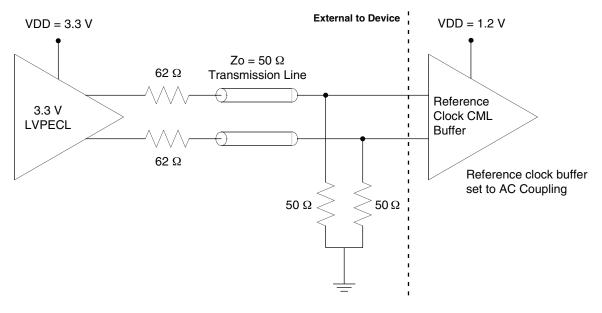

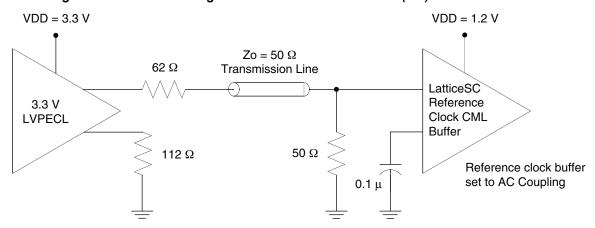

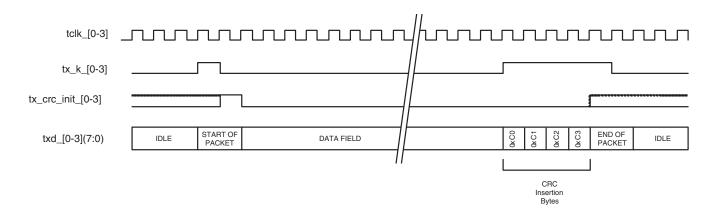

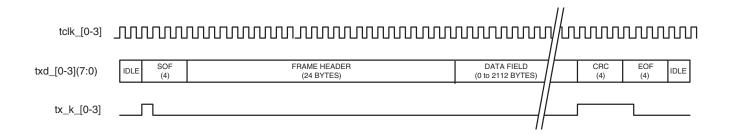

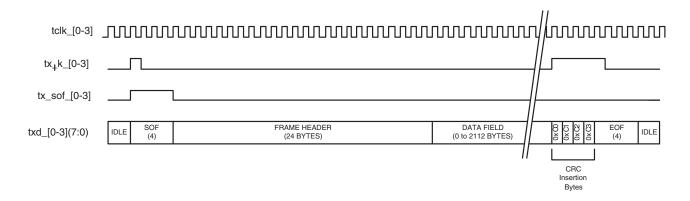

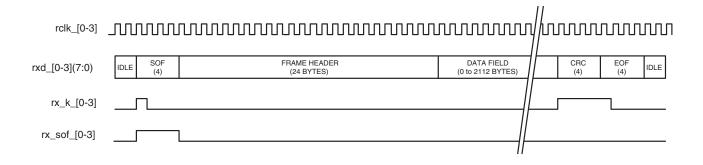

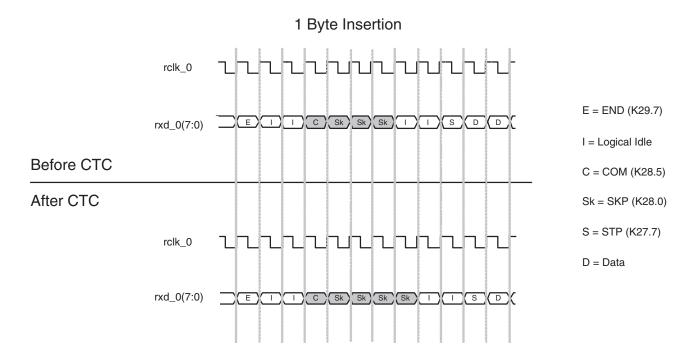

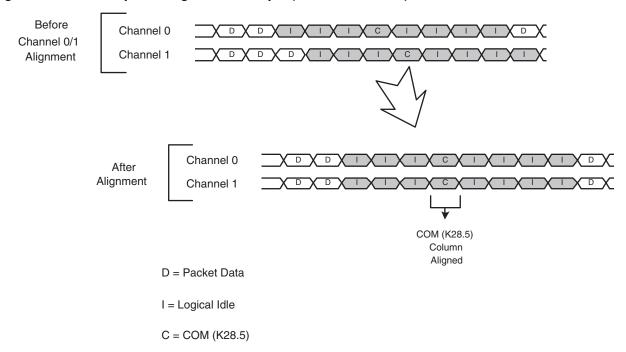

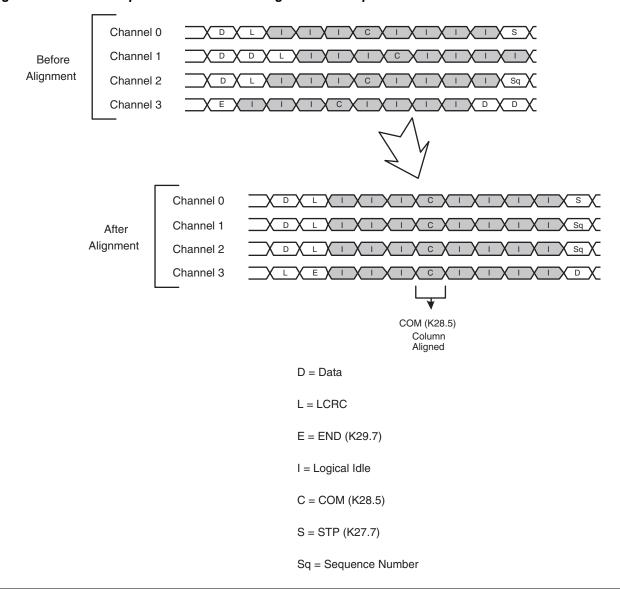

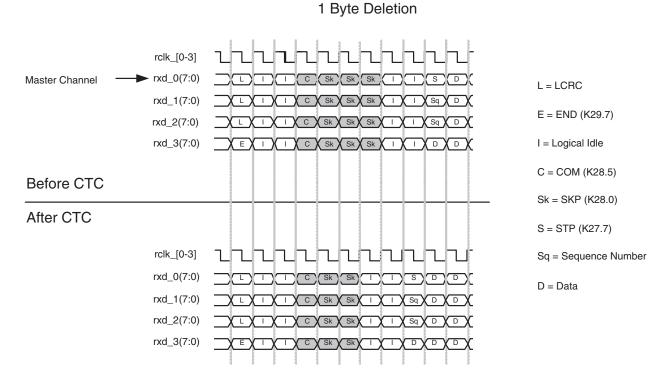

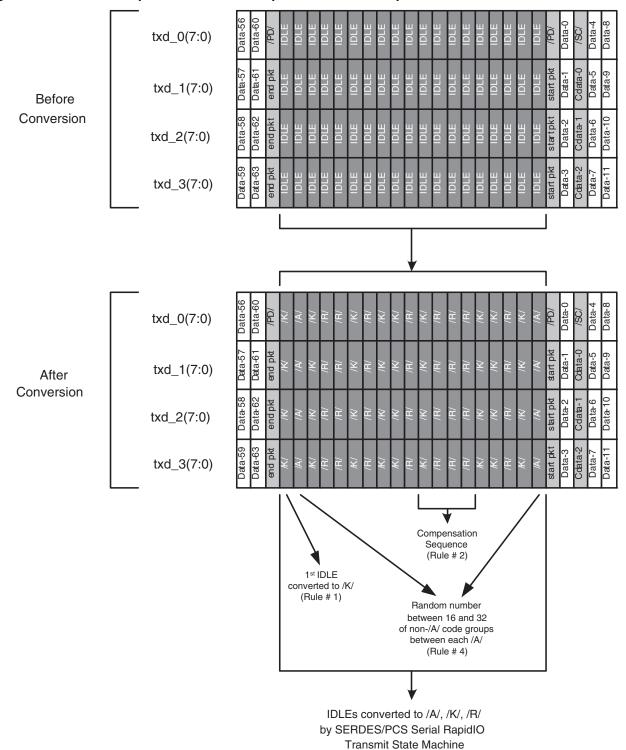

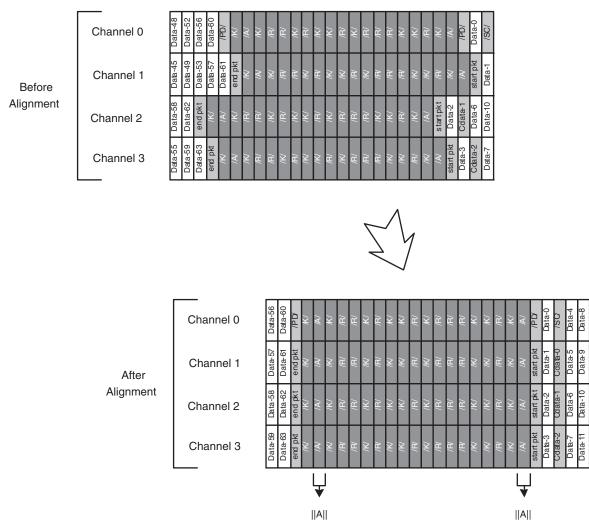

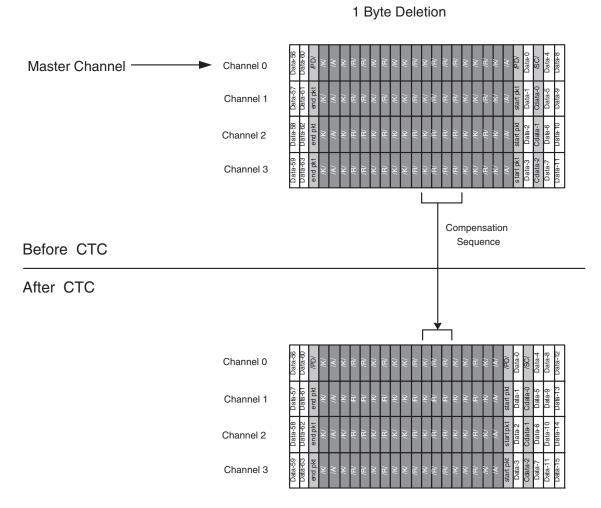

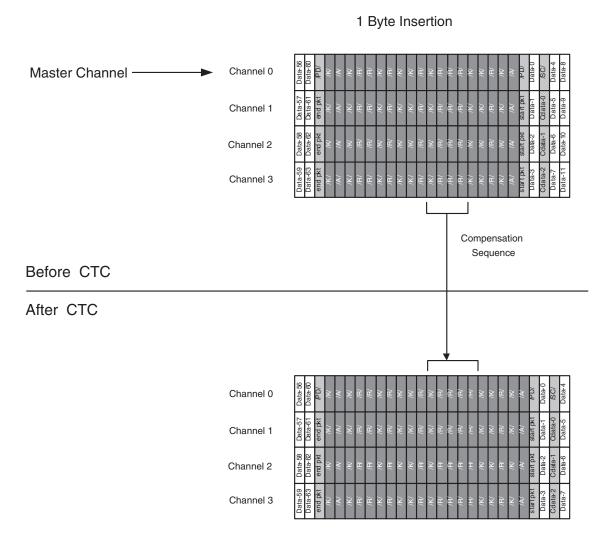

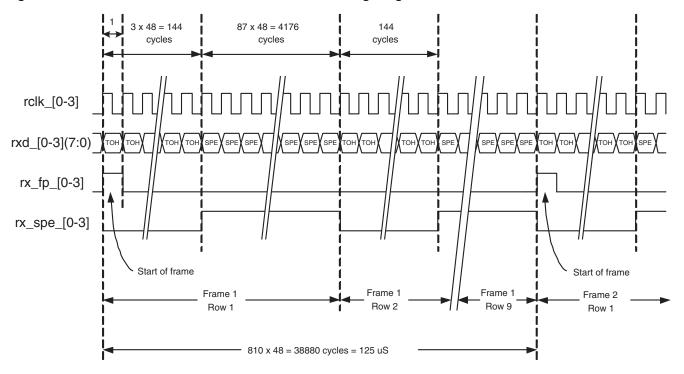

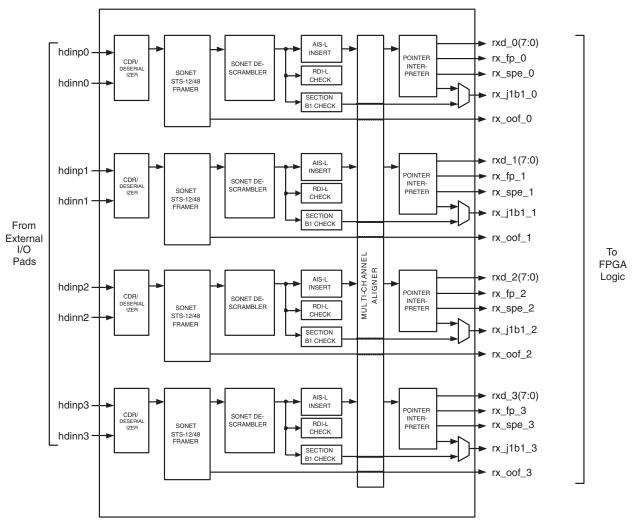

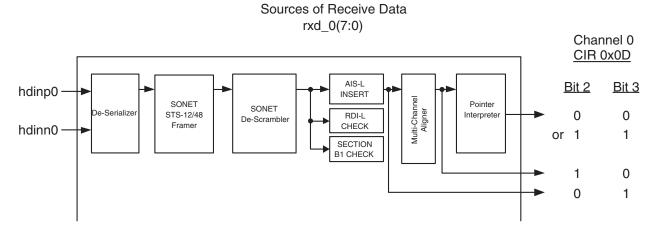

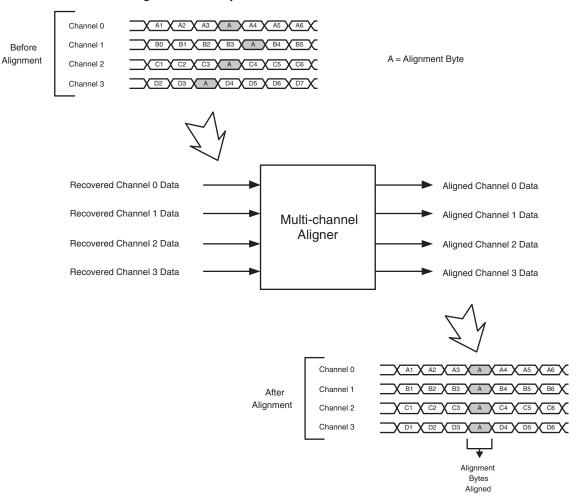

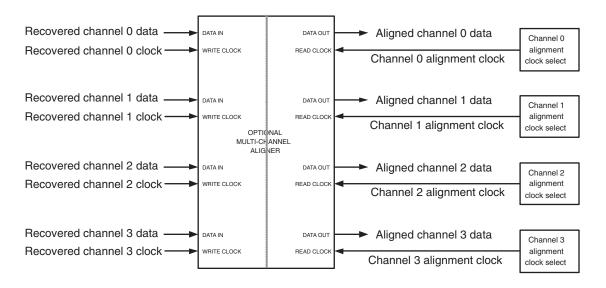

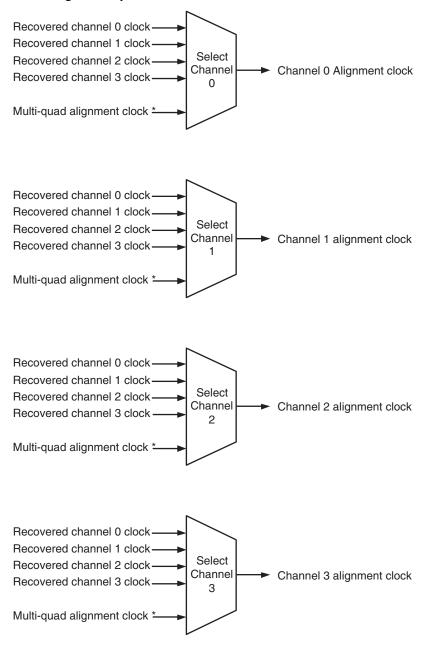

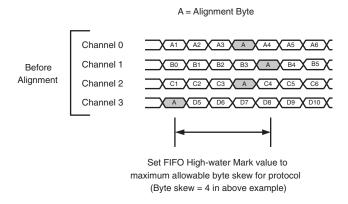

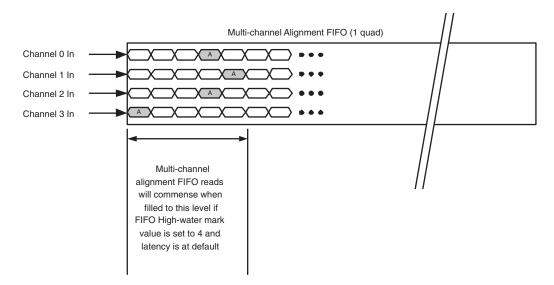

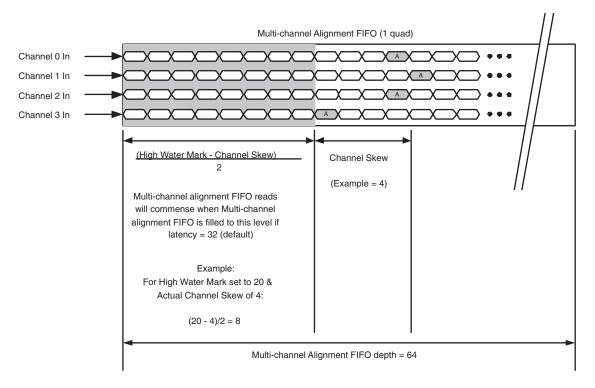

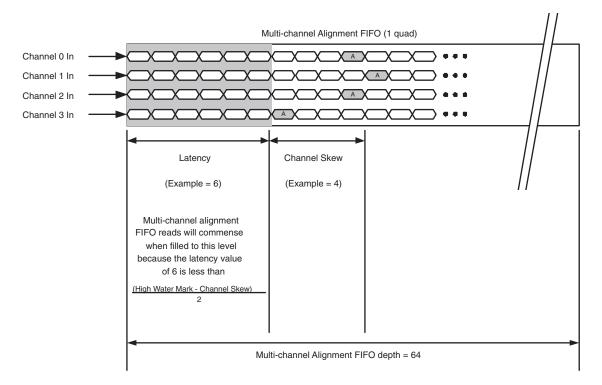

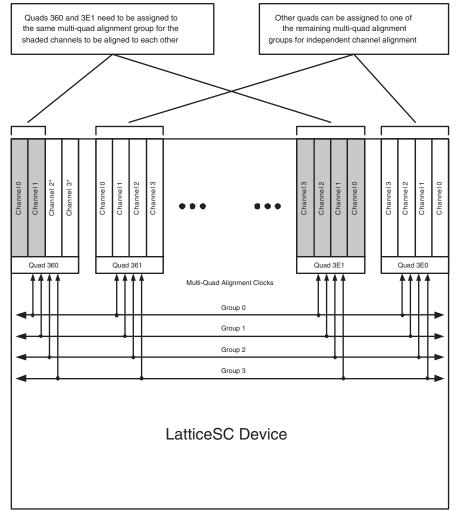

Resets are provided to reset an entire quad (either SERDES logic only or all flexiPCS logic) or each individual channel (all PCS logic per channel). These resets are driven from the FPGA logic or control registers. A summary of the control signals provided for reset are listed below. More detail on recommended initialization and reset sequences for the SERDES is provided in the **flexiPCS Reset Sequences** section.