### MachXO2 Family Handbook

HB1010 Version 03.8, May 2013

# MachXO2 Family Handbook Table of Contents

May 2013

| Introduction Features                                | 1-1  |

|------------------------------------------------------|------|

| Introduction                                         |      |

| Architecture                                         |      |

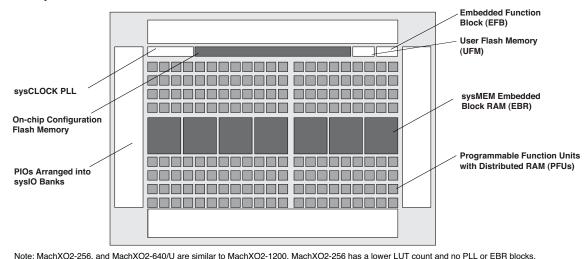

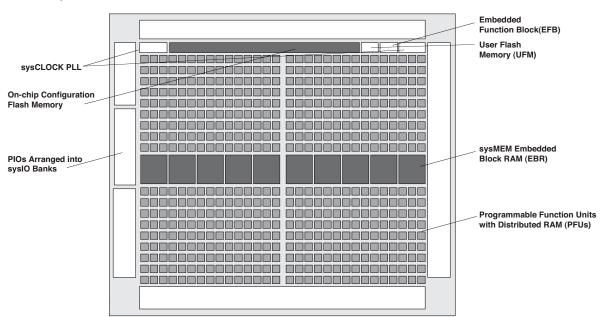

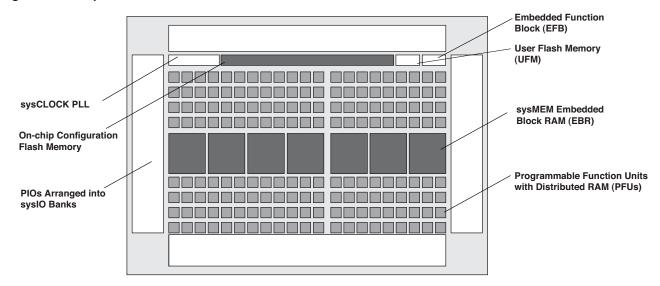

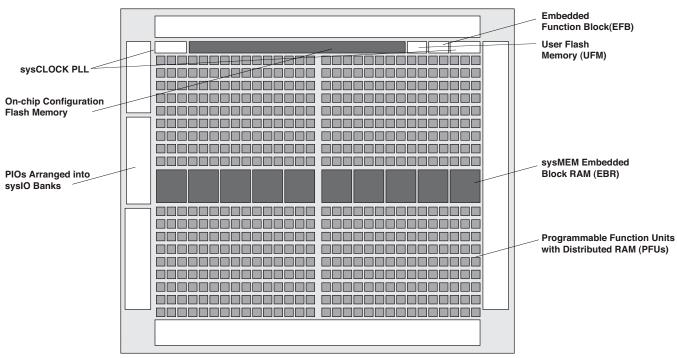

| Architecture Overview                                | 2-1  |

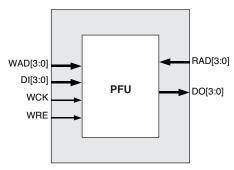

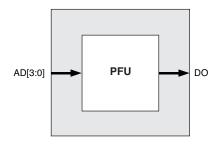

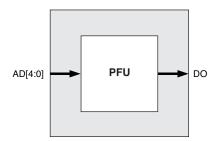

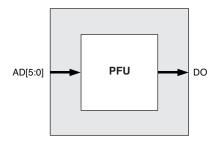

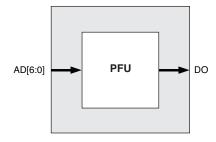

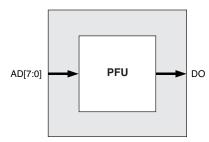

| PFU Blocks                                           |      |

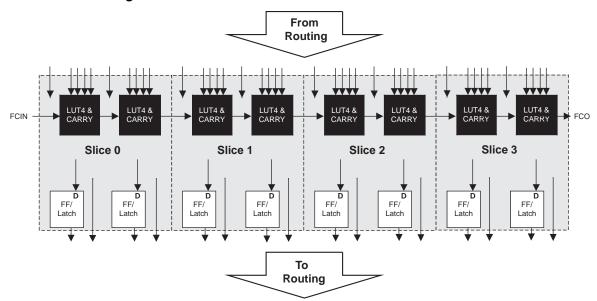

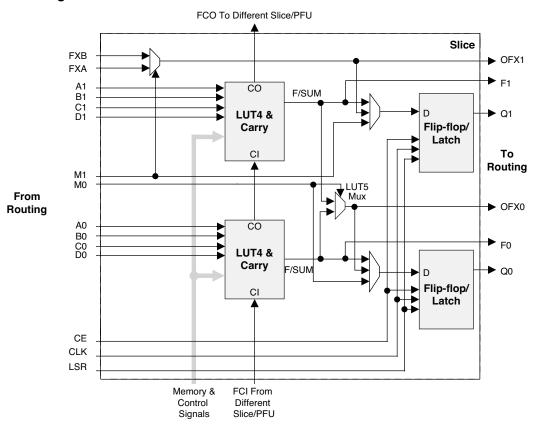

| Slices                                               |      |

| Modes of Operation                                   |      |

| RAM Mode                                             |      |

| ROM Mode                                             |      |

| Routing                                              |      |

| Clock/Control Distribution Network                   |      |

| sysCLOCK Phase Locked Loops (PLLs)                   |      |

| sysMEM Embedded Block RAM Memory                     |      |

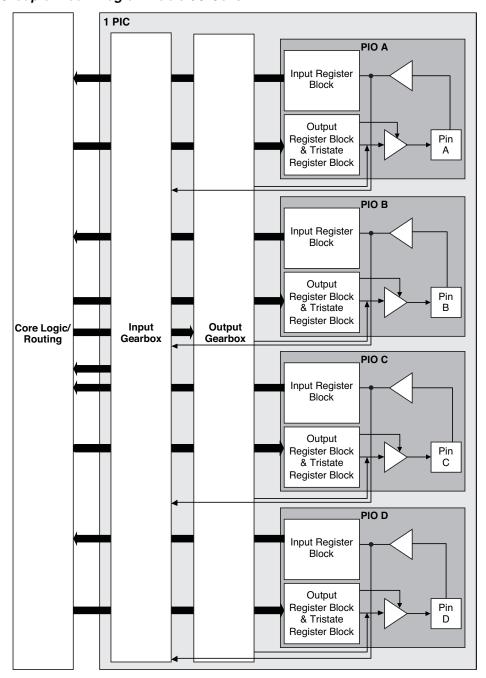

| Programmable I/O Cells (PIC)                         |      |

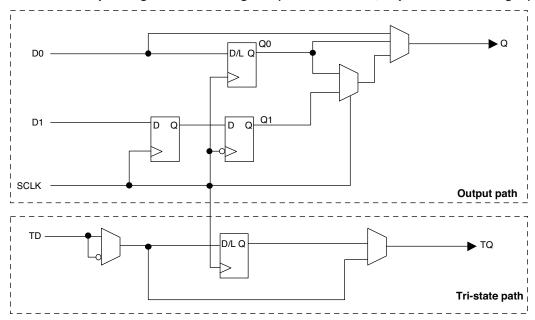

| PIO                                                  |      |

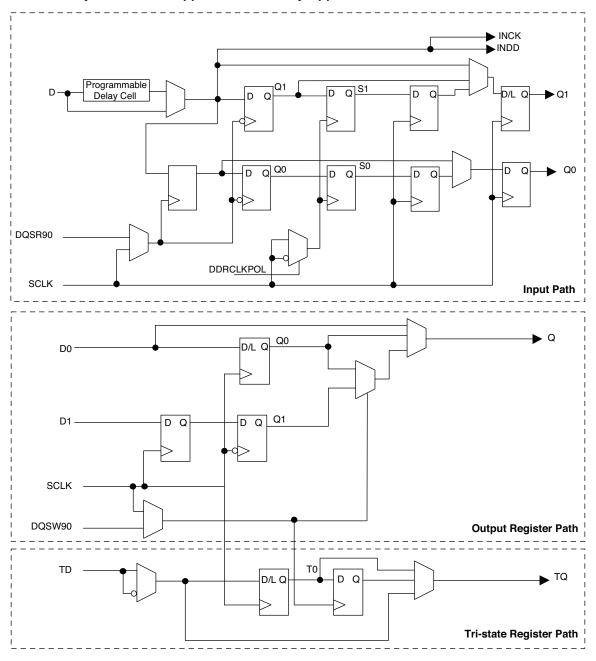

| Input Register Block                                 |      |

| Output Register Block                                |      |

| Tri-state Register Block                             |      |

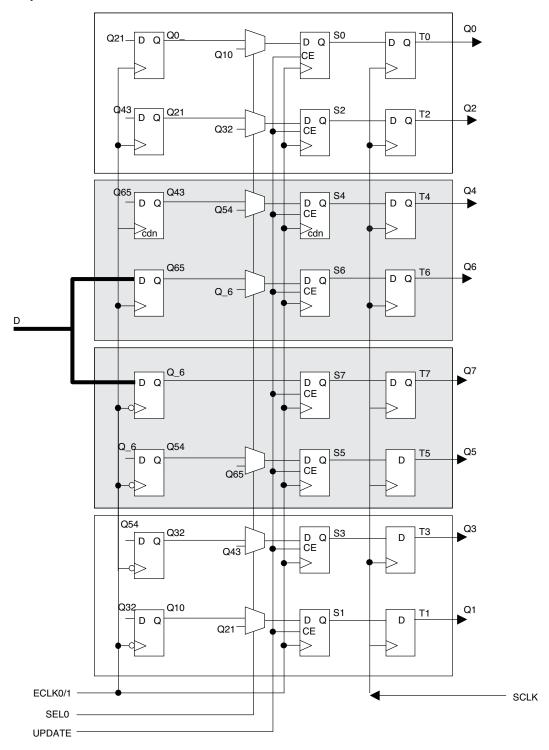

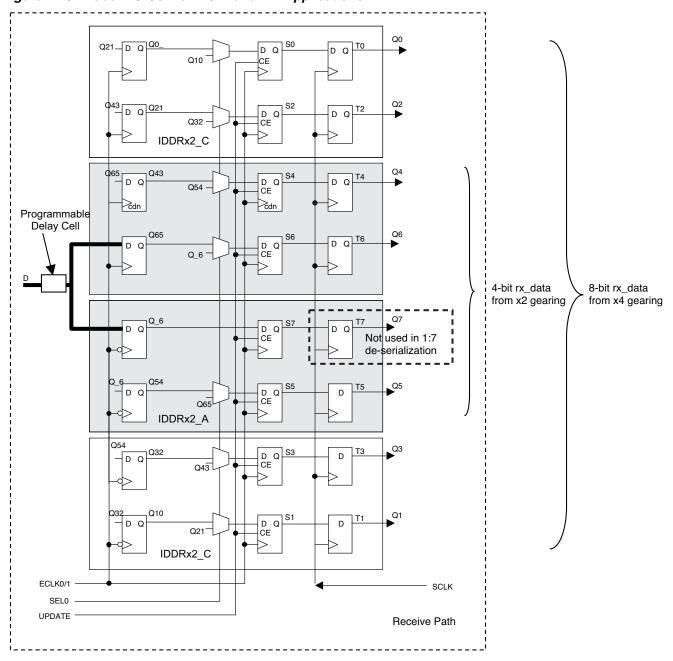

| Input Gearbox                                        |      |

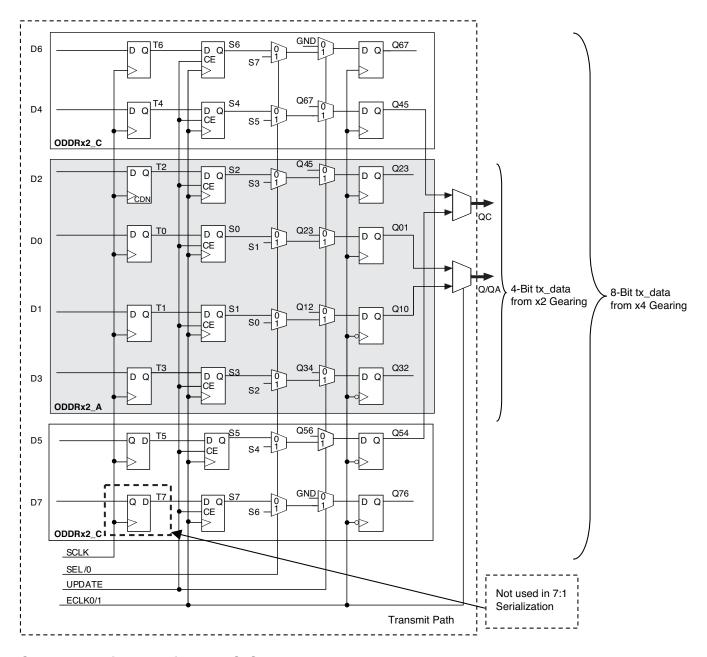

| Output Gearbox                                       |      |

| DDR Memory Support                                   |      |

| DQS Read Write Block                                 |      |

| sysIO Buffer                                         |      |

| Typical I/O Behavior During Power-up                 |      |

| Supported Standards                                  |      |

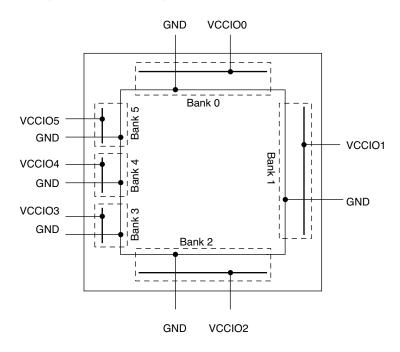

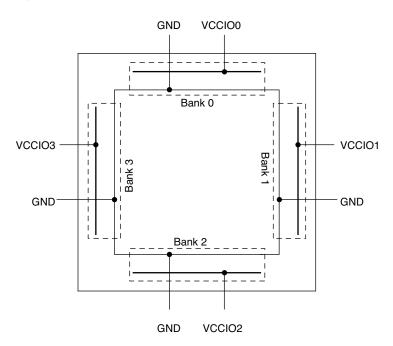

| sysIO Buffer Banks                                   |      |

| Hot Socketing                                        |      |

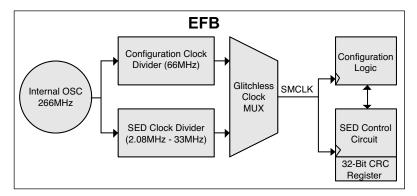

| On-chip Oscillator                                   |      |

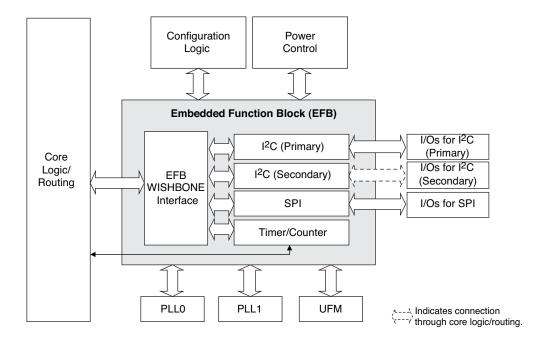

| Embedded Hardened IP Functions and User Flash Memory |      |

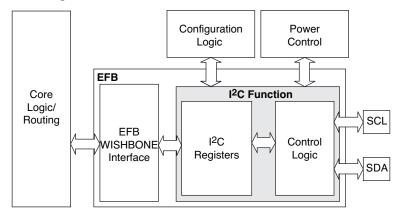

| Hardened I2C IP Core                                 |      |

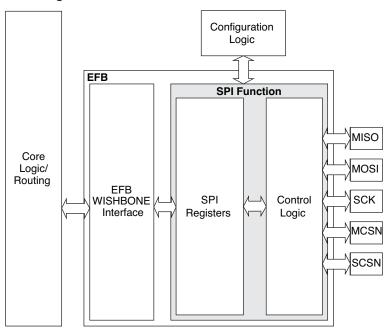

| Hardened SPI IP Core                                 |      |

| Hardened Timer/Counter                               |      |

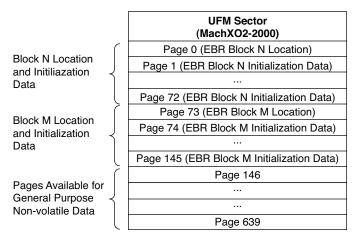

| User Flash Memory (UFM)                              |      |

| Standby Mode and Power Saving Options                |      |

| Power On Reset                                       |      |

| Configuration and Testing                            |      |

| IEEE 1149.1-Compliant Boundary Scan Testability      |      |

| Device Configuration                                 |      |

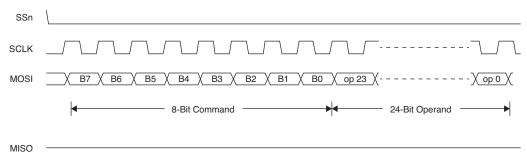

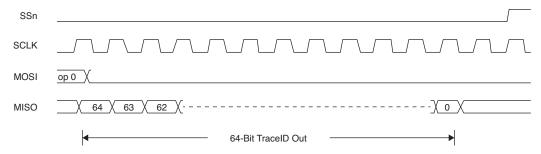

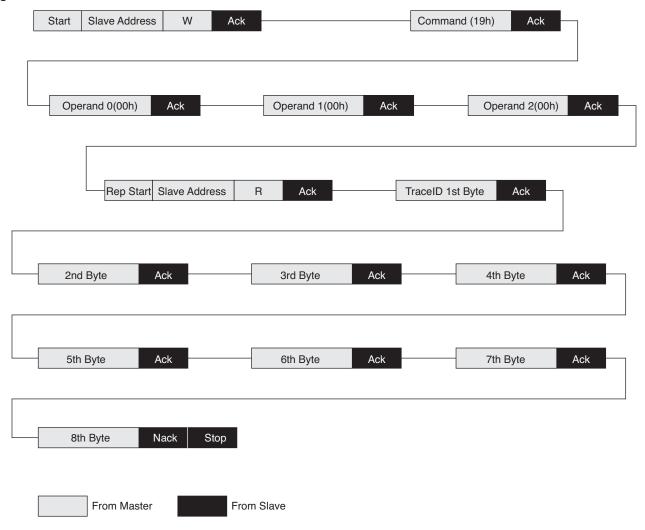

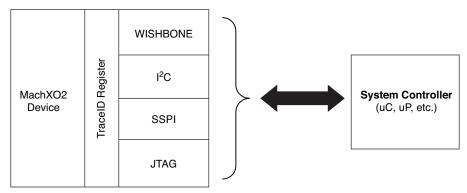

| TraceID                                              |      |

| Density Shifting                                     |      |

| DC and Switching Characteristics                     | 2 00 |

| Absolute Maximum Ratings                             | 3-1  |

| Recommended Operating Conditions                     |      |

| Power Supply Ramp Rates                              |      |

| Power-On-Reset Voltage Levels                        |      |

| Programming/Erase Specifications                     |      |

|                                                      | 0 2  |

© 2013 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Hot Socketing Specifications                                               |      |

|----------------------------------------------------------------------------|------|

| ESD Performance                                                            |      |

| DC Electrical Characteristics                                              |      |

| Static Supply Current – ZE Devices                                         |      |

| Static Power Consumption Contribution of Different Components – ZE Devices |      |

| Static Supply Current – HC/HE Devices                                      |      |

| Programming and Erase Flash Supply Current – ZE Devices                    |      |

| Programming and Erase Flash Supply Current – HC/HE Devices                 |      |

| sysIO Recommended Operating Conditions                                     |      |

| sysIO Single-Ended DC Electrical Characteristics                           |      |

| sysIO Differential Electrical Characteristics                              |      |

| LVDS                                                                       |      |

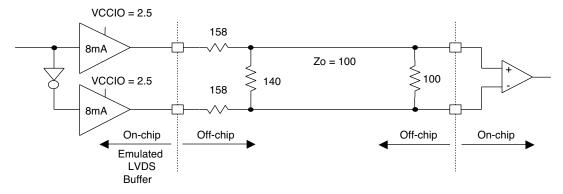

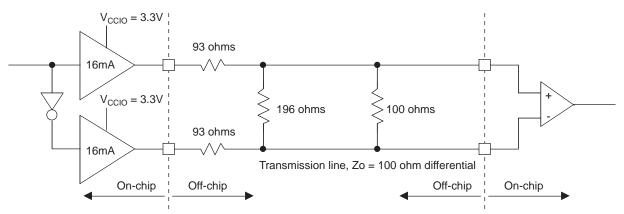

| LVDS Emulation                                                             |      |

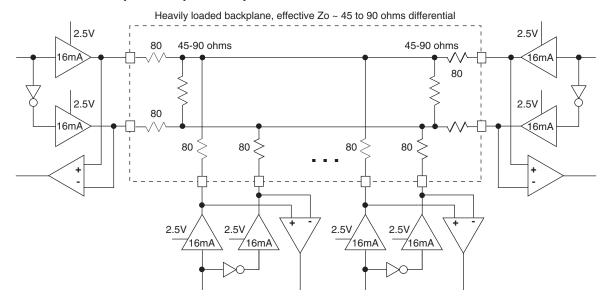

| BLVDS                                                                      |      |

| LVPECL                                                                     |      |

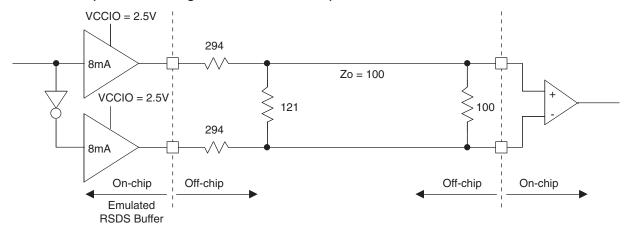

| RSDS                                                                       |      |

| Typical Building Block Function Performance – HC/HE Devices                |      |

| Pin-to-Pin Performance (LVCMOS25 12mA Drive)                               |      |

| Register-to-Register Performance                                           |      |

| Typical Building Block Function Performance – ZE Devices                   |      |

| Pin-to-Pin Performance (LVCMOS25 12mA Drive)                               |      |

| Register-to-Register Performance                                           | 3-15 |

| Derating Logic Timing                                                      |      |

| Maximum sysIO Buffer Performance                                           |      |

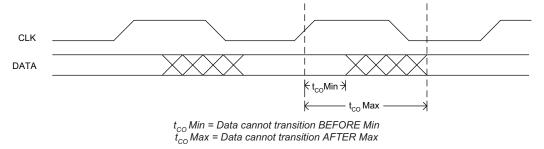

| MachXO2 External Switching Characteristics – HC/HE Devices                 |      |

| MachXO2 External Switching Characteristics – ZE Devices                    |      |

| sysCLOCK PLL Timing                                                        |      |

| MachXO2 Oscillator Output Frequency                                        |      |

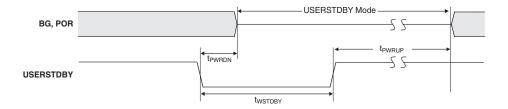

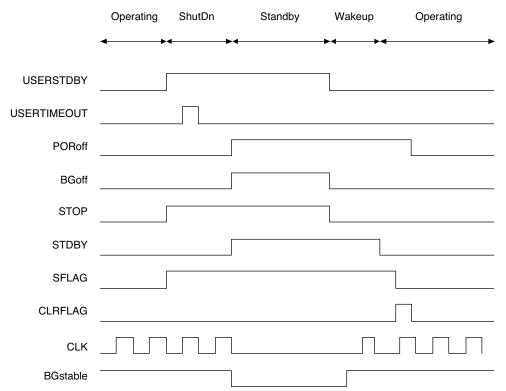

| MachXO2 Standby Mode Timing – ZE Devices                                   |      |

| MachXO2 Standby Mode Timing – HC/HE Devices                                |      |

| Flash Download Time                                                        |      |

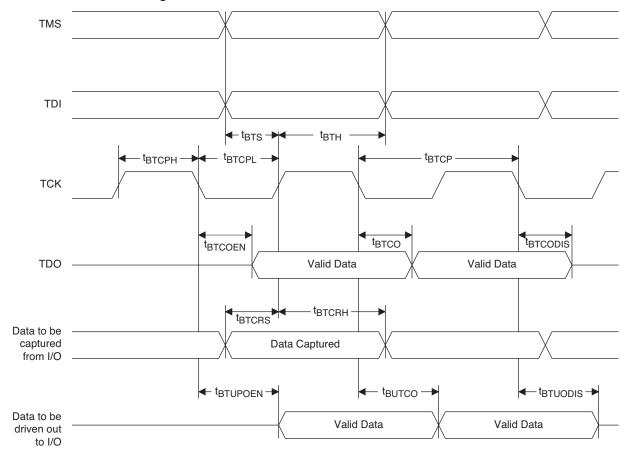

| JTAG Port Timing Specifications                                            |      |

| sysCONFIG Port Timing Specifications                                       |      |

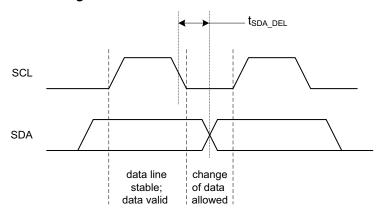

| I2C Port Timing Specifications                                             | 3-36 |

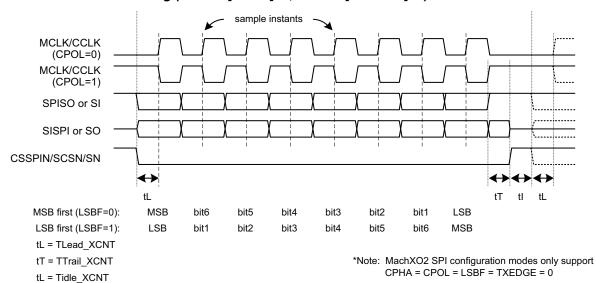

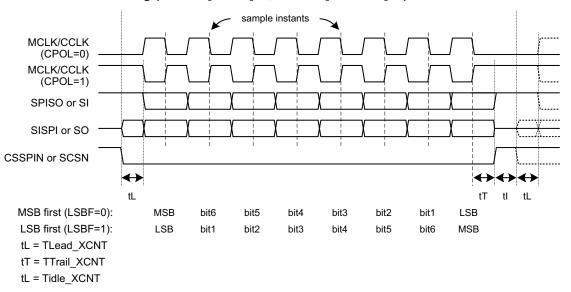

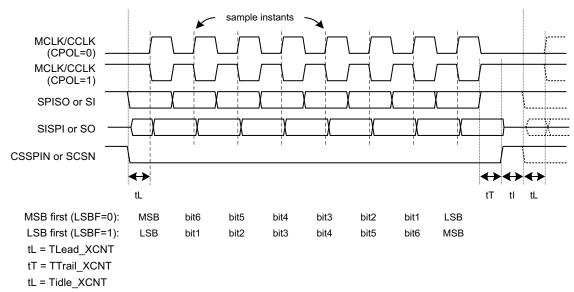

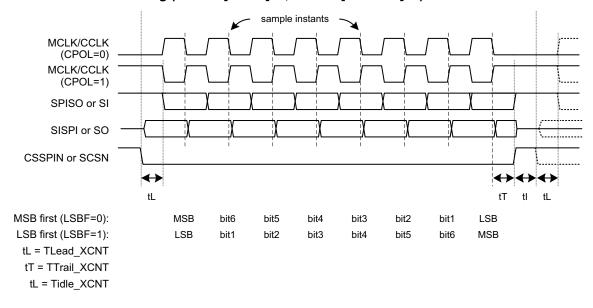

| SPI Port Timing Specifications                                             | 3-36 |

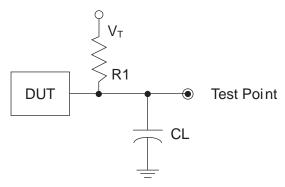

| Switching Test Conditions                                                  | 3-37 |

| Pinout Information                                                         |      |

| Signal Descriptions                                                        | 4-1  |

| Pin Information Summary                                                    | 4-3  |

| For Further Information                                                    | 4-8  |

| Thermal Management                                                         | 4-8  |

| For Further Information                                                    | 4-8  |

| Ordering Information                                                       |      |

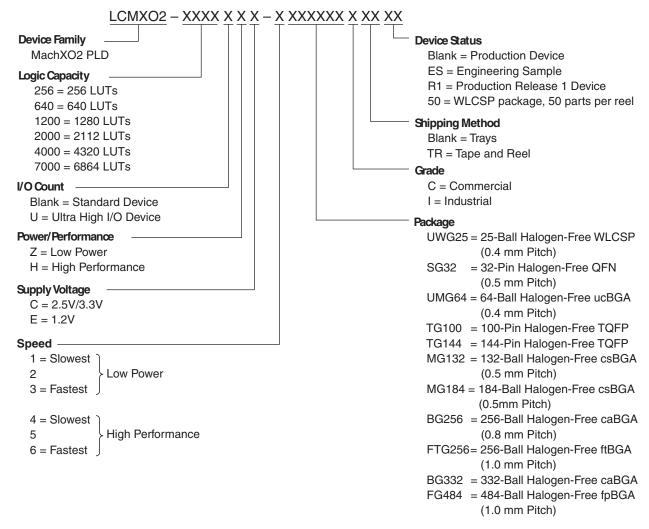

| MachXO2 Part Number Description                                            | 5-1  |

| Ordering Information                                                       | 5-1  |

| Ultra Low Power Commercial Grade Devices, Halogen Free (RoHS) Packaging    | 5-2  |

| High-Performance Commercial Grade Devices with Voltage Regulator,          |      |

| Halogen Free (RoHS) Packaging                                              | 5-4  |

| High-Performance Commercial Grade Devices without Voltage Regulator,       |      |

| Halogen Free (RoHS) Packaging                                              | 5-8  |

| Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging    |      |

| High-Performance Industrial Grade Devices with Voltage Regulator,          | 5 6  |

| Halogen Free (RoHS) Packaging                                              | 5-13 |

| · · · · · · · · · · · · · · · · · · ·                                      |      |

| High Performance Industrial Grade Devices Without Voltage Regulator,     |      |

|--------------------------------------------------------------------------|------|

| Halogen Free (RoHS) Packaging                                            |      |

| R1 Device Specifications                                                 | 5-18 |

| Supplemental Information For Further Information                         | 0.4  |

| Revision History                                                         | 0-1  |

| nevision history                                                         |      |

| Section II. MachXO2 Family Technical Notes                               |      |

| Power Estimation and Management for MachXO2 Devices                      |      |

| Introduction                                                             | 8-1  |

| Power Modes                                                              |      |

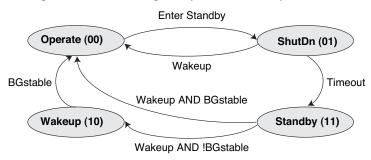

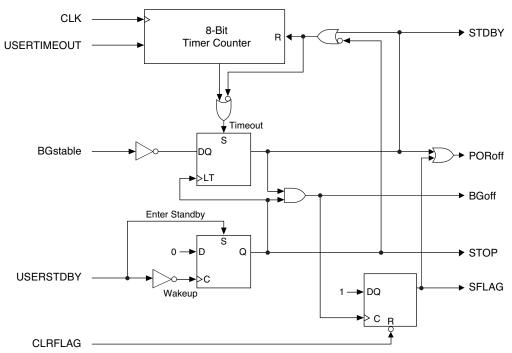

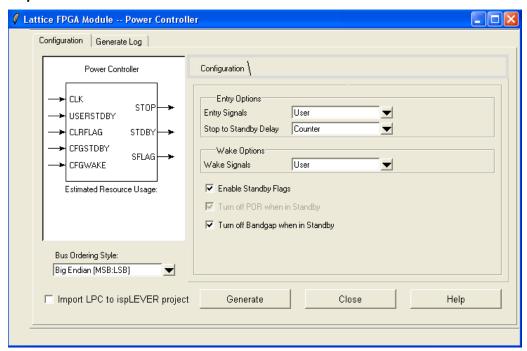

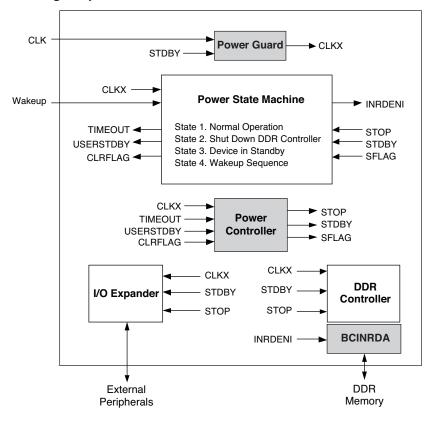

| Power Controller                                                         | 8-2  |

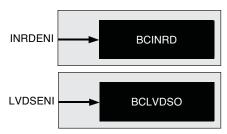

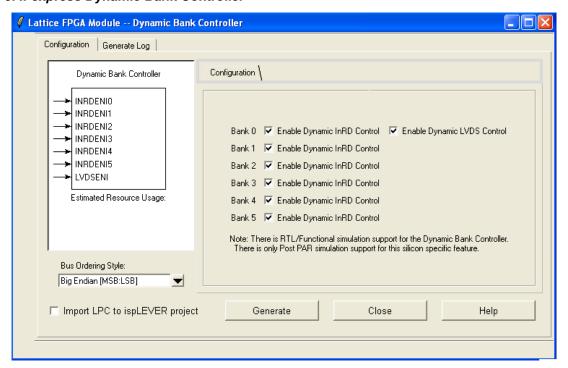

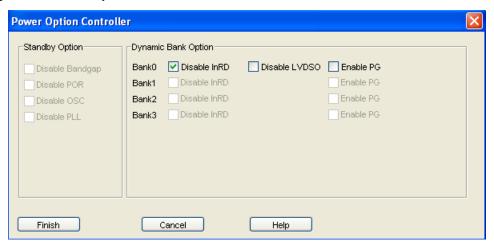

| Bank Controller                                                          | 8-5  |

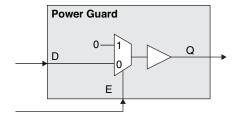

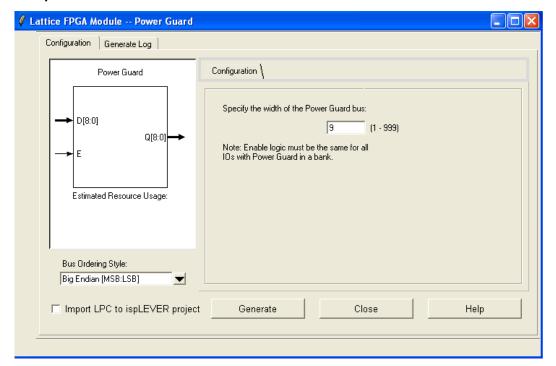

| Power Guard                                                              |      |

| Low Power Design Implementation                                          |      |

| Power Supply Sequencing and Hot Socketing                                |      |

| Recommended Power-up Sequence                                            |      |

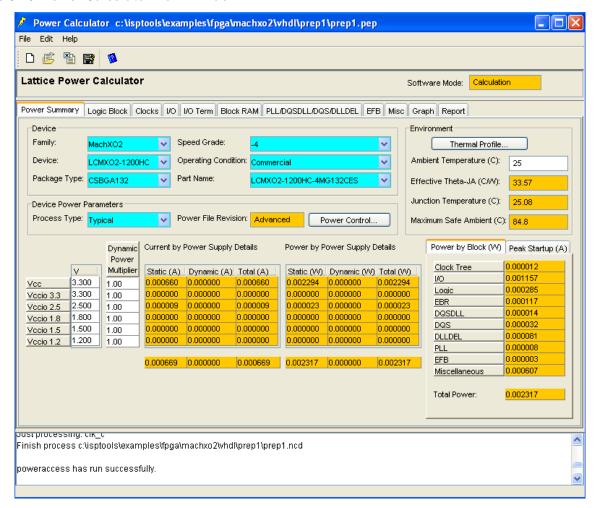

| Power Calculator                                                         |      |

| Power Calculator Hardware Assumptions                                    | 8-9  |

| Power Calculator and Power Equations                                     | 8-9  |

| Typical and Worst Case Process Power/ICC                                 |      |

| Junction Temperature                                                     |      |

| Maximum Safe Ambient Temperature                                         |      |

| Operating Temperature Range                                              |      |

| Dynamic Power Multiplier (DPM)                                           | 8-11 |

| Power Budgeting                                                          |      |

| Dynamic Power Savings                                                    | 8-12 |

| Activity Factor Calculation                                              | 8-12 |

| Thermal Impedance and Airflow                                            | 8-13 |

| Reducing Power Consumption                                               | 8-13 |

| Power Calculator Assumptions                                             | 8-14 |

| Technical Support Assistance                                             | 8-15 |

| Revision History                                                         | 8-15 |

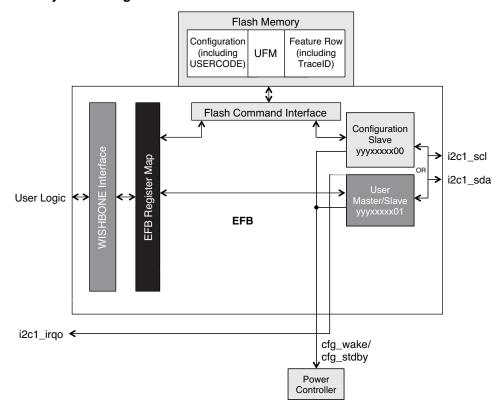

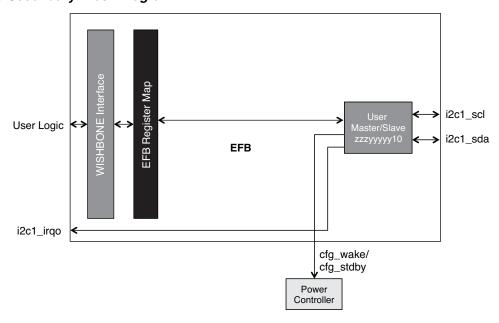

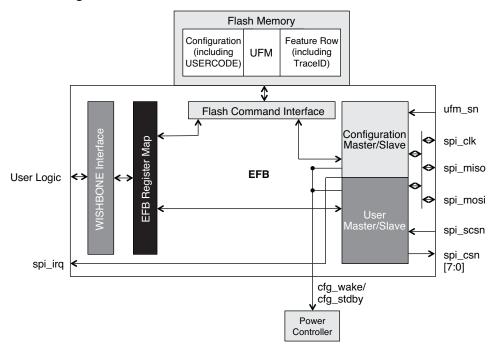

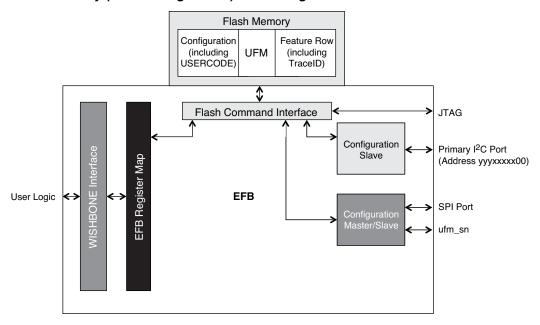

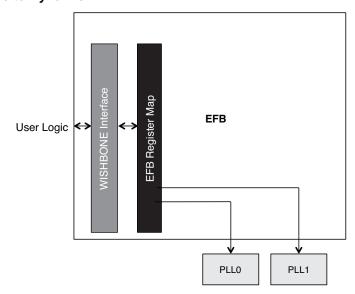

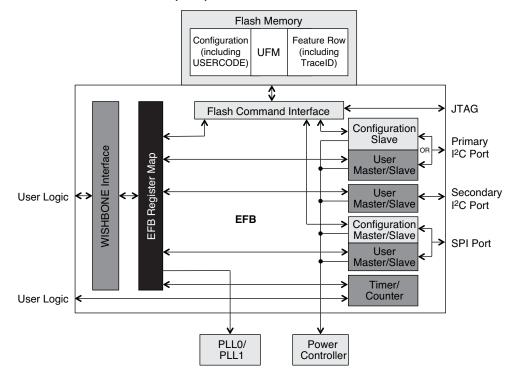

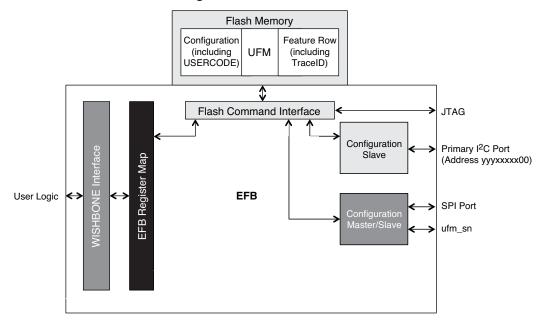

| Using User Flash Memory and Hardened Control Functions in MachXO2 Device | ces  |

| Introduction                                                             | 9-1  |

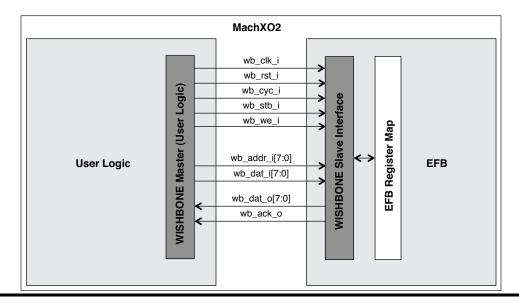

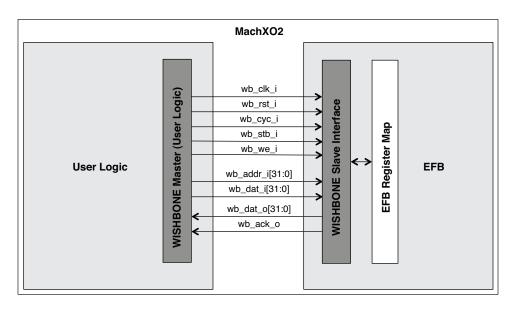

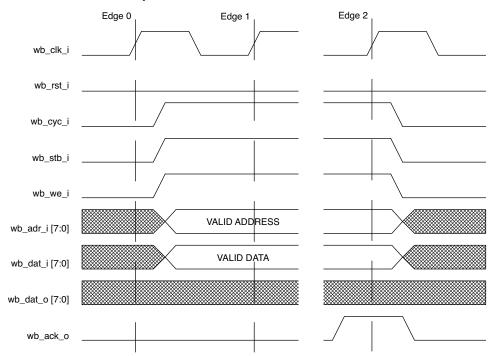

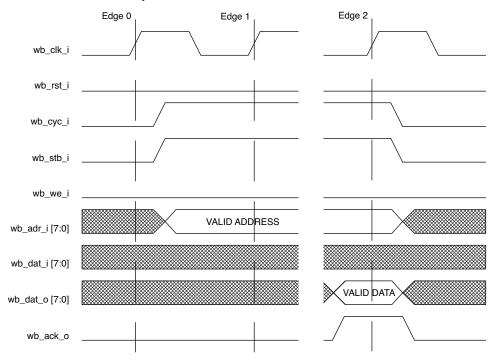

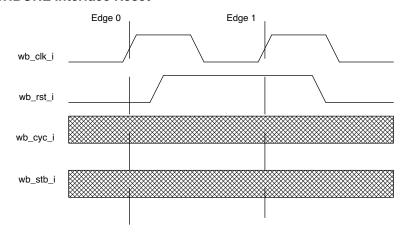

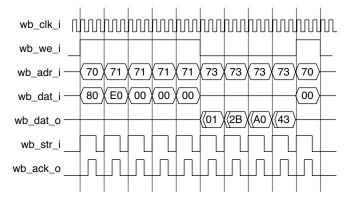

| WISHBONE Bus Interface                                                   |      |

| WISHBONE Protocol                                                        |      |

| WISHBONE Design Tips                                                     |      |

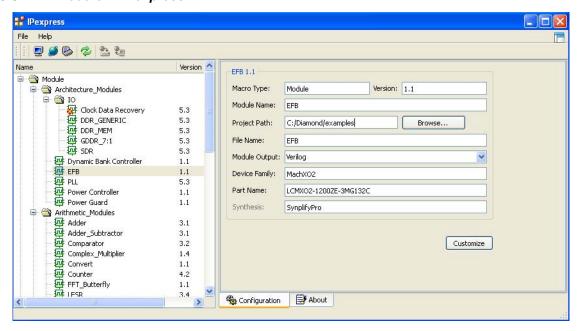

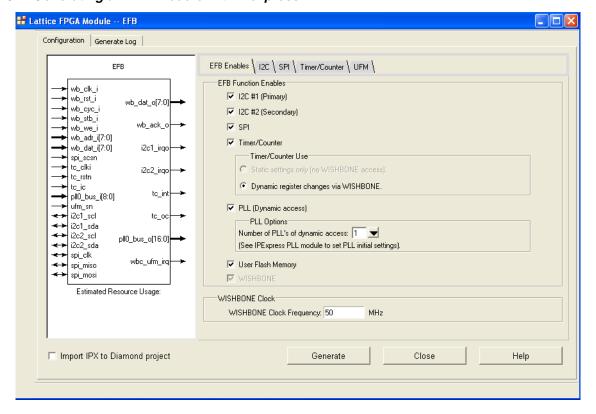

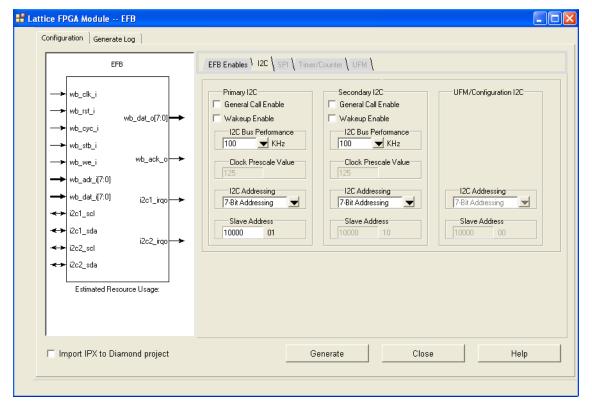

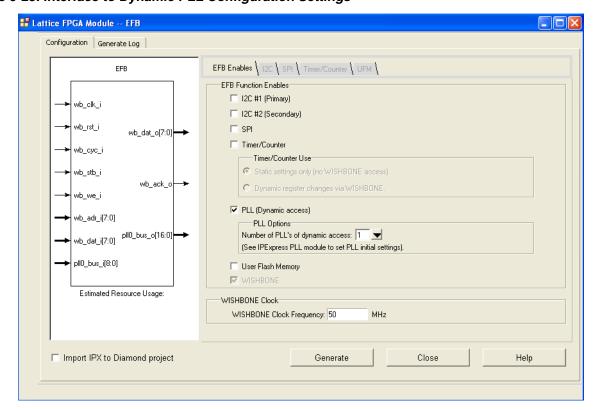

| Generating an EFB Module with IPexpress                                  |      |

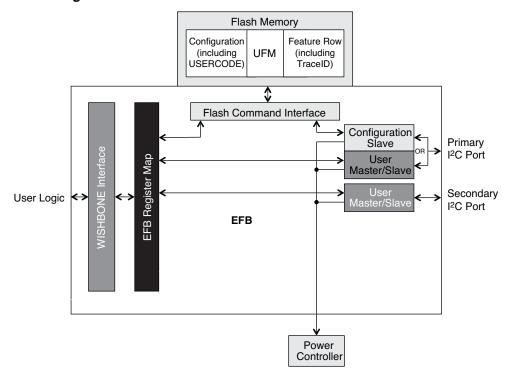

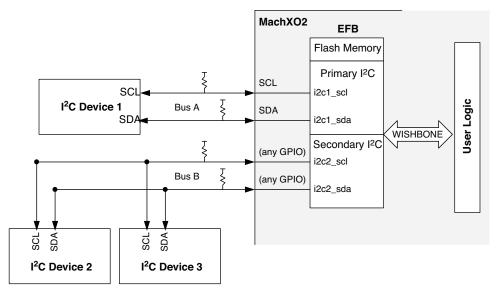

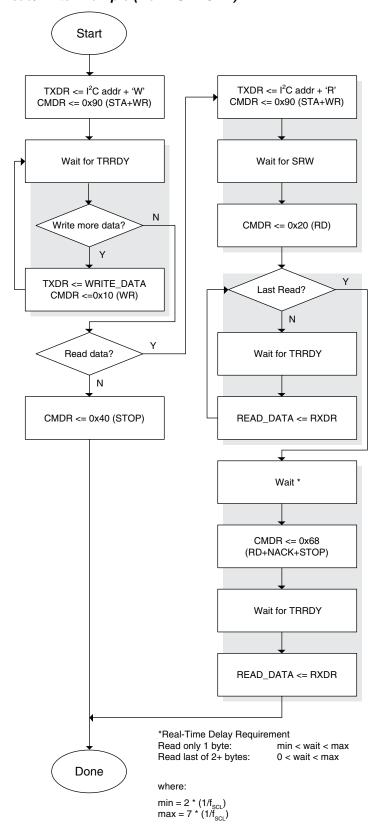

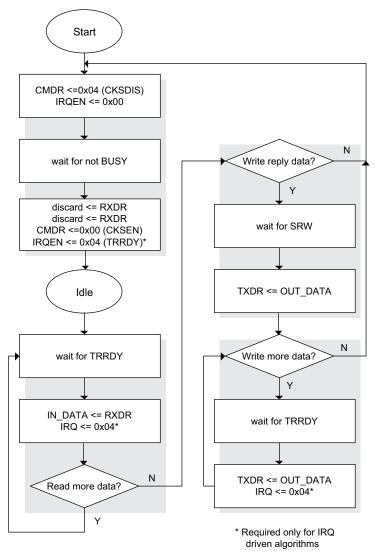

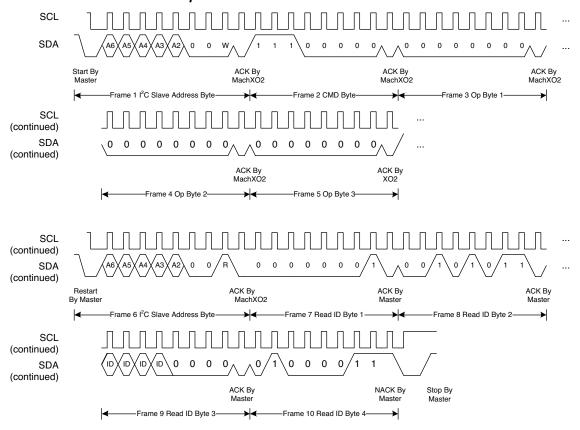

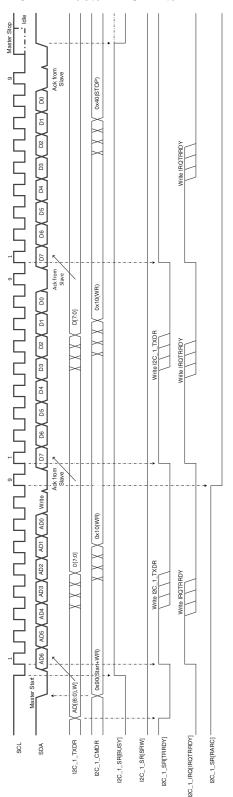

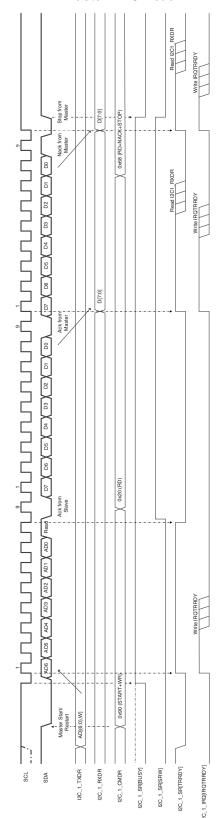

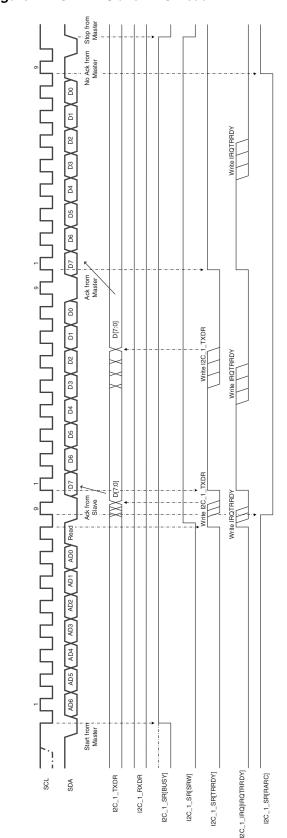

| Hardened I2C IP Cores                                                    | 9-6  |

| Primary I2C                                                              |      |

| Secondary I2C                                                            |      |

| Configuring I2C Cores with IPexpress                                     |      |

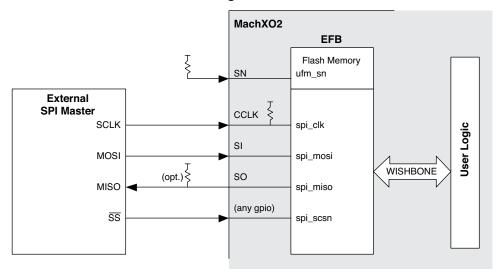

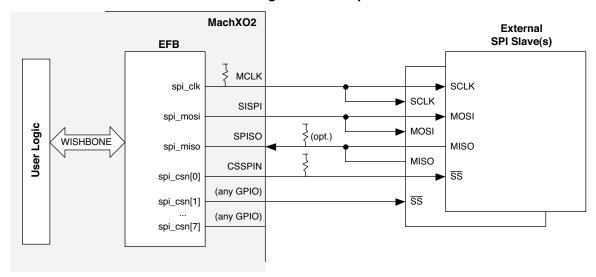

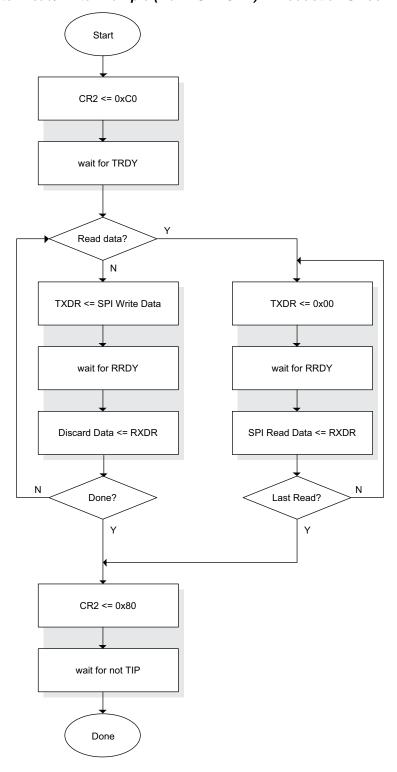

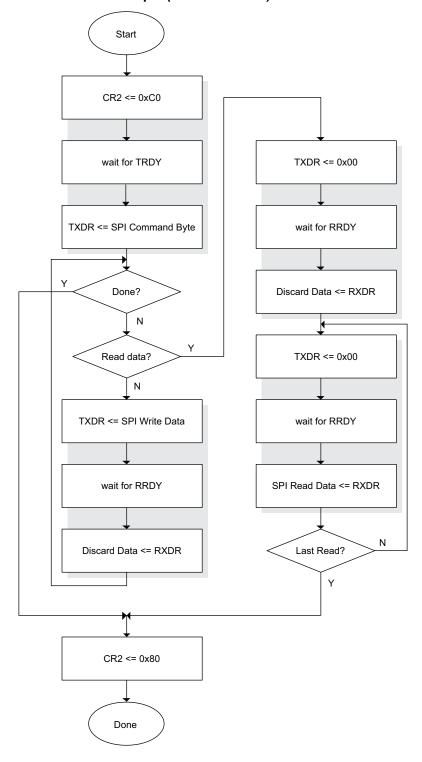

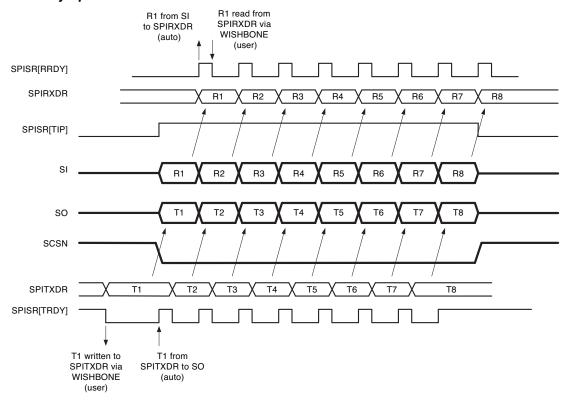

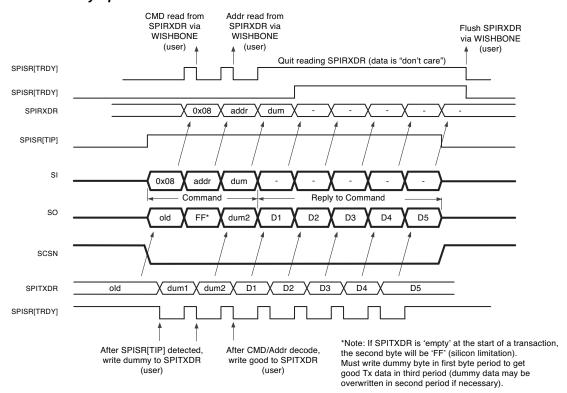

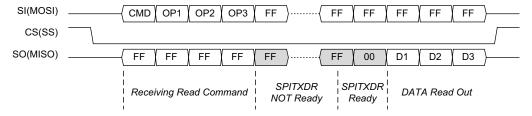

| Hardened SPI IP Core                                                     |      |

| SPI Interface Signals                                                    |      |

| Configuring the SPI Core with IPexpress                                  |      |

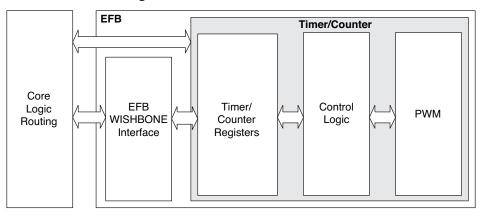

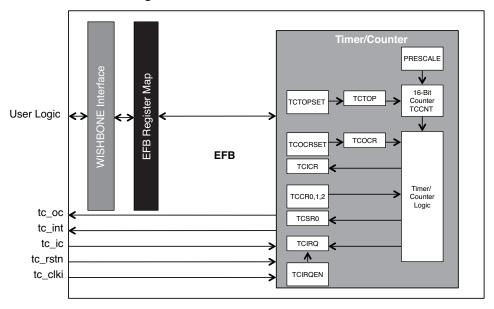

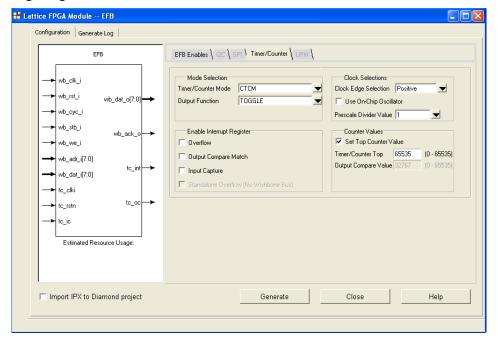

| Timer/Counter                                                            |      |

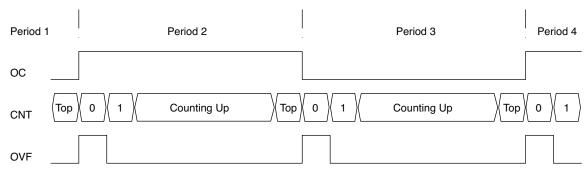

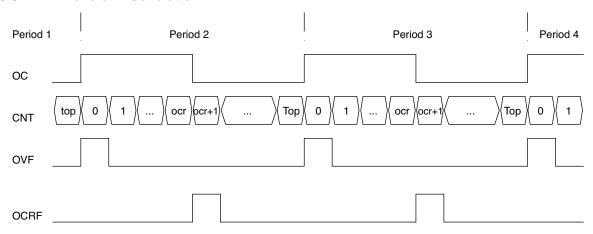

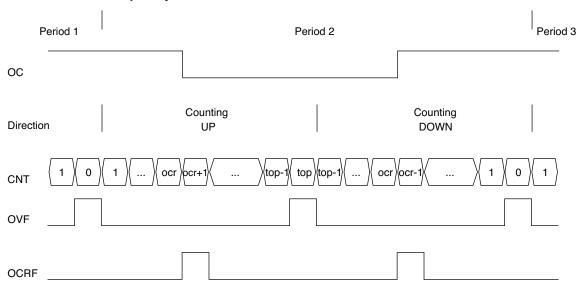

| Timer/Counter Modes of Operation                                         |      |

| Timer/Counter IP Signals                                                 |      |

| Configuring the Timer/Counter                                            |      |

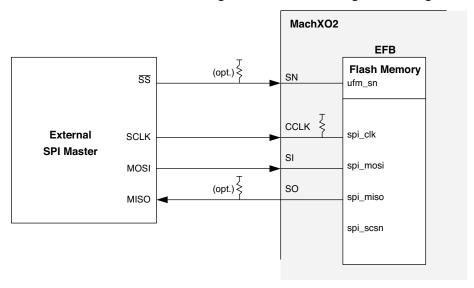

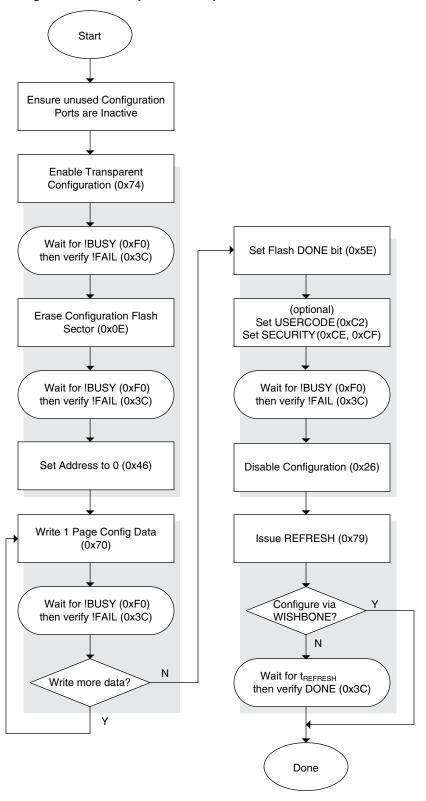

| Flash Memory (UFM/Configuration) Access                                  |      |

| Flash Memory (UFM/Configuration) Access Ports                            |      |

| Interface to UFM                                                         |      |

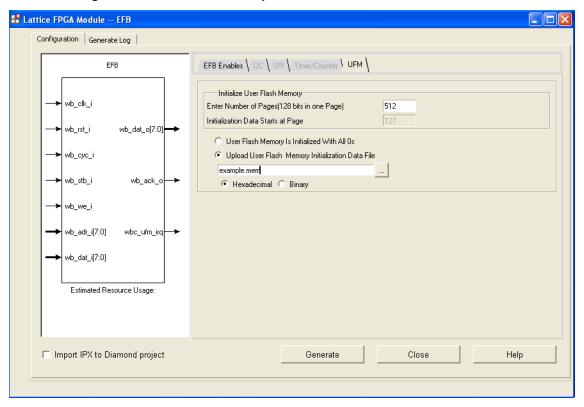

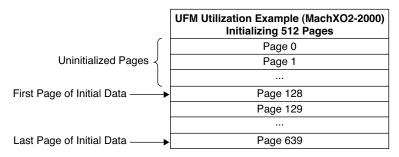

| Initializing the UFM with IPexpress                                      | 9-31 |

| Configuration Flash Memory                                      | 9-33  |

|-----------------------------------------------------------------|-------|

| Interface to Dynamic PLL Configuration Settings                 |       |

| Technical Support Assistance                                    |       |

| Revision History                                                | 9-37  |

| MachXO2 sysIO Usage Guide                                       |       |

| Introduction                                                    | 10-1  |

| sysIO Buffer Overview                                           | 10-1  |

| Supported sysIO Standards                                       | 10-2  |

| sysIO Banking Scheme                                            | 10-3  |

| sysIO Standards Supported by I/O Banks                          | 10-5  |

| Power Supply Requirements                                       | 10-6  |

| VCCIO Requirement for I/O Standards                             | 10-6  |

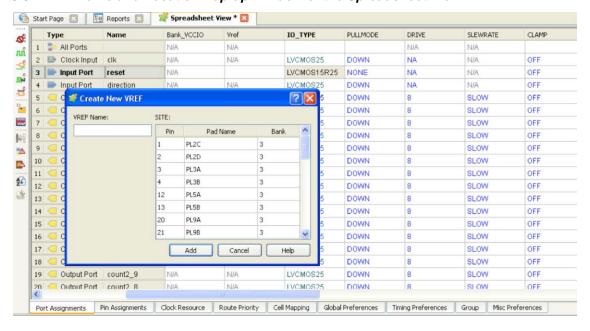

| Input Reference Voltage                                         | 10-8  |

| sysIO Buffer Configuration                                      | 10-9  |

| LVCMOS Buffer Configurations                                    | 10-9  |

| Differential Buffer Configurations                              | 10-10 |

| True Differential Output And Output Drive                       | 10-10 |

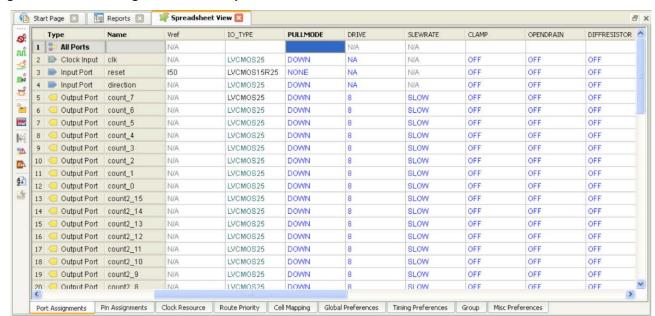

| Software sysIO Attributes                                       | 10-10 |

| HDL Attributes                                                  | 10-10 |

| sysIO Primitives                                                | 10-14 |

| Design Consideration and Usage                                  | 10-15 |

| sysIO Buffer Features Common to All MachXO2 Devices             | 10-15 |

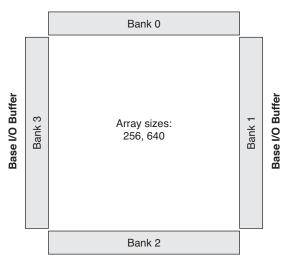

| sysIO Buffer Rules Specific to MachXO2-256 and MachXO2-640      | 10-15 |

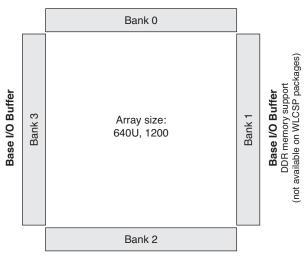

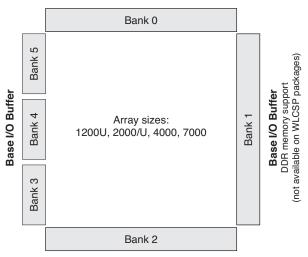

| sysIO Buffer Rules Specific to MachXO2-640U, MachXO2-1200/U,    |       |

| MachXO2-2000/U, MachXO2-4000, and MachXO2-7000                  | 10-15 |

| Technical Support Assistance                                    | 10-16 |

| Revision History                                                | 10-16 |

| Appendix A. sysIO HDL Attributes                                | 10-17 |

| Attributes in VHDL Language                                     | 10-17 |

| PULLMODE                                                        | 10-18 |

| Attributes in Verilog Language                                  |       |

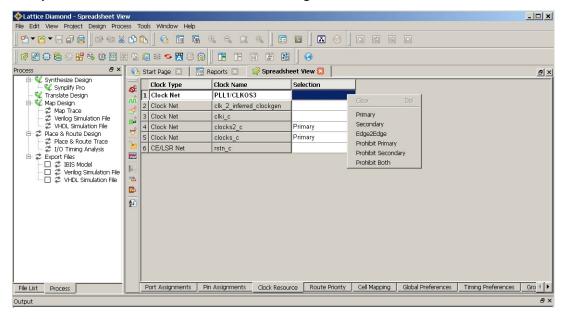

| Appendix B. sysIO Attributes Using the Spreadsheet View         | 10-21 |

| VREF Assignment in the Spreadsheet View                         |       |

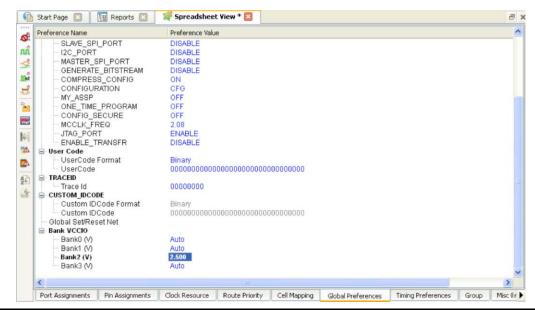

| Bank VCCIO Setting in the Spreadsheet View                      |       |

| Appendix C. sysIO Attributes Using Preference File (ASCII File) | 10-23 |

| Implementing High-Speed Interfaces with MachXO2 Devices         |       |

| Introduction                                                    |       |

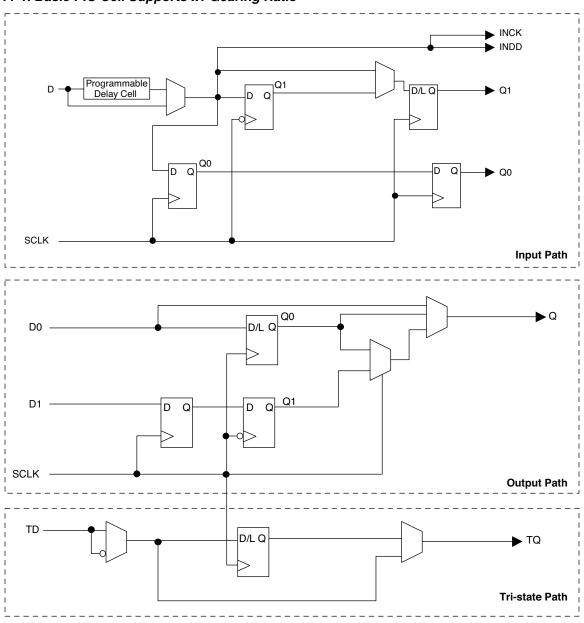

| Architecture for High-Speed Interfaces                          |       |

| Gearing Logic Distribution                                      |       |

| Different Types of I/O Logic Cells                              |       |

| Clock Domain Transfer at PIO Cells                              |       |

| External High-Speed Interface Description                       |       |

| High-Speed Interface Building Blocks                            |       |

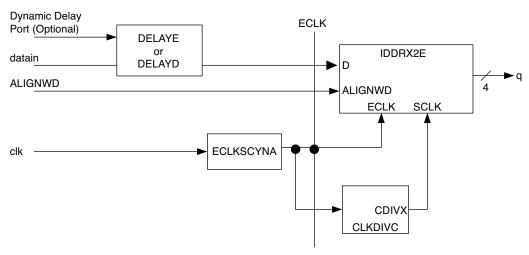

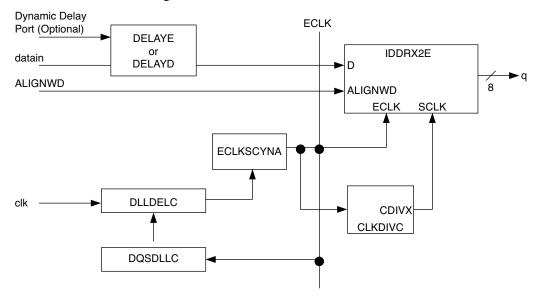

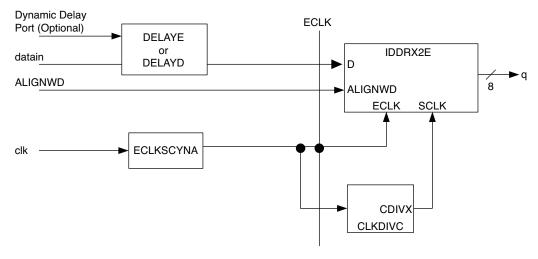

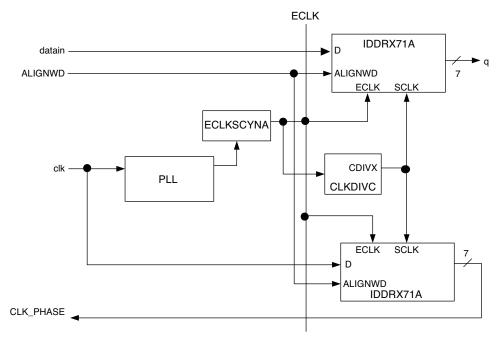

| ECLK                                                            |       |

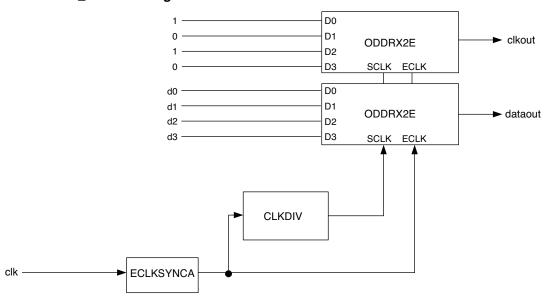

| ECLKSYNC                                                        |       |

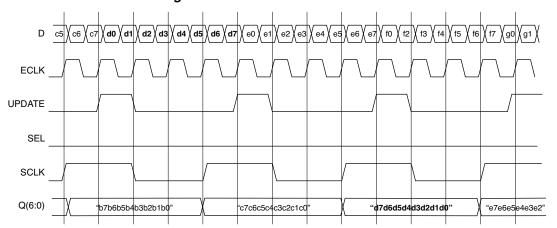

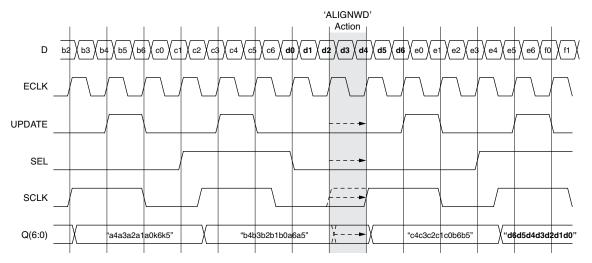

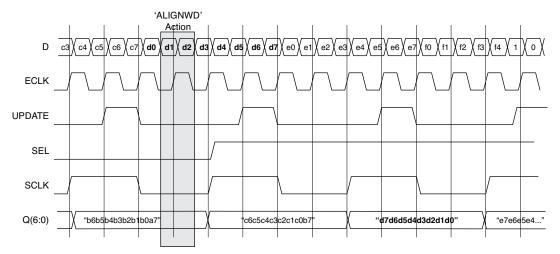

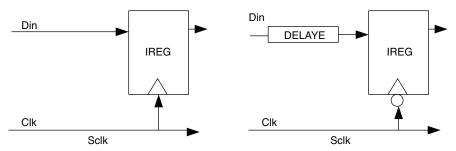

| SCLK                                                            |       |

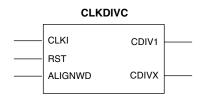

| CLKDIV                                                          |       |

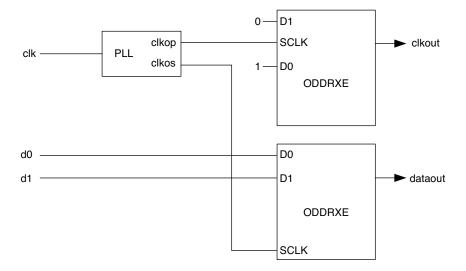

| PLL                                                             |       |

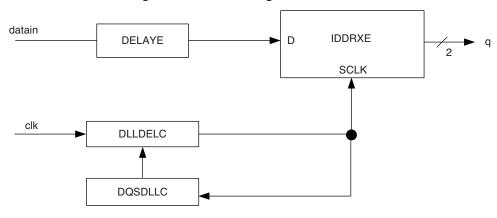

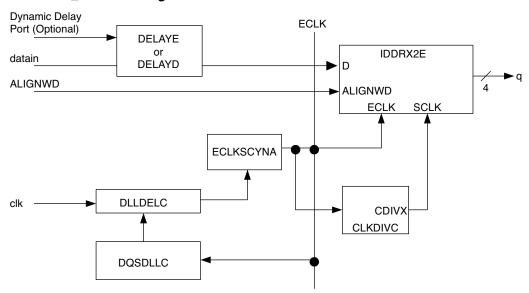

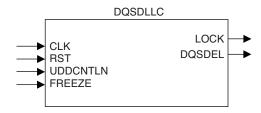

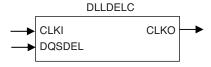

| DQSDLL                                                          |       |

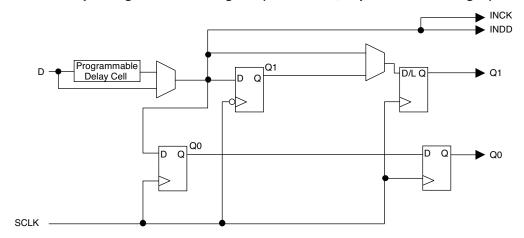

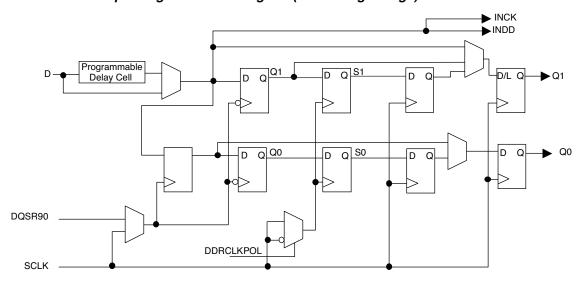

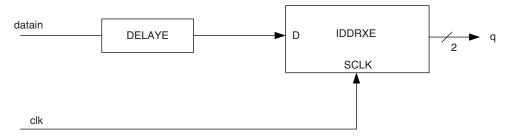

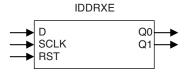

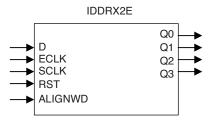

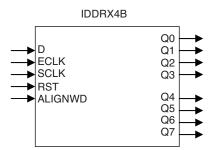

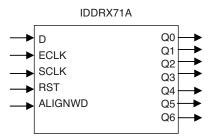

| Input DDR (IDDR)                                                |       |

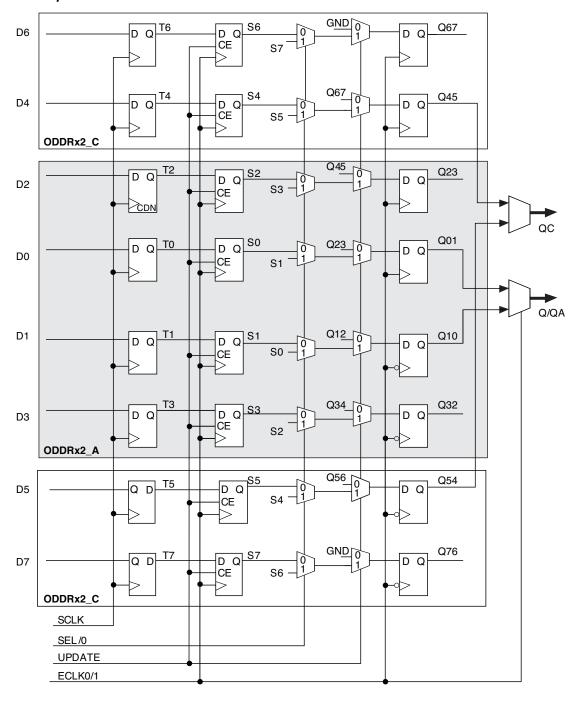

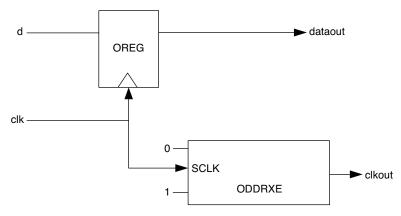

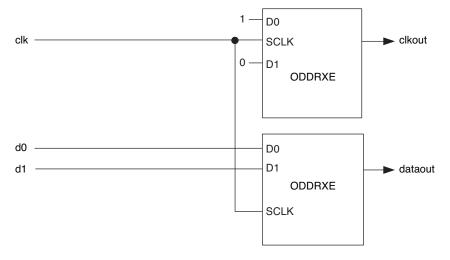

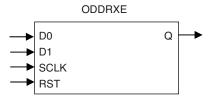

| Output DDR (ODDR)                                               |       |

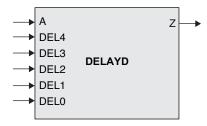

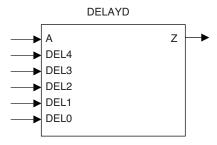

| Delays                                                          |       |

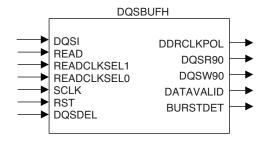

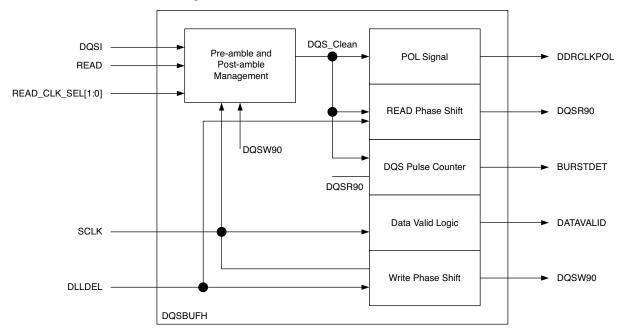

| DQSBUF                                                          |       |

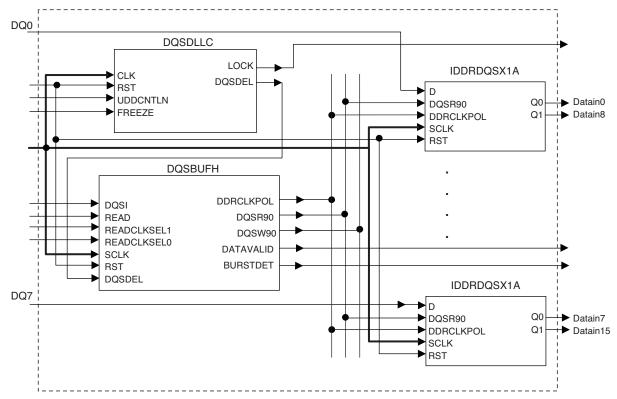

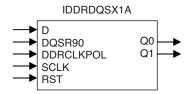

| IDDRDQS                                                         | 11-9  |

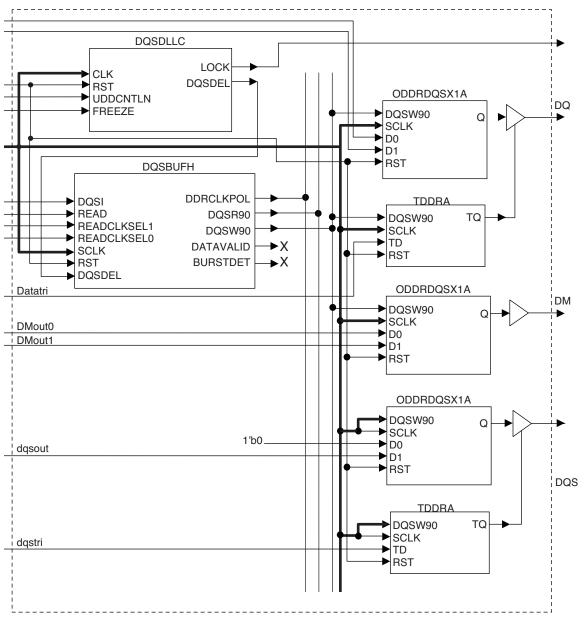

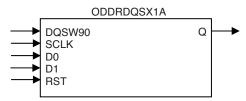

| ODDRDQS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11-10                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

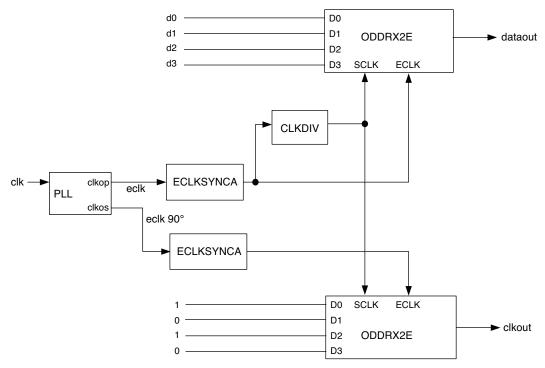

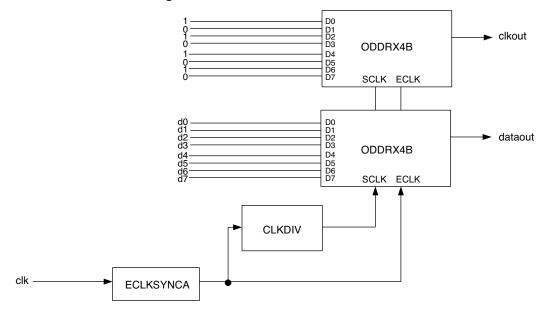

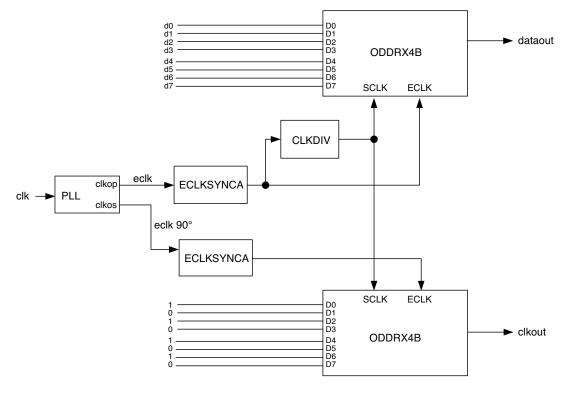

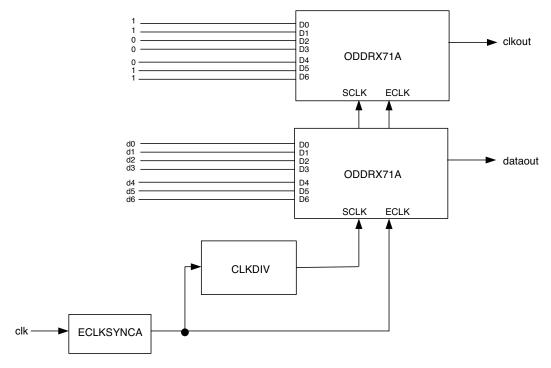

| Generic High-Speed DDR Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

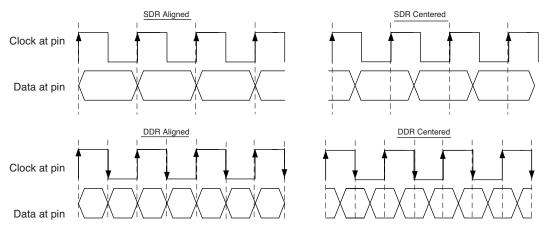

| High-Speed GDDR Interface Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                            |

| High-Speed GDDR Interface Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

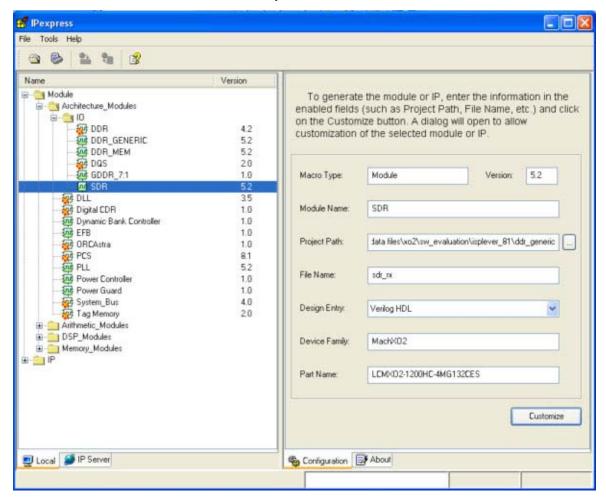

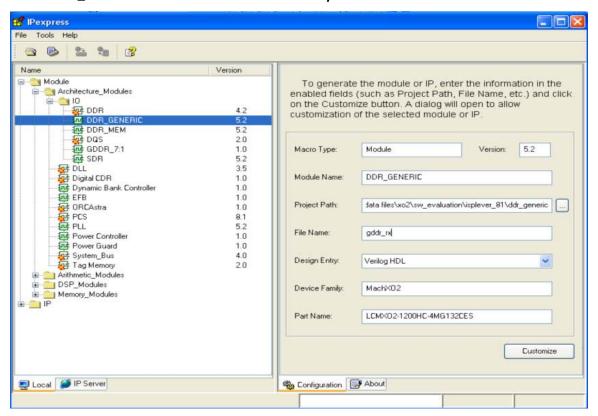

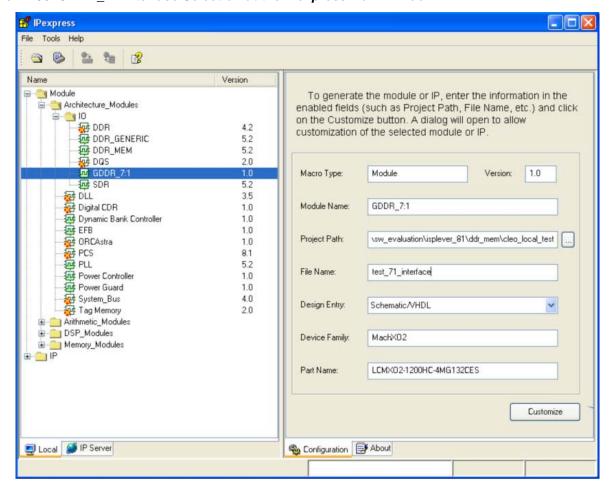

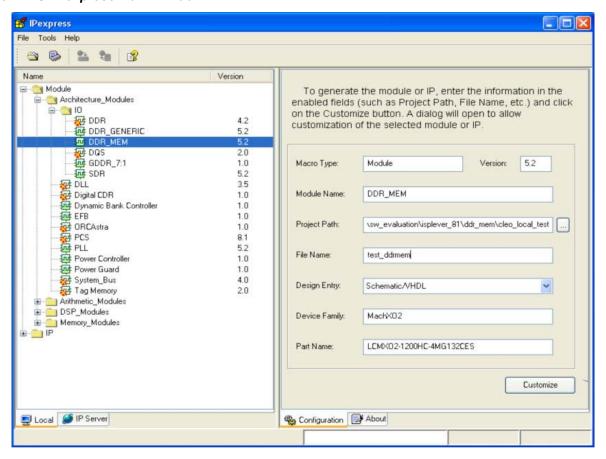

| Using IPexpress to build Generic High-Speed DDR Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                            |

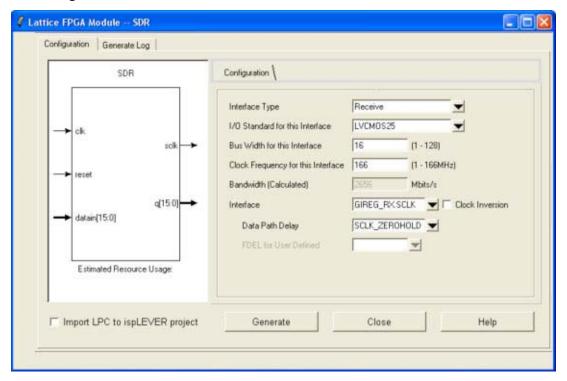

| Building the SDR Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                            |

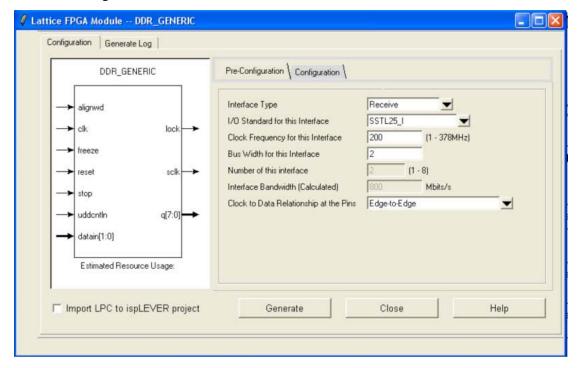

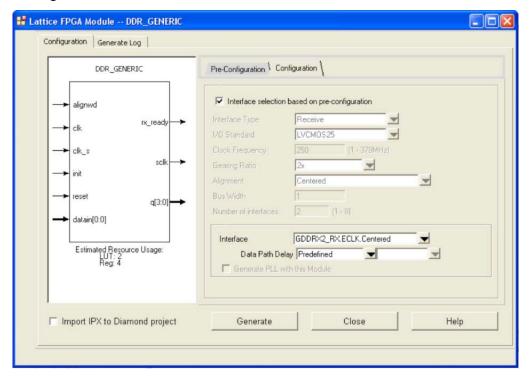

| Building DDR Generic Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                            |

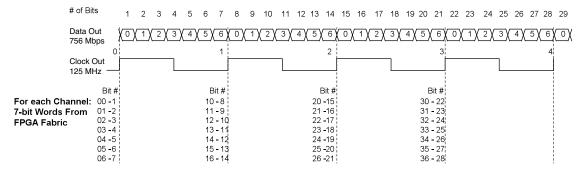

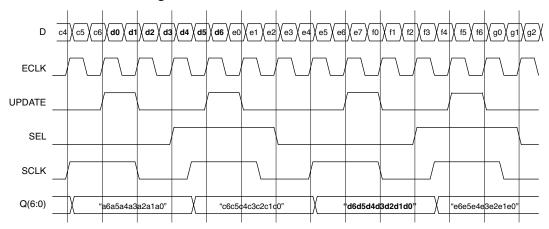

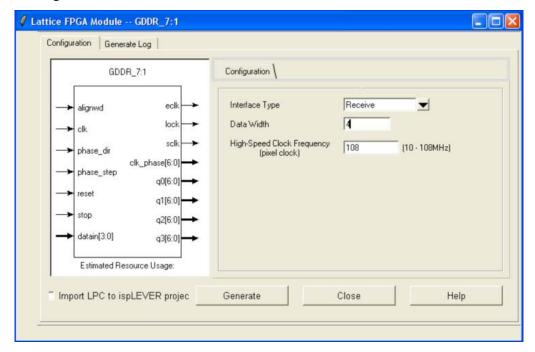

| Building a Generic DDR 7:1 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                            |

| Generic High-Speed DDR Design Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

| I/O Logic Cells and Gearing Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

| High-Speed ECLK Bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                            |

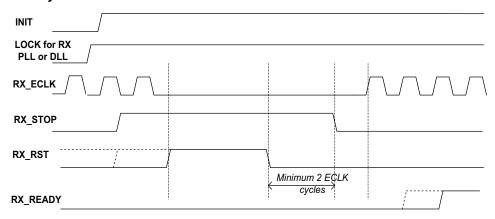

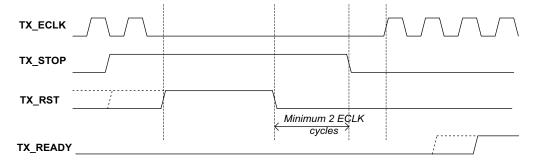

| Reset Synchronization Requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

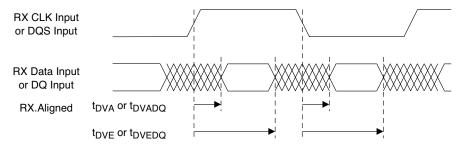

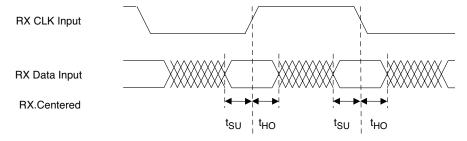

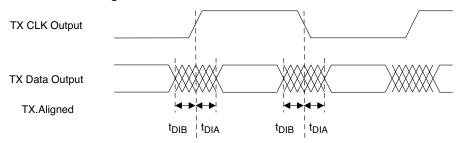

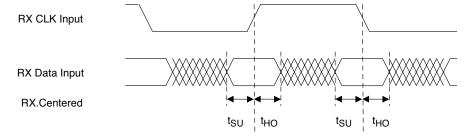

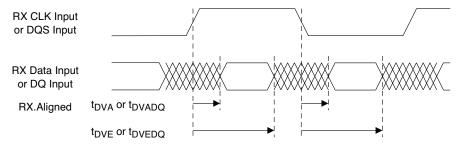

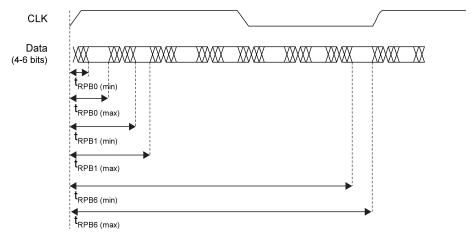

| Timing Analysis for High-Speed GDDR Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                            |

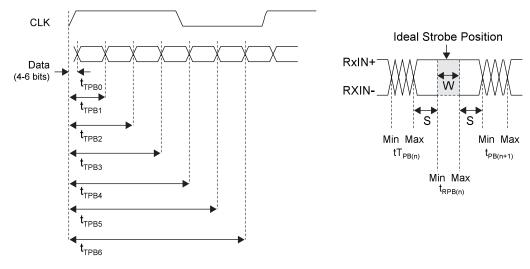

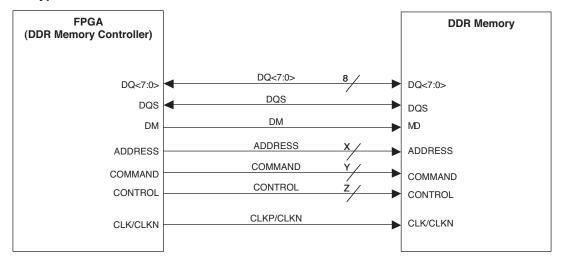

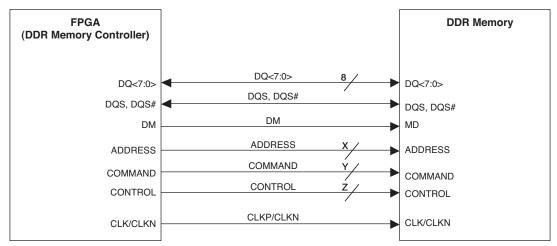

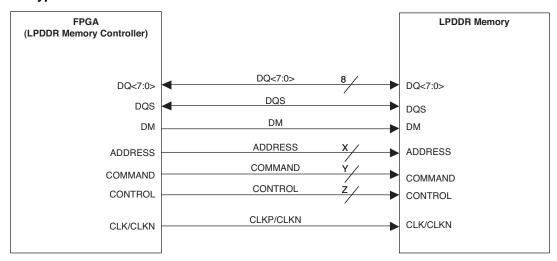

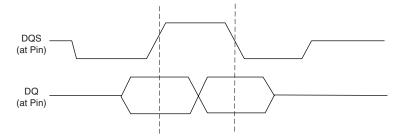

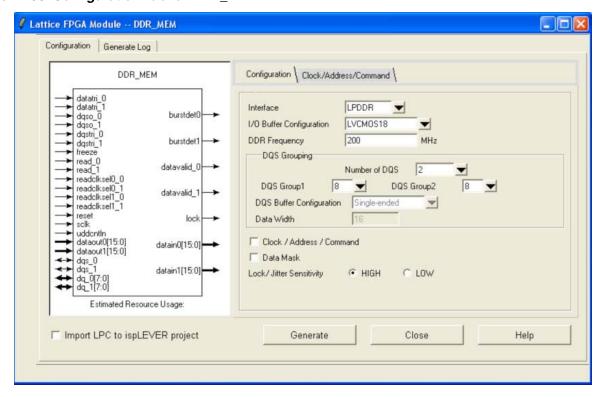

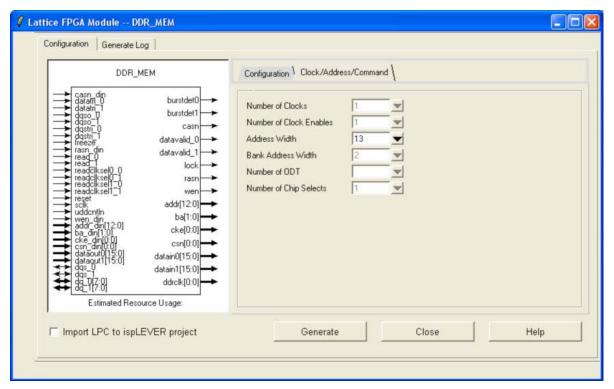

| DDR/DDR2/LPDDR SDRAM Interfaces Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

| DDR/DDR2/LPDDR SDRAM Interfaces Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                            |

| DQS Grouping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                            |

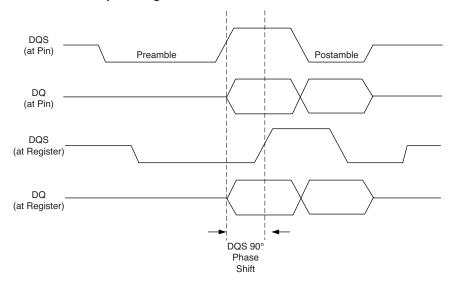

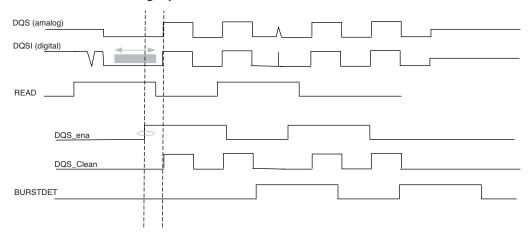

| DQS Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                            |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

| I/O Logic Data Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                            |

| DDR/DDR2/LPDDR Memory READ Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                            |

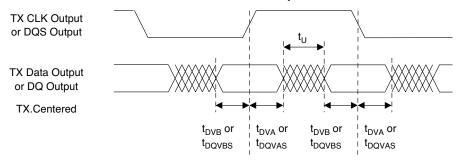

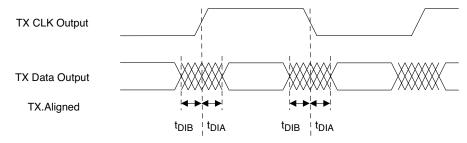

| DDR/DDR2/LPDDR Memory WRITE Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                            |

| DDR Memory Interface Generation Using IPexpress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                            |

| DDR Memory DQ/DQS Design Rules and Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                            |

| DDR/DDR2/LPDDR Pinout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                            |

| DDR Software Primitives and Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                            |

| Input DDR Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                            |

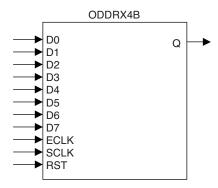

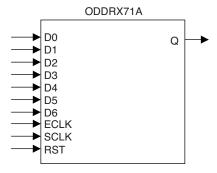

| Output DDR Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                            |

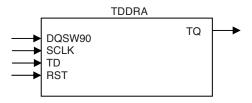

| DDR Control Logic Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                            |

| Technical Support Assistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                            |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                            |

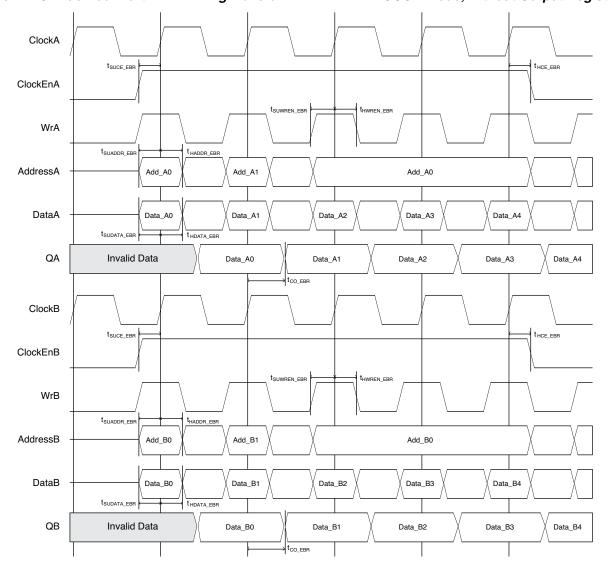

| Revision History  Memory Usage Guide for MachXO2 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11-60                                                                                                      |

| Revision History  Memory Usage Guide for MachXO2 Devices  Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11-60<br>12-1                                                                                              |

| Revision History  Memory Usage Guide for MachXO2 Devices  Introduction  Memories in MachXO2 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11-60<br>12-1<br>12-1                                                                                      |

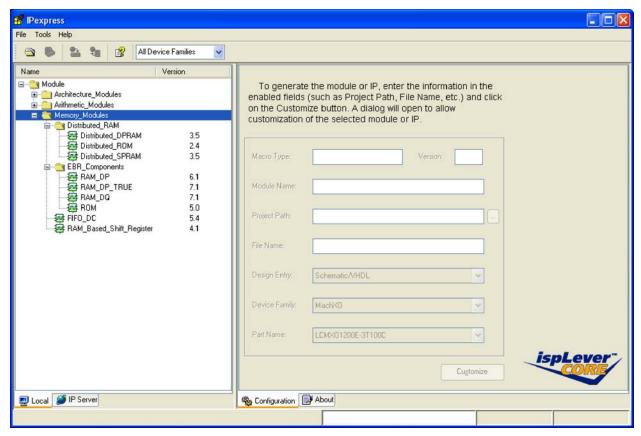

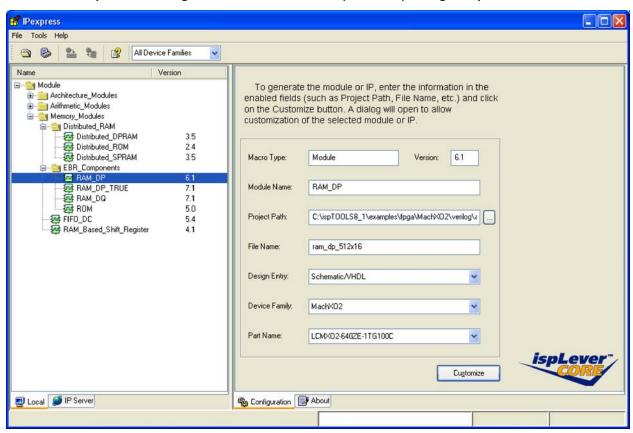

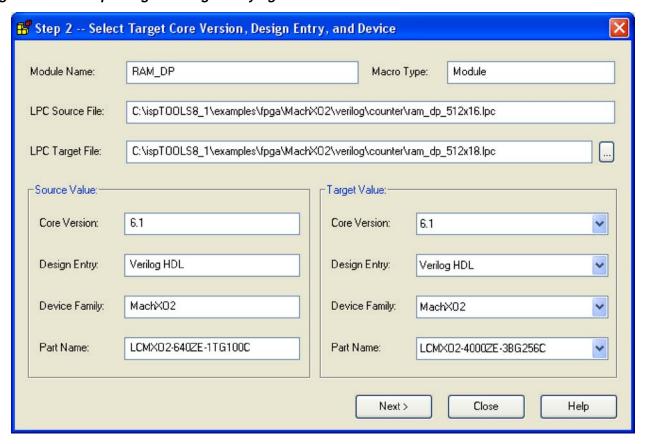

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11-60<br>12-1<br>12-1<br>12-2                                                                              |

| Revision History  Memory Usage Guide for MachXO2 Devices  Introduction  Memories in MachXO2 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11-60<br>12-1<br>12-1<br>12-2                                                                              |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11-60<br>12-1<br>12-1<br>12-2<br>12-3                                                                      |

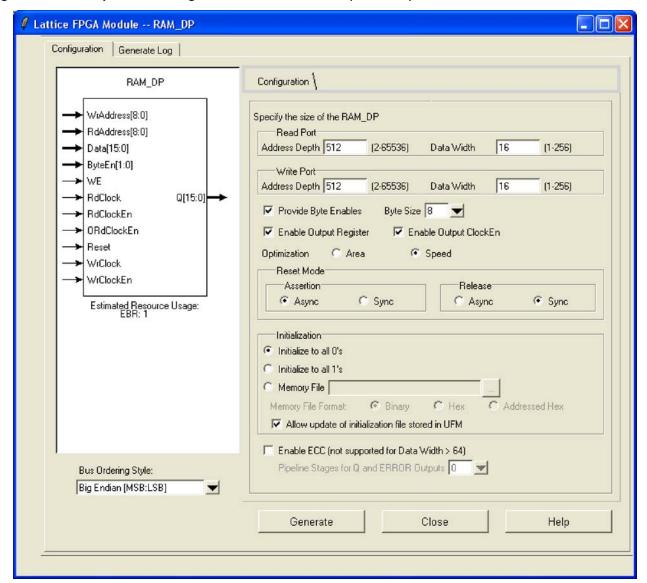

| Revision History  Memory Usage Guide for MachXO2 Devices  Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11-60<br>12-1<br>12-1<br>12-2<br>12-3                                                                      |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11-60<br>12-1<br>12-1<br>12-2<br>12-3<br>12-6<br>12-7                                                      |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules  IP Regeneration/Modification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11-60 12-1 12-2 12-3 12-6 12-7 12-8                                                                        |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8                                                                   |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8                                                                   |

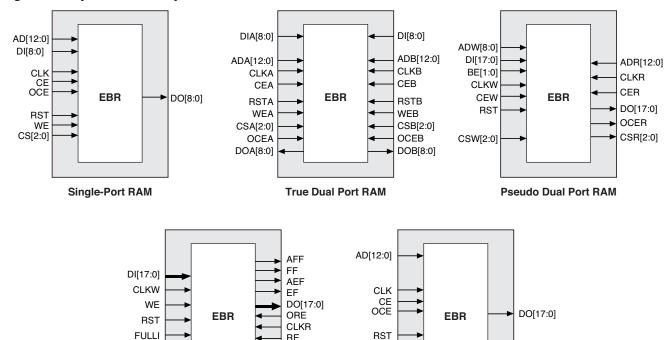

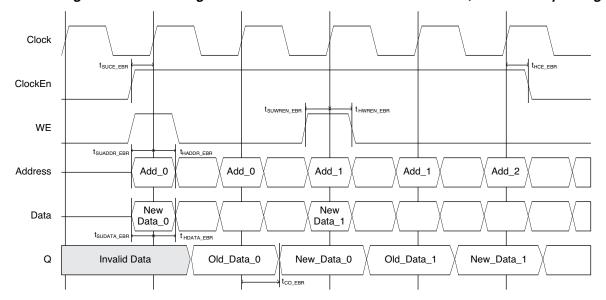

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices.  Utilizing IPexpress.  IPexpress Flow.  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules.  Single Port RAM (RAM_DQ) – EBR Based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-8                                                              |

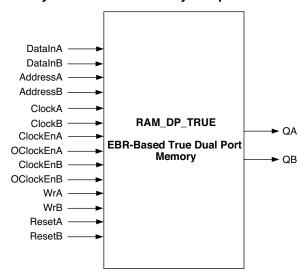

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices.  Utilizing IPexpress.  IPexpress Flow.  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI.  Memory Module Inference  IPexpress Memory Modules.  Single Port RAM (RAM_DQ) – EBR Based  Dual Port RAM (RAM_DP_TRUE) – EBR Based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-8 12-8                                                         |

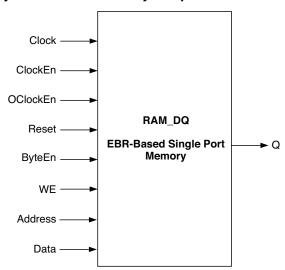

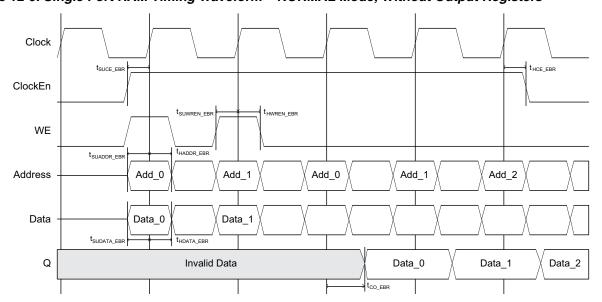

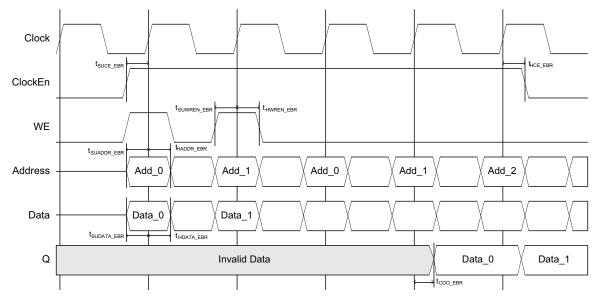

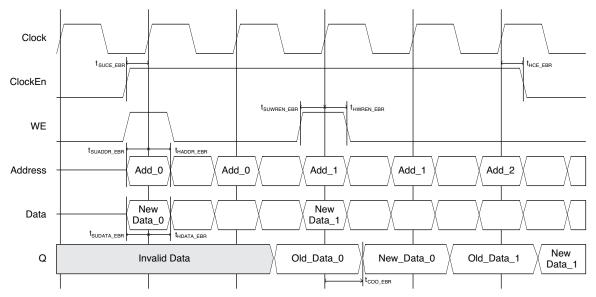

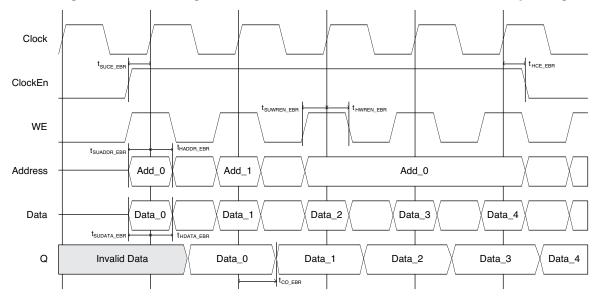

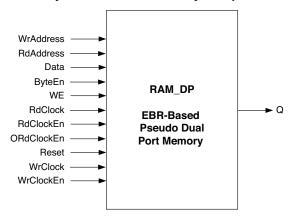

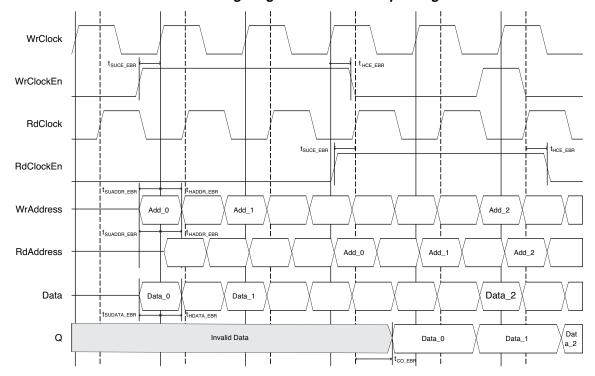

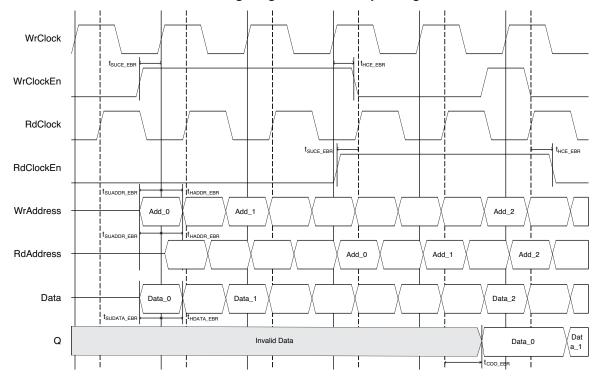

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress.  IPexpress Flow.  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules.  Single Port RAM (RAM_DQ) – EBR Based  Dual Port RAM (RAM_DP_TRUE) – EBR Based  Pseudo Dual Port RAM (RAM_DP) – EBR Based                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-8 12-12 12-19                                                  |

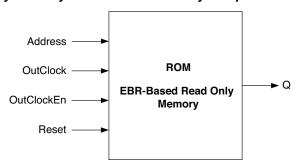

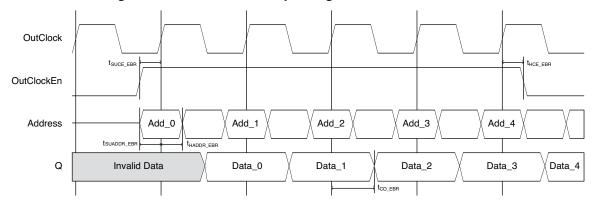

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules  Single Port RAM (RAM_DQ) – EBR Based  Dual Port RAM (RAM_DP_TRUE) – EBR Based  Pseudo Dual Port RAM (RAM_DP) – EBR Based  Read Only Memory (ROM) – EBR Based                                                                                                                                                                                                                                                                                                                                                                                                                   | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-8 12-12 12-12 12-12                                            |

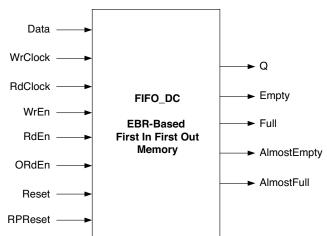

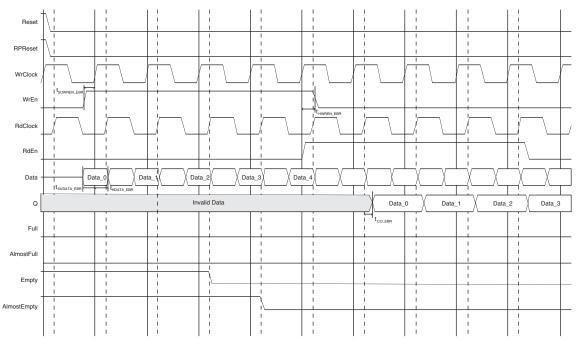

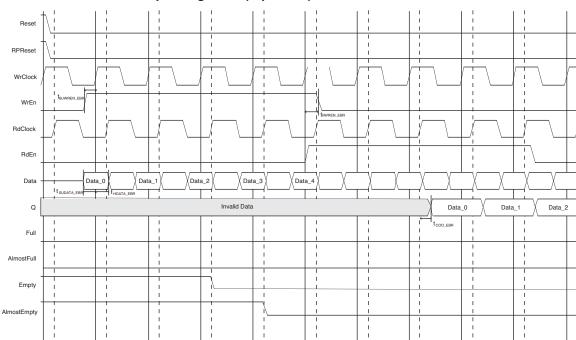

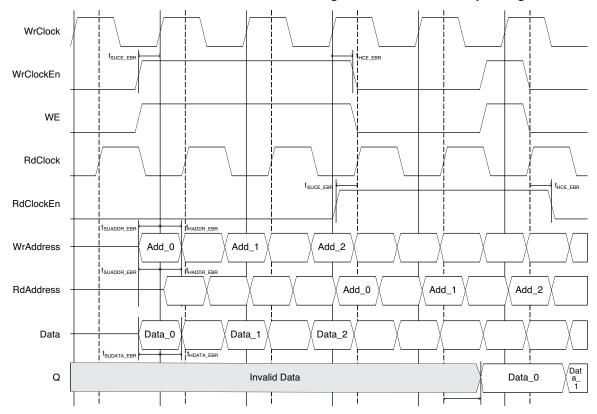

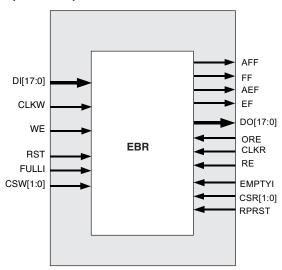

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules.  Single Port RAM (RAM_DQ) – EBR Based  Dual Port RAM (RAM_DP_TRUE) – EBR Based  Pseudo Dual Port RAM (RAM_DP) – EBR Based  Read Only Memory (ROM) – EBR Based  First In First Out (FIFO_DC) – EBR Based                                                                                                                                                                                                                                                                                                                                                                        | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-12 12-12 12-12 12-23                                           |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-12 12-12 12-12 12-23 12-24                                     |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules  Single Port RAM (RAM_DQ) – EBR Based  Dual Port RAM (RAM_DP_TRUE) – EBR Based  Pseudo Dual Port RAM (RAM_DP) – EBR Based  Read Only Memory (ROM) – EBR Based  First In First Out (FIFO_DC) – EBR Based  FIFO_DC Flags  FIFO_DC Dual and Dynamic Threshold Options                                                                                                                                                                                                                                                                                                              | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-12 12-12 12-12 12-23 12-24 12-25                               |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices.  Utilizing IPexpress.  IPexpress Flow.  ECC in Memory Modules  IP Regeneration/Modification.  Utilizing PMI.  Memory Module Inference.  IPexpress Memory Modules.  Single Port RAM (RAM_DQ) – EBR Based.  Dual Port RAM (RAM_DP_TRUE) – EBR Based.  Pseudo Dual Port RAM (RAM_DP) – EBR Based.  Read Only Memory (ROM) – EBR Based.  First In First Out (FIFO_DC) – EBR Based.  FIFO_DC Flags.  FIFO_DC Dual and Dynamic Threshold Options.  FIFO_DC Operation.                                                                                                                                                                                                                                                                            | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-12 12-12 12-12 12-23 12-24 12-25 12-25                         |

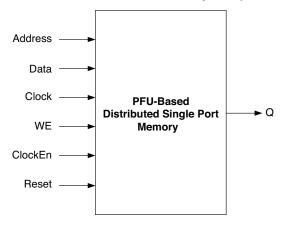

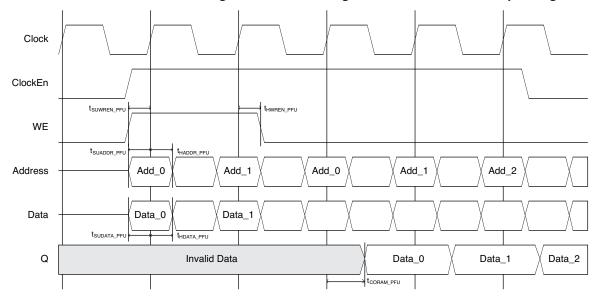

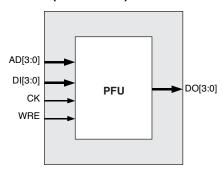

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules  Single Port RAM (RAM_DQ) – EBR Based  Dual Port RAM (RAM_DP_TRUE) – EBR Based  Pseudo Dual Port RAM (RAM_DP) – EBR Based  Read Only Memory (ROM) – EBR Based  First In First Out (FIFO_DC) – EBR Based  FIFO_DC Flags  FIFO_DC Dual and Dynamic Threshold Options  FIFO_DC Operation  Distributed Single Port RAM (Distributed_SPRAM) – PFU Based                                                                                                                                                                                                                              | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-12 12-12 12-12 12-23 12-24 12-25 12-27                         |

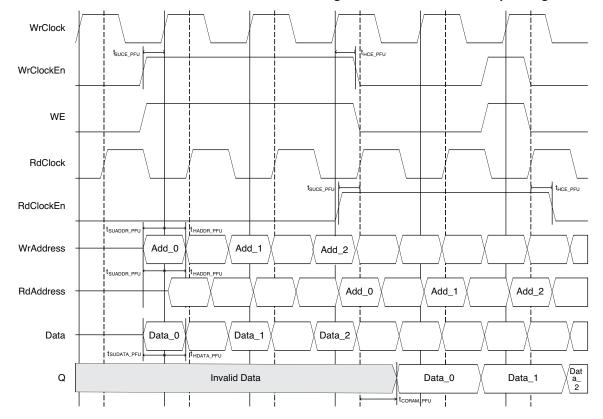

| Revision History  Memory Usage Guide for MachXO2 Devices  Introduction  Memories in MachXO2 Devices.  Utilizing IPexpress.  IPexpress Flow.  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules.  Single Port RAM (RAM_DQ) – EBR Based  Dual Port RAM (RAM_DP_TRUE) – EBR Based  Pseudo Dual Port RAM (RAM_DP) – EBR Based  Read Only Memory (ROM) – EBR Based  First In First Out (FIFO_DC) – EBR Based  FIFO_DC Flags  FIFO_DC Dual and Dynamic Threshold Options  FIFO_DC Operation  Distributed Single Port RAM (Distributed_SPRAM) – PFU Based  Distributed Dual Port RAM (Distributed_DPRAM) – PFU Based                                                                                                                                                              | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-12 12-12 12-12 12-23 12-24 12-25 12-27 12-29                   |

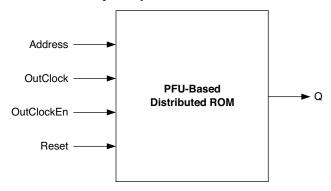

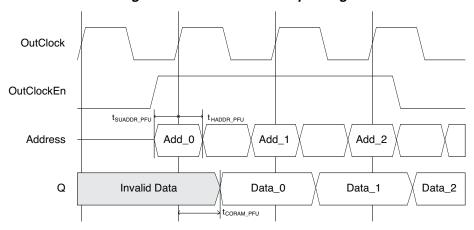

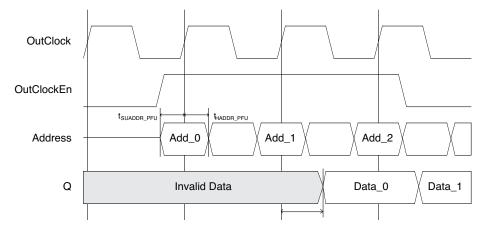

| Revision History  Memory Usage Guide for MachXO2 Devices  Introduction  Memories in MachXO2 Devices  Utilizing IPexpress.  IPexpress Flow.  ECC in Memory Modules.  IP Regeneration/Modification.  Utilizing PMI.  Memory Module Inference.  IPexpress Memory Modules.  Single Port RAM (RAM_DQ) – EBR Based.  Dual Port RAM (RAM_DP_TRUE) – EBR Based.  Pseudo Dual Port RAM (RAM_DP) – EBR Based.  Read Only Memory (ROM) – EBR Based.  First In First Out (FIFO_DC) – EBR Based.  FIFO_DC Flags.  FIFO_DC Dual and Dynamic Threshold Options  FIFO_DC Operation.  Distributed Single Port RAM (Distributed_SPRAM) – PFU Based.  Distributed Dual Port RAM (Distributed_DPRAM) – PFU Based.  Distributed ROM (Distributed_DPRAM) – PFU Based.                                                                                                | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-12 12-12 12-22 12-23 12-25 12-27 12-29 12-31                   |

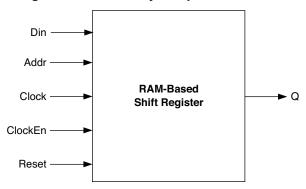

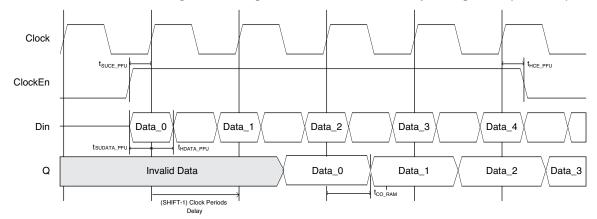

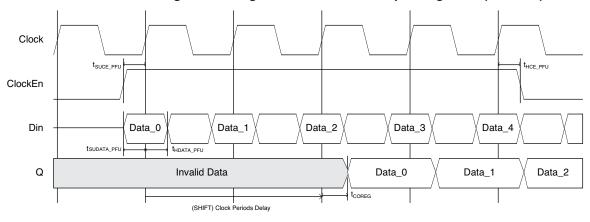

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules  Single Port RAM (RAM_DQ) – EBR Based  Dual Port RAM (RAM_DP_TRUE) – EBR Based  Pseudo Dual Port RAM (RAM_DP) – EBR Based  Read Only Memory (ROM) – EBR Based  First In First Out (FIFO_DC) – EBR Based  FIFO_DC Flags  FIFO_DC Operation  Distributed Single Port RAM (Distributed_SPRAM) – PFU Based  Distributed Dual Port RAM (Distributed_DPRAM) – PFU Based  Distributed ROM (Distributed_ROM) – PFU-Based  RAM-Based Shift Register                                                                                                                                      | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-18 12-19 12-19 12-22 12-23 12-25 12-27 12-27 12-31 12-32            |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress.  IPexpress Flow.  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI.  Memory Module Inference  IPexpress Memory Modules.  Single Port RAM (RAM_DQ) – EBR Based.  Dual Port RAM (RAM_DP_TRUE) – EBR Based  Pseudo Dual Port RAM (RAM_DP) – EBR Based.  Read Only Memory (ROM) – EBR Based.  First In First Out (FIFO_DC) – EBR Based.  First In First Out (FIFO_DC) – EBR Based.  FIFO_DC Dual and Dynamic Threshold Options  FIFO_DC Operation.  Distributed Single Port RAM (Distributed_SPRAM) – PFU Based.  Distributed Dual Port RAM (Distributed_DPRAM) – PFU Based.  Distributed ROM (Distributed_ROM) – PFU Based.  Distributed ROM (Distributed_ROM) – PFU-Based.  RAM-Based Shift Register. | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-19 12-19 12-22 12-23 12-25 12-27 12-29 12-31 12-34                  |

| Revision History  Memory Usage Guide for MachXO2 Devices Introduction  Memories in MachXO2 Devices  Utilizing IPexpress  IPexpress Flow  ECC in Memory Modules  IP Regeneration/Modification  Utilizing PMI  Memory Module Inference  IPexpress Memory Modules  Single Port RAM (RAM_DQ) – EBR Based  Dual Port RAM (RAM_DP_TRUE) – EBR Based  Pseudo Dual Port RAM (RAM_DP) – EBR Based  Read Only Memory (ROM) – EBR Based  First In First Out (FIFO_DC) – EBR Based  FIFO_DC Flags  FIFO_DC Operation  Distributed Single Port RAM (Distributed_SPRAM) – PFU Based  Distributed Dual Port RAM (Distributed_DPRAM) – PFU Based  Distributed ROM (Distributed_ROM) – PFU-Based  RAM-Based Shift Register                                                                                                                                      | 11-60 12-1 12-2 12-3 12-6 12-7 12-8 12-8 12-12 12-12 12-12 12-22 12-23 12-25 12-27 12-31 12-34 12-34 12-34 |

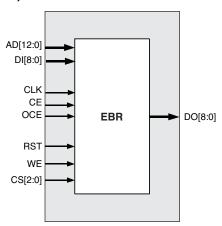

| Pseudo Dual Port RAM (PDPW8KC) – EBR-Based     | 12-38 |

|------------------------------------------------|-------|

| Dual-Clock FIFO (FIFO8KB) - EBR Based          | 12-40 |

| FIFO_DC Flags                                  | 12-41 |

| Distributed SPRAM (SPR16X4C) – PFU Based       | 12-42 |

| Distributed DPRAM (DPR16X4C) - PFU Based       | 12-43 |

| Distributed ROM (ROMnnnX1A) - PFU Based        | 12-43 |

| Initializing Memory                            | 12-44 |

| Initialization File Format                     | 12-44 |

| Technical Support Assistance                   |       |

| Revision History                               | 12-46 |

| Appendix A. Attribute Definitions              | 12-47 |

| DATA_WIDTH                                     | 12-47 |

| REGMODE                                        | 12-47 |

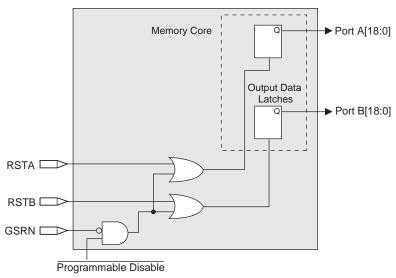

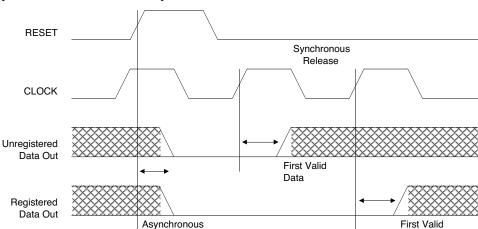

| RESETMODE                                      | 12-47 |

| CSDECODE                                       | 12-47 |

| WRITEMODE                                      | 12-47 |

| GSR                                            | 12-47 |

| ASYNC RESET RELEASE                            | 12-48 |

| INIT DATA                                      | 12-48 |

| Appendix B. Setting FIFO_DC Pointer Attributes | 12-49 |

| MachXO2 sysCLOCK PLL Design and Usage Guide    |       |

| Introduction                                   | 13-1  |

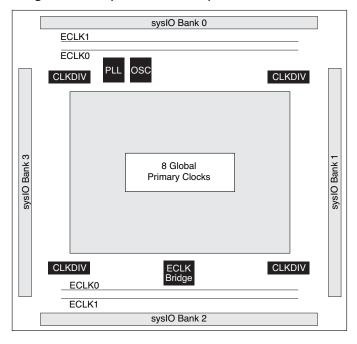

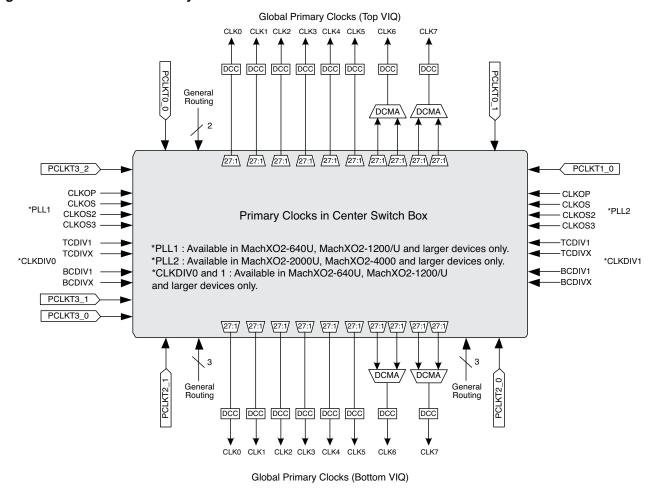

| Clock/Control Distribution Network             | 13-1  |

| MachXO2 Top Level View                         | 13-1  |

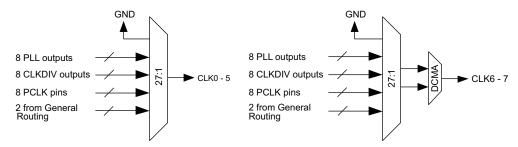

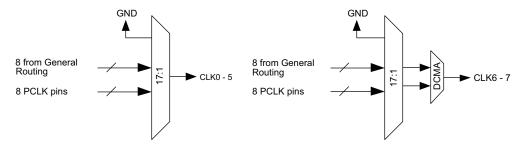

| Primary Clocks                                 | 13-2  |

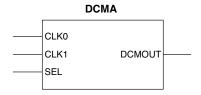

| Dynamic Clock Mux (DCMA)                       | 13-2  |

| DCMA Primitive Definition                      | 13-2  |

| DCMA Declaration in VHDL Source Code           | 13-3  |

| DCMA Usage with Verilog Source Code            | 13-3  |

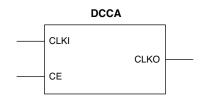

| Dynamic Clock Control (DCCA)                   | 13-4  |

| DCCA Primitive Definition                      | 13-4  |

| DCCA Declaration in VHDL Source Code           | 13-4  |

| DCCA Usage with Verilog Source Code            | 13-5  |

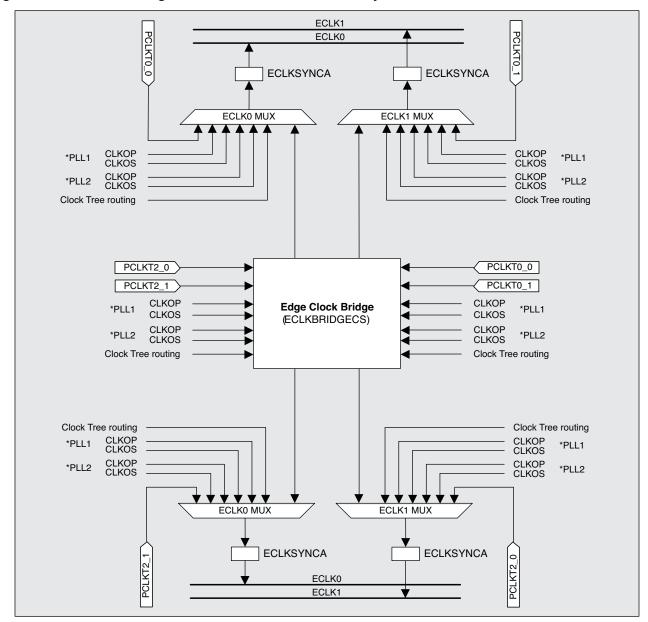

| Edge Clocks                                    | 13-5  |

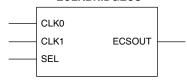

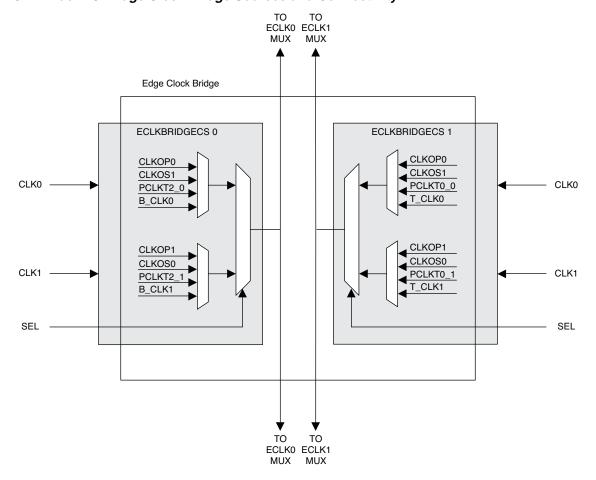

| Edge Clock Bridge                              | 13-5  |

| ECLKBRIDGECS Primitive Definition              | 13-5  |

| ECLKBRIDGECS Declaration in VHDL Source Code   | 13-6  |

| ECLKBRIDGECS Usage with Verilog Source Code    | 13-6  |

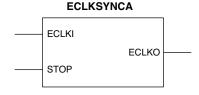

| Edge Clock Synchronization (ECLKSYNCA)         | 13-7  |

| ECLKSYNCA Primitive Definition                 |       |

| ECLKSYNCA Declaration in VHDL Source Code      | 13-7  |

| ECLKSYNCA Usage with Verilog Source Code       | 13-8  |

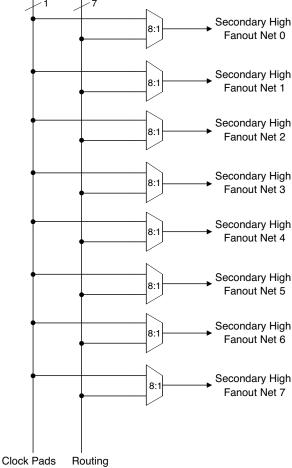

| Secondary High Fan-out Nets                    | 13-8  |

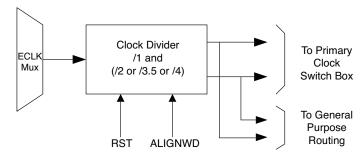

| Clock Dividers (CLKDIVC)                       | 13-8  |

| CLKDIVC Primitive Definition                   | 13-9  |

| CLKDIVC Declaration in VHDL Source Code        | 13-9  |

| CLKDIVC Usage with Verilog Source Code         | 13-10 |

| CLKDIVC Instantiation                          |       |

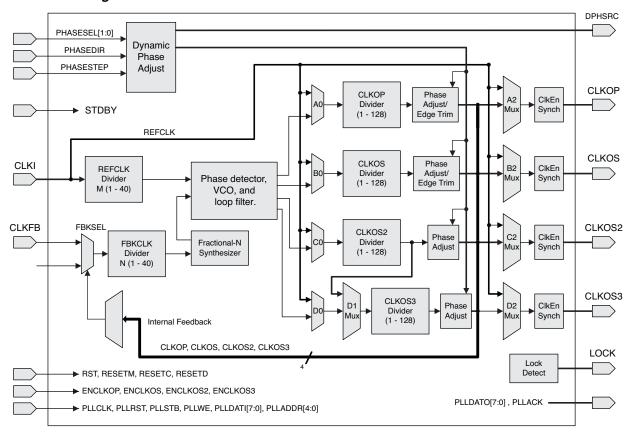

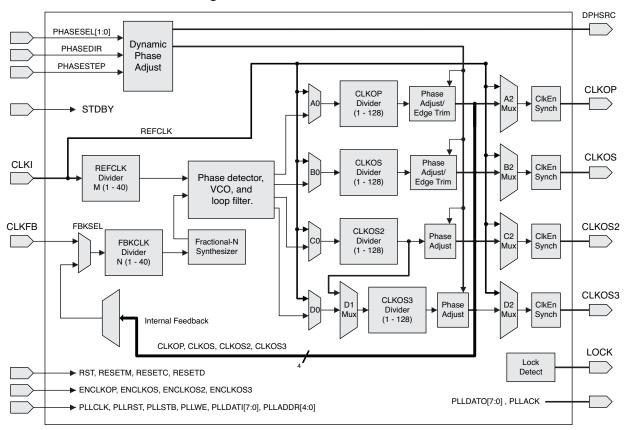

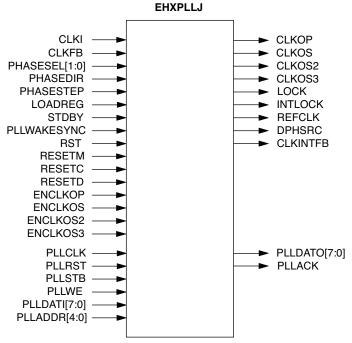

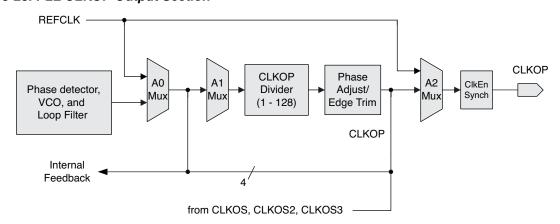

| sysCLOCK PLL                                   | 13-11 |

| Functional Description                         | 13-11 |

| PLL Features                                   |       |

| PLL Inputs and Outputs                         |       |

| PLL Attributes                                 |       |

| MachXO2 PLL Primitive Definition               |       |

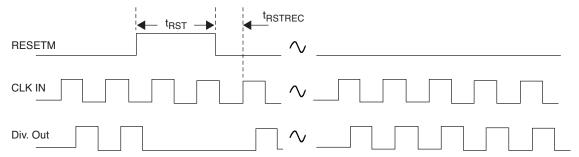

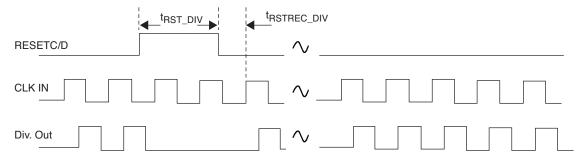

| Dynamic Phase Adjustment                                              | 13-18 |

|-----------------------------------------------------------------------|-------|

| Frequency Calculation                                                 | 13-19 |

| Fractional-N Synthesis Operation                                      | 13-20 |

| Low Power Features                                                    | 13-20 |

| Dynamic Clock Enable                                                  | 13-20 |

| Standby Mode                                                          |       |

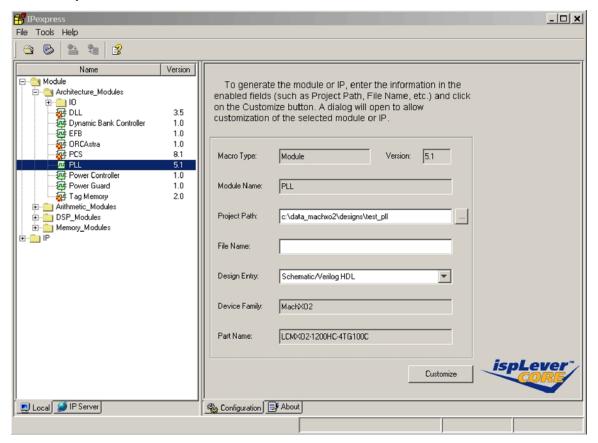

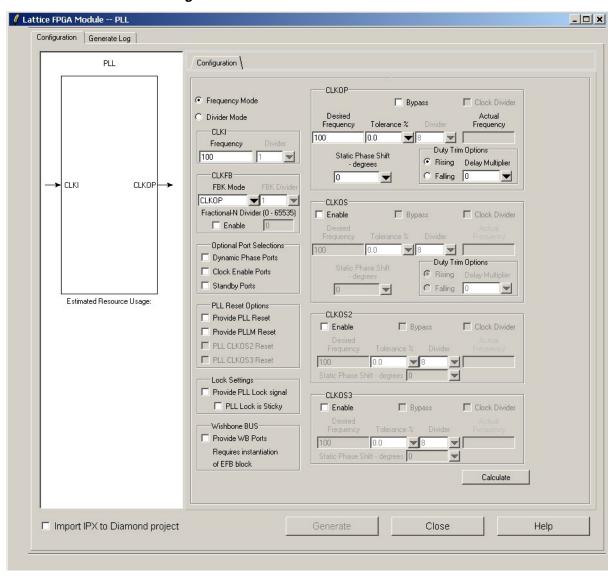

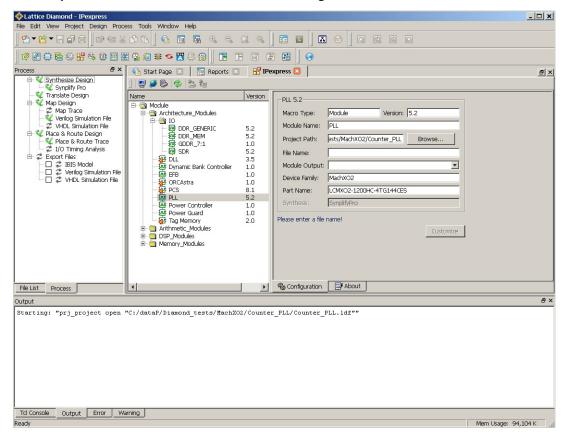

| Configuring the PLL Using IPexpress                                   | 13-21 |

| Configuration Tab                                                     |       |

| Configuration Modes                                                   |       |

| IPexpress Output                                                      |       |

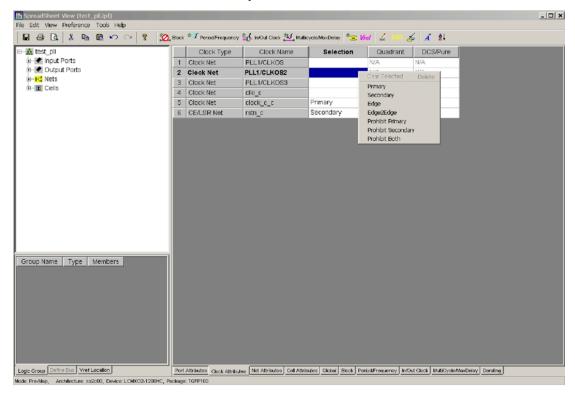

| Use of the Pre-MAP Preference Editor                                  |       |

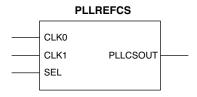

| PLL Reference Clock Switch (PLLREFCS)                                 |       |

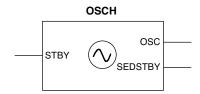

| Internal Oscillator (OSCH)                                            |       |

| OSCH Primitive Definition                                             |       |

| OSCH Declaration in VHDL Source Code                                  |       |

| Technical Support Assistance                                          |       |

| Revision History                                                      |       |

| Appendix A. Primary Clock Sources and Distribution                    |       |

| Appendix B. Edge Clock Sources and Connectivity                       |       |

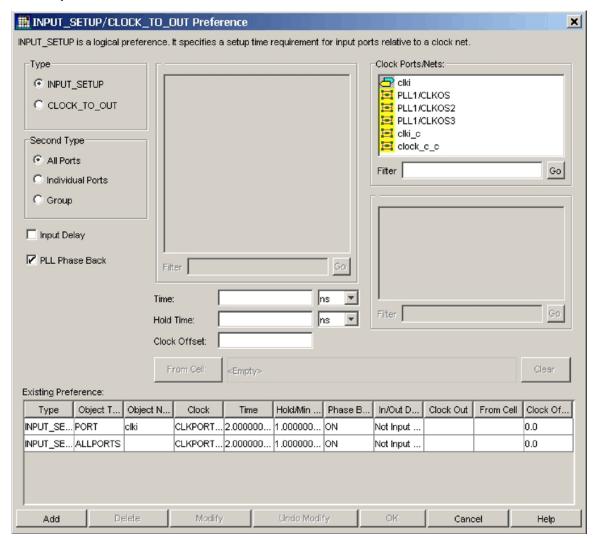

| Appendix C. Clock Preferences                                         |       |

| Appendix D. PLL WISHBONE Bus Operation                                |       |

| PLL Architecture                                                      |       |

| Appendix E. MachXO2 Device Usage with Lattice Diamond Design Software |       |

| MachXO2 Programming and Configuration Usage Guide                     | 13-40 |

| Introduction                                                          | 1/_1  |

| MachXO2 Features                                                      |       |

| Definition of Terms                                                   |       |

| Configuration Details                                                 |       |

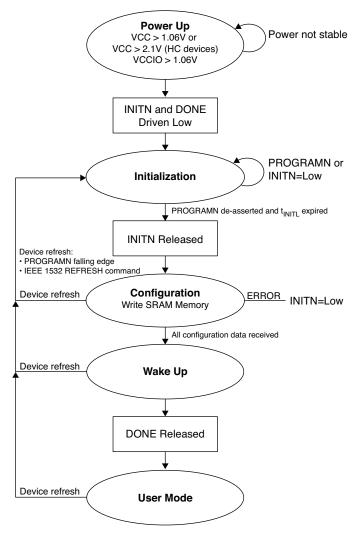

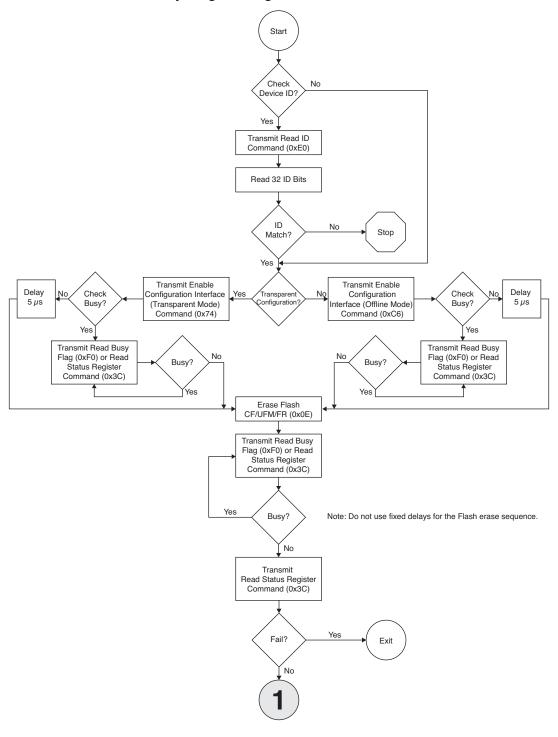

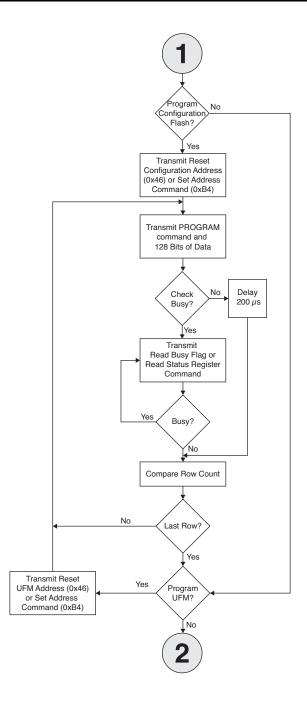

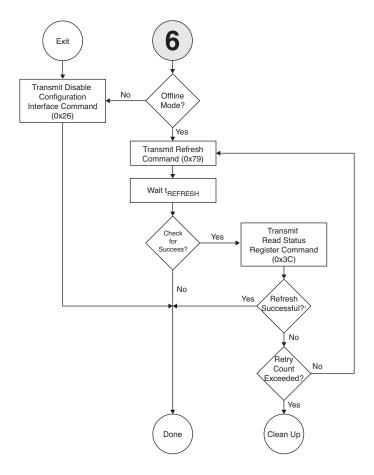

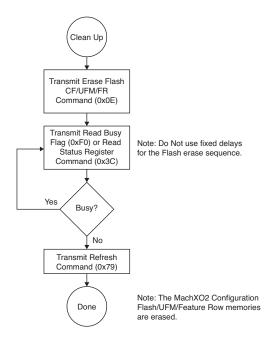

| Configuration Process and Flow                                        |       |

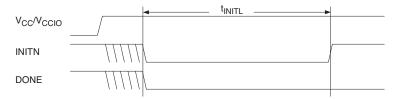

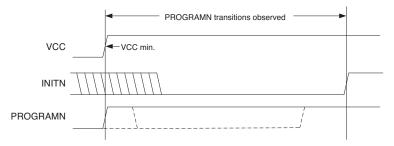

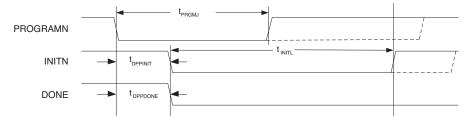

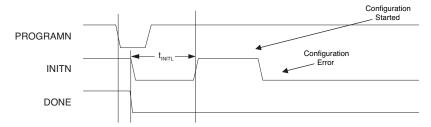

| Power-up Sequence                                                     |       |

| Initialization                                                        |       |

| Configuration                                                         |       |

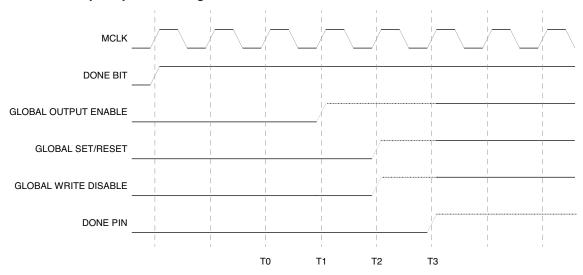

| Wake-up                                                               |       |

| User Mode                                                             |       |

| Clearing the Configuration Memory and Re-initialization               |       |

| ,                                                                     |       |

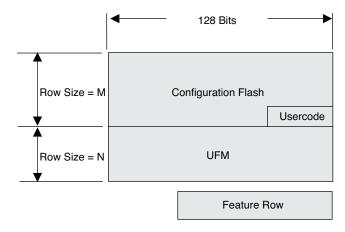

| Memory Space Accessibility                                            |       |

| Bitstream/PROM Sizes                                                  |       |

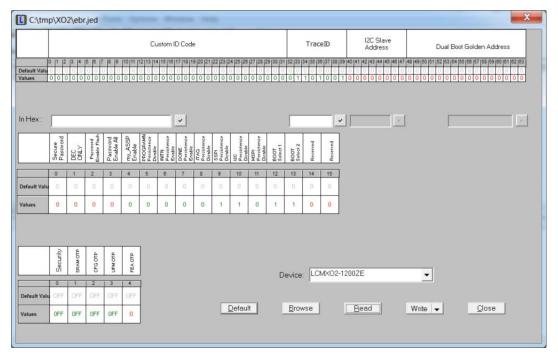

| Feature Row                                                           |       |

| Configuration Modes                                                   |       |

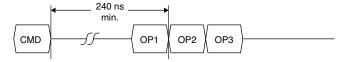

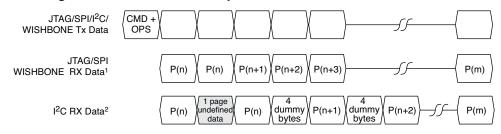

| sysCONFIG™ Ports                                                      |       |

| sysCONFIG Pins                                                        |       |

| Configuration Modes                                                   |       |

| SDM Mode                                                              |       |

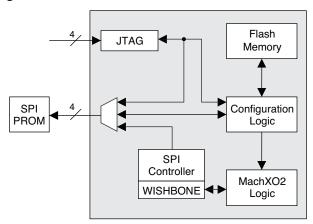

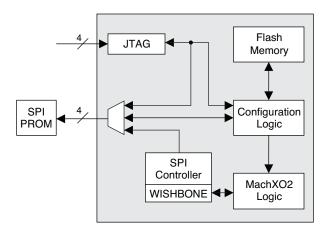

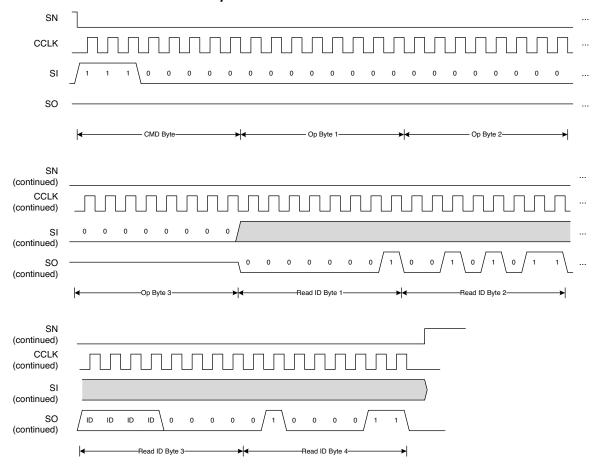

| Master SPI Configuration Mode (MSPI)                                  |       |

| Dual Boot Configuration Mode                                          |       |

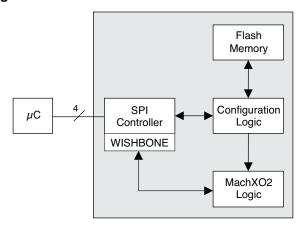

| Slave SPI Mode (SSPI)                                                 |       |

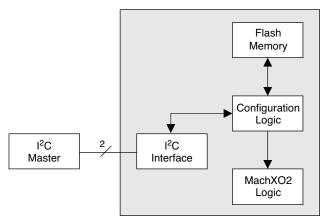

| I2C Configuration Mode                                                |       |

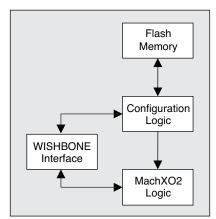

| WISHBONE Configuration Mode                                           |       |

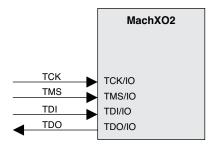

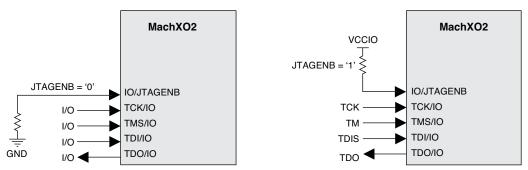

| JTAG Mode                                                             |       |

| TransFR Operation                                                     |       |

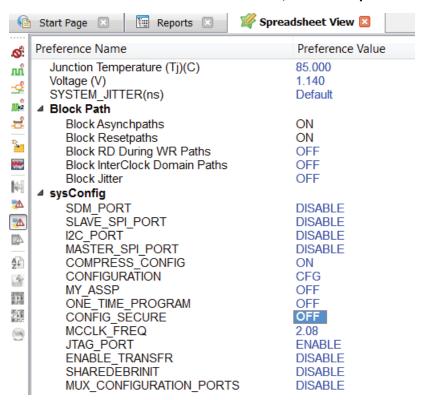

| Software Selectable Options                                           |       |

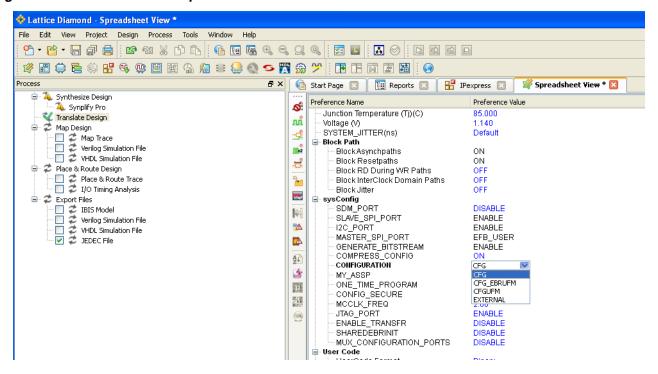

| Configuration Mode and Port Options                                   |       |

| Bitstream Generation Options                                          |       |

| Security Options                                                      | 14-31 |

| Device Wake-up Sequence                             |       |