# High-Performance 8-bit CMOS EPROM Microcontrollers with 10-bit A/D

### **Microcontroller Core Features:**

- · Only 58 single word instructions to learn

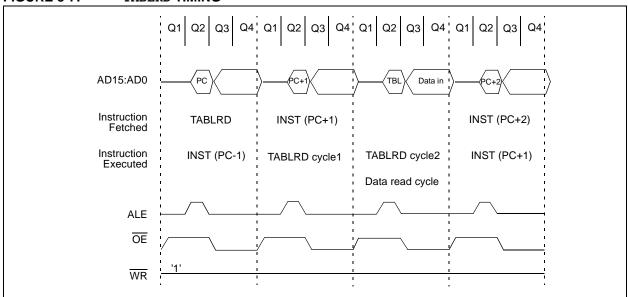

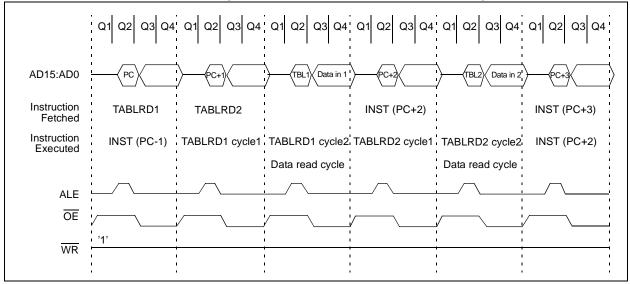

- All single cycle instructions (121 ns), except for program branches and table reads/writes which are two-cycle

- · Operating speed:

- DC 33 MHz clock input

- DC 121 ns instruction cycle

- 8 x 8 Single-Cycle Hardware Multiplier

- · Interrupt capability

- 16 level deep hardware stack

- · Direct, indirect, and relative addressing modes

- Internal/external program memory execution, capable of addressing 64 K x 16 program memory space

| Device     | Memory        |           |  |  |  |

|------------|---------------|-----------|--|--|--|

| Device     | Program (x16) | Data (x8) |  |  |  |

| PIC17C752  | 8 K           | 678       |  |  |  |

| PIC17C756A | 16 K          | 902       |  |  |  |

| PIC17C762  | 8 K           | 678       |  |  |  |

| PIC17C766  | 16 K          | 902       |  |  |  |

## **Peripheral Features:**

- Up to 66 I/O pins with individual direction control

- 10-bit, multi-channel Analog-to-Digital converter

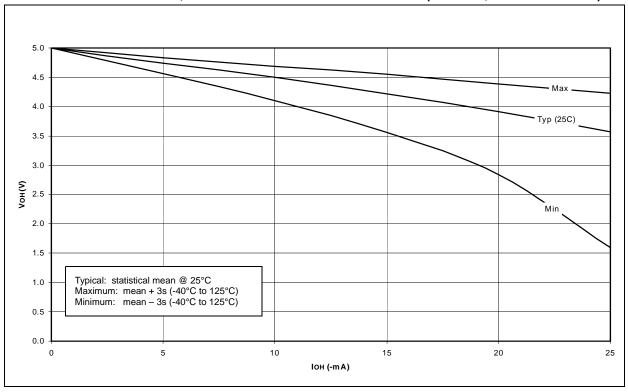

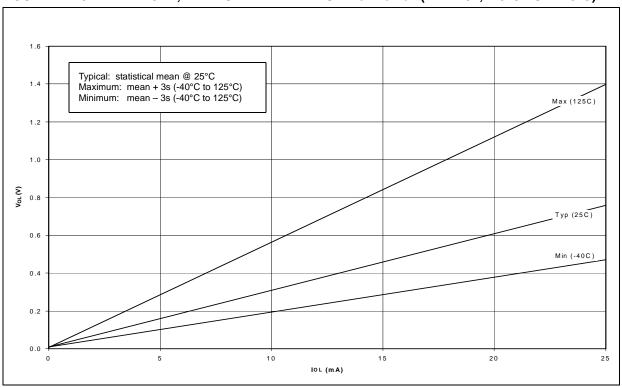

- High current sink/source for direct LED drive

- · Four capture input pins

- Captures are 16-bit, max resolution 121 ns

- Three PWM outputs (resolution is 1 to 10-bits)

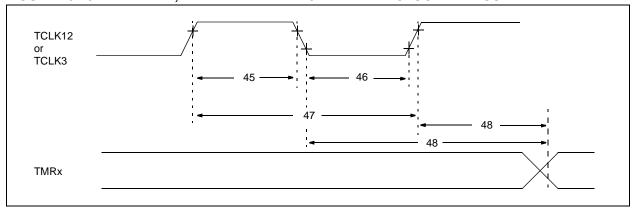

- TMR0: 16-bit timer/counter with 8-bit programmable prescaler

- TMR1: 8-bit timer/counter

- TMR2: 8-bit timer/counter

- TMR3: 16-bit timer/counter

- Two Universal Synchronous Asynchronous Receiver Transmitters (USART/SCI) with independent baud rate generators

- Synchronous Serial Port (SSP) with SPI<sup>™</sup> and I<sup>2</sup>C<sup>™</sup> modes (including I<sup>2</sup>C Master mode)

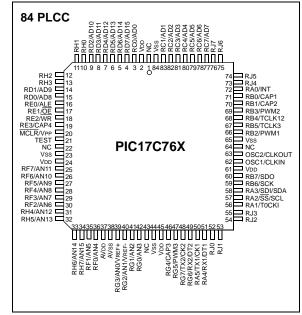

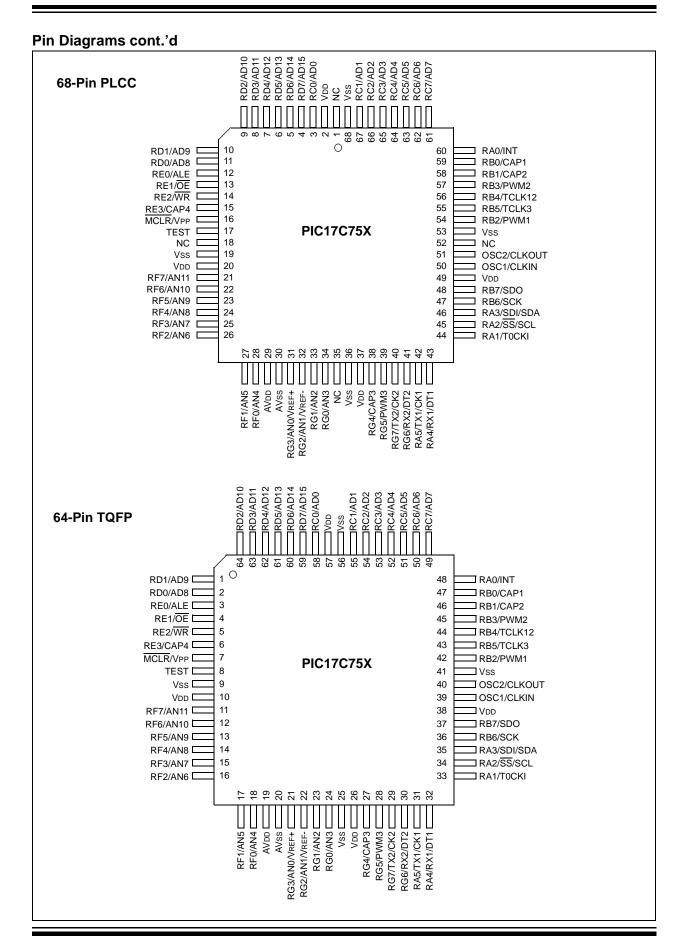

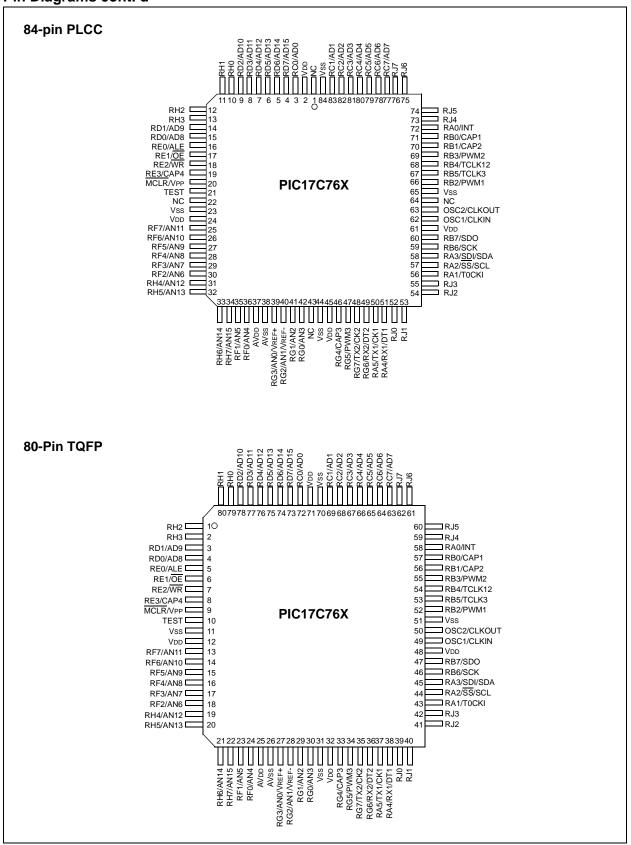

# Pin Diagrams

## **Special Microcontroller Features:**

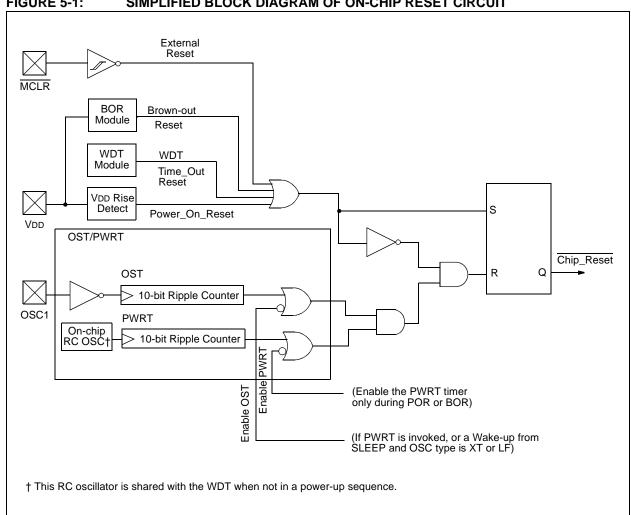

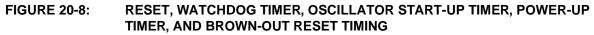

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

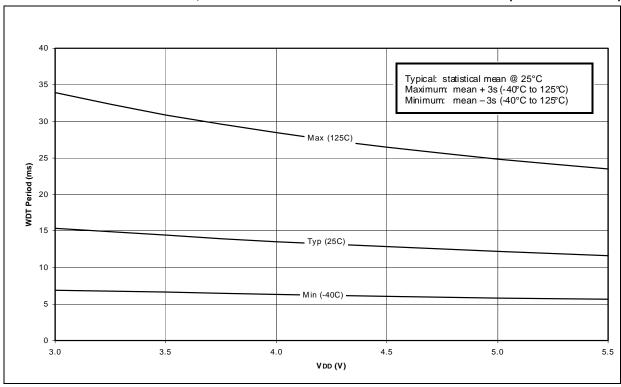

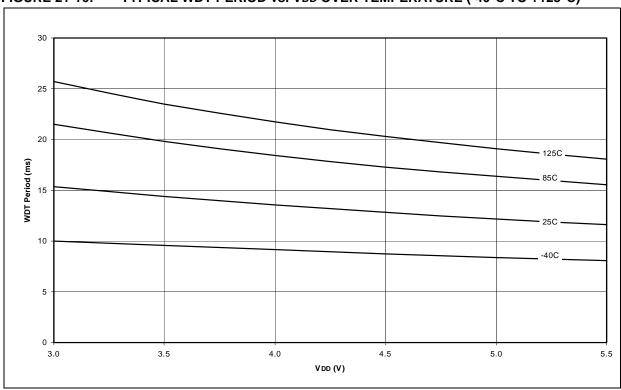

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Brown-out Reset

- · Code protection

- Power saving SLEEP mode

- · Selectable oscillator options

### **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- · Fully static design

- Wide operating voltage range (3.0V to 5.5V)

- Commercial and Industrial temperature ranges

- · Low power consumption

- < 5 mA @ 5V, 4 MHz

- 100 µA typical @ 4.5V, 32 kHz

- < 1 μA typical standby current @ 5V

### Pin Diagrams cont.'d

# **Table of Contents**

| 1.0             | Overview                                                                | 7   |

|-----------------|-------------------------------------------------------------------------|-----|

| 2.0             | Device Varieties                                                        |     |

| 3.0             | Architectural Overview                                                  | 11  |

| 4.0             | On-chip Oscillator Circuit                                              | 17  |

| 5.0             | Reset                                                                   | 23  |

| 6.0             | Interrupts                                                              | 33  |

| 7.0             | Memory Organization                                                     | 43  |

| 8.0             | Table Reads and Table Writes                                            | 59  |

| 9.0             | Hardware Multiplier                                                     | 67  |

| 10.0            | I/O Ports                                                               | 71  |

| 11.0            | Overview of Timer Resources                                             | 95  |

| 12.0            | Timer0                                                                  | 97  |

| 13.0            | Timer1, Timer2, Timer3, PWMs and Captures                               | 101 |

| 14.0            | Universal Synchronous Asynchronous Receiver Transmitter (USART) Modules | 117 |

| 15.0            | Master Synchronous Serial Port (MSSP) Module                            | 133 |

| 16.0            | Analog-to-Digital Converter (A/D) Module                                | 179 |

| 17.0            | Special Features of the CPU                                             | 191 |

| 18.0            | Instruction Set Summary                                                 | 197 |

| 19.0            | Development Support                                                     | 233 |

| 20.0            | PIC17C7XX Electrical Characteristics                                    | 239 |

| 21.0            | PIC17C7XX DC and AC Characteristics                                     | 267 |

| 22.0            | Packaging Information                                                   | 281 |

| <b>Appendix</b> | A: Modifications                                                        | 287 |

| <b>Appendix</b> | B: Compatibility                                                        | 287 |

| Appendix        | C: What's New                                                           | 288 |

| Appendix        | D: What's Changed                                                       | 288 |

| Index           |                                                                         | 289 |

| On-Line S       | Support                                                                 | 299 |

| Reader R        | Response                                                                | 300 |

| Product I       | dentification System                                                    | 301 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

### 1.0 OVERVIEW

This data sheet covers the PIC17C7XX group of the PIC17CXXX family of microcontrollers. The following devices are discussed in this data sheet:

- PIC17C752

- PIC17C756A

- PIC17C762

- PIC17C766

The PIC17C7XX devices are 68/84-pin, EPROM based members of the versatile PIC17CXXX family of low cost, high performance, CMOS, fully static, 8-bit microcontrollers.

All PICmicro® microcontrollers employ an advanced RISC architecture. The PIC17CXXX has enhanced core features, 16-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 16-bit wide instruction word with a separate 8-bit wide data path. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 58 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance. For mathematical intensive applications, all devices have a single cycle 8 x 8 Hardware Multiplier.

PIC17CXXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC17C7XX devices have up to 902 bytes of RAM and 66 I/O pins. In addition, the PIC17C7XX adds several peripheral features, useful in many high performance applications, including:

- · Four timer/counters

- · Four capture inputs

- Three PWM outputs

- Two independent Universal Synchronous Asynchronous Receiver Transmitters (USARTs)

- An A/D converter (multi-channel, 10-bit resolution)

- A Synchronous Serial Port (SPI and I<sup>2</sup>C w/ Master mode)

These special features reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption.

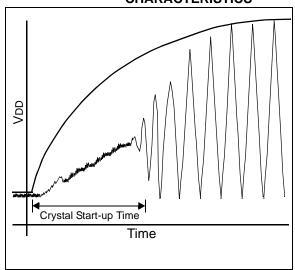

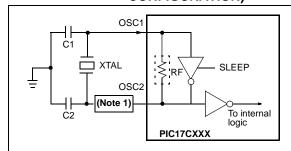

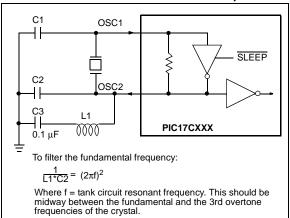

There are four oscillator options, of which the single pin RC oscillator provides a low cost solution, the LF oscillator is for low frequency crystals and minimizes power consumption, XT is a standard crystal and the EC is for external clock input.

The SLEEP (power-down) mode offers additional power saving. Wake-up from SLEEP can occur through several external and internal interrupts and device RESETS.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software malfunction.

There are four configuration options for the device operational mode:

- Microprocessor

- Microcontroller

- · Extended microcontroller

- · Protected microcontroller

The microprocessor and extended microcontroller modes allow up to 64K-words of external program memory.

The device also has Brown-out Reset circuitry. This allows a device RESET to occur if the device VDD falls below the Brown-out voltage trip point (BVDD). The chip will remain in Brown-out Reset until VDD rises above BVDD.

A UV erasable, CERQUAD packaged version (compatible with PLCC), is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC17C7XX fits perfectly in applications that require extremely fast execution of complex software programs. These include applications ranging from precise motor control and industrial process control to automotive, instrumentation, and telecom applications.

The EPROM technology makes customization of application programs (with unique security codes, combinations, model numbers, parameter storage, etc.) fast and convenient. Small footprint package options (including die sales) make the PIC17C7XX ideal for applications with space limitations that require high performance.

High speed execution, powerful peripheral features, flexible I/O, and low power consumption all at low cost make the PIC17C7XX ideal for a wide range of embedded control applications.

## 1.1 Family and Upward Compatibility

The PIC17CXXX family of microcontrollers have architectural enhancements over the PIC16C5X and PIC16CXX families. These enhancements allow the device to be more efficient in software and hardware requirements. Refer to Appendix A for a detailed list of enhancements and modifications. Code written for PIC16C5X or PIC16CXX can be easily ported to PIC17CXXX devices (Appendix B).

### 1.2 Development Support

The PIC17CXXX family is supported by a full featured macro assembler, a software simulator, an in-circuit emulator, a universal programmer, a "C" compiler and fuzzy logic support tools. For additional information, see Section 19.0.

TABLE 1-1: PIC17CXXX FAMILY OF DEVICES

| Feature                             | S         | PIC17C42A                                               | PIC17C43                                                   | PIC17C44                                                   | PIC17C752                  | PIC17C756A                 | PIC17C762                  | PIC17C766                  |

|-------------------------------------|-----------|---------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| Maximum Frequency of Operation      |           | 33 MHz                                                  | 33 MHz                                                     | 33 MHz                                                     | 33 MHz                     | 33 MHz                     | 33 MHz                     | 33 MHz                     |

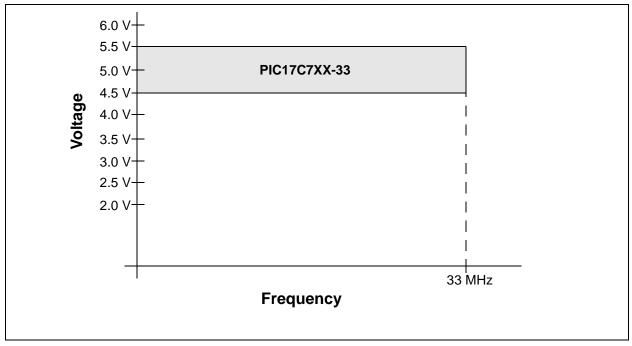

| Operating Voltage                   | Range     | 2.5 - 6.0V                                              | 2.5 - 6.0V                                                 | 2.5 - 6.0V                                                 | 3.0 - 5.5V                 | 3.0 - 5.5V                 | 3.0 - 5.5V                 | 3.0 - 5.5V                 |

| Program                             | (EPROM)   | 2 K                                                     | 4 K                                                        | 8 K                                                        | 8 K                        | 16 K                       | 8 K                        | 16 K                       |

| Memory (x16)                        | (ROM)     | _                                                       | _                                                          | _                                                          | _                          | _                          | _                          | _                          |

| Data Memory (byte                   | es)       | 232                                                     | 454                                                        | 454                                                        | 678                        | 902                        | 678                        | 902                        |

| Hardware Multiplie                  | r (8 x 8) | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Timer0<br>(16-bit + 8-bit posts     | scaler)   | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Timer1 (8-bit)                      |           | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Timer2 (8-bit)                      |           | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Timer3 (16-bit)                     |           | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Capture inputs (16                  | -bit)     | 2                                                       | 2                                                          | 2                                                          | 4                          | 4                          | 4                          | 4                          |

| PWM outputs (up t                   | o 10-bit) | 2                                                       | 2                                                          | 2                                                          | 3                          | 3                          | 3                          | 3                          |

| USART/SCI                           |           | 1                                                       | 1                                                          | 1                                                          | 2                          | 2                          | 2                          | 2                          |

| A/D channels (10-b                  | oit)      | _                                                       | _                                                          | _                                                          | 12                         | 12                         | 16                         | 16                         |

| SSP (SPI/I <sup>2</sup> C w/Mamode) | aster     | -                                                       |                                                            | _                                                          | Yes                        | Yes                        | Yes                        | Yes                        |

| Power-on Reset                      |           | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Watchdog Timer                      |           | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| External Interrupts                 |           | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Interrupt Sources                   |           | 11                                                      | 11                                                         | 11                                                         | 18                         | 18                         | 18                         | 18                         |

| Code Protect                        |           | Yes                                                     | Yes                                                        | Yes                                                        | Yes                        | Yes                        | Yes                        | Yes                        |

| Brown-out Reset                     |           | _                                                       | _                                                          | _                                                          | Yes                        | Yes                        | Yes                        | Yes                        |

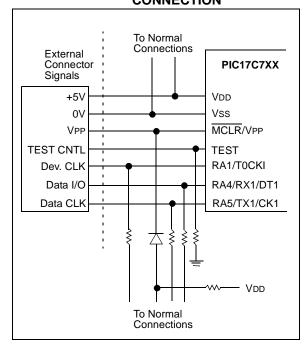

| In-Circuit Serial<br>Programming    |           | _                                                       | _                                                          | _                                                          | Yes                        | Yes                        | Yes                        | Yes                        |

| I/O Pins                            |           | 33                                                      | 33                                                         | 33                                                         | 50                         | 50                         | 66                         | 66                         |

| I/O High                            | Source    | 25 mA                                                   | 25 mA                                                      | 25 mA                                                      | 25 mA                      | 25 mA                      | 25 mA                      | 25 mA                      |

| Current Capability                  | Sink      | 25 mA <sup>(1)</sup>                                    | 25 mA <sup>(1)</sup>                                       | 25 mA <sup>(1)</sup>                                       | 25 mA <sup>(1)</sup>       | 25 mA <sup>(1)</sup>       | 25 mA <sup>(1)</sup>       | 25 mA <sup>(1)</sup>       |

| Package Types                       |           | 40-pin DIP<br>44-pin PLCC<br>44-pin MQFP<br>44-pin TQFP | 40-pin DIP<br>44-pin PLCC<br>44-pin<br>MQFP<br>44-pin TQFP | 40-pin DIP<br>44-pin PLCC<br>44-pin<br>MQFP<br>44-pin TQFP | 64-pin TQFP<br>68-pin PLCC | 64-pin TQFP<br>68-pin PLCC | 80-pin TQFP<br>84-pin PLCC | 80-pin TQFP<br>84-pin PLCC |

Note 1: Pins RA2 and RA3 can sink up to 60 mA.

### 2.0 DEVICE VARIETIES

Each device has a variety of frequency ranges and packaging options. Depending on application and production requirements, the proper device option can be selected using the information in the PIC17C7XX Product Selection System section at the end of this data sheet. When placing orders, please use the "PIC17C7XX Product Identification System" at the back of this data sheet to specify the correct part number. When discussing the functionality of the device, memory technology and voltage range does not matter.

There are two memory type options. These are specified in the middle characters of the part number.

- 1. **C**, as in PIC17**C**756A. These devices have EPROM type memory.

- CR, as in PIC17CR756A. These devices have ROM type memory.

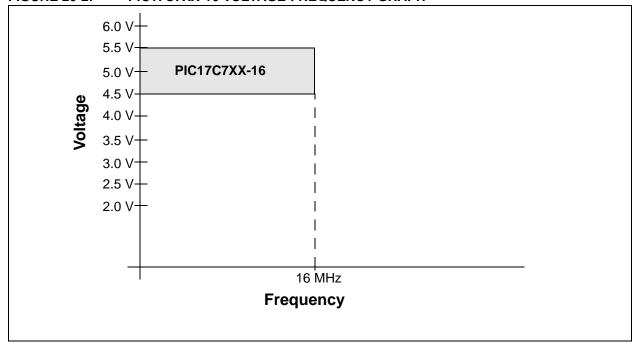

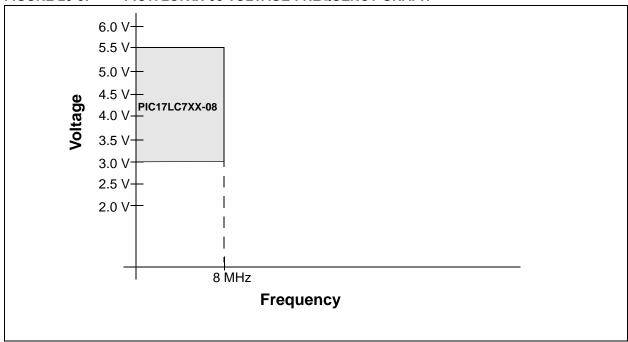

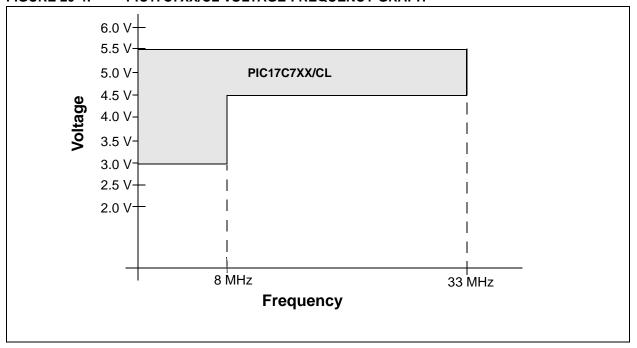

All these devices operate over the standard voltage range. Devices are also offered which operate over an extended voltage range (and reduced frequency range). Table 2-1 shows all possible memory types and voltage range designators for a particular device. These designators are in **bold** typeface.

TABLE 2-1: DEVICE MEMORY VARIETIES

| Memory Type                                                                     | Voltage Range       |                      |  |  |  |

|---------------------------------------------------------------------------------|---------------------|----------------------|--|--|--|

| Memory Type                                                                     | Standard            | Extended             |  |  |  |

| EPROM                                                                           | PIC17 <b>C</b> XXX  | PIC17 <b>LC</b> XXX  |  |  |  |

| ROM                                                                             | PIC17 <b>CR</b> XXX | PIC17 <b>LCR</b> XXX |  |  |  |

| <b>Note:</b> Not all memory technologies are available for a particular device. |                     |                      |  |  |  |

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERQUAD package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Third party programmers also are available; refer to the *Third Party Guide* for a list of sources.

# 2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers expecting frequent code changes and updates.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must be programmed.

# 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

# 2.4 Serialized Quick-Turnaround Production (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service, where a few user defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry code, password or ID number.

### 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

ROM devices do not allow serialization information in the program memory space.

For information on submitting ROM code, please contact your regional sales office.

**Note:** Presently, NO ROM versions of the PIC17C7XX devices are available.

NOTES:

### 3.0 ARCHITECTURAL OVERVIEW

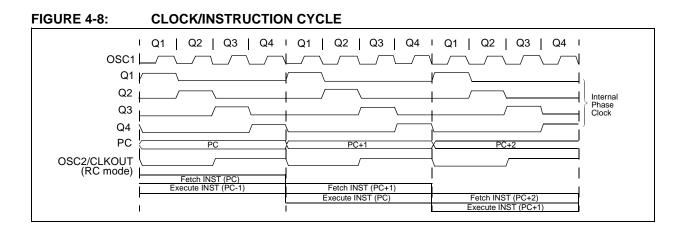

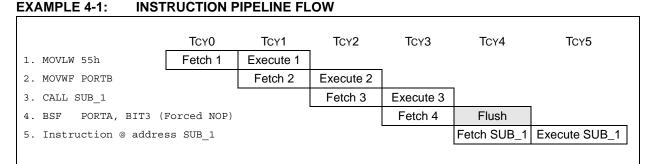

The high performance of the PIC17CXXX can be attributed to a number of architectural features, commonly found in RISC microprocessors. To begin with, the PIC17CXXX uses a modified Harvard architecture. This architecture has the program and data accessed from separate memories. So, the device has a program memory bus and a data memory bus. This improves bandwidth over traditional von Neumann architecture. where program and data are fetched from the same memory (accesses over the same bus). Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. PIC17CXXX opcodes are 16-bits wide, enabling single word instructions. The full 16-bit wide program memory bus fetches a 16-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions. Consequently, all instructions execute in a single cycle (121 ns @ 33 MHz), except for program branches and two special instructions that transfer data between program and data memory.

The PIC17CXXX can address up to 64K x 16 of program memory space.

The **PIC17C752** and **PIC17C762** integrate 8K x 16 of EPROM program memory on-chip.

The **PIC17C756A** and **PIC17C766** integrate 16K x 16 EPROM program memory on-chip.

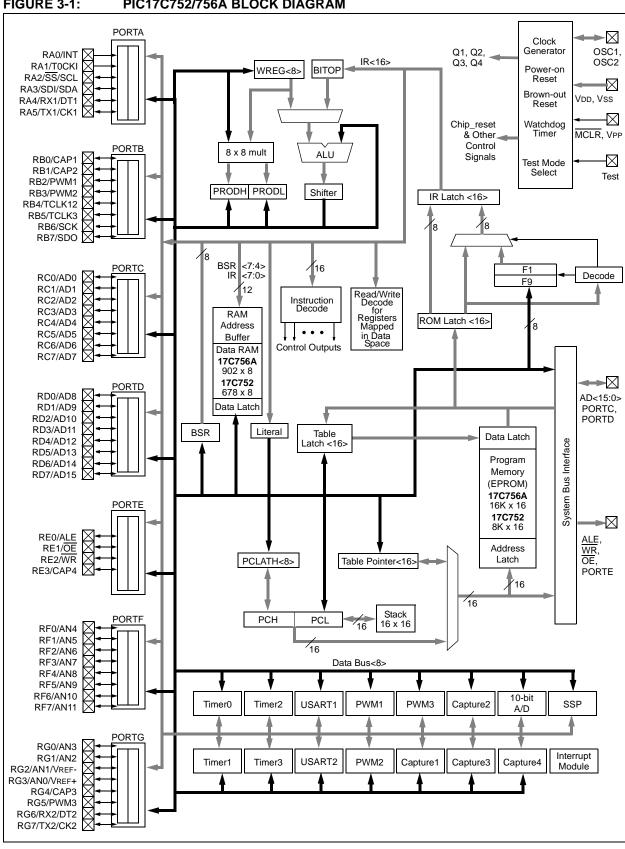

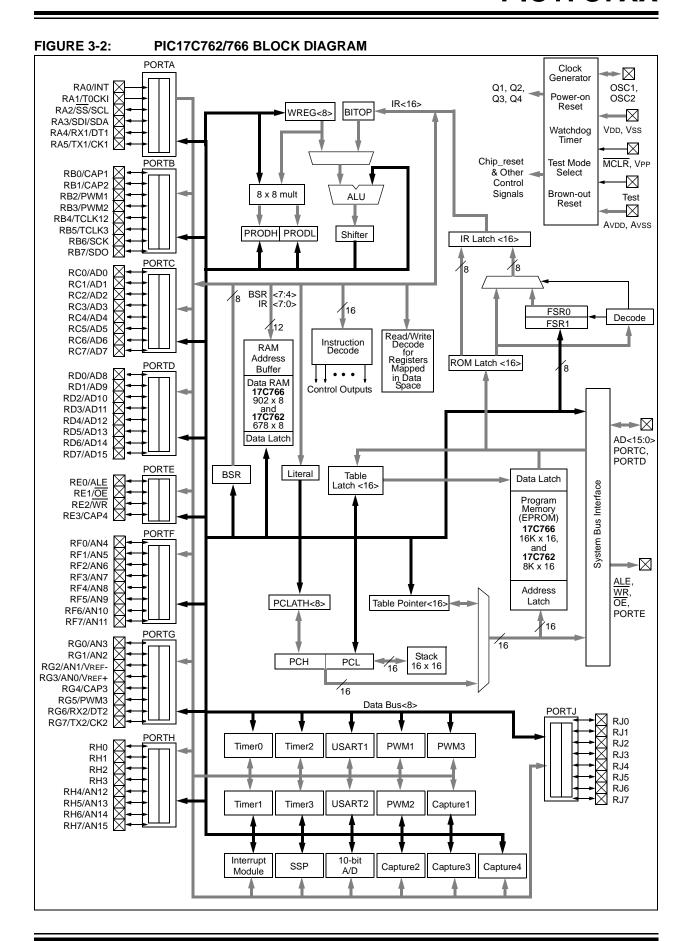

A simplified block diagram is shown in Figure 3-1. The descriptions of the device pins are listed in Table 3-1.

Program execution can be internal only (Microcontroller or Protected Microcontroller mode), external only (Microprocessor mode), or both (Extended Microcontroller mode). Extended Microcontroller mode does not allow code protection.

The PIC17CXXX can directly or indirectly address its register files or data memory. All special function registers, including the Program Counter (PC) and Working Register (WREG), are mapped in data memory. The PIC17CXXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC17CXXX simple, yet efficient. In addition, the learning curve is reduced significantly.

One of the PIC17CXXX family architectural enhancements from the PIC16CXX family, allows two file registers to be used in some two operand instructions. This allows data to be moved directly between two registers without going through the WREG register, thus increasing performance and decreasing program memory usage.

The PIC17CXXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The WREG register is an 8-bit working register used for ALU operations.

All PIC17CXXX devices have an 8 x 8 hardware multiplier. This multiplier generates a 16-bit result in a single cycle.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), Zero (Z) and Overflow (OV) bits in the ALUSTA register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

Signed arithmetic is comprised of a magnitude and a sign bit. The overflow bit indicates if the magnitude overflows and causes the sign bit to change state. That is, if the result of 8-bit signed operations is greater than 127 (7Fh), or less than -128 (80h).

Signed math can have greater than 7-bit values (magnitude), if more than one byte is used. The overflow bit only operates on bit6 (MSb of magnitude) and bit7 (sign bit) of each byte value in the ALU. That is, the overflow bit is not useful if trying to implement signed math where the magnitude, for example, is 11-bits.

If the signed math values are greater than 7-bits (such as 15-, 24-, or 31-bit), the algorithm must ensure that the low order bytes of the signed value ignore the overflow status bit.

Example 3-1 shows two cases of doing signed arithmetic. The Carry (C) bit and the Overflow (OV) bit are the most important status bits for signed math operations.

**EXAMPLE 3-1: 8-BIT MATH ADDITION**

| Hex Value    | Signed Values             | Unsigned Values         |

|--------------|---------------------------|-------------------------|

| FFh<br>+ 01h | -1<br>+ 1                 | 255<br>+ 1              |

| = 00h        | = 0 (FEh)                 | = $256 \rightarrow 00h$ |

| C bit = 1    | C bit = 1                 | C bit = 1               |

| OV bit = 0   | OV bit = 0                | OV bit = 0              |

| DC bit = 1   | DC bit = 1                | DC bit = 1              |

| Z bit = 1    | Z bit = 1                 | Z bit = 1               |

|              |                           |                         |

| Hex Value    | Signed Values             | Unsigned Values         |

| 7Fh          | 127                       | 127                     |

| <u>+ 01h</u> | <u>+ 1</u>                | <u>+ 1</u>              |

| = 80h        | $=$ 128 $\rightarrow$ 00h | = 128                   |

| C bit = 0    | C bit = 0                 | C bit = 0               |

| OV bit = 1   | OV bit = 1                | OV bit = 1              |

| DC bit = 1   | DC bit = 1                | DC bit = 1              |

|              | Z bit = 0                 |                         |

FIGURE 3-1: PIC17C752/756A BLOCK DIAGRAM

**TABLE 3-1: PINOUT DESCRIPTIONS**

|             | Р          | IC17C75     | ΣX          | PIC17       | 7C76X      |                    |                |                                                                                                                                                                                                                                               |

|-------------|------------|-------------|-------------|-------------|------------|--------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name        | DIP<br>No. | PLCC<br>No. | TQFP<br>No. | PLCC<br>No. | QFP<br>No. | I/O/P<br>Type      | Buffer<br>Type | Description                                                                                                                                                                                                                                   |

| OSC1/CLKIN  | 47         | 50          | 39          | 62          | 49         | I                  | ST             | Oscillator input in Crystal/Resonator or RC Oscillator mode. External clock input in External Clock mode.                                                                                                                                     |

| OSC2/CLKOUT | 48         | 51          | 40          | 63          | 50         | 0                  | ı              | Oscillator output. Connects to crystal or resonator in Crystal Oscillator mode. In RC Oscillator or External Clock modes, OSC2 pin outputs CLKOUT which has one fourth the frequency (Fosc/4) of OSC1 and denotes the instruction cycle rate. |

| MCLR/VPP    | 15         | 16          | 7           | 20          | 9          | I/P                | ST             | Master clear (RESET) input or Programming Voltage (VPP) input. This is the active low RESET input to the device.                                                                                                                              |

|             |            |             |             |             |            |                    |                | PORTA pins have individual differentiations that are listed in the following descriptions:                                                                                                                                                    |

| RA0/INT     | 56         | 60          | 48          | 72          | 58         | I                  | ST             | RA0 can also be selected as an external inter-<br>rupt input. Interrupt can be configured to be on<br>positive or negative edge. Input only pin.                                                                                              |

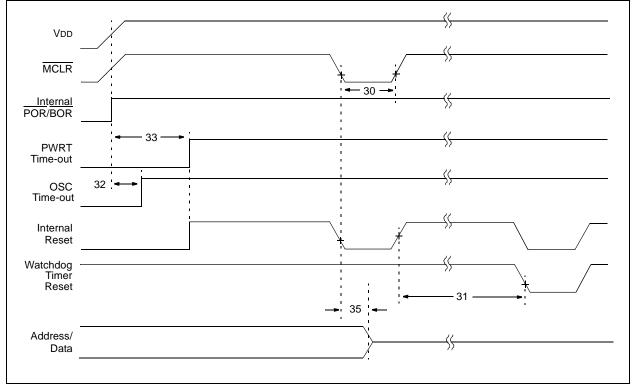

| RA1/T0CKI   | 41         | 44          | 33          | 56          | 43         | I                  | ST             | RA1 can also be selected as an external inter-<br>rupt input and the interrupt can be configured to<br>be on positive or negative edge. RA1 can also<br>be selected to be the clock input to the Timer0<br>timer/counter. Input only pin.     |

| RA2/SS/SCL  | 42         | 45          | 34          | 57          | 44         | I/O <sup>(2)</sup> | ST             | RA2 can also be used as the slave select input for the SPI or the clock input for the I <sup>2</sup> C bus. High voltage, high current, open drain port pin.                                                                                  |

| RA3/SDI/SDA | 43         | 46          | 35          | 58          | 45         | I/O <sup>(2)</sup> | ST             | RA3 can also be used as the data input for the SPI or the data for the I <sup>2</sup> C bus. High voltage, high current, open drain port pin.                                                                                                 |

| RA4/RX1/DT1 | 40         | 43          | 32          | 51          | 38         | I/O <sup>(1)</sup> | ST             | RA4 can also be selected as the USART1 (SCI) Asynchronous Receive or USART1 (SCI) Synchronous Data. Output available from USART only.                                                                                                         |

| RA5/TX1/CK1 | 39         | 42          | 31          | 50          | 37         | I/O <sup>(1)</sup> | ST             | RA5 can also be selected as the USART1 (SCI) Asynchronous Transmit or USART1 (SCI) Synchronous Clock. Output available from USART only.                                                                                                       |

|             |            |             |             |             |            |                    |                | PORTB is a bi-directional I/O Port with software configurable weak pull-ups.                                                                                                                                                                  |

| RB0/CAP1    | 55         | 59          | 47          | 71          | 57         | I/O                | ST             | RB0 can also be the Capture1 input pin.                                                                                                                                                                                                       |

| RB1/CAP2    | 54         | 58          | 46          | 70          | 56         | I/O                | ST             | RB1 can also be the Capture2 input pin.                                                                                                                                                                                                       |

| RB2/PWM1    | 50         | 54          | 42          | 66          | 52         | I/O                | ST             | RB2 can also be the PWM1 output pin.                                                                                                                                                                                                          |

| RB3/PWM2    | 53         | 57          | 45          | 69          | 55         | I/O                | ST             | RB3 can also be the PWM2 output pin.                                                                                                                                                                                                          |

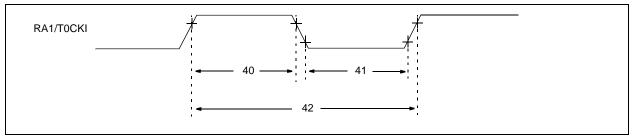

| RB4/TCLK12  | 52         | 56          | 44          | 68          | 54         | I/O                | ST             | RB4 can also be the external clock input to Timer1 and Timer2.                                                                                                                                                                                |

| RB5/TCLK3   | 51         | 55          | 43          | 67          | 53         | I/O                | ST             | RB5 can also be the external clock input to Timer3.                                                                                                                                                                                           |

| RB6/SCK     | 44         | 47          | 36          | 59          | 46         | I/O                | ST             | RB6 can also be used as the master/slave clock for the SPI.                                                                                                                                                                                   |

| RB7/SDO     | 45         | 48          | 37          | 60          | 47         | I/O                | ST             | RB7 can also be used as the data output for the SPI.                                                                                                                                                                                          |

Legend: I = Input only; O = Output only;

P = Power;

— = Not Used;

I/O = Input/Output;

TTL = TTL input;

ST = Schmitt Trigger input

**Note 1:** The output is only available by the peripheral operation.

2: Open drain input/output pin. Pin forced to input upon any device RESET.

TABLE 3-1: PINOUT DESCRIPTIONS (CONTINUED)

|          | P          | IC17C75     | X           | PIC17       | 7C76X      |               |                |                                                                                                                                                                     |

|----------|------------|-------------|-------------|-------------|------------|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | DIP<br>No. | PLCC<br>No. | TQFP<br>No. | PLCC<br>No. | QFP<br>No. | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                         |

|          |            |             |             |             |            |               |                | PORTC is a bi-directional I/O Port.                                                                                                                                 |

| RC0/AD0  | 2          | 3           | 58          | 3           | 72         | I/O           | TTL            | This is also the least significant byte (LSB) of                                                                                                                    |

| RC1/AD1  | 63         | 67          | 55          | 83          | 69         | I/O           | TTL            | the 16-bit wide system bus in Microprocessor                                                                                                                        |

| RC2/AD2  | 62         | 66          | 54          | 82          | 68         | I/O           | TTL            | mode or Extended Microcontroller mode. In                                                                                                                           |

| RC3/AD3  | 61         | 65          | 53          | 81          | 67         | I/O           | TTL            | multiplexed system bus configuration, these pins are address output as well as data input or                                                                        |

| RC4/AD4  | 60         | 64          | 52          | 80          | 66         | I/O           | TTL            | output.                                                                                                                                                             |

| RC5/AD5  | 58         | 63          | 51          | 79          | 65         | I/O           | TTL            |                                                                                                                                                                     |

| RC6/AD6  | 58         | 62          | 50          | 78          | 64         | I/O           | TTL            |                                                                                                                                                                     |

| RC7/AD7  | 57         | 61          | 49          | 77          | 63         | I/O           | TTL            |                                                                                                                                                                     |

|          |            |             |             |             |            |               |                | PORTD is a bi-directional I/O Port.                                                                                                                                 |

| RD0/AD8  | 10         | 11          | 2           | 15          | 4          | I/O           | TTL            | This is also the most significant byte (MSB) of                                                                                                                     |

| RD1/AD9  | 9          | 10          | 1           | 14          | 3          | I/O           | TTL            | the 16-bit system bus in Microprocessor mode                                                                                                                        |

| RD2/AD10 | 8          | 9           | 64          | 9           | 78         | I/O           | TTL            | or Extended Microcontroller mode. In multi-                                                                                                                         |

| RD3/AD11 | 7          | 8           | 63          | 8           | 77         | I/O           | TTL            | plexed system bus configuration, these pins are address output as well as data input or output.                                                                     |

| RD4/AD12 | 6          | 7           | 62          | 7           | 76         | I/O           | TTL            | address output as well as data input of output.                                                                                                                     |

| RD5/AD13 | 5          | 6           | 61          | 6           | 75         | I/O           | TTL            |                                                                                                                                                                     |

| RD6/AD14 | 4          | 5           | 60          | 5           | 74         | I/O           | TTL            |                                                                                                                                                                     |

| RD7/AD15 | 3          | 4           | 59          | 4           | 73         | I/O           | TTL            |                                                                                                                                                                     |

|          |            |             |             |             |            |               |                | PORTE is a bi-directional I/O Port.                                                                                                                                 |

| RE0/ALE  | 11         | 12          | 3           | 16          | 5          | I/O           | TTL            | In Microprocessor mode or Extended Microcontroller mode, RE0 is the Address Latch Enable (ALE) output. Address should be latched on the falling edge of ALE output. |

| RE1/OE   | 12         | 13          | 4           | 17          | 6          | I/O           | TTL            | In Microprocessor or Extended Microcontroller mode, RE1 is the Output Enable (OE) control output (active low).                                                      |

| RE2/WR   | 13         | 14          | 5           | 18          | 7          | I/O           | TTL            | In Microprocessor or Extended Microcontroller mode, RE2 is the Write Enable (WR) control output (active low).                                                       |

| RE3/CAP4 | 14         | 15          | 6           | 19          | 8          | I/O           | ST             | RE3 can also be the Capture4 input pin.                                                                                                                             |

|          |            |             |             |             |            |               |                | PORTF is a bi-directional I/O Port.                                                                                                                                 |

| RF0/AN4  | 26         | 28          | 18          | 36          | 24         | I/O           | ST             | RF0 can also be analog input 4.                                                                                                                                     |

| RF1/AN5  | 25         | 27          | 17          | 35          | 23         | I/O           | ST             | RF1 can also be analog input 5.                                                                                                                                     |

| RF2/AN6  | 24         | 26          | 16          | 30          | 18         | I/O           | ST             | RF2 can also be analog input 6.                                                                                                                                     |

| RF3/AN7  | 23         | 25          | 15          | 29          | 17         | I/O           | ST             | RF3 can also be analog input 7.                                                                                                                                     |

| RF4/AN8  | 22         | 24          | 14          | 28          | 16         | I/O           | ST             | RF4 can also be analog input 8.                                                                                                                                     |

| RF5/AN9  | 21         | 23          | 13          | 27          | 15         | I/O           | ST             | RF5 can also be analog input 9.                                                                                                                                     |

| RF6/AN10 | 20         | 22          | 12          | 26          | 14         | I/O           | ST             | RF6 can also be analog input 10.                                                                                                                                    |

| RF7/AN11 | 19         | 21          | 11          | 25          | 13         | I/O           | ST             | RF7 can also be analog input 11.                                                                                                                                    |

ST = Schmitt Trigger input

**Note 1:** The output is only available by the peripheral operation.

2: Open drain input/output pin. Pin forced to input upon any device RESET.

PINOUT DESCRIPTIONS (CONTINUED) **TABLE 3-1:**

|                   |                                                                       |                                                                                                                                                                                                                          | PIC17                                                                                                                                                                                                                                                                                                                                                 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP<br>No.        | PLCC<br>No.                                                           | TQFP<br>No.                                                                                                                                                                                                              | PLCC<br>No.                                                                                                                                                                                                                                                                                                                                           | QFP<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O/P<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

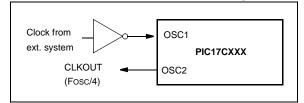

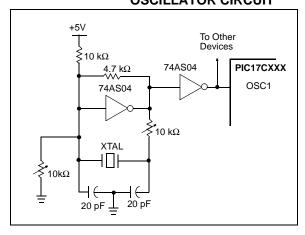

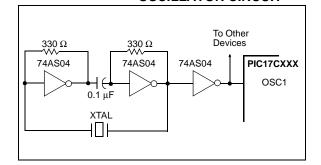

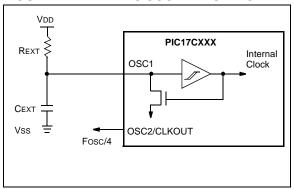

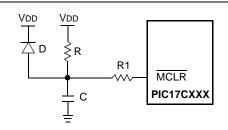

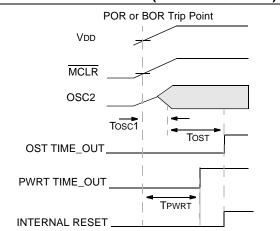

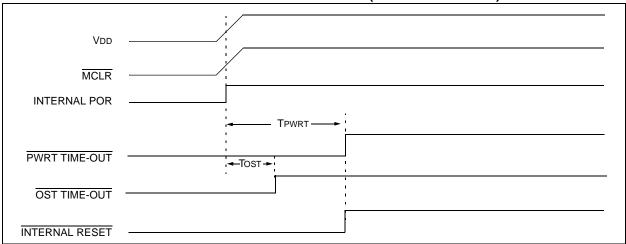

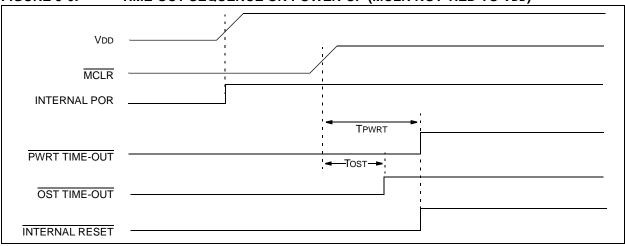

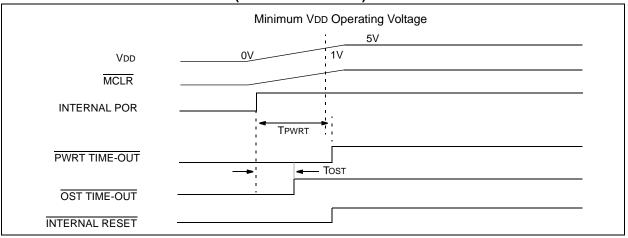

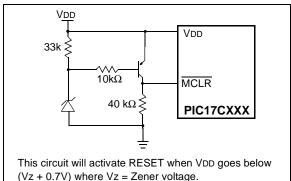

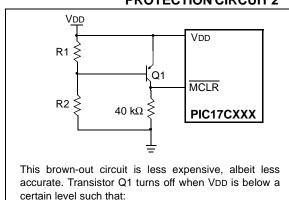

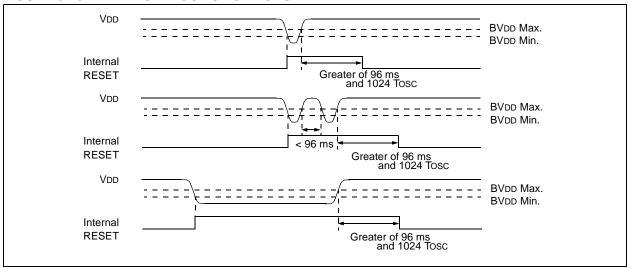

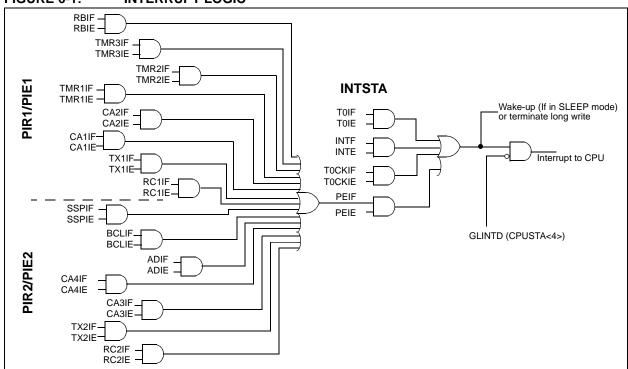

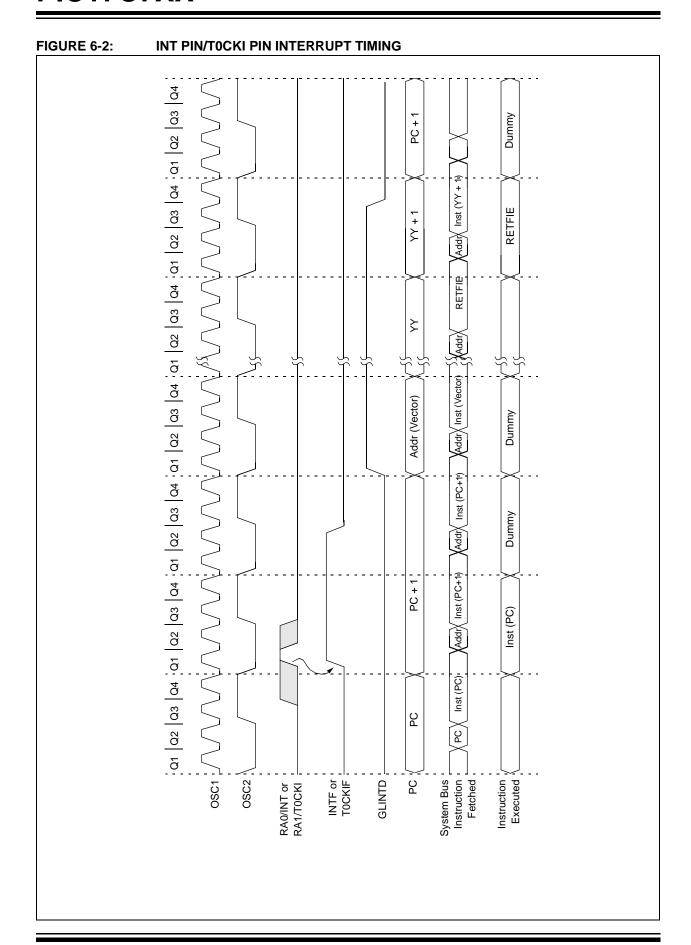

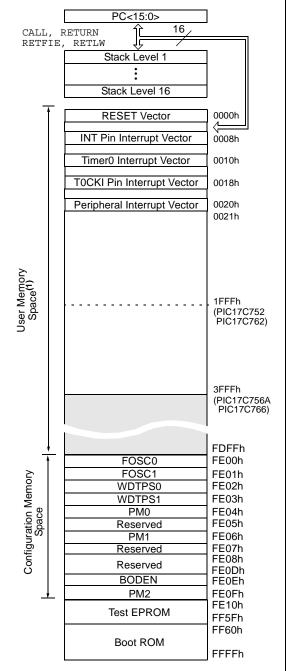

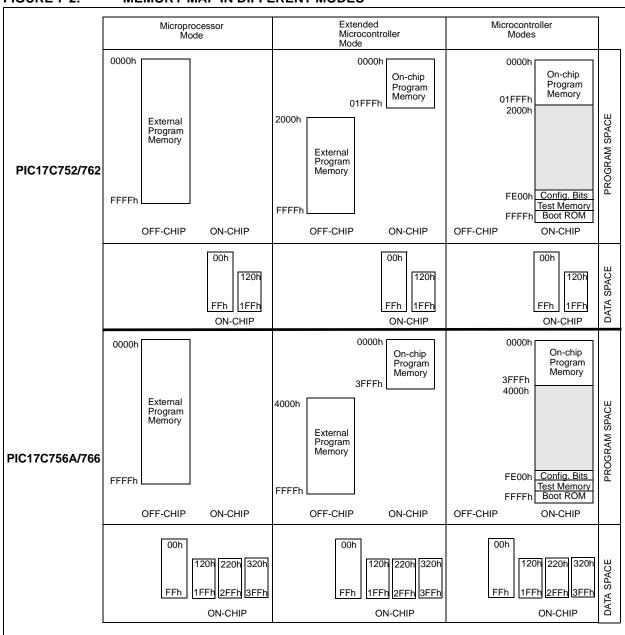

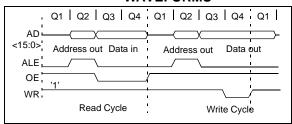

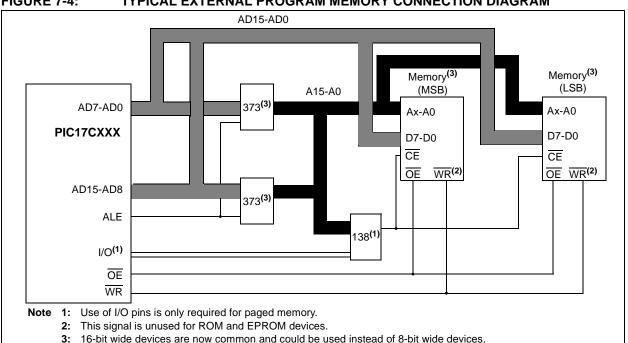

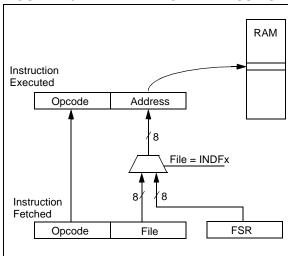

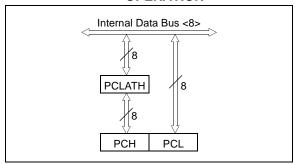

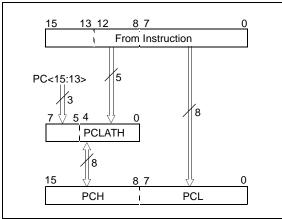

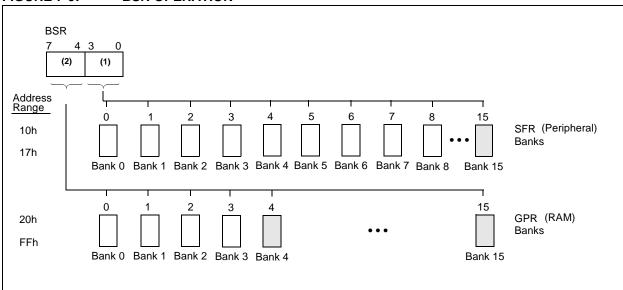

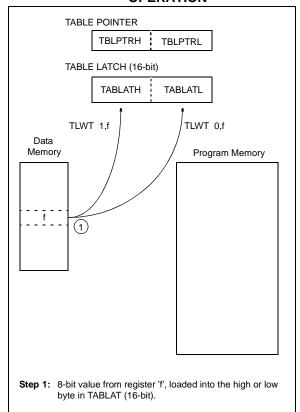

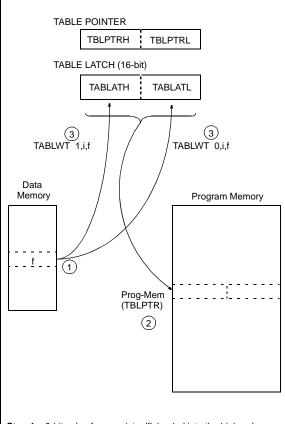

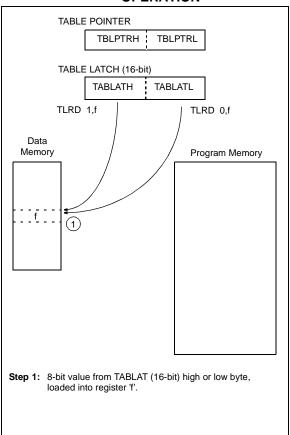

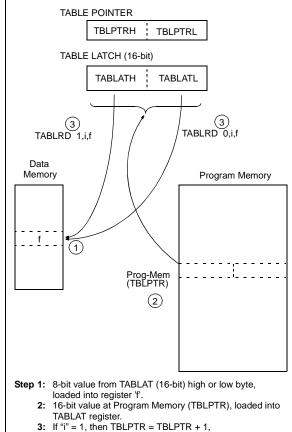

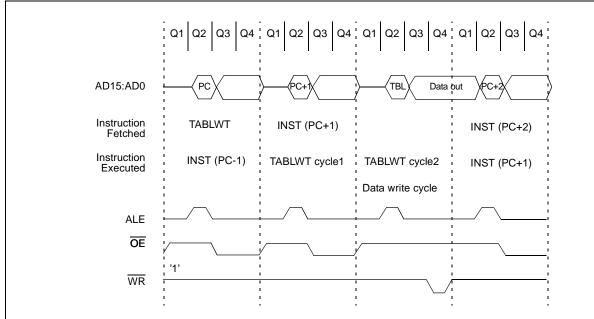

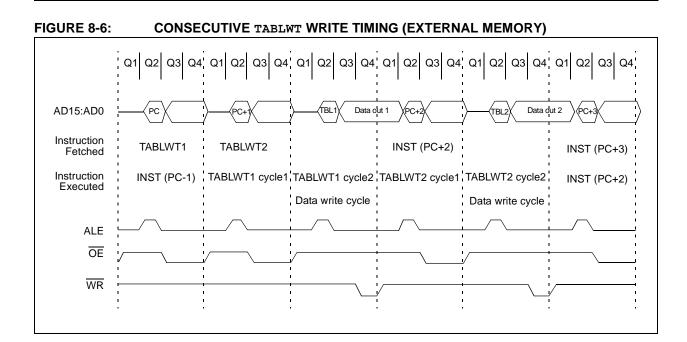

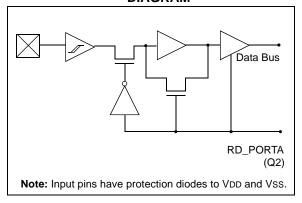

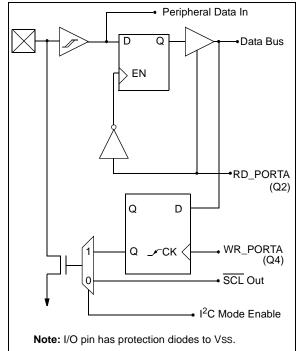

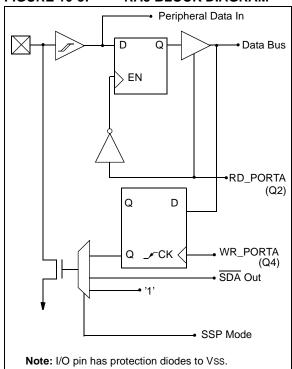

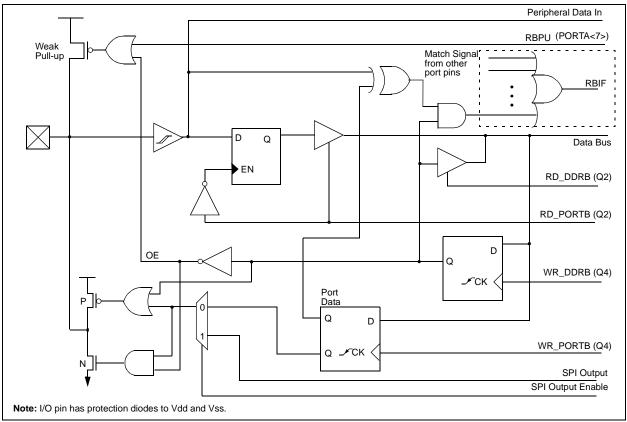

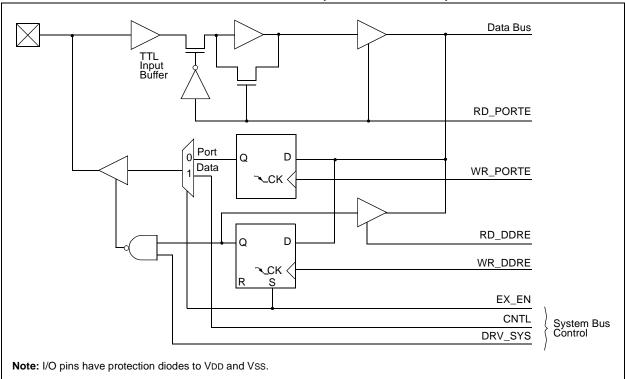

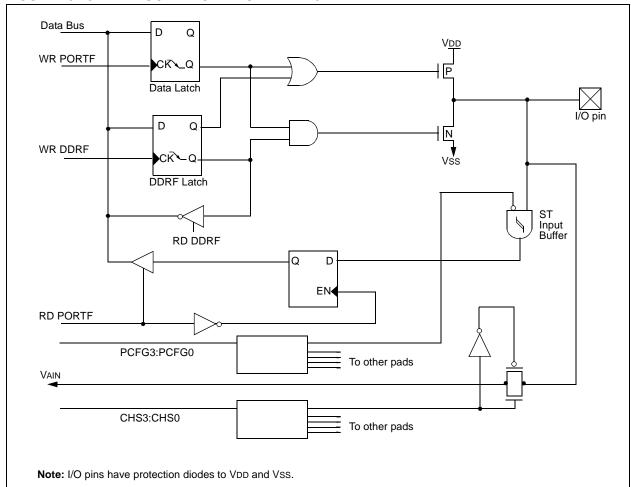

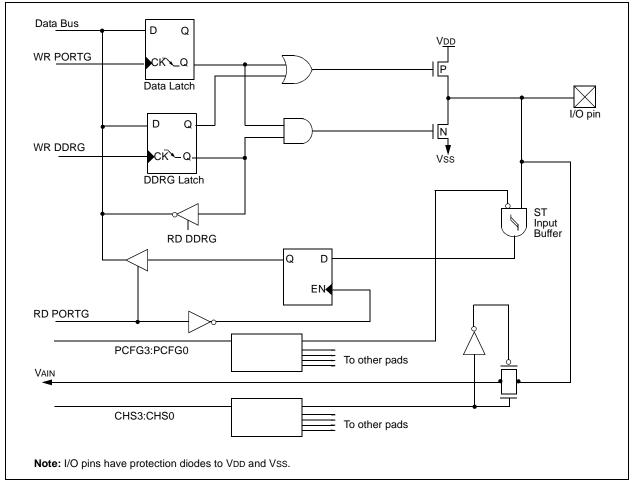

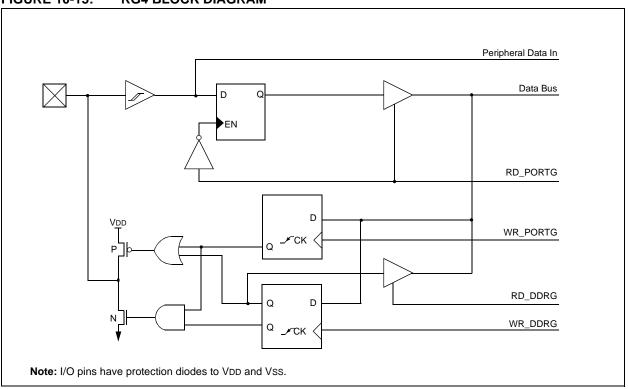

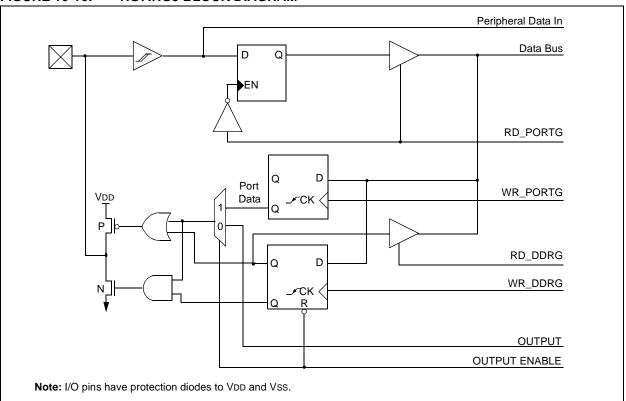

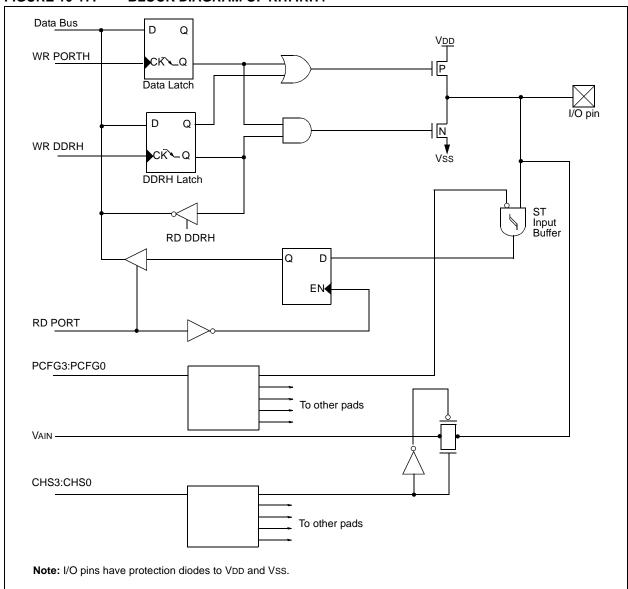

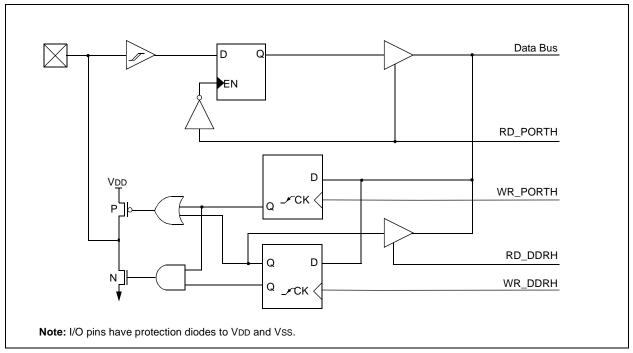

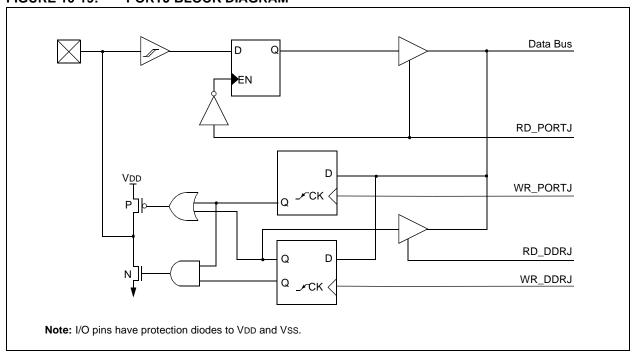

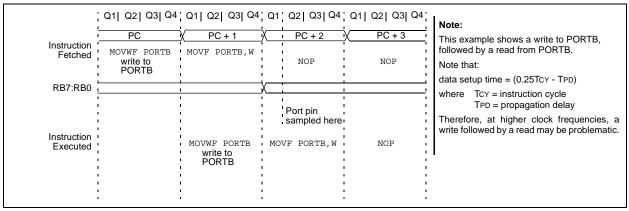

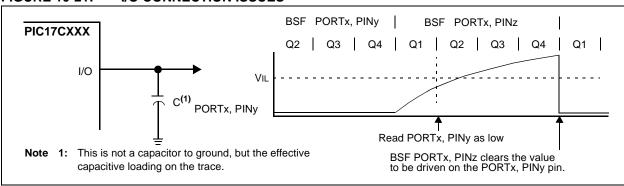

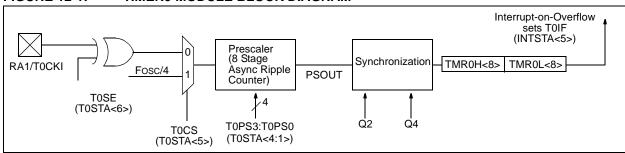

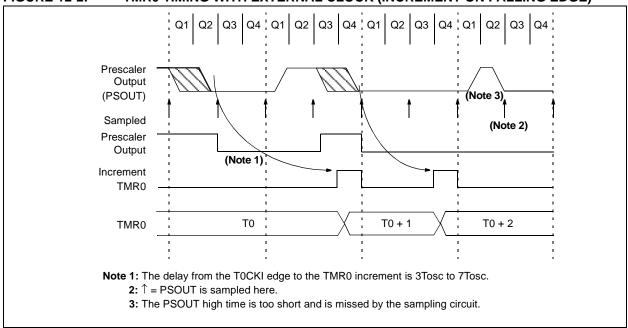

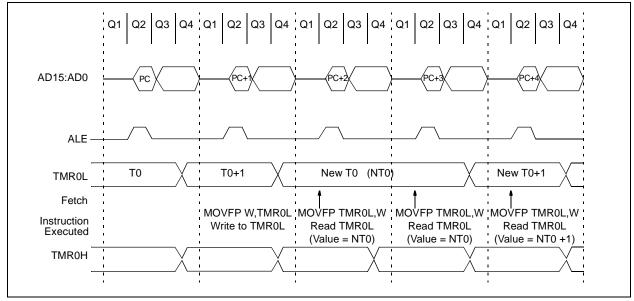

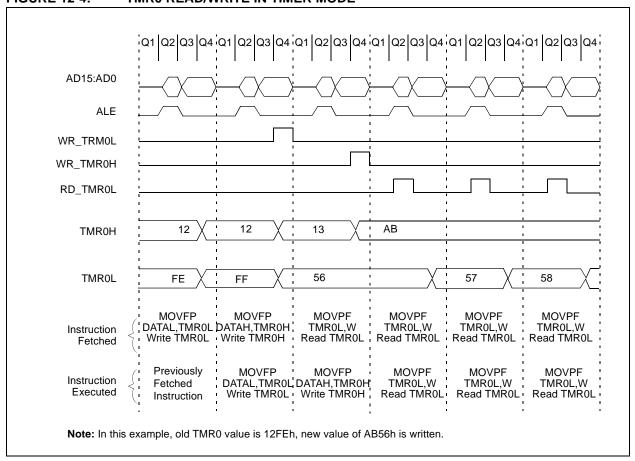

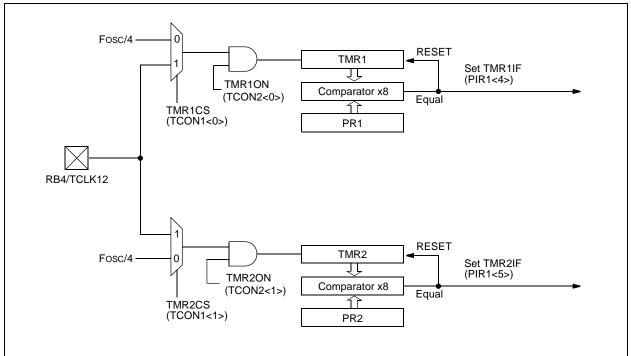

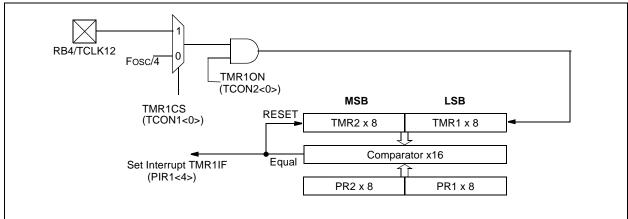

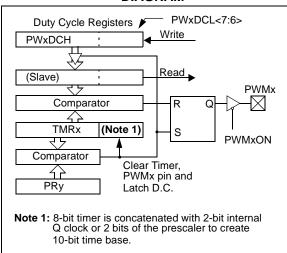

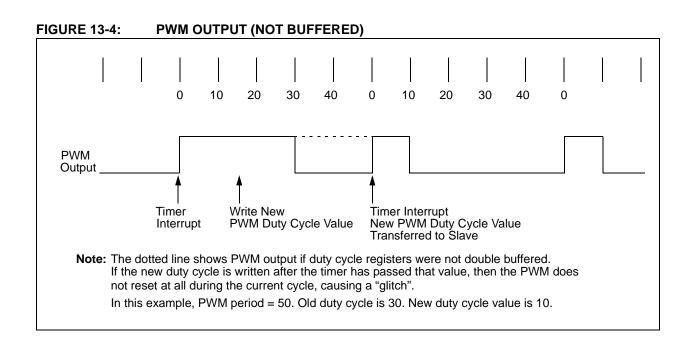

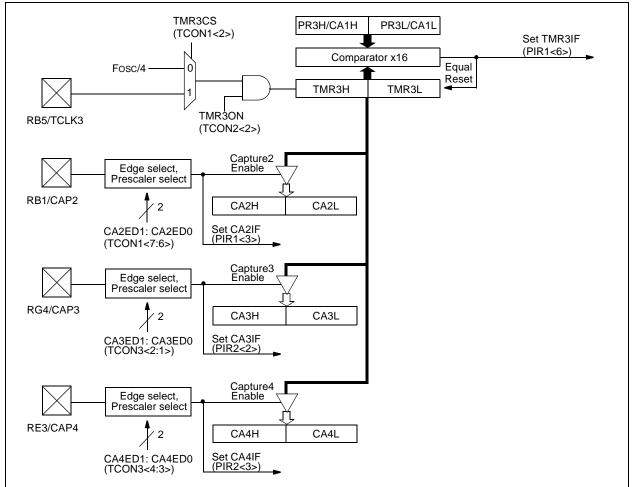

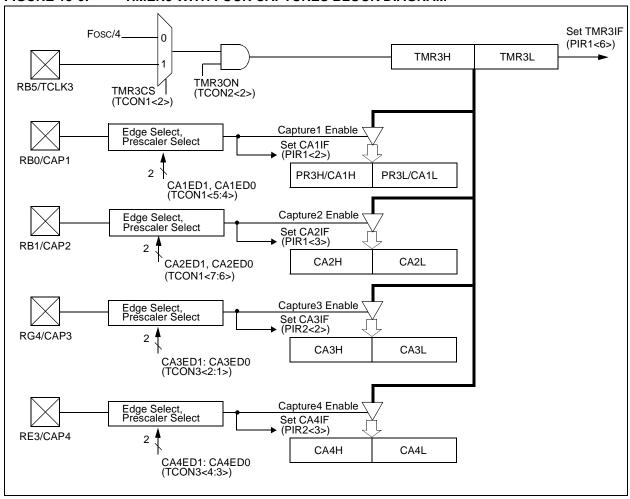

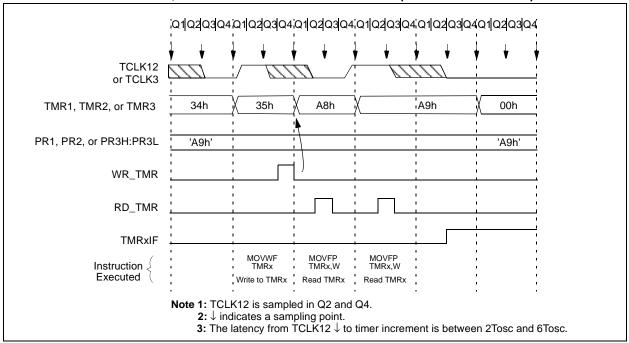

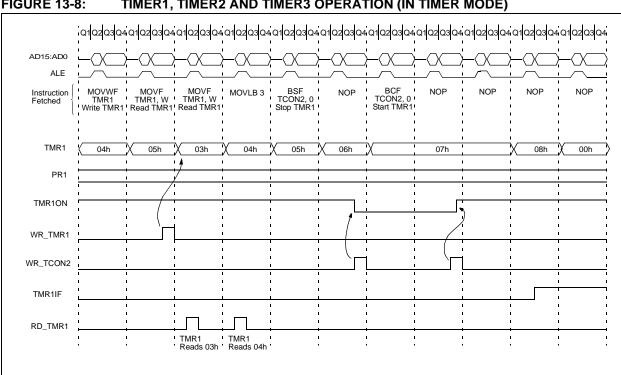

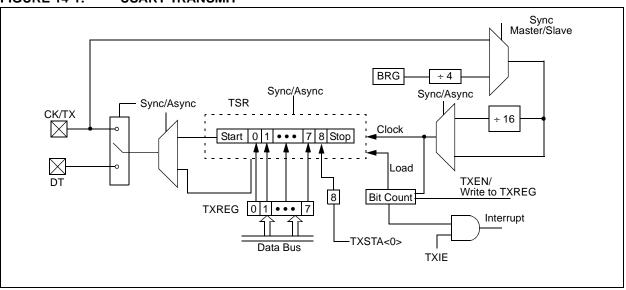

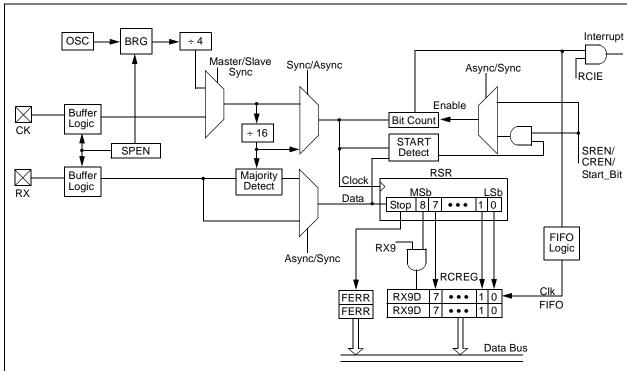

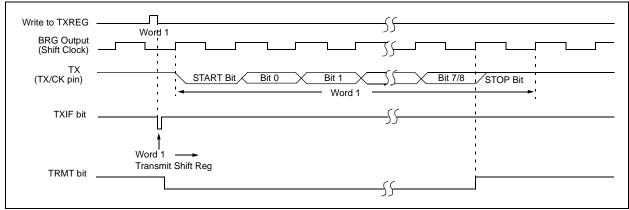

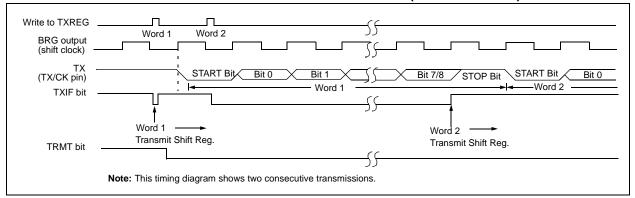

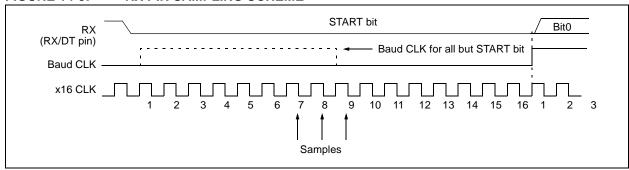

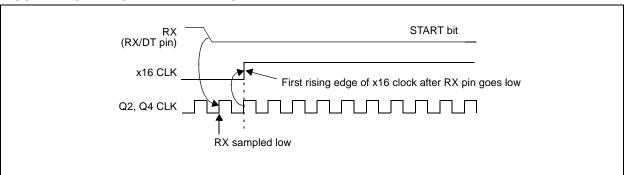

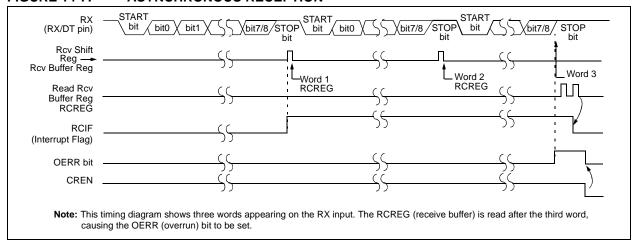

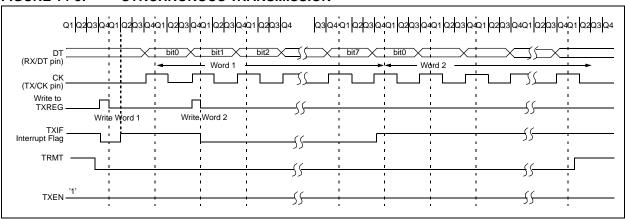

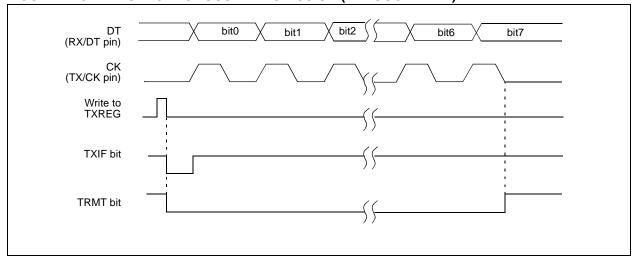

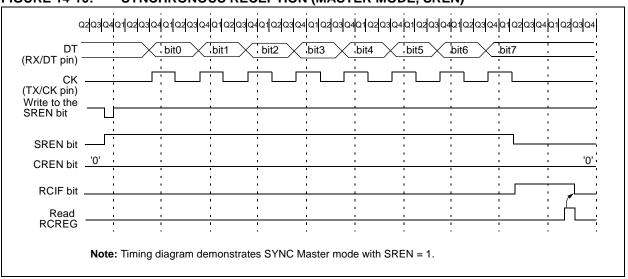

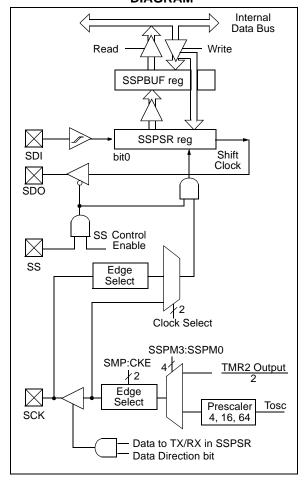

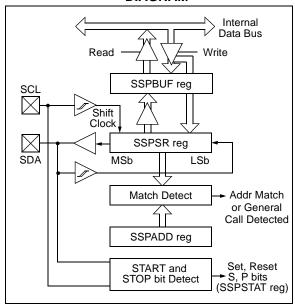

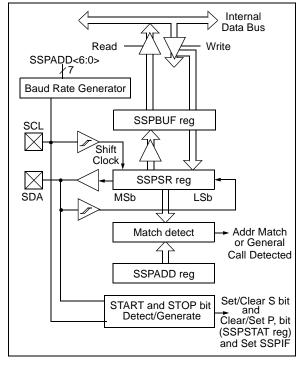

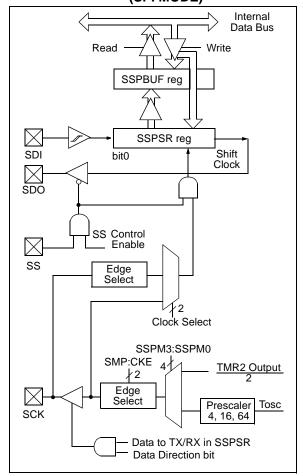

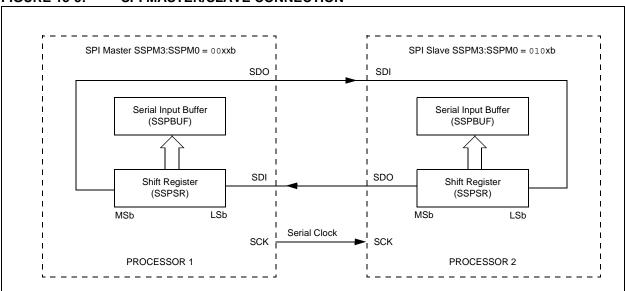

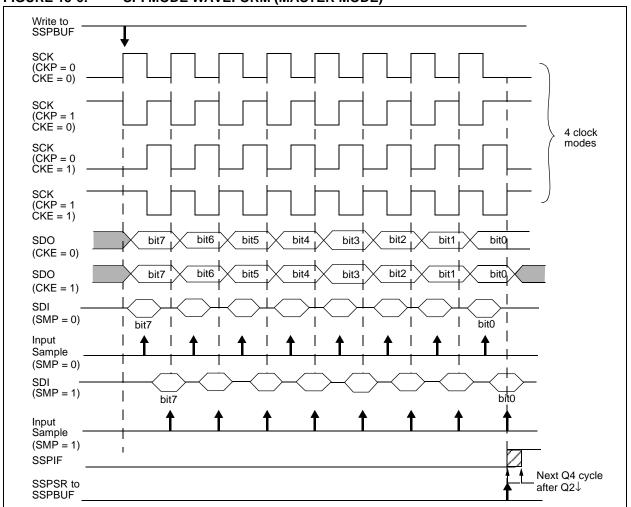

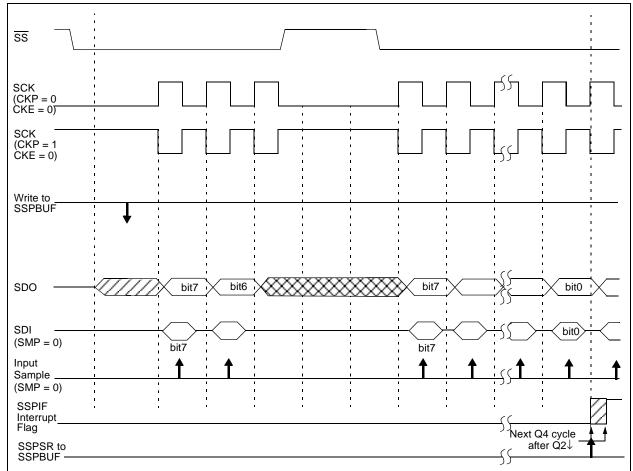

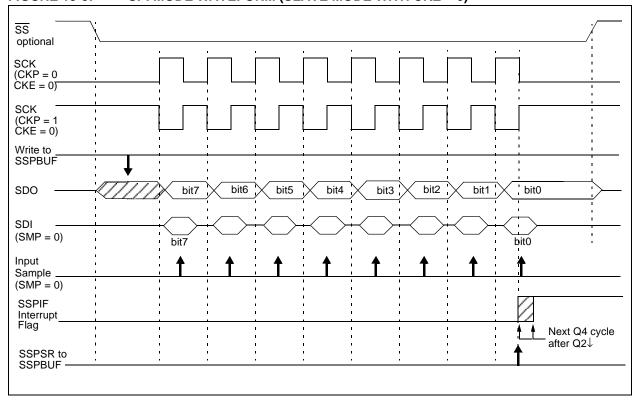

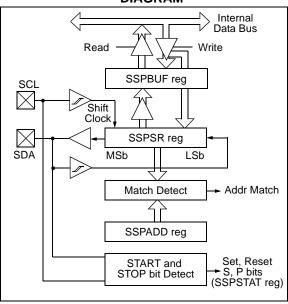

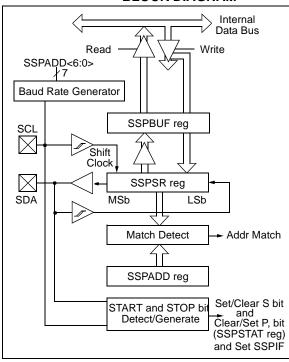

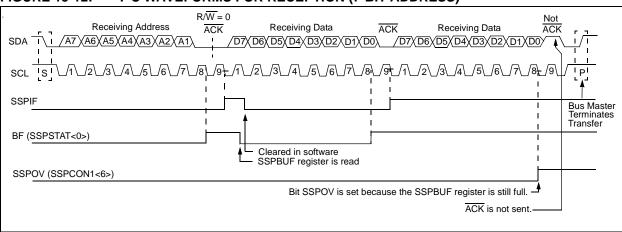

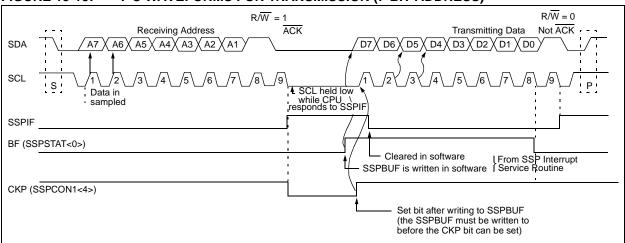

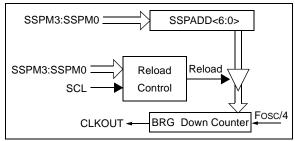

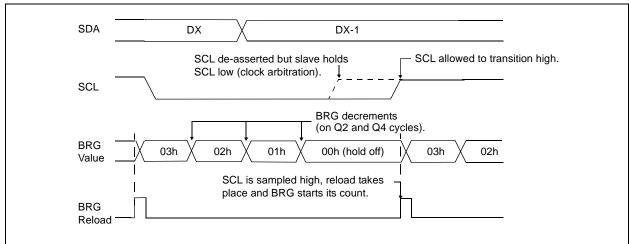

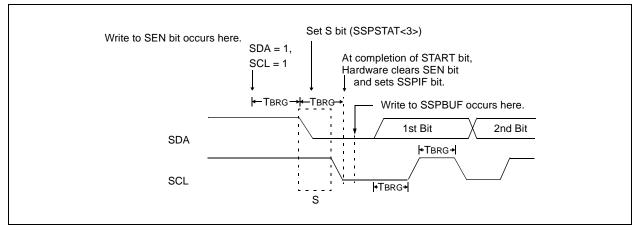

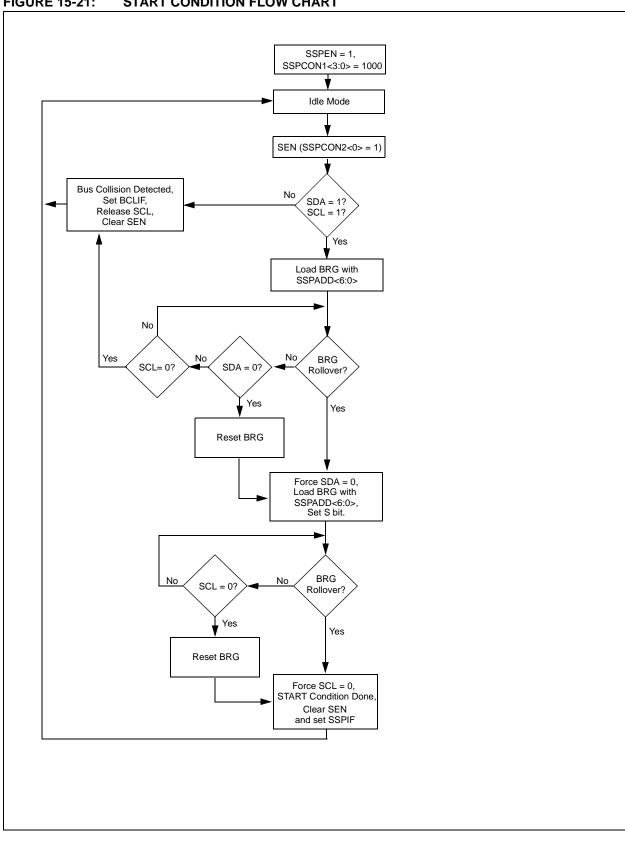

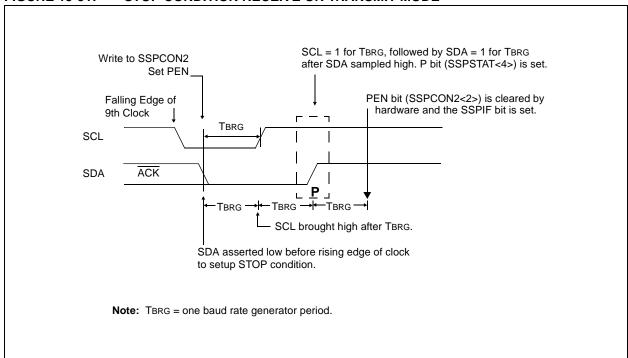

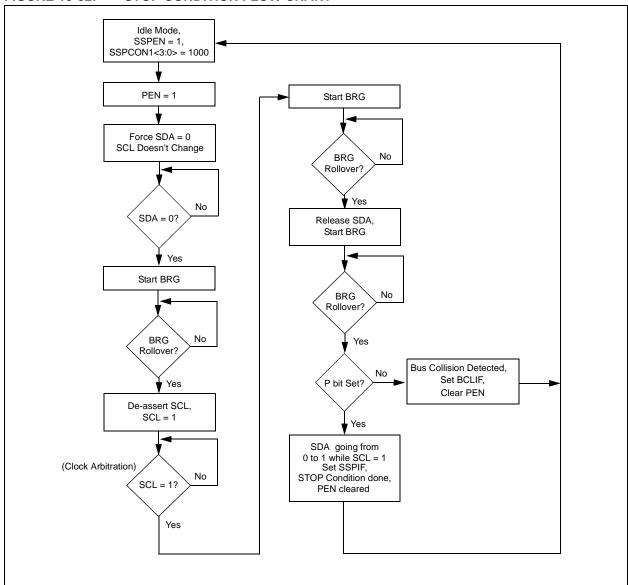

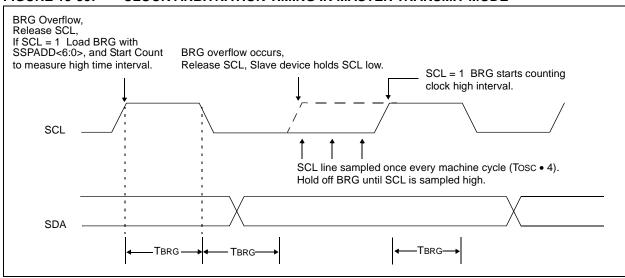

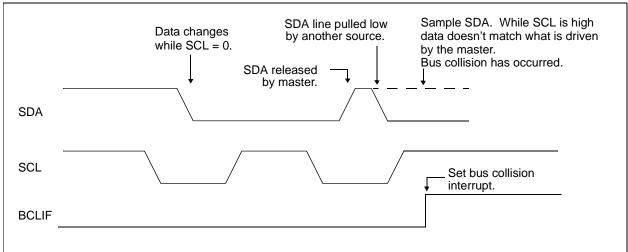

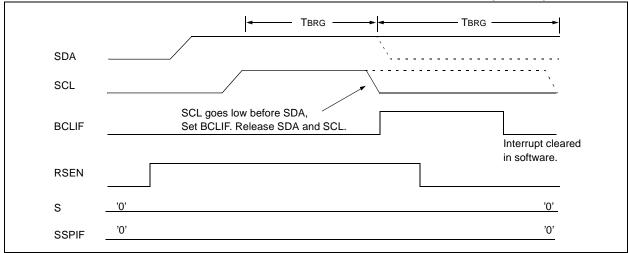

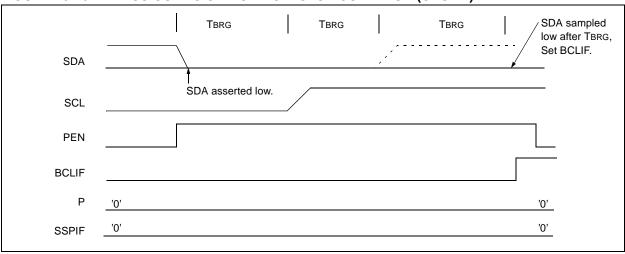

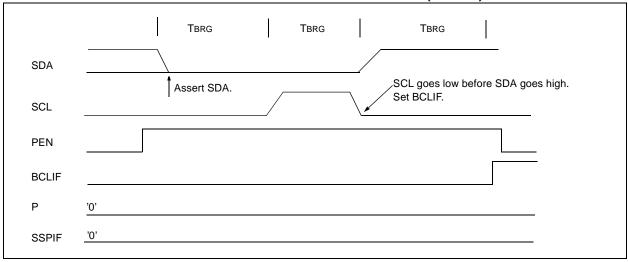

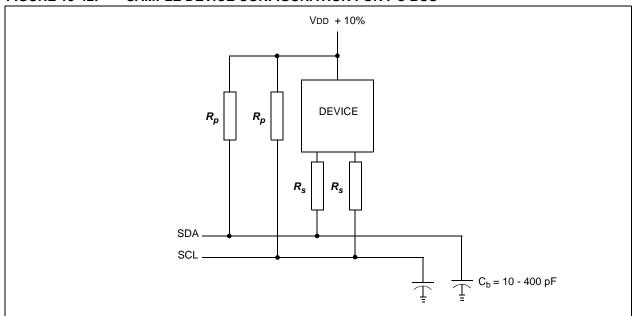

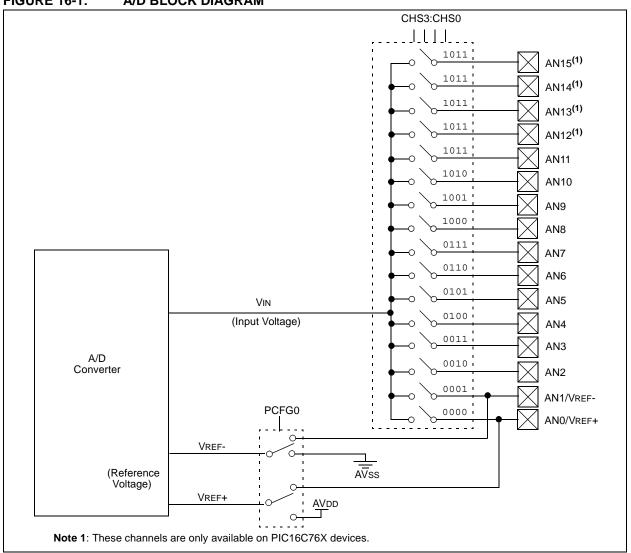

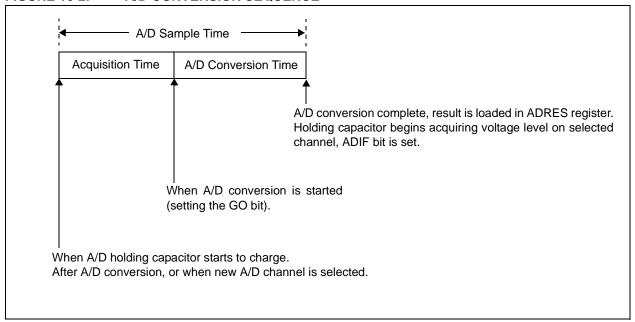

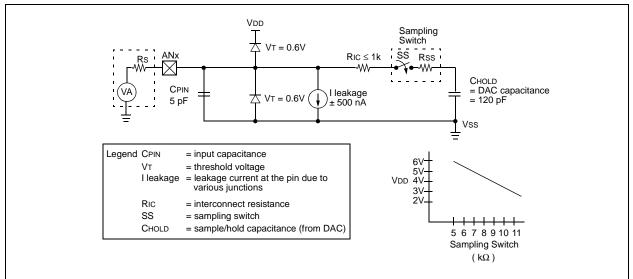

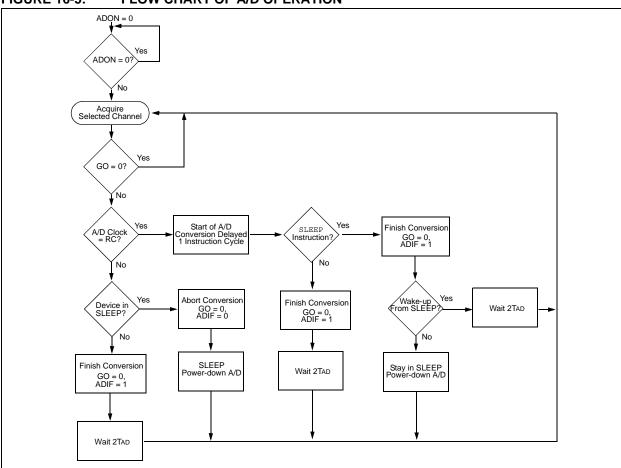

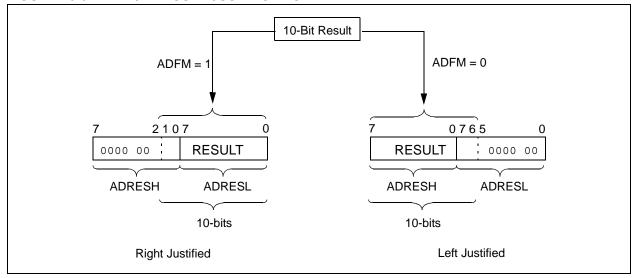

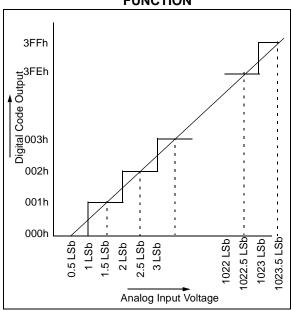

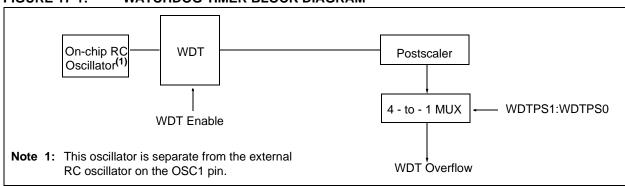

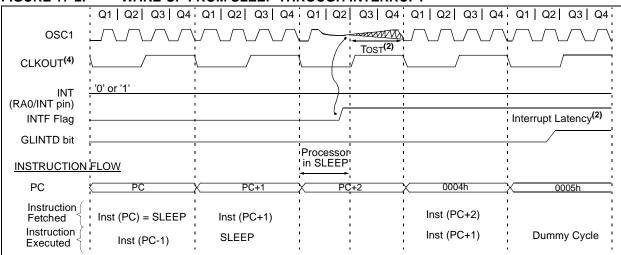

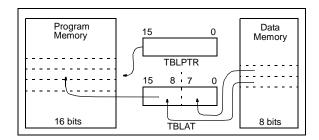

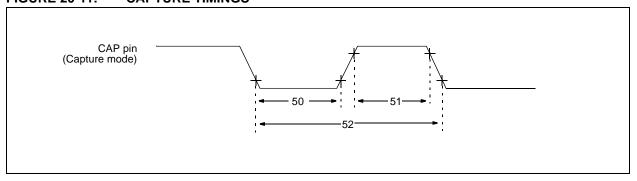

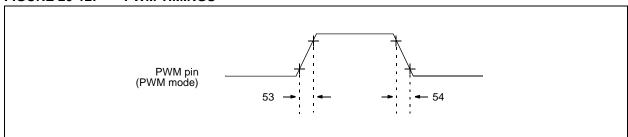

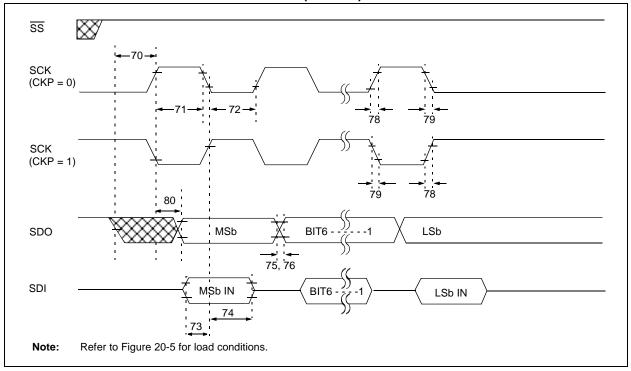

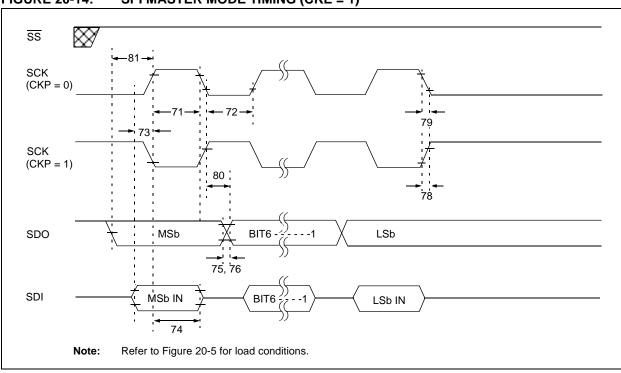

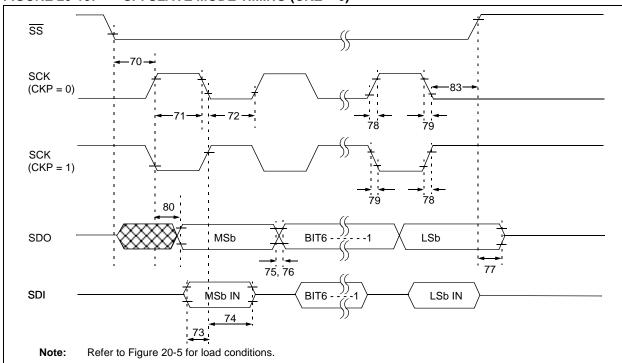

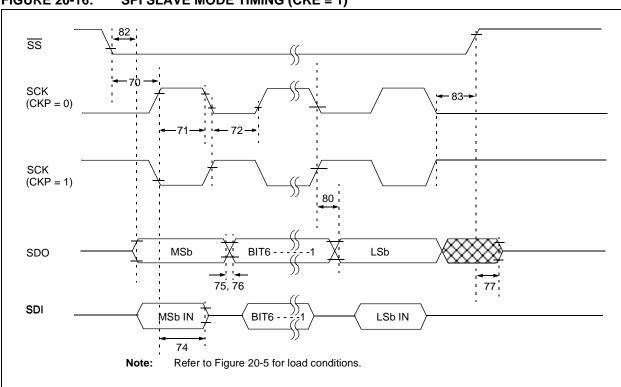

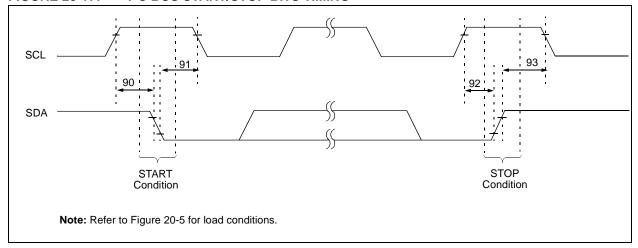

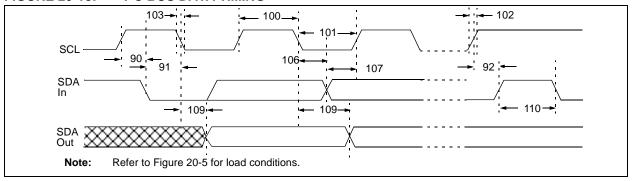

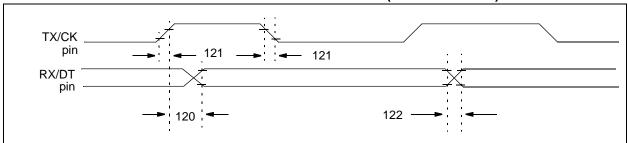

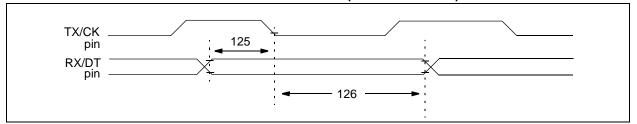

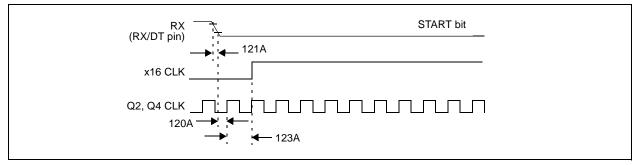

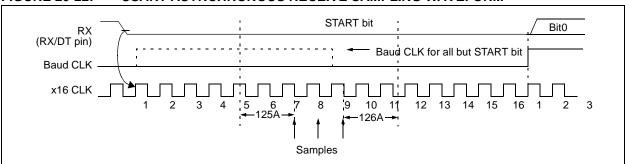

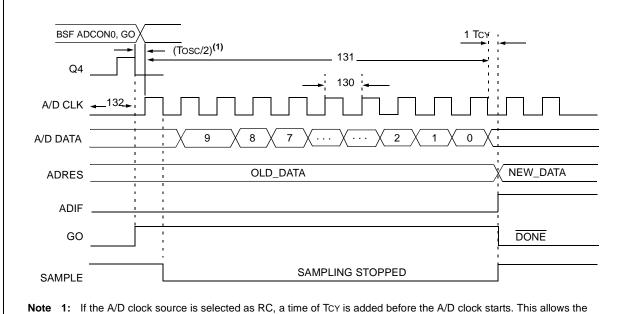

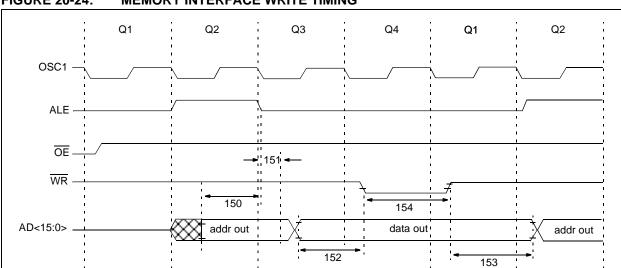

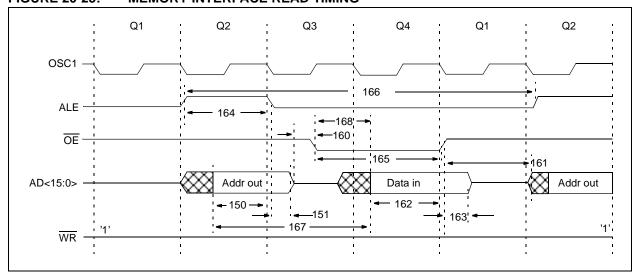

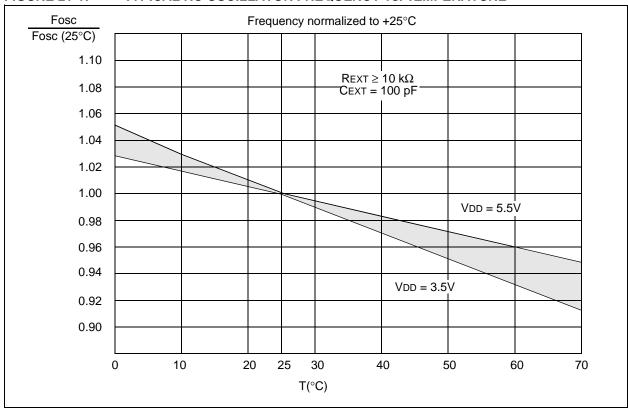

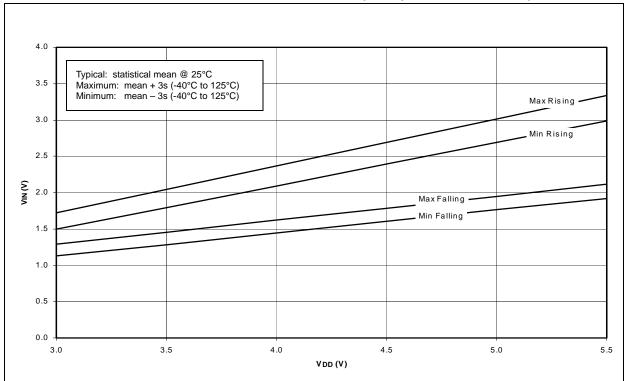

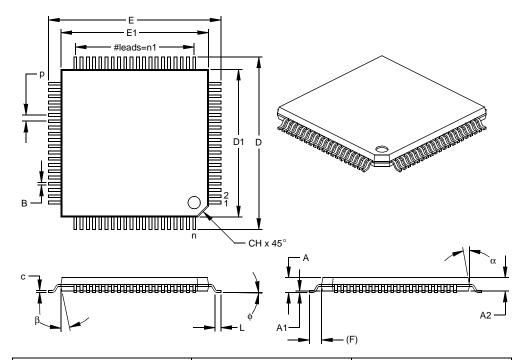

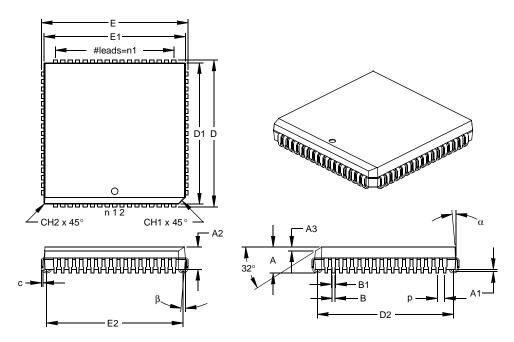

|                   |                                                                       |                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PORTG is a bi-directional I/O Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |