# PIC16F870/871 Data Sheet

28/40-Pin, 8-Bit CMOS FLASH Microcontrollers

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPIC, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELOO® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

## 28/40-Pin, 8-Bit CMOS FLASH Microcontrollers

### **Devices Included in this Data Sheet:**

- PIC16F870

- PIC16F871

#### Microcontroller Core Features:

- · High performance RISC CPU

- · Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two-cycle

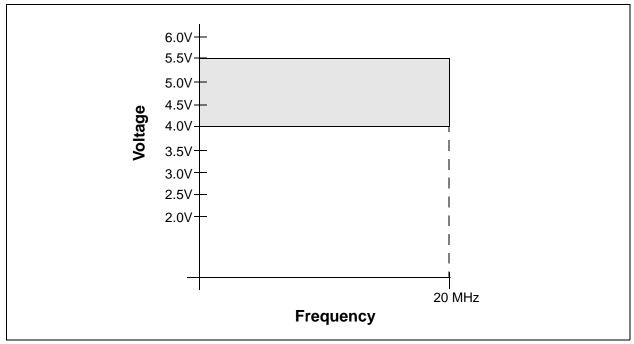

- Operating speed: DC 20 MHz clock input DC - 200 ns instruction cycle

- 2K x 14 words of FLASH Program Memory 128 x 8 bytes of Data Memory (RAM) 64 x 8 bytes of EEPROM Data Memory

- Pinout compatible to the PIC16CXXX 28 and 40-pin devices

- Interrupt capability (up to 11 sources)

- · Eight level deep hardware stack

- · Direct, Indirect and Relative Addressing modes

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

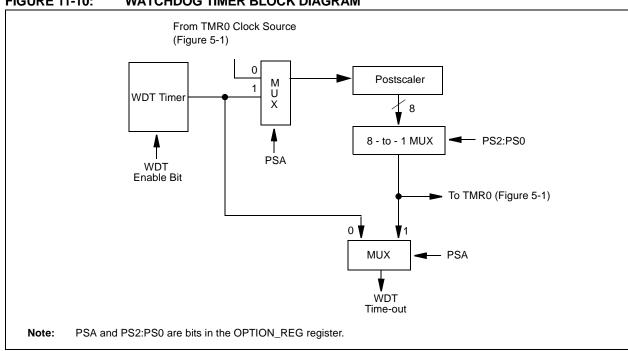

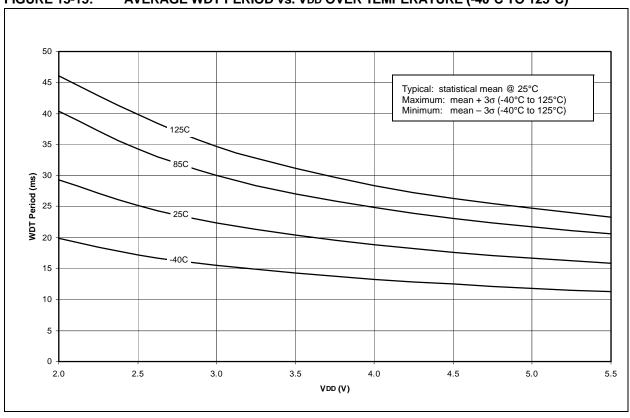

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code protection

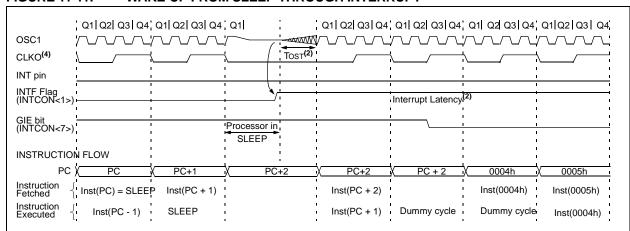

- Power saving SLEEP mode

- · Selectable oscillator options

- Low power, high speed CMOS FLASH/EEPROM technology

- Fully static design

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

- Single 5V In-Circuit Serial Programming capability

- · In-Circuit Debugging via two pins

- · Processor read/write access to program memory

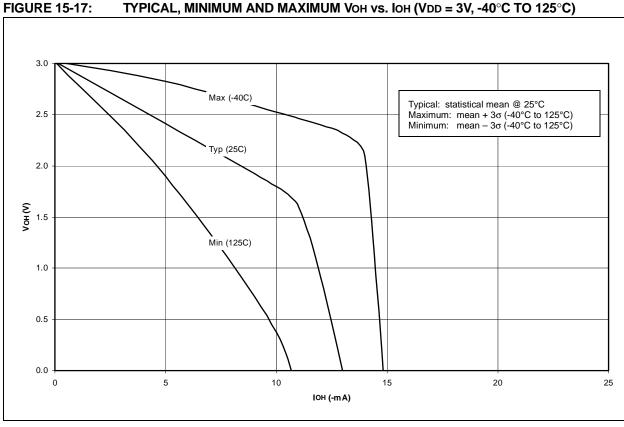

- Wide operating voltage range: 2.0V to 5.5V

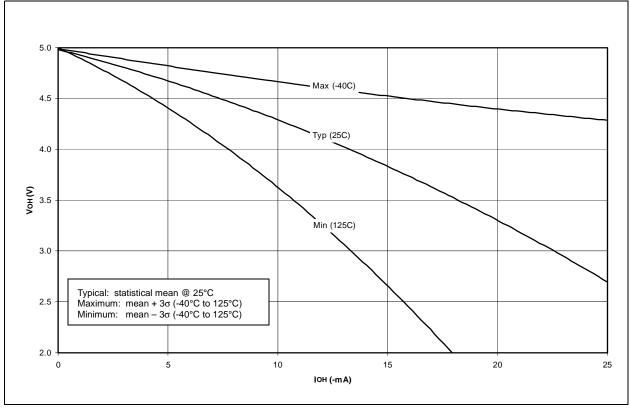

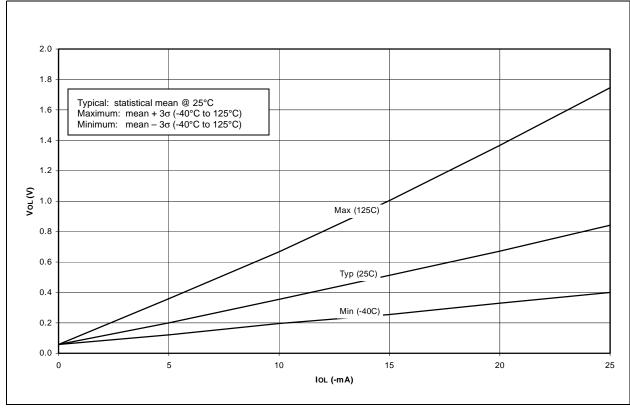

- High Sink/Source Current: 25 mA

- Commercial and Industrial temperature ranges

- Low power consumption:

- < 1.6 mA typical @ 5V, 4 MHz

- 20 μA typical @ 3V, 32 kHz

- < 1 μA typical standby current

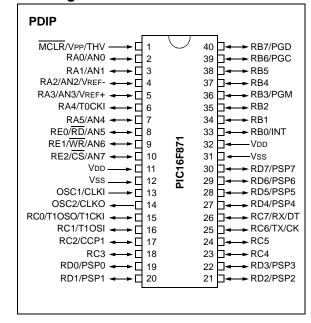

## Pin Diagram

## **Peripheral Features:**

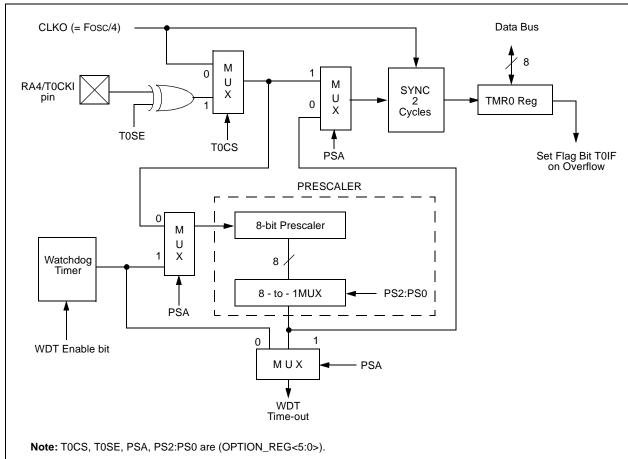

- Timer0: 8-bit timer/counter with 8-bit prescaler

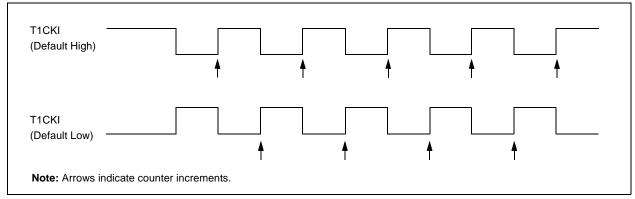

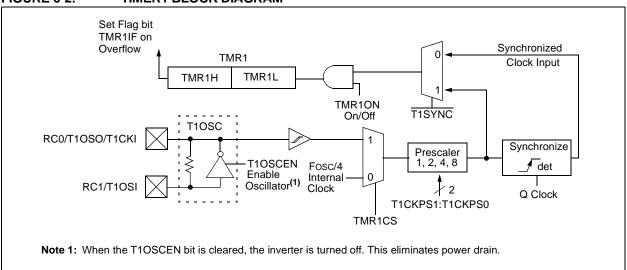

- Timer1: 16-bit timer/counter with prescaler, can be incremented during SLEEP via external crystal/clock

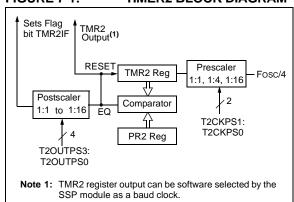

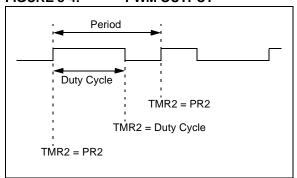

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

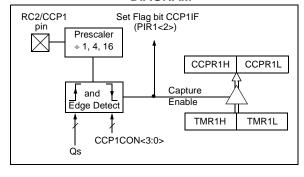

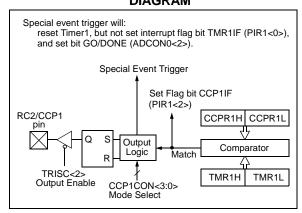

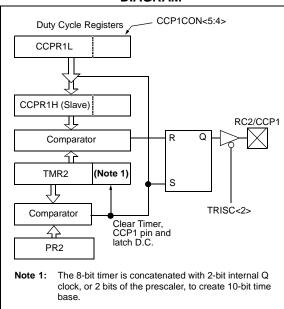

- · One Capture, Compare, PWM module

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

- PWM max. resolution is 10-bit

- 10-bit multi-channel Analog-to-Digital converter

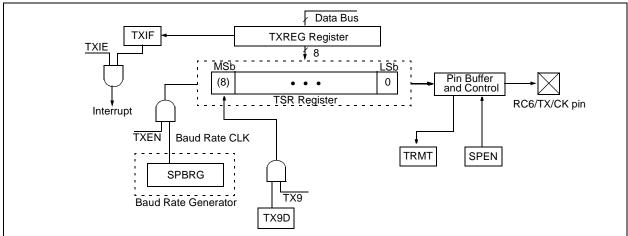

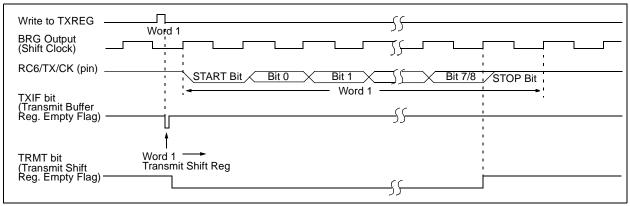

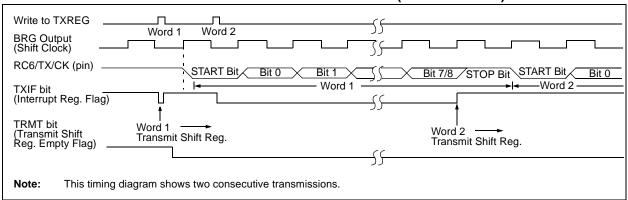

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI) with 9-bit address detection

- Parallel Slave Port (PSP) 8-bits wide, with external RD, WR and CS controls (40/44-pin only)

- Brown-out detection circuitry for Brown-out Reset (BOR)

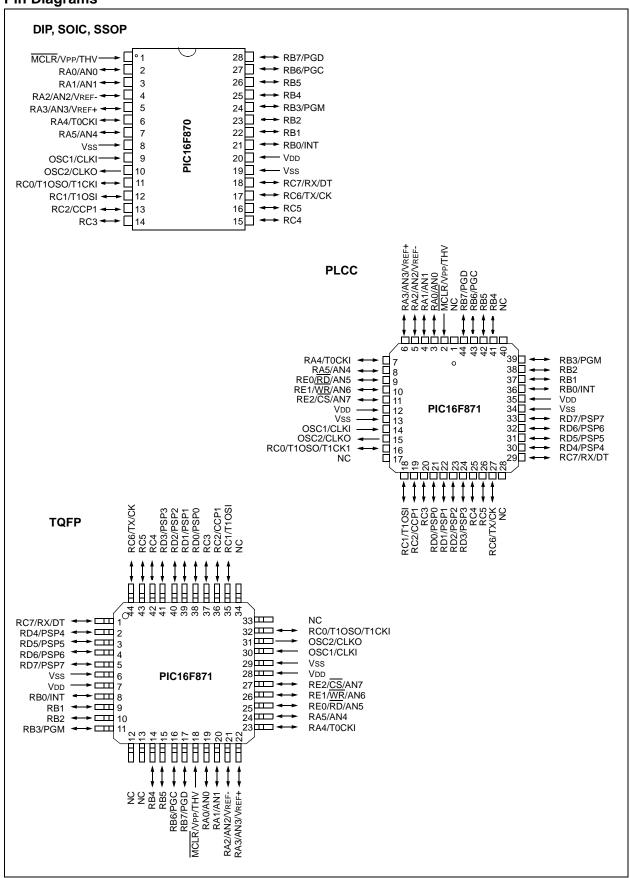

## **Pin Diagrams**

| Key Features<br>PICmicro™ Mid-Range MCU Family Reference Manual<br>(DS33023) | PIC16F870            | PIC16F871            |

|------------------------------------------------------------------------------|----------------------|----------------------|

| Operating Frequency                                                          | DC - 20 MHz          | DC - 20 MHz          |

| RESETS (and Delays)                                                          | POR, BOR (PWRT, OST) | POR, BOR (PWRT, OST) |

| FLASH Program Memory (14-bit words)                                          | 2K                   | 2K                   |

| Data Memory (bytes)                                                          | 128                  | 128                  |

| EEPROM Data Memory                                                           | 64                   | 64                   |

| Interrupts                                                                   | 10                   | 11                   |

| I/O Ports                                                                    | Ports A,B,C          | Ports A,B,C,D,E      |

| Timers                                                                       | 3                    | 3                    |

| Capture/Compare/PWM modules                                                  | 1                    | 1                    |

| Serial Communications                                                        | USART                | USART                |

| Parallel Communications                                                      | _                    | PSP                  |

| 10-bit Analog-to-Digital Module                                              | 5 input channels     | 8 input channels     |

| Instruction Set                                                              | 35 Instructions      | 35 Instructions      |

#### **Table of Contents**

| 1.0              | Device Overview                                                             | 5   |

|------------------|-----------------------------------------------------------------------------|-----|

| 2.0              | Memory Organization                                                         | 11  |

| 3.0              | Data EEPROM and Flash Program Memory                                        | 27  |

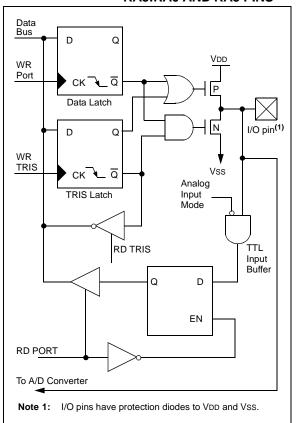

| 4.0              | I/O Ports                                                                   |     |

| 5.0              | Timer0 Module                                                               | 45  |

| 6.0              | Timer1 Module                                                               | 49  |

| 7.0              | Timer2 Module                                                               | 53  |

| 8.0              | Capture/Compare/PWM Modules                                                 | 55  |

| 9.0              | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) | 61  |

| 10.0             | Analog-to-Digital (A/D) Converter Module                                    | 79  |

| 11.0             | Special Features of the CPU                                                 | 87  |

| 12.0             | Instruction Set Summary                                                     | 103 |

| 13.0             | Development Support                                                         | 111 |

| 14.0             | Electrical Characteristics                                                  | 117 |

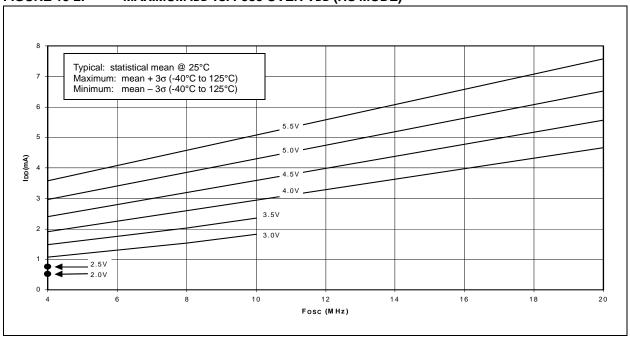

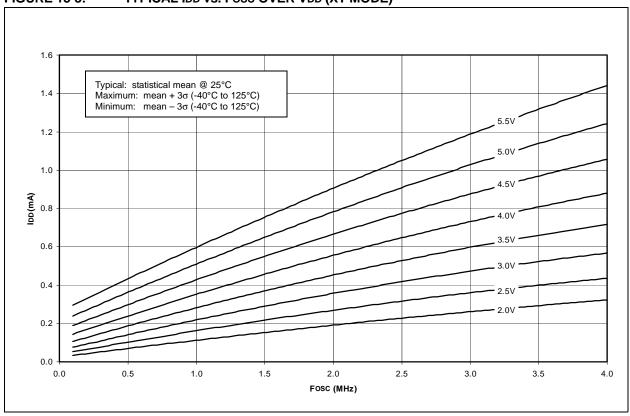

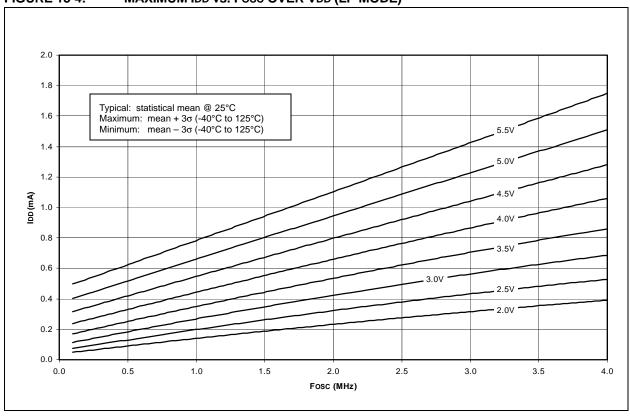

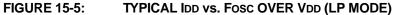

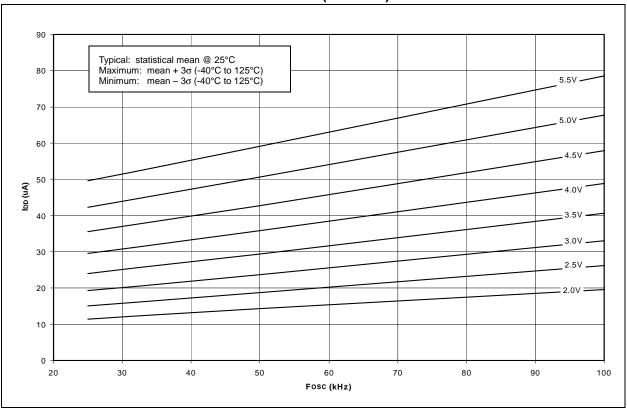

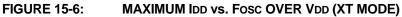

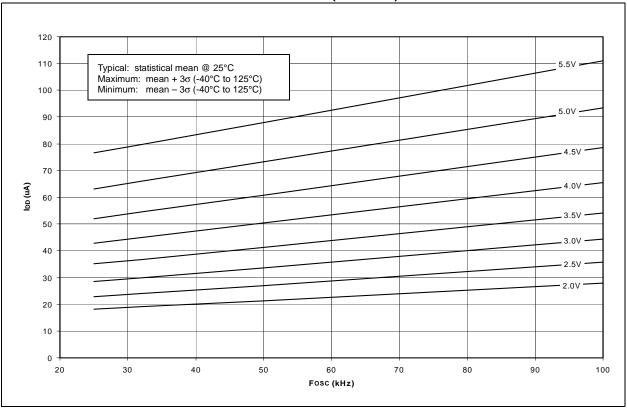

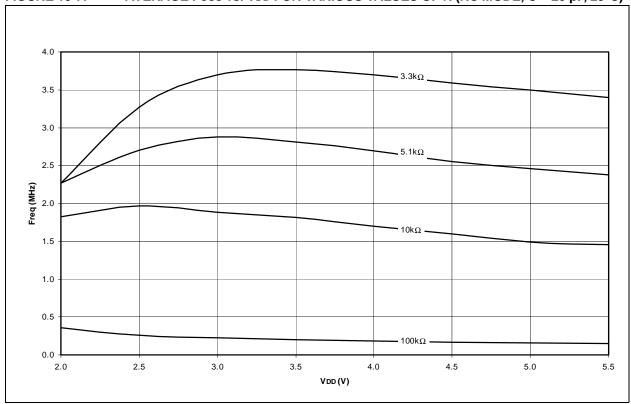

| 15.0             | DC and AC Characteristics Graphs and Tables                                 | 137 |

|                  | Packaging Information                                                       |     |

| Appe             | endix A: Revision History                                                   | 157 |

| Appe             | endix B: Device Differences                                                 | 157 |

| Appe             | endix C: Conversion Considerations                                          | 158 |

| Appe             | endix D: Migration from Mid-Range to Enhanced Devices                       | 158 |

| Appe             | endix E: Migration from High-End to Enhanced Devices                        | 159 |

| Index            | x                                                                           | 161 |

| On-L             | ine Support                                                                 | 167 |

| Syste            | ems Information and Upgrade Hot Line                                        | 167 |

| Read             | der Response                                                                | 168 |

| PIC <sub>1</sub> | 16F870/871 Product Identification System                                    | 169 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

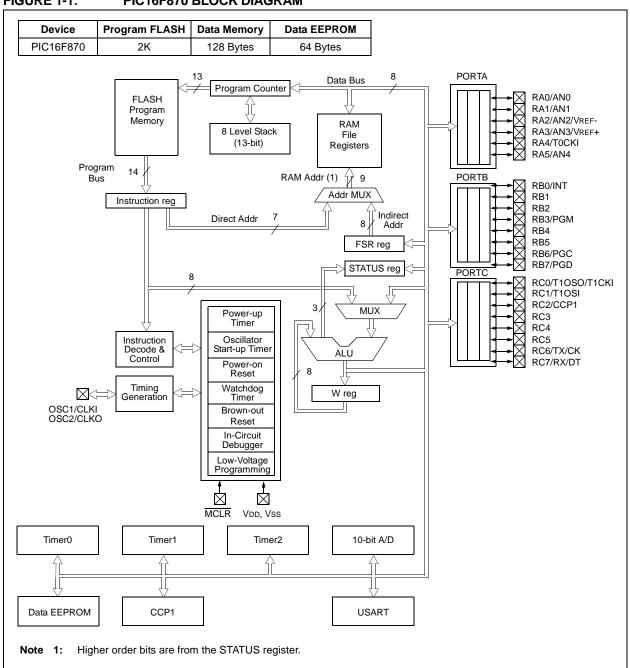

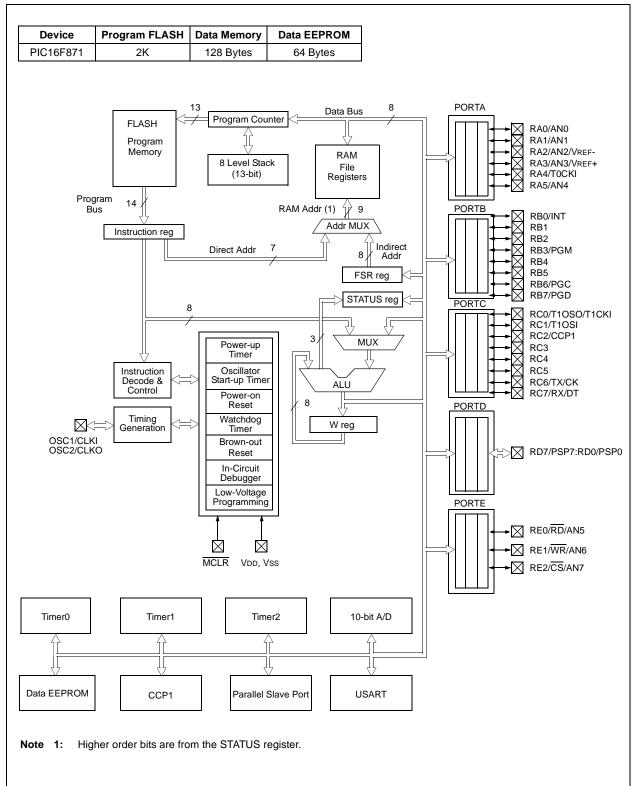

### 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

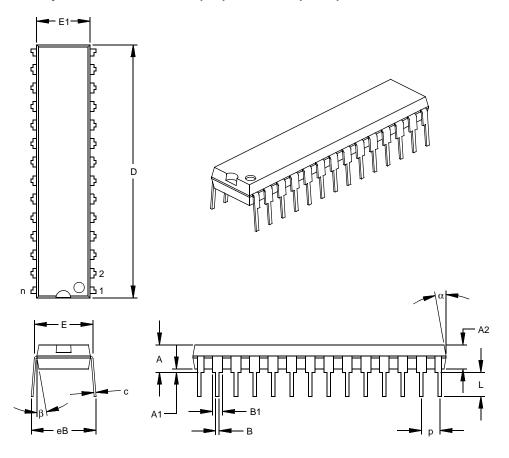

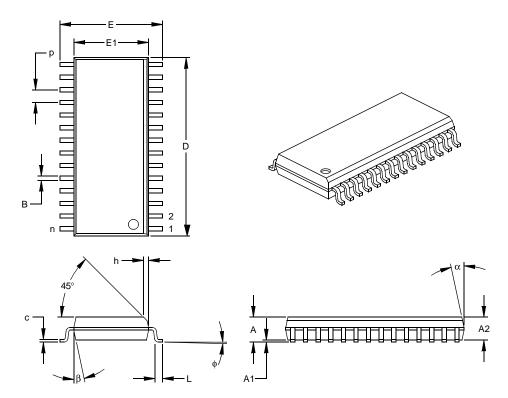

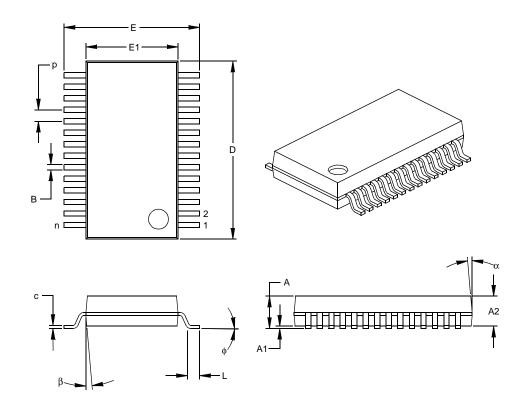

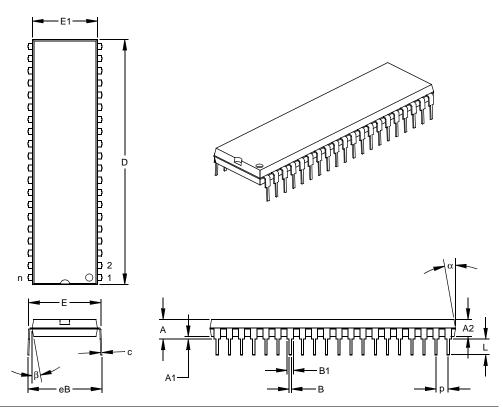

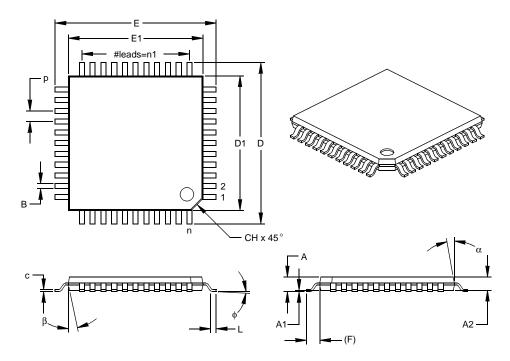

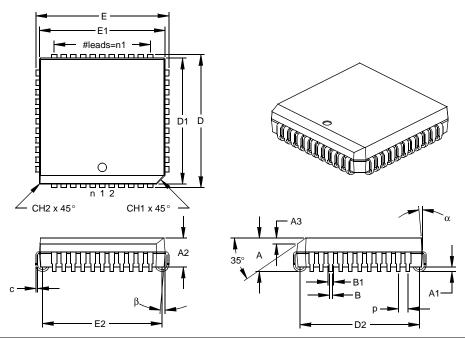

There are two devices (PIC16F870 and PIC16F871) covered by this data sheet. The PIC16F870 device comes in a 28-pin package and the PIC16F871 device comes in a 40-pin package. The 28-pin device does not have a Parallel Slave Port implemented.

The following two figures are device block diagrams sorted by pin number: 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

FIGURE 1-1: PIC16F870 BLOCK DIAGRAM

FIGURE 1-2: PIC16F871 BLOCK DIAGRAM

TABLE 1-1: PIC16F870 PINOUT DESCRIPTION

| Pin Name        | DIP<br>Pin# | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                 |

|-----------------|-------------|--------------|---------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI       | 9           | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                       |

| OSC2/CLKO       | 10          | 10           | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, the OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP/THV    | 1           | 1            | I/P           | ST                     | Master Clear (Reset) input or programming voltage input or High Voltage Test mode control. This pin is an active low RESET to the device.                                                                   |

|                 |             |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                         |

| RA0/AN0         | 2           | 2            | I/O           | TTL                    | RA0 can also be analog input 0.                                                                                                                                                                             |

| RA1/AN1         | 3           | 3            | I/O           | TTL                    | RA1 can also be analog input 1.                                                                                                                                                                             |

| RA2/AN2/VREF-   | 4           | 4            | I/O           | TTL                    | RA2 can also be analog input 2 or negative analog reference voltage.                                                                                                                                        |

| RA3/AN3/VREF+   | 5           | 5            | I/O           | TTL                    | RA3 can also be analog input 3 or positive analog reference voltage.                                                                                                                                        |

| RA4/T0CKI       | 6           | 6            | I/O           | ST/OD                  | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                            |

| RA5/AN4         | 7           | 7            | I/O           | TTL                    | RA5 can also be analog input 4.                                                                                                                                                                             |

|                 |             |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                               |

| RB0/INT         | 21          | 21           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                 |

| RB1             | 22          | 22           | I/O           | TTL                    |                                                                                                                                                                                                             |

| RB2             | 23          | 23           | I/O           | TTL                    |                                                                                                                                                                                                             |

| RB3/PGM         | 24          | 24           | I/O           | TTL/ST <sup>(1)</sup>  | RB3 can also be the low voltage programming input.                                                                                                                                                          |

| RB4             | 25          | 25           | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                    |

| RB5             | 26          | 26           | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                    |

| RB6/PGC         | 27          | 27           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming clock.                                                                                                                               |

| RB7/PGD         | 28          | 28           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming data.                                                                                                                                |

|                 |             |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                         |

| RC0/T1OSO/T1CKI | 11          | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                         |

| RC1/T1OSI       | 12          | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                |

| RC2/CCP1        | 13          | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                         |

| RC3             | 14          | 14           | I/O           | ST                     |                                                                                                                                                                                                             |

| RC4             | 15          | 15           | I/O           | ST                     |                                                                                                                                                                                                             |

| RC5             | 16          | 16           | I/O           | ST                     |                                                                                                                                                                                                             |

| RC6/TX/CK       | 17          | 17           | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit or Synchronous Clock.                                                                                                                                       |

| RC7/RX/DT       | 18          | 18           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive or Synchronous Data.                                                                                                                                         |

| Vss             | 8, 19       | 8, 19        | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                    |

| VDD             | 20          | 20           | Р             | _                      | Positive supply for logic and I/O pins.                                                                                                                                                                     |

Legend: I = input

I = input O = output

OD = Open Drain — = Not used

I/O = input/outputTTL = TTL input P = power ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt or LVP mode.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

TABLE 1-2: PIC16F871 PINOUT DESCRIPTION

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                             |

|-------------------|-------------|--------------|-------------|---------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI         | 13          | 14           | 30          | I             | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                   |

| OSC2/CLKO         | 14          | 15           | 31          | 0             | ı                      | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp/THV      | 1           | 2            | 18          | I/P           | ST                     | Master Clear (Reset) input or programming voltage input or High Voltage Test mode control. This pin is an active low RESET to the device.                                                               |

|                   |             |              |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                     |

| RA0/AN0           | 2           | 3            | 19          | I/O           | TTL                    | RA0 can also be analog input 0.                                                                                                                                                                         |

| RA1/AN1           | 3           | 4            | 20          | I/O           | TTL                    | RA1 can also be analog input 1.                                                                                                                                                                         |

| RA2/AN2/VREF-     | 4           | 5            | 21          | I/O           | TTL                    | RA2 can also be analog input 2 or negative analog reference voltage.                                                                                                                                    |

| RA3/AN3/VREF+     | 5           | 6            | 22          | I/O           | TTL                    | RA3 can also be analog input 3 or positive analog reference voltage.                                                                                                                                    |

| RA4/T0CKI         | 6           | 7            | 23          | I/O           | ST                     | RA4 can also be the clock input to the Timer0 timer/counter. Output is open drain type.                                                                                                                 |

| RA5/AN4           | 7           | 8            | 24          | I/O           | TTL                    | RA5 can also be analog input 4.                                                                                                                                                                         |

|                   |             |              |             |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                           |

| RB0/INT           | 33          | 36           | 8           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                             |

| RB1               | 34          | 37           | 9           | I/O           | TTL                    |                                                                                                                                                                                                         |

| RB2               | 35          | 38           | 10          | I/O           | TTL                    |                                                                                                                                                                                                         |

| RB3/PGM           | 36          | 39           | 11          | I/O           | TTL/ST <sup>(1)</sup>  | RB3 can also be the low voltage programming input.                                                                                                                                                      |

| RB4               | 37          | 41           | 14          | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                |

| RB5               | 38          | 42           | 15          | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                |

| RB6/PGC           | 39          | 43           | 16          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming clock.                                                                                                                        |

| RB7/PGD           | 40          | 44           | 17          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming data.                                                                                                                         |

|                   |             |              |             |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                     |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or a Timer1 clock input.                                                                                                                                   |

| RC1/T1OSI         | 16          | 18           | 35          | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                            |

| RC2/CCP1          | 17          | 19           | 36          | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                                                                                                                         |

| RC3               | 18          | 20           | 37          | I/O           | ST                     |                                                                                                                                                                                                         |

| RC4               | 23          | 25           | 42          | I/O           | ST                     |                                                                                                                                                                                                         |

| RC5               | 24          | 26           | 43          | I/O           | ST                     |                                                                                                                                                                                                         |

| RC6/TX/CK         | 25          | 27           | 44          | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit or Synchronous Clock.                                                                                                                                   |

| RC7/RX/DT         | 26          | 29           | 1           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive or Synchronous Data.                                                                                                                                     |

| Legend: L = input |             | 0 = 0        | .to.ut      |               | I/O = input/ou         | tout P = power                                                                                                                                                                                          |

Legend: I = input

O = output

I/O = input/output

P = power

— = Not used

ed TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt or LVP mode.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

- 4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

TABLE 1-2: PIC16F871 PINOUT DESCRIPTION (CONTINUED)

| Pin Name   | DIP<br>Pin# | PLCC<br>Pin#   | QFP<br>Pin#     | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                         |

|------------|-------------|----------------|-----------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------------|

|            |             |                |                 |               |                       | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus. |

| RD0/PSP0   | 19          | 21             | 38              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD1/PSP1   | 20          | 22             | 39              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD2/PSP2   | 21          | 23             | 40              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD3/PSP3   | 22          | 24             | 41              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD4/PSP4   | 27          | 30             | 2               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD5/PSP5   | 28          | 31             | 3               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD6/PSP6   | 29          | 32             | 4               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD7/PSP7   | 30          | 33             | 5               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

|            |             |                |                 |               |                       | PORTE is a bi-directional I/O port.                                                                 |

| RE0/RD/AN5 | 8           | 9              | 25              | I/O           | ST/TTL <sup>(3)</sup> | RE0 can also be read control for the parallel slave port, or analog input 5.                        |

| RE1/WR/AN6 | 9           | 10             | 26              | I/O           | ST/TTL <sup>(3)</sup> | RE1 can also be write control for the parallel slave port, or analog input 6.                       |

| RE2/CS/AN7 | 10          | 11             | 27              | I/O           | ST/TTL <sup>(3)</sup> | RE2 can also be select control for the parallel slave port, or analog input 7.                      |

| Vss        | 12,31       | 13,34          | 6,29            | Р             | -                     | Ground reference for logic and I/O pins.                                                            |

| VDD        | 11,32       | 12,35          | 7,28            | Р             |                       | Positive supply for logic and I/O pins.                                                             |

| NC         | _           | 1,17,28,<br>40 | 12,13,<br>33,34 |               | _                     | These pins are not internally connected. These pins should be left unconnected.                     |

Legend:

I = input O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt or LVP mode.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

- 4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

NOTES:

### 2.0 MEMORY ORGANIZATION

The PIC16F870/871 devices have three memory blocks. The Program Memory and Data Memory have separate buses, so that concurrent access can occur, and is detailed in this section. The EEPROM data memory block is detailed in Section 3.0.

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

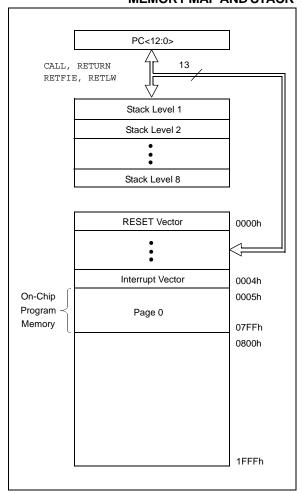

## 2.1 Program Memory Organization

The PIC16F870/871 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. The PIC16F870/871 devices have 2K x 14 words of FLASH program memory. Accessing a location above the physically implemented address will cause a wraparound.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-1: PIC16F870/871 PROGRAM MEMORY MAP AND STACK

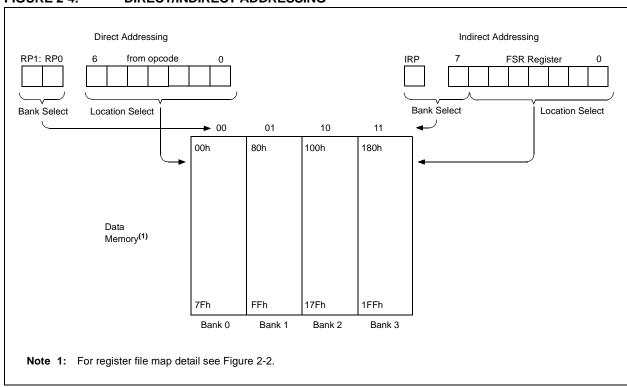

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP<1:0> | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some "high use" Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

**Note:** EEPROM Data Memory description can be found in Section 3.0 of this Data Sheet.

## 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR.

FIGURE 2-2: PIC16F870/871 REGISTER FILE MAP

|                      | File<br>Address |                      | File<br>Address |                     | File<br>Address | A                       | File<br>Addre |

|----------------------|-----------------|----------------------|-----------------|---------------------|-----------------|-------------------------|---------------|

| Indirect addr.(*)    | 00h             | Indirect addr.(*)    | 80h             | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180           |

| TMR0                 | 01h             | OPTION_REG           | 81h             | TMR0                | 101h            | OPTION_REG              | 181           |

| PCL                  | 02h             | PCL                  | 82h             | PCL                 | 102h            | PCL                     | 182           |

| STATUS               | 03h             | STATUS               | 83h             | STATUS              | 103h            | STATUS                  | 183           |

| FSR                  | 04h             | FSR                  | 84h             | FSR                 | 104h            | FSR                     | 184           |

| PORTA                | 05h             | TRISA                | 85h             |                     | 105h            |                         | 18            |

| PORTB                | 06h             | TRISB                | 86h             | PORTB               | 106h            | TRISB                   | 186           |

| PORTC                | 07h             | TRISC                | 87h             |                     | 107h            |                         | 187           |

| PORTD <sup>(2)</sup> | 08h             | TRISD <sup>(2)</sup> | 88h             |                     | 108h            |                         | 188           |

| PORTE <sup>(2)</sup> | 09h             | TRISE <sup>(2)</sup> | 89h             |                     | 109h            |                         | 189           |

| PCLATH               | 0Ah             | PCLATH               | 8Ah             | PCLATH              | 10Ah            | PCLATH                  | 18            |

| INTCON               | 0Bh             | INTCON               | 8Bh             | INTCON              | 10Bh            | INTCON                  | 18            |

| PIR1                 | 0Ch             | PIE1                 | 8Ch             | EEDATA              | 10Ch            | EECON1                  | 18            |

| PIR2                 | 0Dh             | PIE2                 | 8Dh             | EEADR               | 10Dh            | EECON2                  | 18            |

| TMR1L                | 0Eh             | PCON                 | 8Eh             | EEDATH              | 10Eh            | Reserved <sup>(1)</sup> | 18            |

| TMR1H                | 0Fh             |                      | 8Fh             | EEADRH              | 10Fh            | Reserved <sup>(1)</sup> | 18            |

| T1CON                | 10h             |                      | 90h             |                     | 110h            |                         | 19            |

| TMR2                 | 11h             |                      | 91h             |                     |                 |                         |               |

| T2CON                | 12h             | PR2                  | 92h             |                     |                 |                         |               |

|                      | 13h             |                      | 93h             |                     |                 |                         |               |

|                      | 14h             |                      | 94h             |                     |                 |                         |               |

| CCPR1L               | 15h             |                      | 95h             |                     |                 |                         |               |

| CCPR1H               | 16h             |                      | 96h             |                     |                 |                         |               |

| CCP1CON              | 17h             |                      | 97h             |                     |                 |                         |               |

| RCSTA                | 18h             | TXSTA                | 98h             |                     |                 |                         |               |

| TXREG                | 19h             | SPBRG                | 99h             |                     |                 |                         |               |

| RCREG                | 1Ah             |                      | 9Ah             |                     |                 |                         |               |

|                      | 1Bh             |                      | 9Bh             |                     |                 |                         |               |

|                      | 1Ch             |                      | 9Ch             |                     |                 |                         |               |

|                      | 1Dh             |                      | 9Dh             |                     |                 |                         |               |

| ADRESH               | 1Eh             | ADRESL               | 9Eh             |                     |                 |                         |               |

| ADCON0               | 1Fh             | ADCON1               | 9Fh             |                     | 400'            |                         | 4 ^           |

|                      | 20h             | General              | A0h             |                     | 120h            |                         | 1A            |

|                      |                 | Purpose<br>Register  | 71011           | accesses<br>20h-7Fh |                 | accesses<br>A0h - BFh   |               |

| General              |                 | 32 Bytes             | BFh             |                     |                 |                         | 1B            |

| Purpose<br>Register  |                 | ,                    | C0h             |                     |                 |                         | 1C            |

| _                    |                 |                      | 00.1            |                     |                 |                         |               |

| 96 Bytes             |                 |                      | EFh             |                     | 16Fh            |                         | 1E            |

|                      |                 | accesses             | F0h             | accesses            | 170h            | accesses                | 1F            |

|                      | 7Fh             | 70h-7Fh              | FFh             | 70h-7Fh             | 17Fh            | 70h-7Fh                 | 1F            |

| Bank 0               | <i> </i> []     | Bank 1               | FFII            | Bank 2              | 1 1/111         | Bank 3                  | 115           |

<sup>\*</sup> Not a physical register.

Note 1: These registers are reserved; maintain these registers clear.

<sup>2:</sup> These registers are not implemented on the PIC16F870.

### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6                                                                       | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1        | Bit 0       | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS <sup>(2)</sup> |

|----------------------|---------|----------------------|-----------------------------------------------------------------------------|---------------|----------------|---------------|-----------------|--------------|-------------|-----------------------|------------------------------------------------|

| Bank 0               |         |                      |                                                                             |               |                |               |                 |              |             |                       |                                                |

| 00h <sup>(4)</sup>   | INDF    | Addressing           | this location                                                               | uses conte    | ents of FSR to | address dat   | ta memory (n    | ot a physica | l register) | 0000 0000             | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 Mod           | dule's Regist                                                               |               | xxxx xxxx      | uuuu uuuu     |                 |              |             |                       |                                                |

| 02h <sup>(4)</sup>   | PCL     | Program Co           | ounter's (PC                                                                | ) Least Sigr  | ificant Byte   |               |                 |              |             | 0000 0000             | 0000 0000                                      |

| 03h <sup>(4)</sup>   | STATUS  | IRP                  | IRP RP1 RP0 TO PD Z DC C                                                    |               |                |               |                 |              | С           | 0001 1xxx             | 000q quuu                                      |

| 04h <sup>(4)</sup>   | FSR     | Indirect Dat         | a Memory A                                                                  | ddress Poir   | nter           |               |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 05h                  | PORTA   | _                    | _                                                                           | PORTA Da      | ta Latch whe   | n written: PC | RTA pins wh     | en read      |             | 0x 0000               | 0u 0000                                        |

| 06h                  | PORTB   | PORTB Da             | ta Latch whe                                                                | en written: P | ORTB pins v    | vhen read     |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da             | ta Latch whe                                                                | en written: F | ORTC pins v    | vhen read     |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Da             | ta Latch whe                                                                | en written: F | ORTD pins v    | vhen read     |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 09h <sup>(5)</sup>   | PORTE   | _                    | _                                                                           | _             | _              | _             | RE2             | RE1          | RE0         | xxx                   | uuu                                            |

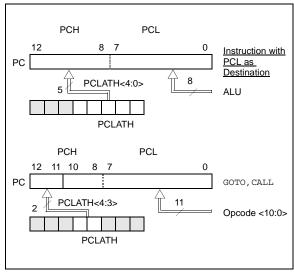

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                    | 1                                                                           | -             | Write Buffer   | for the upper | r 5 bits of the | Program Co   | unter       | 0 0000                | 0 0000                                         |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE                                                                        | TOIE          | INTE           | RBIE          | TOIF            | INTF         | RBIF        | 0000 000x             | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF                                                                        | RCIF          | TXIF           | _             | CCP1IF          | TMR2IF       | TMR1IF      | 0000 -000             | 0000 -000                                      |

| 0Dh                  | PIR2    | _                    |                                                                             | _             | EEIF           | _             | _               | _            | _           | 0                     | 0                                              |

| 0Eh                  | TMR1L   | Holding Re           | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |               |                |               |                 |              |             |                       | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding Re           | gister for the                                                              | Most Signi    | ficant Byte of | the 16-bit TN | MR1 Register    | -            |             | xxxx xxxx             | uuuu uuuu                                      |

| 10h                  | T1CON   | _                    | _                                                                           | T1CKPS1       | T1CKPS0        | T10SCEN       | T1SYNC          | TMR1CS       | TMR10N      | 00 0000               | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 Mod           | dule's Regist                                                               | er            | •              | •             | •               | •            | •           | 0000 0000             | 0000 0000                                      |

| 12h                  | T2CON   | _                    | TOUTPS3                                                                     | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1      | T2CKPS0     | -000 0000             | -000 0000                                      |

| 13h                  | _       | Unimpleme            | nted                                                                        |               |                |               |                 |              |             | _                     | _                                              |

| 14h                  | _       | Unimpleme            | nted                                                                        |               |                |               |                 |              |             | _                     | _                                              |

| 15h                  | CCPR1L  | Capture/Co           | mpare/PWM                                                                   | 1 Register1   | (LSB)          |               |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co           | mpare/PWM                                                                   | 1 Register1   | (MSB)          |               |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 17h                  | CCP1CON | _                    | _                                                                           | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1       | CCP1M0      | 00 0000               | 00 0000                                        |

| 18h                  | RCSTA   | SPEN                 | RX9                                                                         | SREN          | CREN           | ADDEN         | FERR            | OERR         | RX9D        | 0000 000x             | 0000 000x                                      |

| 19h                  | TXREG   | USART Tra            | nsmit Data I                                                                | Register      |                |               |                 |              | •           | 0000 0000             | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Re             | ceive Data F                                                                | Register      |                |               |                 |              |             | 0000 0000             | 0000 0000                                      |

| 1Bh                  | _       | Unimpleme            | nted                                                                        |               |                |               |                 |              |             | _                     | _                                              |

| 1Ch                  | _       | Unimpleme            | nted                                                                        |               |                |               |                 |              |             | _                     | _                                              |

| 1Dh                  | _       | Unimpleme            | nted                                                                        |               |                |               |                 |              |             | _                     | _                                              |

| 1Eh                  | ADRESH  | A/D Result           | Register Hig                                                                | h Byte        |                |               |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0                                                                       | CHS2          | CHS1           | CHS0          | GO/DONE         | _            | ADON        | 0000 00-0             | 0000 00-0                                      |

Legend: x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

- Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

- 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

- 4: These registers can be addressed from any bank.

- 5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address              | Name       | Bit 7                        | Bit 6                                                                                    | Bit 5        | Bit 4           | Bit 3        | Bit 2           | Bit 1         | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS <sup>(2)</sup> |

|----------------------|------------|------------------------------|------------------------------------------------------------------------------------------|--------------|-----------------|--------------|-----------------|---------------|--------|-----------------------|------------------------------------------------|

| Bank 1               |            |                              |                                                                                          | 1            |                 |              |                 |               | I.     |                       |                                                |

| 80h <sup>(4)</sup>   | INDF       | Addressing                   | ddressing this location uses contents of FSR to address data memory (not a physical regi |              |                 |              |                 |               |        |                       | 0000 0000                                      |

| 81h                  | OPTION_REG | RBPU                         | RBPU INTEDG TOCS TOSE PSA PS2 PS1 PSC                                                    |              |                 |              |                 |               |        | 1111 1111             | 1111 1111                                      |

| 82h <sup>(4)</sup>   | PCL        | Program Co                   | ounter's (PC                                                                             | ) Least Sigr | nificant Byte   |              | •               | •             |        | 0000 0000             | 0000 0000                                      |

| 83h <sup>(4)</sup>   | STATUS     | IRP                          | RP1                                                                                      | RP0          | TO              | PD           | Z               | DC            | С      | 0001 1xxx             | 000q quuu                                      |

| 84h <sup>(4)</sup>   | FSR        | Indirect Dat                 | a Memory A                                                                               | ddress Poir  | nter            |              | •               |               | •      | xxxx xxxx             | uuuu uuuu                                      |

| 85h                  | TRISA      | _                            | _                                                                                        | PORTA Da     | ata Direction F | Register     |                 |               |        | 11 1111               | 11 1111                                        |

| 86h                  | TRISB      | PORTB Da                     | ta Direction                                                                             | Register     |                 |              |                 |               |        | 1111 1111             | 1111 1111                                      |

| 87h                  | TRISC      | PORTC Da                     | ta Direction                                                                             | Register     |                 |              |                 |               |        | 1111 1111             | 1111 1111                                      |

| 88h <sup>(5)</sup>   | TRISD      | PORTD Da                     | ta Direction                                                                             | Register     |                 |              |                 |               |        | 1111 1111             | 1111 1111                                      |

| 89h <sup>(5)</sup>   | TRISE      | IBF                          | OBF                                                                                      | IBOV         | PSPMODE         | _            | PORTE Dat       | a Direction E | Bits   | 0000 -111             | 0000 -111                                      |

| 8Ah <sup>(1,4)</sup> | PCLATH     | _                            | _                                                                                        | _            | Write Buffer    | for the uppe | r 5 bits of the | Program Co    | unter  | 0 0000                | 0 0000                                         |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                          | PEIE                                                                                     | TOIE         | INTE            | RBIE         | TOIF            | INTF          | RBIF   | 0000 000x             | 0000 000u                                      |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup>         | ADIE                                                                                     | RCIE         | TXIE            | _            | CCP1IE          | TMR2IE        | TMR1IE | 0000 -000             | 0000 -000                                      |

| 8Dh                  | PIE2       | _                            | _                                                                                        | _            | EEIE            | _            | _               | _             | _      | 0                     | 0                                              |

| 8Eh                  | PCON       | _                            | _                                                                                        | _            | _               | _            | _               | POR           | BOR    | qq                    | uu                                             |

| 8Fh                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 90h                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 91h                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 92h                  | PR2        | Timer2 Peri                  | iod Register                                                                             |              |                 |              |                 |               |        | 1111 1111             | 1111 1111                                      |

| 93h                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 94h                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 95h                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 96h                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 97h                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 98h                  | TXSTA      | CSRC                         | TX9                                                                                      | TXEN         | SYNC            | _            | BRGH            | TRMT          | TX9D   | 0000 -010             | 0000 -010                                      |

| 99h                  | SPBRG      | Baud Rate                    | Generator R                                                                              | Register     |                 |              |                 |               |        | 0000 0000             | 0000 0000                                      |

| 9Ah                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 9Bh                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 9Ch                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 9Dh                  | _          | Unimpleme                    | nted                                                                                     |              |                 |              |                 |               |        | _                     | _                                              |

| 9Eh                  | ADRESL     | A/D Result Register Low Byte |                                                                                          |              |                 |              |                 |               |        | xxxx xxxx             | uuuu uuuu                                      |

|                      | ADCON1     | ADFM                         |                                                                                          |              |                 | PCFG3        | PCFG2           | PCFG1         | PCFG0  | 0 0000                | 0 0000                                         |

Legend: x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

- Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

- 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

- 4: These registers can be addressed from any bank.

- 5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address               | Name                    | Bit 7                                              | Bit 6                   | Bit 5         | Bit 4          | Bit 3        | Bit 2           | Bit 1        | Bit 0       | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS <sup>(2)</sup> |

|-----------------------|-------------------------|----------------------------------------------------|-------------------------|---------------|----------------|--------------|-----------------|--------------|-------------|-----------------------|------------------------------------------------|

| Bank 2                |                         |                                                    |                         |               |                |              |                 |              |             |                       |                                                |

| 100h <sup>(4)</sup>   | INDF                    | Addressing                                         | this location           | uses conte    | ents of FSR to | address da   | ta memory (n    | ot a physica | l register) | 0000 0000             | 0000 0000                                      |

| 101h                  | TMR0                    | Timer0 Mod                                         | lule's Regist           | er            |                |              |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 102h <sup>(4)</sup>   | PCL                     | Program Co                                         | ounter's (PC            | ) Least Sign  | ificant Byte   |              |                 |              |             | 0000 0000             | 0000 0000                                      |

| 103h <sup>(4)</sup>   | STATUS                  | IRP                                                | RP1                     | RP0           | TO             | PD           | Z               | DC           | С           | 0001 1xxx             | 000q quuu                                      |

| 104h <sup>(4)</sup>   | FSR                     | Indirect Dat                                       | a Memory A              | ddress Poir   | nter           |              |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 105h                  | 1                       | Unimpleme                                          | nted                    |               |                |              |                 |              |             | _                     | _                                              |

| 106h                  | PORTB                   | PORTB Da                                           | ta Latch whe            | en written: P | ORTB pins w    | hen read     |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 107h                  | 1                       | Unimpleme                                          | nted                    |               |                |              |                 |              |             | _                     | _                                              |

| 108h                  | _                       | Unimpleme                                          | nted                    |               |                |              |                 |              |             | _                     | _                                              |

| 109h                  | _                       | Unimpleme                                          | nted                    |               |                |              |                 |              |             | _                     | _                                              |

| 10Ah <sup>(1,4)</sup> | PCLATH                  | -                                                  |                         | _             | Write Buffer   | for the uppe | r 5 bits of the | Program Co   | ounter      | 0 0000                | 0 0000                                         |

| 10Bh <sup>(4)</sup>   | INTCON                  | GIE                                                | PEIE                    | TOIE          | INTE           | RBIE         | TOIF            | INTF         | RBIF        | 0000 000x             | 0000 000u                                      |

| 10Ch                  | EEDATA                  | EEPROM D                                           | ata Registe             | r             |                |              |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 10Dh                  | EEADR                   | EEPROM A                                           | EEPROM Address Register |               |                |              |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 10Eh                  | EEDATH                  | EEPROM Data Register High Byte                     |                         |               |                |              |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

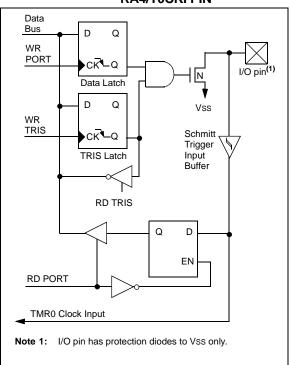

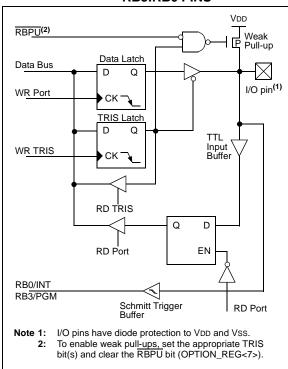

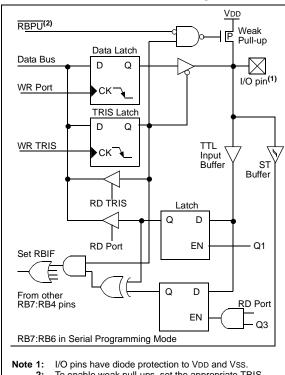

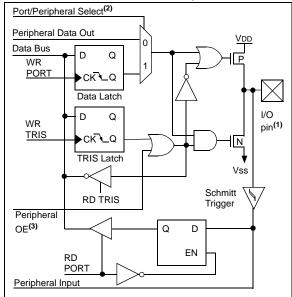

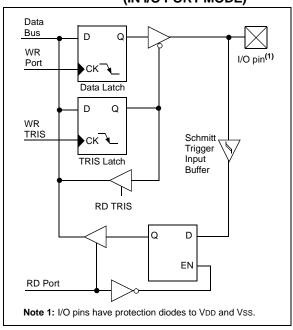

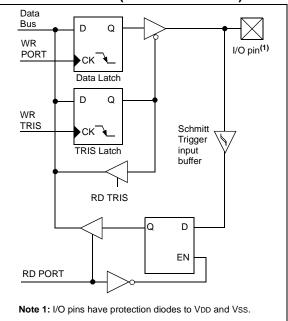

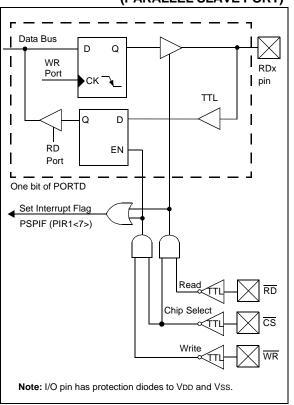

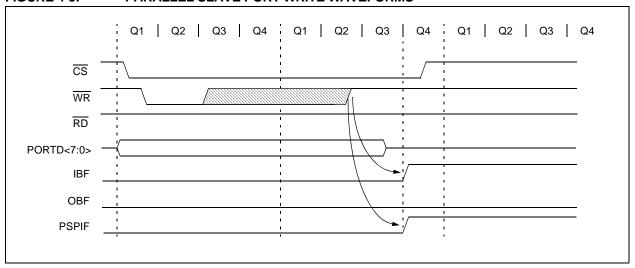

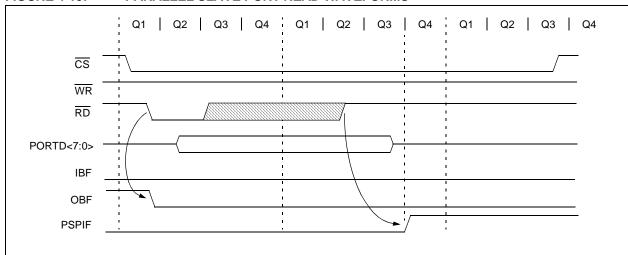

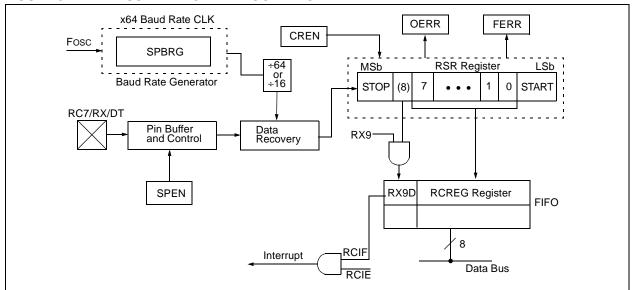

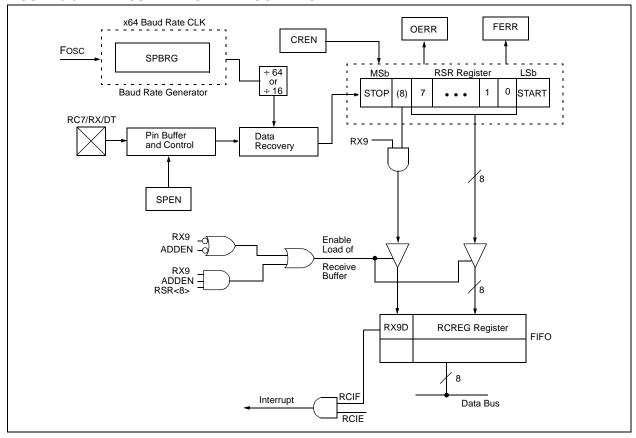

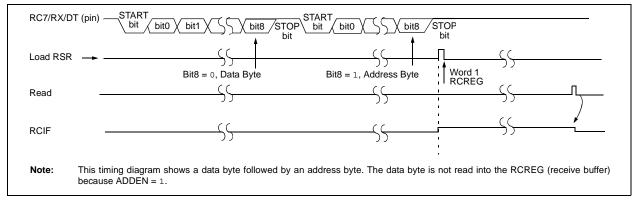

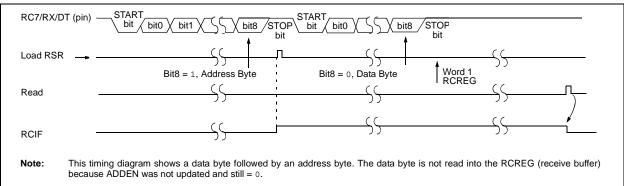

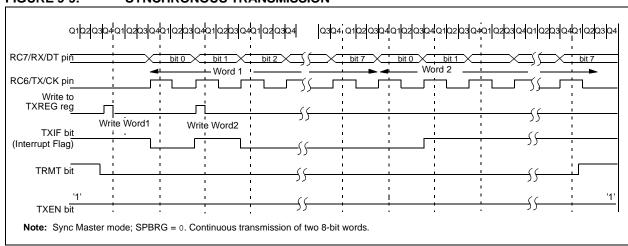

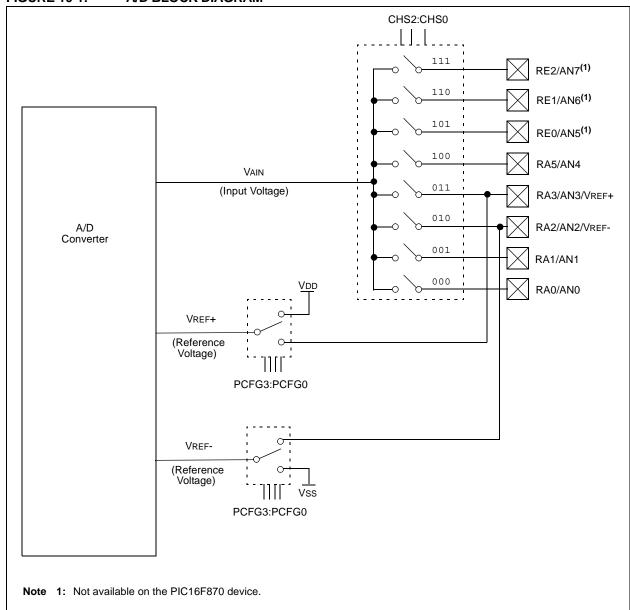

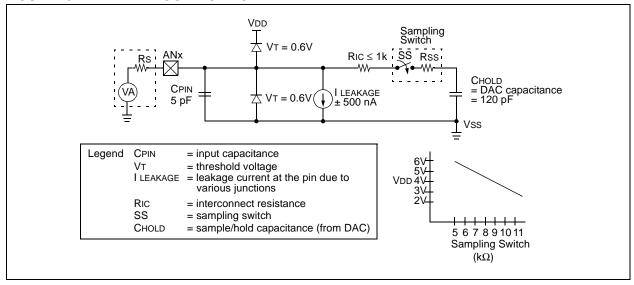

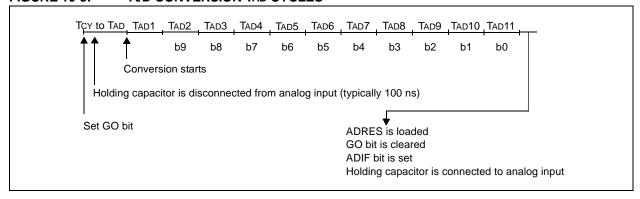

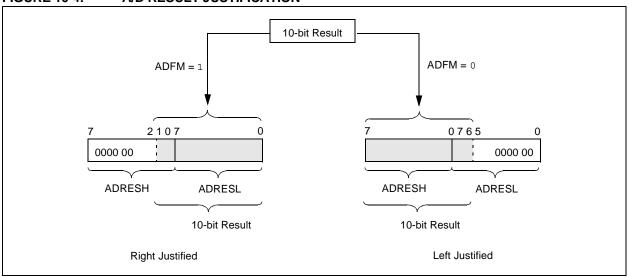

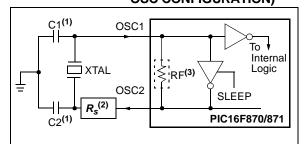

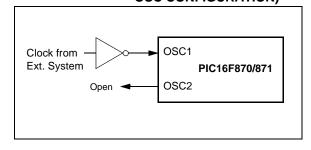

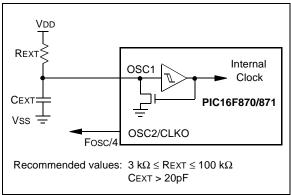

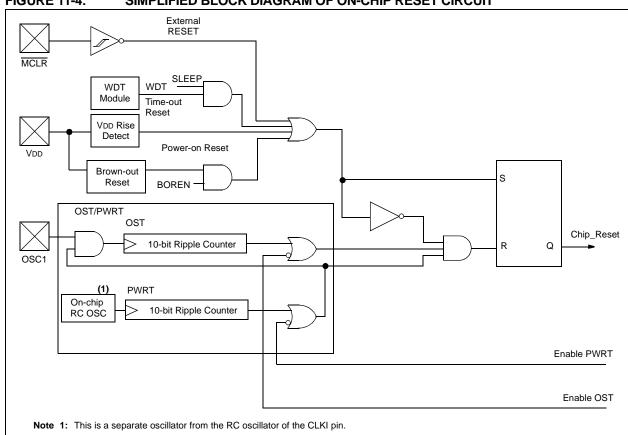

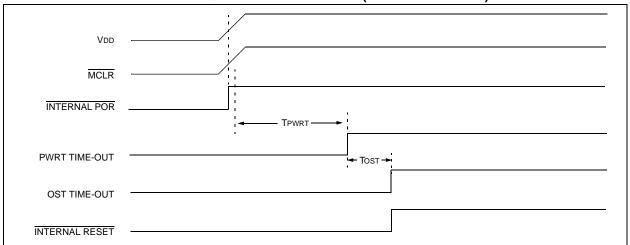

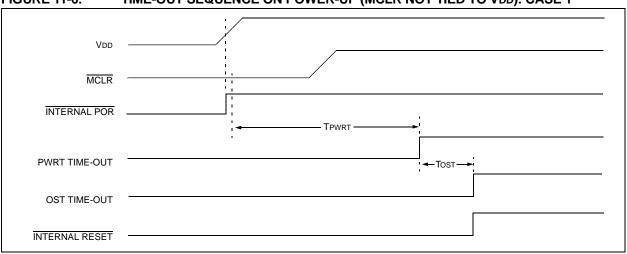

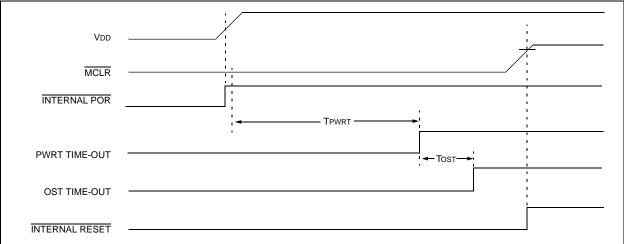

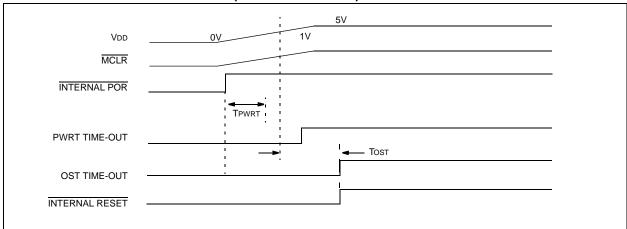

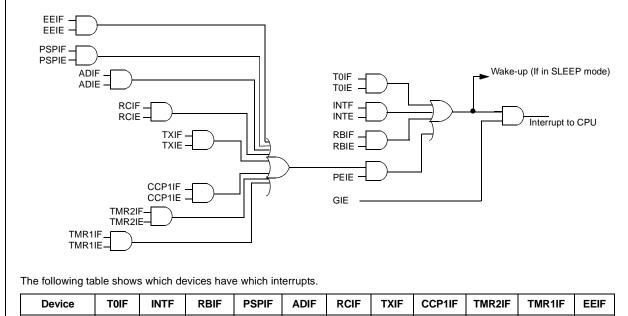

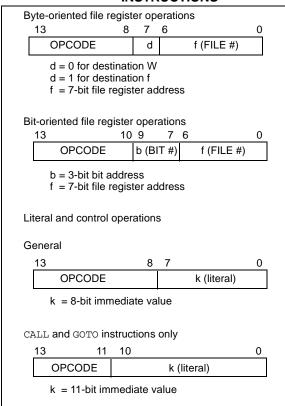

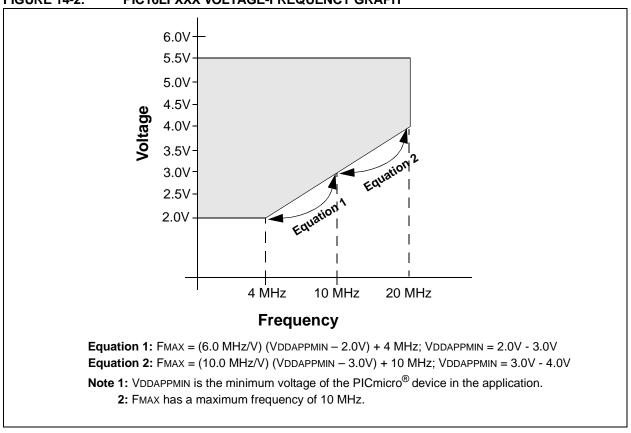

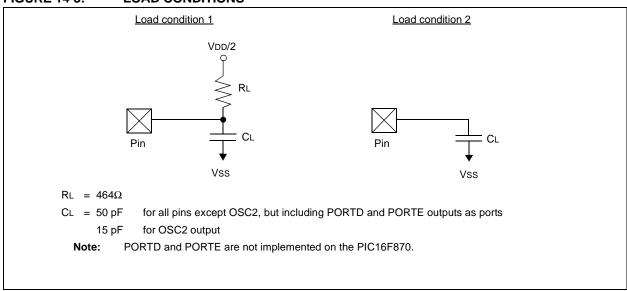

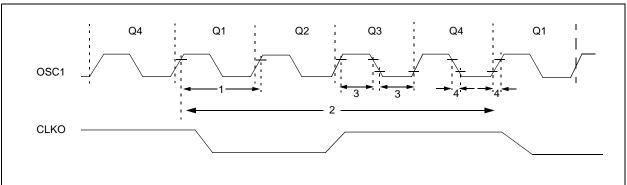

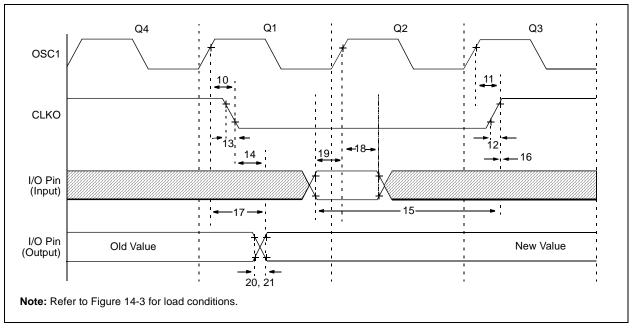

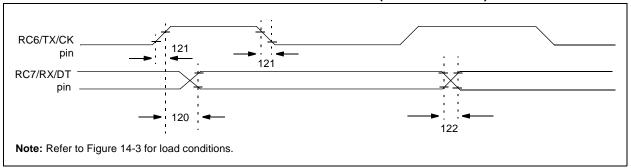

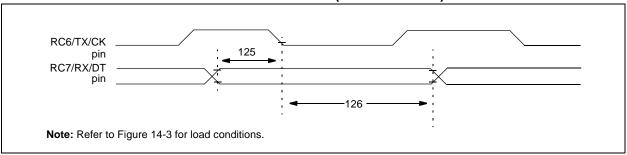

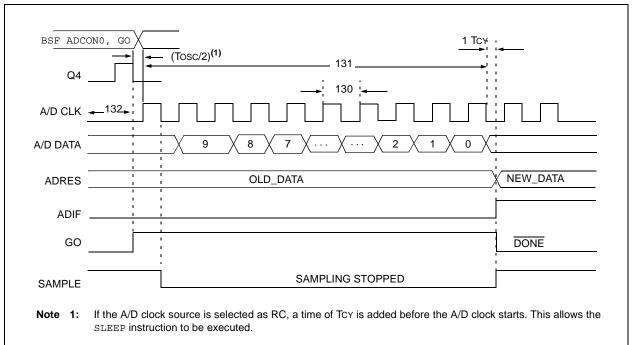

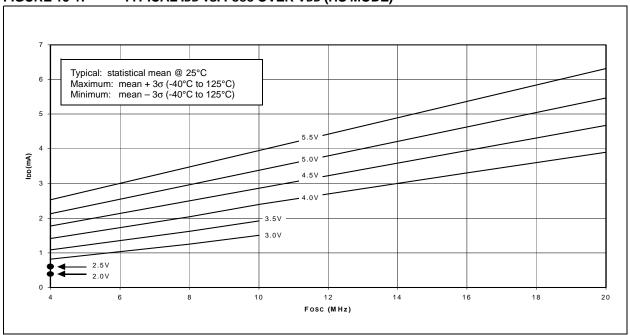

| 10Fh                  | EEADRH                  | _                                                  | _                       |               | EEPROM A       | ddress Regis | ter High Byte   | )            |             | xxxx xxxx             | uuuu uuuu                                      |