# ESDA6V1S3

# Transil<sup>™</sup> array for ESD protection

#### Datasheet - production data

The ESDA6V1S3 is a monolithic voltage suppressors designed to protect components which are connected to data and transmission lines against ESD.

It clamp the voltage just above the logic level supply for positive transients, and to a diode drop below ground for negative transients.

# REPRESENTATION OF THE PARTY OF

## Features

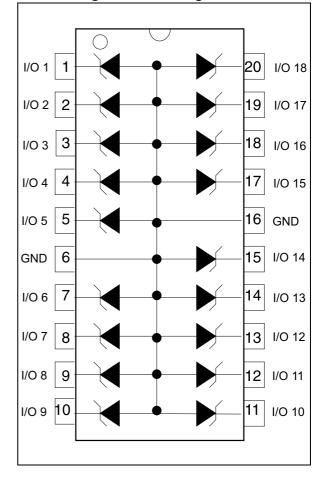

- 18 unidirectional Transil<sup>™</sup> functions

- Low leakage current: I<sub>R</sub> max. < 2 μA</li>

- 200 W peak pulse power (8/20 μs)

## Benefits

- High ESD protection level: up to 25 kV

- High integration

- Suitable for high density boards

### Complies with the following standards:

- IEC 61000-4-2: Level 4

- MIL STD 883C Method 3015-6: Class 3 (human body model)

# Applications

Where transient overvoltage protection in ESD sensitive equipment is required, such as:

- Computers

- Printers

- Communication systems

- GSM handsets and accessories

- Other telephone sets

#### November 2015

DocID5480 Rev 5

This is information on a product in full production.

1/8

#### **Characteristics** 1

| Symbol           | Р                                      | Value                                                                     | Unit |    |

|------------------|----------------------------------------|---------------------------------------------------------------------------|------|----|

| V <sub>PP</sub>  | Peak pulse voltage                     | Peak pulse voltage Electrostatics discharge:   MIL STD 883C-Method 3015-6 |      | kV |

| P <sub>PP</sub>  | Peak pulse power (8/20µs)              | 200                                                                       | W    |    |

| Тj               | Maximum operating junction temperature |                                                                           | +150 | °C |

| T <sub>stg</sub> | Storage temperature range              | -55 to +150                                                               | °C   |    |

| TL               | Maximum lead temperature for so        | 260                                                                       | °C   |    |

| Table 1. Absolute ratings | $T_{amb} = 25 \ ^{\circ}C$ |

|---------------------------|----------------------------|

|---------------------------|----------------------------|

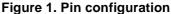

#### Figure 2. Electrical characteristics (definitions)

| Table 2. Electrical c | characteristics - values | (T <sub>amb</sub> = 25 °C) |

|-----------------------|--------------------------|----------------------------|

|-----------------------|--------------------------|----------------------------|

|           | V <sub>BR</sub> at I <sub>R</sub> |      | I <sub>RM</sub> at V <sub>RM</sub> V <sub>F</sub> at I <sub>F</sub> |                     | α <b>Τ<sup>(1)</sup></b> | C <sub>line</sub> at 0 V |     |                     |      |

|-----------|-----------------------------------|------|---------------------------------------------------------------------|---------------------|--------------------------|--------------------------|-----|---------------------|------|

| Types     | min.                              | max. |                                                                     | max. <sup>(2)</sup> |                          | max.                     |     | max.                | typ. |

|           | v                                 | v    | mA                                                                  | μA                  | v                        | v                        | mA  | 10 <sup>-4</sup> /C | pF   |

| ESDA6V1S3 | 6.1                               | 7.2  | 1                                                                   | 2                   | 5.25                     | 1.25                     | 200 | 6                   | 120  |

1.  $\Delta V_{BR} = \alpha T^* (T_{amb} - 25 \text{ °C}) * V_{BR} (25 \text{ °C})$

2. Between any I/O pin and ground.

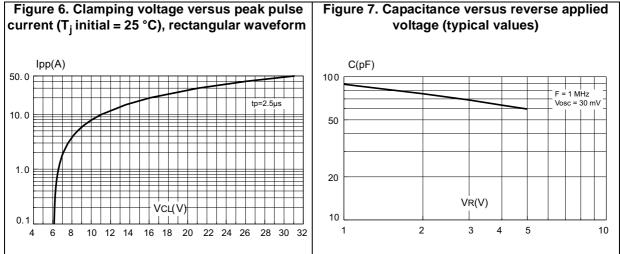

## 2 Calculation of the clamping voltage

## 2.1 Use of the dynamic resistance

The ESDA family has been designed to clamp fast spikes like ESD. Generally the PCB designers need to calculate easily the clamping voltage  $V_{CL}$ . This is why we give the dynamic resistance in addition to the classical parameters. The voltage across the protection cell can be calculated with the following formula:

$V_{CL} = V_{BR} + Rd I_{PP}$

Where Ipp is the peak current through the ESDA cell.

## 2.2 Dynamic resistance measurement

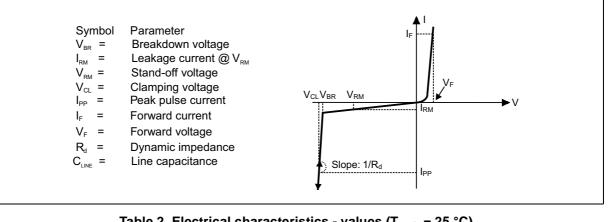

The short duration of the ESD has led us to prefer a more adapted test wave, as below defined, to the classical  $8/20 \ \mu s$  and  $10/1000 \ \mu s$  surges.

Figure 3. 2.5 ms duration measurement wave

As the value of the dynamic resistance remains stable for a surge duration lower than 20  $\mu$ s, the 2.5  $\mu$ s rectangular surge is well adapted. In addition both rise and fall times are optimized to avoid any parasitic phenomenon during the measurement of Rd.

## 3 Application example

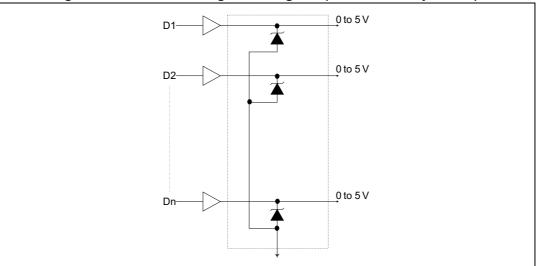

#### Figure 10. Protection of logic-level signals (ex: centronics junction)

Note:

te: Capacitance value between any I/O pin and ground is divided by 2.

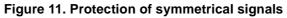

Implementing its ASD<sup>™</sup> technology, STMicroelectronics has developed a monolithic Transil<sup>™</sup> diode array, which is a reliable protection against electrostatic overloads for computer I/O ports, modems, GSM handsets and accessories or other similar systems with data outputs. The ESDA6V1S3 integrates 18 Transil<sup>™</sup> diodes in a compact package that can be easily mounted close to the circuitry to be protected, eliminating the assembly costs associated with the use of discrete diodes, and also increasing system reliability.

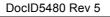

Each Transil<sup>™</sup> has a breakdown voltage between 6.2 V (minimum) and 7.2 V (maximum). When the input voltage is lower than the breakdown voltage, the diodes present a high impedance to ground. For short overvoltage pulses, the fast-acting diodes provide an almost instantaneous response, clamping the voltage to a safe level.

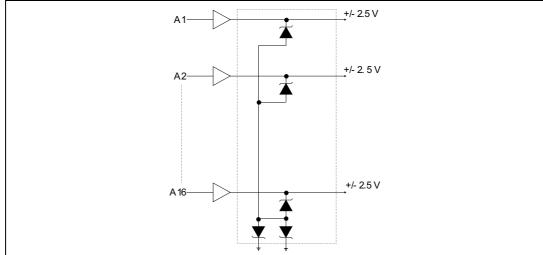

# 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

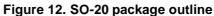

## 4.1 SO-20 package information

#### Table 3. SO-20 package mechanical data

|      |      |             | Dimer | nsions |        |       |

|------|------|-------------|-------|--------|--------|-------|

| Ref. |      | Millimeters |       |        | Inches |       |

|      | Min. | Тур.        | Max.  | Min.   | Тур.   | Max.  |

| А    | 2.35 |             | 2.65  | 0.092  |        | 0.104 |

| A1   | 0.10 |             | 0.20  | 0.004  |        | 0.008 |

| В    | 0.33 |             | 0.51  | 0.013  |        | 0.020 |

| С    | 0.23 |             | 0.32  | 0.009  |        | 0.013 |

| D    | 12.6 |             | 13.0  | 0.484  |        | 0.512 |

| E    | 7.40 |             | 7.60  | 0.291  |        | 0.299 |

| е    |      | 1.27        |       |        | 0.050  |       |

| Н    | 10.0 |             | 10.65 | 0.394  |        | 0.419 |

| h    | 0.25 |             | 0.75  | 0.010  |        | 0.029 |

| L    | 0.50 |             | 1.27  | 0.020  |        | 0.050 |

| К    |      |             | 8°    |        |        | 8°    |

# 5 Ordering information

| ESD array<br>Breakdown voltage<br>Package<br>3 = SO-20 |   | RL |  |

|--------------------------------------------------------|---|----|--|

| Package<br>3 = SO-20                                   | ] |    |  |

| 3 = SO-20                                              |   |    |  |

|                                                        |   |    |  |

| Deskering                                              |   |    |  |

| Packaging                                              |   |    |  |

| RL: Tape and reel                                      |   |    |  |

Figure 13. Ordering information scheme

| Table 4. | Ordering | information  |

|----------|----------|--------------|

|          | oraoring | in or manori |

| Order codes | Marking | Package | Weight | Base qty | Delivery mode |

|-------------|---------|---------|--------|----------|---------------|

| ESDA6V1S3   | E6V1S3  | SO-20   | 0.55 g | 1000     | Tape and reel |

# 6 Revision history

| Table 5. Document re | evision history |

|----------------------|-----------------|

|----------------------|-----------------|

| Date        | Revision | Changes                                |

|-------------|----------|----------------------------------------|

| 18-Sep-2014 | 4        |                                        |

| 13-Nov-2015 | 5        | Removed ESDA6V2S6 package information. |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID5480 Rev 5