## Single Channel 16-bit CIS/CCD AFE with 4-bit Wide Output

### DESCRIPTION

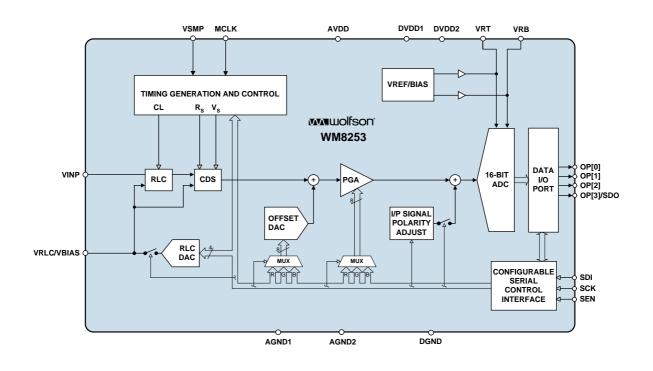

The WM8253 is a 16-bit analogue front end/digitiser IC which processes and digitises the analogue output signals from CCD sensors or Contact Image Sensors (CIS) at pixel sample rates of up to 6MSPS.

The device includes a complete signal processing channel containing Reset Level Clamping, Correlated Double Sampling, Programmable Gain and Offset adjust functions. Internal multiplexers allow fast switching of offset and gain for line-by-line colour processing. The output from this channel is time multiplexed into a high-speed 16-bit Analogue to Digital Converter. The digital output data is available in 4-bit wide multiplexed format.

An internal 4-bit DAC is supplied for internal reference level generation. This may be used during CDS to reference CIS signals or during Reset Level Clamping to clamp CCD signals. An external reference level may also be supplied. ADC references are generated internally, ensuring optimum performance from the device.

The device uses an analogue supply voltage of 3.3V and a digital interface supply of between 2.5V and 3.3V. The WM8253 typically only consumes 132mW when operating from a single 3.3V supply.

## FEATURES

- 16-bit ADC

- 6MSPS conversion rate

- Low power 132mW typical

- 3.3V single supply or 3.3V/2.5V dual supply operation

- Single channel operation

- Correlated double sampling

- Programmable gain (8-bit resolution)

- Programmable offset adjust (8-bit resolution)

- Programmable clamp voltage

- 4-bit wide multiplexed data output format

- Internally generated voltage references

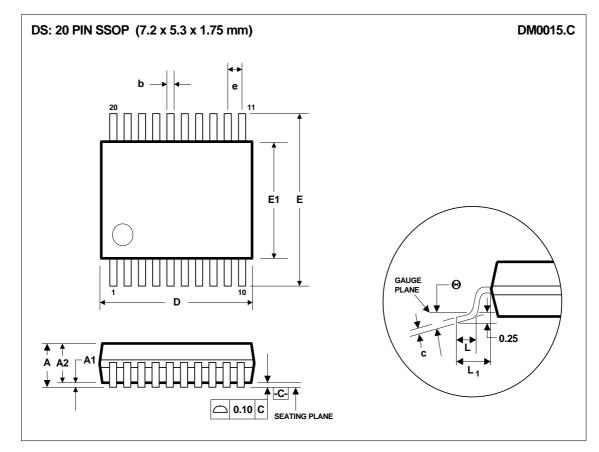

- 20-lead SSOP package

- Serial control interface

## APPLICATIONS

- Flatbed and sheetfeed scanners

- USB compatible scanners

- Multi-function peripherals

- High-performance CCD sensor interface

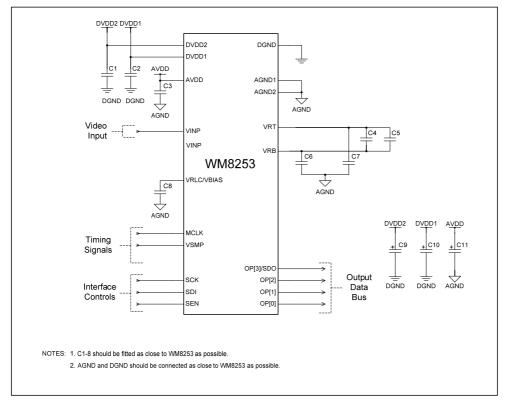

## **BLOCK DIAGRAM**

#### WOLFSON MICROELECTRONICS plc

Production Data, August 2011, Rev 4.1

To receive regular email updates, sign up at http://www.wolfsonmicro.com/enews

## **TABLE OF CONTENTS**

| DESCRIPTION                                                 | . 1 |

|-------------------------------------------------------------|-----|

| FEATURES                                                    | . 1 |

| APPLICATIONS                                                | . 1 |

| BLOCK DIAGRAM                                               | . 1 |

| PIN CONFIGURATION                                           |     |

| ORDERING INFORMATION                                        |     |

| PIN DESCRIPTION                                             |     |

| ABSOLUTE MAXIMUM RATINGS                                    | . 5 |

| RECOMMENDED OPERATING CONDITIONS                            | . 5 |

| ELECTRICAL CHARACTERISTICS                                  |     |

| INPUT VIDEO SAMPLING                                        |     |

| OUTPUT DATA TIMING                                          |     |

| SERIAL INTERFACE                                            | 9   |

| DEVICE DESCRIPTION                                          | 10  |

| INTRODUCTION                                                |     |

| INPUT SAMPLING                                              | 10  |

| RESET LEVEL CLAMPING (RLC)                                  |     |

| CDS/NON-CDS PROCESSING.                                     |     |

|                                                             |     |

| ADC INPUT BLACK LEVEL ADJUST<br>OVERALL SIGNAL FLOW SUMMARY |     |

| CALCULATING OUTPUT FOR ANY GIVEN INPUT                      |     |

| OUTPUT DATA FORMAT                                          |     |

| CONTROL INTERFACE                                           |     |

| TIMING REQUIREMENTS                                         |     |

| PROGRAMMABLE VSMP DETECT CIRCUIT                            | 17  |

| REFERENCES                                                  | 18  |

| POWER SUPPLY                                                |     |

| POWER MANAGEMENT                                            |     |

| OPERATING MODES                                             | 18  |

| OPERATING MODE TIMING DIAGRAMS                              |     |

| DEVICE CONFIGURATION.                                       |     |

|                                                             |     |

|                                                             |     |

| RECOMMENDED EXTERNAL COMPONENTS                             |     |

| PACKAGE DIMENSIONS                                          |     |

|                                                             | -   |

|                                                             | -   |

| REVISION HISTORY                                            | 21  |

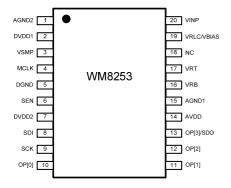

## **PIN CONFIGURATION**

## **ORDERING INFORMATION**

| ORDER CODE    | TEMPERATURE<br>RANGE | PACKAGE                                                | MOISTURE<br>SENSITIVITY LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|---------------|----------------------|--------------------------------------------------------|-------------------------------|-------------------------------|

| WM8253SCDS/V  | 0 to 70°C            | 20-lead SSOP<br>(Pb-free, drybagged)                   | MSL3                          | 260°C                         |

| WM8253SCDS/RV | 0 to 70°C            | 20-lead SSOP<br>(Pb-free, drybagged, tape<br>and reel) | MSL3                          | 260°C                         |

Note:

Reel quantity = 2,000

## **PIN DESCRIPTION**

| PIN<br>NO | NAME       | TYPE            | DESCRIPTION                                  |                                                                                |                       |                       |

|-----------|------------|-----------------|----------------------------------------------|--------------------------------------------------------------------------------|-----------------------|-----------------------|

| 1         | AGND2      | Supply          | Analogue ground pin (0V)                     |                                                                                |                       |                       |

| 2         | DVDD1      | Supply          | Digital Core supply (                        | (3.3V)                                                                         |                       |                       |

| 3         | VSMP       | Digital input   | Video sample synch                           | ronisation pulse.                                                              |                       |                       |

| 4         | MCLK       | Digital input   |                                              | lock is applied at N time reafter depending on in                              |                       | te (N = 2, 3, 6, 8 or |

| 5         | DGND       | Supply          | Digital ground (0V).                         |                                                                                |                       |                       |

| 6         | SEN        | Digital input   | Enables the serial in                        | terface when high.                                                             |                       |                       |

| 7         | DVDD2      | Supply          | Digital I/O supply (2.                       | 5V-3.3V), all digital I/O                                                      | pins.                 |                       |

| 8         | SDI        | Digital input   | Serial data input.                           |                                                                                |                       |                       |

| 9         | SCK        | Digital input   | Serial clock.                                |                                                                                |                       |                       |

|           |            |                 | Digital multiplexed o                        | utput data bus.                                                                |                       |                       |

|           |            |                 | ADC output data (d1                          | 5:d0) is available in 4-b                                                      | oit multiplexed forma | at as shown below.    |

|           |            |                 | Α                                            | В                                                                              | С                     | D                     |

| 10        | OP[0]      | Digital output  | d12                                          | d8                                                                             | d4                    | d0                    |

| 11        | OP[1]      | Digital output  | d13                                          | d9                                                                             | d5                    | d1                    |

| 12        | OP[2]      | Digital output  | d14                                          | d10                                                                            | d6                    | d2                    |

| 13        | OP[3]/SDO  | Digital output  | d15                                          | d11                                                                            | d7                    | d3                    |

|           |            |                 | address bit 4=1 and                          | [3]/SDO may be used t<br>SEN has been pulsed<br>section for further detail     | high. See Serial Inte |                       |

| 14        | AVDD       | Supply          | Analogue supply (3.3                         | 3V)                                                                            |                       |                       |

| 15        | AGND1      | Supply          | Analogue ground (0)                          | ∨).                                                                            |                       |                       |

| 16        | VRB        | Analogue output | Lower reference volt<br>This pin must be cor | tage.<br>nnected to AGND via a                                                 | decoupling capacito   | or.                   |

| 17        | VRT        | Analogue output | Upper reference volt<br>This pin must be cor | tage.<br>nnected to AGND via a                                                 | decoupling capacito   | or.                   |

| 18        | NC         | Not Connected   |                                              |                                                                                |                       |                       |

| 19        | VRLC/VBIAS | Analogue I/O    | This pin would typica                        | e output voltage for RLC<br>ally be connected to AG<br>ally driven if programm | SND via a decouplin   |                       |

| 20        | VINP       | Analogue input  | Video input pin.                             |                                                                                |                       |                       |

## **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                            | MIN        | MAX         |

|------------------------------------------------------|------------|-------------|

| Analogue supply voltage: AVDD                        | GND - 0.3V | GND + 4.2V  |

| Digital core supply voltage: DVDD1                   | GND - 0.3V | GND + 4.2V  |

| Digital IO supply voltage: DVDD2                     | GND - 0.3V | GND + 4.2V  |

| Digital ground: DGND                                 | GND - 0.3V | GND + 0.3V  |

| Analogue grounds AGND                                | GND - 0.3V | GND + 0.3V  |

| Digital inputs, digital outputs and digital I/O pins | GND - 0.3V | DVDD + 0.3V |

| Analogue input                                       | GND - 0.3V | AVDD + 0.3V |

| Other pins                                           | GND - 0.3V | AVDD + 0.3V |

| Operating temperature range: T <sub>A</sub>          | 0°C        | +70°C       |

Notes:

- 2. AGND and DGND pins are intended to be operated at the same potential. Differential voltages between these pins will degrade performance.

- AVDD and DVDD1 pins are intended to be operated at the same potential. Differential voltages between these pins will degrade performance.

## **RECOMMENDED OPERATING CONDITIONS**

| CONDITION                   | SYMBOL         | MIN  | ТҮР | МАХ  | UNITS |

|-----------------------------|----------------|------|-----|------|-------|

| Operating temperature range | T <sub>A</sub> | 0    |     | 70   | °C    |

| Analogue supply voltage     | AVDD           | 2.97 | 3.3 | 3.63 | V     |

| Digital Core supply voltage | DVDD1          | 2.97 | 3.3 | 3.63 | V     |

| Digital I/O supply voltage  | DVDD2          | 2.5  | 3.3 | 3.63 | V     |

<sup>1.</sup> GND denotes the voltage of any ground pin.

## **ELECTRICAL CHARACTERISTICS**

Test Conditions AVDD = DVDD1 = DVDD2 = 3.3V, AGND = DGND = 0V, T<sub>A</sub> =  $25^{\circ}$ C, MCLK = 36MHz, mode 1 unless otherwise stated.

| PARAMETER                                 | SYMBOL              | TEST<br>CONDITIONS                | MIN       | ТҮР   | MAX  | UNIT    |

|-------------------------------------------|---------------------|-----------------------------------|-----------|-------|------|---------|

| <b>Overall System Specification (incl</b> | uding 16-bit Al     | DC, PGA, Offset and CDS f         | unctions) | •     | •    |         |

| Full-scale input voltage range            |                     | Max Gain                          |           | 0.25  |      | Vp-р    |

| (see Note 1)                              |                     | Min Gain                          |           | 2.56  |      | Vp-p    |

| Input signal limits (see Note 2)          | V <sub>IN</sub>     |                                   | 0         |       | AVDD | V       |

| Full-scale transition error               |                     | Gain = 0dB;<br>PGA[7:0] = 07(hex) | -60       | 10    | +60  | mV      |

| Zero-scale transition error               |                     | Gain = 0dB;<br>PGA[7:0] = 07(hex) | -50       | 10    | +50  | mV      |

| Differential non-linearity                | DNL                 |                                   |           | 2.4   |      | LSB     |

| Integral non-linearity                    | INL                 |                                   |           | 17    |      | LSB     |

| Input referred noise                      |                     |                                   |           | 12    |      | LSB rms |

| References                                |                     |                                   |           |       |      |         |

| Upper reference voltage                   | VRT                 |                                   |           | 2.05  |      | V       |

| Lower reference voltage                   | VRB                 |                                   |           | 1.05  |      | V       |

| Diff. reference voltage (VRT-VRB)         | V <sub>RTB</sub>    |                                   | 0.95      | 1.0   | 1.05 | V       |

| Output resistance VRT, VRB, VRX           |                     |                                   |           | 1     |      | Ω       |

| VRLC/Reset-Level Clamp (RLC)              |                     |                                   |           |       |      |         |

| RLC switching impedance                   |                     |                                   | 20        | 50    | 100  | Ω       |

| VRLC short-circuit current                |                     |                                   | 1.6       | 2     | 4.5  | mA      |

| VRLC output resistance                    |                     |                                   |           | 2     |      | Ω       |

| VRLC Hi-Z leakage current                 |                     | VRLC = 0 to AVDD                  |           |       | 1    | μΑ      |

| RLCDAC resolution                         |                     |                                   |           | 4     |      | bits    |

| RLCDAC step size                          | VRLCSTEP            | RLCDACRNG = 0                     |           | 0.18  |      | V/step  |

|                                           | Γ                   | RLCDACRNG = 1                     |           | 0.123 |      | V/step  |

| RLCDAC output voltage at                  | V <sub>RLCBOT</sub> | RLCDACRNG = 0                     |           | 0.3   |      | V       |

| code 0(hex)                               |                     | RLCDACRNG = 1                     |           | 0.2   |      | V       |

| RLCDAC output voltage at                  | V <sub>RLCTOP</sub> | RLCDACRNG = 0                     |           | 3.0   |      | V       |

| code F(hex)                               |                     | RLCDACRNG = 1                     |           | 2.05  |      | V       |

| Offset DAC, Monotonicity Guarant          | teed                |                                   |           | 1     |      |         |

| Resolution                                |                     |                                   |           | 8     |      | bits    |

| Differential non-linearity                | DNL                 |                                   |           | 0.2   |      | LSB     |

| Integral non-linearity                    | INL                 |                                   |           | 0.6   |      | LSB     |

| Step size                                 | 1                   |                                   |           | 2.03  |      | mV/step |

| Output voltage                            | 1                   | Code 00(hex)                      |           | -260  |      | mV      |

| ·                                         |                     | Code FF(hex)                      |           | +260  |      | mV      |

Notes:

1. Full-scale input voltage denotes the peak input signal amplitude that can be gained to match the ADC input range.

Input signal limits are the limits within which the full-scale input voltage signal must lie. 2.

#### **Test Conditions**

AVDD = DVDD1 = DVDD2 = 3.3V, AGND = DGND = 0V,  $T_A = 25^{\circ}C$ , MCLK = 36MHz unless otherwise stated.

| PARAMETER                                                  | SYMBOL             | TEST<br>CONDITIONS    | MIN         | TYP                                   | MAX         | UNIT |

|------------------------------------------------------------|--------------------|-----------------------|-------------|---------------------------------------|-------------|------|

| Programmable Gain Amplifier                                |                    |                       |             |                                       |             |      |

| Resolution                                                 |                    |                       |             | 8                                     |             | bits |

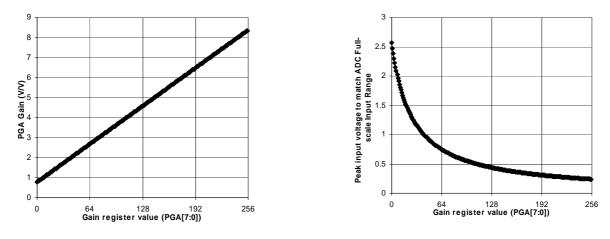

| Gain equation                                              |                    |                       | 0.7         | $8 + \frac{PGA[7:0] \times 7.5}{255}$ | 57          | V/V  |

| Max gain                                                   | G <sub>MAX</sub>   |                       | 8.2         | 8.35                                  | 8.8         | V/V  |

| Min gain                                                   | G <sub>MIN</sub>   |                       | 0.75        | 0.78                                  | 0.87        | V/V  |

| Internal channel offset                                    | V <sub>OFF</sub>   |                       |             | 10                                    |             | mV   |

| Analogue to Digital Converter                              |                    |                       |             |                                       | •           |      |

| Resolution                                                 |                    |                       |             | 16                                    |             | bits |

| Maximum Speed                                              |                    |                       |             |                                       | 6           | MSPS |

| Full-scale input range                                     | V <sub>FS</sub>    |                       |             | 2.0                                   |             | V    |

| (2*(VRT-VRB))                                              |                    |                       |             |                                       |             |      |

| DIGITAL SPECIFICATIONS                                     |                    |                       |             |                                       | •           |      |

| Digital Inputs                                             |                    |                       |             |                                       |             |      |

| High level input voltage                                   | VIH                |                       | 0.8 * DVDD2 |                                       |             | V    |

| Low level input voltage                                    | VIL                |                       |             |                                       | 0.2 * DVDD2 | V    |

| High level input current                                   | IIH                |                       |             |                                       | 1           | μΑ   |

| Low level input current                                    | I <sub>IL</sub>    |                       |             |                                       | 1           | μA   |

| Input capacitance                                          | Cı                 |                       |             | 5                                     |             | pF   |

| Digital Outputs                                            |                    |                       |             |                                       |             |      |

| High level output voltage                                  | V <sub>OH</sub>    | I <sub>OH</sub> = 1mA | DVDD2 - 0.5 |                                       |             | V    |

| Low level output voltage                                   | V <sub>OL</sub>    | I <sub>OL</sub> = 1mA |             |                                       | 0.5         | V    |

| Supply Currents                                            |                    |                       |             |                                       |             |      |

| Total supply current – active                              |                    |                       |             | 45.9                                  |             | mA   |

| Total analogue AVDD, supply current – active               | I <sub>AVDD</sub>  |                       |             | 39.6                                  |             | mA   |

| Total digital core, DVDD1,<br>supply current – active      | I <sub>DVDD1</sub> |                       |             | 3                                     |             | mA   |

| Digital I/O supply current,<br>DVDD2 – active (see note 3) | I <sub>DVDD2</sub> |                       |             | 3.3                                   |             | mA   |

| Supply current – full power down mode                      |                    |                       |             | 30                                    | 200         | μA   |

Notes:

1. Digital I/O supply current depends on the capacitive load attached to the pin. The Digital I/O supply current is measured with approximately 50pF attached to the pin.

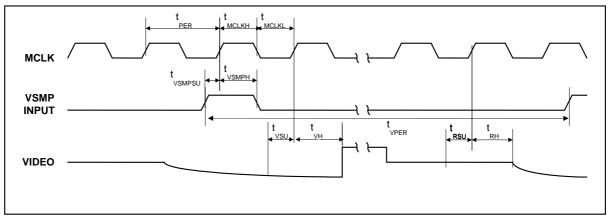

## **INPUT VIDEO SAMPLING**

#### Note:

1. See Page 15 (Programmable VSMP Detect Circuit) for video sampling description.

#### **Test Conditions**

AVDD = DVDD1 = DVDD2 = 3.3V, AGND = DGND = 0V, T<sub>A</sub> =  $25^{\circ}$ C, MCLK = 36MHz unless otherwise stated.

| PARAMETER               | SYMBOL              | TEST CONDITIONS | MIN   | TYP | MAX  | UNITS |

|-------------------------|---------------------|-----------------|-------|-----|------|-------|

| MCLK period             | t <sub>PER</sub>    |                 | 27.7  |     |      | ns    |

| MCLK high period        | t <sub>MCLKH</sub>  |                 | 13.85 |     |      | ns    |

| MCLK low period         | t <sub>MCLKL</sub>  |                 | 13.85 |     |      | ns    |

| VSMP period             | t <sub>VPER</sub>   |                 | 300   |     | 1000 | ns    |

| VSMP set-up time        | t <sub>VSMPSU</sub> |                 | 6     |     |      | ns    |

| VSMP hold time          | t <sub>VSMPH</sub>  |                 | 3     |     |      | ns    |

| Video level set-up time | t <sub>VSU</sub>    |                 | 10    |     |      | ns    |

| Video level hold time   | t <sub>VH</sub>     |                 | 3     |     |      | ns    |

| Reset level set-up time | t <sub>RSU</sub>    |                 | 10    |     |      | ns    |

| Reset level hold time   | t <sub>RH</sub>     |                 | 3     |     |      | ns    |

#### Notes:

1.  $t_{\text{VSU}}$  and  $t_{\text{RSU}}$  denote the set-up time required after the input video signal has settled.

2. Parameters are measured at 50% of the rising/falling edge.

#### **OUTPUT DATA TIMING**

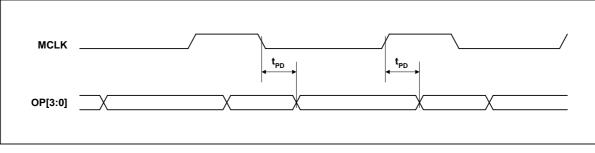

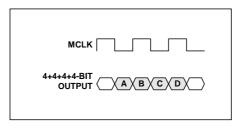

Figure 2 Output Data Timing

#### Test Conditions

AVDD = DVDD1 = DVDD2 = 3.3V, AGND = DGND = 0V, T<sub>A</sub> =  $25^{\circ}C$ , MCLK = 36MHz unless otherwise stated.

| PARAMETER                           | SYMBOL          | TEST CONDITIONS                              | MIN | TYP | MAX | UNITS |

|-------------------------------------|-----------------|----------------------------------------------|-----|-----|-----|-------|

| Output propagation delay OPDLY = 00 | t <sub>PD</sub> | $I_{OH} = 1 \text{mA}, I_{OL} = 1 \text{mA}$ | 5   | 9   | 13  | ns    |

| Output propagation delay OPDLY = 01 | t <sub>PD</sub> | $I_{OH} = 1 \text{mA}, I_{OL} = 1 \text{mA}$ | 8   | 12  | 16  | ns    |

| Output propagation delay OPDLY = 10 | t <sub>PD</sub> | $I_{OH} = 1$ mA, $I_{OL} = 1$ mA             | 9   | 13  | 17  | ns    |

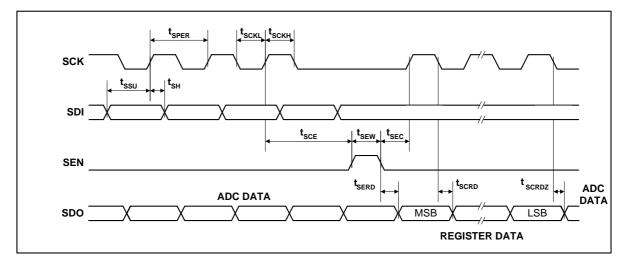

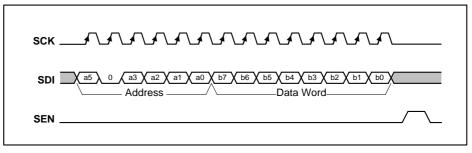

#### SERIAL INTERFACE

#### Figure 3 Serial Interface Timing

#### **Test Conditions**

AVDD = DVDD1 = DVDD2 = 3.3V, AGND = DGND = 0V, T<sub>A</sub> = 25°C, MCLK = 36MHz unless otherwise stated.

| PARAMETER                      | SYMBOL             | TEST CONDITIONS | MIN  | TYP | MAX | UNITS |

|--------------------------------|--------------------|-----------------|------|-----|-----|-------|

| SCK period                     | t <sub>SPER</sub>  |                 | 41.6 |     |     | ns    |

| SCK high                       | t <sub>scкн</sub>  |                 | 18.8 |     |     | ns    |

| SCK low                        | t <sub>SCKL</sub>  |                 | 18.8 |     |     | ns    |

| SDI set-up time                | t <sub>SSU</sub>   |                 | 6    |     |     | ns    |

| SDI hold time                  | t <sub>SH</sub>    |                 | 6    |     |     | ns    |

| SCK to SEN set-up time         | t <sub>SCE</sub>   |                 | 12   |     |     | ns    |

| SEN to SCK set-up time         | t <sub>SEC</sub>   |                 | 12   |     |     | ns    |

| SEN pulse width                | t <sub>SEW</sub>   |                 | 25   |     |     | ns    |

| SEN low to SDO = Register data | t <sub>SERD</sub>  |                 |      |     | 30  | ns    |

| SCK low to SDO = Register data | t <sub>SCRD</sub>  |                 |      |     | 30  | ns    |

| SCK low to SDO = ADC data      | t <sub>SCRDZ</sub> |                 |      |     | 30  | ns    |

Note:

1. Parameters are measured at 50% of the rising/falling edge

#### **DEVICE DESCRIPTION**

#### INTRODUCTION

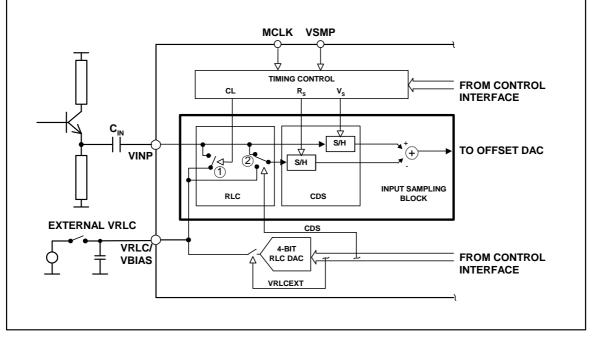

A block diagram of the device showing the signal path is presented on Page 1.

The WM8253 processes the sampled video signal on VINP with respect to the video-reset level or an internally/externally generated reference level through the analogue-processing channel.

This processing channel consists of an Input Sampling block with optional Reset Level Clamping (RLC) and Correlated Double Sampling (CDS), an 8-bit programmable offset DAC and an 8-bit Programmable Gain Amplifier (PGA).

The ADC then converts each resulting analogue signal to a 16-bit digital word. The digital output from the ADC is presented on a 4-bit wide bus.

On-chip control registers determine the configuration of the device, including the offsets and gains applied to each channel. These registers are programmable via a serial interface.

#### **INPUT SAMPLING**

The WM8253 has a single analogue processing channel and ADC, which can be used in a flexible manner to process both monochrome and line-by-line colour inputs.

**Monochrome:** The selected input (VINP) is sampled, processed by the analogue channel, and converted by the ADC. The same offset DAC and PGA register values are always applied.

**Colour Line-by-Line:** VINP is sampled and processed by the analogue channel before being converted by the ADC. The gains and offset register values applied to the PGA and offset DAC can be switched between the independent Red, Green and Blue digital registers (e.g. Red  $\rightarrow$  Green $\rightarrow$  Blue  $\rightarrow$  Red...) at the start of each line in order to facilitate line-by-line colour operation. The INTM[1:0] bits determine which register contents are applied (see Table 1) to the PGA and offset DAC. By using the INTM[1:0] bits to select the desired register values only one register write is required at the start of each new colour line.

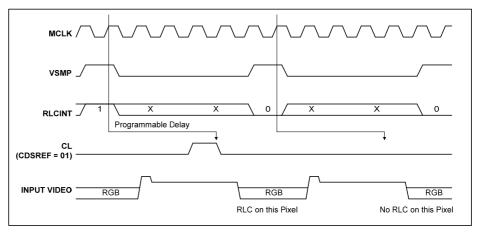

#### **RESET LEVEL CLAMPING (RLC)**

To ensure that the signal applied to the WM8253 VINP pin lies within the valid input range (0V to AVDD) the CCD output signal is usually level shifted by coupling through a capacitor,  $C_{IN}$ . When active, the RLC circuit clamps the WM8253 side of this capacitor to a suitable voltage during the CCD reset period. The RLCINT register bit controls is used to activate the Reset Level Clamp circuit.

A typical input configuration is shown in Figure 4. The Timing Control Block generates a clamp pulse, CL, from MCLK and VSMP (when RLCINT is high). When CL is active the voltage on the WM8253 side of C<sub>IN</sub>, at VINP, is forced to the VRLC/VBIAS voltage (V<sub>VRLC</sub>) by switch 1. When the CL pulse turns off, the voltage at VINP initially remains at V<sub>VRLC</sub> but any subsequent variation in sensor voltage (from reset to video level) will couple through C<sub>IN</sub> to VINP.

RLC is compatible with both CDS and non-CDS operating modes, as selected by switch 2. Refer to the CDS/non-CDS Processing section.

Figure 4 Reset Level Clamping and CDS Circuitry

Reset Level Clamping is controlled by register bit RLCINT. Figure 5 illustrates the effect of the RLCINT bit for a typical CCD waveform, with CL applied during the reset period.

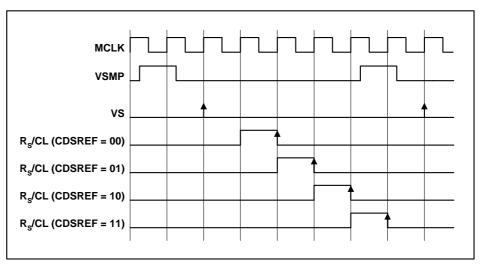

The RLCINT register bit is sampled on the positive edge of MCLK that occurs during each VSMP pulse. The sampled level, high (or low) controls the presence (or absence) of the internal CL pulse on the next reset level. The position of CL can be adjusted by using control bits CDSREF[1:0] (Figure 6).

#### Figure 5 Relationship of RLCINT, MCLK and VSMP to Internal Clamp Pulse, CL

The VRLC/VBIAS pin can be driven internally by a 4-bit DAC (RLCDAC) by writing to control bits RLCV[3:0]. The RLCDAC range and step size may be increased by writing to control bit RLCDACRNG. Alternatively, the VRLC/VBIAS pin can be driven externally by writing to control bit VRLCEXT to disable the RLCDAC and then applying a d.c. voltage to the pin.

#### **CDS/NON-CDS PROCESSING**

For CCD type input signals, the signal may be processed using CDS, which will remove pixel-by-pixel common mode noise. For CDS operation, the video level is processed with respect to the video reset level, regardless of whether RLC has been performed. To sample using CDS, control bit CDS must be set to 1 (default), this controls switch 2 (Figure 4) and causes the signal reference to come from the video reset level. The time at which the reset level is sampled, by clock R<sub>s</sub>/CL, is adjustable by programming control bits CDSREF[1:0], as shown in Figure 6.

#### Figure 6 Reset Sample and Clamp Timing

For CIS type sensor signals, non-CDS processing is used. In this case, the video level is processed with respect to the voltage on pin VRLC/VBIAS, generated internally or externally as described above. The VRLC/VBIAS pin is sampled by  $R_{\rm s}$  at the same time as  $V_{\rm s}$  samples the video level in this mode.

#### OFFSET ADJUST AND PROGRAMMABLE GAIN

The output from the CDS block is a differential signal, which is added to the output of an 8-bit Offset DAC to compensate for offsets and then amplified by an 8-bit PGA. The gain and offset can be set for each of three colours by writing to control bits DACx[7:0] and PGAx[7:0] (where x can be R, G or B).

In colour line-by-line mode the gain and offset coefficients that are applied to the PGA and offset DAC can be multiplexed by control of the INTM[1:0] bits as shown in Table 1.

| INTM[1:0] | DESCRIPTION                                                                               |

|-----------|-------------------------------------------------------------------------------------------|

| 00        | Red offset and gain registers are applied to offset DAC and PGA (DACR[7:0] and PGAR[7:0]) |

| 01        | Green offset and gain registers applied to offset DAC and PGA (DACG[7:0] and PGAG[7:0])   |

| 10        | Blue offset and gain registers applied to offset DAC and PGA (DACB[7:0] and PGAB[7:0])    |

| 11        | Reserved.                                                                                 |

Table 1 Offset DAC and PGA Register Control

The gain characteristic of the WM8253 PGA is shown in Figure 7. Figure 8 shows the maximum input voltage (at VINP) that can be gained up to match the ADC full-scale input range (2.0V).

Figure 7 PGA Gain Characteristic

#### ADC INPUT BLACK LEVEL ADJUST

The output from the PGA should be offset to match the full-scale range of the ADC ( $V_{FS} = 2.0V$ ). For negative-going input video signals, a black level (zero differential) output from the PGA should be offset to the top of the ADC range by setting register bits PGAFS[1:0]=10. For positive going input signal the black level should be offset to the bottom of the ADC range by setting PGAFS[1:0]=11. Bipolar input video is accommodated by setting PGAFS[1:0]=00 or PGAFS[1:0]=01 (zero differential input voltage gives mid-range ADC output).

#### **OVERALL SIGNAL FLOW SUMMARY**

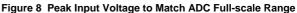

Figure 9 represents the processing of the video signal through the WM8253.

Figure 9 Overall Signal Flow

The **INPUT SAMPLING BLOCK** produces an effective input voltage V<sub>1</sub>. For CDS, this is the difference between the input video level V<sub>IN</sub> and the input reset level V<sub>RESET</sub>. For non-CDS this is the difference between the input video level V<sub>IN</sub> and the voltage on the VRLC/VBIAS pin, V<sub>VRLC</sub>, optionally set via the RLC DAC.

The **OFFSET DAC BLOCK** then adds the amount of fine offset adjustment required to move the black level of the input signal towards 0V, producing  $V_2$ .

The **PGA BLOCK** then amplifies the white level of the input signal to maximise the ADC range, outputting voltage  $V_3$ .

The ADC BLOCK then converts the analogue signal, V<sub>3</sub>, to a 16-bit unsigned digital output, D<sub>1</sub>.

The digital output is then inverted, if required, through the OUTPUT INVERT BLOCK to produce D2.

PD, Rev 4.1, August 2011

#### CALCULATING OUTPUT FOR ANY GIVEN INPUT

The following equations describe the processing of the video and reset level signals through the WM8253.

#### INPUT SAMPLING BLOCK: INPUT SAMPLING AND REFERENCING

If CDS = 1, (i.e. CDS operation) the previously sampled reset level,  $V_{\text{RESET}}$ , is subtracted from the input video.

$V_1 = V_{IN} - V_{RESET}$  ..... Eqn. 1

If CDS = 0, (non-CDS operation) the simultaneously sampled voltage on pin VRLC is subtracted instead.

$V_1 = V_{IN} - V_{VRLC}$  ..... Eqn. 2

If VRLCEXT = 1,  $V_{VRLC}$  is an externally applied voltage on pin VRLC/VBIAS.

If VRLCEXT = 0,  $V_{VRLC}$  is the output from the internal RLC DAC.

$V_{VRLC}$  = ( $V_{RLCSTEP} * RLCV[3:0]$ ) +  $V_{RLCBOT}$  ...... Eqn. 3

V<sub>RLCSTEP</sub> is the step size of the RLC DAC and V<sub>RLCBOT</sub> is the minimum output of the RLC DAC.

#### OFFSET DAC BLOCK: OFFSET (BLACK-LEVEL) ADJUST

The resultant signal  $V_1$  is added to the Offset DAC output.

#### PGA NODE: GAIN ADJUST

The signal is then multiplied by the PGA gain,

$V_3 = V_2 * [0.78 + (PGA[7:0]*7.57)/255]$  ..... Eqn. 5

#### ADC BLOCK: ANALOGUE-DIGITAL CONVERSION

The analogue signal is then converted to a 16-bit unsigned number, with input range configured by PGAFS[1:0].

| $\mathbf{D}_{1}[15:0] = INT\{ (\mathbf{V}_{3}/V_{FS}) * 65535\} + 32767$ | PGAFS[1:0] = 00 or 01 | Eqn. 6 |

|--------------------------------------------------------------------------|-----------------------|--------|

|--------------------------------------------------------------------------|-----------------------|--------|

| $D_1[15:0] = INT\{ (V_3/V_{FS}) * 65535\}$ PGA | AFS[1:0] = 11 Eqn. 7 | 7 |

|------------------------------------------------|----------------------|---|

|------------------------------------------------|----------------------|---|

$D_1[15:0] = INT\{ (V_3/V_{ES}) * 65535\} + 65535 PGAFS[1:0] = 10 \dots Eqn. 8$

where the ADC full-scale range,  $V_{\text{FS}}$  = 2.0V

if  $D_1[15:0] < 0$   $D_1[15:0] = 0$

if **D**<sub>1</sub>[15:0] > 65535 **D**<sub>1</sub>[15:0] = 65535

#### **OUTPUT INVERT BLOCK: POLARITY ADJUST**

The polarity of the digital output may be inverted by control bit INVOP.

| $D_2[15:0] = D_1[15:0]$         | (INVOP = 0) | Eqn. 9  |

|---------------------------------|-------------|---------|

| $D_2[15:0] = 65535 - D_1[15:0]$ | (INVOP = 1) | Eqn. 10 |

## **OUTPUT DATA FORMAT**

The digital data output from the ADC is available to the user in 4-bit wide multiplexed. Latency of valid output data with respect to VSMP is programmable by writing to control bits DEL[1:0]. The latency for each mode is shown in the Operating Mode Timing Diagrams section.

Figure 10 shows the output data formats for all modes. Table 2 summarises the output data obtained for each format.

Figure 10 Output Data Formats (Modes 1, 3, 4)

| OUTPUT<br>FORMAT        | OUTPUT<br>PINS | OUTPUT                                                                                     |

|-------------------------|----------------|--------------------------------------------------------------------------------------------|

| 4+4+4+4-bit<br>(nibble) | OP[3:0]        | A = d15, d14, d13, d12<br>B = d11, d10, d9, d8<br>C = d7, d6, d5, d4<br>D = d3, d2, d1, d0 |

Table 2 Details of Output Data Shown in Figure 10

#### **CONTROL INTERFACE**

The internal control registers are programmable via the serial digital control interface. The register contents can be read back via the serial interface on pin OP[3]/SDO.

It is recommended that a software reset is carried out after the power-up sequence, before writing to any other register. This ensures that all registers are set to their default values (as shown in Table 4).

#### SERIAL INTERFACE: REGISTER WRITE

Figure 11 shows register writing in serial mode. Three pins, SCK, SDI and SEN are used. A six-bit address (a5, 0, a3, a2, a1, a0) is clocked in through SDI, MSB first, followed by an eight-bit data word (b7, b6, b5, b4, b3, b2, b1, b0), also MSB first. Each bit is latched on the rising edge of SCK. When the data has been shifted into the device, a pulse is applied to SEN to transfer the data to the appropriate internal register. Note all valid registers have address bit a4 equal to 0 in write mode.

Figure 11 Serial Interface Register Write

A software reset is carried out by writing to Address "000100" with any value of data, (i.e. Data Word = XXXXXXXX.

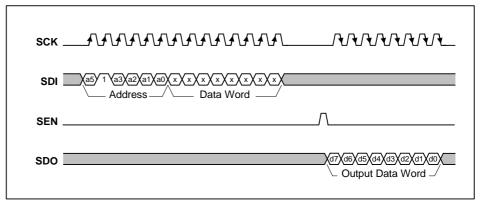

#### SERIAL INTERFACE: REGISTER READ-BACK

Figure 12 shows register read-back in serial mode. Read-back is initiated by writing to the serial bus as described above but with address bit a4 set to 1, followed by an 8-bit dummy data word. Writing address (a5, 1, a3, a2, a1, a0) will cause the contents (d7, d6, d5, d4, d3, d2, d1, d0) of corresponding register (a5, 0, a3, a2, a1, a0) to be output MSB first on pin SDO (on the falling edge of SCK). Note that pin SDO is shared with an output pin, OP[3], so no data can be read when reading from a register. The next word may be read in to SDI while the previous word is still being output on SDO.

Figure 12 Serial Interface Register Read-back

#### TIMING REQUIREMENTS

To use this device a master clock (MCLK) of up to 36MHz and a per-pixel synchronisation clock (VSMP) of up to 6MHz are required. These clocks drive a timing control block, which produces internal signals to control the sampling of the video signal. MCLK to VSMP ratios and maximum sample rates for the various modes are shown in Table 3.

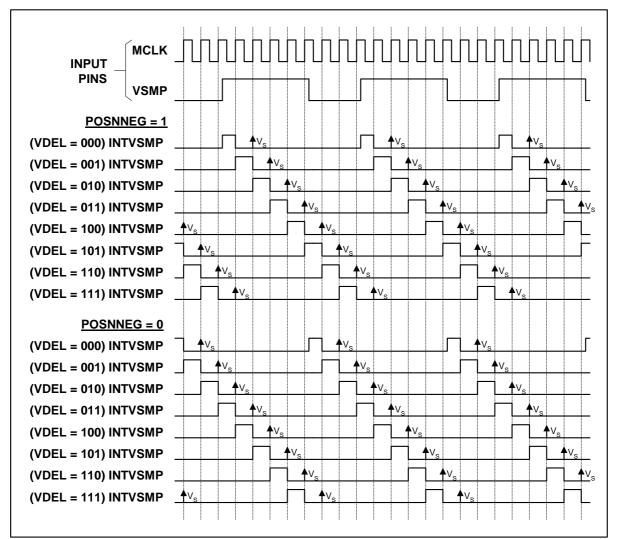

#### PROGRAMMABLE VSMP DETECT CIRCUIT

The VSMP input is used to determine the sampling point and frequency of the WM8253. Under normal operation a pulse of 1 MCLK period should be applied to VSMP at the desired sampling frequency (as shown in the Operating Mode Timing Diagrams) and the input sample will be taken on the first rising MCLK edge after VSMP has gone low. However, in certain applications such a signal may not be readily available. The programmable VSMP detect circuit in the WM8253 allows the sampling point to be derived from any signal of the correct frequency, such as a CCD shift register clock, when applied to the VSMP pin.

When enabled, by setting the VSMPDET control bit, the circuit detects either a rising or falling edge (determined by POSNNEG control bit) on the VSMP input pin and generates an internal VSMP pulse. This pulse can optionally be delayed by a number of MCLK periods, specified by the VDEL[2:0] bits. Figure 13 shows the internal VSMP pulses that can be generated by this circuit for a typical clock input signal. The internal VSMP pulse is then applied to the timing control block in place of the normal VSMP pulse provided from the input pin. The sampling point then occurs on the first rising MCLK edge after this internal VSMP pulse, as shown in the Operating Mode Timing Diagrams.

Figure 13 Internal VSMP Pulses Generated by Programmable VSMP Detect Circuit

#### REFERENCES

The ADC reference voltages are derived from an internal bandgap reference, and buffered to pins VRT and VRB, where they must be decoupled to ground. The output buffer from the RLCDAC also requires decoupling at pin VRLC/VBIAS when this is configured as an output.

#### **POWER SUPPLY**

The WM8253 runs from a 3.3V single supply.

#### **POWER MANAGEMENT**

Power management for the device is performed via the Control Interface. The device can be powered on or off completely by setting the EN bit low.

All the internal registers maintain their previously programmed value in power down mode and the Control Interface inputs remain active.

#### **OPERATING MODES**

Table 3 summarises the most commonly used modes, the clock waveforms required and the register contents required for CDS and non-CDS operation.

| MODE | DESCRIPTION                                         | CDS<br>AVAILABLE | MAX<br>SAMPLE<br>RATE | TIMING<br>REQUIREMENTS                                      | REGISTER<br>CONTENTS WITH<br>CDS                                          | REGISTER<br>CONTENTS<br>WITHOUT CDS |

|------|-----------------------------------------------------|------------------|-----------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------|

| 1    | Monochrome/<br>Colour Line-by-Line                  | Yes              | 6MSPS                 | MCLK max = 36MHz<br>MCLK:VSMP ratio is<br>6:1               | SetReg1: 03(hex)                                                          | SetReg1: 01(hex)                    |

| 2    | Fast Monochrome/<br>Colour Line-by-Line             | Yes              | 6MSPS                 | MCLK max = 18MHz<br>MCLK:VSMP ratio is<br>3:1               | Identical to Mode<br>1 plus SetReg3:<br>bits 5:4 must be<br>set to 0(hex) | Identical to<br>Mode 1              |

| 3    | Maximum speed<br>Monochrome/<br>Colour Line-by-Line | No               | 6MSPS                 | MCLK max = 12MHz<br>MCLK:VSMP ratio is<br>2:1               | CDS not possible                                                          | SetReg1: 41(hex)                    |

| 4    | Slow Monochrome/<br>Colour Line-by-Line             | Yes              | 4.5MSPS               | MCLK max = $36MHz$<br>MCLK:VSMP ratio is<br>$2n:1, n \ge 4$ | Identical to<br>Mode 1                                                    | Identical to<br>Mode 1              |

Table 3 WM8253 Operating Modes

#### **OPERATING MODE TIMING DIAGRAMS**

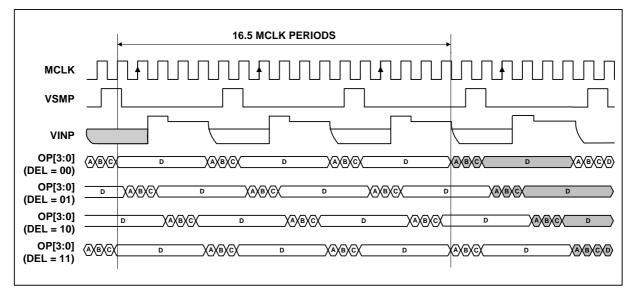

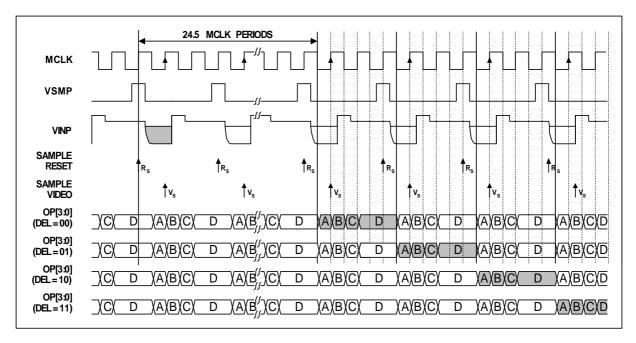

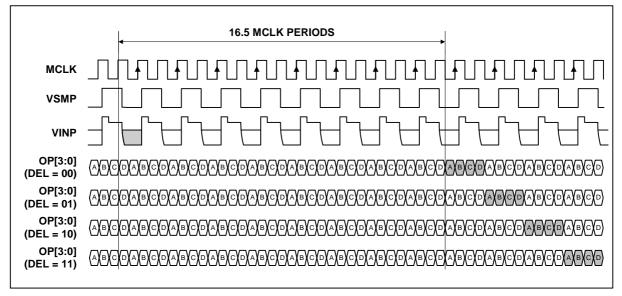

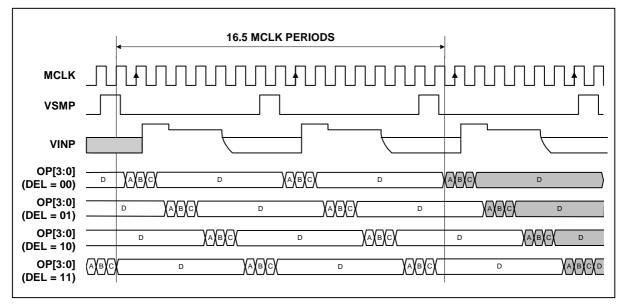

The following diagrams show 4-bit multiplexed output data and MCLK, VSMP and input video requirements for operation of the most commonly used modes as shown in Table 3. The diagrams are identical for both CDS and non-CDS operation.

Note that for extended Mode 4 operation (MCLK:VSMP ratios of 2n:1 where  $n \ge 4$ ) the latency is given by:

Latency (in MCLK periods) = 16.5 + (n-4) \* 2

Figure 14 Mode 1 Operation

Figure 15 Mode 2 Operation

Production Data

Figure 16 Mode 3 Operation

Figure 17 Mode 4 Operation (MCLK:VSMP Ratio = 8:1)

## **DEVICE CONFIGURATION**

## **REGISTER MAP**

The following table describes the location of each control bit used to determine the operation of the WM8253. The register map is programmed by writing the required codes to the appropriate addresses via the serial interface.

| ADDRESS         | DESCRIPTION          | DEF   | RW | BIT         |             |            |            |          |         |         |         |

|-----------------|----------------------|-------|----|-------------|-------------|------------|------------|----------|---------|---------|---------|

| <a5:a0></a5:a0> |                      | (hex) |    | b7          | b6          | b5         | b4         | b3       | b2      | b1      | b0      |

| 000001          | Setup Reg 1          | 03    | RW | 0           | MODE3       | PGAFS[1]   | PGAFS[0]   | 0        | 0       | CDS     | EN      |

| 000010          | Setup Reg 2          | 23    | RW | DEL[1]      | DEL[0]      | RLCDACRNG  | 0          | VRLCEXT  | INVOP   | 1       | 1       |

| 000011          | Setup Reg 3          | 1F    | RW | 0           | 0           | CDSREF [1] | CDSREF [0] | RLCV[3]  | RLCV[2] | RLCV[1] | RLCV[0] |

| 000100          | Software Reset       | 00    | W  |             |             |            |            |          |         |         |         |

| 000110          | Setup Reg 4          | 05    | RW | 0           | 0           | INTM[1]    | INTM[0]    | INTRLC   | 1       | 0       | 1       |

| 001000          | Setup Reg 5          | 00    | RW | 0           | 0           | 0          | POSNNEG    | VDEL[2]  | VDEL[1] | VDEL[0] | VSMPDET |

| 001001          | Setup Reg 6          | 16    | RW | 0           | 0           | 0          | OPDLY[1]   | OPDLY[0] | 1       | 1       | 0       |

| 001010          | Reserved             | 00    | RW | 0           | 0           | 0          | 0          | 0        | 0       | 0       | 0       |

| 001011          | Reserved             | 00    | RW | 0           | 0           | 0          | 0          | 0        | 0       | 0       | 0       |

| 001100          | Reserved             | 00    | RW | 0           | 0           | 0          | 0          | 0        | 0       | 0       | 0       |

| 001101          | Reserved             | 00    | RW | 0           | 0           | 0          | 0          | 0        | 0       | 0       | 0       |

| 001110          | Reserved             | 00    | R  | 0           | 0           | 0          | 0          | 0        | 0       | 0       | 0       |

| 001111          | Reserved             | 00    | R  | 0           | 0           | 0          | 0          | 0        | 0       | 0       | 0       |

| 100000          | DAC Value (Red)      | 80    | RW | DACR[7<br>] | DACR[6<br>] | DACR[5]    | DACR[4]    | DACR[3]  | DACR[2] | DACR[1] | DACR[0] |

| 100001          | DAC Value<br>(Green) | 80    | RW | DACG[7]     | DACG[6]     | DACG[5]    | DACG[4]    | DACG[3]  | DACG[2] | DACG[1] | DACG[0] |

| 100010          | DAC Value (Blue)     | 80    | RW | DACB[7]     | DACB[6]     | DACB[5]    | DACB[4]    | DACB[3]  | DACB[2] | DACB[1] | DACB[0] |

| 100011          | DAC Value<br>(RGB)   | 80    | W  | DAC[7]      | DAC[6]      | DAC[5]     | DAC[4]     | DAC[3]   | DAC[2]  | DAC[1]  | DAC[0]  |

| 101000          | PGA Gain (Red)       | 00    | RW | PGAR[7<br>] | PGAR[6<br>] | PGAR[5]    | PGAR[4]    | PGAR[3]  | PGAR[2] | PGAR[1] | PGAR[0] |

| 101001          | PGA Gain<br>(Green)  | 00    | RW | PGAG[7]     | PGAG[6]     | PGAG[5]    | PGAG[4]    | PGAG[3]  | PGAG[2] | PGAG[1] | PGAG[0] |

| 101010          | PGA Gain (Blue)      | 00    | RW | PGAB[7]     | PGAB[6]     | PGAB[5]    | PGAB[4]    | PGAB[3]  | PGAB[2] | PGAB[1] | PGAB[0] |

| 101011          | PGA Gain (RGB)       | 00    | W  | PGA[7]      | PGA[6]      | PGA[5]     | PGA[4]     | PGA[3]   | PGA[2]  | PGA[1]  | PGA[0]  |

Table 4 Register Map

## **REGISTER MAP DESCRIPTION**

| 0<br>1<br>2<br>3<br>5:4<br>6<br>7<br>1:0<br>2<br>3<br>4 | EN<br>CDS<br>Reserved<br>Reserved<br>PGAFS[1:0]<br>MODE3<br>MODE3<br>Reserved<br>Reserved<br>INVOP | 1<br>1<br>0<br>0<br>00<br>0<br>11<br>0                                                                                                                                                | 0 = complete power down, 1 = fully active.         Select correlated double sampling mode: 0 = single ended mode,<br>1 = CDS mode.         Must be set to zero         Must be set to Zero         Offsets PGA output to optimise the ADC range for different polarity sensor<br>output signals. Zero differential PGA input signal gives:         00 = Zero output       10 = Full-scale positive output<br>(use for bipolar video)         01 = Zero output       11 = Full-scale negative output<br>(use for positive going video)         01 = Zero output       11 = Full-scale negative output<br>(use for positive going video)         This bit must be set when operating in MODE3 (MCLK:VSMP=2:1) 0 =<br>other modes, 1 = MODE3.         NB, when in this mode the CDSREF bits should also be set to 01 to allow<br>clamping to operate correctly.         Must be set to zero         Must be set to One         Digitally inverts the polarity of output data.         0 = negative going video gives negative going output, |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2<br>3<br>5:4<br>6<br>7<br>1:0<br>2<br>3                | Reserved<br>PGAFS[1:0]<br>MODE3<br>Reserved<br>Reserved<br>INVOP                                   | 0<br>0<br>00<br>00<br>0<br>11                                                                                                                                                         | 1 = CDS mode.         Must be set to zero         Must be set to Zero         Offsets PGA output to optimise the ADC range for different polarity sensor output signals. Zero differential PGA input signal gives:         00 = Zero output       10 = Full-scale positive output (use for bipolar video)         01 = Zero output       11 = Full-scale negative going video)         01 = Zero output       11 = Full-scale negative output (use for positive going video)         01 = Zero output       11 = Full-scale negative output (use for positive going video)         This bit must be set when operating in MODE3 (MCLK:VSMP=2:1) 0 = other modes, 1 = MODE3.         NB, when in this mode the CDSREF bits should also be set to 01 to allow clamping to operate correctly.         Must be set to zero         Must be set to One         Digitally inverts the polarity of output data.                                                                                                                                 |  |  |  |

| 3<br>5:4<br>6<br>7<br>1:0<br>2<br>3                     | Reserved<br>PGAFS[1:0]<br>MODE3<br>Reserved<br>Reserved<br>INVOP                                   | 0<br>00<br>0<br>0<br>11                                                                                                                                                               | Must be set to Zero         Offsets PGA output to optimise the ADC range for different polarity sensor output signals. Zero differential PGA input signal gives:         00 = Zero output       10 = Full-scale positive output (use for bipolar video)         01 = Zero output       11 = Full-scale negative going video)         01 = Zero output       11 = Full-scale negative output (use for positive going video)         01 = Zero output       11 = Full-scale negative output (use for positive going video)         This bit must be set when operating in MODE3 (MCLK:VSMP=2:1) 0 = other modes, 1 = MODE3.         NB, when in this mode the CDSREF bits should also be set to 01 to allow clamping to operate correctly.         Must be set to zero         Must be set to One         Digitally inverts the polarity of output data.                                                                                                                                                                                   |  |  |  |

| 5:4<br>6<br>7<br>1:0<br>2<br>3                          | PGAFS[1:0]<br>MODE3<br>Reserved<br>Reserved<br>INVOP                                               | 00<br>0<br>0<br>11                                                                                                                                                                    | Offsets PGA output to optimise the ADC range for different polarity sensor output signals. Zero differential PGA input signal gives:         00 = Zero output       10 = Full-scale positive output (use for hipolar video)         01 = Zero output       11 = Full-scale negative output (use for negative output (use for positive going video)         01 = Zero output       11 = Full-scale negative output (use for positive going video)         01 = Zero output       11 = Full-scale negative output (use for positive going video)         This bit must be set when operating in MODE3 (MCLK:VSMP=2:1) 0 = other modes, 1 = MODE3.         NB, when in this mode the CDSREF bits should also be set to 01 to allow clamping to operate correctly.         Must be set to zero         Must be set to One         Digitally inverts the polarity of output data.                                                                                                                                                             |  |  |  |

| 6<br>7<br>1:0<br>2<br>3                                 | MODE3<br>Reserved<br>Reserved<br>INVOP                                                             | 0<br>0<br>11                                                                                                                                                                          | output signals. Zero differential PGA input signal gives:         00 = Zero output       10 = Full-scale positive output<br>(use for bipolar video)         01 = Zero output       11 = Full-scale negative output<br>(use for positive going video)         This bit must be set when operating in MODE3 (MCLK:VSMP=2:1) 0 =<br>other modes, 1 = MODE3.         NB, when in this mode the CDSREF bits should also be set to 01 to allow<br>clamping to operate correctly.         Must be set to Zero         Must be set to One         Digitally inverts the polarity of output data.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 7<br>1:0<br>2<br>3                                      | Reserved<br>Reserved<br>INVOP                                                                      | 0 11                                                                                                                                                                                  | (use for bipolar video)       (use for negative going video)         01 = Zero output       11 = Full-scale negative output<br>(use for positive going video)         This bit must be set when operating in MODE3 (MCLK:VSMP=2:1) 0 =<br>other modes, 1 = MODE3.         NB, when in this mode the CDSREF bits should also be set to 01 to allow<br>clamping to operate correctly.         Must be set to zero         Must be set to One         Digitally inverts the polarity of output data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 7<br>1:0<br>2<br>3                                      | Reserved<br>Reserved<br>INVOP                                                                      | 0 11                                                                                                                                                                                  | other modes, 1 = MODE3.<br>NB, when in this mode the CDSREF bits should also be set to 01 to allow<br>clamping to operate correctly.<br>Must be set to zero<br>Must be set to One<br>Digitally inverts the polarity of output data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 1:0<br>2<br>3                                           | Reserved<br>INVOP                                                                                  | 11                                                                                                                                                                                    | clamping to operate correctly.<br>Must be set to zero<br>Must be set to One<br>Digitally inverts the polarity of output data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 1:0<br>2<br>3                                           | Reserved<br>INVOP                                                                                  | 11                                                                                                                                                                                    | Must be set to One<br>Digitally inverts the polarity of output data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 2<br>3                                                  | INVOP                                                                                              |                                                                                                                                                                                       | Digitally inverts the polarity of output data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 3                                                       |                                                                                                    | 0                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| -                                                       | VRLCEXT                                                                                            |                                                                                                                                                                                       | 0 -  pegative going video gives pegative going subsut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| -                                                       | VRLCEXT                                                                                            |                                                                                                                                                                                       | <ul> <li>1 = negative going video gives negative going output,</li> <li>1 = negative-going video gives positive going output data.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 4                                                       |                                                                                                    | 0                                                                                                                                                                                     | When set powers down the RLCDAC, changing its output to Hi-Z, allowing VRLC/VBIAS to be externally driven.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                         | Reserved                                                                                           | 0                                                                                                                                                                                     | Must be set to Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 5                                                       | RLCDACRNG                                                                                          | 1                                                                                                                                                                                     | Sets the output range of the RLCDAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                         |                                                                                                    |                                                                                                                                                                                       | 0 = RLCDAC ranges from 0 to VDD (approximately),<br>1 = RLCDAC ranges from 0 to VRT (approximately).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 7:6                                                     | DEL[1:0]                                                                                           | 00                                                                                                                                                                                    | Sets the output latency in ADC clock periods.<br>1 ADC clock period = 2 MCLK periods except in Mode 2 where 1 ADC<br>clock period = 3 MCLK periods.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |