# Mobile Multimedia CODEC with 1W Speaker Driver

### DESCRIPTION

The WM8983 is a low power, high quality stereo CODEC designed for portable multimedia applications. Highly flexible analogue mixing functions enable new application features, combining hi-fi quality audio with voice communication.

The device integrates preamps for stereo differential mics, and includes drivers for speaker, headphone and differential or stereo line output. External component requirements are reduced as no separate microphone or headphone amplifiers are required.

Advanced on-chip digital signal processing includes a 5-band equaliser, a mixed signal Automatic Level Control for the microphone or line input through the ADC as well as a purely digital limiter function for record or playback. A programmable high pass filter in the ADC path is provided for wind noise reduction and an IIR with programmable coefficients can be used as a notch filter to suppress fixed-frequency noise.

The WM8983 digital audio interface can operate in master or slave mode, while an integrated PLL supports flexible clocking schemes. A-law and  $\mu$ -law companding are fully supported.

The WM8983 operates at analogue supply voltages from 2.5V to 3.3V, although the digital core can operate at voltages down to 1.71V to save power. Speaker supplies can operate up to 5V for increased speaker output power. Additional power management control enables individual sections of the chip to be powered down under software control.

### **FEATURES**

### Stereo CODEC:

- DAC SNR 98dB, THD -84dB ('A' weighted @ 48kHz)

- ADC SNR 95dB, THD -84dB ('A' weighted @ 48kHz)

- Speaker driver (1W into 8Ω BTL with 5V supply)

- SNR 90dB

- PSRR 80dB

- Headphone driver with 'capless' option

- 40mW/channel output power into  $16\Omega$  / 3.3V AVDD2

- Pop and click suppression

#### Mic Preamps:

- Stereo Differential or mono microphone Interfaces

- Programmable preamp gain

- Pseudo differential inputs with common mode rejection

- Programmable ALC / Noise Gate in ADC path

- Low-noise bias supplied for electret microphones

#### Other Features:

- Enhanced 3-D function for improved stereo separation

- Highly flexible mixing functions

- 5-band equaliser (ADC or DAC path)

- ADC Programmable high pass filter (wind noise reduction)

- ADC Programmable IIR notch filter

- Aux inputs for stereo analog input signals or 'beep'

- PLL supporting various clocks between 8MHz-50MHz

- Sample rates supported (kHz): 8, 11.025, 16, 12, 16, 22.05, 24, 32, 44.1, 48

- 2.5V to 3.6V analogue supplies

- 1.71V to 3.6V digital supplies

- 2.5V to 5.5V speaker supplies

- 5x5mm 32-lead QFN package

### **APPLICATIONS**

Multimedia mobile phones

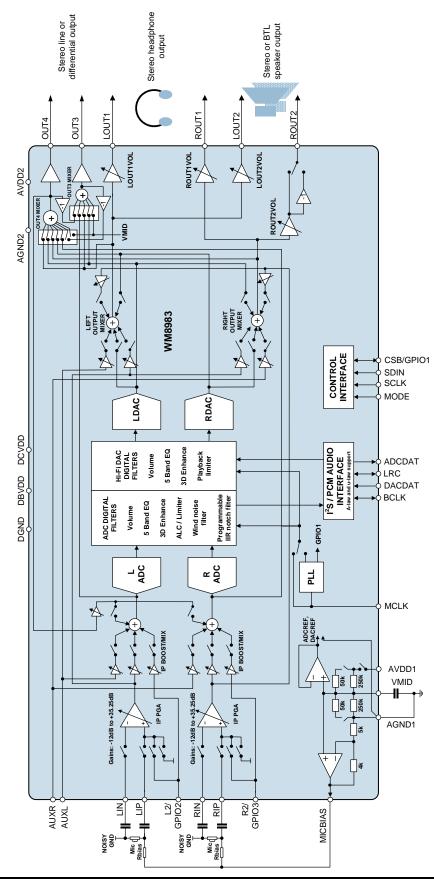

# **BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| DESCRIPTION                                   |     |

|-----------------------------------------------|-----|

| FEATURES                                      | 1   |

| APPLICATIONS                                  | 1   |

| BLOCK DIAGRAM                                 | 2   |

| TABLE OF CONTENTS                             |     |

| PIN CONFIGURATION                             |     |

| ORDERING INFORMATION                          |     |

| PIN DESCRIPTION                               | _   |

| ABSOLUTE MAXIMUM RATINGS                      |     |

|                                               |     |

| RECOMMENDED OPERATING CONDITIONS              |     |

| ELECTRICAL CHARACTERISTICS                    |     |

| TERMINOLOGY                                   | 14  |

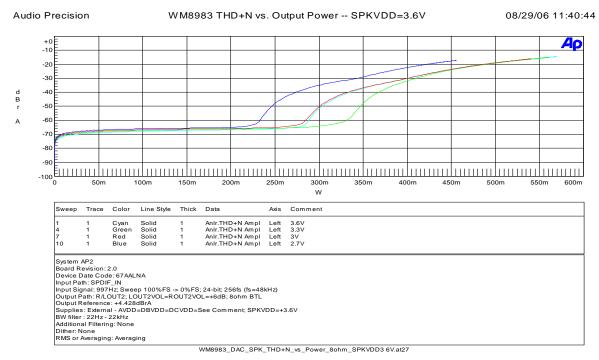

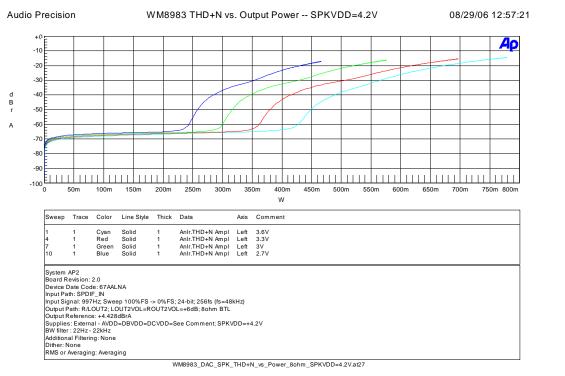

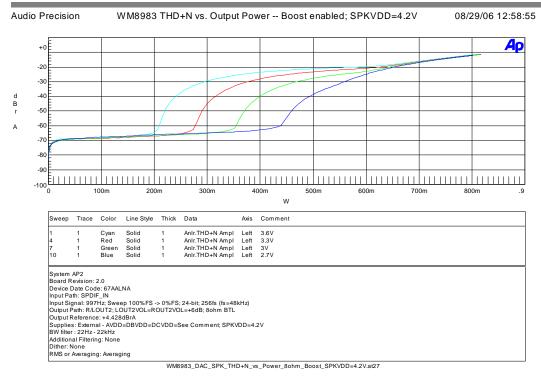

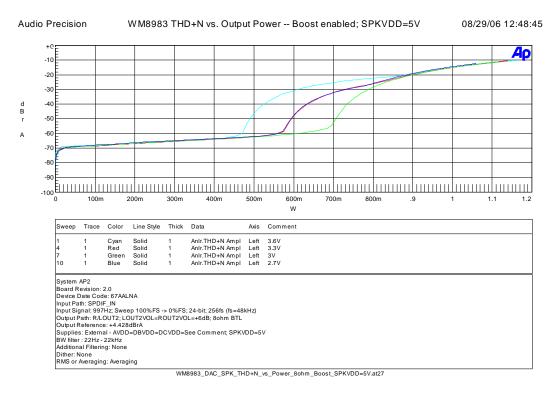

| TYPICAL PERFORMANCE                           | 15  |

| SPEAKER OUTPUT THD VERSUS POWER               |     |

| TYPICAL POWER CONSUMPTION                     |     |

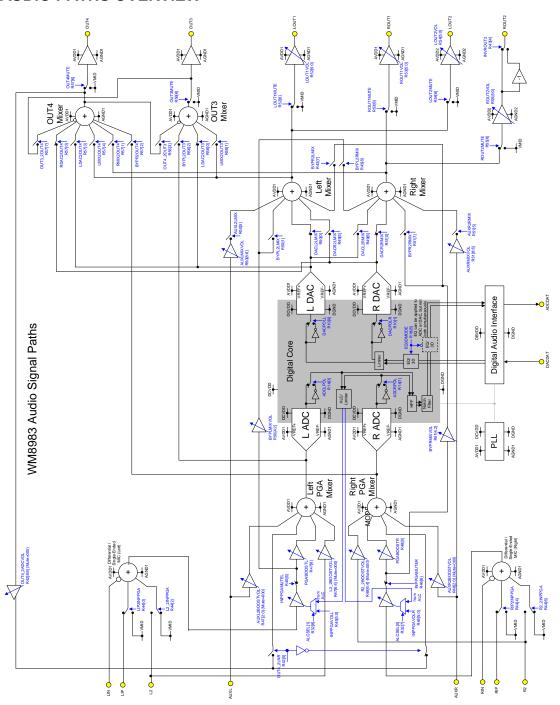

| AUDIO PATHS OVERVIEW                          |     |

| SIGNAL TIMING REQUIREMENTS                    |     |

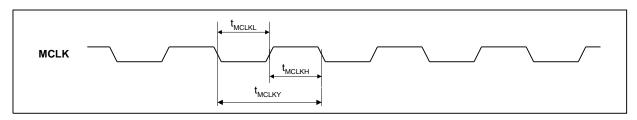

| SYSTEM CLOCK TIMING                           |     |

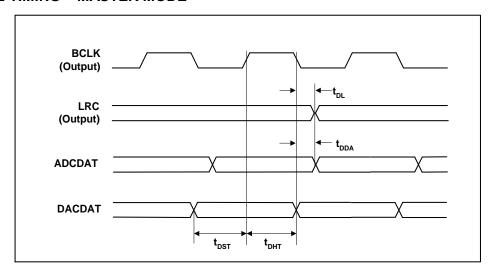

| AUDIO INTERFACE TIMING – MASTER MODE          |     |

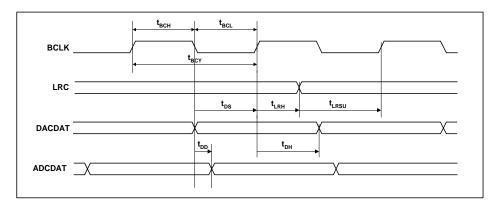

| AUDIO INTERFACE TIMING – SLAVE MODE           |     |

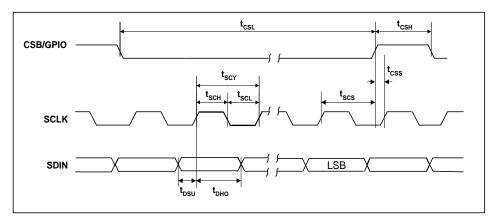

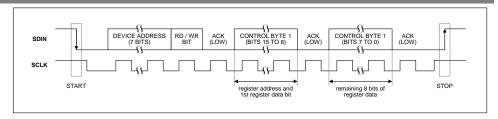

| CONTROL INTERFACE TIMING – 3-WIRE MODE        |     |

| CONTROL INTERFACE TIMING – 2-WIRE MODE        |     |

| INTERNAL POWER ON RESET CIRCUIT               |     |

| RECOMMENDED CONTROL SEQUENCES                 |     |

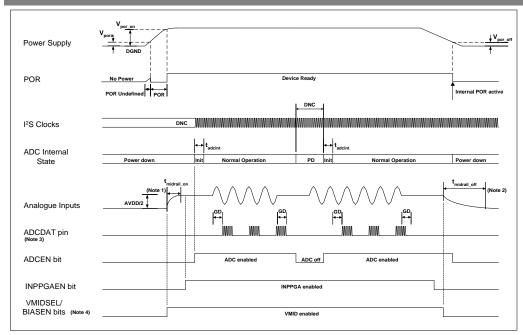

| POWER UP/DOWN SEQUENCE                        |     |

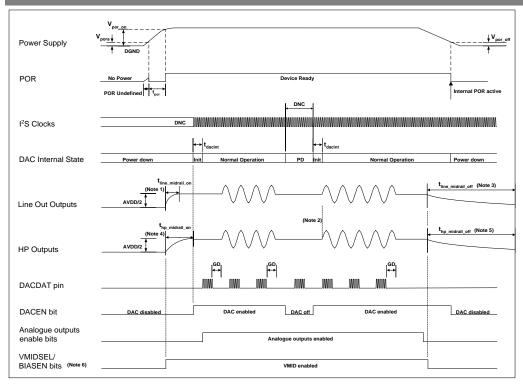

| LOUT1/ROUT1 ENABLE SEQUENCE                   |     |

| DEVICE DESCRIPTION                            | _   |

| INTRODUCTION                                  |     |

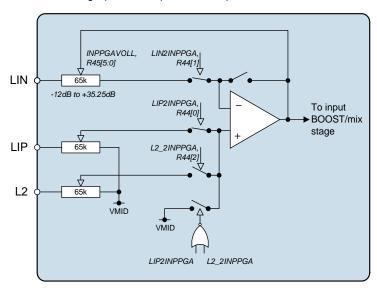

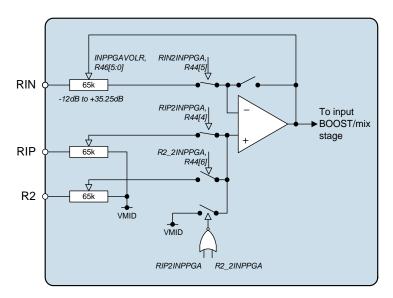

| INPUT SIGNAL PATH                             |     |

| ANALOGUE TO DIGITAL CONVERTER (ADC)           |     |

| INPUT LIMITER / AUTOMATIC LEVEL CONTROL (ALC) |     |

| OUTPUT SIGNAL PATH                            |     |

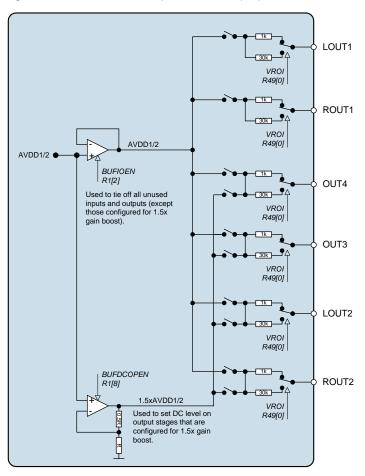

| ANALOGUE OUTPUTS                              |     |

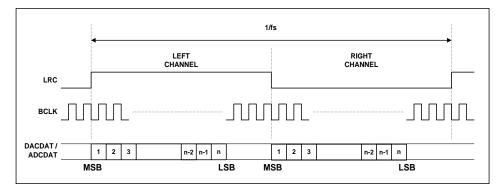

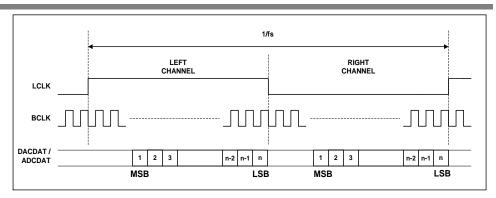

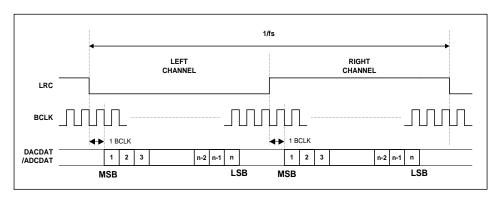

| DIGITAL AUDIO INTERFACES                      |     |

| AUDIO SAMPLE RATES                            |     |

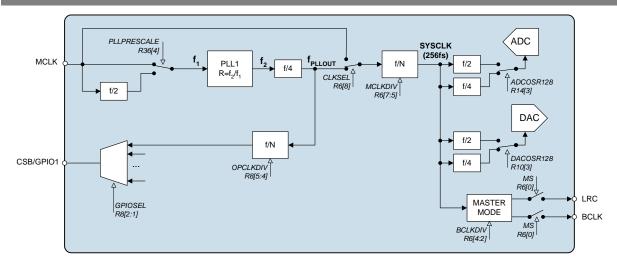

| MASTER CLOCK AND PHASE LOCKED LOOP (PLL)      | 87  |

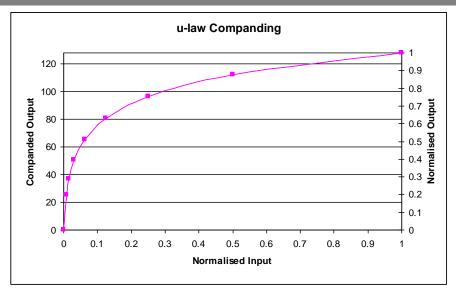

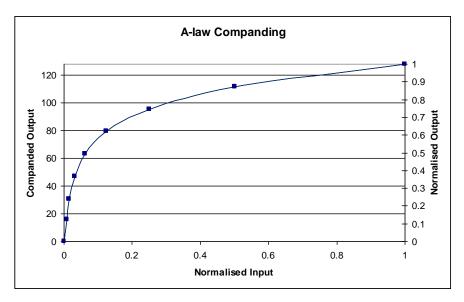

| COMPANDINGGENERAL PURPOSE INPUT/OUTPUT        | 90  |

| GENERAL PURPOSE INPUT/OUTPUT                  | 92  |

| OUTPUT SWITCHING (JACK DETECT)                | 93  |

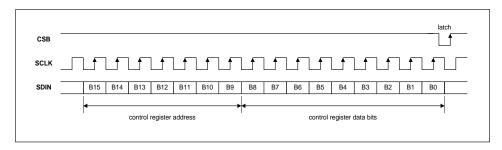

| CONTROL INTERFACE                             |     |

| RESETTING THE CHIP                            |     |

| POWER SUPPLIES                                |     |

| POWER MANAGEMENT                              |     |

| REGISTER MAP                                  | 97  |

| REGISTER BITS BY ADDRESS                      |     |

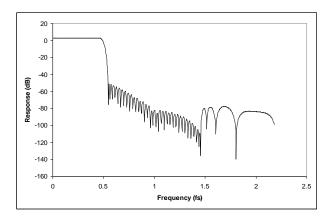

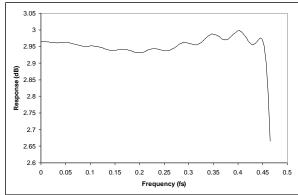

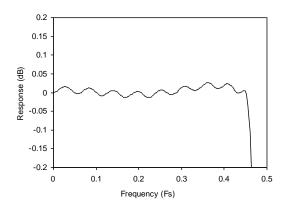

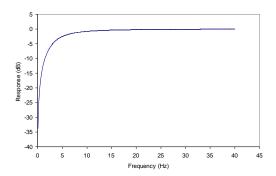

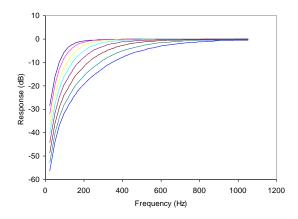

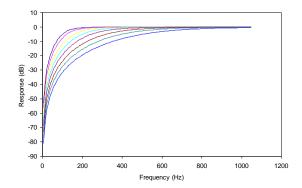

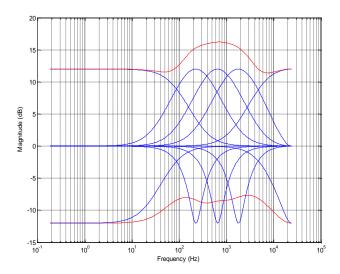

| DIGITAL FILTER CHARACTERISTICS                |     |

| TERMINOLOGY                                   | 118 |

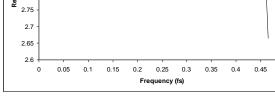

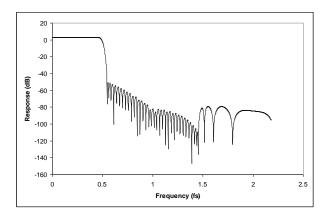

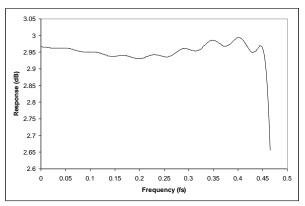

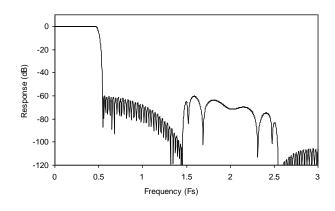

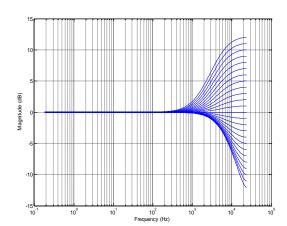

| DAC FILTER RESPONSES                          | 119 |

| ADC FILTER RESPONSES                               | 119                                   |

|----------------------------------------------------|---------------------------------------|

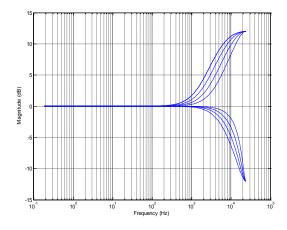

| HIGHPASS FILTER                                    |                                       |

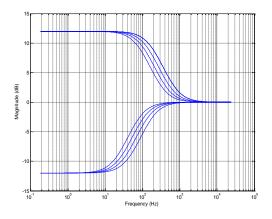

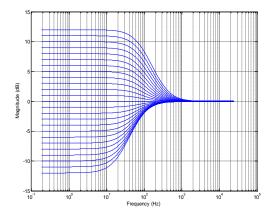

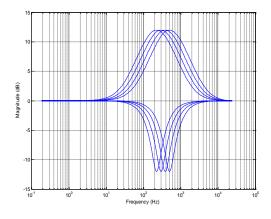

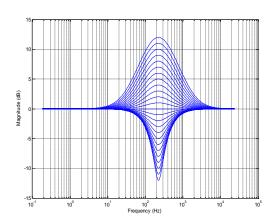

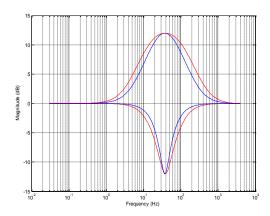

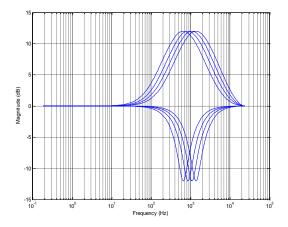

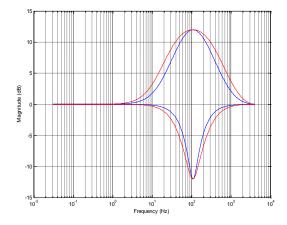

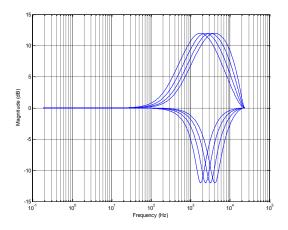

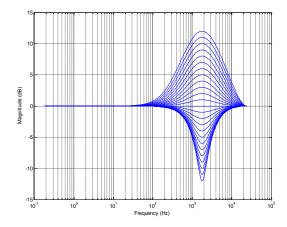

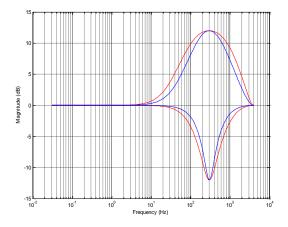

| 5-BAND EQUALISER                                   |                                       |

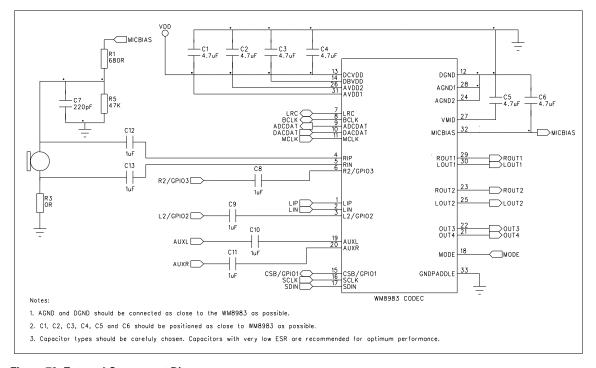

| APPLICATIONS INFORMATION                           | 125                                   |

| RECOMMENDED EXTERNAL COMPONENTS                    | 125                                   |

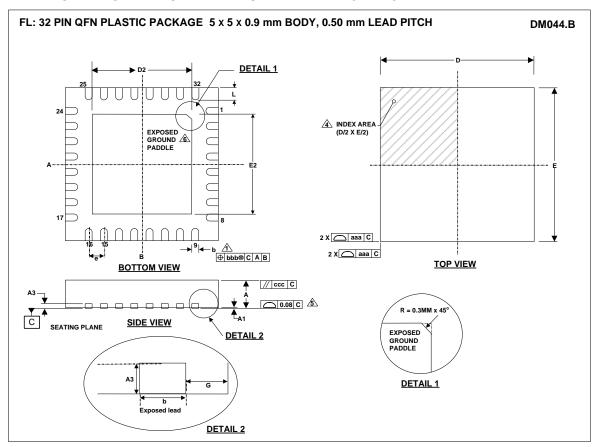

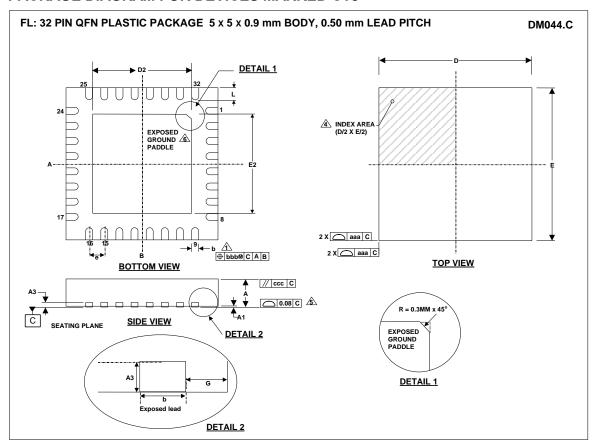

| PACKAGE DIAGRAM                                    |                                       |

| PACKAGE DIAGRAM FOR DEVICES MARKED KF3 / LK8 / RFD | 126                                   |

| PACKAGE DIAGRAM FOR DEVICES MARKED CT8             | 127                                   |

| IMPORTANT NOTICE                                   | 128                                   |

| REVISION HISTORY                                   |                                       |

|                                                    | · · · · · · · · · · · · · · · · · · · |

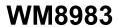

# **PIN CONFIGURATION**

# **ORDERING INFORMATION**

| ORDER CODE    | TEMPERATURE<br>RANGE | PACKAGE                                            | MOISTURE<br>SENSITIVITY LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|---------------|----------------------|----------------------------------------------------|-------------------------------|-------------------------------|

| WM8983GEFL/V  | -25°C to +85°C       | 32-lead QFN (5 x 5 mm)<br>(pb-free)                | MSL3                          | 260°C                         |

| WM8983GEFL/RV | -25°C to +85°C       | 32-lead QFN (5 x 5 mm)<br>(pb-free, tape and reel) | MSL3                          | 260°C                         |

Note:

Reel quantity = 3,500

# **PIN DESCRIPTION**

| PIN | NAME      | TYPE                   | DESCRIPTION                                                                                                             |

|-----|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1   | LIP       | Analogue input         | Left MIC pre-amp positive input                                                                                         |

| 2   | LIN       | Analogue input         | Left MIC pre-amp negative input                                                                                         |

| 3   | L2/GPIO2  | Analogue input         | Left channel line input/secondary mic pre-amp positive input/GPIO2 pin                                                  |

| 4   | RIP       | Analogue input         | Right MIC pre-amp positive input                                                                                        |

| 5   | RIN       | Analogue input         | Right MIC pre-amp negative input                                                                                        |

| 6   | R2/GPIO3  | Analogue input         | Right channel line input/secondary mic pre-amp positive input/GPIO3 pin                                                 |

| 7   | LRC       | Digital Input / Output | DAC and ADC sample rate clock                                                                                           |

| 8   | BCLK      | Digital Input / Output | Digital audio bit clock                                                                                                 |

| 9   | ADCDAT    | Digital Output         | ADC digital audio data output                                                                                           |

| 10  | DACDAT    | Digital Input          | DAC digital audio data input                                                                                            |

| 11  | MCLK      | Digital Input          | Master clock input                                                                                                      |

| 12  | DGND      | Supply                 | Digital ground                                                                                                          |

| 13  | DCVDD     | Supply                 | Digital core logic supply                                                                                               |

| 14  | DBVDD     | Supply                 | Digital buffer (I/O) supply                                                                                             |

| 15  | CSB/GPIO1 | Digital Input / Output | 3-Wire control interface chip Select / GPIO1 pin                                                                        |

| 16  | SCLK      | Digital Input          | 3-Wire control interface clock input / 2-wire control interface clock input                                             |

| 17  | SDIN      | Digital Input / Output | 3-Wire control interface data input / 2-Wire control interface data input                                               |

| 18  | MODE      | Digital Input          | Control interface selection                                                                                             |

| 19  | AUXL      | Analogue input         | Left auxiliary input                                                                                                    |

| 20  | AUXR      | Analogue input         | Right auxiliary input                                                                                                   |

| 21  | OUT4      | Analogue Output        | right line output or mono mix output                                                                                    |

| 22  | OUT3      | Analogue Output        | mono or left line output                                                                                                |

| 23  | ROUT2     | Analogue Output        | Headphone or line output right 2                                                                                        |

| 24  | AGND2     | Supply                 | Analogue ground (feeds ROUT2/LOUT2 and OUT3/OUT4)                                                                       |

| 25  | LOUT2     | Analogue Output        | Headphone or line output left 2                                                                                         |

| 26  | AVDD2     | Supply                 | Analogue supply (feeds output amplifiers ROUT2/LOUT2 and OUT3/OUT4)                                                     |

| 27  | VMID      | Reference              | Decoupling for ADC and DAC reference voltage                                                                            |

| 28  | AGND1     | Supply                 | Analogue ground (feeds all input amplifiers, PLL, ADC and DAC, internal bias circuits, output amplifiers LOUT1, ROUT1)  |

| 29  | ROUT1     | Analogue Output        | Headphone or line output right 1                                                                                        |

| 30  | LOUT1     | Analogue Output        | Headphone or line output left 1                                                                                         |

| 31  | AVDD1     | Supply                 | Analogue supply (feeds all input amplifiers, PLL, ADC and DAC, internal bias circuits, output amplifiers LOUT1, LOUT2)) |

| 32  | MICBIAS   | Analogue Output        | Microphone bias                                                                                                         |

### Note:

It is recommended that the QFN ground paddle should be connected to analogue ground on the application PCB.

Refer to the application note WAN\_0118 on "Guidelines on How to Use QFN Packages and Create Associated PCB Footprints"

# ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Cirrus tests its package types according to IPC/JEDEC J-STD-020 for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                              | MIN          | MAX          |

|----------------------------------------|--------------|--------------|

| DBVDD, DCVDD, AVDD1 supply voltages    | -0.3V        | +4.5V        |

| AVDD2 supply voltage                   | -0.3V        | +7V          |

| Voltage range digital inputs           | DGND - 0.3V  | DVDD + 0.3V  |

| Voltage range analogue inputs          | AGND1 - 0.3V | AVDD1 + 0.3V |

|                                        | AGND2 - 0.3V | AVDD2 + 0.3V |

| Storage temperature prior to soldering | 30°C max / 8 | 35% RH max   |

| Storage temperature after soldering    | -65°C        | +150°C       |

#### Notes:

- 1. Analogue and digital grounds must always be within 0.3V of each other.

- 2. All digital and analogue supplies are completely independent from each other.

- 3. Analogue supply voltages should not be less than digital supply voltages.

- 4. In non-boosted mode AVDD2 should be  $\geq$  AVDD1. In boost mode, AVDD2 should be  $\geq$  1.5 x AVDD1.

- 5. DBVDD must be greater than or equal to DCVDD.

### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                     | SYMBOL             | TEST<br>CONDITIONS | MIN               | TYP | MAX | UNIT |

|-------------------------------|--------------------|--------------------|-------------------|-----|-----|------|

| Digital supply range (Core)   | DCVDD              |                    | 1.71              |     | 3.6 | V    |

| Digital supply range (Buffer) | DBVDD              |                    | 1.71 <sup>2</sup> |     | 3.6 | V    |

| Analogue supply range         | AVDD1              |                    | 2.5               |     | 3.6 | V    |

| Speaker supply range          | AVDD2              |                    | 2.5               |     | 5.5 | V    |

| Ground                        | DGND, AGND1, AGND2 |                    |                   | 0   |     | V    |

#### Notes:

- 1. Analogue supply voltages should not be less than digital supply voltages.

- 2. DBVDD should be  $\geq$  1.9V when using the PLL.

# **ELECTRICAL CHARACTERISTICS**

### **Test Conditions**

$DCVDD=1.8V,\ AVDD1=AVDD2=DBVDD=3.3V,\ T_A=+25^{\circ}C,\ 1kHz\ signal,\ fs=48kHz,\ 24-bit\ audio\ data\ unless\ otherwise\ stated.$

| PARAMETER                                                                      | SYMBOL         | TEST CONDITIONS                                                   | MIN | TYP              | MAX                                   | UNIT             |

|--------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------|-----|------------------|---------------------------------------|------------------|

| Microphone Input PGA Inputs (LIP,                                              | LIN, RIP, RIN, | L2, R2)                                                           |     |                  |                                       |                  |

| INPPGAVOLL, INPPGAVOLR, PGA                                                    | BOOSTL and I   | PGABOOSTR = 0dB                                                   |     | T                | · · · · · · · · · · · · · · · · · · · |                  |

| Full-scale Input Signal Level –<br>Single-ended input via LIN/RIN <sup>1</sup> |                |                                                                   |     | AVDD/3.3         |                                       | $V_{rms}$        |

| Full-scale Input Signal Level –<br>Pseudo-differential input <sup>1,2</sup>    |                |                                                                   |     | AVDD*0.7/<br>3.3 |                                       | $V_{\text{rms}}$ |

| Input PGA equivalent input noise                                               |                | INPPGAVOLL/R = +35.25dB<br>No input signal<br>22Hz to 20kHz       |     | 150              |                                       | μV               |

| LIN, RIN input resistance                                                      |                | INPPGAVOLL and INPPGAVOLR = +35.25dB                              |     | 1.7              |                                       | kΩ               |

| LIN, RIN input resistance                                                      |                | INPPGAVOLL and INPPGAVOLR = 0dB                                   |     | 47               |                                       | kΩ               |

| LIN, RIN input resistance                                                      |                | INPPGAVOLL and INPPGAVOLR = -12dB                                 |     | 76               |                                       | kΩ               |

| LIP, RIP input resistance                                                      |                | All gain settings                                                 |     | 95               |                                       | kΩ               |

| L2, R2 input resistance                                                        |                | L2_2INPPGA and R2_2INPPGA = 1 L2_2BOOSTVOL and R2_2BOOSTVOL = 000 |     | 90               |                                       | kΩ               |

| L2, R2 input resistance                                                        |                | L2_2INPPGA and<br>R2_2INPPGA = 0                                  |     | 11               |                                       | kΩ               |

|                                                                                |                | L2_2BOOSTVOL and<br>R2_2BOOSTVOL = +6dB                           |     |                  |                                       |                  |

| L2, R2 input resistance                                                        |                | L2_2INPPGA and<br>R2_2INPPGA = 0                                  |     | 22               |                                       | kΩ               |

|                                                                                |                | L2_2BOOSTVOL and<br>R2_2BOOSTVOL = 0dB                            |     |                  |                                       |                  |

| L2, R2 input resistance                                                        |                | L2_2INPPGA and<br>R2_2INPPGA = 0                                  |     | 60               |                                       | kΩ               |

|                                                                                |                | L2_2BOOSTVOL and<br>R2_2BOOSTVOL = -12dB                          |     |                  |                                       |                  |

| Input Capacitance                                                              |                | All analogue input pins                                           |     | 10               |                                       | pF               |

| Input PGA Programmable Gain                                                    |                | Gain adjusted by INPPGAVOLL and INPPGAVOLL                        | -12 |                  | +35.25                                | dB               |

| Programmable Gain Step Size                                                    |                | Guaranteed monotonic                                              |     | 0.75             |                                       | dB               |

| Input PGA Mute Attenuation                                                     |                | INPPGAMUTEL and INPPGAMUTER = 1                                   |     | 100              |                                       | dB               |

| Input Gain Boost                                                               |                | PGABOOSTL and<br>PGABOOSTR = 0                                    |     | 0                |                                       | dB               |

| Input Gain Boost                                                               |                | PGABOOSTL and<br>PGABOOSTR = 1                                    |     | +20              |                                       | dB               |

$DCVDD=1.8V, AVDD1=AVDD2=DBVDD=3.3V, T_A=+25^{\circ}C, 1kHz \ signal, fs=48kHz, 24-bit \ audio \ data \ unless \ otherwise \ stated.$

| PARAMETER                                      | SYMBOL         | TEST CONDITIONS                                   | MIN       | TYP            | MAX    | UNIT      |

|------------------------------------------------|----------------|---------------------------------------------------|-----------|----------------|--------|-----------|

| Auxiliary Analogue Inputs (AUXL, A             | UXR)           |                                                   |           |                |        |           |

| Full-scale Input Signal Level <sup>2</sup>     |                |                                                   |           | AVDD/3.3       |        | $V_{rms}$ |

| Input Resistance                               |                | Left Input boost and mixer                        |           | 4.3            |        | kΩ        |

|                                                |                | enabled, at +6dB                                  |           |                |        |           |

|                                                |                | Left Input boost and mixer                        |           | 8.6            |        | kΩ        |

|                                                |                | enabled, at 0dB gain                              |           | 00.4           |        |           |

|                                                |                | Left Input boost and mixer enabled, at -12dB gain |           | 39.1           |        | kΩ        |

|                                                |                | Right Input boost, mixer                          |           | 3              |        | kΩ        |

|                                                |                | enabled, at +6dB gain                             |           | Ü              |        | 1432      |

|                                                |                | Right Input boost, mixer                          |           | 6              |        | kΩ        |

|                                                |                | enabled, at 0dB gain                              |           |                |        |           |

|                                                |                | Right Input boost, mixer                          |           | 29             |        | kΩ        |

|                                                |                | enabled, at -12dB gain                            |           |                |        |           |

| Input Capacitance                              |                | All analogue Inputs                               |           | 10             |        | pF        |

| Gain range from AUXL and AUXR                  |                | Gain adjusted by AUXL2BOOSTVOL and                | -12       |                | +6     | dB        |

| input to left and right input PGA mixers       |                | AUXR2BOOSTVOL and                                 |           |                |        |           |

| AUXLBOOSTVOL and                               |                | AUXINZBOOSTVOL                                    |           | 3              |        | dB        |

| AUXRBOOSTVOL and<br>AUXRBOOSTVOL step size     |                |                                                   |           | 3              |        | иь        |

| L2, R2 Line Input Programmable Ga              | in             | l                                                 |           | <u> </u>       |        |           |

| Gain range from L2/R2 input to left            |                | Gain adjusted by                                  | -12       |                | +6     | dB        |

| and right input PGA mixers                     |                | L2_2BOOSTVOL and                                  |           |                | . •    | <u> </u>  |

|                                                |                | R2_2BOOSTVOL                                      |           |                |        |           |

| L2/R2_2BOOSTVOL step size                      |                |                                                   |           | 3              |        | dB        |

| L2/R2_2BOOSTVOL mute                           |                |                                                   |           | 100            |        | dB        |

| attenuation                                    |                |                                                   |           |                |        |           |

| OUT4 to left or right input boost rec          | ord path       |                                                   |           |                |        |           |

| Gain range into left and right input           |                | Gain adjusted by                                  | -6        |                | +12    | dB        |

| PGA mixers                                     |                | OUT4_2ADCVOL                                      |           |                |        |           |

| OUT4_2ADCVOL gain step size                    |                |                                                   |           | 3              |        | dB        |

| OUT4_2ADCVOL mute attenuation                  |                |                                                   |           | 100            |        | dB        |

| Analogue to Digital Converter (ADC             | ) - Input from | LIN/P and RIN/P in differenti                     | al config | uration to inp | ut PGA |           |

| INPPGAVOLL, INPPGAVOLR, PGA                    | BOOSTL, PGA    | ABOOSTR, ADCLVOL and AL                           | DCRVOL    | = 0dB          |        |           |

| Signal to Noise Ratio 3                        | SNR            | A-weighted                                        |           | 93             |        | dB        |

|                                                |                | AVDD1=AVDD2=3.3V                                  |           |                |        |           |

|                                                |                | A-weighted                                        |           | 91.5           |        | dB        |

|                                                |                | AVDD1=AVDD2=2.5V                                  |           |                |        |           |

| Total Harmonic Distortion <sup>4</sup>         | THD            | -12dBV Input                                      |           | -78            |        | dBFS      |

|                                                |                | AVDD1=AVDD2=3.3V                                  |           |                |        |           |

|                                                |                | -12dBV Input                                      |           | -75            |        | dBFS      |

|                                                |                | AVDD1=AVDD2=2.5V                                  |           |                |        | 3         |

| Total Harmonic Distortion + Noise <sup>5</sup> | THD+N          | -12dBV Input                                      |           | -75            |        | dBFS      |

| Total Haimonic Distortion + Noise              |                | AVDD1=AVDD2=3.3V                                  |           |                |        | u.D. 0    |

|                                                |                | -12dBV Input                                      |           | -72            |        | dBFS      |

|                                                |                | AVDD1=AVDD2=2.5V                                  |           | -12            |        | ubro      |

|                                                | ļ              | 1kHz full scale input signal                      |           |                |        | dBFS      |

$DCVDD=1.8V, AVDD1=AVDD2=DBVDD=3.3V, T_A=+25^{\circ}C, 1kHz \ signal, fs=48kHz, 24-bit \ audio \ data \ unless \ otherwise \ stated.$

| PARAMETER                                                       | SYMBOL        | TEST CONDITIONS                 | MIN | TYP       | MAX      | UNIT      |

|-----------------------------------------------------------------|---------------|---------------------------------|-----|-----------|----------|-----------|

| Analogue to Digital Converter (ADC INPPGAVOLL, INPPGAVOLR, L2_2 |               |                                 |     |           | INPPGA = | 0.        |

| Signal to Noise Ratio <sup>3</sup>                              | SNR           | A-weighted                      |     | 95        |          | dB        |

|                                                                 |               | AVDD1=AVDD2=3.3V                |     |           |          |           |

|                                                                 |               | A-weighted                      |     | 93        |          | dB        |

|                                                                 |               | AVDD1=AVDD2=2.5V                |     |           |          |           |

| Total Harmonic Distortion <sup>4</sup>                          | THD           | -3dBV Input                     |     | -86       |          | dBFS      |

|                                                                 |               | AVDD1=AVDD2=3.3V                |     |           |          |           |

|                                                                 |               | -3dBV Input                     |     | -78       |          | dBFS      |

|                                                                 |               | AVDD1=AVDD2=2.5V                |     |           |          | ab. c     |

| Total Harmonic Distortion + Noise <sup>5</sup>                  | THD+N         | -3dBV Input                     |     | -80       |          | dBFS      |

| Total Harmonic Distortion 1 Noise                               | IIIDIN        | AVDD1=AVDD2=3.3V                |     | -00       |          | ubi 5     |

|                                                                 |               | -3dBV Input                     |     | -76       |          | dBFS      |

|                                                                 |               | AVDD1=AVDD2=2.5V                |     | -76       |          | ubro      |

| Channel Consention 6                                            |               |                                 |     | 400       |          | 4DEC      |

| Channel Separation <sup>6</sup>                                 |               | 1kHz input signal               |     | 100       |          | dBFS      |

| DAC to left and right mixers into 10 LOUT1VOL, ROUT1VOL, DACLVO | •             |                                 |     |           |          |           |

| Full-scale output <sup>1</sup>                                  |               | LOUT1VOL and                    |     | AVDD1/3.3 |          | $V_{rms}$ |

|                                                                 |               | ROUTVOL = 0dB                   |     |           |          | - 11113   |

| Signal to Noise Ratio <sup>3</sup>                              | SNR           | A-weighted                      |     | 100       |          | dB        |

| orginal to Moloo Matte                                          | J. Crark      | AVDD1=AVDD2=3.3V                |     | 100       |          | 45        |

|                                                                 |               | A-weighted                      |     | 99        |          | dB        |

|                                                                 |               | AVDD1=AVDD2=2.5V                |     | 99        |          | ub        |

| Total Harmonic Distortion <sup>4</sup>                          | THD           | 0dBFS input                     |     | -84       |          | dBFS      |

| Total Harmonic Distortion                                       | 1110          | AVDD1=AVDD2=3.3V                |     | -04       |          | ubi 3     |

|                                                                 |               | 0dBFS input                     |     | -86       |          | dBFS      |

|                                                                 |               | AVDD1=AVDD2=2.5V                |     | -00       |          | dbi 3     |

| Total Harmonic Distortion + Noise <sup>5</sup>                  | THD+N         | 0dBFS input<br>AVDD1=AVDD2=3.3V |     | -83       |          | dBFS      |

|                                                                 |               | 0dBFS input                     |     | -84       |          | dBFS      |

|                                                                 |               | AVDD1=AVDD2=2.5V                |     | -04       |          | ubro      |

| Channel Separation <sup>6</sup>                                 |               | 1kHz signal                     |     | 100       |          | dB        |

| DAC to L/R mixer into 10kΩ / 50pF                               | load on L/ROU |                                 |     | 100       |          | u.b       |

| LOUT2VOL, ROUT2VOL, DACLVOL                                     |               |                                 |     |           |          |           |

| Full-scale output 1                                             |               |                                 |     | AVDD1/3.3 |          | $V_{rms}$ |

| Signal to Noise Ratio 3                                         | SNR           | A-weighted                      |     | 100       |          | dB        |

|                                                                 |               | AVDD1=AVDD2=3.3V                |     |           |          |           |

|                                                                 |               | A-weighted                      |     | 96        |          | dB        |

|                                                                 |               | AVDD1=AVDD2=2.5V                |     |           |          |           |

| Total Harmonic Distortion <sup>4</sup>                          | THD           | 0dBFS input                     |     | -84       |          | dBFS      |

| Total Harmonio Biotoriion                                       |               | AVDD1=AVDD2=3.3V                |     | "         |          |           |

|                                                                 |               | 0dBFS input                     |     | -82       |          | dBFS      |

|                                                                 |               | AVDD1=AVDD2=2.5V                |     |           |          |           |

| Total Harmonic Distortion + Noise 5                             | THD+N         | 0dBFS input                     |     | -82       |          | dBFS      |

|                                                                 |               | AVDD1=AVDD2=3.3V                |     |           |          |           |

|                                                                 |               | 0dBFS input                     |     | -80       |          | dBFS      |

|                                                                 |               | AVDD1=AVDD2=2.5V                |     |           |          |           |

| Channel Separation <sup>6</sup>                                 |               | 1kHz input signal               |     | 100       |          | dB        |

$DCVDD=1.8V, AVDD1=AVDD2=DBVDD=3.3V, T_A=+25^{\circ}C, 1kHz \ signal, fs=48kHz, 24-bit \ audio \ data \ unless \ otherwise \ stated.$

| PARAMETER                                      | SYMBOL        | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN        | TYP         | MAX      | UNIT      |

|------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|----------|-----------|

| DAC to OUT3 and OUT4 mixers to 0               | OUT3/OUT4 ou  | tputs into 10kΩ / 50pF load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . DACLVO   | L and DACRV | OL = 0dB |           |

| Full-scale output voltage                      |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | AVDD2/3.3   |          | $V_{rms}$ |

| Signal to Noise Ratio <sup>3</sup>             | SNR           | A-weighted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | 101.5       |          | dB        |

|                                                |               | AVDD1=AVDD2=3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |             |          |           |

| Total Harmonic Distortion <sup>4</sup>         | THD           | full-scale signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | -80         |          | dBFS      |

|                                                |               | AVDD1=AVDD2=3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |             |          |           |

|                                                |               | full-scale signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | -87         |          | dBFS      |

|                                                |               | AVDD1=AVDD2=2.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |             |          |           |

| Total Harmonic Distortion + Noise <sup>5</sup> | THD+N         | full-scale signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | -77         |          | dBFS      |

|                                                |               | AVDD1=AVDD2=3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |             |          |           |

|                                                |               | full-scale signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | -85         |          | dBFS      |

|                                                |               | AVDD1=AVDD2=2.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |             |          |           |

| Channel Separation <sup>6</sup>                |               | 1kHz signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            | 100         |          | dBFS      |

| DAC to left and right mixer into hea           | dphone (16Ω l | oad) on LOUT2 and ROUT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2          |             |          |           |

| LOUT2VOL, ROUT2VOL, DACLVOL                    | and DACRVO    | L = 0dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |             |          |           |

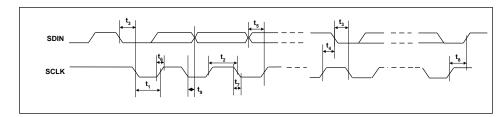

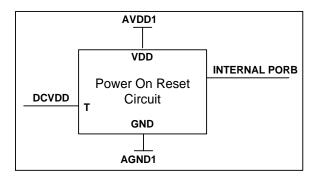

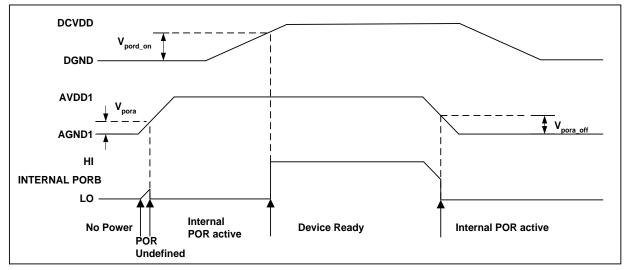

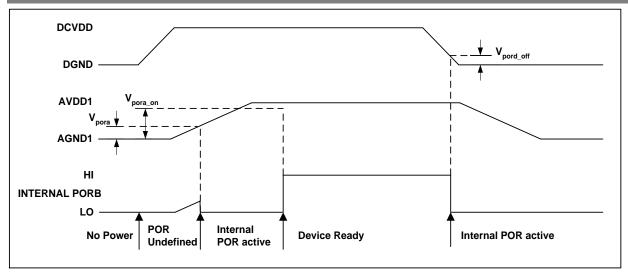

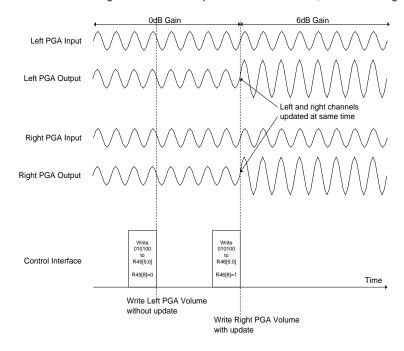

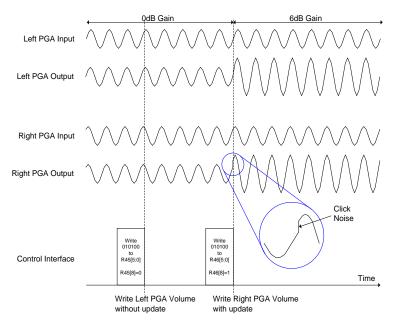

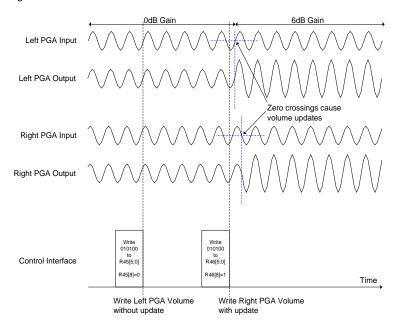

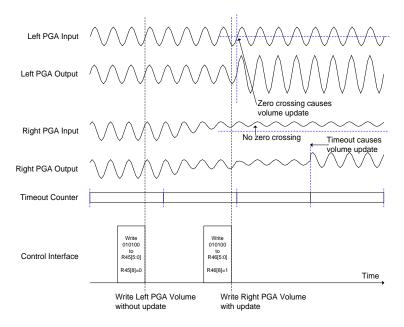

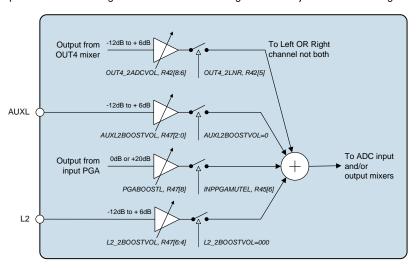

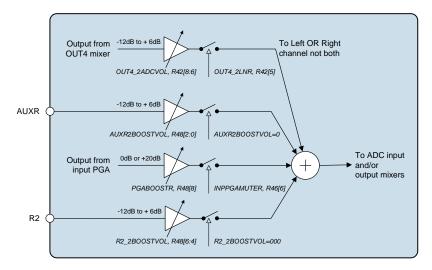

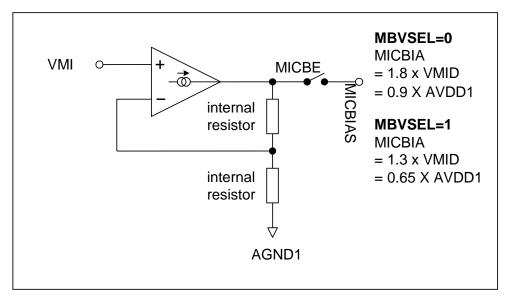

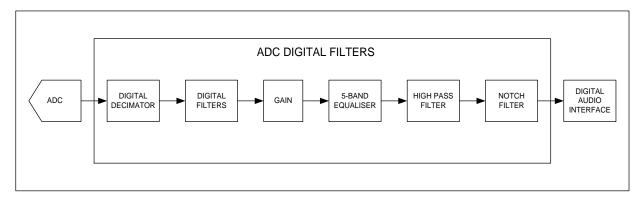

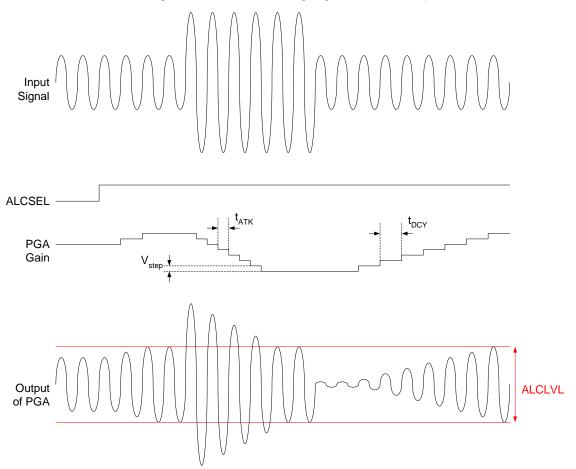

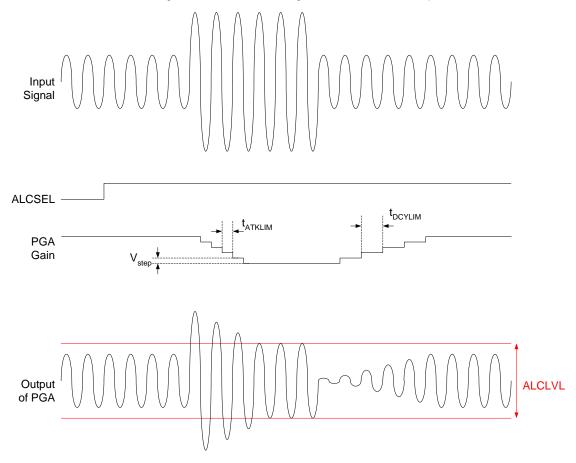

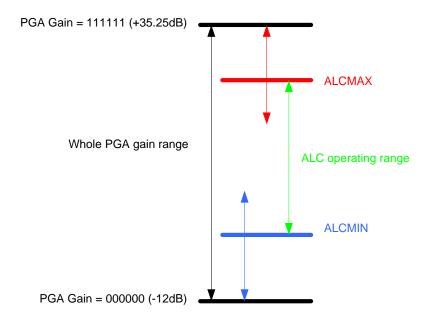

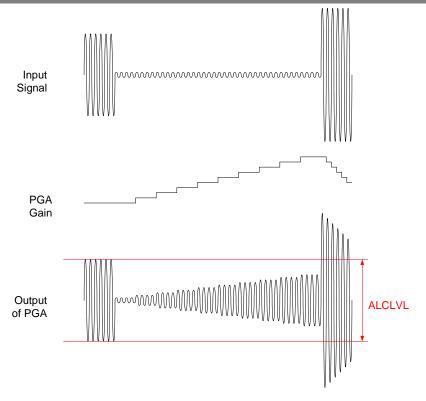

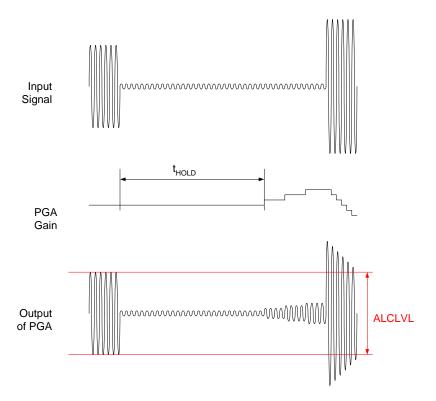

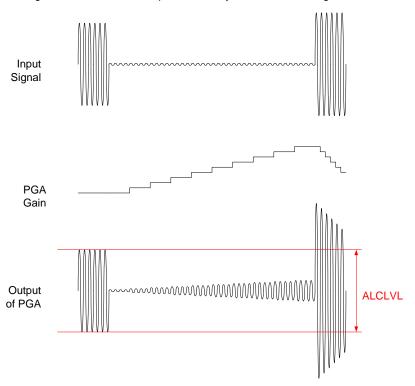

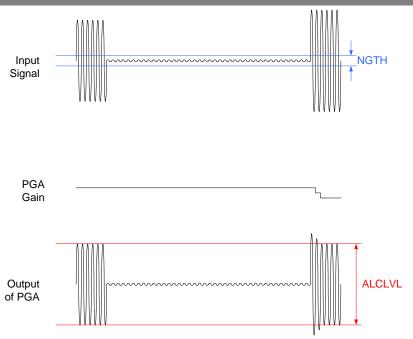

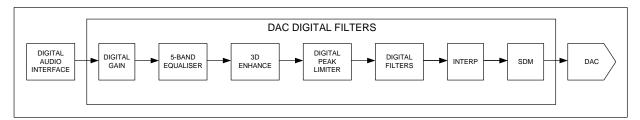

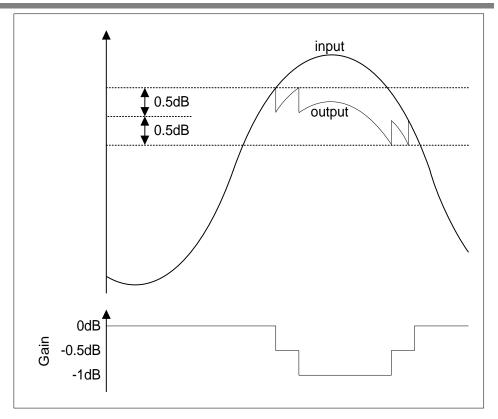

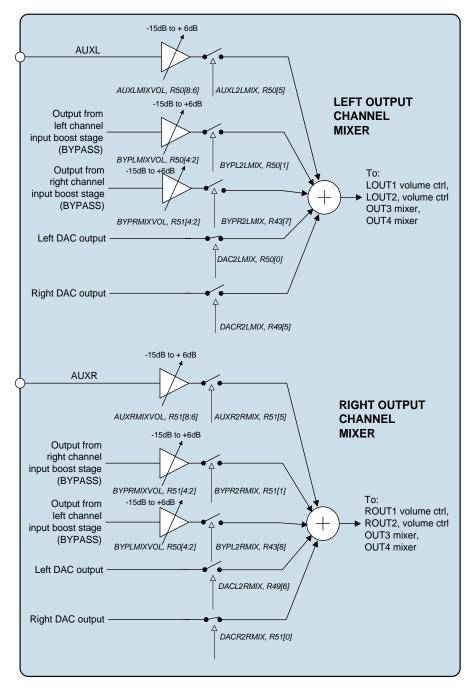

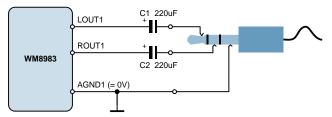

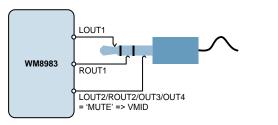

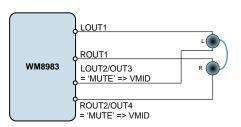

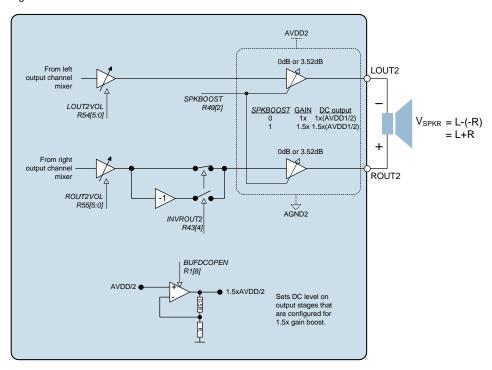

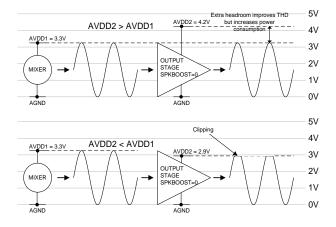

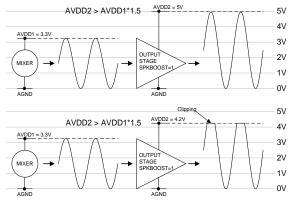

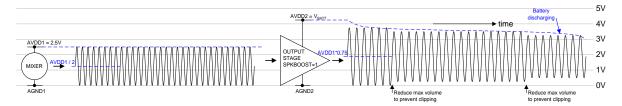

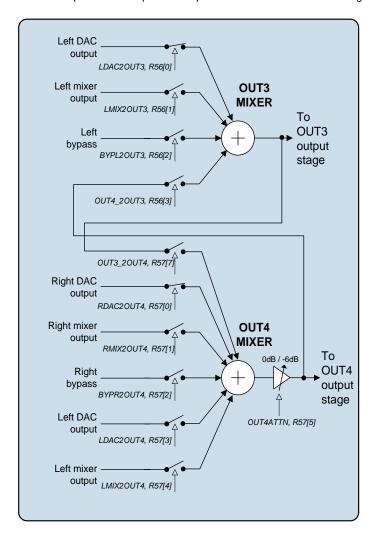

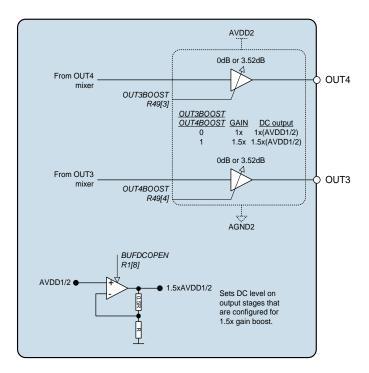

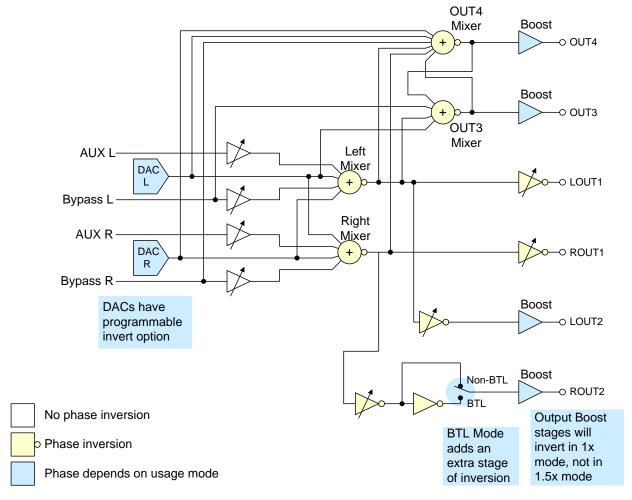

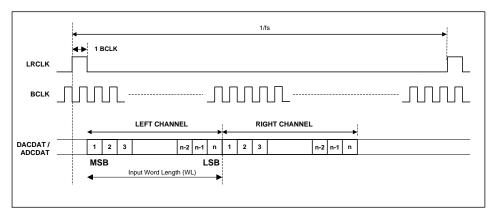

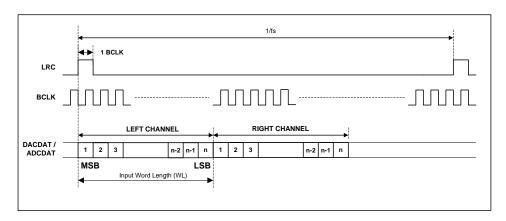

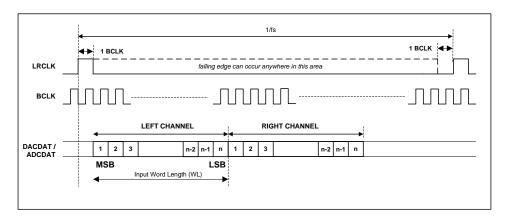

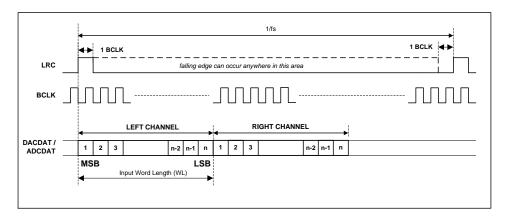

| Full-scale output                              |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | AVDD1/3.3   |          | $V_{rms}$ |