# S-5715 Series

# HIGH-SPEED / MIDDLE-SPEED LOW CURRENT CONSUMPTION BOTH POLES / UNIPOLAR DETECTION TYPE HALL IC

www.ablic.com

Rev.2.3\_02

© ABLIC Inc., 2011-2012

The S-5715 Series, developed by CMOS technology, is a high-accuracy Hall IC that operates with high-speed / middle-speed detection and low current consumption.

The output voltage changes when the S-5715 Series detects the intensity level of flux density. Using the S-5715 Series with a magnet makes it possible to detect the open / close and rotation state in various devices.

High-density mounting is possible by using the small SOT-23-3 or the super-small SNT-4A packages.

Due to its high-accuracy magnetic characteristics, the S-5715 Series can make operation's dispersion in the system combined with magnet smaller.

Caution This product is intended to use in general electronic devices such as consumer electronics, office equipment, and communications devices. Before using the product in medical equipment or automobile equipment including car audio, keyless entry and engine control unit, contact to ABLIC Inc. is indispensable.

# Features

- Pole detection<sup>\*1</sup>:

- Detection logic for magnetism<sup>\*1</sup>:

- Output form<sup>\*1</sup>:

- Magnetic sensitivity:

- Operating cycle (current consumption)<sup>\*1</sup>:

Detection of both poles, S pole or N pole Active "L", active "H" Nch open-drain output, CMOS output  $B_{OP} = 3.0 \text{ mT}$  typ. Product with both poles detection  $t_{CYCLE} = 0.10 \text{ ms} (1400 \ \mu\text{A}) \text{ typ.}$  $t_{CYCLE} = 0.90 \text{ ms} (155 \ \mu\text{A}) \text{ typ.}$  $t_{CYCLE} = 5.70 \text{ ms} (26 \ \mu\text{A}) \text{ typ.}$ Product with S pole or N pole detection  $t_{CYCLE} = 0.05 \text{ ms} (1400 \ \mu\text{A}) \text{ typ.}$  $t_{CYCLE} = 1.25 \text{ ms} (60 \ \mu\text{A}) \text{ typ.}$  $t_{CYCLE} = 6.05 \text{ ms} (13 \ \mu\text{A}) \text{ typ.}$  $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$ Ta =  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$

• Power supply voltage range:

- Lead-free (Sn 100%), halogen-free<sup>\*2</sup>

\*1. The option can be selected.

\*2. Refer to "

Product Name Structure" for details.

# Applications

- Plaything, portable game

- Home appliance

- Housing equipment

- Industrial equipment

## Packages

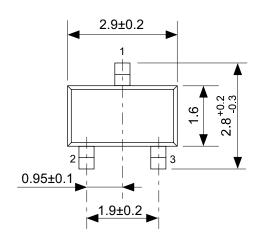

- SOT-23-3

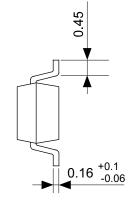

- SNT-4A

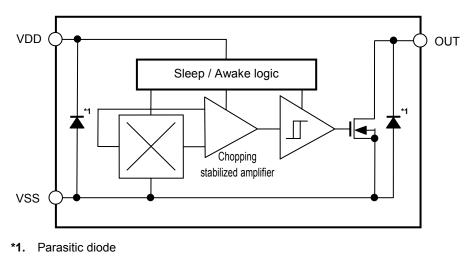

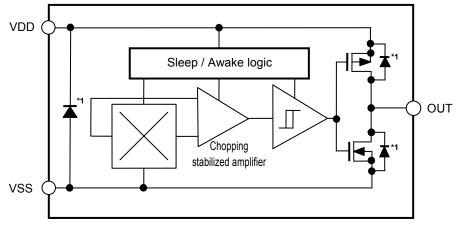

# Block Diagrams

1. Nch open-drain output product

2. CMOS output product

\*1. Parasitic diode

Figure 2

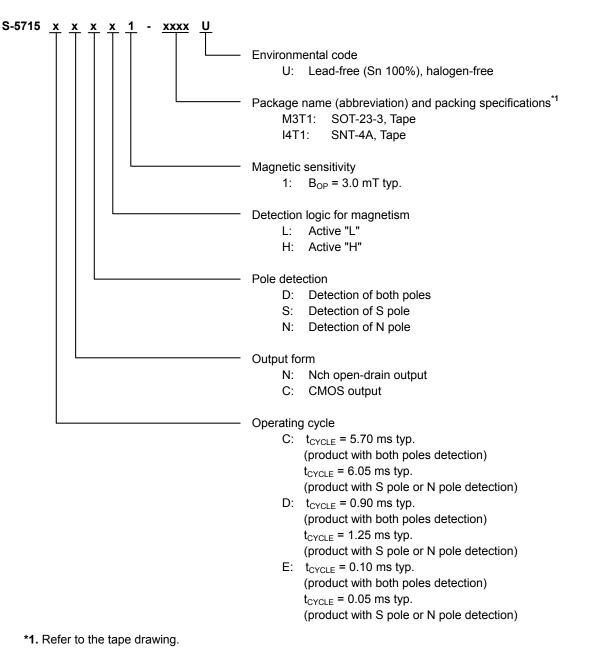

### Product Name Structure

1. Product name

#### 2. Packages

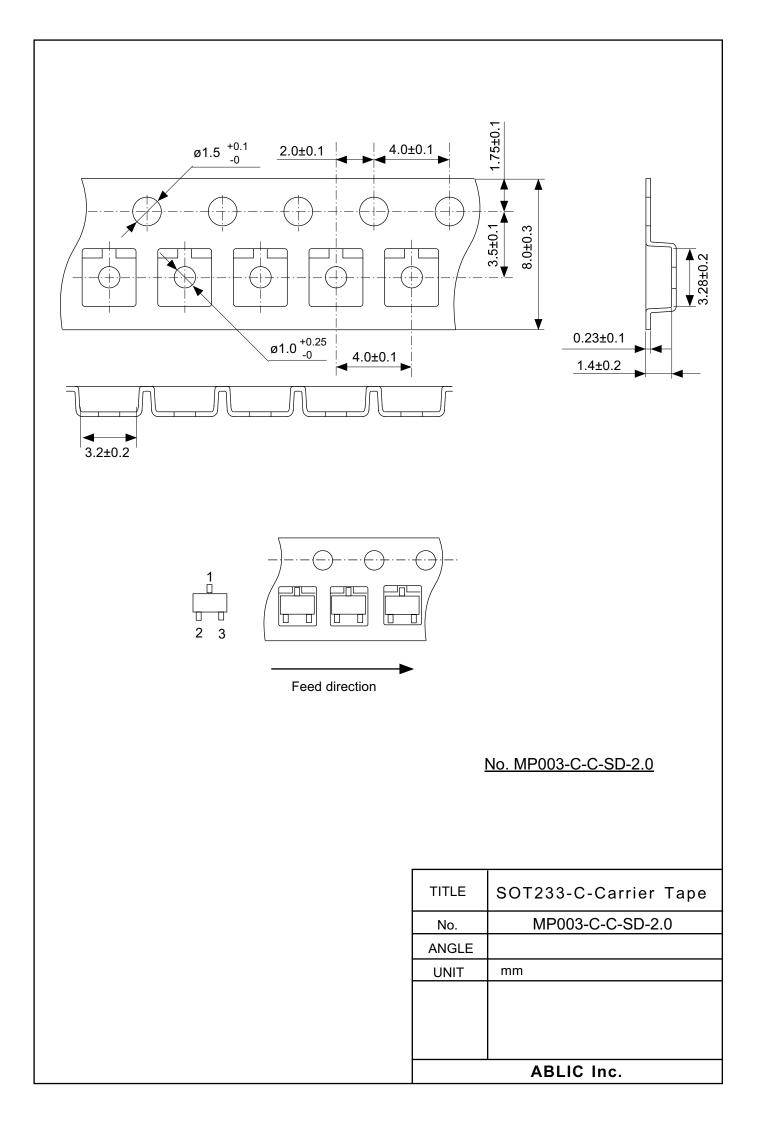

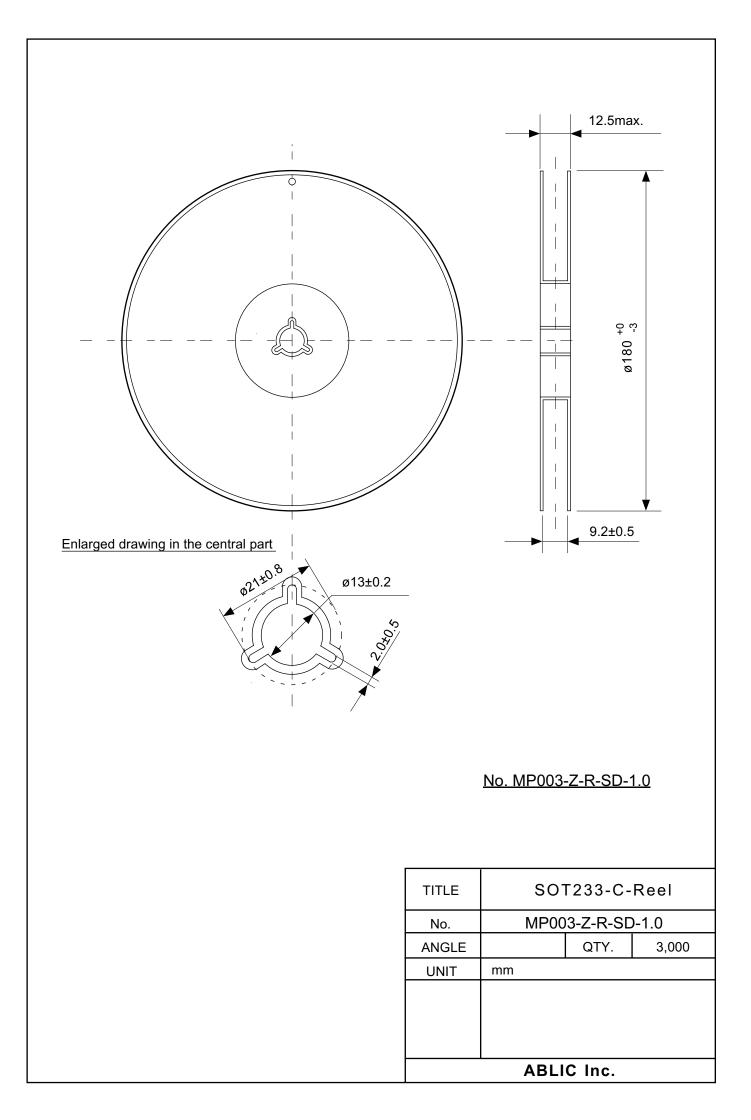

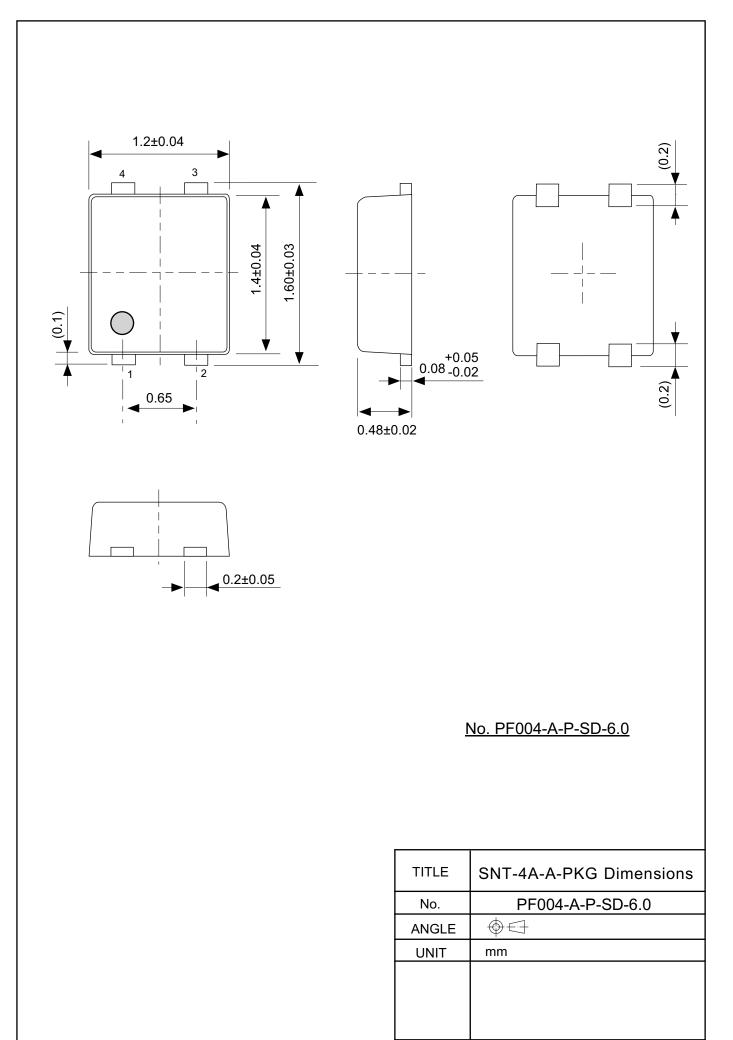

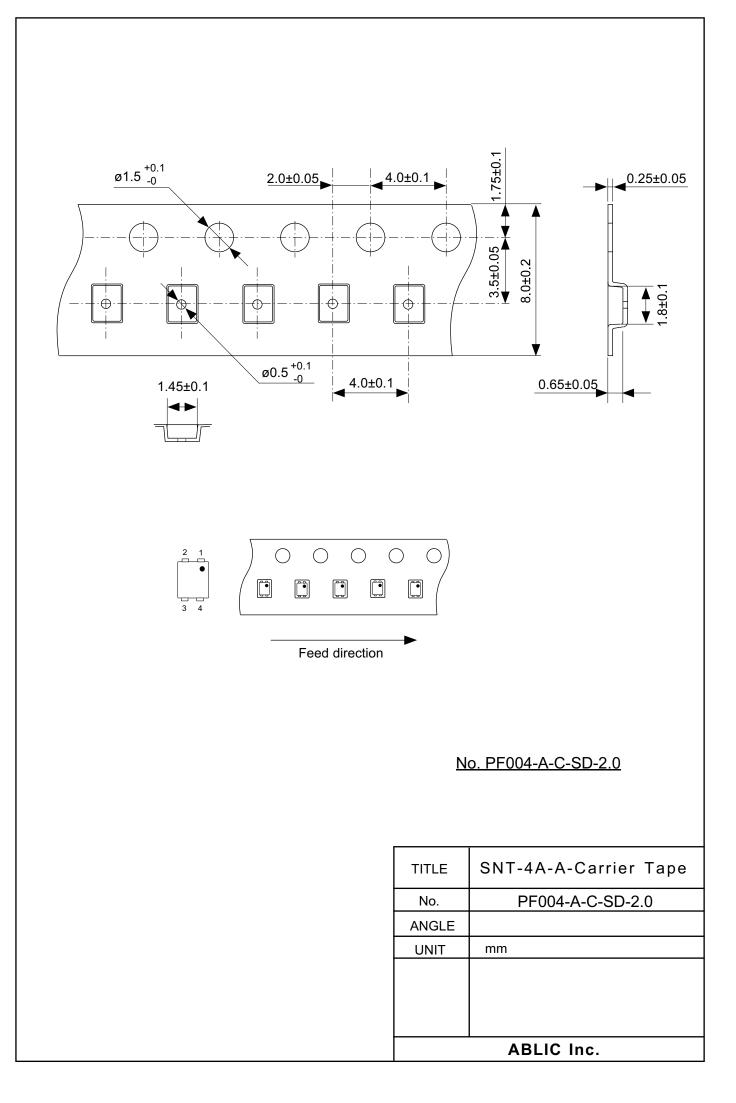

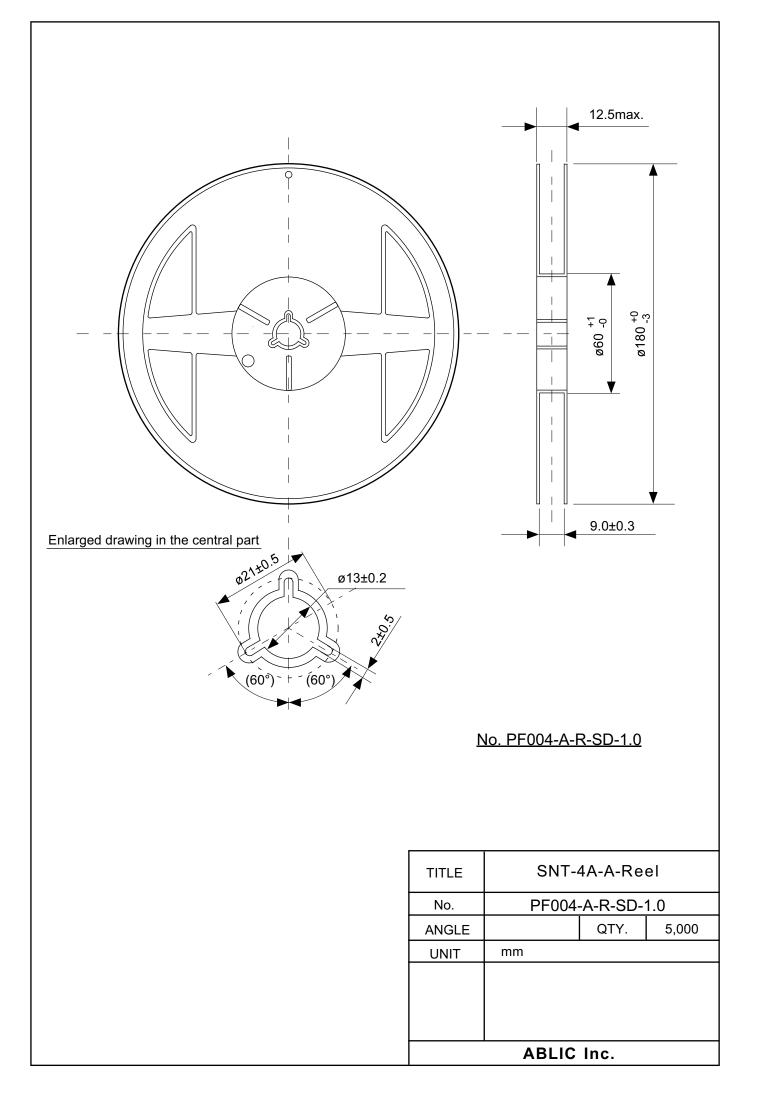

| Package Name | Dimension    | Таре         | Reel         | Land         |

|--------------|--------------|--------------|--------------|--------------|

| SOT-23-3     | MP003-C-P-SD | MP003-C-C-SD | MP003-Z-R-SD | -            |

| SNT-4A       | PF004-A-P-SD | PF004-A-C-SD | PF004-A-R-SD | PF004-A-L-SD |

#### 3. Product name list

#### 3.1 SOT-23-3

#### 3. 1. 1 Nch open-drain output product

#### Table 2

| Product Name      | Operating Cycle<br>(t <sub>CYCLE</sub> ) | Output Form           | Pole Detection | Detection Logic<br>for Magnetism | Magnetic<br>Sensitivity (B <sub>OP</sub> ) |

|-------------------|------------------------------------------|-----------------------|----------------|----------------------------------|--------------------------------------------|

| S-5715CNDL1-M3T1U | 5.70 ms                                  | Nch open-drain output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715CNSL1-M3T1U | 6.05 ms                                  | Nch open-drain output | S pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715DNDL1-M3T1U | 0.90 ms                                  | Nch open-drain output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715DNSL1-M3T1U | 1.25 ms                                  | Nch open-drain output | S pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715ENDL1-M3T1U | 0.10 ms                                  | Nch open-drain output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715ENSL1-M3T1U | 0.05 ms                                  | Nch open-drain output | S pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715ENSH1-M3T1U | 0.05 ms                                  | Nch open-drain output | S pole         | Active "H"                       | 3.0 mT typ.                                |

Remark Please contact our sales office for products other than the above.

#### 3. 1. 2 CMOS output product

#### Table 3

| Product Name      | Operating Cycle<br>(t <sub>CYCLE</sub> ) | Output Form | Pole Detection | Detection Logic<br>for Magnetism | Magnetic<br>Sensitivity (B <sub>OP</sub> ) |

|-------------------|------------------------------------------|-------------|----------------|----------------------------------|--------------------------------------------|

| S-5715CCDL1-M3T1U | 5.70 ms                                  | CMOS output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715CCSL1-M3T1U | 6.05 ms                                  | CMOS output | S pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715DCDL1-M3T1U | 0.90 ms                                  | CMOS output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715DCSL1-M3T1U | 1.25 ms                                  | CMOS output | S pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715ECDL1-M3T1U | 0.10 ms                                  | CMOS output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715ECSL1-M3T1U | 0.05 ms                                  | CMOS output | S pole         | Active "L"                       | 3.0 mT typ.                                |

Remark Please contact our sales office for products other than the above.

#### 3.2 SNT-4A

# 3. 2. 1 Nch open-drain output product

#### Table 4

| Product Name      | Operating Cycle<br>(t <sub>CYCLE</sub> ) | Output Form           | Pole Detection | Detection Logic<br>for Magnetism | Magnetic<br>Sensitivity (B <sub>OP</sub> ) |

|-------------------|------------------------------------------|-----------------------|----------------|----------------------------------|--------------------------------------------|

| S-5715CNDL1-I4T1U | 5.70 ms                                  | Nch open-drain output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715CNSL1-I4T1U | 6.05 ms                                  | Nch open-drain output | S pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715CNNL1-I4T1U | 6.05 ms                                  | Nch open-drain output | N pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715DNDL1-I4T1U | 0.90 ms                                  | Nch open-drain output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715DNSL1-I4T1U | 1.25 ms                                  | Nch open-drain output | S pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715ENDL1-I4T1U | 0.10 ms                                  | Nch open-drain output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

**Remark** Please contact our sales office for products other than the above.

### 3. 2. 2 CMOS output product

#### Table 5

| Product Name      | Operating Cycle<br>(t <sub>CYCLE</sub> ) | Output Form | Pole Detection | Detection Logic<br>for Magnetism | Magnetic<br>Sensitivity (B <sub>OP</sub> ) |

|-------------------|------------------------------------------|-------------|----------------|----------------------------------|--------------------------------------------|

| S-5715CCDL1-I4T1U | 5.70 ms                                  | CMOS output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715CCSL1-I4T1U | 6.05 ms                                  | CMOS output | S pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715CCNL1-I4T1U | 6.05 ms                                  | CMOS output | N pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715DCDL1-I4T1U | 0.90 ms                                  | CMOS output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

| S-5715DCSL1-I4T1U | 1.25 ms                                  | CMOS output | S pole         | Active "L"                       | 3.0 mT typ.                                |

| S-5715ECDL1-I4T1U | 0.10 ms                                  | CMOS output | Both poles     | Active "L"                       | 3.0 mT typ.                                |

**Remark** Please contact our sales office for products other than the above.

# Pin Configurations

# 1. SOT-23-3

| Pin No. | Symbol | Description      |

|---------|--------|------------------|

| 1       | VSS    | GND pin          |

| 2       | VDD    | Power supply pin |

| 3       | OUT    | Output pin       |

Table 6

Figure 3

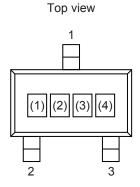

## 2. SNT-4A

| Т      | ор | view   |

|--------|----|--------|

| 1<br>2 | P  | 4<br>3 |

Figure 4

| Pin No. | Symbol           | Description      |

|---------|------------------|------------------|

| 1       | VDD              | Power supply pin |

| 2       | VSS              | GND pin          |

| 3       | NC <sup>*1</sup> | No connection    |

| 4       | OUT              | Output pin       |

Table 7

**\*1.** The NC pin is electrically open.

The NC pin can be connected to the VDD pin or the VSS pin.

# Absolute Maximum Ratings

Table 8

|                                                                |                     |                  | (Ta = +25°C unless otherwis                    | se specified) |

|----------------------------------------------------------------|---------------------|------------------|------------------------------------------------|---------------|

|                                                                | Item                | Symbol           | Absolute Maximum Rating                        | Unit          |

| Power supply voltage                                           |                     | V <sub>DD</sub>  | $V_{SS}{-}0.3$ to $V_{SS}{+}7.0$               | V             |

| Output current                                                 |                     | I <sub>OUT</sub> | ±2.0                                           | mA            |

| Nch open-drain output           Output voltage         product |                     | V <sub>OUT</sub> | $V_{SS}{-}0.3$ to $V_{SS}{+}7.0$               | V             |

|                                                                | CMOS output product |                  | $V_{\text{SS}} - 0.3$ to $V_{\text{DD}} + 0.3$ | V             |

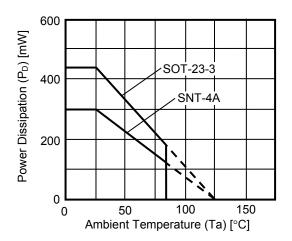

| Power dissipation                                              | SOT-23-3            | D                | 430*1                                          | mW            |

| Power dissipation                                              | SNT-4A              | - P <sub>D</sub> | 300 <sup>*1</sup>                              | mW            |

| Operation ambient temperature                                  |                     | T <sub>opr</sub> | -40 to +85                                     | °C            |

| Storage temperature                                            |                     | T <sub>stg</sub> | -40 to +125                                    | °C            |

**\*1.** When mounted on board

[Mounted board]

(1) Board size:(2) Name:

114.3 mm × 76.2 mm × t1.6 mm JEDEC STANDARD51-7

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

Figure 5 Power Dissipation of Package (When Mounted on Board)

# Electrical Characteristics

# 1. Product with both poles detection

#### 1.1 S-5715CxDxx

### Table 9

|                                |                    |                                                                     | (Ta = +25°C, V <sub>DD</sub> = 5.0                  | V, V <sub>SS</sub> =  | 0 V unl | ess othe | erwise s | pecified)       |

|--------------------------------|--------------------|---------------------------------------------------------------------|-----------------------------------------------------|-----------------------|---------|----------|----------|-----------------|

| Item                           | Symbol             | Con                                                                 | Condition                                           |                       | Тур.    | Max.     | Unit     | Test<br>Circuit |

| Power supply voltage           | $V_{DD}$           | _                                                                   |                                                     | 2.7                   | 5.0     | 5.5      | V        | _               |

| Current consumption            | I <sub>DD</sub>    | Average value                                                       |                                                     | _                     | 26.0    | 40.0     | μA       | 1               |

| Output voltage V <sub>ot</sub> |                    | Nch open-drain output<br>product                                    | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA   | -                     | -       | 0.4      | V        | 2               |

|                                | V <sub>OUT</sub>   | CMOS output product                                                 | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA   | _                     | _       | 0.4      | V        | 2               |

|                                |                    |                                                                     | Output transistor Pch,<br>$I_{OUT} = -2 \text{ mA}$ | V <sub>DD</sub> - 0.4 | _       | _        | V        | 3               |

| Leakage current                | $I_{LEAK}$         | Nch open-drain output production output transistor Nch, $V_{\rm C}$ |                                                     | _                     | _       | 1        | μA       | 4               |

| Awake mode time                | t <sub>AW</sub>    |                                                                     | _                                                   | _                     | 0.10    | -        | ms       | _               |

| Sleep mode time                | t <sub>SL</sub>    |                                                                     |                                                     |                       | 5.60    | -        | ms       | -               |

| Operating cycle                | t <sub>CYCLE</sub> | $t_{AW} + t_{SL}$                                                   |                                                     | -                     | 5.70    | 12.00    | ms       | -               |

#### 1.2 S-5715DxDxx

#### Table 10

|                                 |                    |                                  | (Ta = +25°C, V <sub>DD</sub> = 5.0                                       | V, V <sub>SS</sub> =  | 0 V unl | ess othe | erwise s | pecified)       |

|---------------------------------|--------------------|----------------------------------|--------------------------------------------------------------------------|-----------------------|---------|----------|----------|-----------------|

| Item                            | Symbol             | Con                              | dition                                                                   | Min.                  | Тур.    | Max.     | Unit     | Test<br>Circuit |

| Power supply voltage            | $V_{DD}$           |                                  | -                                                                        | 2.7                   | 5.0     | 5.5      | V        | _               |

| Current consumption             | I <sub>DD</sub>    | verage value                     |                                                                          | _                     | 155.0   | 230.0    | μA       | 1               |

| Output voltage V <sub>OUT</sub> |                    | Nch open-drain output<br>product | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA                        | _                     | _       | 0.4      | V        | 2               |

|                                 | V <sub>OUT</sub>   | CMOS output product              | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA                        | _                     | _       | 0.4      | V        | 2               |

|                                 |                    |                                  | Output transistor Pch,<br>$I_{OUT} = -2 \text{ mA}$                      | V <sub>DD</sub> - 0.4 | -       | _        | V        | 3               |

| Leakage current                 | $I_{LEAK}$         |                                  | ch open-drain output product<br>putput transistor Nch, $V_{OUT}$ = 5.5 V |                       | _       | 1        | μA       | 4               |

| Awake mode time                 | t <sub>AW</sub>    |                                  | _                                                                        | _                     | 0.10    | _        | ms       | -               |

| Sleep mode time                 | t <sub>SL</sub>    |                                  | _                                                                        |                       | 0.80    | _        | ms       | _               |

| Operating cycle                 | t <sub>CYCLE</sub> | $t_{AW} + t_{SL}$                |                                                                          | _                     | 0.90    | 2.00     | ms       | _               |

#### . . **.** . .

# HIGH-SPEED / MIDDLE-SPEED LOW CURRENT CONSUMPTION BOTH POLES / UNIPOLAR DETECTION TYPE HALL IC S-5715 Series Rev.2.3\_02

#### 1.3 S-5715ExDxx

#### Table 11

| Item                            | Symbol             | Cond                                                                    | Condition                                                                        |                       | Тур.   | Max.   | Unit | Test<br>Circuit |

|---------------------------------|--------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|--------|--------|------|-----------------|

| Power supply voltage            | V <sub>DD</sub>    | -                                                                       | _                                                                                |                       | 5.0    | 5.5    | V    | _               |

| Current consumption             | I <sub>DD</sub>    | Average value                                                           |                                                                                  | -                     | 1400.0 | 2000.0 | μA   | 1               |

| Output voltage V <sub>OUT</sub> |                    | Nch open-drain output<br>product                                        | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA                                | -                     | _      | 0.4    | V    | 2               |

|                                 | V <sub>OUT</sub>   | CMOS output product                                                     | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA                                | -                     | _      | 0.4    | V    | 2               |

|                                 |                    | CMOS output product Output transistor Pch,<br>$I_{OUT} = -2 \text{ mA}$ |                                                                                  | V <sub>DD</sub> - 0.4 | _      | -      | V    | 3               |

| Leakage current                 | $I_{LEAK}$         |                                                                         | Nch open-drain output product<br>Output transistor Nch, V <sub>OUT</sub> = 5.5 V |                       | _      | 1      | μA   | 4               |

| Awake mode time                 | t <sub>AW</sub>    | _                                                                       |                                                                                  | -                     | 0.10   | _      | ms   | -               |

| Sleep mode time                 | t <sub>SL</sub>    | _                                                                       |                                                                                  | Ι                     | 0.00   | _      | ms   | _               |

| Operating cycle                 | t <sub>CYCLE</sub> | $t_{AW} + t_{SL}$                                                       | i <sub>AW</sub> + t <sub>SL</sub>                                                |                       | 0.10   | 0.20   | ms   | _               |

#### (Ta = $+25^{\circ}$ C, V<sub>DD</sub> = 5.0 V, V<sub>SS</sub> = 0 V unless otherwise specified)

#### 2. Product with S pole or N pole detection

#### 2.1 S-5715CxSxx, S-5715CxNxx

#### Table 12

|                                 |                                  |                                                   | (Ta = +25°C, V <sub>DD</sub> = 5.0                                        | V, V <sub>SS</sub> =  | 0 V unl | ess othe | erwise s | pecified)       |

|---------------------------------|----------------------------------|---------------------------------------------------|---------------------------------------------------------------------------|-----------------------|---------|----------|----------|-----------------|

| Item                            | Symbol                           | Con                                               | Condition                                                                 |                       | Тур.    | Max.     | Unit     | Test<br>Circuit |

| Power supply voltage            | $V_{DD}$                         |                                                   | -                                                                         | 2.7                   | 5.0     | 5.5      | V        | -               |

| Current consumption             | I <sub>DD</sub>                  | Average value                                     |                                                                           | _                     | 13.0    | 20.0     | μA       | 1               |

| Output voltage V <sub>OUT</sub> | Nch open-drain output<br>product | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA | _                                                                         | _                     | 0.4     | V        | 2        |                 |

|                                 | V <sub>OUT</sub>                 | CMOS output product                               | Output transistor Nch,<br>$I_{OUT} = 2 \text{ mA}$                        | _                     | Ι       | 0.4      | V        | 2               |

|                                 |                                  |                                                   | Output transistor Pch,<br>$I_{OUT} = -2 \text{ mA}$                       | V <sub>DD</sub> - 0.4 | -       | -        | V        | 3               |

| Leakage current                 | $I_{LEAK}$                       |                                                   | Nch open-drain output product<br>Output transistor Nch, $V_{OUT}$ = 5.5 V |                       | Ι       | 1        | μA       | 4               |

| Awake mode time                 | t <sub>AW</sub>                  |                                                   | _                                                                         |                       | 0.05    | _        | ms       | _               |

| Sleep mode time                 | t <sub>SL</sub>                  | _                                                 |                                                                           | _                     | 6.00    | -        | ms       | _               |

| Operating cycle                 | t <sub>CYCLE</sub>               | t <sub>AW</sub> + t <sub>SL</sub>                 |                                                                           | -                     | 6.05    | 12.00    | ms       | _               |

#### 2. 2 S-5715DxSxx, S-5715DxNxx

#### Table 13

| (Ta = +25°C, V <sub>DD</sub> = 5.0 V, V <sub>SS</sub> = 0 V unless otherwise specifie |                    |                                                                                                                                                                        |                                                                                  |                       | peemeu) |      |      |                 |

|---------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|---------|------|------|-----------------|

| Item                                                                                  | Symbol             | Con                                                                                                                                                                    | Condition                                                                        |                       | Тур.    | Max. | Unit | Test<br>Circuit |

| Power supply voltage                                                                  | $V_{DD}$           |                                                                                                                                                                        | _                                                                                | 2.7                   | 5.0     | 5.5  | V    | _               |

| Current consumption                                                                   | I <sub>DD</sub>    | Average value                                                                                                                                                          |                                                                                  | _                     | 60.0    | 90.0 | μA   | 1               |

| Output voltage V <sub>OUT</sub>                                                       |                    | Nch open-drain output product                                                                                                                                          | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA                                | _                     | I       | 0.4  | V    | 2               |

|                                                                                       | V <sub>OUT</sub>   | CMOS output product $\begin{array}{l} \text{Output transistor Nch,} \\ I_{OUT} = 2 \text{ mA} \\ \text{Output transistor Pch,} \\ I_{OUT} = -2 \text{ mA} \end{array}$ | _                                                                                | Ι                     | 0.4     | V    | 2    |                 |

|                                                                                       |                    |                                                                                                                                                                        | -                                                                                | V <sub>DD</sub> - 0.4 | Ι       | _    | V    | 3               |

| Leakage current                                                                       | $I_{LEAK}$         |                                                                                                                                                                        | Nch open-drain output product<br>Output transistor Nch, V <sub>OUT</sub> = 5.5 V |                       | Ι       | 1    | μA   | 4               |

| Awake mode time                                                                       | t <sub>AW</sub>    | _                                                                                                                                                                      |                                                                                  | _                     | 0.05    | _    | ms   | -               |

| Sleep mode time                                                                       | t <sub>SL</sub>    | _                                                                                                                                                                      |                                                                                  | -                     | 1.20    | -    | ms   | -               |

| Operating cycle                                                                       | t <sub>CYCLE</sub> | $t_{AW} + t_{SL}$                                                                                                                                                      | t <sub>AW</sub> + t <sub>SL</sub>                                                |                       | 1.25    | 2.50 | ms   | _               |

# (Ta = +25°C, $V_{DD}$ = 5.0 V, $V_{SS}$ = 0 V unless otherwise specified)

#### 2.3 S-5715ExSxx, S-5715ExNxx

#### Table 14

| Item                            | Symbol             | Con                                                                     | Condition                                                                        |                          | Тур.   | Max.   | Unit | Test<br>Circuit |

|---------------------------------|--------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------|--------|--------|------|-----------------|

| Power supply voltage            | $V_{DD}$           |                                                                         | _                                                                                |                          | 5.0    | 5.5    | V    | _               |

| Current consumption             | I <sub>DD</sub>    | Average value                                                           |                                                                                  | -                        | 1400.0 | 2000.0 | μA   | 1               |

| Output voltage V <sub>OUT</sub> |                    | Nch open-drain output<br>product                                        | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA                                | -                        | _      | 0.4    | V    | 2               |

|                                 | V <sub>OUT</sub>   | CMOS output product                                                     | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA                                | -                        | _      | 0.4    | V    | 2               |

|                                 |                    | CMOS output product Output transistor Pch,<br>$I_{OUT} = -2 \text{ mA}$ |                                                                                  | V <sub>DD</sub> –<br>0.4 | _      | -      | V    | 3               |

| Leakage current                 | $I_{\text{LEAK}}$  |                                                                         | Nch open-drain output product<br>Output transistor Nch, V <sub>OUT</sub> = 5.5 V |                          | _      | 1      | μA   | 4               |

| Awake mode time                 | t <sub>AW</sub>    |                                                                         | _                                                                                |                          | 0.05   | _      | ms   | _               |

| Sleep mode time                 | t <sub>SL</sub>    |                                                                         |                                                                                  | _                        | 0.00   | _      | ms   | _               |

| Operating cycle                 | t <sub>CYCLE</sub> | $t_{AW} + t_{SL}$                                                       | i <sub>AW</sub> + t <sub>SL</sub>                                                |                          | 0.05   | 0.10   | ms   | _               |

#### $(Ta = +25^{\circ}C, V_{DD} = 5.0 \text{ V}, V_{SS} = 0 \text{ V}$ unless otherwise specified)

### Magnetic Characteristics

#### 1. Product with both poles detection

#### Table 15

|                                |        |                   | (Ta = +2                         | 5°C, V <sub>DD</sub> = | 5.0 V, V <sub>SS</sub> | = 0 V unle | ss other | wise specified) |

|--------------------------------|--------|-------------------|----------------------------------|------------------------|------------------------|------------|----------|-----------------|

| Item                           |        | Symbol            | Condition                        | Min.                   | Тур.                   | Max.       | Unit     | Test Circuit    |

| Operation paint*1              | S pole | B <sub>OPS</sub>  | -                                | 1.4                    | 3.0                    | 4.0        | mT       | 5               |

| Operation point <sup>*1</sup>  | N pole | B <sub>OPN</sub>  | _                                | -4.0                   | -3.0                   | -1.4       | mT       | 5               |

| Release point <sup>*2</sup>    | S pole | B <sub>RPS</sub>  | -                                | 1.1                    | 2.2                    | 3.7        | mT       | 5               |

| Release point                  | N pole | B <sub>RPN</sub>  | _                                | -3.7                   | -2.2                   | -1.1       | mT       | 5               |

| Hysteresis width <sup>*3</sup> | S pole | B <sub>HYSS</sub> | $B_{HYSS} = B_{OPS} - B_{RPS}$   | _                      | 0.8                    | I          | mT       | 5               |

|                                | N pole | B <sub>HYSN</sub> | $B_{HYSN} =  B_{OPN} - B_{RPN} $ | -                      | 0.8                    | -          | mT       | 5               |

#### 2. Product with S pole detection

#### Table 16

|                               |        |                   | (Ta = +2                                                | 5°C, V <sub>DD</sub> = | 5.0 V, V <sub>SS</sub> | = 0 V unle | ess other | wise specified) |

|-------------------------------|--------|-------------------|---------------------------------------------------------|------------------------|------------------------|------------|-----------|-----------------|

| Item                          |        | Symbol            | Condition                                               | Min.                   | Тур.                   | Max.       | Unit      | Test Circuit    |

| Operation point <sup>*1</sup> | S pole | B <sub>OPS</sub>  | -                                                       | 1.4                    | 3.0                    | 4.0        | mT        | 5               |

| Release point <sup>*2</sup>   | S pole | B <sub>RPS</sub>  | -                                                       | 1.1                    | 2.2                    | 3.7        | mT        | 5               |

| Hysteresis width*3            | S pole | B <sub>HYSS</sub> | B <sub>HYSS</sub> = B <sub>OPS</sub> – B <sub>RPS</sub> | -                      | 0.8                    | -          | mT        | 5               |

#### 3. Product with N pole detection

#### Table 17

(Ta =  $+25^{\circ}$ C, V<sub>DD</sub> = 5.0 V, V<sub>SS</sub> = 0 V unless otherwise specified)

| Item                          |        | Symbol            | Condition                        | Min. | Тур. | Max. | Unit | Test Circuit |

|-------------------------------|--------|-------------------|----------------------------------|------|------|------|------|--------------|

| Operation point <sup>*1</sup> | N pole | B <sub>OPN</sub>  | -                                | -4.0 | -3.0 | -1.4 | mT   | 5            |

| Release point <sup>*2</sup>   | N pole | B <sub>RPN</sub>  | _                                | -3.7 | -2.2 | -1.1 | mT   | 5            |

| Hysteresis width*3            | N pole | B <sub>HYSN</sub> | $B_{HYSN} =  B_{OPN} - B_{RPN} $ | I    | 0.8  | I    | mT   | 5            |

\*1. B<sub>OPN</sub>, B<sub>OPS</sub>: Operation points

$B_{OPN}$  and  $B_{OPS}$  are the values of magnetic flux density when the output voltage (V<sub>OUT</sub>) is inverted after the magnetic flux density applied to the S-5715 Series by the magnet (N pole or S pole) is increased (the magnet is moved closer). Even when the magnetic flux density exceeds  $B_{OPN}$  or  $B_{OPS}$ ,  $V_{OUT}$  retains the status.

\*2. B<sub>RPN</sub>, B<sub>RPS</sub>: Release points

$B_{RPN}$  and  $B_{RPS}$  are the values of magnetic flux density when the output voltage (V<sub>OUT</sub>) is inverted after the magnetic flux density applied to the S-5715 Series by the magnet (N pole or S pole) is decreased (the magnet is moved further away). Even when the magnetic flux density falls below  $B_{RPN}$  or  $B_{RPS}$ , V<sub>OUT</sub> retains the status.

#### \*3. B<sub>HYSN</sub>, B<sub>HYSS</sub>: Hysteresis widths

$B_{HYSN}$  and  $B_{HYSS}$  are the difference between  $B_{OPN}$  and  $B_{RPN}$ , and  $B_{OPS}$  and  $B_{RPS}$ , respectively.

**Remark** The unit of magnetic density mT can be converted by using the formula 1 mT = 10 Gauss.

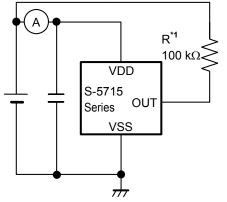

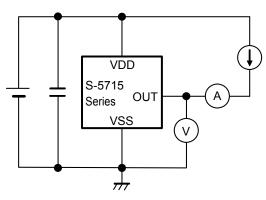

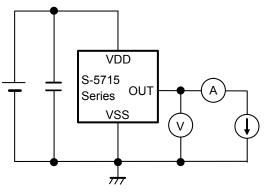

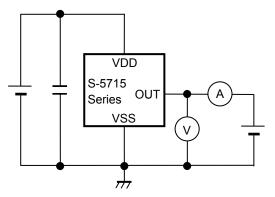

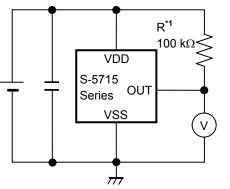

# Test Circuits

\*1. Resistor (R) is unnecessary for the CMOS output product.

Figure 6 Test Circuit 1

Figure 7 Test Circuit 2

Figure 8 Test Circuit 3

Figure 9 Test Circuit 4

\*1. Resistor (R) is unnecessary for the CMOS output product.

Figure 10 Test Circuit 5

# Standard Circuit

\*1. Resistor (R) is unnecessary for the CMOS output product.

#### Figure 11

Caution The above connection diagram and constant will not guarantee successful operation. Perform thorough evaluation using the actual application to set the constant.

# Operation

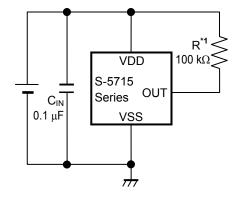

#### 1. Direction of applied magnetic flux

The S-5715 Series detects the flux density which is vertical to the marking surface.

In product with both poles detection, the output voltage (V<sub>OUT</sub>) is inverted when the S pole or N pole is moved closer to the marking surface.

In product with S pole detection, the output voltage ( $V_{OUT}$ ) is inverted when the S pole is moved closer to the marking surface.

In product with N pole detection, the output voltage ( $V_{OUT}$ ) is inverted when the N pole is moved closer to the marking surface.

Figure 12 and Figure 13 show the direction in which magnetic flux is being applied.

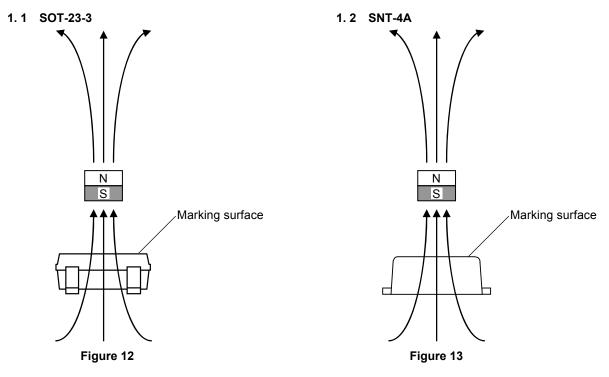

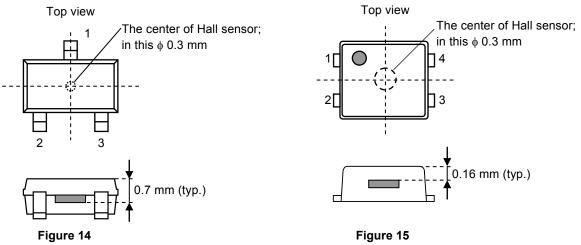

#### 2. Position of Hall sensor

Figure 14 and Figure 15 show the position of Hall sensor.

The center of this Hall sensor is located in the area indicated by a circle, which is in the center of a package as described below.

2.2 SNT-4A

The following also shows the distance (typ. value) between the marking surface and the chip surface of a package.

#### 2.1 SOT-23-3

**ABLIC Inc.**

#### 3. Basic operation

The S-5715 Series changes the output voltage level ( $V_{OUT}$ ) according to the level of the magnetic flux density (N pole or S pole) applied by a magnet.

The following explains the operation when the magnetism detection logic is active "L".

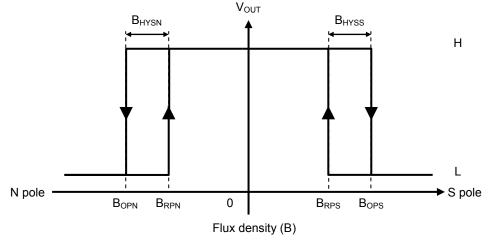

#### 3.1 Product with both poles detection

When the magnetic flux density vertical to the marking surface exceeds  $B_{OPN}$  or  $B_{OPS}$  after the S pole or N pole of a magnet is moved closer to the marking surface of the S-5715 Series,  $V_{OUT}$  changes from "H" to "L". When the S pole or N pole of a magnet is moved further away from the marking surface of the S-5715 Series and the magnetic flux density is lower than  $B_{RPN}$  or  $B_{RPS}$ ,  $V_{OUT}$  changes from "L" to "H".

Figure 16 shows the relationship between the magnetic flux density and  $V_{\mbox{\scriptsize OUT}}.$

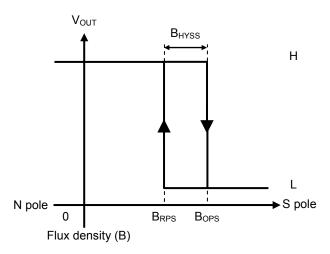

#### 3.2 Product with S pole detection

When the magnetic flux density vertical to the marking surface exceeds  $B_{OPS}$  after the S pole of a magnet is moved closer to the marking surface of the S-5715 Series,  $V_{OUT}$  changes from "H" to "L". When the S pole of a magnet is moved further away from the marking surface of the S-5715 Series and the magnetic flux density is lower than  $B_{RPS}$ ,  $V_{OUT}$  changes from "L" to "H".

Figure 17 shows the relationship between the magnetic flux density and  $V_{OUT}$ .

Figure 17

# ABLIC Inc.

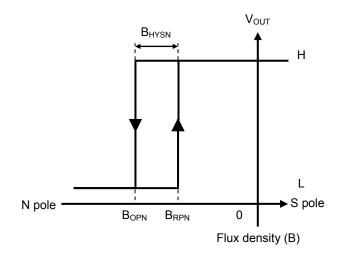

#### 3.3 Product with N pole detection

When the magnetic flux density vertical to the marking surface exceeds  $B_{OPN}$  after the N pole of a magnet is moved closer to the marking surface of the S-5715 Series,  $V_{OUT}$  changes from "H" to "L". When the N pole of a magnet is moved further away from the marking surface of the S-5715 Series and the magnetic flux density is lower than  $B_{RPN}$ ,  $V_{OUT}$  changes from "L" to "H".

Figure 18 shows the relationship between the magnetic flux density and  $V_{OUT}$ .

Figure 18

# Precautions

- If the impedance of the power supply is high, the IC may malfunction due to a supply voltage drop caused by feedthrough current. Take care with the pattern wiring to ensure that the impedance of the power supply is low.

- Note that the IC may malfunction if the power supply voltage rapidly changes.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- Large stress on this IC may affect on the magnetic characteristics. Avoid large stress which is caused by bend and distortion during mounting the IC on a board or handle after mounting.

- ABLIC Inc. claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

# Marking Specifications

1. SOT-23-3

(4):

(1) to (3): Product code (Refer to Product name vs. Product code.) Lot number

#### Product name vs. Product code

#### 1.1 Nch open-drain output product

| Product Name      | Pro | oduct Co | de  |

|-------------------|-----|----------|-----|

| Product Name      | (1) | (2)      | (3) |

| S-5715CNDL1-M3T1U | Х   | 2        | С   |

| S-5715CNSL1-M3T1U | Х   | 2        | L   |

| S-5715DNDL1-M3T1U | Х   | 2        | В   |

| S-5715DNSL1-M3T1U | Х   | 2        | 0   |

| S-5715ENDL1-M3T1U | Х   | 2        | R   |

| S-5715ENSL1-M3T1U | Х   | 2        | Α   |

| S-5715ENSH1-M3T1U | Х   | 2        | U   |

#### 1.2 CMOS output product

| Product Name      | Product Code |     |     |  |  |

|-------------------|--------------|-----|-----|--|--|

| FIODUCEINAILIE    | (1)          | (2) | (3) |  |  |

| S-5715CCDL1-M3T1U | Х            | 2   | М   |  |  |

| S-5715CCSL1-M3T1U | Х            | 2   | Ν   |  |  |

| S-5715DCDL1-M3T1U | Х            | 2   | Р   |  |  |

| S-5715DCSL1-M3T1U | Х            | 2   | Q   |  |  |

| S-5715ECDL1-M3T1U | Х            | 2   | S   |  |  |

| S-5715ECSL1-M3T1U | Х            | 2   | Т   |  |  |

# HIGH-SPEED / MIDDLE-SPEED LOW CURRENT CONSUMPTION BOTH POLES / UNIPOLAR DETECTION TYPE HALL IC S-5715 Series Rev.2.3\_02

#### 2. SNT-4A

Top view 1 2 (1) (2) (3) 3

(1) to (3): Product code (Refer to Product name vs. Product code.)

#### Product name vs. Product code

#### 2.1 Nch open-drain output product

| Product Name      | Product Code |     |     |  |

|-------------------|--------------|-----|-----|--|

| Product Name      | (1)          | (2) | (3) |  |

| S-5715CNDL1-I4T1U | Х            | 2   | С   |  |

| S-5715CNSL1-I4T1U | Х            | 2   | L   |  |

| S-5715CNNL1-I4T1U | Х            | 2   | V   |  |

| S-5715DNDL1-I4T1U | Х            | 2   | В   |  |

| S-5715DNSL1-I4T1U | Х            | 2   | 0   |  |

| S-5715ENDL1-I4T1U | Х            | 2   | R   |  |

#### 2.2 CMOS output product

| Product Name      | Product Code |     |     |  |

|-------------------|--------------|-----|-----|--|

| FIGULE Name       | (1)          | (2) | (3) |  |

| S-5715CCDL1-I4T1U | Х            | 2   | М   |  |

| S-5715CCSL1-I4T1U | Х            | 2   | Ν   |  |

| S-5715CCNL1-I4T1U | Х            | 2   | W   |  |

| S-5715DCDL1-I4T1U | Х            | 2   | Р   |  |

| S-5715DCSL1-I4T1U | Х            | 2   | Q   |  |

| S-5715ECDL1-I4T1U | Х            | 2   | S   |  |

No. MP003-C-P-SD-1.1

| TITLE      | SOT233-C-PKG Dimensions |  |  |  |

|------------|-------------------------|--|--|--|

| No.        | MP003-C-P-SD-1.1        |  |  |  |

| ANGLE      | $\oplus$                |  |  |  |

| UNIT       | mm                      |  |  |  |

|            |                         |  |  |  |

|            |                         |  |  |  |

|            |                         |  |  |  |

| ABLIC Inc. |                         |  |  |  |

ABLIC Inc.

※1. ランドパターンの幅に注意してください (0.25 mm min. / 0.30 mm typ.)。 ※2. パッケージ中央にランドパターンを広げないでください (1.10 mm ~ 1.20 mm)。

- 注意 1. パッケージのモールド樹脂下にシルク印刷やハンダ印刷などしないでください。

- 2. パッケージ下の配線上のソルダーレジストなどの厚みをランドパターン表面から0.03 mm 以下にしてください。

- 3. マスク開口サイズと開口位置はランドパターンと合わせてください。

- 4. 詳細は "SNTパッケージ活用の手引き" を参照してください。

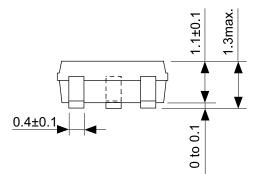

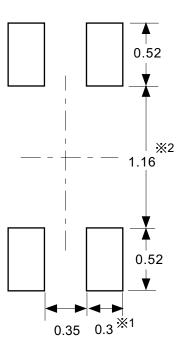

%1. Pay attention to the land pattern width (0.25 mm min. / 0.30 mm typ.).

%2. Do not widen the land pattern to the center of the package (1.10 mm to 1.20 mm).

Caution 1. Do not do silkscreen printing and solder printing under the mold resin of the package.

- 2. The thickness of the solder resist on the wire pattern under the package should be 0.03 mm or less from the land pattern surface.

- 3. Match the mask aperture size and aperture position with the land pattern.

- 4. Refer to "SNT Package User's Guide" for details.

- ※1. 请注意焊盘模式的宽度 (0.25 mm min. / 0.30 mm typ.)。

- ※2. 请勿向封装中间扩展焊盘模式 (1.10 mm ~ 1.20 mm)。

- 注意 1. 请勿在树脂型封装的下面印刷丝网、焊锡。

- 2. 在封装下、布线上的阻焊膜厚度 (从焊盘模式表面起) 请控制在 0.03 mm 以下。

- 3. 钢网的开口尺寸和开口位置请与焊盘模式对齐。

- 4. 详细内容请参阅 "SNT 封装的应用指南"。

| TITLE      | SNT-4A-A<br>-Land Recommendation |

|------------|----------------------------------|

| No.        | PF004-A-L-SD-4.1                 |

| ANGLE      |                                  |

| UNIT       | mm                               |

|            |                                  |

|            |                                  |

|            |                                  |

| ABLIC Inc. |                                  |

# **Disclaimers (Handling Precautions)**

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the incorrect information described herein.

- 4. Be careful to use the products within their ranges described herein. Pay special attention for use to the absolute maximum ratings, operation voltage range and electrical characteristics, etc. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by failures and / or accidents, etc. due to the use of the products outside their specified ranges.

- 5. Before using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products are strictly prohibited from using, providing or exporting for the purposes of the development of weapons of mass destruction or military use. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by any provision or export to the person or entity who intends to develop, manufacture, use or store nuclear, biological or chemical weapons or missiles, or use any other military purposes.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses by ABLIC, Inc. Do not apply the products to the above listed devices and equipments. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by unauthorized or unspecified use of the products.

- 9. In general, semiconductor products may fail or malfunction with some probability. The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

The entire system in which the products are used must be sufficiently evaluated and judged whether the products are allowed to apply for the system on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of ABLIC Inc. The information described herein does not convey any license under any intellectual property rights or any other rights belonging to ABLIC Inc. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party is strictly prohibited without the express permission of ABLIC Inc.

- 14. For more details on the information described herein or any other questions, please contact ABLIC Inc.'s sales representative.

- 15. This Disclaimers have been delivered in a text using the Japanese language, which text, despite any translations into the English language and the Chinese language, shall be controlling.

2.4-2019.07

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Board Mount Hall Effect/Magnetic Sensors category:

Click to view products by Ablic manufacturer:

Other Similar products are found below :

HGPRDT005A AH1808-P-A AH277AZ4-AG1 AV-10379 AV-10448 SS41C AH1894-Z-7 ATS601LSGTN-LT-WU4-T TLE4917 50017859-003 TY-13101 TLE4976L SS85CA AH277AZ4-BG1 TLE49614MXTSA1 AH3377-P-B AH211Z4-AG1 AH3360-FT4-7 SS460S-100SAMPLE 50065820-03 TLE4941PLUSCB AH374-P-A AH1806-P-A AH374-W-7 SS460P-T2 SI7201-B-20-IVR SS413F TLE5046ICAKLRHALA1 TLE49421CHAMA2 TLE4941PLUSCXAMA1 AH1912-W-EVM AH1903-FA-EVM AH3774-W-EVM AH49FNTR-EVM MMC5633NJL AH3360-FA-EVM AH8502-FDC-EVM AH3366Q-SA-EVM AH3774-P-EVM KTH1601SU-ST3 MG910 MG910M MG911 MG610 MW921 MW922 TLE4998S3XALA1 TLE5011FUMA1 TLE5027CE6747HAMA1 TLE5109A16E1210XUMA1