### **FEATURES AND BENEFITS**

- Five floating N-channel MOSFET drives

- Maintains  $V_{GS}$  with 100 k $\Omega$  gate-source resistors

- Integrated charge pump controller

- 4.5 to 85 V supply voltage operating range

- Supports source-to-source and drain-to-drain battery MOSFET isolation

- V<sub>CP</sub> and V<sub>GS</sub> undervoltage protection

- 150°C ambient (165°C junction) continuous

- Fully integrated diagnostics for safe motor phase and battery disconnect

- Extensive programmable diagnostics

- · Diagnostic verification

- · Automotive AEC-Q100 qualified

- A<sup>2</sup>-SIL<sup>TM</sup> product—device features for safety-critical system: Developed in accordance with ISO 26262 as a hardware safety element out of context with ASIL B capability for use in automotive safety-related systems when integrated and used in the manner prescribed in the applicable safety application note and datasheet.

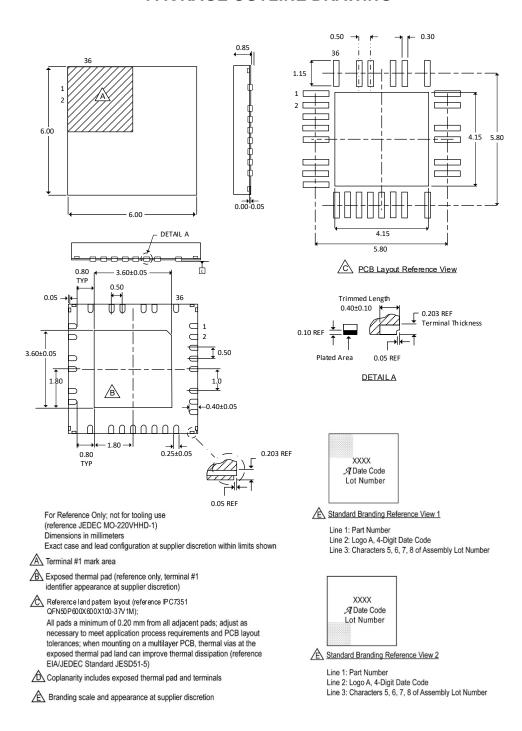

### **PACKAGES**

Not to scale

28-contact QFN with wettable flanks and exposed pad (suffix ET)

28-contact QFN with wettable flanks and exposed pad (suffix EV)

#### **DESCRIPTION**

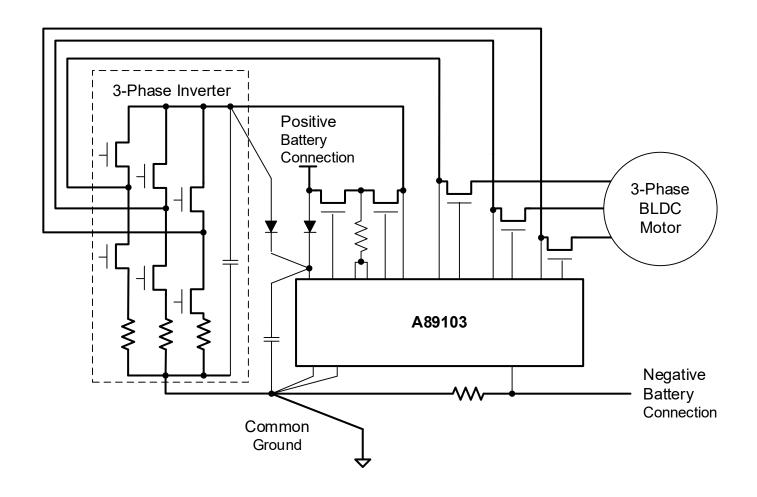

The A89103 is an N-channel power MOSFET driver capable of controlling five MOSFETs to provide motor-phase isolation and supply isolation in three-phase BLDC applications. Three floating gate-drive outputs maintain phase-isolator power MOSFETs in the on state, over the full supply range, with high-phase voltage and high dv/dt on the motor-phase connection for  $12\,V$  and  $48\,V$  systems. Two additional floating gate drivers are provided to isolate the battery supply voltage during reverse-battery or short-circuit conditions. The A89103 supports both source-to-source and drain-to-drain battery MOSFET isolation. An integrated charge-pump regulator provides the above-battery-supply voltage necessary to continuously maintain the power N-channel MOSFETs in the on state. The charge pump maintains sufficient gate drive power (> 7.5 V) for battery voltages down to 4.5 V with  $100\,\mathrm{k}\Omega$  gate source resistors.

The five floating gate drives can be configured, monitored, and controlled through the SPI interface. When not in use, the A89103 can be placed in a low-power sleep mode.

Undervoltage monitors check that the pumped supply voltage and the gate drive outputs are high enough to ensure that the MOSFETs are maintained in a safe conducting state.

The A89103 is supplied in a 28-contact wettable-flank quad flat no-lead (QFN) package (suffix ET), and 28-contact wettable-flank QFN (suffix EV), both with exposed pads for enhanced thermal dissipation. They are lead (Pb) free, with 100% matte tin leadframe plating.

#### TYPICAL APPLICATIONS

- Three-phase and battery isolation for ASIL systems up to level B

- Electric power steering (EPS)

- Electric braking (EMB)

- Redundant motor-control systems

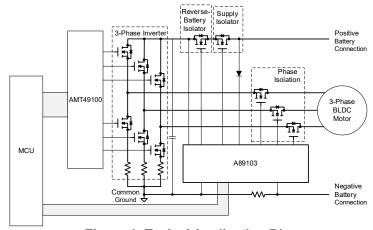

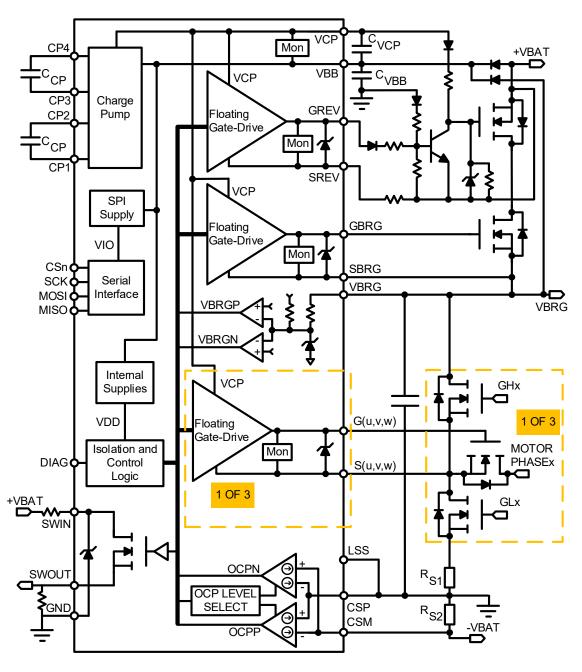

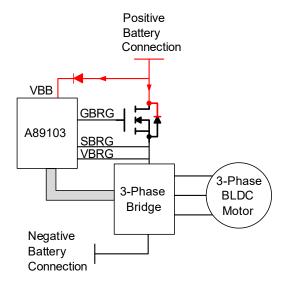

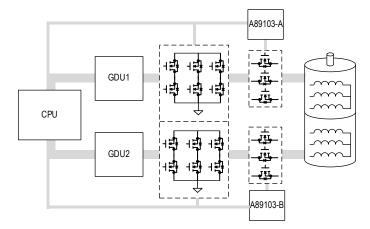

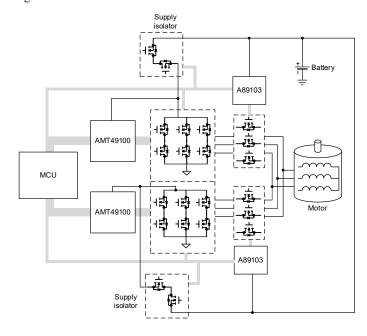

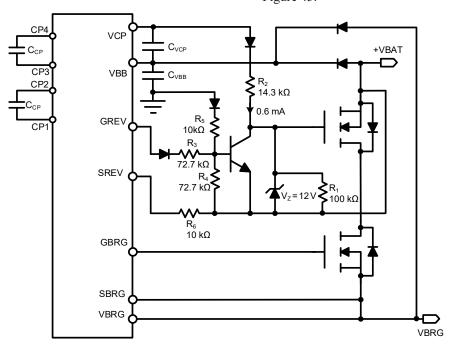

**Figure 1: Typical Application Diagram**

# Automotive Three-Phase and Battery Isolator MOSFET Driver

## **Table of Contents**

| Features and Benefits                                    | 1  | Enable/Disable Registers                          | 4  |

|----------------------------------------------------------|----|---------------------------------------------------|----|

| Packages                                                 | 1  | Configuration Registers                           | 4  |

| Description                                              | 1  | Verification Registers                            | 4  |

| Typical Applications                                     | 1  | Diagnostic Registers                              | 4  |

| Specifications                                           | 3  | Readback                                          | 4  |

| Pinout Diagrams and Terminal List Table                  |    | Device Identification                             | 4  |

| Functional Block Diagrams                                |    | Status Serial Register Reference                  | 4  |

| Characteristic Performance                               |    | Enable/Disable Serial Register Reference          |    |

| Functional Description                                   | 13 | Configuration Serial Register Reference           | 4  |

| Overview                                                 | 13 | Verify Command Serial Register Reference          |    |

| Input and Output Terminal Functions                      | 14 | Diagnostic Serial Register Reference              | 49 |

| Power Supply                                             |    | Verify Result Serial Register Reference           |    |

| DC Link Charging                                         |    | Readback Serial Register Reference                |    |

| Charge Pump Regulator                                    | 17 | Identification Serial Register Reference          |    |

| Gate Drives                                              | 18 | Application Information                           |    |

| Driver Control via Serial Interface                      | 19 | Isolation Current Considerations                  |    |

| Common-Source/Drain Driver Configuration                 |    | Battery Isolation                                 |    |

| VBAT Resistor Divider Switch                             |    | Reverse Battery Isolation                         |    |

| Diagnostic Monitors                                      | 21 | Phase-Current Isolation                           |    |

| DIAG Diagnostic Output                                   | 21 | MOSFET Avalanche Protection                       | 5  |

| Diagnostic Registers                                     | 22 | External Protection                               | 54 |

| Chip Fault State: Internal Logic Overvoltage             | 23 | Digital Protection                                | 5  |

| Chip Fault State: Internal Logic and Supply Undervoltage | 23 | MOSFET Avalanche Allowance                        |    |

| Chip Fault State: Serial Error                           | 23 | Additional Features                               | 5  |

| Operational Monitors                                     | 24 | Current-Dependent Isolation                       | 50 |

| Gate-Drive Output Monitor                                | 24 | Reverse-Supply MOSFET Current-Dependent Isolation |    |

| Charge Pump Output Monitor                               | 24 | Voltage-Dependent Isolation                       |    |

| Temperature Warning                                      |    | External Triggering Isolation                     |    |

| Negative-Overcurrent Sensing                             | 25 | Automatic Isolation Combinations                  | 5  |

| Positive-Overcurrent Sensing                             | 26 | Battery MOSFET Driver Basic Configuration         | 6  |

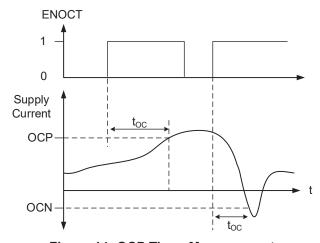

| OCP Timer                                                | 27 | Reverse MOSFET Driver Basic Configuration         | 60 |

| VBRG Voltage Monitoring                                  | 28 | Phase MOSFET Driver Basic Configuration           | 6  |

| Fault Action                                             | 30 | Watchdog Monitor Basic Configuration              |    |

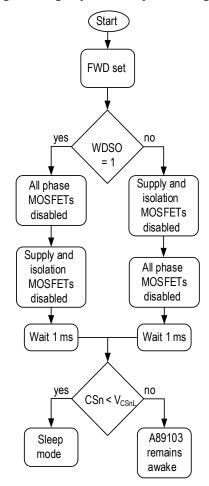

| SPI Watchdog                                             | 31 | DC Link Capacitor Charging                        | 6  |

| Sleep State                                              | 32 | Fault Masking                                     | 6  |

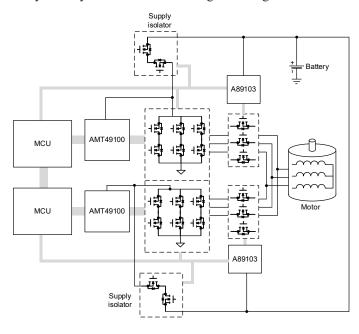

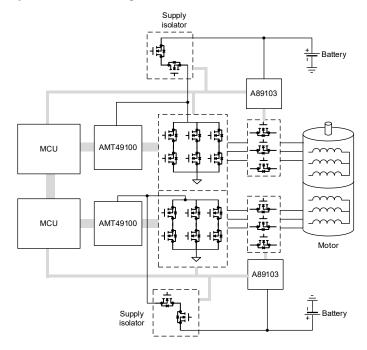

| Diagnostic and System Verification                       | 33 | Independent Drive Systems                         | 6  |

| Online Verification                                      | 33 | Redundant Drive Systems                           |    |

| Offline Verification                                     | 33 | Digital Clock Frequency Configuration             | 6  |

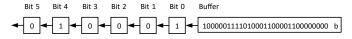

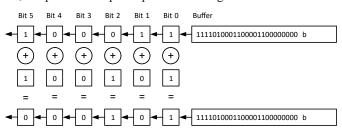

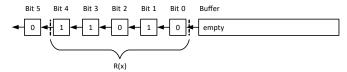

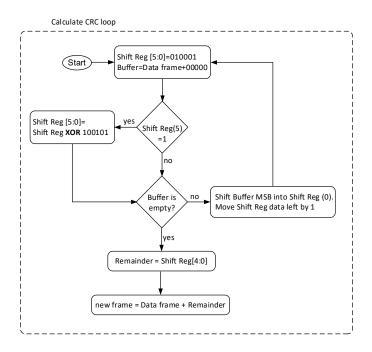

| Serial Interface                                         | 35 | Cyclic Redundancy Check                           | 68 |

| Header Frame                                             | 36 | Current Sense Monitor Configuration               |    |

| Response Frame                                           | 36 | Input/Output Structures                           | 7  |

| F <sub>CLK</sub> -Dependent Timing Configuration         |    | Layout Recommendations                            | 7  |

| Device Identification Register                           | 37 | Package Outline Drawing                           | 7  |

| Transmission Error Handling                              | 37 | Package Outline Drawing                           | 7  |

| Sequential Transmissions                                 |    | Appendix                                          | 7  |

| Serial Interface Default Values                          | 40 | Errata—Recommended Deglitch Filter Time Setting   | 70 |

| Status Register                                          | 41 | Errata—SPI Watchdog Timeout Consideration         | 7  |

### **SPECIFICATIONS**

### **SELECTION GUIDE**

| Part Number   | I/O Logic | Package                                                       |  |  |  |  |

|---------------|-----------|---------------------------------------------------------------|--|--|--|--|

| A89103KETSR-3 | 3.3 V     | 5 mm × 5 mm × 0.75 mm 28-contact QFN with exposed thermal p   |  |  |  |  |

| A89103KETSR-5 | 5 V       | 3 mm × 3 mm × 0.73 mm 20-contact QFN with exposed thermal pad |  |  |  |  |

| A89103KEVSR-3 | 3.3 V     | 6 mm × 6 mm × 0.9 mm 28-contact QFN with exposed thermal pad  |  |  |  |  |

| A89103KEVSR-5 | 5 V       | 6 mm × 6 mm × 0.9 mm 26-contact QFN with exposed thermal pad  |  |  |  |  |

#### **ESD RATINGS**

ESD Information for Handling of ESDS in an ESD Protected Area

CDM (AEC-Q100-011JS-002: CDM withstand threshold of 1000 V; CDM Class C3

**HBM** (AEC-Q100-002/JS-00102017): HBM withstand threshold of 1500 V; HBM Class 2 NOTE: The HBM withstand threshold is determined by two pins (GREV and GBRG) that pass at 1500 V. All other pins pass at 2000 V.

# **Automotive Three-Phase and Battery Isolator MOSFET Driver**

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                          | Symbol                                | Conditions                                                                                                                      | Rating [1]                                    | Units |

|-----------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------|

| Load Voltage Supply                     | $V_{BB}$                              |                                                                                                                                 | -0.3 to 85                                    | V     |

| Terminal VCP                            | V <sub>CP</sub>                       |                                                                                                                                 | $V_{BB} - 0.3$ to $V_{BB} + 12$               | V     |

| Terminal CP1                            | V <sub>CP1</sub>                      |                                                                                                                                 | $V_{BB} - 12 \text{ to } V_{BB} + 0.3$        | V     |

| Terminal CP2                            | V <sub>CP2</sub>                      |                                                                                                                                 | $V_{BB} - 0.3 \text{ to } V_{CP} + 1$         | V     |

| Terminal CP3                            | V <sub>CP3</sub>                      |                                                                                                                                 | V <sub>BB</sub> – 12 to V <sub>BB</sub> + 0.3 | V     |

| Terminal CP4                            | V <sub>CP4</sub>                      |                                                                                                                                 | $V_{BB} - 0.3 \text{ to } V_{CP} + 1$         | V     |

| Terminal CSn, SCK, MOSI, MISO, DIAG     | V <sub>IO</sub>                       | A89103KETSR-3                                                                                                                   | -0.3 to 4 [2]                                 | V     |

| Terminal CSn, SCK, MOSI, MISO, DIAG     | V <sub>IO</sub>                       | A89103KETSR-5                                                                                                                   | -0.3 to 6 <sup>[2]</sup>                      | V     |

| Terminal SWIN                           | V <sub>SWIN</sub>                     | V <sub>SWINSCL</sub> > 85 V                                                                                                     | -0.3 to SCL <sup>[3]</sup>                    | V     |

| Terminal SWIN                           | I <sub>SWIN</sub>                     |                                                                                                                                 | -4 to 4                                       | mA    |

| Terminal SWOUT                          | V <sub>SWOUT</sub>                    |                                                                                                                                 | -0.3 to 6                                     | V     |

| Terminal GU, GV, GW, GREV, GBRG         | $V_{GX}$                              |                                                                                                                                 | $V_{SX} - 0.3 \text{ to } V_{SX} + 16$        | V     |

| Terminal CSP, CSM                       | V <sub>CSN</sub>                      |                                                                                                                                 | -4 to 6                                       | V     |

| Terminal LSS                            | V <sub>LSS</sub>                      |                                                                                                                                 | –4 to 6                                       | V     |

| Terminal SU, SV, SW                     | V <sub>Sx</sub>                       |                                                                                                                                 | -16 to 85                                     | V     |

| Terminal SREV, SBRG                     | $V_{SREV}, V_{SBRG}$                  | V <sub>SREVSCL</sub> and V <sub>SBRGSCL</sub> < -16 V                                                                           | -SCL <sup>[4]</sup> to 85                     | V     |

| Terminal SREV, SBRG                     | I <sub>SREV</sub> , I <sub>SBRG</sub> | Limited by power dissipation                                                                                                    | -150 to 10                                    | mA    |

| Terminal VBRG                           | $V_{BRG}$                             |                                                                                                                                 | -5 to 85                                      | V     |

| Operating Ambient Temperature           | T <sub>A</sub>                        | Limited by power dissipation                                                                                                    | -40 to 150                                    | °C    |

| Maximum Continuous Junction Temperature | T <sub>J(max)</sub>                   |                                                                                                                                 | 165                                           | °C    |

| Transient Junction Temperature          | $T_{Jt}$                              | Overtemperature event not exceeding 10 seconds; lifetime duration not exceeding 10 hours; guaranteed by design characterization | 180                                           | °C    |

| Storage Temperature                     | T <sub>stg</sub>                      |                                                                                                                                 | -55 to 150                                    | °C    |

<sup>[1]</sup> With respect to GND, unless otherwise specified. Ratings apply when no other circuit operating constraints are present.

<sup>[2]</sup> The V<sub>IO</sub> absolute maximum voltage ratings can be exceeded if the terminal currents are externally limited to ± 10 mA. The VIO terminals conduct when the voltage exceeds a diode below ground or a diode above V<sub>IO</sub>.

[3] This terminal self-clamp sat a self-clamp level (SCL) of greater than 85 V. The resistor divider impedance should be chosen to ensure the terminal current does not

exceed the I<sub>SWIN</sub> absolute maximum rating under any condition.

<sup>[4]</sup> These terminals self-clamp at an SCL of less than –16 V. The terminal current during self-clamping must not exceed the I<sub>SREV</sub> or I<sub>SBRG</sub> absolute maximum ratings under any condition. The current level and duration may be limited by package power dissipation limits and transient junction temperature limits.

# Automotive Three-Phase and Battery Isolator MOSFET Driver

### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic                                                  | Characteristic Symbol Test Conditions [1] |                                        | Value | Units |

|-----------------------------------------------------------------|-------------------------------------------|----------------------------------------|-------|-------|

| Package Thermal Resistance,<br>ET Package (Junction to Ambient) | $R_{	heta JA}$                            | Four-layer PCB based on JEDEC standard | 32    | °C/W  |

|                                                                 | $R_{\theta JP}$                           |                                        | 2     | °C/W  |

| Package Thermal Resistance,                                     | $R_{\theta JA}$                           | Four-layer PCB based on JEDEC standard | 27    | °C/W  |

| EV Package (Junction to Pad)                                    | $R_{\theta JP}$                           |                                        | 2     | °C/W  |

<sup>[1]</sup> Additional thermal information available on the Allegro website.

### PINOUT DIAGRAMS AND TERMINAL LIST TABLE

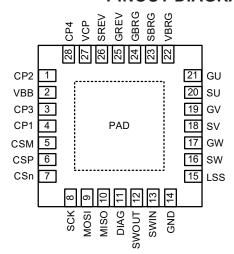

Figure 2: Package ET, 28-Pin,  $5 \times 5$  QFN Pinouts

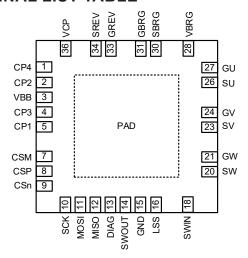

Figure 3: Package EV, 28-Pin, 6 × 6 QFN Pinouts

### **Terminal List Table**

| Name  | Number (ET) | Number (EV) | Description                                      |  |

|-------|-------------|-------------|--------------------------------------------------|--|

| CP1   | 4           | 5           | Charge-Pump Capacitor Connection                 |  |

| CP2   | 1           | 2           | Charge-Pump Capacitor Connection                 |  |

| CP3   | 3           | 4           | Charge-Pump Capacitor Connection                 |  |

| CP4   | 28          | 1           | Charge-Pump Capacitor Connection                 |  |

| CSM   | 5           | 7           | Current Sense, Negative Input                    |  |

| CSn   | 7           | 9           | Chip Select (Active Low)                         |  |

| CSP   | 6           | 8           | Current Sense, Positive Input                    |  |

| DIAG  | 11          | 13          | Programmable Diagnostic Bidirectional Pin        |  |

| GBRG  | 24          | 31          | Bridge-Supply Isolator MOSFET Gate Drive         |  |

| GND   | 14          | 15          | Ground                                           |  |

| GREV  | 25          | 33          | Reverse-Battery Isolator MOSFET Gate Drive       |  |

| GU    | 21          | 27          | U-Phase MOSFET Gate Drive                        |  |

| GV    | 19          | 24          | V-Phase MOSFET Gate Drive                        |  |

| GW    | 17          | 21          | W-Phase MOSFET Gate Drive                        |  |

| LSS   | 15          | 16          | Extra Pin                                        |  |

| MOSI  | 9           | 11          | Serial Data Input                                |  |

| MISO  | 10          | 12          | Serial Data Output                               |  |

| SBRG  | 23          | 30          | Bridge-Supply Isolator MOSFET Source Reference   |  |

| SCK   | 8           | 10          | Serial Clock Input                               |  |

| SREV  | 26          | 34          | Reverse-Battery Isolator MOSFET Source Reference |  |

| SU    | 20          | 26          | U-Phase MOSFET Source Reference                  |  |

| SV    | 18          | 23          | V-Phase MOSFET Source Reference                  |  |

| SW    | 16          | 20          | W-Phase MOSFET Source Reference                  |  |

| SWIN  | 13          | 18          | VBAT Divider Switch Input                        |  |

| SWOUT | 12          | 14          | VBAT Divider Switch Output                       |  |

| VBB   | 2           | 3           | Main Power Supply                                |  |

| VBRG  | 22          | 28          | Bridge High-Side MOSFET Drain Reference          |  |

| VCP   | 27          | 36          | Pumped Supply                                    |  |

| PAD   | _           | _           | Exposed Pad, Connect to GND                      |  |

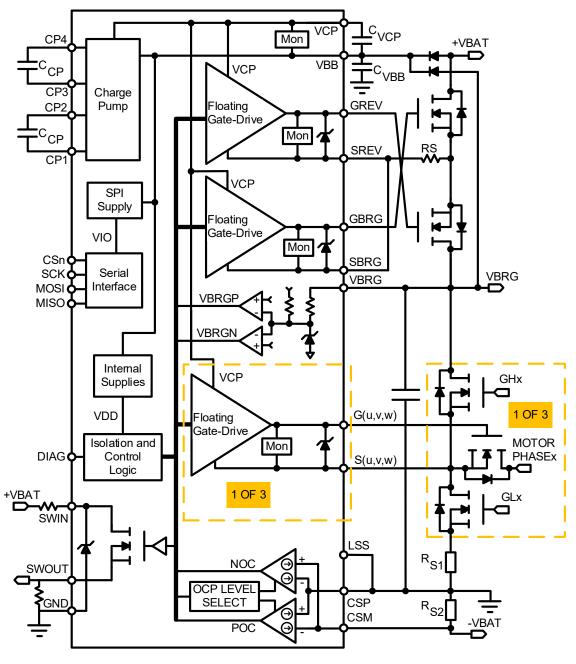

### **FUNCTIONAL BLOCK DIAGRAMS**

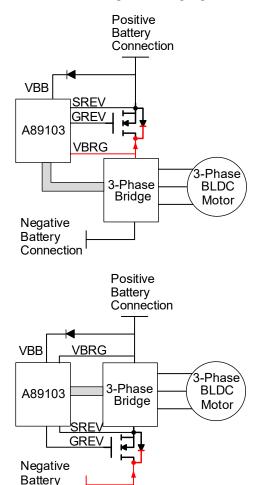

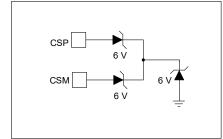

Figure 4: Battery-Disconnect Common-Source Configuration

Figure 5: Battery-Disconnect Common-Drain Configuration

### CHARACTERISTIC PERFORMANCE

**OPERATING CHARACTERISTICS:** Valid at  $T_J = -40$  to 150°C,  $V_{BB} = 4.5$  to 85 V, unless noted otherwise

| Characteristics Symbol                      |                    | bol Test Conditions                                                                |      | Тур. | Max. | Units |

|---------------------------------------------|--------------------|------------------------------------------------------------------------------------|------|------|------|-------|

| SUPPLY                                      |                    |                                                                                    |      | •    | •    |       |

|                                             |                    | Operating; outputs active                                                          | 4.5  | _    | 85   | V     |

| VBB Functional Operating Range [1]          | V <sub>BB</sub>    | Operating; outputs disabled                                                        | 4    | _    | 85   | V     |

|                                             |                    | No undefined states [1]                                                            | 0    | _    | 85   | V     |

|                                             | I <sub>BB</sub>    | Gate drive off, V <sub>BB</sub> = 12 V                                             | _    | _    | 20   | mA    |

| VBB Supply Current                          | I <sub>BBS</sub>   | Sleep mode, $V_{BB}$ = 12, 48 V, $T_{J}$ < 85°C, $CSn < V_{CSnL}$ (0.66 V)         | _    | _    | 3    | μA    |

| VOD Outsid Valle on a sittle or a state VDD | .,                 | V <sub>BB</sub> > 6 V, I <sub>VCP</sub> > -1 mA [2][3]                             | 9.5  | 10.5 | 11.5 | V     |

| /CP Output Voltage, with respect to VBB     | V <sub>CP</sub>    | $4.5 \text{ V} < \text{V}_{BB} \le 6 \text{ V}, I_{VCP} > -800 \mu\text{A} [2][3]$ | 8    | 8.5  | _    | V     |

| VDD Hardemielte se                          | V <sub>BBON</sub>  | V <sub>BB</sub> rising                                                             | 3.85 | 4    | 4.15 | V     |

| /BB Undervoltage                            | V <sub>BBOFF</sub> | V <sub>BB</sub> falling                                                            | 3.6  | 3.75 | 3.9  | V     |

| /DD Undervoltage <sup>[4]</sup>             | V <sub>DDON</sub>  | V <sub>DD</sub> rising                                                             | 2.7  | -    | 3    | V     |

|                                             | V <sub>DDOFF</sub> | V <sub>DD</sub> falling                                                            | 2.6  | _    | 2.8  | V     |

| VDD Undervoltage Hysteresis [4]             | V <sub>DDUVH</sub> |                                                                                    | 200  | 250  | 300  | mV    |

| Internal Legis I/O Regulator Voltage        | \/                 | A89103KETSR-3, V <sub>BB</sub> > 4 V                                               | 3.17 | 3.3  | 3.43 | V     |

| Internal Logic I/O Regulator Voltage        | V <sub>IO</sub>    | A89103KETSR-5, V <sub>BB</sub> > 5.5 V                                             | 4.8  | 5    | 5.2  | V     |

| DIAGNOSTICS AND PROTECTION                  |                    |                                                                                    | ,    |      |      |       |

| Internal Timing Clock Frequency             | f <sub>CLK</sub>   | Uncalibrated [5]                                                                   | 2.5  | 4    | 5.5  | MHz   |

| VGS Undervoltage Threshold Rising           | V <sub>GSUV</sub>  | SDCFG = 0                                                                          | 5.7  | 6.5  | 7.35 | V     |

| VGS Undervoltage Threshold<br>Hysteresis    | $V_{GShys}$        | SDCFG = 0                                                                          | _    | 200  | _    | mV    |

| VGS Undervoltage Filter Time                | t <sub>GSUV</sub>  |                                                                                    | 3.7  | -    | 18   | μs    |

| VCP Undervoltage Filter Time                | t <sub>CPUV</sub>  |                                                                                    | -    | 12.5 | _    | μs    |

| VCP Startup Blank Timer                     | t <sub>CPON</sub>  |                                                                                    | -    | 100  | -    | μs    |

| VCP Undervoltage Lockout                    | V <sub>CPON</sub>  | $V_{CP}$ with respect to $V_{BB}$ , $V_{CP}$ rising                                | 6.5  | 7    | 7.5  | V     |

| VOF Undervollage Lockout                    | V <sub>CPOFF</sub> | $V_{CP}$ with respect to $V_{BB}$ , $V_{CP}$ falling                               | 6.25 | 6.75 | 7.25 | V     |

| Current Comparator Input Open<br>Threshold  | V <sub>CD</sub>    |                                                                                    | 1.8  | 2.2  | 2.6  | V     |

| Current Sense Disconnect Filter Time        | t <sub>CD</sub>    |                                                                                    | 6    | 10   | 14   | μs    |

| Temperature Warning Threshold               | $T_JW$             | Temperature increasing                                                             | _    | 160  | -    | °C    |

| Temperature Warning Hysteresis              | T <sub>JWHys</sub> |                                                                                    | _    | 15   | _    | °C    |

$<sup>^{[1]}</sup>$  Function is correct, but parameters are not guaranteed below the general limits (4.5 to 85 V).

Continued on next page...

<sup>[2]</sup> For input and output current specifications, negative current is defined as coming out of the specified device terminal (termed "sourcing").

<sup>[3]</sup> Tested with all drivers in the on state. I<sub>VCP</sub> current specified is the minimum average V<sub>CP</sub> current available for driver on-/off-switching transitions, in addition to the static on-state current.

<sup>[4]</sup> Verified by design and characterization. Not production tested.

<sup>[5]</sup> The f<sub>CLK</sub> frequency can be calibrated through the SPI interface to improve accuracy.

# Automotive Three-Phase and Battery Isolator MOSFET Driver

## **OPERATING CHARACTERISTICS:** Valid at $T_J$ = -40 to 150°C, $V_{BB}$ = 4.5 to 85 V, unless noted otherwise

| Characteristics                         | Symbol                | Test Conditions                                                | Min.     | Тур. | Max.                  | Units |

|-----------------------------------------|-----------------------|----------------------------------------------------------------|----------|------|-----------------------|-------|

| GATE DRIVE                              |                       |                                                                | <u> </u> |      | •                     |       |

| Turn-On Rise Time                       | t <sub>r</sub>        | C <sub>LOAD</sub> = 2. 5 nF, 20% to 80%, Sx < V <sub>BB</sub>  | _        | 1.2  | 2                     | μs    |

| Turn-Off Fall Time                      | t <sub>f</sub>        | C <sub>LOAD</sub> = 2. 5 nF, 20% to 80%, Sx < V <sub>BB</sub>  | _        | 0.15 | 0.2                   | μs    |

| Propagation Delay—Turn On               | t <sub>PON</sub>      | C <sub>LOAD</sub> = 2.5 nF, internal enable command to Gx 20%  | -        | _    | 0.85                  | μs    |

| Propagation Delay—Turn Off              | t <sub>POFF</sub>     | C <sub>LOAD</sub> = 2.5 nF, internal disable command to Gx 80% | _        | _    | 0.4                   | μs    |

| Turn-On Pulse Current                   | $I_{GPx}$             |                                                                | 8.5      | 11.5 | 14.5                  | mA    |

| Turn-On Pulse Time                      | t <sub>GPx</sub>      |                                                                | 16       | 26   | 36                    | μs    |

| On Hold Current                         | I <sub>GHx</sub>      |                                                                | 200      | 300  | 400                   | μA    |

| Pull-Down On Resistance                 | R <sub>DS(on)DN</sub> | T <sub>J</sub> = 25°C, I <sub>Gx</sub> = 10 mA                 | _        | 5    | 6.5                   | Ω     |

| Pull-Down On Resistance                 |                       | T <sub>J</sub> = 150°C, I <sub>Gx</sub> = 10 mA                | _        | 10   | 13                    | Ω     |

| Gx Output High Voltage, with respect to | V <sub>GH</sub>       | V <sub>BB</sub> > 6 V                                          | 9        | 9.5  | 12                    | V     |

| $Sx$ , when $Sx \le V_{BB}$             |                       | 4.5 V < V <sub>BB</sub> ≤ 6 V                                  | 7.5      | 8    | _                     | V     |

| Gate Drive Static Load Resistor         | R <sub>GS</sub>       | Between Gx and Sx (using ±1% tolerance resistor)               | 100      | _    | -                     | kΩ    |

| Gx Output Voltage Low                   | $V_{GL}$              | –10 μA < I <sub>Gx</sub> < 10 μA                               | _        | _    | V <sub>Sx</sub> + 0.3 | V     |

| Gx Passive Pull-Down                    | R <sub>GPD</sub>      | $V_{Gx} - V_{Sx} < 0.3 \text{ V}$                              | _        | 950  | _                     | kΩ    |

| VBAT RESISTOR DIVIDER SWITCH            |                       |                                                                | '        |      |                       |       |

| Divider Switch On Resistance            | R <sub>SW</sub>       |                                                                | _        | _    | 100                   | Ω     |

| Divider Switch Off State Leakage        | I <sub>LSW</sub>      | V <sub>SWIN</sub> = 85 V, T <sub>J</sub> < 85°C                | _        | -    | 1                     | μA    |

| SWOUT Operational Range                 | V <sub>SWOR</sub>     |                                                                | 0        | -    | 5.5                   | V     |

Continued on next page...

# Automotive Three-Phase and Battery Isolator MOSFET Driver

**OPERATING CHARACTERISTICS:** Valid at  $T_J = -40$  to 150°C,  $V_{BB} = 4.5$  to 85 V, unless noted otherwise

| Characteristics                            | Symbol              | Test Conditions                                  |        | Limits |        |       |  |

|--------------------------------------------|---------------------|--------------------------------------------------|--------|--------|--------|-------|--|

| Characteristics                            | Symbol              | rest Conditions                                  | Min.   | Тур.   | Max.   | Units |  |

| OVERCURRENT PROTECTION                     |                     |                                                  | ,      |        | 1      |       |  |

|                                            |                     | OCP = 17                                         | 15     | 18     | 21     | mV    |  |

| CCD Community Throughold                   |                     | OCP = 63                                         | 59     | 64     | 69     | mV    |  |

| OCP Comparator Threshold                   | V <sub>OCP</sub>    | OCP = 99                                         | 93     | 100    | 107    | mV    |  |

|                                            |                     | OCP = 127                                        | 118.8  | 128    | 137.5  | mV    |  |

|                                            |                     | OCN = 17                                         | -21    | -18    | -15    | mV    |  |

| CON Comments Throughold                    |                     | OCN = 63                                         | -69    | -64    | -59    | mV    |  |

| OCN Comparator Threshold                   | V <sub>OCN</sub>    | OCN = 99                                         | -107   | -100   | -93    | mV    |  |

|                                            |                     | OCN = 127                                        | -137.5 | -128   | -118.8 | mV    |  |

| OCP/OCN Common Mode Range                  | V <sub>CM</sub>     |                                                  | -1.8   | _      | 2      | V     |  |

| CSP Input Bias Current [1]                 | I <sub>BIASP</sub>  | V <sub>CM</sub> in range                         | -160   | _      | _      | μΑ    |  |

| CSM Input Bias Current [1]                 | I <sub>BIASM</sub>  | V <sub>CM</sub> in range                         | -160   | _      | _      | μΑ    |  |

| CSP/CSM Input Bias Current<br>Matching [1] | I <sub>BIASCM</sub> | V <sub>CM</sub> in range, OCP = 127, OCN = 18    | -15    | _      | +15    | μΑ    |  |

| Comparator Propagation Delay Time          | t <sub>CPD</sub>    | V <sub>OD</sub> = 25 mV, OCP = 99                | _      | _      | 500    | ns    |  |

| VBRG PROTECTION                            |                     |                                                  | •      |        | `      |       |  |

| VBRG Comparator Positive-Voltage           | V <sub>VBRGP0</sub> | VCMFG = 0                                        | 1.2    | 1.5    | 1.8    | V     |  |

| Threshold [2]                              | V <sub>VBRGP1</sub> | VCMFG = 1                                        | 5.75   | 6      | 6.4    | V     |  |

| VBRG Comparator Negative-Voltage           | V <sub>VBRGN0</sub> | VCMFG = 0                                        | -1     | -0.75  | -0.5   | V     |  |

| Threshold [2]                              | V <sub>VBRGN1</sub> | VCMFG = 1                                        | -1     | -0.75  | -0.5   | V     |  |

| VBRG Comparator Filter Time                | t <sub>CPBR</sub>   |                                                  | _      | 1      | _      | μs    |  |

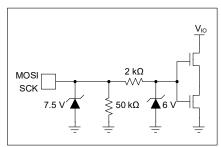

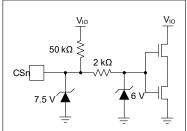

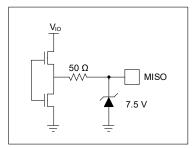

| IO LOGIC (CSn, MOSI, MISO, SCK, DIA        | AG)                 |                                                  | '      |        |        |       |  |

| Input Low Voltage                          | V <sub>IL</sub>     |                                                  | _      | _      | 0.8    | V     |  |

| Input High Voltage                         | V <sub>IH</sub>     | All logic inputs                                 | 2      | _      | _      | V     |  |

| Input Hysteresis                           | V <sub>IHYS</sub>   | All logic inputs                                 | 250    | 550    | _      | mV    |  |

| Input Negative Clamping Voltage            | V <sub>ILNC</sub>   | I = -10 mA                                       | _      | -100   | _      | mV    |  |

| MOSI and SCK Input Pull-Down               | R <sub>PD</sub>     |                                                  | 37     | 50     | 63     | kΩ    |  |

| La sia Occasionationa Thomashald           | .,                  | V <sub>IO</sub> rising                           | 6.1    | 6.3    | 6.5    | V     |  |

| Logic Overvoltage Threshold                | V <sub>LO</sub>     | Hysteresis                                       | _      | 0.5    | _      | V     |  |

| CSn Input Pull-Up to V <sub>IO</sub>       | R <sub>PU</sub>     | When device active                               | 37     | 50     | 63     | kΩ    |  |

| Outrout Law Valtage                        | V <sub>OL</sub>     | (MISO) I <sub>OL</sub> = 1 mA <sup>[1]</sup>     | -      | _      | 0.4    | V     |  |

| Output Low Voltage                         | V <sub>OL</sub>     | (DIAG) I <sub>OL</sub> = 2 mA <sup>[1]</sup>     | _      | _      | 0.4    | V     |  |

| Outroot High Walts are (MICO)              | V <sub>OH</sub>     | A89103-5, I <sub>OH</sub> = -1 mA <sup>[1]</sup> | 4      | _      | -      | V     |  |

| Output High Voltage (MISO)                 | V <sub>OH</sub>     | A89103-3, I <sub>OH</sub> = -1 mA <sup>[1]</sup> | 2.85   | _      | _      | V     |  |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (termed "sourcing"); positive current is defined as going into the node or pin (termed "sinking").

Continued on next page...

$<sup>\</sup>ensuremath{^{[2]}}$  Comparator voltage thresholds are measured with respect to ground.

**OPERATING CHARACTERISTICS:** Valid at  $T_J = -40$  to  $150^{\circ}$ C,  $V_{BB} = 4.5$  to 85 V, unless noted otherwise

| Characteristic                              | Symbol               | Test Conditions                   | Min. | Тур. | Max.  | Unit |  |  |

|---------------------------------------------|----------------------|-----------------------------------|------|------|-------|------|--|--|

| SERIAL INTERFACE TIMING                     |                      |                                   |      |      |       |      |  |  |

| SPI Clock Frequency                         | f <sub>SCK</sub>     | MISO pins, C <sub>L</sub> = 20 pF | 0.1  | _    | 10    | MHz  |  |  |

| SPI Frame Rate                              | t <sub>SPI</sub> [1] |                                   | 3.15 | _    | 181.8 | kHz  |  |  |

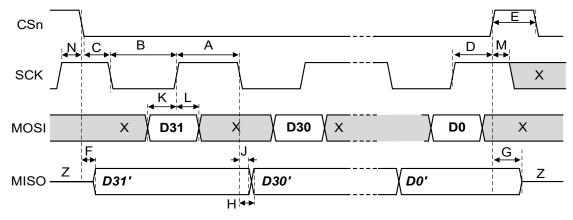

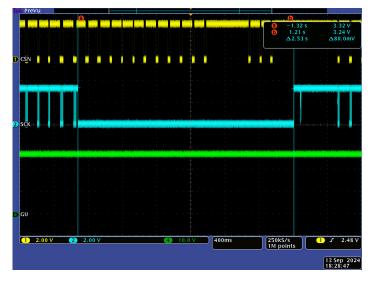

| Clock High Time                             | t <sub>SCK,H</sub>   | A in Figure 6                     | 50   | _    | _     | ns   |  |  |

| Clock Low Time                              | t <sub>SCK,L</sub>   | B in Figure 6                     | 50   | _    | _     | ns   |  |  |

| Chip Select Lead Time to SCK Low            | t <sub>CSLD</sub>    | C in Figure 6                     | 1    |      |       | μs   |  |  |

| Chip Select Lag Time                        | t <sub>CSn,LG</sub>  | D in Figure 6                     | 30   | _    | _     | ns   |  |  |

| Chip Select High Time                       | t <sub>CSn,H</sub>   | E in Figure 6                     | 1320 | _    | _     | ns   |  |  |

| Data Out (MISO) Enable Time [2]             | t <sub>MISO,EN</sub> | F in Figure 6                     | _    | _    | 50    | ns   |  |  |

| Data Out (MISO) Disable Time [2]            | t <sub>MISO,D</sub>  | G in Figure 6                     | _    | _    | 30    | ns   |  |  |

| Data Out (MISO) Valid Time from SCK         | t <sub>MISO,V</sub>  | H in Figure 6, A89103-5           | _    | _    | 50    | ns   |  |  |

| Falling [2]                                 |                      | H in Figure 6, A89103-3           | _    | _    | 75    | ns   |  |  |

| Data Out (MISO) Hold Time from SCK Falling  | t <sub>MISO,H</sub>  | J in Figure 6                     | 5    | _    | _     | ns   |  |  |

| Data In (MOSI) Set-Up Time to SCK<br>Rising | t <sub>MOSI,SU</sub> | K in Figure 6                     | 15   | _    | _     | ns   |  |  |

| Data In (MOSI) Hold Time from SCK<br>Rising | t <sub>MOSI,H</sub>  | L in Figure 6                     | 10   | _    | _     | ns   |  |  |

| SCK High from CSn Rising                    | t <sub>CSn,HCK</sub> | M in Figure 6                     | 30   | _    | _     | ns   |  |  |

| SCK High to CSn Rising                      | t <sub>CSn,LCK</sub> | N in Figure 6                     | 30   | _    | _     | ns   |  |  |

| Wake Up from Sleep                          | t <sub>EN</sub>      |                                   |      |      | 100   | μs   |  |  |

| CSn Wake-Up Threshold Rising                | V <sub>CSnH</sub>    |                                   | 0.8  | 1.33 | 1.68  | V    |  |  |

| CSn Wake-Up Threshold Falling               | V <sub>CSnL</sub>    |                                   | 0.66 | 1.12 | 1.43  | V    |  |  |

| CSn Wake-Up Threshold Hysteresis            | V <sub>CSn</sub>     |                                   | 128  | 215  | 300   | mV   |  |  |

$<sup>^{[1]} \</sup> t_{SPI} = t_{CSLD} + t_{CSn,Lg} + t_{CSn,H} + (32 \times t_{SCK,L}) + (31 \times t_{SCK,H}); \ t_{SPI(min)} \ is \ calculated \ using a \ value \ of \ t_{SCK,H} \ and \ t_{SCK,L} = 5 \ \mu s.$

<sup>[2]</sup> Verified by design and characterization. Not production tested.

Figure 6: Serial Interface Timing for Write and Read Cycle

X = not relevant; Z = high impedance; MISO activity assumes the chip ID from the previous frame was correct

# Automotive Three-Phase and Battery Isolator MOSFET Driver

### **FUNCTIONAL DESCRIPTION**

#### Overview

The A89103 is an N-channel power MOSFET driver capable of controlling five MOSFETs to provide motor-phase isolation and power-supply isolation in three-phase BLDC applications.

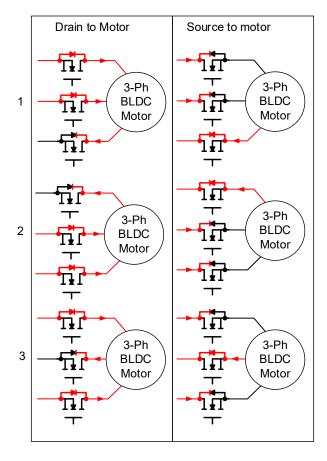

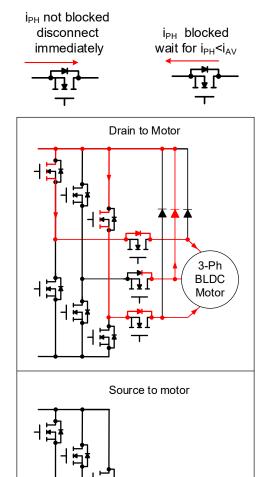

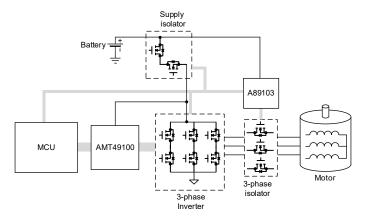

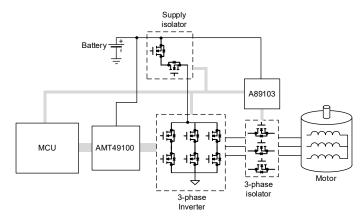

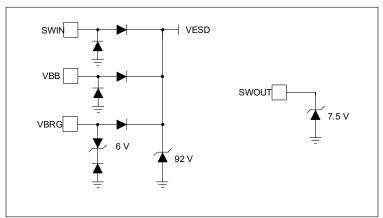

Three floating gate drivers are capable of driving N-channel power MOSFETs for motor-phase isolation. These MOSFETs are placed in series with each motor phase and can be used to restrict current flowing into the motor, as shown in Figure 3 and Figure 4. The three-phase disconnect MOSFET can be turned on (enabled) through SPI and kept in the on state, over the full supply range. When enabled by SPI, the three floating gate-drive outputs maintain the phase-isolator power MOSFETs in the on state, over the full supply voltage range. When a system failure occurs, the phase-isolator power MOSFETs can be disabled to allow the motor to spin freely. The A89103 is capable of providing all the data required to safely disconnect the phase MOSFETs via the serial interface.

The two floating gate drivers for battery isolation are capable of independently controlling a wide range of N-channel MOSFETs in source-to-source or drain-to-drain configuration for battery disconnect. These MOSFETs are connected in series and are placed between the battery supply (VBB) and the DC bridge (VBRG) as shown in Figure 3 and Figure 4. When these MOSFETS are turned off, they block the current flowing to and from VBRG, isolating the bridge or inverter from the supply. This protects the bridge in the case of a negative battery and protects the battery in the case of a malfunction, such as a short in the bridge. These MOSFETs can be used independently for auxiliary functions as switches when battery-disconnect features are not required.

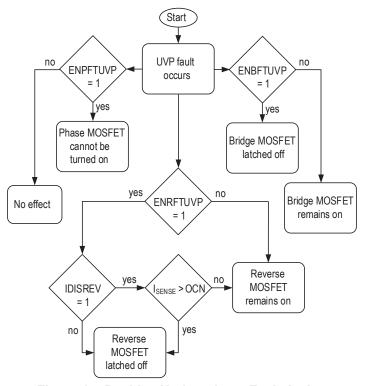

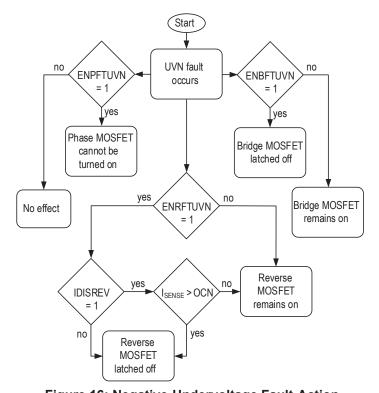

To facilitate battery isolation, two comparators are included to sense the bridge voltage, as well as two comparators used to sense positive and negative current for the negative battery connection. The two voltage comparators detect positive-undervoltage (UVP) and negative-undervoltage (UVN) nominal voltage conditions.

Detected UVP and UVN conditions are flagged in the SPI diagnostics and can be configured through the SPI to independently

trigger the automatic disabling of the supply- and phase-disconnect MOSFETS.

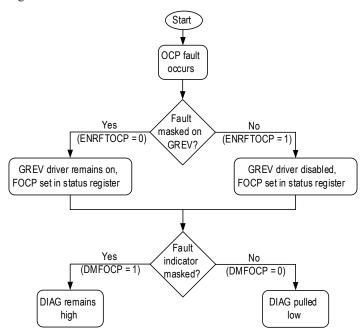

The current sense comparator detects positive-overcurrent (OCP) and negative-overcurrent (OCN) conditions, and the thresholds can be controlled through the SPI interface.

The positive- and negative-overcurrent fault conditions are flagged in the SPI diagnostics and can be configured through the SPI to independently trigger the automatic disabling of the supply- and phase-disconnect MOSFETS.

When power is not applied to VBB, the MOSFET connected to GREV is held off by passive and active circuit elements to prevent reverse battery current flow.

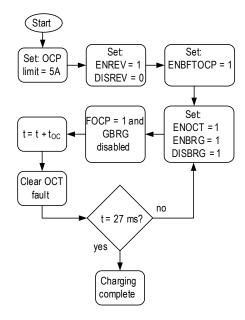

DC link capacitor charging current can be limited by using a positive-overcurrent fault circuit to prevent a high inrush current spike when connecting VBRG. The charging current pulse and charging rate can be programmed through the SPI interface as described in the DC Link Charging section.

An integrated charge-pump regulator provides the voltage that is a larger magnitude than the battery supply voltage necessary to continuously maintain the power MOSFETs in the on state. The charge pump maintains sufficient gate drive power (> 7.5 V) for battery voltages down to 4.5 V with 100 k $\Omega$  gate source resistors.

Undervoltage monitors check that the pumped supply voltage (VCP) and the gate drive outputs are high enough to ensure that the MOSFETs are maintained in a safe conducting state. Both the gate driver and charge pump voltages are monitored. If the pumped supply voltage or any gate drive output voltage is less than the undervoltage threshold for longer than a fault filter time, a fault becomes set and can be read-back from the SPI.

A SPI-compatible serial interface with watchdog function is incorporated to configure, control, and monitor device operation.

The A89103 allows for the battery voltage to be measured. Two pins are dedicated to sense the voltage at the supply while minimizing the current drawn from the supply for sensing.

# Automotive Three-Phase and Battery Isolator MOSFET Driver

### **Input and Output Terminal Functions**

#### **VBB**

Main power supply for internal regulators and charge pump. The main power supply should be connected to VBB through a reverse voltage protection circuit as shown in Figure 3 and Figure 4 and should be decoupled with ceramic capacitors connected close to the supply and ground terminals.

#### **VBRG**

Sense input to the top of the external MOSFET bridge. Allows detection of a negative- or positive-undervoltage event.

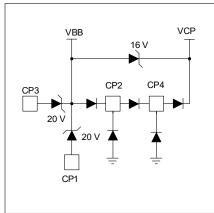

#### CP1, CP2, CP3, CP4

Pump capacitor connection for charge pump. Connect a ceramic capacitor with a recommended nominal value of 680 nF between CP1 and CP2 and 680 nF between CP3 and CP4. These capacitors should have a rated working voltage of at least 25 V and a tolerance of  $\pm 20\%$  or better.

#### **VCP**

Regulated voltage (10.5 V, typical), used to supply the five floating gate drivers and to provide current for the above supply charge pump. A sufficiently large storage capacitor must be connected to this terminal to provide the required transient charging current.

### **GND**

Analog, digital, and inverter ground. This ground does not connect to the supply ground. For more information, refer to the Layout Recommendations section.

#### GREV

Gate-drive output for an external N-channel MOSFET used for reverse supply protection.

#### **GBRG**

Gate-drive output for an external N-channel MOSFET used for bridge supply protection.

#### GU, GV, GW

Floating gate-drive outputs for external N-channel MOSFETs used for phase disconnection.

### **SREV**

Source connection for reverse-protection MOSFET that provides the negative-supply connections for the floating gate diver.

#### **SBRG**

Source connection for the bridge-protection MOSFET that provides the negative-supply connections for the floating gate diver.

### SU, SV, SW

Source connection for the phase-disconnection MOSFETs that provide the negative-supply connections for the floating gate divers.

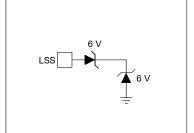

#### LSS

An extra pin for future development. This pin must be connected to ground.

#### CSP, CSM

Current sense monitor inputs.

#### SWIN, SWOUT

Input and output terminals for the VBAT resistor divider switch.

#### MOSI

Serial data logic input with pull-down. 32-bit serial word input, most-significant-bit (msb) first.

#### **MISO**

Serial data output. High impedance when CSn is high. Outputs the STATUS\_0 register of the previous frame when CSn is pulled low if a read was not requested. Otherwise, the data of the selected register is output.

### SCK

Serial clock logic input with pull-down. Data is latched-in from the serial digital interface (SDI) on the rising edge of SCK. There must be 32 rising edges per write, and SCK must be held high when CSn changes.

### CSN

Serial data strobe and serial access enable logic input with pullup. When CSn is high, any activity on SCK or MOSI is ignored and MISO is high impedance, allowing multiple SPI peripherals to have common MOSI, SCK, and MISO connections.

#### DIAG

Diagnostic output. Provides general fault flag output and can be programmed to output the internal clock frequency.

# Automotive Three-Phase and Battery Isolator MOSFET Driver

## **Power Supply**

A reverse-polarity-protected power-supply voltage (V<sub>BB</sub>) is required to provide power to the A89103. This power supply is connected to the VBB pin. The VBB pin is internally isolated from the VBRG pin and can be driven from separate power supplies. In this scenario, VBRG can be disconnected and the supply to the A89103 can be simultaneously maintained. A good practice is to introduce a path from VBRG to VBB through a diode, as shown in Figure 3 and Figure 4. This allows the device to be temporarily back-powered from the large DC link capacitors connected to VBRG when the VBB connection is lost. Decoupling of the supply is recommended using a ceramic capacitor connected close to the device supply (VBB) and ground (GND) terminals. This decoupling capacitor must be rated to remove the DC current ripple that occurs due to the switching of the charge pump. A 470 nF ceramic capacitor is recommended because it gives a good balance of speed and current decoupling. The method for calculating the size of the decoupling capacitor can be found in the Application Information section.

An energy-storage capacitor ( $C_{VBB}$ ) is also recommended, connected close to the device. This capacitor should be sized to provide sufficient supply during supply isolation or loss of power that it can hold-up to allow the system to complete the required isolation operation. Typically, a 220  $\mu F$  electrolytic capacitor is used. Sizing of this capacitor is described in the Application Information section.

The A89103 operates within specified parameters with  $V_{BB}$  from 4.5 V to 85 V and can maintain the external phase-isolator MOSFETs in the off condition down to 4 V. The A89103 operates without any undefined states down to 0 V to ensure deterministic operation during power-up and power-down events. As the supply voltage rises from 0 V, the gate-drive outputs are maintained in the off state until the charge pump voltage is sufficiently high to ensure conduction and enablement of the outputs via the SPI interface.

The A89103 input/output (I/O) voltage can be selected by ordering the A89103-5 part number for 5 V operation or the A89103-3 part number for 3.3 V operation. The device selected determines the digital high output voltage on the MISO terminals and the logic input high threshold.

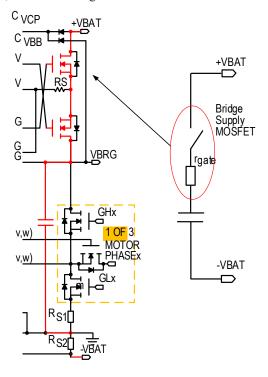

### DC LINK CHARGING

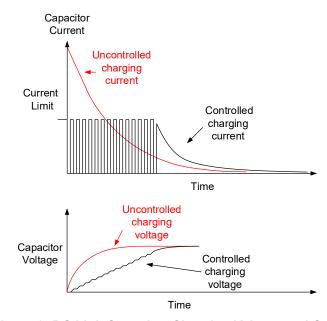

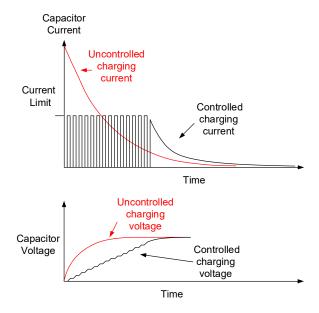

When charging the DC link capacitor, it is common to encounter a large inrush current drawn from the power supply at startup. A typical RC charging circuit with a switch, where the capacitor is the DC link capacitor and the resistor represents the sum of the turn-on gate resistance of the bridge supply and the reverse battery MOSFETs, is shown in Figure 7. The switch represents the bridge supply MOSFET When the switch is closed at time 0, the uncontrolled current flowing into the capacitor decays as shown in Figure 8. This large current is known as the inrush current and can damage components in the system.

C VCP

C VBB

V

V

RS

WOTOR

V,w)

RS1

RS2

VBAT

Figure 7: DC Link Capacitor Charging Circuit

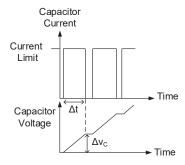

Overcurrent protection circuitry can be used to limit the charge current for the DC link capacitor. This is accomplished by providing a series of programmable magnitude current pulses through successive SPI commands. Current limits and overcurrent timeouts can be used to enable controlled-mode charging of the the DC link capacitor from the battery supply. When controlled, the DC link capacitor current decays as shown in Figure 8. The voltage drop across the DC link capacitor increases in small steps that correspond to the current pulses. To calculate the required magnitude of the pulses and to charge the DC link capacitance, refer to the Application Information section.

Figure 8: DC Link Capacitor Charging Voltage and Current Waveforms

# Automotive Three-Phase and Battery Isolator MOSFET Driver

## **Charge Pump Regulator**

The gate drivers are powered by a regulated charge pump, which provides the voltage above  $V_{BB}$  to ensure that the MOSFETs are fully enhanced with low on-resistance when the source of the MOSFET is at the same voltage as  $V_{BB}$ .

This regulator uses a charge-pump scheme with a switching frequency of 62.5 kHz and operates as a regulated doubler/tripler or a step-down regulator, depending on the input voltage on the VBB terminal. The charge pump voltage is regulated based on the difference between the VBB and VCP pins. The pumped voltage,  $V_{CP}$ , is available at the VCP terminal and is limited to  $12\ V$  maximum with respect to  $V_{BB}$ . This removes the need for external clamp diodes on the power MOSFETs to limit the gate-source voltage.

To provide the continuous low-level current required when gate-source resistors are connected to the external MOSFETs, a storage capacitor can be connected between the VCP and VBB terminals. Typically, a 1.5  $\mu F$  capacitor of tolerance 5% is used. Pump capacitors, typically 680 nF ceramic capacitors of tolerance 10%, must be connected between the CP1 and CP2 terminals and between the CP3 and CP4 terminals to provide sufficient charge transfer, especially at low supply voltage.

The charge pump can be disabled through the SPI interface by writing 0 to the ENVCP configuration bit. When the charge pump is disabled, the MOSFETs being driven do not remain on and the state is indicated by a  $V_{\rm GS}$  undervoltage fault. The charge pump is inactive during sleep mode.

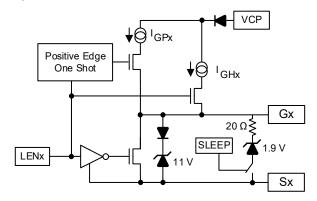

#### **Gate Drives**

The A89103 is designed to drive external, low on-state resistance, power N-channel MOSFETs when used in supply- and phase-isolation applications.

One of the five drivers in the A89103 is illustrated in Figure 9. The gate driver contains two current sources. The pulsed current source I<sub>GPx</sub> is required to provide the MOSFET charge current, and the hold current source I<sub>GHx</sub> is required to hold the MOS-FET in the on state. When LENx goes high, the upper half of the drivers are turned on (low sides are turned off) and a current (I<sub>GPx</sub> +  $I_{GHx}$  = 11.5 mA + 300  $\mu$ A, typically) is sourced to the gate for a duration of t<sub>GPx</sub>. Because drain-to-source voltage does not change during this period, in typical operations these parameters should be set to quickly charge the MOSFET input capacitance to the start of the Miller region. After this period, an on-hold current ( $I_{GHx} = 300 \mu A$ , typically) is sourced to the gates of the MOSFETs to keep them in the on state. The gate drive outputs accomplish turn-on of the MOSFETs in 8 µs (typically) and maintain the on state during voltage transients on the source of the MOSFETs. This is guaranteed as long as Sx is within its rated operating range.

When LENx goes low, the lower half of the drivers are turned on (high side is turned off) and current from the external MOSFET's gates to the respective Sx terminal sinks, which turns them off. To enable rapid, safe, on-demand opening of the circuit, turn-off is performed without current control. The gate drive outputs achieve turn-off of the MOSFETs in less than 300 ns (typically) and hold them in the off state during transients on the source.

An integrated hold-off circuit ensures that the gate source voltage of the MOSFET is held close to 0 V, even when power is disconnected. This can remove the need for additional gate-source resistors on the isolation MOSFETs. If gate-source resistors are mandatory for the application, the pump regulator can provide sufficient current to maintain the MOSFET in the on state using a gate-source resistor as low as  $100 \ k\Omega$  with 1% tolerance.

The floating gate-drive outputs for external N-channel MOSFETs are provided on pins GU, GV, GW, GREV, and GBRG. The reference points for the floating drives are the load phase connections SU, SV, and SW, and the sources of the reverse battery and bridge isolation MOSFETs, SREV and SBRG, respectively. The discharge current from the floating MOSFET gate capacitance flows through these connections.

For a detailed explanation of the circuit operation and a calculation of the external components, refer to the Application Information section.

When operating in the battery-disconnect common-drain configuration, the polarity of the reverse-battery gate driver is inverted, which drives the external discrete components. This ensures there is sufficient reverse-voltage protection in the common-drain configuration.

Each driver has independent internally latched control signals (LENx).

Figure 9: Operational Output Drive

#### **Driver Control via Serial Interface**

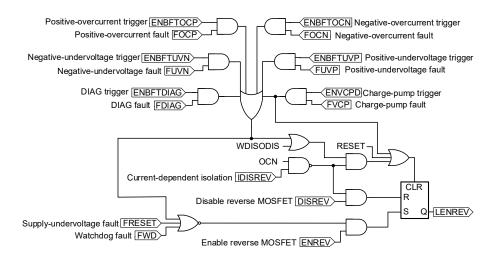

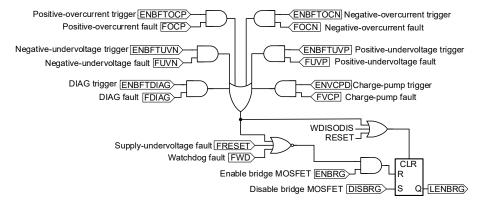

The gate drivers are controlled by setting control bits in the enable/disable 0 register. These bis are ENU, ENV, ENW, ENBRG, ENREV, DISU, DISV, DISW, DISBRG, and DISREV.

When these bits are set or cleared accordingly, they toggle the internal signal LENx that controls turn-on and turn-off of the gate driver, as shown in Figure 9.

At power-on, the gate-driver-latched enable signals, LENx, and the serial driver control registers, ENx, are reset, disabling all gate drives. The gate-driver LENx enable signals can be directly enabled and disabled by serial command but may also be controlled by internal A89103 disconnect and protection functions.

To avoid unintended serial driver reactivation, the serial interface uses independent enable and disable control bits for each MOSFET driver. The enable (ENx) disable (DISx) control bits—ENBRG, ENREV, ENU, ENV, ENW, DISBRG, DISREV, DISU, DISV, and DISW—can be written in a single SPI word to command the drivers to turn on and turn off. Truth tables that summarize the operation of the gate driver are shown in Table 1.

For a driver to be turned on, LENx must be enabled, ENx must be set to 1, and DISx must be set to 0. For a driver to be turned off, LENx must be disabled, ENx must be set to 0, and DISx must be set to 1. After the commanded state is latched, the ENx and DISx

bits are automatically reset to 0. Therefore, when these bits are read, they always appear to be zero.

Individual driver LENx control signals can be latched in the disable state by writing ENx = 0 and DISx = 1 in a single SPI command. After the commanded state is latched, the ENx and DISx bits are reset to 0.

If a serial command is received where ENx = DISx, the state of LENx for that driver retains the previous state. After the commanded state is latched, the ENx and DISx bits are reset to 0.

Each gate driver control is independent such that a single serial command can enable some drivers while disabling others.

During any operating condition, if any LENx signal is commanded through the SPI to be disabled, the respective driver switches off without delay. The only exception to this operation occurs when SPI control bit IDISREV is set to 1. In that case, if the LENREV signal is commanded through the SPI to be disabled, the transition to the disable state is blocked until the OCP sensed current is greater than the programmed OCN level (I > OCN). This feature ensures that, when the reverse MOSFET is turning off, the reverse current is small.

The status of the LENx control signals can be read from the SPI data registers STATx.

Phase U Phase V Phase W **ENU** DISU **LENU** GU **ENV** DISV **LENV** GV **ENW DISW** LENW GW No No No 0 0 Latched 0 0 Latched 0 0 Latched change change change 0 1 0 Lo 0 1 0 Lo 0 1 0 Lo 1 1 1 0 Hi 0 1 1 0 1 Hi Hi No No No 1 1 1 1 1 Latched Latched 1 Latched change change change

**Table 1: Gate Driver Control Truth Table**

| Bridge Driver |        |         | Reverse-Battery Driver |       |        |         |           |

|---------------|--------|---------|------------------------|-------|--------|---------|-----------|

| ENBRG         | DISBRG | LENBRG  | GBRG                   | ENREV | DISREV | LENREV  | GREV      |

| 0             | 0      | Latched | No change              | 0     | 0      | Latched | No change |

| 0             | 1      | 0       | Lo                     | 0     | 1      | 0       | Lo        |

| 1             | 0      | 1       | Hi                     | 1     | 0      | 1       | Hi        |

| 1             | 1      | Latched | No change              | 1     | 1      | Latched | No change |

# Automotive Three-Phase and Battery Isolator MOSFET Driver

## Common-Source/Drain Driver Configuration

There are two supported configurations when connecting the bridge and reverse supply MOSFETs. When the sources of both MOSFETs are connected together, this is known as a common-source configuration. Connecting the drain pins of both MOSFETs together creates the common-drain configuration. Because both configurations block the reverse and battery currents, the choice of common-drain or common-source configuration dependends on the system layout.

The common-source configuration is the default configuration of the A89103. When operating in the common-source configuration, the SPI control bit SDCFG should be set to 0. This configuration offers simpler design and requires fewer external components. When common source is selected, the GREV gate driver operates with the same polarity as the other gate drivers.

The common-drain configuration is selected by setting the SPI control bit SDCFG to 1. The GREV gate driver operates with an inverted polarity to drive the external discreet components in the common-drain configuration diagram shown in Figure 5. In this configuration, the gate driver status indication bit STATREV does not monitor the status of the GREV gate monitor. STATREV monitors the status of the reverse MOSFET. The  $V_{\rm GS}$  undervoltage fault is also masked in this configuration because the monitor cannot produce accurate results.

### VBAT Resistor Divider Switch

The VBAT resistor divider switch between the SWIN and SWOUT terminals can be used to reduce the battery current draw when sensing VBAT is not required.

The switch can be enabled or disabled through the SPI interface by writing 1 or 0, respectively, to the ENSW configuration bit.

The resistor divider switch is inactive during sleep mode. When the switch is disabled, if +VBAT is greater than 85 V and the top half of the resistor divider is chosen to limit the current into the terminal to less than 4 mA, the ESD structure on the SWIN terminal conducts to clamp the terminal voltage to an allowable level.

The SWOUT terminal operating range is limited to -0.3 to 5.5 V.

### **DIAGNOSTIC MONITORS**

Multiple diagnostic features provide three levels of fault monitoring. These diagnostics can be categorized into three levels of protection:

- Chip-level protection: Chip-wide parameters critical for correct operation of the A89103 are monitored. These include maximum internal logic supply voltage, minimum internal logic and terminal supply voltage, and serial interface transmission. These three monitors are necessary to ensure that the A89103 is able to respond as specified.

- Operational Monitors: Parameters related to the safe operation of the A89103 in a system are monitored. These include parameters associated with external active and passive components, power supplies, and interaction with external controllers.

- **System Level Protection:** These include the detection of power bridge and load fault conditions.

All diagnostics remain operational and cannot be masked when the A89103 is in its typical operating range. The diagnostics and their functions are summarized in Table 2.

Except for the temperature warning, power-on-reset, and internal logic overvoltage monitors, the fault is reported through two mechanisms—DIAG output terminal and the STATUS\_0 register accessed through the serial interface, which provide the status of the respective faults.

**Table 2: Diagnostic Functions**

| Name   | Diagnostic                                                                                            | Level   |

|--------|-------------------------------------------------------------------------------------------------------|---------|

| FDIAG  | Externally triggered fault on the DIAG terminal                                                       | System  |

| VIO    | Internal logic supply overvoltage                                                                     | Chip    |

| FRESET | Terminal supply undervoltage or internal logic supply undervoltage causing a power-on-reset operation | Chip    |

| FSPI   | Serial transmission error                                                                             | Chip    |

| TW     | High chip junction temperature warning                                                                | Monitor |

| FUVP   | VBRG supply positive undervoltage                                                                     | Monitor |

| FUVN   | VBRG supply negative undervoltage                                                                     | Monitor |

| FWD    | Watchdog timeout                                                                                      | Monitor |

| FOCP   | Positive overcurrent                                                                                  | Monitor |

| FOCN   | Negative overcurrent                                                                                  | Monitor |

| FVCP   | Charge pump undervoltage                                                                              | Monitor |

| FGBRG  | Bridge driver V <sub>GS</sub> undervoltage                                                            | Monitor |

| FGREV  | Reverse-battery driver V <sub>GS</sub> undervoltage                                                   | Monitor |

| FGW    | Phase-W driver V <sub>GS</sub> undervoltage                                                           | Monitor |

| FGV    | Phase-V driver V <sub>GS</sub> undervoltage                                                           | Monitor |

| FGU    | Phase-U driver V <sub>GS</sub> undervoltage                                                           | Monitor |

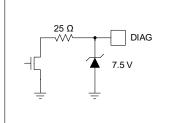

### **DIAG Diagnostic Output**

The DIAG terminal is a single diagnostic output signal that can be configured through the serial interface by writing to the DIAG [1:0] configuration bits. The list of configured functions is:

• **DIAG\_0—Digital Open-Drain Output:** Output pulled low in case of a fault.

At power-up, or after a power-on-reset event, the DIAG terminal outputs a general logic-level fault flag that is active-low if a fault is present. This fault flag remains low while the fault is present or if one of the latched faults has been detected. When all the faults are reset, the DIAG output returns to high.

• **DIAG\_1—Digital Open-Drain Output:** Clock signal derived from the internal chip clock.

The clock output option provides a logic level square wave proportional to the digital clock frequency FCLK to allow for accurate configuration of the system clock. This is useful for obtaining accurate timing measurements that depend on the system clock.

- **DIAG 2—Tristate:** Input only.

- **DIAG\_3—Tristate:** Input only.

When the DIAG terminal is not driven low by the A89103, the terminal can be externally pulled low. This is known as an external fault trigger. A DIAG fault appears and is represented by the setting of the FDIAG bit in the STATUS\_0 register.

When DIAG is externally pulled low, FDIAG is set in the STATUS\_0 register. The DIAG terminal is pulled low if the bit DMFDIAG is set to 0 and remains low until the fault is cleared in the status register by writing 1 to FDIAG. If DMFDIAG is set to 1, the DIAG terminal remains high.

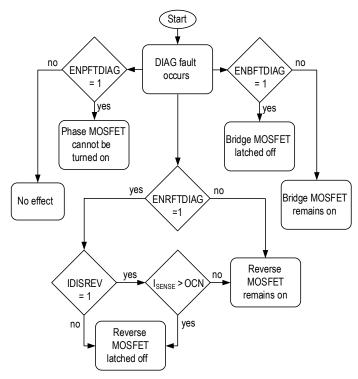

The A89103 can be configured to respond to a DIAG fault in three fault mechanisms:

- Bridge-supply MOSFET turns off.

- Reverse-battery MOSFET turns off.

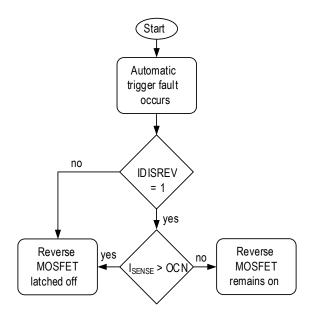

- Phase MOSFETs latch (cannot be turned on).

if the fault action bit ENBFTDIAG is set to 1, the bridge-supply MOSFET latches in the off state. If ENBFTDIAG is set to 0, the bridge-supply MOSFET remains in the on state.

If the fault action bit ENRFTDIAG is set to 1 and current-dependent isolation is disabled, the reverse supply MOSFET latches off. This is achieved by setting IDISREV to 0.

Current-dependent isolation can be activated by setting IDISREV to 1. For this scenario, the reverse-supply MOSFET latches in the off state only when the voltage of the negative-overcurrent monitor is greater than the negative-threshold overcurrent voltage. The DIAG fault can be cleared when the positive-overcurrent event has passed and 1 is written to FDIAG.

For both isolation cases described above, if the fault action bit ENRFTDIAG is set to 0, the reverse-supply MOSFET remains in the on state. Because the magnitude and direction of phase currents is unknown, a positive-undervoltage fault does not cause the phase MOSFETs to turn off. If the fault action bit ENPFTDIAG is set to 1 and the phase MOSFETs are already off, they remain latched in the off state until the DIAG fault is cleared.

If the fault action bit ENPFTDIAG is set to 0, the phase MOS-FETs do not latch to the off state.

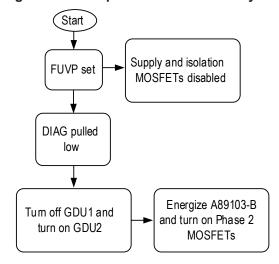

The fault action for a DIAG fault is summarized in the flowchart in Figure 10.

When the A89103 pulls the DIAG terminal low and the low state is then deserted, the DIAG trigger function is blanked for 10  $\mu s$  to prevent false tripping.

Figure 10: DIAG Fault-Action Scenarios

### **Diagnostic Registers**

The serial interface allows detailed diagnostic data to be read from the diagnostic registers on the MISO output terminal at any time.

A system status register, STATUS\_0, provides a summary of all faults in a single read transaction. The status register is always output on MISO when any register is written. In all cases, the fault bits in the status register are latched and are only cleared by writing 1 to the corresponding bit.

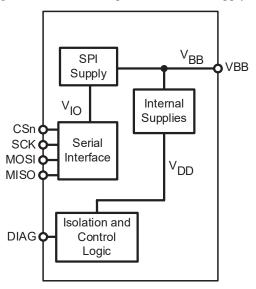

## **Chip Fault State: Internal Logic Overvoltage**

The A89103 has two independent integrated logic regulators, as shown in Figure 11. The SPI supply regulator provides power to the serial interface and the internal supply regulator provides power to the isolation and control logic. This supply architecture ensures that external events, other than loss of supply, do not prevent the A89103 from operating correctly. For example, during transient load event, if the main supply voltage drops below the  $V_{BB}$  undervoltage falling threshold ( $V_{BBOFF}$ ), the internal logic supply regulator continues to operate with a low supply voltage.

Figure 11: A89103 Internal Regulators

The A89103 monitors the internal supply voltage to detect when it exceeds the logic overvoltage threshold ( $V_{LO}$ ). In the event of a logic overvoltage, the DIAG terminal is pulled low and remains low unless the regulated voltage supplying the serial interface,  $V_{IO}$ , recovers to the typical operating voltage. There is no SPI fault for  $V_{LO}$ , and the fault action on DIAG cannot be masked.

# Chip Fault State: Internal Logic and Supply Undervoltage

When supply voltage is extremely, or during power-up or power-down, two undervoltage detectors ensure that the A89103 operates correctly. Neither the  $V_{DD}$  logic supply undervoltage lockout nor the VBB terminal supply undervoltage lockout can be masked: Both are essential to guarantee correct operation over the full supply range.

When power is first applied to the A89103, the internal logic is prevented from operating, and all gate drive outputs are held in the off state until both the  $V_{DD}$  logic supply exceeds its undervoltage rising threshold ( $V_{DDON}$ ) and the VBB terminal exceeds its undervoltage rising threshold ( $V_{BBON}$ ). At this point, all serial control registers are reset to their power-on state and all fault states are reset. The FFRESET bit in the STATUS\_0 register becomes set to one to indicate that a power-on-reset operation has occurred. The A89103 then goes into its fully operational state and begins to operate as specified.

Once the A89103 is operational, the  $V_{DD}$  logic supply and the VBB terminal supply continue to be monitored. During operation, if  $V_{DD}$  drops below the logic supply undervoltage lockout falling (turn-off) threshold, or if  $V_{DDOFF}$  or  $V_{BB}$  drops below the terminal-supply undervoltage-lockout falling (turn-off) threshold, the logical function of the A89103 cannot be guaranteed and the outputs are immediately disabled. If there is sufficient voltage present to drive the pull-down device, the DIAG terminal is pulled low. The A89103 enters a power-down state and all internal activity, other than the  $V_{DD}$  and  $V_{BB}$  voltage monitors, are suspended. If the  $V_{BB}$  or  $V_{DD}$  undervoltage is a transient event, then the A89103 follows the power-up sequence above as the voltage rises.

## **Chip Fault State: Serial Error**

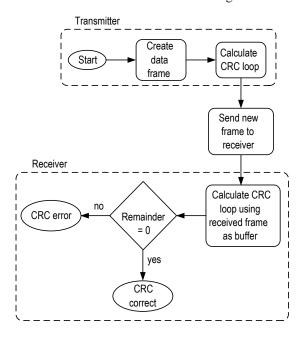

The data transfer into the A89103 through the serial interface is monitored for two fault conditions:

- Transfer length: A transfer length fault is detected if there are more than 32 rising edges on SCK, or if CSn goes high and there have been fewer than 32 rising edges on SCK.

- Cyclic redundancy check (CRC) checksum: A CRC checksum error occurs when the calculated CRC does not match the received CRC. For a more-detailed explanation of the CRC calculation and operation, refer to the Application Information section.

In both cases, the write process is cancelled without writing data to the register. In addition, the FSPI bit becomes set to indicate a data transfer error. Due to the nature of out-of-frame communication, the contents of the register during the last valid serial transaction are still able to be read.

# Automotive Three-Phase and Battery Isolator MOSFET Driver

### **Operational Monitors**

Voltages related to the driving of external power MOSFETs are monitored—specifically, the  $V_{CP}$  and  $V_{GS}$  of each gate drive output as well as the logic voltages. The inverter bridge voltage,  $V_{BRG}$ , is monitored for positive- and negative-undervoltage events. In addition, a watchdog timer can be applied to the serial input to verify continued operation of the SPI interface.

## **Gate-Drive Output Monitor**

For each gate driver, the gate-to-source voltage between the Gx terminal and the Sx terminal is monitored during the on state for the presence of an undervoltage condition. This monitor ensures that the gate-drive output is operating correctly and that the drive voltage is sufficient to fully enhance the power MOSFET to which it is connected. The undervoltage threshold,  $V_{\rm GSUV}$ , has a typical value of 6.5 V.

If  $V_{GS}$  on any active gate-drive output is lower than the gate-drive undervoltage warning threshold,  $V_{GSUV}$ , the fault condition becomes latched in the appropriate gate-drive undervoltage status bit—FGREV, FGBRG, FGU, FGV, or FGW. All gate-drive outputs remain in the on state. The gate-drive undervoltage bits FGREV, FGBRG, FGU, FGV, and FGW can only be reset by writing 1 to the appropriate status bit or via a power-on-reset operation.

The output of each  $V_{GS}$  undervoltage comparator is filtered by a  $V_{GS}$  fault-qualifier circuit. This circuit uses a timer to verify that the output from the comparator has indicated a valid  $V_{GS}$  fault. The duration of the  $V_{GS}$  qualifying timer,  $t_{GSUV}$ , is specified in the Characteristic Performance section.

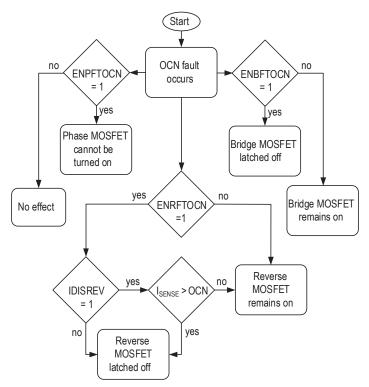

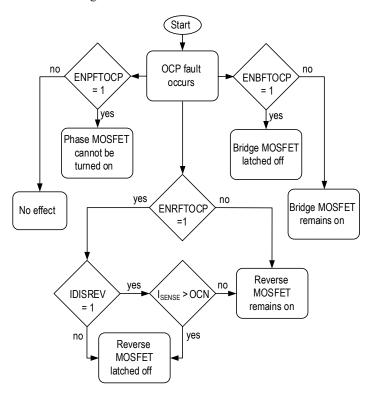

### **Charge Pump Output Monitor**