## High-Precision, Programmable Linear Hall-Effect Sensor IC

with VREF and High-Bandwidth (400 kHz) Analog Output for Core-Based Current Sensing

#### **FEATURES AND BENEFITS**

- Industry-leading noise performance

- User-programmable bandwidth (100 to 400 kHz) for easy tradeoff between speed and noise

- Very fast response time (<1.25 μs typ.)

- · Wide sensing range

- Factory-programmed sensitivity and offset over temperature

- User-programmable sensitivity and offset

- User-programmable sensitivity over temperature for ferromagnetic core drift compensation

- User-programmable, bidirectional reference pin (VREF) for full control over offset levels

- Non-ratiometric output for immunity to noisy supplies

- Undervoltage and overvoltage detection

- High output drive current (15 mA)

- Low power mode for reduced I<sub>CC</sub>

- VDD pin survives exposure up to 15 V

- Monolithic Hall IC for high reliability

## PACKAGE: 4-pin SIP (suffix OK)

#### TYPICAL APPLICATIONS

- · Current sensing modules

- Solar (MPPT, combiner box)

- Motor control

- Uninterruptible power supplies (UPS)

- · Smart fuse

- Overcurrent detection

- · Power supplies

#### **DESCRIPTION**

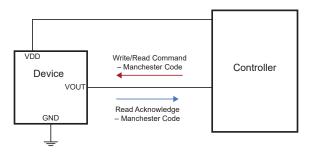

The Allegro ACS37600 is a linear sensor IC designed to be used in conjunction with a ferromagnetic core to provide a highly accurate current sensor suitable for industrial, commercial, and communications applications.

The device consists of a precise, low-offset, chopper-stabilized Hall-effect front end. Magnetic flux orthogonal to the IC package surface is sensed by the integrated Hall and converted into a proportional voltage. A very wide sensitivity range allows current sensor module makers to use this IC for a <20 A or a >1000 A module.

A selectable bandwidth from 100 kHz to >400 kHz makes the device ideal for fast switching applications and applications where low noise is required.

A user-programmable, bidirectional reference voltage pin (VREF) enables constant monitoring of the zero-current voltage and easy interfacing with 3.3 V and 5 V ADCs.

The sensitivity and offset drift over temperature are factoryprogrammed at Allegro to provide a highly accurate solution across the full temperature range.

The ACS37600 is customer programmable. The absolute value of sensitivity and offset can be programmed after manufacturing. Additionally, customers can program the sensitivity over temperature to compensate for ferromagnetic core drifts, enabling industry-leading current sensor accuracy.

A nonratiometric output immune to supply noise, the ability to survive up to 15 V on the supply pin, and a stellar ESD performance make the ACS37600 ideal for applications where reliability and robustness are required.

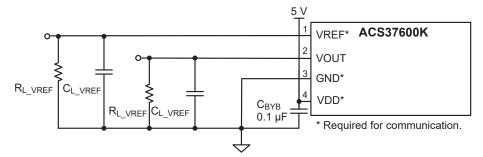

Figure 1: Typical Application Circuit for ACS37600K

## High-Precision, Programmable Linear Hall-Effect Sensor IC

with VREF and High-Bandwidth (400 kHz) Analog Output for Core-Based Current Sensing

#### **SELECTION GUIDE**

| Part Number           | Factory-Trimmed    |               | ogrammed<br>Range (G) | Programmable<br>Sens Range | T <sub>A</sub><br>(°C) | Packing          |

|-----------------------|--------------------|---------------|-----------------------|----------------------------|------------------------|------------------|

|                       | Sensitivity (mV/G) | Bidirectional | Unidirectional [1]    | (mV/G) <sup>[2]</sup>      | ( 0)                   |                  |

| ACS37600KOKA-003B5-C  | 3                  | ±667          | 0 to 1333             | 2.4 to 3.6                 | -40 to 125             |                  |

| ACS37600KOKA-006B5-C  | 6                  | ±333          | 0 to 667              | 4.8 to 7.2                 |                        | 4000 pieces      |

| ACS37600KOKA-003B5-CP | -3                 | ±667          | 0 to -1333            | −3.6 to −2.4               |                        | per 13-inch reel |

| ACS37600KOKA-006B5-CP | -6                 | ±333          | 0 to -667             | -7.2 to -4.8               |                        |                  |

<sup>[1]</sup> This range applies if the VREF pin is overdriven to 0.5 V.

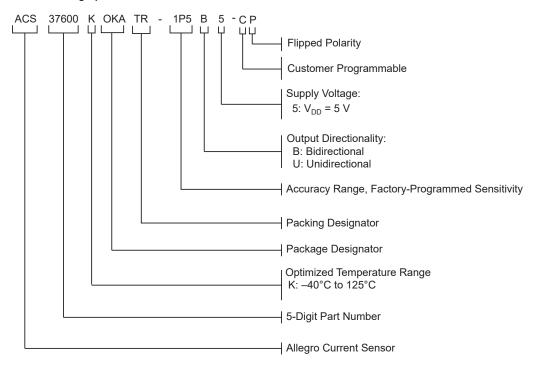

#### **Part Numbering Specification**

<sup>[2]</sup> Characteristics are guaranteed within the sense programmable range of the corresponding part number.

# High-Precision, Programmable Linear Hall-Effect Sensor IC with VREF and High-Bandwidth (400 kHz) Analog Output for Core-Based Current Sensing

## **Table of Contents**

| Features and Benefits                                             |    |

|-------------------------------------------------------------------|----|

| Description                                                       |    |

| Packages                                                          |    |

| Typical Applications                                              |    |

| Selection Guide                                                   |    |

| Absolute Maximum Ratings                                          |    |

| Operating Parameters                                              |    |

| Pinout Diagram and Terminal List                                  |    |

| Functional Block Diagram                                          |    |

| Electrical Characteristics                                        |    |

| Performance Characteristics: Factory                              | 10 |

| Functional Description                                            | 11 |

| Power-On Reset Operation                                          |    |

| Power-On                                                          | 11 |

| Power-Off                                                         | 11 |

| Power-On Timing                                                   |    |

| Power-On Reset (POR)                                              | 11 |

| Power-On Reset Release Time (t <sub>PORR</sub> )                  | 11 |

| Power-On Reset Output Delay (t <sub>POR-OUT</sub> )               | 12 |

| Power-On Reset Reference Delay(t <sub>POR-REF</sub> )             | 12 |

| Power-On Delay (t <sub>POD</sub> )                                | 12 |

| Overvoltage and Undervoltage Detection                            | 13 |

| Undervoltage Detection Voltage Thresholds $(V_{UVD(H/L)})$        | 13 |

| Overvoltage Detection Voltage Thresholds (V <sub>OVD(H/L)</sub> ) | 13 |

| Overvoltage/Undervoltage Detection Hysteresis                     |    |

| Overvoltage and Undervoltage Enable and Disable Time.             | 13 |

| Definitions of Operating and Performance Characteristics          | 15 |

| Quiescent Voltage Output (V <sub>OUT(Q)</sub> )                   | 15 |

| QVO Temperature Drift (V <sub>QVO(Q)_TC</sub> )                   |    |

| Reference Voltage (V <sub>REF</sub> )                             | 15 |

| Reference Voltage Temperature Drift (V <sub>REF_TC</sub> )        | 15 |

| Reference Voltage Programming Step Size (STEP <sub>VREF</sub> )   | 15 |

| Offset Voltage (V <sub>OFF</sub> )                                | 15 |

| Offset Error Temperature Drift (V <sub>OFF_TC</sub> )                          | . 15 |

|--------------------------------------------------------------------------------|------|

| Offset Voltage Programming Step Size (STEP <sub>VOFF</sub> )                   | 15   |

| Output Saturation Voltage (V <sub>SAT(HIGH/LOW)</sub> )                        |      |

| Sensitivity (Sens)                                                             | . 16 |

| Sensitivity Programming Range (Sens <sub>PR</sub> )                            | 16   |

| Sensitivity Temperature Drift (E <sub>sens</sub> )                             | 16   |

| Dynamic Response Parameters                                                    |      |

| Propagation Delay (t <sub>REACTION</sub> )                                     | . 17 |

| Rise Time (t <sub>RISE</sub> )                                                 | . 17 |

| Response Time (t <sub>RESPONSE</sub> )                                         | . 17 |

| Overshoot (V <sub>OS</sub> )                                                   | . 17 |

| Settling Time (t <sub>Settle</sub> )                                           | . 17 |

| Temperature Compensation                                                       | 18   |

| Temperature Compensation Update Rate (t <sub>UR</sub> )                        |      |

| Gain Temperature Coefficient (SENS <sub>SLOPE</sub> )                          | . 18 |

| Gain Temperature Coefficient Step Size (STEP <sub>SENS SLOPE</sub> )           | 18   |

| Package Stress Compensation                                                    |      |

| Application and Theory                                                         | . 19 |

| Parameter Trim Algorithm                                                       |      |

| OCF Pulled Up to Different Power Domain                                        |      |

| Overdriving V <sub>REF</sub> : Dynamic Output and Accelerated t <sub>POD</sub> | .20  |

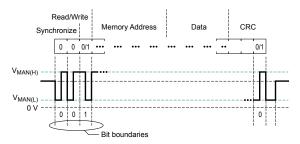

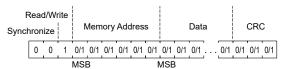

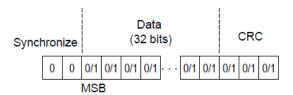

| Manchester Communication and Device Features                                   | 20   |

| Programming Parameters                                                         | 21   |

| Fine Tuning Sensitivity, Reference and Quiescent Voltage                       | 21   |

| Additional Core / Temperature Compensation                                     |      |

| Registers Useful for Prototyping                                               |      |

| Device Programming                                                             | 24   |

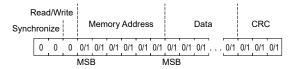

| Serial Communication                                                           |      |

| Customer Memory Map                                                            |      |

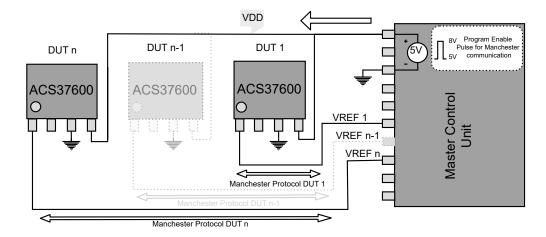

| Multi-Device Communication Setup                                               |      |

| Error Checking                                                                 |      |

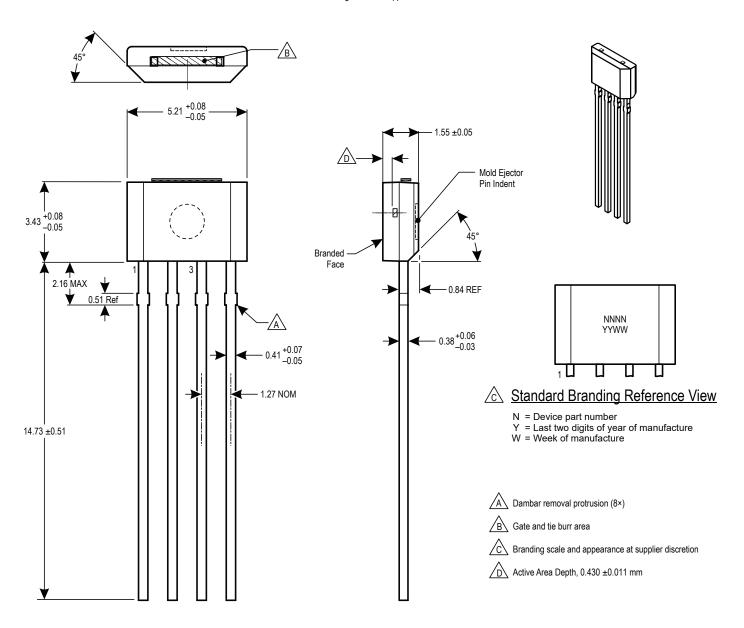

| Package Outline Drawing                                                        | 28   |

|                                                                                |      |

with VREF and High-Bandwidth (400 kHz) Analog Output for Core-Based Current Sensing

## **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                | Symbol           | Notes                                                                               | Min.            | Max.                     | Unit |

|-------------------------------|------------------|-------------------------------------------------------------------------------------|-----------------|--------------------------|------|

| Supply Voltage                | $V_{DD}$         |                                                                                     | -0.5            | 15                       | V    |

| Output Voltage                | V <sub>O</sub>   | Applies to V <sub>OUT</sub>                                                         | -0.5            | $(V_{DD} + 0.5) \le 15$  | V    |

| Reference Voltage             | V <sub>R</sub>   | Applies to V <sub>REF</sub>                                                         | -0.5            | $(V_{DD} + 0.5) \le 6.5$ | V    |

| Operating Ambient Temperature | T <sub>A</sub>   | Range K                                                                             | -40             | 125                      | °C   |

| Storage Temperature           | T <sub>STG</sub> |                                                                                     | <del>-</del> 65 | 165                      | °C   |

| Maximum Field Range           | В                | The output may still respond but linearity degrades significantly within this range | -3000           | 3000                     | G    |

#### **OPERATING PARAMETERS**

| Characteristics              | Symbol          | Test Conditions                                                         | Min. | Тур. | Max. | Unit |

|------------------------------|-----------------|-------------------------------------------------------------------------|------|------|------|------|

| Optimal Absolute Field Range | B <sub>og</sub> | Performance specifications are guaranteed at or within this limit of  B | 0    | _    | 1650 | G    |

| Nominal Absolute Field Range | B <sub>NG</sub> | Linearity degrades within this  B  range                                | 1650 | _    | 2000 | G    |

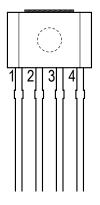

#### **Terminal List Table**

| Number | Name                                | Function                                           |  |  |

|--------|-------------------------------------|----------------------------------------------------|--|--|

| 1      | 1 VREF Zero gauss reference voltage |                                                    |  |  |

| 2      | VOUT                                | Output signal                                      |  |  |

| 3      | GND                                 | Device ground terminal                             |  |  |

| 4      | VDD                                 | Device power supply terminal; used for programming |  |  |

Figure 2: OK Package Pinout Diagram

(Ejector pin mark on opposite side)

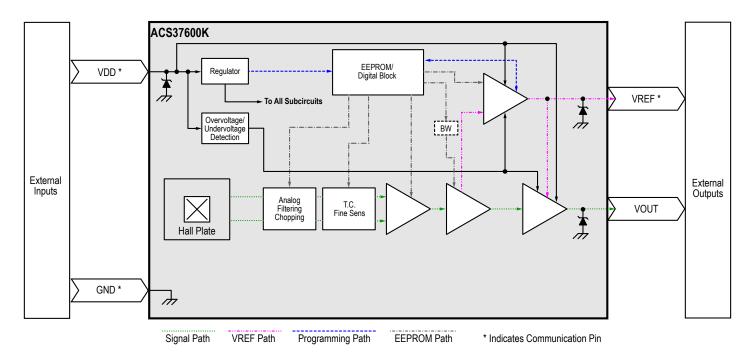

## **FUNCTIONAL BLOCK DIAGRAM**

**ELECTRICAL CHARACTERISTICS:** Valid through the full operating temperature range,  $T_A$ ,  $C_{BYPASS} = 0.1 \, \mu F$ ,  $V_{DD} = 5 \, V$ ,  $ECO\_MODE = 0$ , unless otherwise specified

| Characteristics                             | Symbol               | Test Conditions                                                                                                                                           | Min. | Тур. | Max. | Unit |

|---------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply Voltage                              | $V_{DD}$             |                                                                                                                                                           | 4.5  | 5    | 5.5  | V    |

| Cumply Current                              |                      | V <sub>DD</sub> = 4.5 to 5.5 V, output open, factory default                                                                                              | -    | 16   | 23   | mA   |

| Supply Current                              | I <sub>cc</sub>      | V <sub>DD</sub> = 4.5 to 5.5 V, output open, ECO_MODE = 1                                                                                                 | -    | 14   | 23   | mA   |

| VOUT Resistive Load                         | R <sub>L_VOUT</sub>  | VOUT to GND, VOUT to VDD                                                                                                                                  | -    | _    | 4.7  | kΩ   |

| VOUT Capacitive Load                        | C <sub>L_VOUT</sub>  | VOUT to GND                                                                                                                                               | 2    | _    | _    | nF   |

| VREF Resistive Load                         | R <sub>L_VREF</sub>  | VREF to GND                                                                                                                                               | 200  | _    | _    | kΩ   |

| VREF Capacitive Load                        | C                    | VREF in input/output mode, VREF to GND                                                                                                                    | 0.5  | _    | 47   | nF   |

| VINER Capacitive Load                       | C <sub>L_VREF</sub>  | VREF in output mode only, VREF to GND                                                                                                                     | 0.5  | _    | 4.7  | nF   |

| Supply Bypass Capacitor                     | C <sub>BYPASS</sub>  | VDD to GND                                                                                                                                                | _    | 0.1  | _    | μF   |

| Power-On Reset Release<br>Voltage           | V <sub>POR</sub>     | V <sub>DD</sub> rising 1 V/ms                                                                                                                             | 3.6  | 3.8  | 3.9  | V    |

| Power-On Reset Hysteresis                   | V <sub>POR_HYS</sub> |                                                                                                                                                           | 250  | 400  | 560  | mV   |

| Power-On Reset Release Time [1]             | t <sub>PORR</sub>    |                                                                                                                                                           | _    | 95   | _    | μs   |

| Power-On Reset Output Delay [1]             | t <sub>POR_OUT</sub> | C <sub>L_VREF</sub> = 4.7 nF, no R <sub>L_VOUT</sub>                                                                                                      | _    | 8    | _    | μs   |

| Power-On Reset Reference<br>Delay [1]       | t <sub>POR_REF</sub> | $V_{REF}$ in output/input or output only mode; no $R_{L\_VREF}$ , $C_{L\_VREF}$ = 4.7 nF                                                                  | _    | 17   | _    | μs   |

| Power-On Delay [1]                          | +                    | $T_A$ = 25°C, $V_{REF}$ in input only mode, driven to 2.5 V; $C_{L\_VOUT}$ = 4.7 nF, no $R_{L\_VOUT}$                                                     | _    | 103  | _    | μs   |

| Tower-on belay to                           | t <sub>PO</sub>      | $T_A$ = 25°C, $V_{REF}$ in input/output or output only mode, driving to 2.5 V; $C_{L\_VOUT}$ and $C_{L\_VEF}$ = 4.7 nF, no $R_{L\_VOUT}$ or $R_{L\_VREF}$ | _    | 112  | _    | μs   |

| Temperature Compensation Update Rate        | t <sub>UR</sub>      |                                                                                                                                                           | _    | 8    | _    | ms   |

| Undervoltage Detection<br>Threshold         | V <sub>UVD</sub>     | T <sub>A</sub> = 25°C, V <sub>DD</sub> falling 1 V/ms                                                                                                     | 4    | _    | 4.4  | V    |

| Undervoltage Detection<br>Hysteresis        | V <sub>UVD_HYS</sub> |                                                                                                                                                           | _    | 0.4  | _    | V    |

| Undervoltage Detection Time [1] [2]         | t <sub>UVD</sub>     | $V_{DD} < V_{UVD}$                                                                                                                                        | 35   | 64   | 90   | μs   |

| Undervoltage Detection Release Time [1] [2] | t <sub>UVD_R</sub>   | $V_{DD} > (V_{UVD} + V_{UVD\_HYS})$                                                                                                                       | _    | 8    | _    | μs   |

| Overvoltage Detection<br>Threshold          | V <sub>OVD</sub>     | T <sub>A</sub> = 25°C, VDD rising 1 V/ms                                                                                                                  | 7.2  | 7.6  | 8    | V    |

| Overvoltage Detection<br>Hysteresis         | V <sub>OVD_HYS</sub> | T <sub>A</sub> = 25°C                                                                                                                                     | -    | 1    | _    | V    |

| Overvoltage Detection Time [1]              | t <sub>OVD</sub>     | $V_{DD} > V_{OVD}$                                                                                                                                        | 35   | 64   | 90   | μs   |

| Overvoltage Detection Release Time [1]      | t <sub>OVD_R</sub>   | $V_{DD} < (V_{OVD} - V_{OVD\_HYS})$                                                                                                                       | _    | 7    | _    | μs   |

$<sup>\</sup>ensuremath{^{[1]}}$  Timing parameters are based off design and characterization data.

<sup>[2]</sup> Power-on release threshold is either  $V_{POR}$  if UVD\_DIS = 1 or  $V_{UVD}$  if UVD\_DIS = 0. Factory default setting is UVD\_DIS = 0.

## **ELECTRICAL CHARACTERISTICS (continued):** Valid through the full operating temperature range, $T_A$ , $C_{BYPASS} = 0.1 \mu F$ , $V_{DD} = 5 \text{ V}$ , ECO\_MODE = 0, unless otherwise specified

| Characteristics                         | Symbol               | Test Conditions                                                                           | <b>i</b>               | Min.                  | Тур.      | Max. | Unit                 |

|-----------------------------------------|----------------------|-------------------------------------------------------------------------------------------|------------------------|-----------------------|-----------|------|----------------------|

| OUTPUT OPERATING CHARAC                 | TERISTICS (          | (VOUT)                                                                                    |                        |                       | · · · · · |      |                      |

| Outrook Outrooking Vallage              | V <sub>SAT_H</sub>   | $R_{L_VOUT} = 2 \text{ k}\Omega \text{ to GND}$                                           |                        | V <sub>DD</sub> - 0.3 | _         | _    | V                    |

| Output Saturation Voltage               | V <sub>SAT_L</sub>   | $R_{L_{VOUT}} = 2 \text{ k}\Omega \text{ to GND}$                                         |                        | 0                     | _         | 0.4  | V                    |

| DC Output Resistance                    | R <sub>OUT</sub>     |                                                                                           |                        | _                     | 2         | 5    | Ω                    |

| Outrot Marinetta Priva Comment          |                      | Drive mode: Turbo                                                                         |                        | _                     | _         | 15   | mA                   |

| Output Maximum Drive Current            | I <sub>OD</sub>      | Drive mode: Economy                                                                       |                        | -                     | _         | 7.5  | mA                   |

|                                         |                      |                                                                                           | BW = 100 kHz           | -                     | 2.4       | 3.5  | μs                   |

| Rise Time                               |                      | $T_A = 25^{\circ}\text{C}, C_{L\_VOUT} = 4.7 \text{ nF},$<br>$C_{BYPASS} = 1 \mu\text{F}$ | BW = 250 kHz           | _                     | 1.65      | 2.5  | μs                   |

| Rise Title                              | t <sub>R</sub>       | C <sub>BYPASS</sub> = 1 µF                                                                | BW = 400 kHz           | _                     | 1.2       | 2    | μs                   |

|                                         |                      |                                                                                           | BW = 450 kHz           | _                     | 1.15      | -    | μs                   |

|                                         |                      |                                                                                           | BW = 100 kHz           | _                     | 0.9       | 1.5  | μs                   |

| Propagation Delay                       |                      | $T_A = 25^{\circ}\text{C}, C_{L\_VOUT} = 4.7 \text{ nF},$<br>$C_{BYPASS} = 1 \mu\text{F}$ | BW = 250 kHz           | _                     | 0.85      | 1.4  | μs                   |

| Propagation Delay                       | t <sub>PD</sub>      | $C_{\text{BYPASS}} = 1  \mu \text{F}$                                                     | BW = 400 kHz           | _                     | 0.75      | 1.3  | μs                   |

|                                         |                      |                                                                                           | BW = 450 kHz           | _                     | 0.7       | _    | μs                   |

|                                         |                      | T <sub>A</sub> = 25°C, C <sub>L_VOUT</sub> = 4.7 nF,                                      | BW = 100 kHz           | -                     | 3.5       | 6    | μs                   |

| Beenenee Time                           | t <sub>RESP</sub>    |                                                                                           | BW = 250 kHz           | -                     | 2.4       | 3.5  | μs                   |

| Response Time                           |                      |                                                                                           | BW = 400 kHz           | -                     | 1.25      | 2.5  | μs                   |

|                                         |                      |                                                                                           | BW = 450 kHz           | _                     | - 1.2 -   | μs   |                      |

| Noise Density                           | N                    | T <sub>4</sub> = 25°C at 400 kHz                                                          | T <sub>A</sub> = 25°C  | _                     | 1.21      | 1.64 | mG/√Hz               |

| Noise Defisity                          | N <sub>D</sub>       |                                                                                           | T <sub>A</sub> = 125°C | _                     | 1.69      | 2.25 | mG/√Hz               |

| Noise                                   | N                    | T <sub>A</sub> = 25°C, C <sub>L VOUT</sub> = 1 nF,                                        | T <sub>A</sub> = 25°C  | _                     | 2.83      | _    | ${\rm mV}_{\rm RMS}$ |

| Noise                                   | IN                   | Sens = 3 mV/G, BW = 400 kHz                                                               | T <sub>A</sub> = 125°C | _                     | 3.61      | _    | ${\rm mV}_{\rm RMS}$ |

| Nonlinearity                            | _                    | $T_A = -40^{\circ}C \text{ to } 125^{\circ}C,  B  \le 1650 \text{ G}$                     |                        | -0.5                  | ±0.25     | 0.5  | %                    |

| Nonlinearity                            | E <sub>LIN</sub>     | $T_A = -40$ °C to 125°C, 2000 G >  B  > 1                                                 | 1650 G                 | -1                    | _         | 1    | %                    |

| Power Supply Sensitivity Error          | E <sub>SENS_PS</sub> | V <sub>DD(MIN)</sub> to V <sub>DD(MAX)</sub>                                              |                        | -5                    | ±0.25     | 5    | mV                   |

| Power Supply Offset Error               | V <sub>OE_PS</sub>   | V <sub>DD(MIN)</sub> to V <sub>DD(MAX)</sub>                                              |                        | -0.5                  | _         | 0.5  | %                    |

| VOUT Short-Circuit Current              |                      | T <sub>A</sub> = 25°C, VOUT shorted to GND                                                |                        | _                     | 30        | _    | mA                   |

| VOOT Short-circuit Current              | I <sub>SC_VOUT</sub> | T <sub>A</sub> = 25°C, VOUT shorted to VDD                                                |                        | _                     | -30       | _    | mA                   |

| REFERENCE OUTPUT OPERAT                 | ING CHARA            | CTERISTICS (VREF)                                                                         |                        |                       |           |      |                      |

| VREF Noise Density                      | N <sub>D_VREF</sub>  | f > 100 Hz                                                                                |                        | _                     | 0.5       | _    | μV/√Hz               |

|                                         |                      | Output/Input Mode                                                                         |                        | 150                   | 200       | 300  | Ω                    |

| DC Internal Reference Output Resistance | R <sub>REF_INT</sub> | Output Mode Only                                                                          |                        | -                     | 2         | 5    | Ω                    |

|                                         |                      | Input Mode Only                                                                           | -                      | 200                   | _         | kΩ   |                      |

| Reference Voltage Input Range           | V <sub>REF_IN</sub>  | T <sub>A</sub> = 25°C, VREF overdriven externall                                          | у                      | 0.5                   | _         | 2.65 | V                    |

| VREF Short-Circuit Current              |                      | T <sub>A</sub> = 25°C, VREF shorted to GND                                                |                        | 0.5                   | 0.7       | 1    | mA                   |

| VILL SHOIL-GIICUIT GUITEIIL             | I <sub>SC_VREF</sub> | T <sub>A</sub> = 25°C, VREF shorted to VDD                                                |                        |                       | 5         | 10   | mA                   |

# High-Precision, Programmable Linear Hall-Effect Sensor IC with VREF and High-Bandwidth (400 kHz) Analog Output for Core-Based Current Sensing

## ACS37600K

**ELECTRICAL CHARACTERISTICS (continued):** Valid through the full operating temperature range,  $T_A$ ,  $C_{BYPASS} = 0.1 \mu F$ ,  $V_{DD} = 5 \text{ V}$ ,  $ECO\_MODE = 0$ , unless otherwise specified

| Characteristics                                            | Symbol                            | Test Condition                                                             | s                               | Min.  | Тур.                                                                                                          | Max.  | Unit |

|------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------|---------------------------------|-------|---------------------------------------------------------------------------------------------------------------|-------|------|

| PROGRAMMABLE CHARACT                                       | TERISTICS: C                      | UIESCENT VOLTAGE AND REFERE                                                | NCE VOLTAGE                     |       |                                                                                                               |       |      |

| Reference Voltage Coarse                                   | BITS <sub>VREF</sub> _<br>COARSE  | VREF_COARSE                                                                |                                 | -     | 2                                                                                                             | -     | bit  |

| Reference Voltage Fine                                     | BITS <sub>VREF_FINE</sub>         | VOFF_FINE                                                                  |                                 | _     | 9                                                                                                             | -     | bit  |

| Factory-Programmed<br>Reference Voltage                    | V <sub>REF</sub>                  |                                                                            |                                 | _     | 2.5                                                                                                           | -     | V    |

| Average VREF Programming<br>Step Size                      | STEP <sub>VREF</sub>              | T <sub>A</sub> = 25°C                                                      |                                 | _     | 0.98                                                                                                          | _     | mV   |

| Reference Voltage<br>Temperature Compensation<br>Step Size | STEP <sub>VREF_TC</sub>           | Step size at each of TC point                                              |                                 | _     | STEP <sub>VREF</sub>                                                                                          | -     | mV   |

|                                                            | VREF_COARSE = 11; factory default |                                                                            | 2.35                            | 2.5   | 2.65                                                                                                          | V     |      |

| Reference Voltage Output Programming Range                 | V <sub>REF_OUT</sub>              | T <sub>A</sub> = 25°C; VREF_FINE programming range for a given VREF_COARSE | VREF_COARSE = 10                | 1.5   | 1.65                                                                                                          | 1.8   | V    |

| Programming Range                                          |                                   | range for a given VREF_COARSE                                              | VREF_COARSE = 01                | 1.35  | 9 2.5 0.98 STEP <sub>VREF</sub> 2.5 1.65 1.5 0.5 9 V <sub>REF</sub> 1.15 STEP <sub>VREF</sub> - 2 9 6 3 15.11 | 1.65  | V    |

|                                                            |                                   |                                                                            | VREF_COARSE = 11                | 0.35  | 0.5                                                                                                           | 0.65  | V    |

| Offset Voltage<br>Programming Bits                         | BITS <sub>VOFF_FINE</sub>         | VOFF_FINE                                                                  |                                 | _     | 9                                                                                                             | -     | bit  |

| Factory-Programmed Quiescent Voltage Output                | V <sub>QVO</sub>                  | T <sub>A</sub> = 25°C; 0 G                                                 |                                 | _     | V <sub>REF</sub>                                                                                              | _     | V    |

| Offset Voltage Programming<br>Step Size                    | STEP <sub>VOE</sub>               | V <sub>OE</sub> = V <sub>QVO</sub> – V <sub>REF</sub>                      |                                 | _     | 1.15                                                                                                          | -     | mV   |

| Offset Voltage Temperature<br>Compensation Step Size       | STEP <sub>VOE_TC</sub>            | Step size at each of TC point                                              |                                 | -     | STEP <sub>VREF</sub>                                                                                          | -     | mV   |

| Offset Voltage Programming Range                           | V <sub>OE_PR</sub>                | $V_{OE} = V_{QVO} - V_{REF}$                                               |                                 | -200  | -                                                                                                             | 200   | mV   |

| PROGRAMMABLE CHARACT                                       | TERISTICS: S                      | ENSITIVITY                                                                 |                                 |       |                                                                                                               |       |      |

| Coarse Sensitivity Programming Bits                        | BITS <sub>SENS_C</sub>            | SENS_COARSE                                                                |                                 | _     | 2                                                                                                             | _     | bit  |

| Sensitivity Programming Bits                               | BITS <sub>SENS_FINE</sub>         | SENS_FINE                                                                  |                                 | _     | 9                                                                                                             | -     | bit  |

| Factory-Programmed Sensitivity                             | Sens                              | T = 25°C                                                                   | SENS_COARSE = 10;<br>006B5-C/CP | _     | 6                                                                                                             | -     | mV/G |

| r actory-mogrammed Sensitivity                             | Sens                              | T <sub>A</sub> = 25°C                                                      | SENS_COARSE = 01;<br>003B5-C/CP | _     | 3                                                                                                             | -     | mV/G |

| Average Consitivity Stor Size                              | STED                              | T <sub>A</sub> = 25°C; SENS_FINE programming                               | SENS_COARSE = 10                | 13.14 | 15.11                                                                                                         | 17.78 | μV/G |

| Average Sensitivity Step Size                              | STEP <sub>SENS</sub>              | step size for a given SENS_COARSE                                          | SENS_COARSE = 01                | 6.57  | 7.56                                                                                                          | 8.89  | μV/G |

| Sensitivity Temperature Compensation Step Size             | STEP <sub>SENS_TC</sub>           | Step size at each of TC point                                              |                                 | _     | STEP <sub>SENS</sub>                                                                                          | _     | Sens |

# High-Precision, Programmable Linear Hall-Effect Sensor IC with VREF and High-Bandwidth (400 kHz) Analog Output for Core-Based Current Sensing

**ELECTRICAL CHARACTERISTICS (continued):** Valid through the full operating temperature range,  $T_A$ ,  $C_{BYPASS} = 0.1 \mu F$ ,  $V_{DD} = 5 \text{ V}$ ,  $ECO\_MODE = 0$ , unless otherwise specified

| Characteristics                                                   | Symbol                         | Test Condition                | IS               | Min.   | Тур.  | Max. | Unit |

|-------------------------------------------------------------------|--------------------------------|-------------------------------|------------------|--------|-------|------|------|

| PROGRAMMABLE CHARAC                                               | TERISTICS: S                   | SENSITIVITY (CONTINUED)       |                  |        |       | •    |      |

| Sensitivity Programming                                           | C                              |                               | 4.8              | _      | 7.2   | mV/G |      |

| Range                                                             | Sens <sub>PR</sub>             | range for a given SENS_COARSE | SENS_COARSE = 01 | 2.4    | -     | 3.6  | mV/G |

| Sensitivity Slope Over<br>Temperature Bits                        | BITS <sub>SENS_</sub><br>SLOPE | GAIN_TC                       |                  | -      | 6     | -    | bit  |

| Sensitivity Slope Temperature<br>Coefficient Step Size            | STEP <sub>SENS_</sub><br>SLOPE |                               |                  | _      | 0.002 | _    | %/°C |

| Sensitivity Slope Temperature<br>Coefficient Programming<br>Range | Sens <sub>SLOPE_PR</sub>       |                               |                  | -0.025 | _     | 0.05 | %/°C |

## High-Precision, Programmable Linear Hall-Effect Sensor IC with VREF and High-Bandwidth (400 kHz) Analog Output for Core-Based Current Sensing

ACS37600KOK DEVICE PERFORMANCE CHARACTERISTICS: Valid through the full operating temperature range,

$T_A$ ,  $C_{BYPASS} = 0.1 \mu F$ ,  $V_{DD} = 5 V$ , ECO\_MODE = 0, unless otherwise specified

| Characteristics <sup>[1]</sup>                   | Symbol                  | Test Conditions                                               | Min. <sup>[2]</sup> | Typ. <sup>[3]</sup> | Max. <sup>[2]</sup> | Unit |

|--------------------------------------------------|-------------------------|---------------------------------------------------------------|---------------------|---------------------|---------------------|------|

| ERROR COMPONENTS                                 |                         |                                                               |                     |                     |                     |      |

|                                                  |                         | T <sub>A</sub> = 25°C                                         | -1.75               | ±0.6                | 1.75                | %    |

| Sensitivity Error                                | E <sub>SENS</sub>       | T <sub>A</sub> = 25°C to 125°C, with respect to 25°C          | -1.75               | ±0.6                | 1.75                | %    |

|                                                  |                         | $T_A = -40$ °C to 25°C, with respect to 25°C                  | -3.5                | ±1                  | 3.5                 | %    |

|                                                  |                         | B = 0 G, T <sub>A</sub> = 25°C                                | -10                 | ±2                  | 10                  | mV   |

| Quiescent Voltage Output Error                   | V <sub>QVO_E</sub>      | B = 0 G, T <sub>A</sub> = 25°C to 125°C, with respect to 25°C | -10                 | ±2.5                | 10                  | mV   |

|                                                  |                         | B = 0 G, $T_A = -40$ °C to 25°C, with respect to 25°C         | -16                 | ±5                  | 16                  | mV   |

|                                                  |                         | T <sub>A</sub> = 25°C                                         | -10                 | ±2                  | 10                  | mV   |

| Reference Voltage Output Error                   | V <sub>REF_E</sub>      | T <sub>A</sub> = 25°C to 125°C, with respect to 25°C          | -10                 | ±2.2                | 10                  | mV   |

|                                                  | _                       | T <sub>A</sub> = -40°C to 25°C, with respect to 25°C          | -10                 | ±2                  | 10                  | mV   |

|                                                  |                         | B = 0 G, T <sub>A</sub> = 25°C                                | -10                 | ±1                  | 10                  | mV   |

| Offset Error                                     | V <sub>OE</sub>         | B = 0 G, T <sub>A</sub> = 25°C to 125°C, with respect to 25°C | -10                 | ±1                  | 10                  | mV   |

|                                                  |                         | B = 0 G, $T_A = -40$ °C to 25°C, with respect to 25°C         | -14                 | ±4                  | 14                  | mV   |

| ERROR COMPONENTS LIFETI                          | ME DRIFT <sup>[4]</sup> |                                                               |                     |                     |                     |      |

| Sensitivity Error Lifetime Drift                 | E <sub>SENS_LTD</sub>   | T <sub>A</sub> = 25°C                                         | _                   | ±0.6                | _                   | %    |

| Quiescent Voltage Output Error<br>Lifetime Drift | V <sub>QVO_LTD</sub>    | B = 0 G, T <sub>A</sub> = 25°C                                | -                   | ±1.2                | _                   | mV   |

| Reference Voltage Output Error<br>Lifetime Drift | V <sub>REF_LTD</sub>    | B = 0 G, T <sub>A</sub> = 25°C                                | _                   | ±1                  | _                   | mV   |

| Offset Error Lifetime Drift                      | V <sub>OE_LTD</sub>     | B = 0 G, T <sub>A</sub> = 25°C                                | _                   | ±0.5                | _                   | mV   |

<sup>[1]</sup> Characteristics are valid within the sense programmable range of the corresponding part number.

## ACS37600KOK-CP DEVICE PERFORMANCE CHARACTERISTICS: Valid through the full operating temperature range, $T_A$ , $C_{BYPASS} = 0.1 \mu F$ , $V_{DD} = 5 V$ , ECO\_MODE = 0, unless otherwise specified

| Characteristics | Symbol | Test Conditions  | Min. | Тур.    | Max. | Unit |

|-----------------|--------|------------------|------|---------|------|------|

| Polarity Bit    | _      | Flipped polarity |      | Enabled |      | _    |

<sup>[2]</sup> Min. and Max. is determined such that 99.73% of devices lie within the interval during initial characterization. The worst case of mean ± 3σ from production characterization data was calculated and applied symmetrically. These values can drift after solder reflow and over lifetime.

<sup>[3]</sup> Typical values are |mean| +1 $\sigma$  based on production characterization data.

<sup>[4]</sup> Lifetime drift typical values are worst case mean values seen during AEC Q-100 qualification.

## **FUNCTIONAL DESCRIPTION**

#### Introduction

The Power-On thresholds of the ACS37600 are based on a combination of a check on the internal regulator supplied and  $V_{DD}.$  This allows the ACS37600 to accurately report a signal, including internal stress and temperature compensation, at startup. To ensure that the device output is reporting accurately, the ACS37600 contains an overvoltage and an undervoltage detection flag. This internal flag on  $V_{OUT}$  can be used to alert the system when the supply voltage for the device is outside of the operational range by putting the output into a known high-impedance (high Z) state. If one or both are not desired, the UVD and OVD functionality can be individually toggled off.

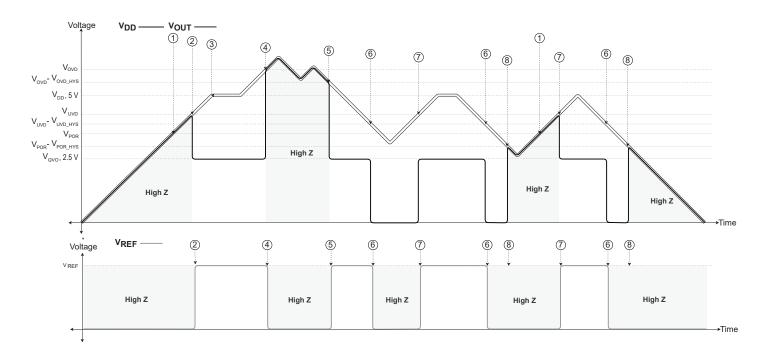

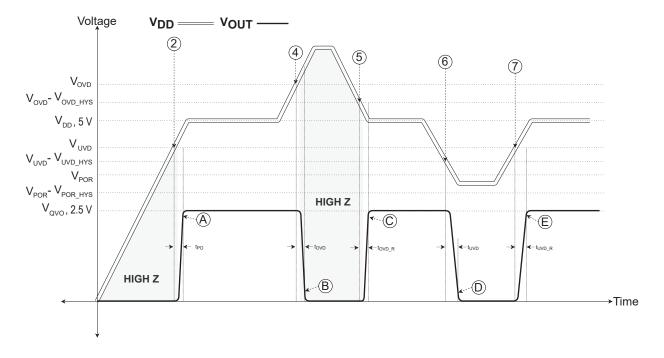

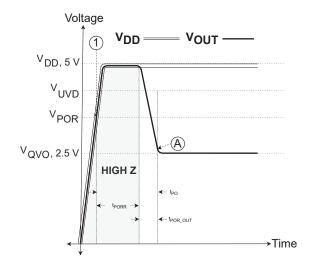

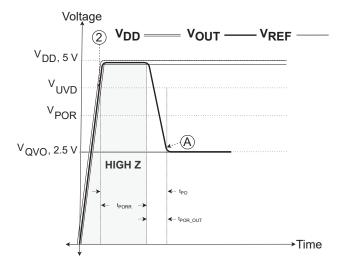

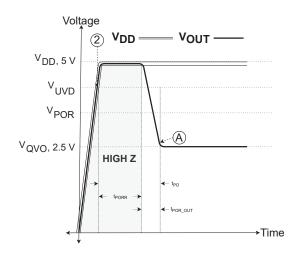

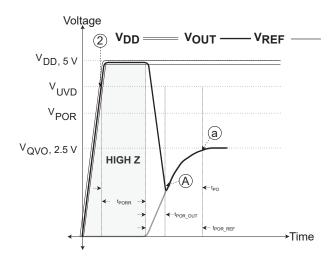

The provided graphs in this section show  $V_{OUT}$  moving with  $V_{DD}$ . The voltage of  $V_{OUT}$  during a high Z state will be most consistent with a known load ( $R_{L\_VOUT}$ ,  $C_{L\_VOUT}$ ,  $R_{L\_VREF}$ ,  $C_{L\_VREF}$ ). Figure 3, Figure 4, Figure 5, Figure 6, Figure 7, and Figure 8 all use the same labeling scheme for different power thresholds. References in brackets "[]" are valid for each of these plots.

#### **POWER-ON OPERATION**

Note that the ACS37600 comes factory programmed with UVD enabled.

#### **UVD** Enabled

When UVD is enabled, as  $V_{DD}$  ramps up, the ACS37600  $V_{OUT}$  and  $V_{REF}$  pins are high Z until  $V_{DD}$  reaches and passes  $V_{UVD}$  [2]. Once  $V_{DD}$  passes [2], the device takes some time without  $V_{DD}$  dropping below  $V_{POR}$ - $V_{POR}$ - $W_{POR}$ - $W_{P$

#### **UVD** Disabled

When UVD is disabled, as  $V_{DD}$  ramps up, the ACS37600  $V_{OUT}$  and  $V_{REF}$  pins are high Z until  $V_{DD}$  reaches and passes  $V_{POR}$  [1]. Once  $V_{DD}$  has passed  $V_{POR}$  [1],  $V_{OUT}$  enters normal operation.

#### **POWER-OFF OPERATION**

#### **UVD** Enabled

When UVD is enabled, before the device powers off, it will force  $V_{OUT}$  to GND if  $V_{DD}$  reaches below  $V_{UVD} - V_{UVD\_HYS}$  [6]. When  $V_{POR} - V_{POR\_HYS}$  [8] is reached,  $V_{OUT}$  and  $V_{REF}$  will go high Z.

#### **UVD** Disabled

When UVD is disabled, then  $V_{REF}$  and  $V_{OUT}$  will continue to report until  $V_{DD}$  is less than  $V_{POR} - V_{POR\_HYS}$  [8], at which point,  $V_{OUT}$  and  $V_{REF}$  will enter a high Z state.

Note: since the device is entering a high Z state and not driving the output, the time it takes the output to reach a steady state will depend on the external circuitry used.

## **Voltage Thresholds**

## POWER-ON RESET RELEASE VOLTAGE(VPOR)

If  $V_{DD}$  falls below  $V_{POR} - V_{POR\_HYS}$  [8] while in operation, the digital circuitry turns off and the output will re-enter a high Z state. After  $V_{DD}$  recovers and exceeds  $V_{UVD}$  [2], the output will begin reporting again after the delay of  $t_{PO}$ .

#### UNDERVOLTAGE DETECTION THRESHOLD (V<sub>UVD</sub>)

The 5 V devices are factory-programmed with UVD enabled. It is important to note that when powering up the device for the first time after a Power-On Reset event,  $V_{OUT}$  and  $V_{REF}$  will remain high Z until  $V_{DD}$  is raised above  $V_{UVD}$  [2], at which point the  $V_{OUT}$  and  $V_{REF}$  outputs will begin to normal operation. If UVD is disabled,  $V_{OUT}$  and  $V_{REF}$  will begin normal operation after  $V_{DD}$  raises above  $V_{POR}$  [1] under the same conditions.

If  $V_{DD}$  drops below  $V_{UVD} - V_{UVD\_HYS}$  [6] after normal operation,  $V_{OUT}$  will pull to GND regardless of  $R_{L\_VOUT}$  configuration. The  $V_{OUT}$  will remain at GND until  $V_{DD}$  raises above  $V_{UVD}$  [7] or  $V_{DD}$  falls below  $V_{POR} - V_{POR\_HYS}$  [8]. If  $V_{DD}$  rises above  $V_{UVD}$  [7] after a UVD event, the  $V_{OUT}$  and  $V_{REF}$  outputs will resume operation. If  $V_{DD}$  drops below  $V_{POR} - V_{POR\_HYS}$  [8], the device will enter a POR event and reset;  $V_{OUT}$  and  $V_{REF}$  will switch to high Z if this occurs.

#### OVERVOLTAGE DETECTION THRESHOLD (V<sub>OVD</sub>)

When  $V_{DD}$  raises above  $V_{OVD}$  [4], the output of the  $V_{OUT}$  and  $V_{REF}$  pin will go high Z,  $V_{REF}$  be pulled to GND, and  $V_{OUT}$  will be pulled to either VDD or GND, depending if  $R_{L\_VOUT}$  is in a pull-up or pull-down configuration.

## High-Precision, Programmable Linear Hall-Effect Sensor IC

## ACS37600K

with VREF and High-Bandwidth (400 kHz) Analog Output for Core-Based Current Sensing

## OVERVOLTAGE/UNDERVOLTAGE DETECTION HYSTERESIS (V<sub>OVD\_HYS</sub>, V<sub>UVD\_HYS</sub>)

There is hysteresis between enable and disable thresholds to reducing nuisance flagging and clears.

## **Timing Thresholds**

## Overvoltage and Undervoltage Detection Time and Detection Release Time $(t_{OVD}/t_{OVD\_R}, t_{UVD}/t_{UVD\_R})$

The enable time for OVD,  $t_{OVD}$ , is the time from  $V_{OVD}$  [4] to OVD flag [B]. The UVD enable time, t<sub>UVD</sub>, is the time from  $V_{UVD} - V_{UVD\ HYS}$  [6] to the UVD flag [D]. The enable flag for both OVD and UVD have a counter to reduce transients faster than 64 us from nuisance flags.

If  $V_{DD}$  ramps from  $>V_{UVD} - V_{UVD HYS}$  [6] to  $<V_{POR} - V_{POR HYS}$ [8] faster than  $t_{UVD}$  ( $\approx$ 64 µs), then the device will not have time to report a UVD event before power off occurs.

The detection release time for OVD, t<sub>OVD</sub> <sub>R</sub>, is the time from  $V_{OVD} - V_{OVD HYS}$  [5] to the OVD clear to normal operation [C]. The UVD disable time,  $t_{UVD\ R}$  is the time from  $V_{UVD}$  [7] to the point that the UVD flag clears and V<sub>OUT</sub> returns to nominal operation [E]. The disable time does not have a counter for either OVD or UVD to release the output and resume reporting.

#### Power-On Reset (POR)

If V<sub>DD</sub> falls below V<sub>POR</sub> – V<sub>POR HYS</sub> [8] while in operation, the output will re-enter a high Z state. After V<sub>DD</sub> recovers and exceeds V<sub>UVD</sub> [2], the output will begin reporting again after the delay of t<sub>PO</sub>. This t<sub>PO</sub> depends on t<sub>PORR</sub>, t<sub>POR OUT</sub> and, t<sub>POR REF</sub>.

#### Power-On Reset Release Time (tpork)

When  $V_{DD}$  rises above  $V_{UVD}$  [2], the Power-On Release Time counter starts. If UVD is disabled, this threshold is  $V_{POR}$  [1]. The output will only release from high Z to nominal operation after the Power-On Reset counter has reached the internal tport value and the temperature compensation has been updated. This allows for robust and stable output reporting that is temperature compensated. If V<sub>DD</sub> falls below V<sub>POR</sub> – V<sub>POR HYS</sub> [8] before the counter finishes, the counter is reset and the part remains in the reset state.

## Power-On Reset Output Delay (t<sub>POR OUT</sub>)

The term t<sub>POR OUT</sub> is defined as the time required for the output to reach 90% of its stable state around V<sub>REF</sub> after t<sub>PORR</sub>. This is best measured with V<sub>REF</sub> either being overdriven or externally supplied. Because V<sub>OUT</sub> takes direct input and is centered at  $V_{REF}$ , the output stable state is  $V_{OUT(Field)} = Sens \times Field + V_{REF}$ . Refer to the next section for discussion of the implications of V<sub>REF</sub> driven internally.

#### Power-On Reset Reference Delay (t<sub>POR REF</sub>)

The term  $t_{POR\ REF}$  is defined as the time required for the  $V_{REF}$  output to drive the pin to 90% V<sub>REF</sub> stable state from the high-Z state. The voltage on the VREF pin is the common mode voltage for the V<sub>OUT</sub> amplifier and dictates the zero for V<sub>OUT</sub>.

The VREF pin is meant to be overdriven, which is achieved by limiting the drive strength of the output amplifier. This drive limitation makes the t<sub>POR REF</sub> extremely dependent on the application circuit elements R<sub>L</sub> V<sub>REF</sub> and C<sub>L</sub> V<sub>REF</sub>. This dependency should be considered when selecting the R<sub>L VREF</sub> and C<sub>L VREF</sub> values.

#### Power-On Delay (t<sub>PO</sub>)

When the supply is ramped to  $V_{UVD}$  [2], the device requires a finite time to power its internal components before the outputs are released from high Z and can respond to an input magnetic field. Power-On Time, t<sub>PO</sub>, is defined as the time it takes for the output voltage to settle within  $\pm 10\%$  of its steady-state value under an applied magnetic field, which can be viewed as the time from [2] to [A] or [a], depending on the  $V_{REF}$  configuration. After this delay, the output quickly approaches  $V_{OUT(Field)} = Sens \times Field + V_{REF}$ . An externally driven  $V_{REF} t_{PO}$ is shown in Figure 7, and the internally driven  $V_{REF}$   $t_{PO}$  is shown in Figure 8.

Figure 3: Power States Thresholds with VOUT and VREF Behavior, R<sub>L</sub> = Pull Up, UVD Enabled

Figure 4:  $t_{PO}$ ,  $t_{OVD}/t_{OVD}$   $_R$ , and  $t_{UVD}/t_{UVD}$   $_R$ , Behavior with Fast  $V_{DD}$  Ramping

Figure 5: Power-on Reset Behavior, UVD Disabled,  $R_L$  = Pull-Up

Figure 7:  $t_{PO}$   $V_{OUT}$  Behavior with  $V_{REF}$  Externally Driven,  $t_{POR\_OUT}$ ,  $R_L$  = Pull-Up

Figure 6: Power-on Reset Behavior, UVD Enabled, R<sub>L</sub> = Pull-Up

Figure 8:  $t_{PO}$   $V_{OUT}$  Behavior with  $V_{REF}$  Internally Driven,  $t_{POR}$   $_{REF}$ ,  $R_{L}$  = Pull-Up

#### **DEFINITIONS OF OPERATING AND PERFORMANCE CHARACTERISTICS**

## Quiescent Voltage Output (VOVO)

The quiescent voltage output is defined as the voltage on the output VOUT when zero gauss is applied.  $V_{QVO}$  is determined by two quantities, the VREF pin voltage and the VOFF\_FINE register that adjusts the output channel offset error from the VREF pin.

## Quiescent Voltage Output Error(V<sub>QVO</sub> E)

Quiescent Voltage Output Error, or  $V_{QVO\_E}$ , is defined as the drift of  $V_{OUT}$  from room to hot or room to cold (25°C to 125°C or 25°C to -40°C, respectively). Temperature drift is compensated with the Allegro factory trim to remain within the limits across temperature; because of this, only room-trimming/programming is needed. This parameter is controlled by the VOFF\_FINE register. Programming too close (<32 LSB) to the minimum and maximum values of the VOFF\_FINE register will affect temperature performance. This compensation is performed in increments of STEP\_VOE over temperature.

## Reference Voltage Output (VRFF)

The reference voltage output pin (VREF) is used as the common-mode voltage reference for the output channel  $V_{OUT}$ . The voltage of the VREF pin determines the quiescent voltage,  $V_{OUT}$ , of the output amplifier, allowing the pin to be driven internally, externally, and overdriven to change the quiescent output voltage. This pin can be programmed to operate as input-only, output-only, or input/output using the IO\_VREF\_MODE register. The output voltage can also be adjusted with two internal VREF DACs: VREF\_COARSE, which determines the coarse range that VREF\_FINE can adjust, and fine tune. For further information about these registers, refer to the Defining Programming Parameters section.

- V<sub>REF</sub> programmable range is 0.35 to 2.65 V

- V<sub>REF</sub> can be overdriven to 0.5 to 2.65 V

## Reference Voltage Temperature Drift ( $V_{REF\_E}$ )

Reference voltage temperature drift,  $V_{REF\_E}$ , is defined as the drift of VREF from room to hot or room to cold (25°C to 125°C or 25°C to -40°C, respectively). Only room-trimming/programming is needed because temperature drift is compensated with the Allegro

factory trim to remain within the limits across temperature. This parameter is controlled by the VREF\_FINE register. Programming too close (<32 LSB) to the minimum and maximum values of the VREF\_FINE register will affect temperature performance. This compensation is performed in increments of STEP\_VREF over temperature.  $V_{REF\_E}$  is dependent on the VREF\_COARSE register. If VREF\_COARSE is changed from factory default,  $V_{REF\_E}$  may not meet datasheet parameters.

## Reference Voltage Programming Step Size (STEP<sub>VREF</sub>)

Reference voltage programming step size is defined as the average change in VREF voltage per an LSB change in VREF\_FINE register.

## Offset Voltage (VoE)

Offset voltage,  $V_{OE}$ , is defined as  $V_{QVO} - V_{REF}$ . The voltage offset between the output and  $V_{REF}$  can be adjusted with the VOFF\_FINE register. For best accuracy, verify actual device step size and result when trimming.

## Offset Voltage Programming Step Size (STEP<sub>VOE</sub>)

Offset voltage programming step size is defined as the average of change in  $V_{QVO} - V_{REF}$  voltage per an LSB change in the VOFF\_FINE register. For best accuracy, verify the actual device step size and result when trimming.

## Output Saturation Voltage (V<sub>SAT H/L</sub>)

Output saturation voltage,  $V_{SAT}$ , is defined as the voltage at which output no longer changes when the magnitude of the magnetic field is increased.  $V_{SAT\_H}$  is the highest voltage the output can drive, while  $V_{SAT\_L}$  is the lowest. Note that changing the sensitivity does not change the  $V_{SAT}$  points.

## Power Supply Offset Error (V<sub>OE PS</sub>)

Power supply offset error,  $V_{PS}$ , is defined as the offset error in mV between  $V_{DD}$  at 5 V to 4.5 V and 5 V to 5.5 V.

## Power Supply Sensitivity Error (E<sub>SENS PS</sub>)

Power supply sensitivity error, EPS, is defined as the percentage of the sensitivity error measured between  $V_{DD}$  at 5 V to 4.5 V and 5 V to 5.5 V.

## Sensitivity (Sens)

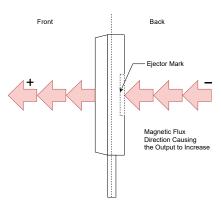

Sensitivity, or Sens, is the output swing in the presence of a magnetic field, perpendicular to and out of the top surface of the package face. This magnetic field moves the output voltage away from its  $V_{OUT}$  and toward the supply voltage rails. The magnitude and direction of the output voltage swing is proportional by Sens to the magnitude and direction of the applied magnetic field. The Sens of the device is calculated slightly differently for unidirectional application (positive or negative operating range) and bidirectional (positive and negative operating range) parts.

Bidirectional parts have sensitivity defined as:

$$Sens = \frac{V_{OUT(B_1)} - V_{OUT(B_2)}}{B_1 - B_2}$$

Parts in a unidirectional application have sensitivity defined as:

$$Sens = \frac{V_{OUT(B+)} - V_{QVO}}{B+}$$

$$Sens = \frac{V_{OUT(B-)} - V_{QVO}}{B-}$$

B+/B- are two magnetic fields with opposite polarities, and  $V_{OUT(B^+)}$  and  $V_{OUT(B^-)}$  are the output voltages at the applied fields.  $V_{QVO}$  is the actual measured offset voltage, not calculated. The fine sensitivity of the device can be programmed and controlled by the SNS\_FINE register.

## Sensitivity Programming Range (Senspr)

Sensitivity programming range, Sens<sub>PR</sub>, is the sensitivity programming range of the device with the SNS\_FINE register. The SNS\_FINE register scales with the SNS\_COARSE register to determine the Sens range of a given device; for specific devices, refer to the Device Performance Characteristics section. Sensitivity can be programmed from the factory value within the Sensitivity Programming Range limits. Exceeding the specified Sens<sub>PR</sub> limits can cause the device to operate beyond datasheet limits. For further information about these registers, refer to the Defining Programming Parameters section.

## Sensitivity Error (E<sub>SENS</sub>)

Sensitivity error, or  $\rm E_{SENS}$ , is defined as the drift of Sens from room to hot or room to cold (25°C to 125°C or 25°C to –40°C, respectively). Only room-trimming/programming is needed because temperature drift is compensated with the Allegro factory trim to remain within limits across temperature. This parameter is controlled by the SNS\_FINE register. Programming too close (<32 LSB) to the STEP<sub>SENS</sub> min and max values affects temperature performance. This compensation is performed in increments of STEP<sub>SENS</sub> over temperature and, because STEP<sub>SENS</sub> is dependent on SNS\_COARSE, the  $\rm E_{SENS\_TC}$  limit is only valid for factory-programmed SNS\_COARSE.

## Average Sensitivity Step Size (STEP<sub>SENS</sub>)

Average sensitivity step size, STEP<sub>SENS</sub>, is defined as the average change in the magnetic sensitivity of the device with an LSB change to the SNS\_FINE register. STEP<sub>SENS</sub> is dependent on SNS\_COARSE; as such, the device STEP<sub>SENS</sub> varies for different SENS\_COARSE settings.

#### **Polarity**

Polarity can be changed using the GC\_POL register, inverting the output response to a magnetic field. If this is changed from the factory default, then  $E_{SENS\_TC}$ ,  $V_{OFF\_TC}$ , and  $V_{REF\_TC}$  may not meet datasheet limits. The default fault polarity is a positive output swing in the presence of a magnetic field, perpendicular and out of the top surface of the package face, as shown in Figure 9.

Figure 9: OK Package Flux and Output Directionality

## Nonlinearity (E<sub>LIN</sub>)

As the amount of field applied to the part changes, the sensitivity of the device can also change slightly. This is referred to as linearity error, or  $E_{LIN}$ . Consider two magnetic fields,  $B1(1/2\ FS)$  and B2(FS). Ideally, the sensitivity of the device is the same for both fields. Linearity Error is calculated as the percent change in sensitivity from one field to another. Error is calculated separately for positive  $(E_{LIN(+)})$  and negative  $(E_{LIN(-)})$  magnetic fields, and the percent errors are defined as:

$$E_{LIN(\pm)} = [1 - Sens_{B2\pm} / (Sens_{B1\pm})] \times 100\%$$

where:

$$Sens_{Ry+} = (V_{OUTRy+} - QVO) / B_{y+}$$

and

$$Sens_{Bx-} = (V_{OUTBx-} - QVO) / B_{x-}$$

$B_x$  are positive and negative magnetic fields, such that  $|B_{+2}|=2\times|B_{+1}| \text{ and } |\ B_{-2}|=2\times|B_{-1}|\times E_{LIN}=\max(E_{LIN(+)},E_{LIN(-)}).$

Assumed fields are within the response range of the device.

## **Temperature Compensation**

To remove the effects of temperature on the performance of the ACS37600, an internal temperature sensor is integrated. This sensor, along with compensation algorithms, helps to standardize device performance over the full range of operating temperatures.

## TEMPERATURE COMPENSATION UPDATE RATE (t<sub>UR</sub>)

After power-on delay  $(t_{PO})$  elapses, the temperature compensation update rate,  $t_{UR}$ , is required to maintain a valid temperature-compensated output.

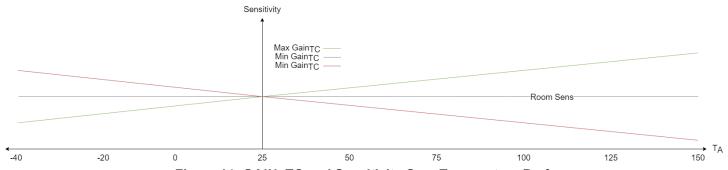

## SENSITIVITY TEMPERATURE COEFFICIENT (SENS-SLOPE)

The Sensitivity Temperature Coefficient,  $SENS_{SLOPE}$ , is a parameter that allows the user to increase or decrease the sensitivity linearly over temperature. This allows for temperature compensation of other elements in the application system.

# SENSITIVITY TEMPERATURE COEFFICIENT STEP SIZE (STEP $_{SENS\ SLOPE}$ )

Sensitivity Temperature Coefficient Step Size, STEP<sub>SENS\_SLOPE</sub>, is defined as the average change in % Sens/°C per LSB change in the gain\_tc register.

## **Package Stress Compensation**

Sensitivity drift due to package hysteresis is internally compensated to reduce the effects of temperature and lifetime drift error. Package stress and relaxation can cause the device sensitivity at  $T_A = 25$ °C to change during and after temperature cycling and over life stress.

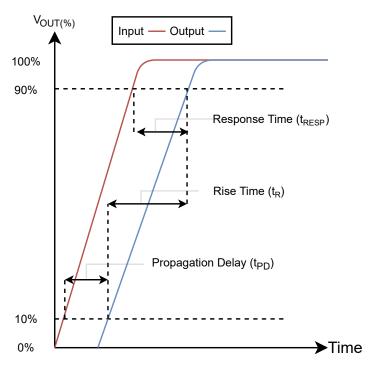

## RESPONSE CHARACTERISTICS DEFINITIONS AND TYPICAL PERFORMANCE DATA

## Response Time (t<sub>RESP</sub>)

The time interval between a) when the sensed input current reaches 90% of its final value, and b) when the sensor output reaches 90% of its full-scale value.

## Propagation Delay (t<sub>PD</sub>)

The time interval between a) when the sensed input current reaches 20% of its full-scale value, and b) when the sensor output reaches 20% of its full-scale value.

## Rise Time (t<sub>R</sub>)

The time interval between a) when the sensor reaches 10% of its full-scale value, and b) when it reaches 90% of its full-scale value.

## **Output Slew Rate (SR)**

The rate of change  $[V/\mu s]$  in the output voltage from a) when the sensor reaches 10% of its full-scale value, and b) when it reaches 90% of its full-scale value.

Figure 10: Dynamic Response Parameters

## **APPLICATION AND THEORY**

## **Parameter Trim Algorithm**

For best results, a trim flow of sensitivity,  $V_{REF}$ , then  $V_{OE}/V_{QVO}$  is recommended, because sensitivity and  $V_{REF}$  affect  $V_{OE}/V_{QVO}$ .

### **SENSITIVITY (SENS):**

- 1. Determine the actual sensitivity and target sensitivity. To calculate Sens:

- $Sens = Sens_{TARGET} Sens_{ACTUAL}$

- 2. Divide the calculated Sens by STEP<sub>SENS</sub> to determine the number of codes to change the SNS\_FINE register.

- A. If more accuracy is required or desired, the actual STEP<sub>Sens</sub> of the device must be measured. This measurement should be performed if an iterative process is used. Number of Sens codes = round(Sens/STEP<sub>SENS</sub>)

- 3. Read the SNS\_FINE register and add the number of Sens codes to the register value. Write the result in SNS\_FINE.

- 4. Measure the new sensitivity. If it is not within 0.5 × STEP<sub>SENS</sub> or within the desired error, repeat steps 1 through 4; for best accuracy, be sure to measure STEP<sub>Sens</sub>.

#### REFERENCE VOLTAGE OUTPUT (VREF):

- 5. Determine the actual  $V_{REF}$  and target  $V_{REF}$ . Calculate  $V_{REF}$  as:  $V_{REF} = V_{REF TARGET} V_{REF ACTUAL}$

- 6. Divide the calculated V<sub>REF</sub> by STEP<sub>VREF</sub> to determine the number of codes to change for the VREF FINE register.

- A. If more accuracy is required or desired, the actual  $STEP_{VREF}$  of the device must be measured. This measurement should be performed if an iterative process is used. Number of VREF codes = round( $V_{REF}$  /  $STEP_{VREF}$ )

- 7. Read the vref\_fine register and add the number of V<sub>REF</sub> codes to the register value. Write the result in VREF\_FINE.

- 8. Measure the new  $V_{REF}$ . If it is not within  $0.5 \times STEP_{VREF}$  or within the desired error, repeat steps 5 through 8; for best accuracy, be sure to measure  $STEP_{VREF}$ .

## QUIESCENT VOLTAGE OUTPUT (VOVO):

- Knowing the actual V<sub>OE</sub> and target V<sub>OE</sub>, calculate V<sub>OE\_STEP</sub> as:

- $V_{OE} = V_{OE\_TARGET} V_{OE\_ACTUAL}.$

- 10. Divide the calculated  $V_{OE}$  by  $STEP_{VOE}$  to determine the number of codes to change for the voff fine register.

- A. If more accuracy is required or desired, the actual  $STEP_{VOE}$  of the device must be measured. This measurement should be performed if an iterative process is used. Number of  $V_{OE}$  codes = round ( $V_{OE}$  /  $STEP_{VOE}$ )

- Read the VOFF\_FINE register and add the number of V<sub>OE</sub> codes to the REGISTER value. Write the result in VOFF\_FINE.

- Measure the new V<sub>OE</sub>. If it is not within 0.5 × STEP<sub>VOE</sub> or within desired error, repeat steps 9 through 12; for best accuracy, be sure to measure STEP<sub>VREF</sub>.

## High-Precision, Programmable Linear Hall-Effect Sensor IC with VREF and High-Bandwidth (400 kHz) Analog Output for Core-Based Current Sensing

## ACS37600K

## Overdriving V<sub>REF</sub> Introduction

The VREF pin can be overdriven while in the factory VREF\_IO\_MODE. This can be used to dynamically change the effective range of field to which the output is mapped, as well as overdriving the VREF pin during startup POR to reduce the  $t_{PO}$  time. To increase  $V_{REF}$  voltage, the pin must be supplied with a source that can maintain the desired higher voltage level while being capable of supplying a current greater than  $I_{SC\_VREF}$ . To decrease the voltage, the pin must be supplied with a sink that can maintain the desired lower voltage while being able to sink  $I_{SC\_VREF}$ .

#### **DYNAMIC OUTPUT**

Range changing can be performed by adjusting the VREF pin by overdriving the pin voltage.  $V_{REF}$  can be overdriven in the opposite direction down 2 V from 2.5 V to 0.5 V. This effectively allows for a dynamic output operation range, allowing for better accuracy during low current needs while maintaining the ability to capture signals that would otherwise be out of range of the device for the accuracy requirement.

### ACCELERATED tpo

When the ACS37600 powers up, the power-on time can be limited by the low internal drive strength of the VREF pin. One way to reduce this is by overdriving the VREF pin during POR to remove the VREF limited drive strength from slowing  $t_{PO}$ . This allows  $t_{PO}$  to depend on  $t_{POR\_OUT}$  instead of  $t_{POR\_REF}$ , which is twice as slow.

## Manchester Communication and Device Features

## **USING THE ANALOG\_LOCK BIT**

The ANALOG\_LOCK configuration is located in register 0x0F, bit 24, and controls whether an OVD event is required for read/write communications after the initial unlock. With this bit set to the factory default of 0, OVD is not required to send a read or write command. With this bit set to 1, OVD is required for every read/write. This bit does not change the unlock procedure, but only communication after unlock.

## USING THE UNLOCK\_CODE BIT

The UNLOCK\_CODE register is located in register 0x0F, bit 25, and sets the requirement for and additional unlock code to unlock and communicate with the device. With this bit set to the factory default of 0, only one unlock code is required to unlock the part. With this bit set to 1, two codes must be used in succession in order to successfully unlock the part for communication. This bit does not affect communication after unlock.

#### HOW OVD CAN BE USED WITH PROGRAMMING

Using OVD during read/write removes the need for the MCU to overdrive the VREF pin for successful communication. Using the OVD flag to make VREF high Z during communication can be used with ANALOG\_LOCK = 1 or 0, but only when OVD\_DIS = 0, which is the factory default.

## **DEFINING PROGRAMMING PARAMETERS**

# Fine Tuning Sensitivity, Reference Voltage Output, and Quiescent Voltage Output

Sensitivity and  $V_{OE}$  can be adjusted by programming the SNS\_FINE and VOFF\_FINE bits, as illustrated in Figure 11. Users should not program sensitivity or  $V_{QVO}$  beyond the maximum or minimum programming ranges specified in the Operating Characteristics table. Exceeding the specified limits will cause sensitivity and  $V_{QVO}$  to drift through the temperature range ( $V_{REF\_E}$ ,  $V_{OE}$ , and  $E_{SENS}$ ) to deteriorate beyond the specified values.

Programming sensitivity might cause a small change in  $V_{QVO}/V_{OE}$ ; as a result, Allegro recommends programming sensitivity first, then programming  $V_{QVO}/V_{OE}$ .

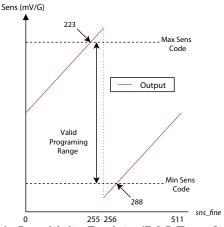

#### FINE SENSITIVITY (SNS\_FINE)

Device sensitivity can be programmed by adjusting the SNS\_FINE register. This register is a 2's complement number, meaning that the sensitivity can be programmed up or down from its nominal value at SNS\_FINE = 0. As part of final testing, the SNS\_FINE register is set by Allegro in the trimming process, so devices may already contain a nonzero SNS\_FINE value. Programing too close (<32 LSB) to the STEP<sub>SENS</sub> minimum and maximum values affects temperature performance. It is recommended that the user keep the codes from 0 to 223 and 288 to 511.

Figure 11: Sensitivity Register/DAC Transfer Curve

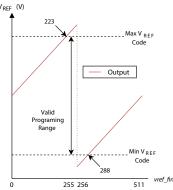

#### FINE REFERENCE VOLTAGE (VREF\_FINE)

The reference voltage, V<sub>REF</sub>, can be set two different ways. The value can be programmed internally, in which case the VREF\_FINE and VREF\_COARSE (refer to the Coarse Reference Voltage (VREF\_COARSE) section) settings determine which

voltage the device outputs on the VREF pin. The second method of setting the reference voltage is by externally overdriving the VREF pin to the desired voltage. In this case, the internal settings do not matter, because the reference is the physical voltage on the pin, not related to the internal settings. Programming too close (<32 LSB) to the STEP<sub>SENS</sub> minimum and maximum values affects temperature performance. It is recommended that the user keep the codes from 0 to 223 and 288 to 511.

Figure 12: V<sub>REF</sub> Register/DAC Transfer Curve

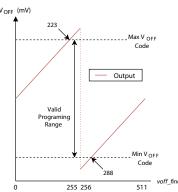

## QUIESCENT VOLTAGE OFFSET (VOVO)

The quiescent voltage output,  $V_{\rm QVO}$ , is defined as the output voltage when zero gauss is present on the device sensing element. In application, this is determined by the reference voltage ( $V_{\rm REF}$ ) and any offset voltage from the reference ( $V_{\rm OE}$ ). To eliminate this offset, VOFF\_FINE can be adjusted to remove any error. This 2's complement number allows  $V_{\rm QVO}$  to be moved up and down without affecting  $V_{\rm REF}$  to remove  $V_{\rm OE}$ . At final test, this value is set to trim for the chosen  $V_{\rm REF}$  and may need to be adjusted if  $V_{\rm REF}$  is changed or overdriven. Programming too close (<32 LSB) to the STEP\_SENS minimum and maximum values affects temperature performance. It is recommended that the user keep the codes from 0 to 223 and 288 to 511.

Figure 13: V<sub>OFF</sub> Register/DAC Transfer Curve

# VREF INPUT/OUTPUT OPERATIONAL MODES (IO\_REF\_MODE)

The VREF pin has two different operational modes. The VREF pin factory default is input/output mode; this means that the output is internally driving but is configured to be overdriven. If it is desired to change this to either a dedicated input or dedicated output, the value of IO\_REF\_MODE can be change to the corresponding value below.

| IO_REF_MODE (code)  | Mode         |

|---------------------|--------------|

| 0                   | Input only   |

| 1                   | Input only   |

| 2                   | Output only  |

| 3 (factory default) | Input/Output |

#### ECONOMY MODE (VOUT\_ECO\_MODE)

This device has an aggressive drive strength at the cost of current consumption during normal operation. If this is not desired, the VOUT\_ECO\_MODE register can be set to 1. This reduces the drive strength and quiescent current, thereby reducing the overall current consumption.

| VOUT_ECO_MODE (code) | Name    | Max. Output Drive |

|----------------------|---------|-------------------|

| 0 (factor default)   | Turbo   | 15 mA             |

| 1                    | Economy | 7.5 mA            |

# Additional Core / Temperature Compensation SENSITIVITY TEMPERATURE COMPENSATION SLOPE (GAIN\_TC)