#### **Features and Benefits**

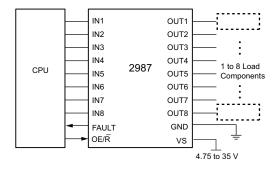

- 4.75 to 35 V driver supply voltage

- Output enable-disable (OE/R)

- 350 mA output source current

- Overcurrent protected

- Internal ground clamp diodes

- Output Breakdown Voltage 35 V minimum

- TTL, DTL, PMOS, or CMOS compatible inputs

- Internal Thermal Shutdown (TSD)

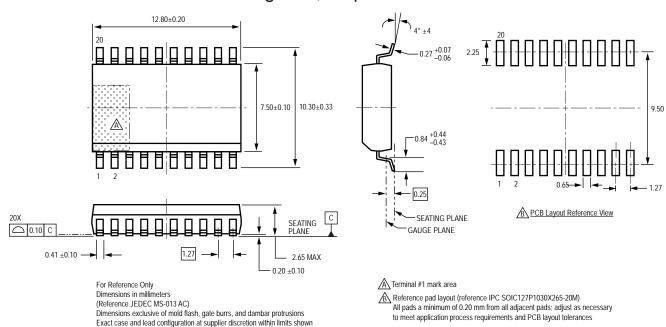

#### Package: 20-pin SOICW (suffix LW)

Not to scale

#### **Description**

Providing overcurrent protection for each of its eight sourcing outputs, the UDN2987LW-6 driver is used as an interface between standard low-level logic and relays, motors, solenoids, LEDs, and incandescent lamps. This device includes thermal shutdown and output transient protection/clamp diodes for use with sustaining voltages to 35 V.

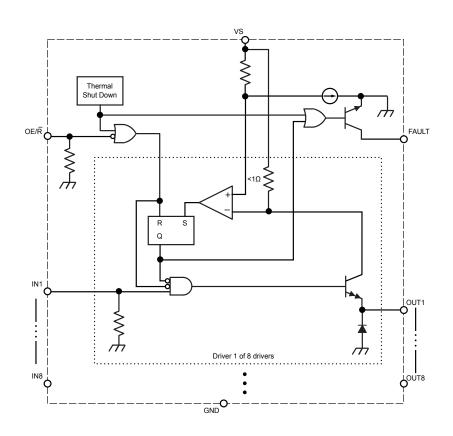

In this driver, each channel includes a latch to turn off that channel if the maximum channel current is exceeded. All channels are disabled if the thermal shutdown is activated. A common FAULT output is used to indicate either chip thermal shutdown or any overcurrent condition. All outputs are enabled by pulling the common OE/R input high. When OE/ $\overline{R}$  is low, all outputs are inhibited and the eight latches are reset. The OE/ $\overline{R}$  function can be especially important during power-up, in preventing floating inputs from turning on the outputs.

Under normal operating conditions, each of eight outputs will source in excess of 100 mA continuously at an ambient temperature of 25°C and a supply of 35 V. The overcurrent fault circuit will protect the device from short-circuits to ground with supply voltages of up to 30 V.

Continued on the next page...

### **Typical Application**

## UDN2987x-6

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

#### **Description (continued)**

The inputs are compatible with 5 and 12 V logic systems: TTL, Schottky TTL, DTL, PMOS, and CMOS. In all cases, the output is switched ON by an active high input level. Compared to predecessor devices, the UDN2987LW-6 has a significantly faster  $T_{PHL}$  (200 ns typical) and a lower driver supply voltage rating (4.75 V), which allows the use of 5 V logic.

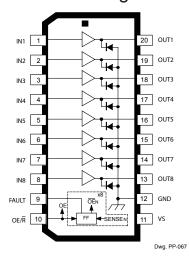

The UDN2987LW-6 is supplied in a 20-lead small-outline (SOIC-W) plastic package. All packages are lead (Pb) free, with 100% mattetin leadframe plating.

#### **Selection Guide**

| Part Number     | Packing                 | Package                |

|-----------------|-------------------------|------------------------|

| UDN2987LWTR-6-T | 1000 pieces/13-in. reel | 20-pin SOIC, wide body |

#### **Absolute Maximum Ratings**

| Parameter                   | Symbol           | Notes                                         | Rating     | Units |

|-----------------------------|------------------|-----------------------------------------------|------------|-------|

| Supply Voltage              | V <sub>S</sub>   |                                               | 35         | V     |

| Continuous Output Current*  | I <sub>OUT</sub> | Outputs are disabled at approximately –500 mA | -500       | mA    |

| FAULT Output Voltage        | V <sub>CE</sub>  |                                               | 35         | V     |

| FAULT Output Current        | I <sub>C</sub>   |                                               | 30         | mA    |

| Input Voltage               | V <sub>IN</sub>  |                                               | -0.3 to 14 | V     |

| Junction Temperature        | T <sub>J</sub>   |                                               | 150        | °C    |

| Storage Temperature Range   | T <sub>S</sub>   | Range N                                       | -55 to 150 | °C    |

| Operating Temperature Range | T <sub>A</sub>   |                                               | -20 to 85  | °C    |

<sup>\*</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

## Functional Block Diagram

# Pin-Out Diagram

#### **Terminal List Table**

| Number | Name  | Description                             |  |

|--------|-------|-----------------------------------------|--|

| 1      | IN1   | Logic input 1                           |  |

| 2      | IN2   | Logic input 2                           |  |

| 3      | IN3   | Logic input 3                           |  |

| 4      | IN4   | Logic input 4                           |  |

| 5      | IN5   | Logic input 5                           |  |

| 6      | IN6   | Logic input 6                           |  |

| 7      | IN7   | Logic input 7                           |  |

| 8      | IN8   | Logic input 8                           |  |

| 9      | FAULT | Fault output                            |  |

| 10     | OE/R  | Logic input for Output Enable and Reset |  |

| 11     | VS    | Supply voltage                          |  |

| 12     | GND   | Supply ground                           |  |

| 13     | OUT8  | Output 8 to load                        |  |

| 14     | OUT7  | Output 7 to load                        |  |

| 15     | OUT6  | Output 6 to load                        |  |

| 16     | OUT5  | Output 5 to load                        |  |

| 17     | OUT4  | Output 4 to load                        |  |

| 18     | OUT3  | Output 3 to load                        |  |

| 19     | OUT2  | Output 2 to load                        |  |

| 20     | OUT1  | Output 1 to load                        |  |

Allegro MicroSystems, LLC

# UDN2987x-6

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

#### ELECTRICAL CHARACTERISTICS, valid at $T_A = 25$ °C, $V_{OER} = 2.4$ V, $V_S = 35$ V, unless otherwise noted

| Characteristic                           | Symbol                | Test Conditions                                                      | Min.  | Typ.1 | Max.  | Units |

|------------------------------------------|-----------------------|----------------------------------------------------------------------|-------|-------|-------|-------|

| Supply Voltage Functional Range          | V <sub>S</sub>        |                                                                      | 4.75  | _     | 35    | V     |

| Output Leakage Current <sup>2</sup>      | I <sub>OUTCEX</sub>   | V <sub>IN</sub> = 0.4 V, all inputs simultaneously                   | - 200 | <-5.0 | _     | μA    |

| Output Sustaining Voltage                | V <sub>OUT(sus)</sub> | I <sub>OUT</sub> = –350 mA, L = 2.0 mH                               | 35    | _     | _     | V     |

|                                          |                       | V <sub>IN</sub> = 2.4 V, I <sub>OUT</sub> = -100 mA                  | _     | 1.6   | 1.8   | V     |

| Output Saturation Voltage                | V <sub>OUT(SAT)</sub> | V <sub>IN</sub> = 2.4 V, I <sub>OUT</sub> = -225 mA                  | _     | 1.7   | 1.9   | V     |

|                                          |                       | V <sub>IN</sub> = 2.4 V, I <sub>OUT</sub> = -350 mA                  | _     | 1.8   | 2.0   | V     |

| Channel Shut Down Threshold <sup>2</sup> | I <sub>M</sub>        | V <sub>IN</sub> = 2.4 V, V <sub>S</sub> = 30 V                       | _     | -500  | - 370 | mA    |

| FAULT Leakage Current                    | I <sub>CEX</sub>      | V <sub>CC</sub> = 35 V                                               | _     | <1.0  | 100   | μA    |

| FAULT Saturation Voltage                 | V <sub>CE(SAT)</sub>  | I <sub>C</sub> = 30 mA                                               | _     | 0.3   | 0.8   | V     |

| Innut Valtage                            | V <sub>IN(ON)</sub>   |                                                                      | 2.4   | _     | _     | V     |

| Input Voltage                            | V <sub>IN(OFF)</sub>  |                                                                      | _     | _     | 0.4   | V     |

|                                          |                       | V <sub>IN</sub> = 2.4 V                                              | _     | _     | 100   | μA    |

| Input Current: INx, OE/R pins            | I <sub>IN(ON)</sub>   | V <sub>IN</sub> = 5.0 V                                              | _     | _     | 600   | μA    |

|                                          |                       | V <sub>IN</sub> = 12 V                                               | _     | _     | 1000  | μA    |

|                                          | I <sub>IN(OFF)</sub>  | V <sub>IN</sub> = 0.4 V                                              | _     | _     | 15    | μA    |

| Clamp Diode Leakage Current              | I <sub>R</sub>        | V <sub>R</sub> = 35 V, T <sub>A</sub> = 70°C                         | _     | _     | 50    | μA    |

| Clamp Diode Forward Voltage              | V <sub>F</sub>        | I <sub>F</sub> = 350 mA                                              | _     | 1.5   | 1.8   | V     |

| 0 10 1                                   | I <sub>S(ON)</sub>    | V <sub>IN</sub> = 2.4 V, all inputs simultaneously; outputs open     | _     | 7.0   | 18    | mA    |

| Supply Current I <sub>S(OFF)</sub>       |                       | V <sub>IN</sub> = 0.4 V, all inputs simultaneously                   | _     | 6.0   | 12    | mA    |

| Thermal Shut Down                        | T <sub>JTSD</sub>     |                                                                      | _     | 165   | _     | °C    |

| Thermal Hysteresis                       | T <sub>JTSDhys</sub>  |                                                                      | _     | 15    | _     | °C    |

| Reset Pulse Duration                     | t <sub>RPD</sub>      |                                                                      | 1.0   | _     | _     | μs    |

| Propagation Delay Time                   | t <sub>PLH</sub>      | $V_S = 35 \text{ V}, R_L = 100 \Omega, C_{LOAD} = 30 \text{ pF}$     | _     | 100   | 600   | ns    |

|                                          | t <sub>PHL</sub>      | $V_{S} = 35 \text{ V}, R_{L} = 100 \Omega, C_{LOAD} = 30 \text{ pF}$ | _     | 200   | 1000  | ns    |

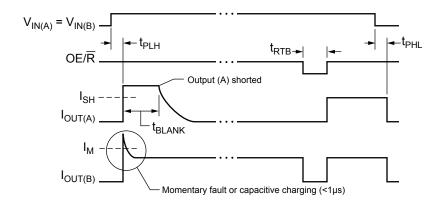

| Blank Time                               | t <sub>BLANK</sub>    |                                                                      |       | 1.0   | _     | μs    |

<sup>&</sup>lt;sup>1</sup>Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions. Performance may vary for individual units, within the specified maximum and minimum limits.

<sup>&</sup>lt;sup>2</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

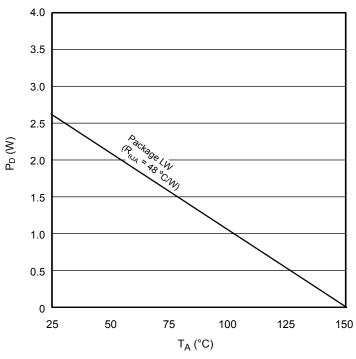

#### THERMAL CHARACTERISTICS

| Characteristics             | Symbol          | Test Conditions                                      | Rating | Unit |

|-----------------------------|-----------------|------------------------------------------------------|--------|------|

| Package Thermal Resistance* | $R_{\theta JA}$ | Package LW, on 4-layer board based on JEDEC standard | 48     | °C/W |

<sup>\*</sup>Additional thermal information is available on the Allegro Web site.

#### **Power Dissipation versus Ambient Temperature**

#### Characteristic Performance

### **Output Current Waveshapes**

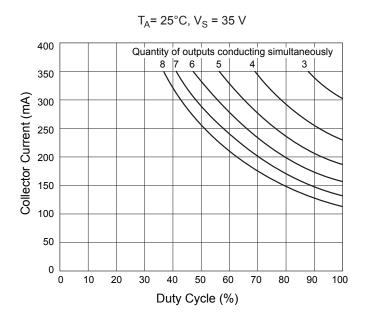

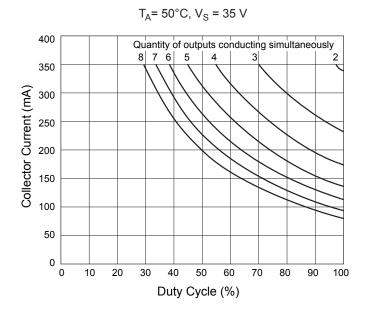

### **Allowable Output Current as a Function of Duty Cycle**

(Multiply by 78% for UDN2987LW-6)

### Applications Information and Circuit Description

As with all power integrated circuits, the UDN2987LW-6 has a maximum allowable output current rating. The 500 mA rating does not imply that operation at that value is permitted or even obtainable. The channel output current trip point is specified as –370 mA, minimum; therefore, attempted operation at current levels greater than –370 mA may cause a fault indication and channel shutdown. The device is tested at a maximum of –350 mA and that is the recommended maximum output current per driver. It provides protection for current overloads or shorted loads up to 30 V.

All outputs are enabled by pulling the  $OE/\overline{R}$  input high. When  $OE/\overline{R}$  is low or allowed to float (internal pull-down), all outputs are inhibited and the latches are reset. Note that the reset pulse duration ( $OE/\overline{R}$  low) should be at least 1  $\mu s$ . This will ensure safe operation under attempted reset conditions with a shorted load. The latches are also reset during power-up, regardless of the state of the  $OE/\overline{R}$  input.

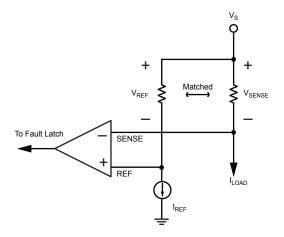

The load current causes a small voltage drop across the internal low-value sense resistor. This voltage is com-

pared to the voltage drop across a reference resistor with a constant current. The two resistors are matched to eliminate errors due to manufacturing tolerances or temperature effects. Each channel includes a comparator and its own latch. An overcurrent fault ( $V_{\text{SENSE}} > V_{\text{REF}}$ ) will set the affected latch and shut down only that channel. All other channels will continue to operate normally. The latch includes a 1  $\mu$ s blanking delay,  $t_{\text{BLANK}}$ , to prevent unwanted triggering due to crossover currents generated when switching inductive loads. For an abrupt short circuit, the blanking and output switching times will allow a brief, permissible current in excess of the trip current before the output driver is turned off.

A common thermal shutdown disables all outputs if the chip temperature exceeds 165°C. At thermal shutdown, all latches are reset. The outputs are disabled until the chip cools down to approximately 150°C (thermal hysteresis).

In the event of an overcurrent condition on any channel, or chip thermal shutdown, the FAULT open-collector output is pulled low (turned on).

#### **Overcurrent Fault Sense Circuit**

1.508.853.5000: www.allegromicro.com

## Package LW, 20-pin SOIC-W

8

## UDN2987x-6

# DABIC-5 8-Channel Source Driver with Overcurrent Protection

#### **Revision History**

| Revision | Revision Date  | Description of Revision     |

|----------|----------------|-----------------------------|

| Rev. 6   | April 30, 2012 | Update product availability |

|          |                |                             |

Copyright ©2006-2013, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LED Lighting Drivers category:

Click to view products by Allegro manufacturer:

Other Similar products are found below:

LV5235V-MPB-H MB39C602PNF-G-JNEFE1 FAN5701UMP20X FAN5702UMP30X MIC2871YMK-T5 MP1518DJ-LF-P MP3202DG-LF-P MP3304BDD-LF-P MP3306EG-LF-P MP3398AGY MP4033GK AL1676-10BS7-13 AL1676-20AS7-13 MX877RTR

NCL30085BDR2G ICL8201 IS31BL3506B-TTLS2-TR PAM2841GR A8519KLPTR-T FAN5701UMP08X FAN5702UMP20X AL3157F-7 AL8807BQMP-13 LV52204MTTBG MP2488DN-LF MP24893DQ-LF-P MP24894GJ-P MP24895GJ-P MP3308DL-LF-Z MP3393EF-LF MP3394SGF MP3802DQ-LF-P MP4008GS MP4031GS MP4032-1GS MP4034GS MP46885DN-LF SLG7NT4082V SLG7NT4082VTR PCA9955BTWQ900J TLD5095EL LED6001TR STP4CMPQTR BD1604MVV-E2 MC10SX1130DG MAX16832CASAT MAX16814CATP+ NCL30086BDR2G NCL30088BDR2G IS31LT3350-V1SDLS2-EB3CH