### Datasheet

DS000507

### Low Noise ANC Solution

v4-00 • 2020-Jan-23

## **Content Guide**

| 1                 | General Description                                      | 3  |

|-------------------|----------------------------------------------------------|----|

| 1.1<br>1.2<br>1.3 | Key Benefits & Features<br>Applications<br>Block Diagram | 4  |

| 2                 | Ordering Information                                     | 5  |

| 3                 | Pin Assignment                                           | 6  |

| 3.1<br>3.2        | Pin Diagram<br>Pin Description                           |    |

| 4                 | Absolute Maximum Ratings                                 | 9  |

| -                 | Electrical Characteristics                               | 10 |

| 5                 |                                                          | 10 |

| ວ<br>6            | Functional Description                                   |    |

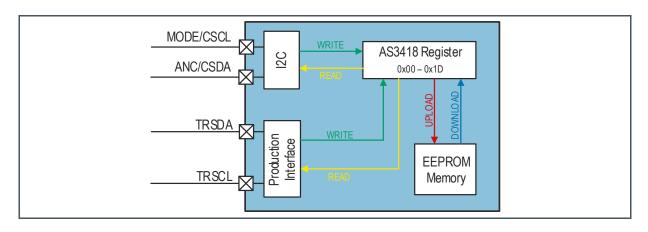

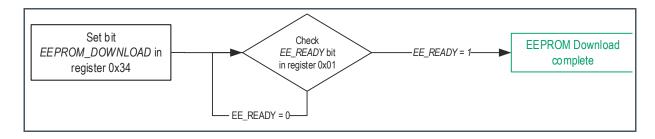

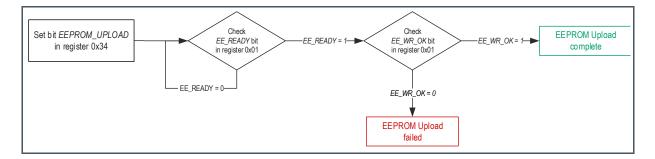

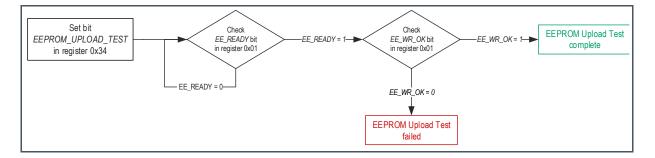

| 6.8<br>6.9<br>6.10<br>6.11<br>6.12 | Operation Modes<br>V <sub>NEG</sub> Charge Pump<br>EEPROM<br>Production Trimming Interface<br>I <sup>2</sup> C Interface | . 38<br>. 39<br>. 41 |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|

| 7                                  | Register Description                                                                                                     | 47                   |

| 7.1<br>7.2                         | Register Overview<br>Detailed Register Description                                                                       |                      |

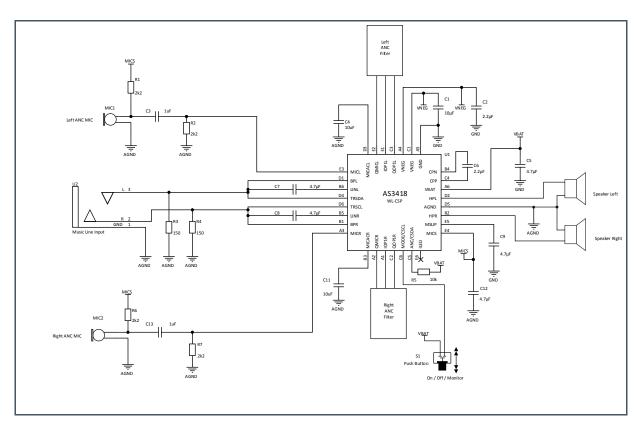

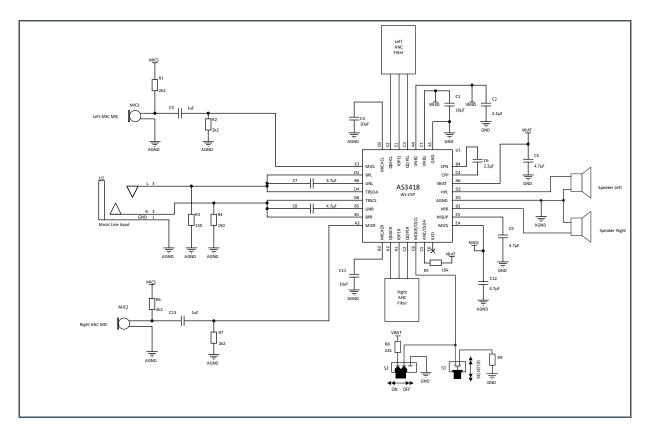

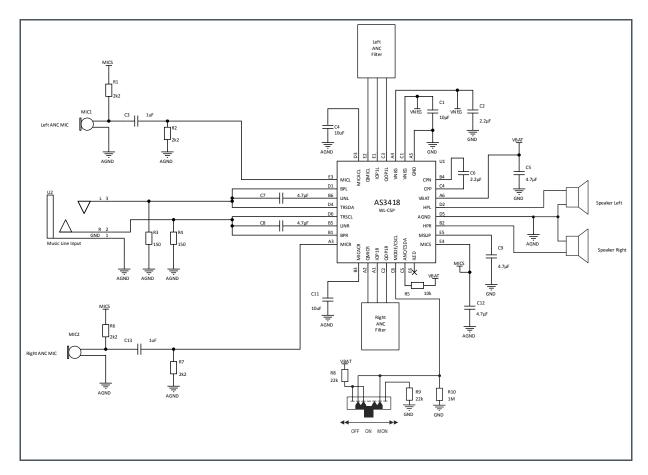

| 8                                  | Application Information                                                                                                  | 70                   |

| 8.1<br>8.2                         | Schematic<br>External Components                                                                                         |                      |

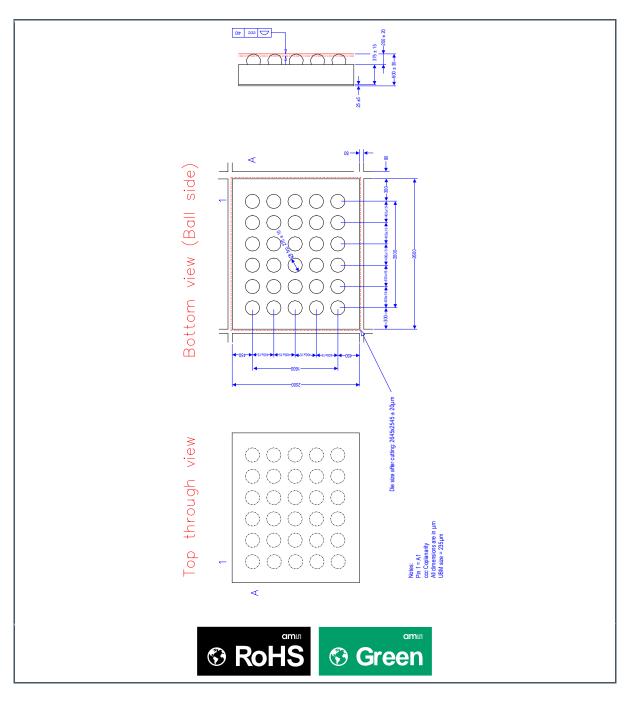

| 9                                  | Package Drawings & Markings                                                                                              | 74                   |

| 10                                 | Revision Information                                                                                                     | 76                   |

| 11                                 | Legal Information                                                                                                        | 77                   |

## **1** General Description

The AS3418 speaker driver with Ambient Noise Cancelling function for headsets, headphones or ear pieces. They are intended to improve quality of e.g. music listening, a phone conversation etc. by reducing background ambient noise.

The fully analog implementation allows the lowest power consumption, lowest system BOM cost and most natural received voice enhancement otherwise difficult to achieve with DSP implementations. The device is designed to be easily applied to existing architectures.

An internal EEPROM can be optionally used to store the microphones gain calibration settings. The AS3418 can be used in different configurations for best trade-off of noise cancellation, required filtering functions and mechanical designs.

The AS3418 targeting feed-forward topology is used to effectively reduce frequencies typically up to 2-3 kHz. The typical bandwidth for a feed-forward system is from 20Hz up to 3 kHz which is lower than the feed-forward systems.

The filter loop for the system is determined by measurements, for each specific headset individually, and depends very much on mechanical designs. The gain and phase compensation filter network is implemented with cheap resistors and capacitors for lowest system costs.

### 1.1 Key Benefits & Features

The benefits and features of AS3418, Low Noise ANC Solution, are listed below:

Figure 1: Added Value of Using AS3418

| Benefits                       | Features                                            |

|--------------------------------|-----------------------------------------------------|

| Low Noise Floor                | Low Noise Amplifiers                                |

| Integrated Music Bypass Switch | Depletion mode transistors for passive music bypass |

| Smallest ANC form factor       | WL-CSP package 2.645mm x 2.545mm; 0.4mm pitch       |

| Reprogrammable ANC settings    | EEPROM Memory for system settings                   |

### 1.2 Applications

- Ear Pieces

- Headsets

- Hands-Free Kits

- Mobile Phones

- Voice Communicating Devices

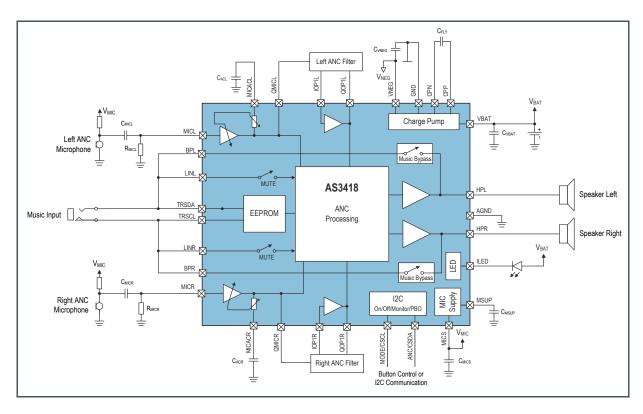

### 1.3 Block Diagram

The functional blocks of this device are shown below:

#### Figure 2 : Functional Blocks of AS3418

## **2** Ordering Information

| Ordering Code | Package | Marking | Delivery Form | Delivery Quantity |

|---------------|---------|---------|---------------|-------------------|

| AS3418-EWLT   | WL-CSP  | AS3418  | Tape & Reel   | 6500 pcs/reel     |

| AS3418-EWLM   | WL-CSP  | AS3418  | Tape & Reel   | 500 pcs/reel      |

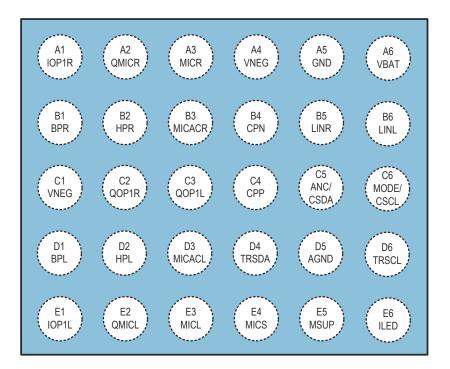

## 3 Pin Assignment

### 3.1 Pin Diagram

Figure 3 : Pin Assignment AS3418

### 3.2 Pin Description

#### Figure 4:

Pin Description of AS3418

| Pin Number | Pin Name | Pin Type <sup>(1)</sup> | Description                                                                                                                                          |  |  |  |  |

|------------|----------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A1         | IOP1R    | ANA IN                  | ANC filter OPAMP1 input - right channel.                                                                                                             |  |  |  |  |

| A2         | QMICR    | ANA OUT                 | ANC microphone preamplifier output - right channe                                                                                                    |  |  |  |  |

| A3         | MICR     | ANA IN                  | ANC microphone preamplifier input - right channel.                                                                                                   |  |  |  |  |

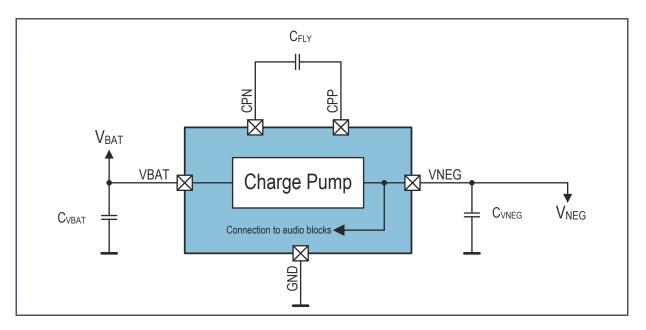

| A4         | VNEG     | SUP OUT                 | V <sub>NEG</sub> charge pump output terminal. This output provides the negative amplifier supply voltage for all OPAMPs and the headphone amplifier. |  |  |  |  |

| Pin Number | Pin Name      | Pin Type <sup>(1)</sup> | Description                                                                                                                                                                  |

|------------|---------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A5         | GND           | ANA IN                  | V <sub>NEG</sub> charge pump ground terminal.                                                                                                                                |

| A6         | VBAT          | SUP IN                  | Positive supply terminal of AS3418.                                                                                                                                          |

| B1         | BPR           | ANA IN                  | Right audio bypass switch input. This pin features a music bypass function for the right audio channel in off mode operation in order to replace and external analog switch. |

| B2         | HPR           | ANA OUT                 | Headphone amplifier output - right channel.                                                                                                                                  |

| B3         | MICACR        | ANA OUT                 | Microphone preamplifier AC coupling ground terminal. This pin requires a typ. 10µF capacitor connected to AGND pin.                                                          |

| B4         | CPN           | ANA OUT                 | V <sub>NEG</sub> charge pump negative terminal for flying capacitor                                                                                                          |

| B5         | LINR          | ANA IN                  | Line input - right channel.                                                                                                                                                  |

| B6         | LINL          | ANA IN                  | Line input - left channel.                                                                                                                                                   |

| C1         | VNEG          | SUP OUT                 | V <sub>NEG</sub> charge pump output terminal. This output provides the negative amplifier supply voltage for all OPAMPs and the headphone amplifier.                         |

| C2         | QOP1R         | ANA OUT                 | ANC filter OPAMP1 output - right channel                                                                                                                                     |

| C3         | QOP1L         | ANA OUT                 | ANC filter OPAMP1 output - left channel                                                                                                                                      |

| C4         | CPP           | ANA OUT                 | V <sub>NEG</sub> charge pump positive terminal for flying capacitor                                                                                                          |

| C5         | ANC/<br>CSDA  | DIG IN/OUT              | Serial interface data signal line for I <sup>2</sup> C interface and alternatively ANC control to enable/disable ANC.                                                        |

| C6         | MODE/<br>CSCL | DIG IN                  | Serial Interface clock signal line for I <sup>2</sup> C interface and alternatively control pin for power up/down and Monitor mode.                                          |

| D1         | BPL           | ANA IN                  | Left audio bypass switch input. This pin features a music bypass function for the left audio channel in off mode operation in order to replace and external analog switch.   |

| D2         | HPL           | ANA OUT                 | Headphone amplifier output - left channel.                                                                                                                                   |

| D3         | MICACL        | ANA OUT                 | Microphone preamplifier AC coupling ground terminal. This pin requires a typ. 10µF capacitor connected to AGND pin.                                                          |

| D4         | TRSDA         | ANA IN                  | Data input for production trimming. Can be connected to LINL pin to enable production trimming via 3.5mm audio jack.                                                         |

| D5         | AGND          | ANA IN                  | Analog reference ground. Do not connect this pin to power or digital ground plane.                                                                                           |

| D6         | TRSCL         | ANA IN                  | Clock input for production trimming. Can be connected to LINR pin to enable production trimming via 3.5mm audio jack.                                                        |

| E1         | IOP1L         | ANA IN                  | ANC filter OPAMP1 input - left channel                                                                                                                                       |

|            |               |                         |                                                                                                                                                                              |

| Pin Number | Pin Name | Pin Type <sup>(1)</sup> | Description                                                                                                                                                                                                                                                           |

|------------|----------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E2         | QMICL    | ANA OUT                 | ANC microphone preamplifier output - left channel                                                                                                                                                                                                                     |

| E3         | MICL     | ANA IN                  | ANC microphone preamplifier input - left channel                                                                                                                                                                                                                      |

| E4         | MICS     | SUP OUT                 | Microphone Supply output to source analog ECM via a bias resistor or MEMs microphones. This pin needs an output blocking capacitor with $4.7\mu$ F.                                                                                                                   |

| E5         | MSUP     | SUP IN/OUT              | In default configuration a charge pump output that<br>provides the power for the low noise microphone<br>supply LDO. The internal charge pump can also be<br>disabled the MSUP serves as a supply input<br>terminal to source the low noise microphone supply<br>LDO. |

| E6         | ILED     | ANA IN                  | Current sink input for on-indication LED. The<br>Cathode of an LED can be directly connected to this<br>terminal without the need of an external current<br>limitation resistor.                                                                                      |

| ) | Explanation of apprev | lations.                          |

|---|-----------------------|-----------------------------------|

|   | ANA IN                | Analog Input                      |

|   | ANA OUT               | Analog Output                     |

|   | DIG IN                | Digital Input                     |

|   | SUP IN/OUT            | Supply input or supply output pad |

|   | SUP IN                | Supply input terminal             |

|   | SUP OUT               | Supply output terminal            |

|   |                       |                                   |

### 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Figure 5

**Absolute Maximum Ratings of AS3418**

| Symbol                         | Parameter                              | Min Max Unit               |                        | Comments                                         |                                                                                                                                             |

|--------------------------------|----------------------------------------|----------------------------|------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Pa                  | arameters                              |                            |                        |                                                  |                                                                                                                                             |

| $V_{\text{SUP}\_\text{MAX}}$   | Supply Voltage to Ground               | -0.5                       | 2                      | V                                                | Applicable for pin VBAT                                                                                                                     |

| $V_{\text{GND}\_\text{MAX}}$   | Ground Terminals                       | -0.5                       | +0.5                   | V                                                | Applicable for pin AGND and GND                                                                                                             |

| $V_{NEG\_MAX}$                 | Negative Terminals                     | -2.0                       | 0.5                    | V                                                | Applicable for pin VNEG                                                                                                                     |

| $V_{\text{CP}\_\text{MAX}}$    | Charge Pump Terminals                  | V <sub>NEG</sub> - 0.5     | V <sub>POS</sub> + 0.5 | V                                                | Applicable for pins CPN and CPP                                                                                                             |

| $V_{\text{HP}\_\text{MAX}}$    | Headphone Pins                         | V <sub>NEG</sub> - 0.5     | V <sub>POS</sub> + 0.5 | V                                                | Applicable for pins HPR and HPL                                                                                                             |

| Vana_max                       | Analog Pins                            | V <sub>NEG</sub> - 0.5     | V <sub>POS</sub> + 0.5 | V                                                | Applicable for pins LINL,<br>LINR, MICL/R, HPR, HPL,<br>QMICL/R, IOP1x, QOP1x,<br>CPP, CPN, TRSCL, BPR,<br>TRSDA, BPL, MICACL<br>and MICACR |

| $V_{\text{CON}\_\text{MAX}}$   | Control Pins                           | V <sub>NEG</sub> - 0.5 5 V |                        | Applicable for pins<br>ANC/CSDA and<br>MODE/CSCL |                                                                                                                                             |

| $V_{\text{OTHER}\_\text{MAX}}$ | Other Pins                             | V <sub>NEG</sub> - 0.5     | 5                      | V                                                | Applicable for pins MICS and MICFB                                                                                                          |

| I <sub>SCR</sub>               | Input Current (latch-up immunity)      | ±                          | : 100                  | mA                                               | Class II JEDEC JESD78D                                                                                                                      |

| Electrostatio                  | c Discharge                            |                            |                        |                                                  |                                                                                                                                             |

| ESD <sub>HBM</sub>             | Electrostatic Discharge HBM            | ±                          | 2000                   | V                                                | Norm: JS-001-2014                                                                                                                           |

| Temperature                    | e Ranges and Storage Conditions        |                            |                        |                                                  |                                                                                                                                             |

| TJ                             | Operating Junction Temperature         |                            | 85                     | °C                                               |                                                                                                                                             |

| T <sub>STRG</sub>              | Storage Temperature Range              | - 55                       | 125                    | °C                                               |                                                                                                                                             |

| T <sub>BODY</sub>              | Package Body Temperature               |                            | 260                    | °C                                               | IPC/JEDEC J-STD-020 <sup>(1)</sup>                                                                                                          |

| RH <sub>NC</sub>               | Relative Humidity (non-<br>condensing) | 5                          | 85                     | %                                                |                                                                                                                                             |

| MSL                            | Moisture Sensitivity Level             |                            | 1                      |                                                  | Unlimited floor lifetime                                                                                                                    |

|                                |                                        |                            |                        |                                                  |                                                                                                                                             |

(1) The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices." The lead finish for Pbfree leaded packages is "Matte Tin" (100% Sn)

## **5 Electrical Characteristics**

$V_{BAT} = 1.4V$  to 1.8V,  $T_A = -20^{\circ}C$  to 85°C. Typical values are at  $V_{BAT} = 1.6V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified. All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

**Electrical Characteristics of AS3418**

| Symbol               | Parameter                                  | Conditions                                                                                                      | Min                                  | Тур  | Мах                                | Unit |

|----------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------|------|------------------------------------|------|

| T <sub>A</sub>       | Ambient Temperature<br>Range               |                                                                                                                 | -20                                  |      | 85                                 | °C   |

| Supply V             | oltages                                    |                                                                                                                 |                                      |      |                                    |      |

| GND                  | Reference Ground                           |                                                                                                                 | 0                                    |      | 0                                  | V    |

| V <sub>BAT</sub>     | Battery Supply Voltage                     | Normal Operation                                                                                                | 1.4                                  | 1.6  | 1.8                                | V    |

| $V_{\text{NEG}}$     | Charge Pump Voltage                        |                                                                                                                 | -1.8                                 |      | -1.2                               | V    |

| V <sub>DELTA</sub>   | Difference of Ground<br>Supplies GND, AGND | To achieve good performance, the negative supply terminals should be connected to a low impedance ground plane. | -0.1                                 |      | 0.1                                | V    |

| Other Pins           |                                            |                                                                                                                 |                                      |      |                                    |      |

| V <sub>MICS</sub>    | Microphone Supply Voltage                  | Applicable to MICS pin                                                                                          | 0                                    |      | 3.6                                | V    |

| V <sub>ANALOG</sub>  | Analog Pins                                | MICACL, MICACR,LINR, LINL, HPR,<br>HPL, QMICL, QMICR, IOP1x, and<br>QOP1x                                       | $V_{\text{NEG}}$                     |      | $V_{BAT}$                          | V    |

| V <sub>CONTROL</sub> | Control Pins                               | Applicable to MODE/CSCL and ANC/CSDA pins                                                                       | 0                                    |      | 3.7                                | V    |

| V <sub>CP</sub>      | Charge Pump Pins                           | Applicable to CPN and CPP pins                                                                                  | $V_{NEG}$                            |      | $V_{\text{BAT}}$                   | V    |

| V <sub>trim</sub>    | Application Trim Pins                      | Applicable to TRSCL and TRSDA pins                                                                              | V <sub>NEG</sub> -<br>0.3<br>or -1.8 |      | V <sub>BAT</sub><br>+0.5<br>or 1.8 | V    |

| V <sub>BYP</sub>     | Bypass Pins                                | Applicable to BPR and BPL pins                                                                                  | V <sub>NEG</sub> -<br>0.3<br>or -1.8 |      | V <sub>BAT</sub><br>+0.5<br>or 1.8 | V    |

| V <sub>MIC</sub>     | Microphone Inputs                          | Applicable to MICL and MICR pins.                                                                               | $V_{\text{NEG}}$                     |      | $V_{\text{BAT}}$                   | V    |

| Block Po             | wer Requirements                           |                                                                                                                 |                                      |      |                                    |      |

| I <sub>OFF</sub>     | Off mode current                           | MODE/CSCL pin low, device switched off                                                                          |                                      | 1    | 5                                  | μA   |

| 1                    |                                            | $V_{\text{BAT}}$ = 1.8V; Bias generation, oscillator, POR and $V_{\text{NEG}}$                                  |                                      | 1.45 |                                    | mA   |

| I <sub>SYS</sub>     | Reference supply current                   | $V_{\text{BAT}}$ = 1.4V; Bias generation, oscillator, POR and $V_{\text{NEG}}$                                  |                                      | 1    |                                    | mA   |

|                      |                                            | $V_{BAT}$ = 1.8V; no signal, stereo, High quality mode                                                          |                                      | 0.97 |                                    | mA   |

| I <sub>MIC</sub>     | Microphone gain stage<br>current           | $V_{BAT}$ = 1.8V; no signal, stereo, ECO mode                                                                   |                                      | 0.68 |                                    | mA   |

|                      |                                            | $V_{BAT} = 1.4V$ ; no signal, stereo, High quality mode                                                         |                                      | 0.92 |                                    | mA   |

Figure 6:

| Symbol                                             | Parameter                                                                                              | Conditions                                                                                                    | Min  | Тур  | Max | Unit |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|-----|------|

|                                                    |                                                                                                        | V <sub>BAT</sub> = 1.4V; no signal, stereo, ECO<br>mode                                                       |      | 0.63 |     | mA   |

|                                                    |                                                                                                        | V <sub>BAT</sub> = 1.8V; no signal, high quality mode                                                         |      | 2.9  |     | mA   |

|                                                    | Llaadabaaa ataga gurraat                                                                               | V <sub>BAT</sub> = 1.8V; no signal, ECO mode                                                                  |      | 2.4  |     | mA   |

| I <sub>HP</sub>                                    | Headphone stage current                                                                                | $V_{BAT} = 1.4V$ ; no signal, high quality mode                                                               |      | 2.78 |     | mA   |

|                                                    |                                                                                                        | V <sub>BAT</sub> = 1.4V; no signal, ECO mode                                                                  |      | 2.32 |     | mA   |

|                                                    |                                                                                                        | $V_{BAT}$ = 1.8V; OP1L and OP1R enabled,<br>High quality mode                                                 |      | 1    |     | mA   |

|                                                    |                                                                                                        | $V_{BAT}$ = 1.8V; OP1L and OP1R enabled, ECO mode                                                             |      | 0.7  |     | mA   |

| I <sub>OP1</sub>                                   | ANC Filter OPAMP current                                                                               | $V_{BAT}$ = 1.8V; OP1L and OP1R enabled,<br>High quality mode                                                 |      | 0.95 |     | mA   |

|                                                    |                                                                                                        | V <sub>BAT</sub> = 1.8V; OP1L and OP1R enabled,<br>ECO mode                                                   |      | 0.65 |     | mA   |

|                                                    | Microphone low noise LDO                                                                               | V <sub>BAT</sub> = 1.8V; no load; high quality mode                                                           |      | 0.69 |     | mA   |

|                                                    |                                                                                                        | $V_{BAT}$ = 1.4V; no load; high quality mode                                                                  |      | 0.67 |     | mA   |

| I <sub>MICS</sub>                                  | supply current                                                                                         | V <sub>BAT</sub> = 1.8V; no load; ECO mode                                                                    |      | 0.33 |     | mA   |

|                                                    |                                                                                                        | $V_{BAT} = 1.4V$ ; no load; ECO mode                                                                          |      | 0.32 |     | mA   |

|                                                    | Microphone supply charge                                                                               | V <sub>BAT</sub> = 1.8V; no load                                                                              |      | 0.3  |     | mA   |

| I <sub>MICS_CP</sub>                               | pump current                                                                                           | $V_{BAT} = 1.4V$ ; no load                                                                                    |      | 0.26 |     | mA   |

| Typical S                                          | System Power Consump                                                                                   | tion                                                                                                          |      |      |     |      |

|                                                    | Typical power consumption feed forward application in                                                  | V <sub>BAT</sub> = 1.8V; OP1L, OP1R enabled,<br>250µA microphone load; all amplifiers in<br>high quality mode |      | 15   |     | mW   |

| P <sub>FF</sub> high quality mode<br>configuration | $V_{BAT}$ = 1.4V; OP1L, OP1R enabled,<br>250µA microphone load; all amplifiers in<br>high quality mode |                                                                                                               | 10.7 |      | mW  |      |

| D                                                  | Typical power consumption                                                                              | V <sub>BAT</sub> = 1.8V; OP1L, OP1R enabled,<br>250µA microphone load; all amplifiers in<br>ECO mode          |      | 12.4 |     | mW   |

| P <sub>FF_ECO</sub>                                | feed forward application in ECO mode configuration                                                     | V <sub>BAT</sub> = 1.4V; OP1L, OP1R enabled,<br>250µA microphone load; all amplifiers in<br>ECO mode          |      | 8.8  |     | mW   |

### 6 Functional Description

This section provides a detailed description of the device related components.

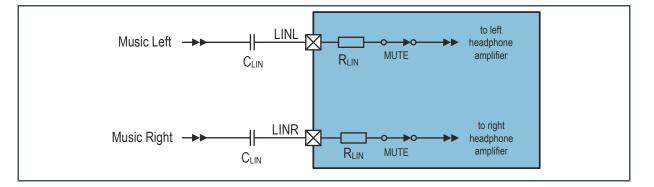

### 6.1 Audio Line Input

The chip features one stereo line input for music playback. In monitor mode the line inputs can also be muted in order to interrupt the music playback and increase speech intelligibility.

Figure 7: Stereo Line Input

If there is a high pass function desired in an application, to block very low frequencies that could harm the speaker or eliminate little offset voltages, a series capacitor  $C_{LIN}$  can support this function. The implementation is shown in Figure 7. The correct capacitor value for the desired cut-off frequency can be calculated with the following formula:

Equation 1:

$$C_{LIN} = \frac{1}{2 * \pi * R_{LIN} * f_{cut-off}}$$

A typical cut-off frequency in an audio application is 20Hz. With an input impedance RLIN of typ.  $1k\Omega$  and a desired cut off frequency of 20Hz the input capacitor should be bigger than  $8\mu$ F. Therefore a typical value of  $10\mu$ F is recommended.

#### 6.1.1 Parameter

$V_{BAT}$ =1.65V,  $T_{A}$ = 25°C unless otherwise specified.

#### Figure 8:

Parameter of Line Input

| Symbol           | Parameter          | Conditions | Min | Тур                       | Max       | Unit  |

|------------------|--------------------|------------|-----|---------------------------|-----------|-------|

| V <sub>LIN</sub> | Input Signal Level |            |     | V <sub>BAT</sub> *<br>0.9 | $V_{BAT}$ | Vpeak |

| RLIN             | Input Impedance    |            |     | 1                         |           | kΩ    |

| Amute            | Mute Attenuation   |            | 100 |                           |           | dB    |

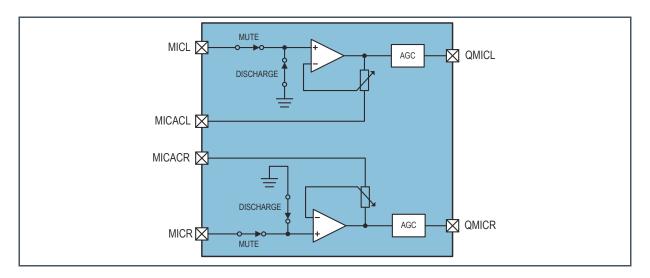

### 6.2 Microphone Inputs

The AS3418 offers two low noise microphone inputs with full digital control and a dedicated DC offset cancellation pin for each microphone input. In total each gain stage offers up to 63 gain steps of 0.5dB resulting in a gain range from 0dB to +31dB. The microphone gain is stored digitally during production, in an EEPROM memory on the ANC chip. Besides the standard microphone gain register for left and right channel, the chip features also four additional microphone gain registers for Monitor- and Playback Only operation mode. Thus, in Monitor/Playback Only mode, a completely different gain setting for left and right microphone can be selected to implement voice filter functions in order to amplify the speech band for better intelligibility.

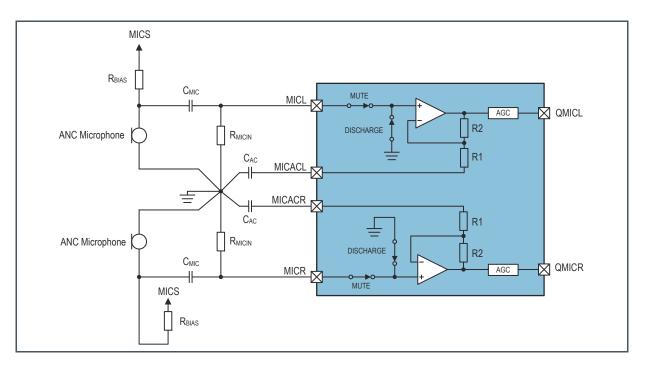

#### Figure 9: Stereo Microphone Inputs

To avoid unwanted start-up pop noise, a soft-start function is implemented for an automatic gain ramping of the device. In case of an overload condition on the microphone input (e.g. high sound pressure level) there is also an automatic gain control (AGC) function available which reduces the gain to a moderate level. For some designs it might be useful to switch off this feature. Especially in feedback systems infrasound can cause an overload condition of the microphone preamplifier that results in low frequency noise which can be avoided by disabling the AGC.

#### 6.2.1 Input Capacitor Selection

The microphone preamplifier needs a bias resistor ( $R_{Bias}$ ) per channel as well as DC blocking capacitors ( $C_{MIC}$ ). The capacitors  $C_{AC}$  are DC blocking capacitors to avoid DC amplification of the non-inverting microphone preamplifier. This capacitor has an influence on the frequency response because the internal feedback resistors create a high pass filter. The typical application circuit is shown in Figure 10 with all necessary components.

#### Figure 10:

**Microphone Capacitor Selection Circuit**

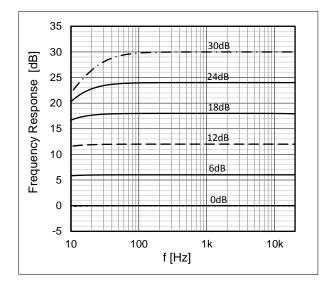

The corner frequency of this high pass filter is defined with the capacitor  $C_{AC}$  and the gain of the headphone amplifier. Figure 11 shows an overview of typical cut-off frequencies with different microphone gain settings.

#### Figure 11:

**Microphone Cut-Off Frequency Overview**

| Microphone Gain | R <sub>1</sub> | R <sub>2</sub> | f <sub>cut-off</sub> |

|-----------------|----------------|----------------|----------------------|

| 0dB             | 22.2kΩ         | 00             | 1.7Hz                |

| 3dB             | 15716Ω         | 6484Ω          | 1.9Hz                |

| 6dB             | 11126Ω         | 11074Ω         | 2.2Hz                |

| 9dB             | 7877Ω          | 14323Ω         | 2.7Hz                |

| 12dB            | 5576Ω          | 16623Ω         | 3.5Hz                |

| 15dB            | 3948Ω          | 18252Ω         | 4.5Hz                |

| Microphone Gain | R <sub>1</sub> | R <sub>2</sub> | f <sub>cut-off</sub> |

|-----------------|----------------|----------------|----------------------|

| 18dB            | 2795Ω          | 19405Ω         | 6.1Hz                |

| 21dB            | 1979Ω          | 20221Ω         | 8.4Hz                |

| 24dB            | 1400Ω          | 20800Ω         | 11.5Hz               |

| 27dB            | 992Ω           | 21208Ω         | 16.3Hz               |

| 30dB            | 702Ω           | 21498Ω         | 22.7Hz               |

It is important when doing the ANC filter simulations to include all microphone filter components to incorporate the **gain and phase influence** of these components. In the cut-off frequency overview, capacitor  $C_{AC}$  was defined as  $10\mu$ F which results in a rather low cut-off frequency for best ANC filter design. If a different capacitor value is desired in the application, the following formula defines the transfer function of the high pass circuit of the microphone preamplifier:

**Equation 2:**

$$|A| = \frac{\sqrt{4 * C_{AC}^2 * f^2 * (R_1 + R_2)^2 * \pi^2 + 1}}{\sqrt{4 * C_{AC}^2 * f^2 * R_1^2 * \pi^2 + 1}}$$

The simplified transfer function does not include the high pass filter defined by CMIC and RMICIN. With the recommended values of  $2.2\mu$ F for CMIC and  $22k\Omega$  for RMICIN this filter can be neglected because of the very low cut-off frequency of 1.5Hz. The cut-off frequency for this filter can be calculated with the following formula:

Equation 3:

$$f_{cut-off} = \frac{1}{2 * \pi * R_{MICIN} * C_{MIC}}$$

The simulated frequency response for the microphone preamplifier with the recommended component values is shown in Figure 12.

#### Figure 12 : Simulated Microphone Frequency Response

In applications with PCB space limitations it is also possible to remove the capacitors C<sub>AC</sub> and connect MICACL and MICACR pins directly to AGND. In this configuration AC coupling of the QMICR and QMICL signals is recommended.

#### 6.2.2 Parameter

$V_{BAT}$ =1.8V,  $T_{A}$ = 25°C ,  $C_{AC}$ =10 $\mu$ F,  $C_{MIC}$ =4.7 $\mu$ F and  $R_{MICIN}$ =2.2k $\Omega$  unless otherwise specified.

Figure 13: Microphone Parameter

| Symbol               | Parameter                | Conditions                                    | Min | Тур  | Max | Unit              |

|----------------------|--------------------------|-----------------------------------------------|-----|------|-----|-------------------|

| VMICIN_0             | Typical maximum          | Preamplifier gain=0dB, THD < 0.1%             |     | 1050 |     | $mV_{\text{RMS}}$ |

| V <sub>MICIN_0</sub> | Input Signal Level       | Preamplifier gain=20dB, THD < 0.1%            |     | 110  |     | $mV_{RMS}$        |

|                      |                          | 0dB gain, High quality mode,<br>AGC disabled  |     | 119  |     | dB                |

|                      |                          | 10dB gain, High quality mode, AGC disabled    |     | 109  |     | dB                |

| SNR                  | Signal to Noise<br>Ratio | 20dB gain, High quality mode,<br>AGC disabled |     | 106  |     | dB                |

|                      |                          | 0dB gain, ECO mode, AGC disabled              |     | 117  |     | dB                |

|                      |                          | 10dB gain, ECO mode, AGC disabled             |     | 108  |     | dB                |

| Symbol               | Parameter            | Conditions                                                 | Min | Тур  | Max | Unit |

|----------------------|----------------------|------------------------------------------------------------|-----|------|-----|------|

|                      |                      | 20dB gain, ECO mode, AGC disabled                          |     | 105  |     | dB   |

|                      |                      | 0dB gain, 20Hz – 20kHz<br>bandwidth, high quality          |     | 1.3  |     | μV   |

|                      |                      | 10dB gain, 20Hz – 20kHz<br>bandwidth, high quality         |     | 4.5  |     | μV   |

|                      | A-weighted output    | 20dB gain, 20Hz – 20kHz<br>bandwidth, high quality         |     | 13.7 |     | μV   |

| V <sub>NOISE-A</sub> | noise floor          | 0dB gain, 20Hz – 20kHz<br>bandwidth, ECO mode              |     | 1.4  |     | μV   |

|                      |                      | 10dB gain, 20Hz – 20kHz<br>bandwidth, ECO mode             |     | 5    |     | μV   |

|                      |                      | 20dB gain, 20Hz – 20kHz<br>bandwidth, ECO mode             |     | 15.7 |     | μV   |

|                      | Block Current        | V <sub>BAT</sub> = 1.8V; no signal, stereo,<br>normal mode |     | 1    |     | mA   |

| Іміс                 |                      | V <sub>BAT</sub> = 1.8V; no signal, stereo,<br>ECO mode    |     | 0.7  |     | mA   |

| IMIC                 | Consumption          | V <sub>BAT</sub> = 1.4V; no signal, stereo,<br>normal mode |     | 0.9  |     | mA   |

|                      |                      | V <sub>BAT</sub> = 1.4V; no signal, stereo,<br>ECO mode    |     | 0.6  |     | mA   |

| Аміс                 | Programmable<br>Gain |                                                            | 0   |      | 31  | dB   |

|                      | Gain Step Size       |                                                            |     | 0.5  |     | dB   |

|                      | Gain Step Precision  |                                                            |     |      | 0.2 | dB   |

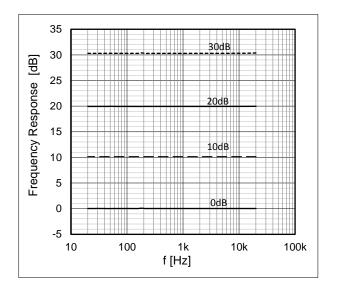

#### Figure 14 : Microphone Frequency Response (MICACx grounded; C<sub>MIC</sub>=10µF)

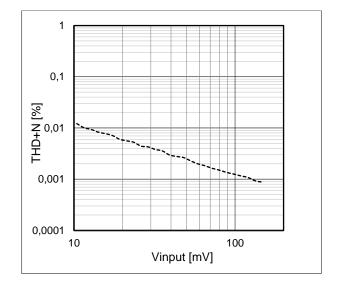

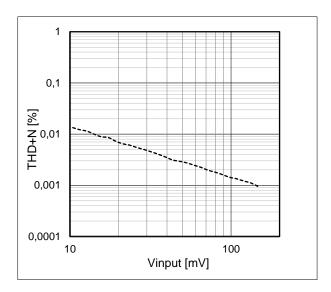

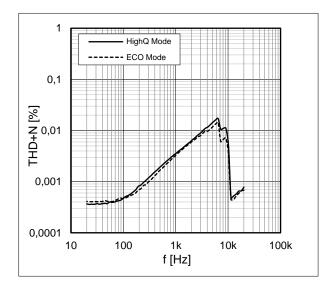

#### Figure 16: Microphone THD+N vs. V<sub>input</sub> ECO Mode (A-weighted)

### 6.3 Microphone Supply

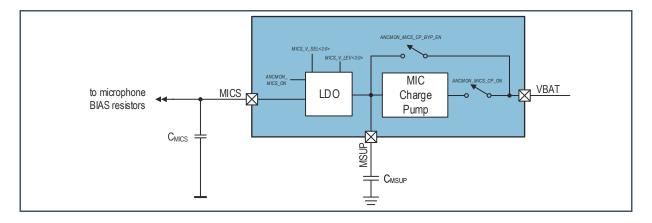

The AS3418 features an integrated microphone supply voltage regulator and a charge pump to source the microphone LDO even with a 1.4V chip supply voltage in order to increase the sensitivity of the microphone. The microphone supply charge pump is in default configuration enabled and can be controlled in ANC and Monitor operation mode with register **ANCMON\_MICS\_CP\_ON** bit. For PBO operation mode there is a dedicated control bit **PBO\_MICS\_CP\_ON**.

The output of the charge pump is directly connected to an internal microphone supply ultra-low noise voltage regulator. This low dropout (LDO) regulator is in default configuration enabled and can be controlled with **ANCMON\_MICS\_ON** bit. The default output voltage of the regulator is 2.9V. If there is a lower output voltage desired in an application the voltage level can be changed via register **MICS\_V\_SEL** register.

If the AS3418 is connected to a 1.5V battery the input voltage will of course drop during operation because the battery is discharging during operation. In order to make sure the microphone supply LDO has enough headroom to regulate properly the device features an automatic output voltage adjustment feature. This function makes sure the voltage regulator has enough headroom and adjusts the output voltage of the LDO accordingly.

Figure 17: Microphone Supply

The microphone supply charge pump is also used to switch off the integrated music bypass switch of the AS3418 in active mode. Therefore, during normal operation the microphone supply must not be switched off if the BPL and BPR pins are in use.

#### 6.3.1 Parameter

$V_{\text{BAT}}\text{=}1.8V,$   $T_{\text{A}}\text{=}25^{o}C,$   $C_{\text{MSUP}}\text{=}4.7\mu F$  and  $C_{\text{MICS}}\text{=}4.7\mu F$  unless otherwise specified.

#### Figure 18:

**Microphone Supply Parameter**

| Symbol               | Parameter                                                | Conditions                                                      | Min | Тур  | Max | Unit |

|----------------------|----------------------------------------------------------|-----------------------------------------------------------------|-----|------|-----|------|

| VMICS                | Microphone supply                                        | V <sub>BAT</sub> = 1.8V; no load; charge pump activated         |     | 2.9  |     | V    |

| V MICS               | LDO output voltage                                       | V <sub>BAT</sub> =1.4V; no load; charge pump activated          |     | 2.5  |     | V    |

| Magaz                | Microphone supply<br>charge pump<br>output voltage       | V <sub>BAT</sub> = 1.8V; no load; MICS voltage regulator off    |     | 3.15 |     | V    |

| Vmsup                |                                                          | V <sub>BAT</sub> = 1.4V; no load; MICS<br>voltage regulator off |     | 2.7  |     | V    |

|                      | Microphone Supply                                        | High quality mode enabled; 1mA load; A-weighted                 |     | 1.7  |     | μV   |

| V <sub>Noise-A</sub> | Noise at MICS<br>output                                  | High quality mode disabled;<br>1mA load; A-weighted             |     | 2.2  |     | μV   |

|                      | Current<br>consumption low<br>noise voltage<br>regulator | V <sub>BAT</sub> = 1.8V; no load;<br>HIQ_EN_MICS_LDO = 1        |     | 0.69 |     | mA   |

| Imics                |                                                          | V <sub>BAT</sub> = 1.4V; no load;<br>HIQ_EN_MICS_LDO = 1        |     | 0.67 |     | mA   |

| Symbol   | Parameter                        | Conditions                                                    | Min | Тур  | Max | Unit |

|----------|----------------------------------|---------------------------------------------------------------|-----|------|-----|------|

|          |                                  | V <sub>BAT</sub> = 1.8V; no load;<br>HIQ_EN_MICS_LDO = 0      |     | 0.33 |     | mA   |

|          |                                  | V <sub>BAT</sub> = 1.4V; no load;<br>HIQ_EN_MICS_LDO = 0      |     | 0.32 |     | mA   |

|          |                                  | V <sub>BAT</sub> = 1.8V; MICS voltage regulator off; no load  |     | 0.3  |     | mA   |

|          | Current consumption              | V <sub>BAT</sub> = 1.8V; MICS voltage regulator off; 1mA load |     | 3.5  |     | mA   |

| IMICS_CP | microphone supply<br>charge pump | V <sub>BAT</sub> = 1.4V; MICS voltage regulator off; no load  |     | 0.26 |     | mA   |

|          |                                  | V <sub>BAT</sub> = 1.4V; MICS voltage regulator off; 1mA load |     | 3.33 |     | mA   |

| Іоит     | Output current                   | Charge pump activated                                         |     | 2    |     | mA   |

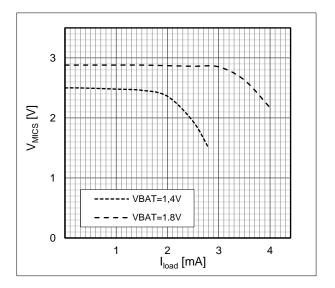

Figure 19:

**Microphone Supply Load Characteristic**

### 6.4 Headphone Amplifier

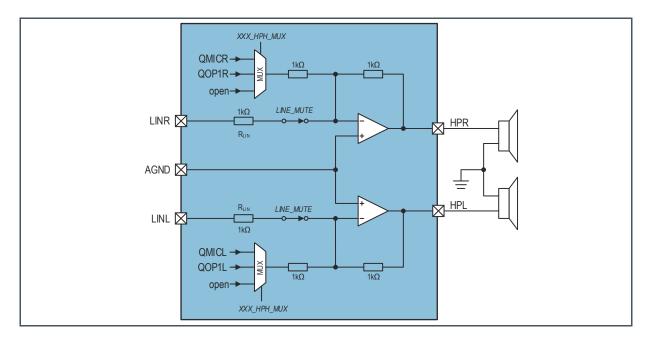

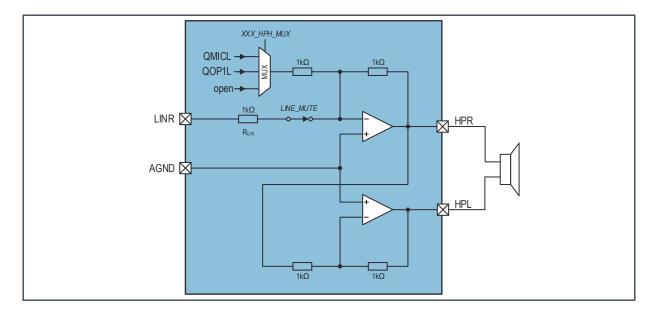

The headphone amplifier is a true ground output using  $V_{NEG}$  as negative supply. It is designed to feature an output power of 2x34mW @ 32 $\Omega$ load. For higher output requirements, the headphone amplifier is also capable of operating in bridged mode. In this mode the left output is carrying the inverted signal of the right output shown in Figure 21. With a V<sub>BAT</sub> voltage of 1.8V, a maximum output power of 100mW can be achieved. This is necessary for over- and on ear headsets with higher output power requirements. The amplifier itself features various input sources. The line input signal is directly connected to the headphone amplifier. The input multiplexer supports three different input signals

which can be configured according in the **ANC\_HPH\_MUX**, **MON\_HPH\_MUX** and **PBO\_HPH\_MUX** registers independently for each operation mode. The "Open" setting is being used to disable the active noise cancelling function.

Figure 20: Headphone Amplifier Single Ended

#### Figure 21: Headphone Amplifier Differential

#### 6.4.1 Parameter

$V_{BAT}$  =1.8V, TA= 25°C, unless otherwise specified.

#### Figure 22:

**Microphone Supply Parameter**

| Symbol                      | Parameter                       | Conditions                                                                                                                           | Min | Тур   | Max | Unit |

|-----------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| D                           | Lood Impodopoo                  | Stereo Operation Mode                                                                                                                | 16  | 32    |     | Ω    |

| Rl_hp                       | Load Impedance                  | Mono Operation Mode                                                                                                                  | 32  |       |     | Ω    |

| $C_{\text{L}_{-}\text{HP}}$ | Load Capacitance                | Per channel                                                                                                                          |     |       | 100 | pF   |

|                             |                                 | V <sub>BAT</sub> = 1.8V; 32Ω load;<br>THD<0.1%                                                                                       |     | 35    |     | mW   |

| D                           | Nominal Output                  | V <sub>BAT</sub> = 1.4V; 32Ω load;<br>THD<0.1%                                                                                       |     | 20    |     | mW   |

| P <sub>HP</sub>             | Power Stereo Mode               | V <sub>BAT</sub> = 1.8V; 16Ω load;<br>THD<0.1%                                                                                       |     | 55    |     | mW   |

|                             |                                 | V <sub>BAT</sub> = 1.4V; 16Ω load;<br>THD<0.1%                                                                                       |     | 30    |     | mW   |

| Deer                        | Nominal Output                  | V <sub>BAT</sub> = 1.8V; 32Ω load;<br>THD<0.1%                                                                                       |     | 130   |     | mW   |

| Pbridge                     | Power Differential<br>Mode      | V <sub>BAT</sub> = 1.4V; 32Ω load;<br>THD<0.1%                                                                                       |     | 75    |     | mW   |

|                             |                                 | V <sub>BAT</sub> = 1.8V; no input signal,<br>normal mode                                                                             |     | 2.9   |     | mA   |

|                             |                                 | V <sub>BAT</sub> = 1.8V; no input signal,<br>ECO mode                                                                                |     | 2.4   |     | mA   |

| Інрн                        | Supply Current                  | V <sub>BAT</sub> = 1.4V; no input signal,<br>normal mode                                                                             |     | 2.8   |     | mA   |

|                             |                                 | $V_{BAT} = 1.4V$ ; no signal, ECO mode                                                                                               |     | 2.3   |     | mA   |

| PSRRHP                      | Power Supply<br>Rejection Ratio | 1kHz                                                                                                                                 |     | 100   |     | dB   |

|                             |                                 | High Quality Mode, Line Input -<br>> HPH stereo in phase test<br>signal; $32\Omega$ load; V <sub>BAT</sub> = 1.8V;<br>A-weighted     |     | 117   |     | dB   |

| SNR                         | Signal to Noise<br>Ratio        | High Quality Mode, Line Input -<br>> HPH stereo out of phase test<br>signal; $32\Omega$ load; V <sub>BAT</sub> = 1.8V;<br>A-weighted |     | 117.5 |     | dB   |

|                             |                                 | ECO Mode, Line Input -> HPH<br>stereo in phase test signal;<br>$32\Omega$ load; V <sub>BAT</sub> = 1.8V; A-<br>weighted              |     | 114   |     | dB   |

| Symbol               | Parameter                        | Conditions                                                                                                                  | Min | Тур   | Max | Unit |

|----------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

|                      |                                  | ECO Mode, Line Input -> HPH<br>stereo out of phase test signal;<br>$32\Omega$ load; V <sub>BAT</sub> = 1.8V; A-<br>weighted |     | 114.5 |     | dB   |

| Achannel             | Channel Separation               | 32Ω load                                                                                                                    |     | 93    |     | dB   |

| N/                   | A-Weighted Output<br>Noise Floor | High Quality Mode; 32Ω load;<br><i>HP_MUX</i> = nc; LINx<br>connected to ground                                             |     | 1.5   |     | μV   |

| V <sub>NOISE-A</sub> |                                  | ECO Mode; $32\Omega$ load;<br>HP_MUX = nc; LINx<br>connected to ground                                                      |     | 2.1   |     | μV   |

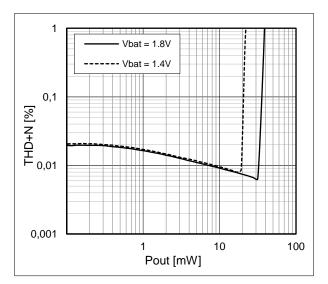

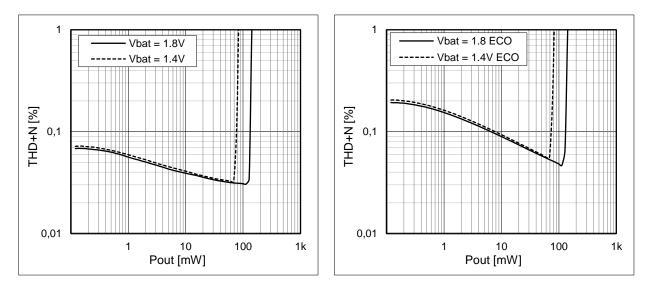

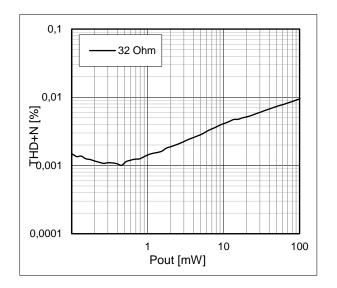

Figure 23: Headphone THD+N vs. Output Power 32Ω Stereo – High Quality Mode Figure 24:

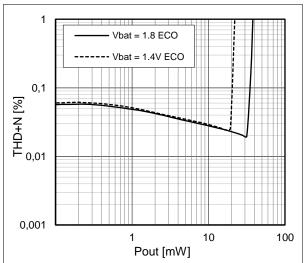

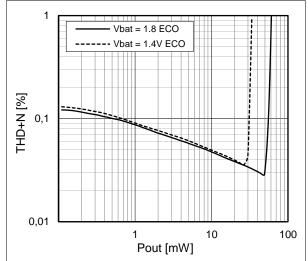

Headphone THD+N vs. Output Power 32Ω Stereo – ECO Mode

Figure 25:

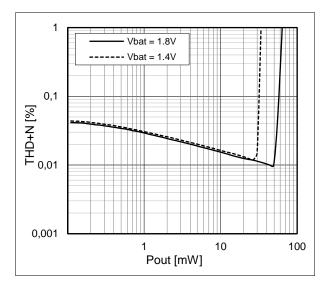

Headphone THD+N vs. Output Power 16Ω Stereo – High Quality Mode

Figure 26: Headphone THD+N vs. Output Power 16Ω Stereo – ECO Mode

Figure 27: Headphone THD+N vs. Output Power 32Ω MONO – High Quality Mode (1.8//1.4V) Figure 28: Headphone THD+N vs. Output Power 32Ω MONO –ECO Mode (1.8//1.4V)

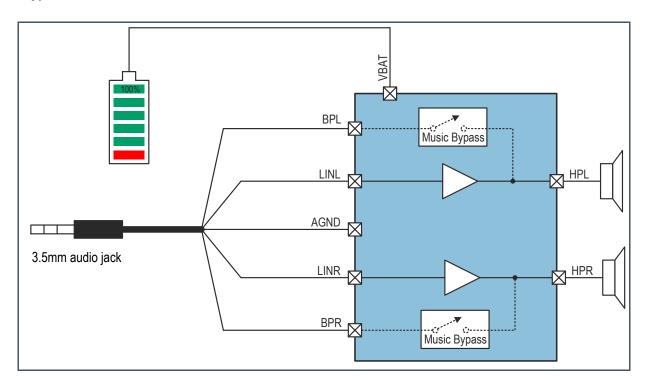

### 6.5 Music Bypass Switch

If the AS3418 is switched off, the device features a unique feature, which are integrated music bypass switches. These switches can be used to replace a mechanical switch to bypass the music signal in

off mode or if the headset runs out of battery. Figure 29 shows the basic music playback path of the AS3418 with a full battery. In this mode the line input signal is feed to the headphone amplifier. The integrated bypass switches are automatically disabled in this operation mode.

#### Figure 29: Bypass Mode Inactive

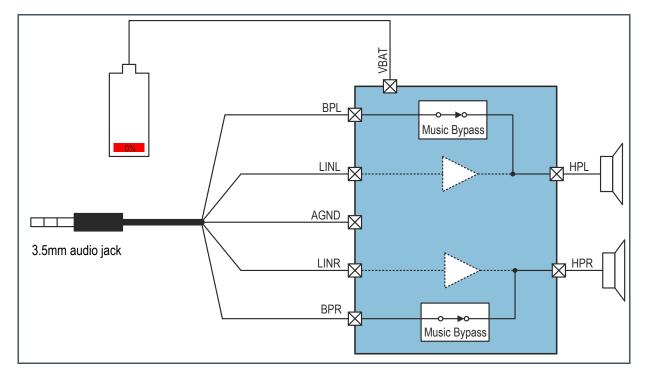

Figure 30 shows the AS3418 in off mode with an empty battery. This is basically the same use case as no battery at all. In this mode the internal bypass switch becomes active. The headphone amplifier is not powered because the headset has run out of battery and the bypass switch becomes active. Thus the music signal coming from the 3.5mm audio jack is routed through the ANC chip, without any power source connected to the device, to the speakers. The integrated bypass switch works even without any battery connected to the device. It helps to reduce BOM costs and PCB area. Furthermore it facilitates new industrial designs to ANC solutions.

#### Figure 30: Bypass Mode Active

#### 6.5.1 Parameter

$V_{BAT}$  =0V,  $T_A$ = 25°C, unless otherwise specified.

#### Figure 31:

**Bypass Switch Parameter**

| Symbol         | Parameter         | Conditions                            | Min | Тур | Max | Unit |

|----------------|-------------------|---------------------------------------|-----|-----|-----|------|

| Rswitch        | Switch resistance | Power down                            |     | 1.2 |     | Ω    |

| тир            | Total Harmonic    | $0dBV$ input signal, $32\Omega$ load  |     | -85 |     | dB   |

| THD Distortion | Distortion        | $0 dBV$ input signal, $16\Omega$ load |     | -79 |     | dB   |

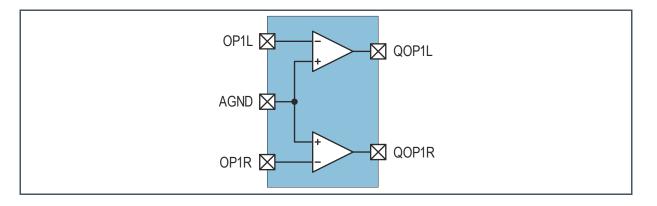

### 6.6 Operational Amplifier

The AS3418 offers one general purpose operational amplifier for feed-forward ANC. The amplifier is used to develop the gain- and phase compensation filter for the ANC signal path.

#### Figure 33: Operational Amplifier

#### 6.6.1 Parameter

$V_{BAT}$  =1.8V,  $T_{A}$ = 25°C,  $R_{input}$  =  $R_{FB}$  = 1k $\Omega$  unless otherwise specified.

#### Figure 34:

**Operational Amplifier Parameter**

| Symbol   | Parameter                    | Conditions                                                                                     | Min | Тур                  | Max  | Unit  |

|----------|------------------------------|------------------------------------------------------------------------------------------------|-----|----------------------|------|-------|

| VIN      | Input Signal Level           | Gain=0dB                                                                                       |     | 0.9*V <sub>BAT</sub> | Vbat | Vpeak |

|          |                              | 10k $\Omega$ load, Gain = 0dB <sup>(1)</sup> ,<br>V <sub>BAT</sub> =1.8V,<br>High Quality Mode |     | 114.5                |      | dB    |

| SNR      | Signal to Noise              | 10k $\Omega$ load, Gain = 0dB <sup>(1)</sup> ,<br>V <sub>BAT</sub> =1.4V<br>High Quality Mode  |     | 111.4                |      | dB    |

| SNR      | Ratio                        | 10k $\Omega$ load, Gain = 0dB <sup>(1)</sup> ,<br>V <sub>BAT</sub> =1.8V,<br>ECO Mode          |     | 113.3                |      | dB    |

|          |                              | 10k $\Omega$ load, Gain = 0dB <sup>(1)</sup> ,<br>V <sub>BAT</sub> =1.4V,<br>ECO Mode          |     | 110                  |      | dB    |

|          | Block Current<br>Consumption | $V_{BAT}$ = 1.8V; OP1L and OP1R enabled; normal mode                                           |     | 1                    |      | mA    |

|          |                              | V <sub>BAT</sub> = 1.8V; OP1L and OP1R enabled; ECO mode                                       |     | 0.7                  |      | mA    |

| IOP1     |                              | V <sub>BAT</sub> = 1.4V; OP1L and<br>OP1R enabled; normal mode                                 |     | 0.95                 |      | mA    |

|          |                              | $V_{BAT}$ = 1.4V; OP1L and OP1R enabled; ECO mode                                              |     | 0.65                 |      | mA    |

|          | Input Referred               | High Quality Mode                                                                              |     | 2.2                  |      | μV    |

| VNOISE-A | Noise Floor A-<br>Weighted   | ECO Mode                                                                                       |     | 2.6                  |      | μV    |

| Voffset  | DC offset voltage            | Gain=0dB                                                                                       |     |                      | 500  | μV    |

| CL       | Load Capacitance             |                                                                                                |     |                      | 100  | pF    |

| R∟       | Load Impedance               |                                                                                                | 1   |                      |      | kΩ    |

| Aloop    | Open Loop Gain               | 100MHz                                                                                         |     | 120                  |      | dB    |

(1) SNR figure measured with 20dB gain to minimize audio analyzer noise floor

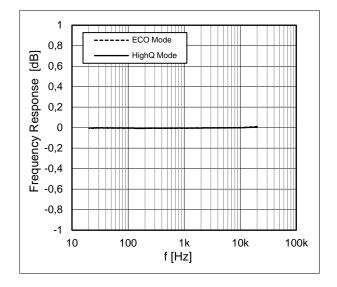

Figure 35 : Operational Amplifier Frequency Response

### 6.7 System

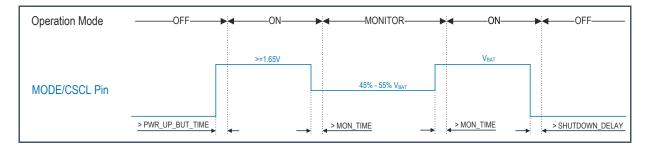

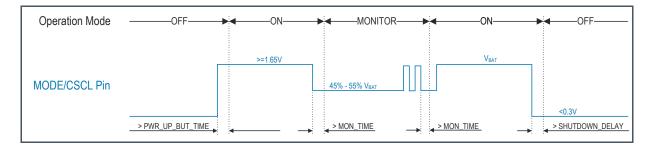

This chapter describes the power up and power down conditions of AS3418. Furthermore the Start-up sequence of the device is also described in more detail.

Figure 37: Power Up Conditions

| # | Source                           | Description                                                                                                                                                                                                                                                                            |

|---|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | MODE/CSCL pin                    | Depending on the operation mode the power up/down pin<br>MODE/CSCL pin behaves differently:                                                                                                                                                                                            |

|   |                                  | Slider Mode: Mode pin has to be driven high turn on the device. Since<br>the timing can be programmed the value depends also on<br><b>POWER_UP_BUT_TIME</b> register setting. With default configuration of                                                                            |

|   |                                  | <b>POWER_UP_BUT_TIME</b> register typ. button press time is ~16ms.                                                                                                                                                                                                                     |

| 1 |                                  | Full Slider Mode: Mode pin has to be driven high turn on the device.                                                                                                                                                                                                                   |

|   |                                  | Since the timing can be programmed the value depends also on                                                                                                                                                                                                                           |

|   |                                  | <b>POWER_UP_BUT_TIME</b> register setting. With default configuration of <b>POWER_UP_BUT_TIME</b> register typ. button press time is ~16ms.                                                                                                                                            |

|   |                                  | Push Button Mode: Mode pin has to be driven high turn on the device.<br>Since the timing can be programmed the value depends also on<br><b>POWER_UP_BUT_TIME</b> register setting. With default configuration of<br><b>POWER_UP_BUT_TIME</b> register typ. button press time is ~16ms. |

| 2 | I <sup>2</sup> C start condition | In I <sup>2</sup> C mode, an I <sup>2</sup> C start condition turns on the device. For this startup function <b>I2C_MODE</b> bit must be set in the EEPROM register.                                                                                                                   |

The chip automatically powers down if one of the following conditions arises:

### Figure 38:

Power Down Conditions

| # | Source                              | Description                                                                                                                                                                                                            |

|---|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                     | Depending on the operation mode the power MODE/CSCL pin behaves differently:                                                                                                                                           |

|   |                                     | Slider Mode: Mode pin has to be driven low for min. 10ms to turn off                                                                                                                                                   |

| 1 | MODE/CSCL pin                       | the device                                                                                                                                                                                                             |

|   |                                     | Full Slider Mode: Mode pin has to be driven low for min. 10ms to turn off the device                                                                                                                                   |

|   |                                     | Push Button Mode: Mode pin has to be high for the time defined in<br><b>PWR_DOWN_BUT_TIME</b> register to turn off the device.                                                                                         |

| 2 | I <sup>2</sup> C power down command | Power down by serial interface is initiated by clearing the <b>PWR_HOLD</b> bit. (Please mind that the <b>I2C_MODE</b> bit has to be set before clearing the <b>PWR_HOLD</b> bit to enable the $I_2C$ power down mode) |

| 3 | V <sub>NEG</sub> over current       | Power down if $V_{\text{NEG}}$ is higher than the $V_{\text{NEG}}$ off-threshold.                                                                                                                                      |

#### 6.7.1 Start-Up Sequence

The AS3418 has a defined startup sequence. Once the AS3418 MODE pin is pulled high, the device initiates the automatic startup sequence shown in Figure 39 or Figure 40 depending on the operation

## am

mode. In case the **I2C\_MODE** bit is set the device behaves differently during startup compared to normal operation with external slide switch or push button.

#### Figure 39:

Normal Start-Up Sequence

| VBAT                              |                           |                                     |  |

|-----------------------------------|---------------------------|-------------------------------------|--|

| MODE/CSCL                         | min. 70% V <sub>BAT</sub> |                                     |  |

| VOL/CSDA                          | X don't care              |                                     |  |

| BIAS & OSC ON                     |                           |                                     |  |

| VNEG OK                           | -10mi                     |                                     |  |

| START EEPROM DOWNLOAD             |                           |                                     |  |

| EEPROM READY                      | *****                     |                                     |  |

| Enable MICS charge pump (MSUP)    |                           |                                     |  |

| Enable OPAMPs and MIC Amplifiers  |                           |                                     |  |

| MICS LDO Chargepump OK            |                           |                                     |  |

| MICS LDO OK                       |                           |                                     |  |

| Enable Line Zero Cross Comparator | ~40µs masking             |                                     |  |

| Right Zero Cross Detect           |                           |                                     |  |

| Left Zero Cross Detect            |                           |                                     |  |

| Enable Right Music Bypass         |                           |                                     |  |

| Enable Left Music Bypass          |                           |                                     |  |

| Enable Headphone Right            |                           |                                     |  |

| Enable Headphone Left             |                           |                                     |  |

| Configure HPH_MUX                 | not connected b'11'       | ANC_HPH_MUX<1:0>                    |  |

| PWRUP COMPLETE                    |                           |                                     |  |

| Fade in MIC Gain                  | MUTE                      | FADE IN MIC GAIN ANC_MICx_GAIN<6:0> |  |

| Operating State                   | OFF                       | ANC Operation                       |  |

| Time Axis                         | <b>%</b>                  |                                     |  |

|                                   | 0 11 ty                   | rp. 52 t<br>[ms]                    |  |

Figure 40: I<sup>2</sup>C Start-Up Sequence

| VBAT                              | min. 1.4V                                 |               |  |

|-----------------------------------|-------------------------------------------|---------------|--|

| MODE/CSCL                         | min. 70% V <sub>BAT</sub> VPWRUP_HOLD = 1 |               |  |

| VOL/CSDA                          | PWRUP_HOLD = 1                            |               |  |

| BIAS & OSC ON                     |                                           |               |  |

| VNEG OK                           |                                           |               |  |

| START EEPROM DOWNLOAD             |                                           |               |  |

| EEPROM READY                      |                                           |               |  |

| I2C_MODE                          |                                           |               |  |

| PWR_HOLD                          |                                           |               |  |

| Enable MICS charge pump (MSUP)    |                                           |               |  |

| Enable OPAMPs and MIC Amplifiers  |                                           |               |  |

| MICS LDO Chargepump OK            |                                           |               |  |

| MICS LDO OK                       |                                           |               |  |

| Enable Line Zero Cross Comparator | -40ja masking                             |               |  |

| Right Zero Cross Detect           |                                           |               |  |

| Left Zero Cross Detect            |                                           |               |  |

| Enable Right Music Bypass         |                                           |               |  |

| Enable Left Music Bypass          |                                           |               |  |

| Enable Headphone Right            |                                           |               |  |

| Enable Headphone Left             |                                           |               |  |

| Configure HPH_MUX                 | not connected b'11' X ANC_HF              | PH_MUX<1:0>   |  |

| PWRUP COMPLETE                    |                                           |               |  |

| Fade in MIC Gain                  | MUTE FADE IN MIC O                        |               |  |

| Operating State                   | OFF                                       | ANC Operation |  |

| Time Axis                         |                                           |               |  |

|                                   | 0 11 typ. 55                              | t<br>[ms]     |  |

### 6.8 Operation Modes

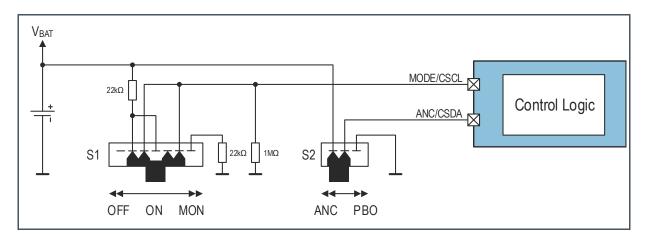

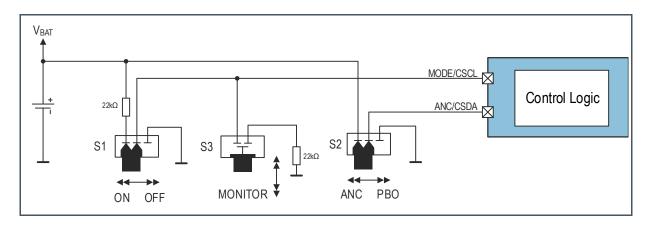

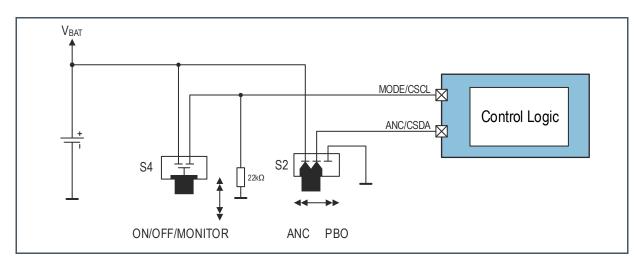

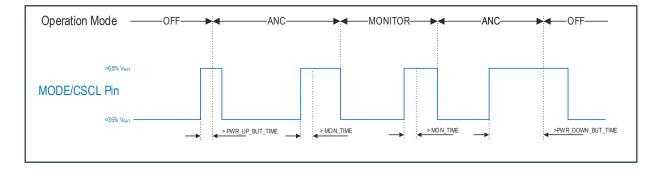

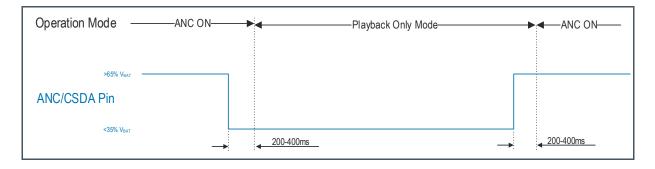

If the AS3418 is in stand-alone mode (no  $I^2C$  control), the device can work in different operation modes. An overview of the different operation modes is shown in Figure 41.

Figure 41: Operation Modes

| MODE | Description                                                 |

|------|-------------------------------------------------------------|

| OFF  | Chip is turned off.                                         |

| ANC  | Chip is turned on and active noise cancellation is enabled. |

| MODE    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

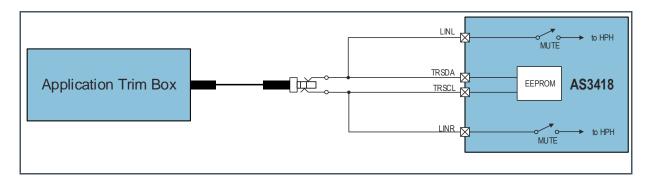

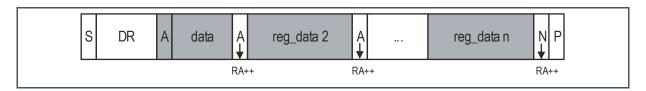

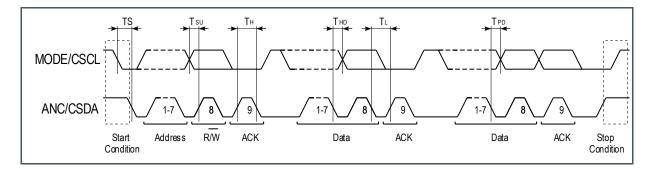

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|