# **AS3661**

# **Programmable 9-channel LED Driver**

## **General Description**

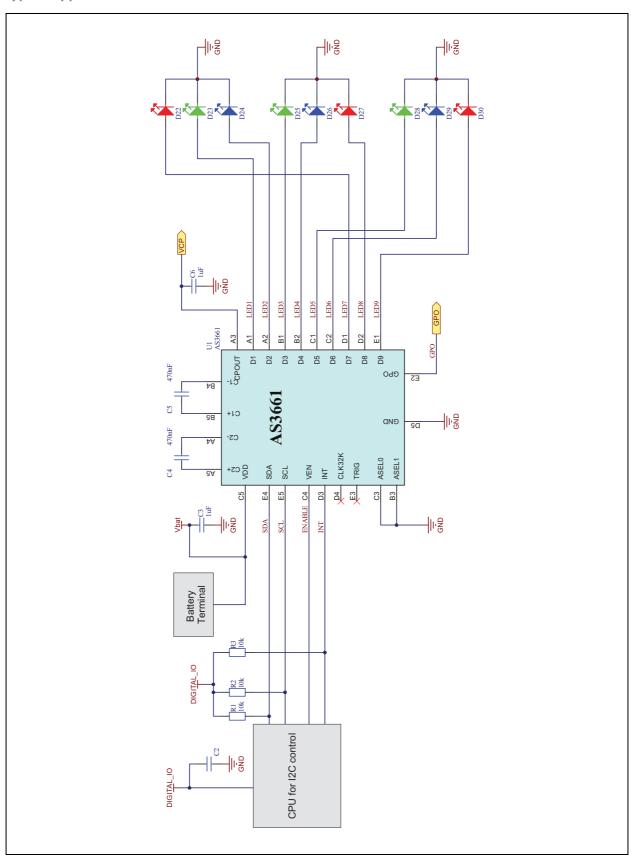

The AS3661 is a 9-channel LED driver designed to produce lighting effects for mobile devices. A high efficiency charge pump enables LED driving over full Li- Ion battery voltage range. The device is equipped with an internal program memory, which allows operation without processor control. The AS3661 maintains excellent efficiency over a wide operating range by autonomously selecting the best charge pump gain based on LED forward voltage requirements. AS3661 is able to automatically enter power-save mode when LED outputs are not active, thus lowering idle current consumption down to  $10\mu A$  (typ).

The AS3661 has an I<sup>2</sup>C-compatible control interface with four pin selectable addresses. Also, the device has a flexible General Purpose Output (GPO), which can be used as a digital control pin for other devices. INT pin can be used to notify processor when a lighting sequence has ended (interrupt - function). Also, the device has a trigger input interface, which allows synchronization between multiple devices. The device requires only four small and low-cost ceramic capacitors.

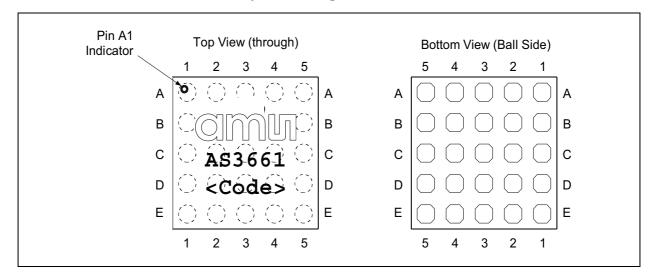

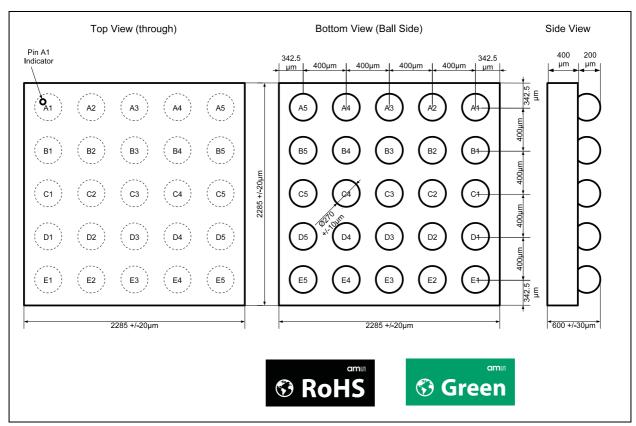

The AS3661 is available in a tiny WL-CSP-25  $(2.285 \times 2.285 \text{mm})$  0.4mm pitch package.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of AS3661, Programmable 9-channel LED Driver are listed below:

Figure 1: Added Value Of Using AS3661

| Benefits                              | Features                                                                                                                                                                                                      |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Smooth light effects for the end user | <ul> <li>Three independent program execution engines</li> <li>9 programmable outputs with 25.5 mA full-scale current,</li> <li>8- bit current setting resolution and 12-bit PWM control resolution</li> </ul> |

| Long battery operating time           | <ul> <li>Adaptive charge pump with 1x and 1.5x gain provides up<br/>to 95% LED drive efficiency</li> </ul>                                                                                                    |

| Easy system integration               | <ul><li>Charge pump with soft start and overcurrent/short</li><li>circuit protection</li></ul>                                                                                                                |

| Easy system integration               | Built-in LED test                                                                                                                                                                                             |

| Long battery operating time           | <ul> <li>Automatic power save mode; IVDD = 10 μA (typ.)</li> </ul>                                                                                                                                            |

# **Applications**

The AS3661, Programmable 9-channel LED Driver is ideal for fun and indicator lights, LED backlighting, and programmable current source.

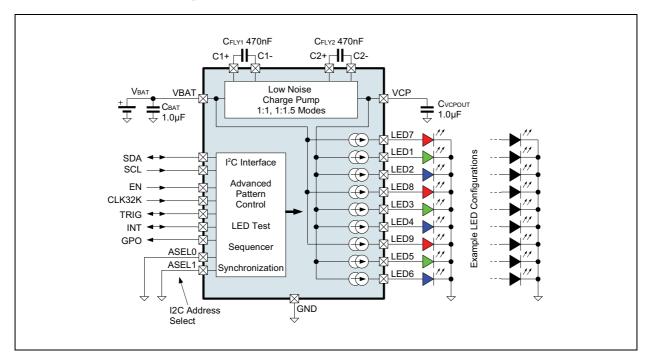

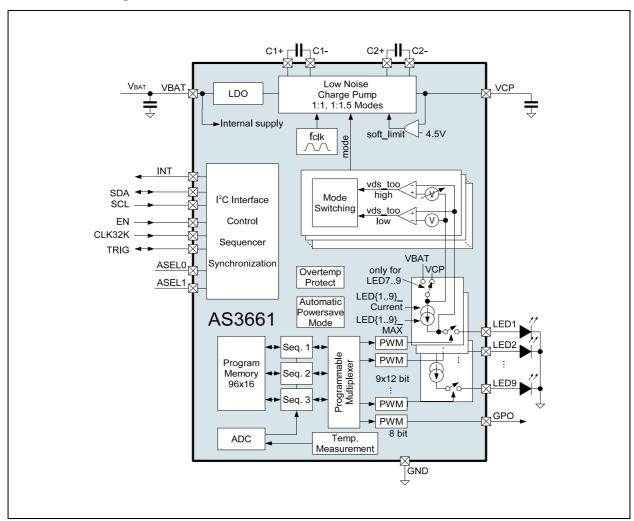

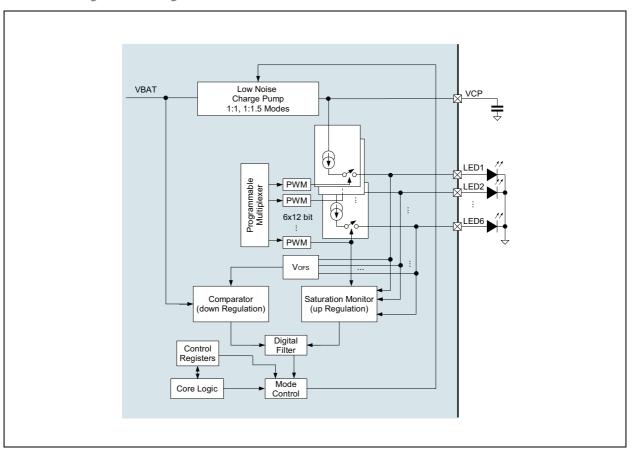

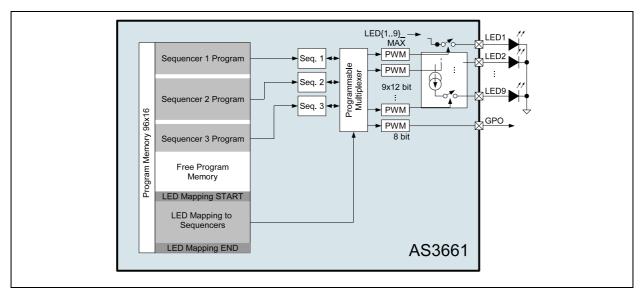

## **Block Diagram**

The functional blocks of this device for reference are shown below:

Figure 2: AS3661 LED Driver Block Diagram

Page 2 ams Datasheet

Document Feedback [v1-31] 2015-Feb-03

# **Pin Assignments**

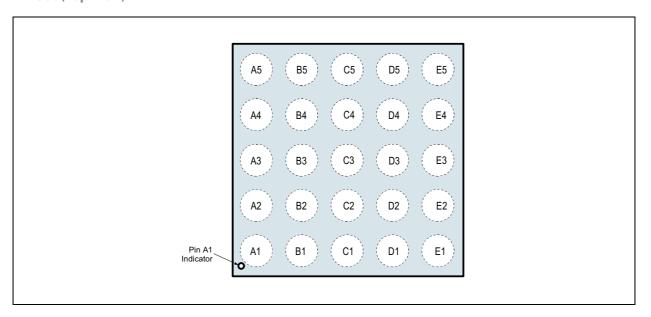

Figure 3: Pin Out (Top View)

Figure 4: Pin Description for AS3661

| Pin<br>Number | Pin<br>Name | Description                                                                                     |

|---------------|-------------|-------------------------------------------------------------------------------------------------|

| A1            | LED1        | <b>LED1 Output</b> . Current source from V <sub>CP</sub> .                                      |

| A2            | LED2        | <b>LED2 Output</b> . Current source from V <sub>CP</sub> .                                      |

| А3            | VCP         | <b>Charge Pump output.</b> make a short connection to capacitor C <sub>VCPOUT</sub> .           |

| A4            | C2-         | <b>Charge Pump flying capacitor 2.</b> make a short connection to capacitor C <sub>FLY2</sub> . |

| A5            | C2+         | <b>Charge Pump flying capacitor 2.</b> make a short connection to capacitor C <sub>FLY2</sub> . |

| B1            | LED3        | <b>LED3 Output</b> . Current source from V <sub>CP</sub> .                                      |

| B2            | LED4        | <b>LED4 Output</b> . Current source from V <sub>CP</sub> .                                      |

| В3            | ASEL1       | Digital input -l <sup>2</sup> C address select                                                  |

| B4            | C1-         | <b>Charge Pump flying capacitor 1.</b> make a short connection to capacitor C <sub>FLY1</sub> . |

| B5            | C1+         | <b>Charge Pump flying capacitor 1.</b> make a short connection to capacitor C <sub>FLY1</sub> . |

| C1            | LED5        | <b>LED5 Output</b> . Current source from V <sub>CP</sub> .                                      |

| C2            | LED6        | <b>LED6 Output</b> . Current source from V <sub>CP</sub> .                                      |

| С3            | ASEL0       | Digital input -l <sup>2</sup> C address select                                                  |

| C4            | EN          | Enable. Active high digital input.                                                              |

| Pin<br>Number | Pin<br>Name | Description                                                                                                   |

|---------------|-------------|---------------------------------------------------------------------------------------------------------------|

| C5            | VBAT        | Positive Power Supply Input                                                                                   |

| D1            | LED7        | LED7 Output. Current source from VBAT.                                                                        |

| D2            | LED8        | LED8 Output. Current source from VBAT.                                                                        |

| D3            | INT         | Interrupt Output. Open drain digital output for microcontroller unit, leave unconnected if not used.          |

| D4            | CLK32K      | <b>Digital Clock Input.</b> Connect a 32kHz signal; if this signal is not available, connect this pin to GND. |

| D5            | GND         | Ground                                                                                                        |

| E1            | LED9        | LED9 Output. Current source from VBAT.                                                                        |

| E2            | GPO         | General Purpose Output. Leave unconnected if not used.                                                        |

| E3            | TRIG        | Trigger Input. Open drain, connect to ground if not used.                                                     |

| E4            | SDA         | <b>Serial-Data I/O</b> . Open drain digital I/O I <sup>2</sup> C data pin.                                    |

| E5            | SCL         | Serial-Clock Input                                                                                            |

Page 4

Document Feedback

[v1-31] 2015-Feb-03

## **Absolute Maximum Ratings**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in

Electrical Characteristics, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5: Absolute Maximum Ratings

| Parameter                                                    | Min       | Max      | Units     | Comments                                              |  |  |  |

|--------------------------------------------------------------|-----------|----------|-----------|-------------------------------------------------------|--|--|--|

| VBAT, VCP, C1+, C1-, C2+, C2- to GND                         | -0.3      | +7.0     | V         |                                                       |  |  |  |

| VCP to VBAT                                                  | -0.3      |          | V         | Diode between V <sub>CP</sub> and VBAT                |  |  |  |

| LED1, LED2 to LED9 to GND                                    | -0.3      | +7.0     | V         |                                                       |  |  |  |

| SDA, SCL, EN, CLK32K, TRIG, INT, GPO,<br>ASEL0, ASEL1 to GND | -0.3      | +7.0     | V         |                                                       |  |  |  |

| Elec                                                         | ctrostati | c Discha | rge       |                                                       |  |  |  |

| ESD HBM (LED1 to LED2)                                       | 8         | 3        | kV        | JEDEC JESD22-A114                                     |  |  |  |

| ESD HBM (all other pins)                                     | 2         | .5       | kV        | JEDEC JESDZZ ATTA                                     |  |  |  |

| ESD MM                                                       | 25        | 50       | V         | JEDEC JESD22-A115                                     |  |  |  |

| ESD CDM                                                      |           | 1        | kV        | JEDEC JESD22-C101                                     |  |  |  |

| Temperature F                                                | Ranges a  | nd Stora | ge Condit | ions                                                  |  |  |  |

| Continous Power Dissipation                                  |           |          |           | Internally limited                                    |  |  |  |

| Junction Temperature (T <sub>JMAX</sub> )                    |           | 125      | °C        | (overtemperature protection) (1)                      |  |  |  |

| Storage Temperature Range                                    | -55       | 125      | °C        |                                                       |  |  |  |

| Body Temperature during Soldering                            |           | 260      | °C        | IPC/JEDEC J-STD-020                                   |  |  |  |

| Junction to Ambient Thermal Resistance $(\theta_{JA})^{(2)}$ |           | 87       | °C/W      |                                                       |  |  |  |

| Moisture Sensitivity Level                                   | 1         |          |           | Represents a max. floor life time of <i>unlimited</i> |  |  |  |

| Recommended Operating Conditions                             |           |          |           |                                                       |  |  |  |

| Recommended charge pump load current                         | 0         | 100      | mA        |                                                       |  |  |  |

#### Note(s) and/or Footnote(s):

- 1. Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J = 150^{\circ}\text{C}$  (typ.) and disengages at  $T_J = 130^{\circ}\text{C}$  (typ.).

- 2. Junction to ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

ams Datasheet Page 5

[v1-31] 2015-Feb-03 Document Feedback

## **Electrical Characteristics**

$V_{BAT}=3.6V, V_{EN}=1.65V, C_{BAT}=C_{VCPOUT}=1.0\mu\text{F}, C_{FLY1-2}=0.47\mu\text{F}, \\ T_{AMB}=-30^{\circ}\text{C to }85^{\circ}\text{C, typical values @ }T_{AMB}=25^{\circ}\text{C (unless otherwise specified)} \label{eq:total_fit}$

Figure 6: Electrical Characteristics

| Symbol            | Parameter                                   | Condition                                                                            | Min | Тур  | Max  | Unit |

|-------------------|---------------------------------------------|--------------------------------------------------------------------------------------|-----|------|------|------|

|                   |                                             | General Operating Conditions                                                         |     |      |      |      |

| V <sub>BAT</sub>  | Supply Voltage                              |                                                                                      | 2.7 |      | 5.5  | V    |

|                   | Standby supply current                      | EN = 0V or CHIP_EN=0 (bit), external 32 kHz clock running or not running             |     | 1.4  | 4    | μА   |

| I <sub>VBAT</sub> |                                             | External 32 kHz clock running,<br>charge pump and current source<br>outputs disabled |     | 0.16 | 0.22 | mA   |

|                   | Normal Mode supply current                  | Charge pump in 1x mode, no load, current source outputs disabled                     |     | 0.16 | 0.22 | mA   |

|                   |                                             | Charge pump in 1.5x mode, no load, current source outputs disabled                   |     | 1.4  |      | mA   |

|                   | Power Save Mode                             | External 32 kHz clock running                                                        |     | 3.1  | 5    | μΑ   |

|                   | supply current                              | Internal oscillator running                                                          |     | 0.16 | 0.23 | mA   |

| f <sub>OSC</sub>  | Internal Oscillator                         | T <sub>AMB</sub> = +25°C                                                             | -4  |      | +4   | %    |

| ·Osc              | Frequency Accuracy                          |                                                                                      | -7  |      | +7   | 70   |

| T <sub>AMB</sub>  | Operating<br>Temperature (1)                |                                                                                      | -30 | 25   | 85   | °C   |

|                   |                                             | Charge Pump                                                                          | ·   |      |      |      |

|                   |                                             | Gain = 1.5 and V <sub>BAT</sub> = 2.9V                                               |     | 6    |      |      |

| D                 | Charge Pump Output                          | Gain = 1 and V <sub>BAT</sub> = 2.9V                                                 |     | 1    |      | Ω    |

| R <sub>OUT</sub>  | Resistance                                  | Gain = 1.5 and V <sub>BAT</sub> = 3.6V                                               |     | 1.4  |      | 52   |

|                   |                                             | Gain = 1 and V <sub>BAT</sub> = 3.6V                                                 |     | 1    |      | -    |

| f <sub>SW</sub>   | Switching Frequency                         |                                                                                      | 1.2 | 1.25 | 1.3  | MHz  |

| 1                 | Ground current                              | Gain = 1.5                                                                           |     | 1.2  |      | mA   |

| I <sub>GND</sub>  | Ground current                              | Gain = 1                                                                             |     | 1    |      | μΑ   |

| t <sub>ON</sub>   | V <sub>CP</sub> Turn-On Time <sup>(2)</sup> | V <sub>BAT</sub> = 3.6V, I <sub>OUT</sub> = 60 mA                                    |     | 100  |      | μs   |

| I <sub>LOAD</sub> | Charge Pump load current                    | Recommended charge pump load current                                                 | 0   |      | 100  | mA   |

Page 6

Document Feedback

[v1-31] 2015-Feb-03

| Symbol               | Parameter                                | Condit                                  | Min                     | Тур                     | Max  | Unit                    |     |  |  |

|----------------------|------------------------------------------|-----------------------------------------|-------------------------|-------------------------|------|-------------------------|-----|--|--|

| LED Driver           |                                          |                                         |                         |                         |      |                         |     |  |  |

| I <sub>LEAK</sub>    | Leakage Current<br>(LED1 to LED9)        | PWM = 0%                                |                         |                         | 0.1  | 1                       | μА  |  |  |

| I <sub>MAX</sub>     | Maximum Source<br>Current                | Outputs LED1 to LED                     | )9                      |                         | 25.5 |                         | mA  |  |  |

| I <sub>OUT</sub>     | Output Current <sup>(3)</sup> Accuracy   | Output Current set to 17.5 mA           | T <sub>AMB</sub> = 25°C | -2.5%<br>-5             |      | +2.5%<br>+5             | . % |  |  |

| I <sub>MATCH</sub>   | Matching                                 | Output Current set to                   | o 17.5 mA               |                         | 1    | 2.5                     | %   |  |  |

| f <sub>LED</sub>     | LED Switching<br>Frequency               |                                         |                         |                         | 312  |                         | Hz  |  |  |

| V <sub>SAT</sub>     | Saturation Voltage (4)                   | Output Current set to                   | o 17.5 mA               |                         | 45   | 100                     | mV  |  |  |

|                      | 1                                        | LED Test                                | t                       |                         |      |                         |     |  |  |

| LSB                  | Least Significant Bit                    |                                         |                         |                         | 30   |                         | mV  |  |  |

| E <sub>ABS</sub>     | Total Unadjusted<br>Error <sup>(5)</sup> | $V_{IN\_TEST} = 0V \text{ to } V_{BAT}$ |                         |                         | <±3  | <u>±</u> 4              | LSB |  |  |

| t <sub>CONV</sub>    | Conversion Time                          |                                         |                         |                         |      |                         | ms  |  |  |

| V <sub>IN_TEST</sub> | DC Voltage Range                         |                                         | 0                       |                         | 5    | V                       |     |  |  |

|                      |                                          | LOGIC INTER                             | FACE                    |                         |      |                         |     |  |  |

|                      |                                          | Logic Input                             | : EN                    |                         |      |                         |     |  |  |

| V <sub>IL</sub>      | Input Low Level                          |                                         |                         |                         |      | 0.5                     | V   |  |  |

| V <sub>IH</sub>      | Input High Level                         |                                         |                         | 1.2                     |      |                         | V   |  |  |

| I <sub>IN</sub>      | Input Current                            |                                         |                         | -1.0                    |      | 1.0                     | μΑ  |  |  |

| t <sub>DELAY</sub>   | Input Delay <sup>(6)</sup>               |                                         |                         |                         | 2    |                         | μs  |  |  |

|                      | Logic In                                 | put SCL, SDA, TRIG, C                   | LK32K, ASELO,           | ASEL1                   | I    |                         |     |  |  |

| V <sub>IL</sub>      | Input Low Level                          |                                         |                         |                         |      | 0.2×<br>V <sub>EN</sub> | V   |  |  |

| V <sub>IH</sub>      | Input High Level                         |                                         |                         | 0.8×<br>V <sub>EN</sub> |      |                         | V   |  |  |

| I <sub>IN</sub>      | Input Current                            |                                         |                         | -1.0                    |      | 1.0                     | μΑ  |  |  |

|                      |                                          | Logic Output SDA                        | , TRIG, INT             | ,                       |      |                         | L   |  |  |

| V <sub>OL</sub>      | Output Low Level                         | I <sub>OUT</sub> = 3 mA (pull-up        | current)                |                         | 0.3  | 0.5                     | V   |  |  |

| Symbol            | Parameter                 | Condition                | Min                      | Тур                      | Max | Unit |

|-------------------|---------------------------|--------------------------|--------------------------|--------------------------|-----|------|

| IL                | Output Leakage<br>Current | V <sub>CP</sub> = 2.8V   |                          |                          | 1.0 | μА   |

|                   |                           | Logic Output GPO         |                          |                          |     |      |

| V <sub>OL</sub>   | Output Low Level          | I <sub>OUT</sub> = 3 mA  |                          | 0.3                      | 0.5 | V    |

| V <sub>OH</sub>   | Output High Level         | I <sub>OUT</sub> = -2 mA | V <sub>BAT</sub><br>-0.5 | V <sub>BAT</sub><br>-0.3 |     | V    |

| IL                | Output Leakage<br>Current | V <sub>CP</sub> = 2.8V   |                          |                          | 1.0 | μΑ   |

|                   |                           | Logic Input CLK32K       |                          |                          |     |      |

| f <sub>CLK</sub>  | Clock Frequency           |                          |                          | 32.7                     |     | kHz  |

| f <sub>CLKH</sub> | High Time                 |                          | 6                        |                          |     | μs   |

| f <sub>CLKL</sub> | Low Time                  |                          | 6                        |                          |     | μs   |

| t <sub>R</sub>    | Clock Rise Time           | 10 to 90%                |                          |                          | 2   | μs   |

| t <sub>F</sub>    | Clock Fall Time           | 90 to 10%                |                          |                          | 2   | μs   |

#### Note(s) and/or Footnote(s):

- 1. In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature ( $T_{Amb-MAX}$ ) is dependent on the maximum operating junction temperature ( $T_{J-MAX} = 125^{\circ}$ C), the maximum power dissipation of the device in the application ( $P_{D-MAX}$ ) and the junction to ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ) as given by the following equation:  $T_{Amb-MAX} = T_{J-MAX} (\theta_{JA} * P_{D-MAX})$ .

- 2. Turn-on time is measured from the moment the charge pump is activated until the  $V_{CP}$  crosses 90% of its target value.

- 3. Output current accuracy is the difference between actual value of the output current and programmed value of this current. I<sub>MATCH</sub> is determined as follows:

- For the constant current D1 to D9, the following are determined: The maximum current (max) and the minimum current (min), then the  $I_{MATCH}$  is calculated with:  $I_{MATCH} = 100*(((max-min)/2)+((max+min)/2))/((max+min)/2)-100$ .

- 4. Saturation voltage is defined as the voltage when the LED current has dropped 10% from the value measured at  $V_{CP}$  1V.

- 5. Total unadjusted error includes offset, full-scale and linearity errors.

- 6. The I<sup>2</sup>C host should allow at least 500µs before sending data the AS3661after the rising edge of the enable line.

- 7. Low-ESR Surface-Mount Ceramic Capacitors 8MLCCs) used in setting electrical characteristics.

Page 8

Document Feedback

[v1-31] 2015-Feb-03

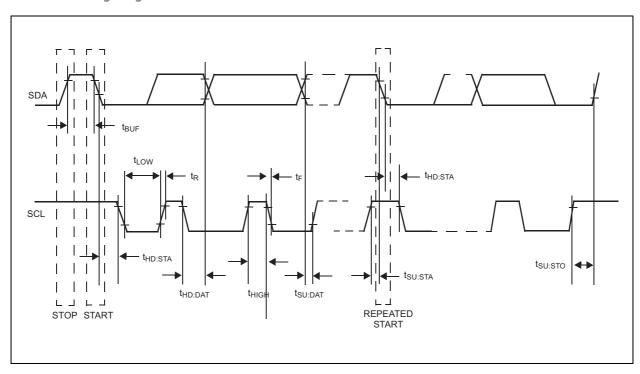

Figure 7: I<sup>2</sup>C Mode Timing Diagram

Figure 8: Electrical Characteristics I<sup>2</sup>C<sup>(1)</sup>

| Symbol              | Parameter                                              | Condition                                    | Min | Тур | Max | Unit |

|---------------------|--------------------------------------------------------|----------------------------------------------|-----|-----|-----|------|

|                     |                                                        | I <sup>2</sup> C mode timings (see Figure 7) |     |     |     |      |

| f <sub>SCLK</sub>   | SCL Clock Frequency                                    |                                              | 0   |     | 400 | kHz  |

| t <sub>BUF</sub>    | Bus Free Time<br>Between a STOP and<br>START Condition |                                              | 1.3 |     |     | μs   |

| t <sub>HD:STA</sub> | Hold Time (Repeated) START Condition (2)               |                                              | 0.6 |     |     | μs   |

| t <sub>LOW</sub>    | LOW Period of SCL<br>Clock                             |                                              | 1.3 |     |     | μs   |

| t <sub>HIGH</sub>   | HIGH Period of SCL<br>Clock                            |                                              | 0.6 |     |     | μs   |

| t <sub>SU:STA</sub> | Setup Time for a<br>Repeated START<br>Condition        |                                              | 0.6 |     |     | μs   |

| t <sub>HD:DAT</sub> | Data Hold Time <sup>(3)</sup>                          |                                              | 50  |     |     | ns   |

| t <sub>SU:DAT</sub> | Data Setup Time <sup>(4)</sup>                         |                                              | 100 |     |     | ns   |

ams Datasheet Page 9

[v1-31] 2015-Feb-03 Document Feedback

| Symbol              | Parameter                                | Condition                                            | Min                       | Тур | Max | Unit |

|---------------------|------------------------------------------|------------------------------------------------------|---------------------------|-----|-----|------|

| t <sub>R</sub>      | Rise Time of Both SDA<br>and SCL Signals |                                                      | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns   |

| t <sub>F</sub>      | Fall Time of Both SDA and SCL Signals    |                                                      | 15+<br>0.1C <sub>B</sub>  |     | 300 | ns   |

| t <sub>SU:STO</sub> | Setup Time for STOP<br>Condition         |                                                      | 0.6                       |     |     | μs   |

| C <sub>B</sub>      | Capacitive Load for<br>Each Bus Line     | Load of one picofarad corresponds to one nanosecond. | 10                        |     | 200 | ns   |

| C <sub>I/O</sub>    | I/O Capacitance (SDA,<br>SCL)            |                                                      |                           |     | 10  | pF   |

#### Note(s) and/or Footnote(s):

- 1. Specification is guaranteed by design and is not tested in production.  $V_{EN} = 1.65 V$  to  $V_{BAT}$ .

- 2. After this period the first clock pulse is generated.

- 3. A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 4. A fast-mode device can be used in a standard-mode system, but the requirement  $t_{SU:DAT} = to 250$ ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_R \max + t_{SU:DAT} = 1000 + 250 = 1250$ ns before the SCL line is released.

Page 10

Document Feedback

[v1-31] 2015-Feb-03

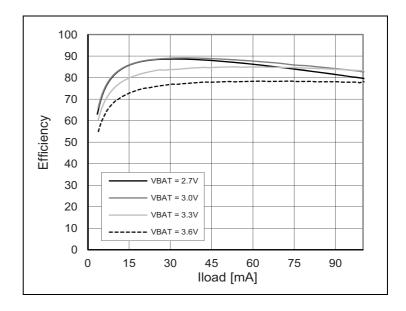

# Typical Operating Characteristics

$V_{BAT}=3.6V, V_{EN}=1.65V, C_{BAT}=C_{VCPOUT}=1.0\mu\text{F}, C_{FLY1-2}=0.47\mu\text{F}, \\ T_{AMB}=25^{\circ}\text{C, unless otherwise specified.}$

Figure 9: Charge Pump 1.5 × Efficiency vs. Load

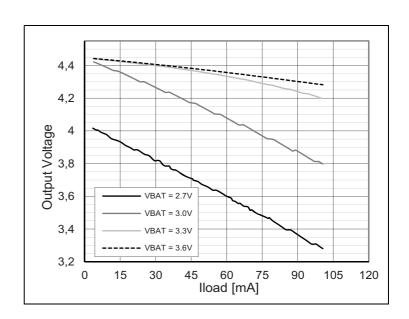

Figure 10: Output Voltage vs. Load Current (1.5 × CP)

ams Datasheet Page 11

[v1-31] 2015-Feb-03 Document Feedback

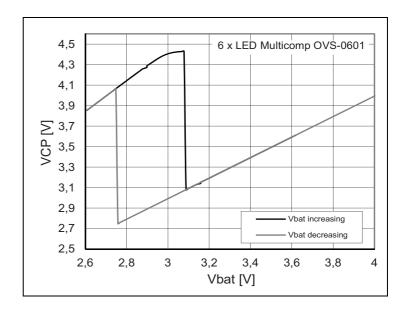

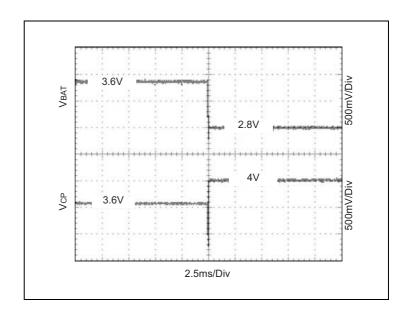

Figure 11: Gain Change Hysteresis Loop (6 × 1mA load)

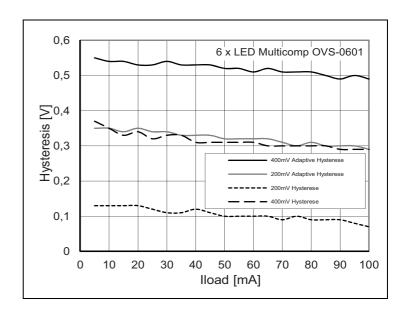

Figure 12: Effect of Adaptive Hysteresis on Width of Hysteresis Loop

Page 12ams DatasheetDocument Feedback[v1-31] 2015-Feb-03

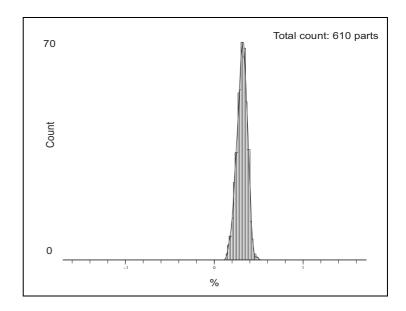

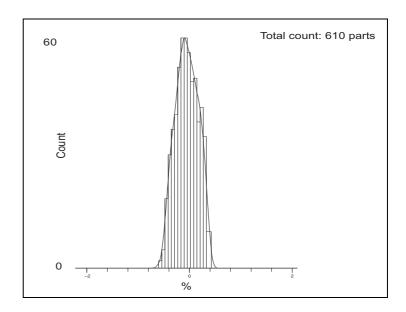

Figure 13: **LED Current Matching Distribution @17.5mA**

Figure 14: **LED Current Accuracy Distribution @17.5mA**

ams Datasheet Page 13 Document Feedback

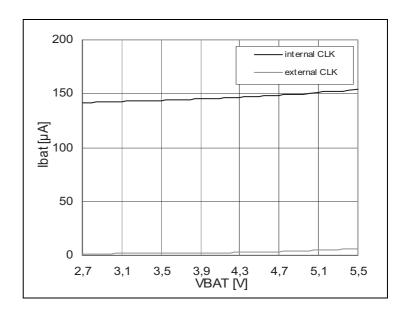

Figure 15: Power Save Mode Supply Current vs.VBAT, Charge Pump in 1x Mode

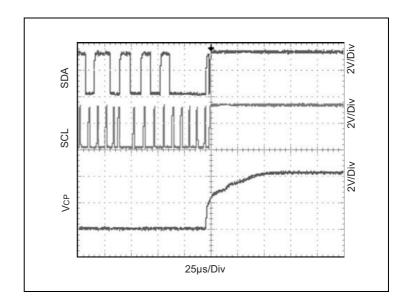

Figure 16: Serial Bus Write and Charge Pump Startup, I<sub>LOAD</sub> = 60mA

Page 14ams DatasheetDocument Feedback[v1-31] 2015-Feb-03

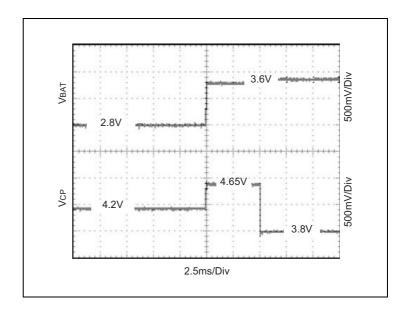

Figure 17: Line Transient and Charge Pump Automatic Gain Change 1.5 to 1, 6LEDs@1mA 100% PWM

Figure 18: Line Transient and Charge Pump Automatic Gain Change 1 to 1.5, 6LEDs@1mA 100% PWM

ams Datasheet Page 15

[v1-31] 2015-Feb-03 Document Feedback

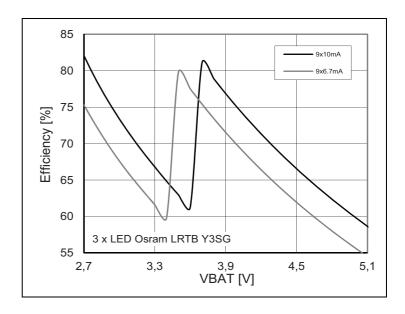

Figure 19: 100% PWM RGB LED Efficiency vs. VBAT

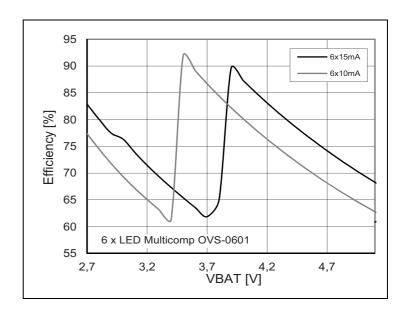

Figure 20: 100% PWM WLED Efficiency vs. VBAT

Page 16

Document Feedback

[v1-31] 2015-Feb-03

## **Detailed Description**

The AS3661 is a fully integrated lighting management unit for producing lighting effects for mobile devices. The AS3661 includes all necessary power management, high-side current sources, temperature compensation, two wire control interface and programmable pattern generators. The overall maximum current for each driver is set by an 8-bit register. The AS3661 controls LED luminance with a pulse width modulation (PWM) scheme with a resolution of 12 bits. The temperature compensation is also done by a PWM.

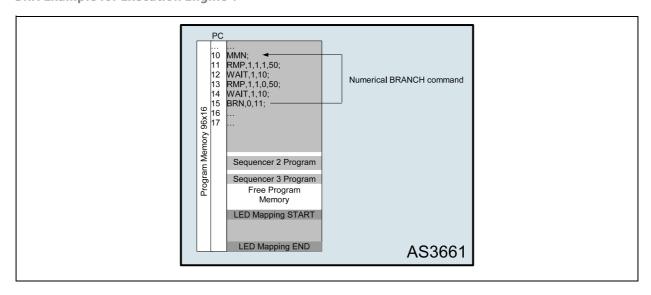

### **Programming**

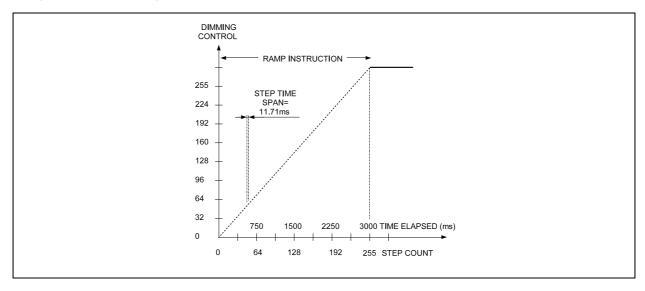

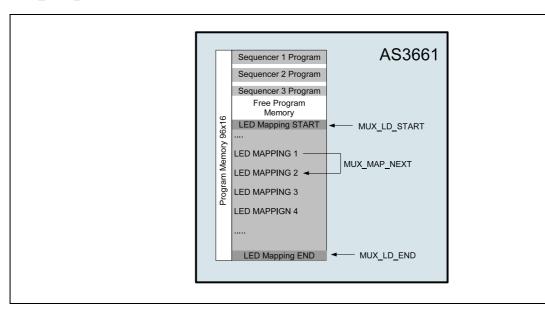

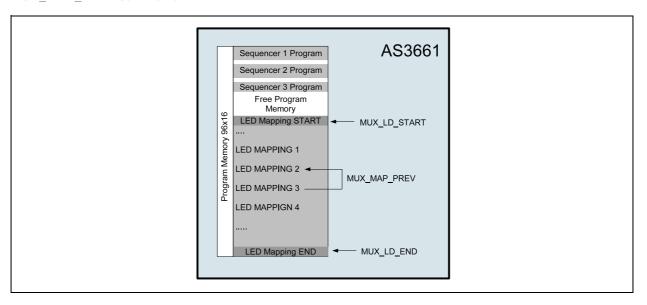

The AS3661 provides flexibility and programmability for dimming and sequencing control. Each LED can be controlled directly and independently through the serial bus or LED drivers can be grouped together for pre-programmed flashing patterns. The AS3661 has three independent program execution engines, so it is possible to form three independently programmable LED banks. LED drivers can be grouped based on their function so that, for example, the first bank of drivers can be assigned to the keypad illumination, the second bank to the "funlights" and the third group to the indicator LED(s). Each bank can contain 1 to 9 LED driver outputs. Instructions for program execution engines are stored in the program memory. The total amount of the program memory is 96 instructions and the user can allocate the memory as required by the engines.

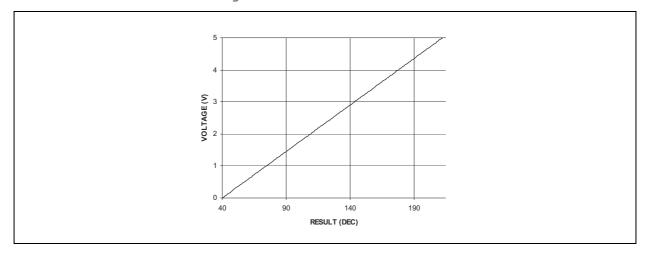

#### **LED Error Detection**

AS3661 has a built-in LED error detection. Error detection does not only detect open and short circuit, but provides an opportunity to measure the  $V_F$ 's of the LEDs. The test event is activated by a serial interface write and the result can be read through the serial interface during the next cycle. This feature can also be addressed to measure the voltage on VBAT, VCP and INT pins. Typical example usage includes monitoring battery voltage or using INT pin as a light sensor interface.

#### **Energy Efficiency**

When charge pump automatic mode selection is enabled, the AS3661 monitors the voltage over the drivers of LED1 to LED6 so that the device can select the best charge pump gain and maintain good efficiency over the whole operating voltage range. The red LED element of an RGB LED typically has a forward voltage of about 2V. For that reason, the outputs LED7, LED8 and LED9 are internally powered by VBAT, since battery voltage is high enough to drive red LEDs over the whole operating voltage range. This allows to drive three RGB LEDs with good efficiency because the red LEDs doesn't load the charge pump. AS3661 is able to automatically enter power-save mode, when LED outputs are not active and thus lowering idle current consumption down to  $10\mu A$  (typ.). During the

ams Datasheet Page 17

[v1-31] 2015-Feb-03 Document Feedback

"downtime" of the PWM cycle (constant current output status is low) additional power savings can be achieved when the PWM power save feature is enabled.

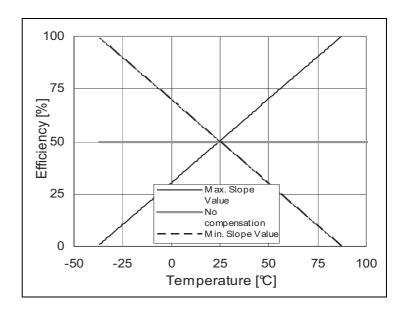

### **Temperature Compensation**

The luminance of an LED is typically a function of its temperature even though the current flowing through the LED remains constant. Since luminance is temperature dependent, many LED applications require some form of temperature compensation to decrease luminance and color purity variations due to temperature changes. The AS3661 has a build in temperature sensing element and PWM duty cycle of the LED drivers changes linearly in relationship to changes in temperature. User can select the slope of the graph (31 slopes) based on the LED characteristics. This compensation can be done either constantly, or only right after when the device wakes up from power save mode, to avoid error due to self-heating of the device. Linear compensation is considered to be practical and accurate enough for most LED applications. Compensation is effective over the temperature range from -40°C to 90°C.

Figure 21: Temperature Compensation Principle

Page 18

Document Feedback

[v1-31] 2015-Feb-03

Figure 22: AS3661 - Block Diagram

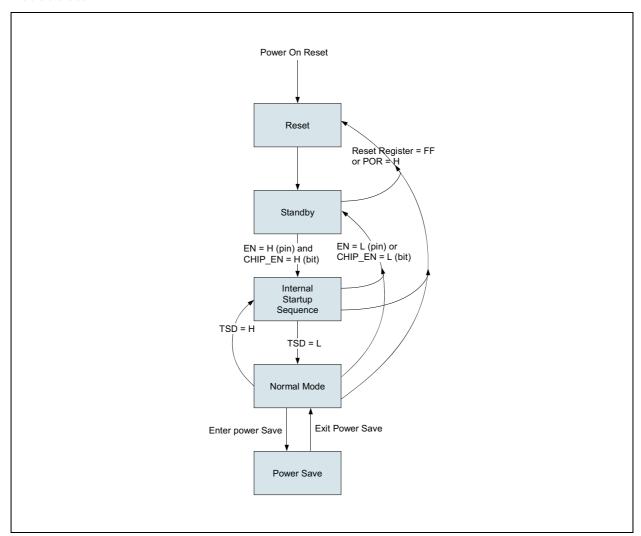

## **Modes of Operation**

The following are the different modes of operation of AS3661

#### RESET

In the RESET mode all the internal registers are reset to the default values. Reset is entered always if Reset Register (3DH) is written FFH or internal Power ON Reset is active. Power ON Reset (POR) will activate during the chip startup or when the supply voltage V<sub>BAT</sub> fall below 1.5V (typ.). Once V<sub>BAT</sub> rises above 1.5V (typ.) POR will be inactivate and the chip will continue to the STANDBY mode. CHIP\_EN control bit is low after POR by default.

#### **STANDBY**

The STANDBY mode is entered if the register bit CHIP\_EN or EN pin is logic low and Reset is not active. This is the low power consumption mode, when all circuit functions are disabled. Registers can be written in this mode if EN pin is logic high so that the control bits will be effective right after the start up.

ams Datasheet Page 19

[v1-31] 2015-Feb-03 Document Feedback

#### **STARTUP**

When CHIP\_EN bit is written high and the EN pin is high, the INTERNAL STARTUP SEQUENCE powers up all the needed internal blocks ( $V_{REF}$ , Bias, Oscillator etc.). Startup delay is 500  $\mu$ s. If the chip temperature rises too high, the Thermal Shutdown (TSD) disables the chip operation and chip waits in STARTUP mode until no thermal shutdown event is present.

#### NORMAL

During NORMAL mode the user controls the chip using the Control Registers.

#### **POWER SAVE**

In POWER SAVE mode analog blocks are disabled to minimize power consumption. (see Automatic Power Save Mode).

Figure 23: Mode Select

Page 20

Document Feedback

[v1-31] 2015-Feb-03

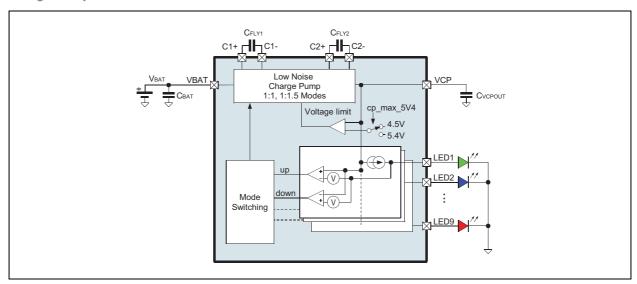

## **Charge Pump Operational Description**

#### Overview

The AS3661 includes a pre-regulated switched-capacitor charge pump with a programmable voltage multiplication of 1 and 1.5x. In 1.5x mode by combining the principles of a switched-capacitor charge pump and a linear regulator, it generates a regulated 4.5V output from Li-lon input voltage range. A two-phase non-overlapping clock generated internally controls the operation of the charge pump. During the charge phase, both flying capacitors ( $C_{FLY1}$  and  $C_{FLY2}$ ) are charged from input voltage. In the pump phase that follows, the flying capacitors are discharged to output. A traditional switched capacitor charge pump operating in this manner will use switches with very low on-resistance, ideally  $0\Omega$ , to generate an output voltage that is 1.5x the input voltage. The AS3661 regulates the output voltage by controlling the resistance of the input-connected pass-transistor switches in the charge pump.

Figure 24: **Charge Pump**

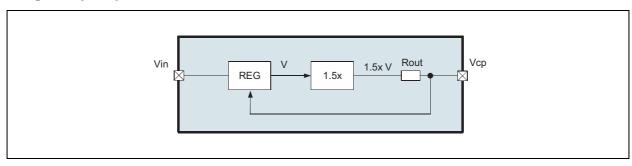

#### **Output Resistance**

At lower input voltages, the charge pump output voltage may degrade due to effective output resistance (R<sub>OUT</sub>) of the charge pump. The expected voltage drop can be calculated by using a simple model for the charge pump illustrated in Figure 25 below.

ams Datasheet Page 21 **Document Feedback**

Figure 25: Charge Pump Output Resistance

The model shows a linear pre-regulation block (REG), a voltage multiplier (1.5x), and an output resistance (R<sub>OUT</sub>). The output resistance models the output voltage drop that is inherent to switched capacitor converters. The output resistance is  $3.5\Omega$ (typ.), and it is a function of switching frequency, input voltage, flying capacitors' capacitance value, internal resistances of the switches and ESR of the flying capacitors. When the output voltage is in regulation, the regulator in the model controls the voltage V to keep the output voltage equal to 4.5V (typ.). With increased output current, the voltage drop across ROUT increases. To prevent drop in output voltage, the voltage drop across the regulator is reduced, V increases, and V<sub>CP</sub> remains at 4.5V. When the output current increases to the point that there is zero voltage drop across the regulator, V equals the input voltage, and the output voltage is "on the edge" of regulation. Additional output current causes the output voltage to fall out of regulation, so that the operation is similar to a basic open-loop 1.5x charge pump. In this mode, output current results in output voltage drop proportional to the output resistance of the charge pump. The out-of-regulation output voltage can be approximated by:

(EQ1)

$$V_{CP} = 1.5 \times V_{IN} - I_{OUT} \times R_{OUT}$$

.

### **Controlling the Charge Pump**

The charge pump is controlled with two CP\_MODE bits in MISC register (address 36H). When both of the bits are low, the charge pump is disabled and the output voltage is pulled down with an internal 300  $k\Omega$  (typ.) resistor. The charge pump can be forced to bypass mode, so that the battery voltage is connected directly to the current sources. In 1.5x mode the output voltage is boosted to 4.5V. In automatic mode the charge pump operation mode is determined by saturation of constant current drivers, like described in chapter LED Forward Voltage Monitoring.

#### **LED Forward Voltage Monitoring**

When the charge pump automatic mode selection is enabled, the voltages over the LED drivers LED1 to LED6 are monitored.

**Note(s):** Power input for current source outputs LED7, LED8 and LED9 are internally connected to the VBAT pin.

Page 22

Document Feedback

[v1-31] 2015-Feb-03

If the LED1 to LED6 drivers do not have enough headroom, the charge pump gain is set to 1.5x. Driver saturation monitor does not have a fixed voltage limit, since saturation voltage is a function of temperature and current. The charge pump gain is set to 1x, when the battery voltage is high enough to supply all LEDs. In automatic gain change mode, the charge pump is switched to bypass mode (1x), when LEDs are inactive for over 50 ms.

## **Gain Change Hysteresis**

The charge pump gain control utilizes digital filtering to prevent supply voltage disturbances (for example, the transient voltage on the power supply during the GSM burst) from triggering unnecessary gain changes. Hysteresis is provided to prevent periodic gain changes, which would occur due to LED driver and charge pump voltage drop in 1x mode. The hysteresis of the gain change is user configurable, default setting is factory programmable. Flexible configuration ensures, that the hysteresis can be minimized or set to desired level in each application. LED forward voltage monitoring and gain control block diagram is shown in Figure 26.

Figure 26: Forward Voltage Monitoring and Gain Control Block

ams Datasheet Page 23

[v1-31] 2015-Feb-03 Document Feedback

#### **Automatic Power Save Mode**

Automatic power save mode is enabled when POWERSAVE\_EN bit in register address 36H is '1'. Almost all analog blocks are powered down in power save, if an external clock signal is used. Only the charge pump protection circuits remain active. However, if the internal clock has been selected, only charge pump and LED drivers are disabled during the power save; the digital part of the LED controller needs to stay active. In both cases the charge pump enters to the weak 1x mode. In this mode the charge pump utilizes a passive current limited keep-alive switch, which keeps the output voltage at the battery level. During the program execution AS3661 can enter power save if there is no PWM activity in any of the LED driver outputs. To prevent short power save sequences during program execution, AS3661 has an instruction look-ahead filter. During program execution engine 1, engine 2 and engine 3 instructions are constantly analyzed, and if there is time intervals of more than 50ms in length with no PWM activity on LED driver outputs, the device will enter power save. In power save mode program execution continues uninterruptedly. When an instruction that requires PWM activity is executed, a fast internal startup sequence will be started automatically.

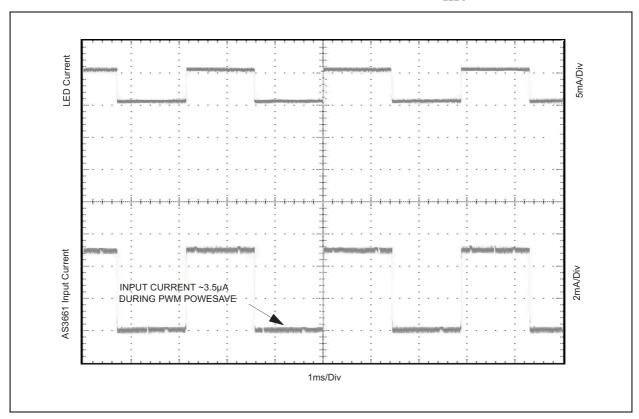

#### **PWM Power Save Mode**

PWM cycle power save mode is enabled when register 36 bit [2] PWM\_PS\_EN is set to '1'. In PWM power save mode analog blocks are powered down during the "down time" of the PWM cycle. Blocks that are powered down depends whether external or internal clock is used. While the Automatic Power Save Mode (see above) saves energy when there is no PWM activity at all, the PWM Power Save mode saves energy during PWM cycles. Like the Automatic Power Save Mode, PWM Power Save Mode works also during program execution.

Page 24

Document Feedback [v1-31] 2015-Feb-03

Figure 27: PWM Powersave Principle with External Clock (VDD =3.6V, 50% PWM, I<sub>LED9</sub>=5mA)

## **LED Driver Operational Description**

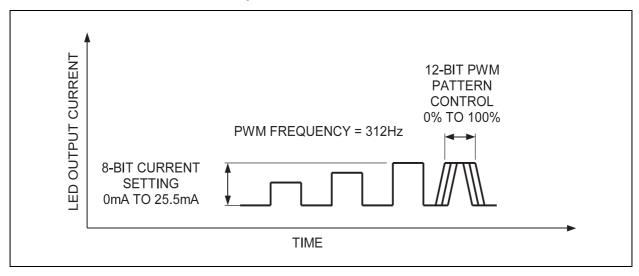

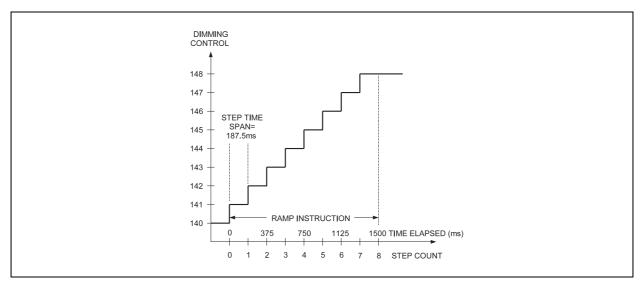

AS3661 LED drivers are constant current sources. The output current can be programmed by control registers up to 25.5 mA. The overall maximum current is set by 8-bit output current control registers with 100  $\mu$ A step size. Each of the 9 LED drivers has a separate output current control register. The LED luminance pattern (dimming) is controlled with PWM (pulse width modulation) technique, which has internal resolution of 12 bits (8-bit control can be seen by user). PWM frequency is 312 Hz (see Figure 28).

ams Datasheet Page 25

[v1-31] 2015-Feb-03 Document Feedback

Figure 28: LED Pattern and Current Control Principle

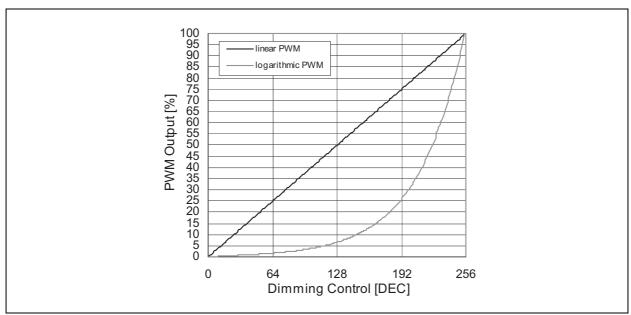

LED dimming is controlled according to a logarithmic or linear scale (see Figure 29). Logarithmic or linear scheme can be set for both the program execution engine control and direct PWM control.

Figure 29: Logarithmic vs. Linear Dimming

**Note(s):** If the temperature compensation is active, the maximum PWM duty cycle is limited to 50% at 25°C. This is required to allow enough headroom for temperature compensation over the whole temperature range -40 °C to 90°C.

Page 26

Document Feedback

[v1-31] 2015-Feb-03

#### **Powering LEDs**

Although the AS3661 is very suitable for white LED and general purpose applications, it is particularly well suited to use with RGB LEDs. The AS3661 architecture is optimized for use with three RGB LEDs. Typically, the red LEDs have forward voltages below 2V and thus red LEDs can be powered directly from  $V_{BAT}$ . In AS3661 the LED7, LED8 and LED9 drivers are directly powered from the battery voltage ( $V_{BAT}$ ), not from the charge pump output. The LED1 to LED6 drivers are internally connected to the charge pump output and these outputs can be used for driving green and blue ( $V_{F}=2.7 \mbox{V}$  to 3.7V) or white LEDs. Of course, LED7, LED8 and LED9 outputs can be used for green, blue or white LEDs if the VBAT voltage is high enough. An RGB LED configuration example is given in the Typical Applications section.

#### **Controlling the High-side LED Drivers**

· Direct PWM Control

All AS3661 LED drivers, LED1 to LED9, can be controlled independently through the two-wire serial I<sup>2</sup>C compatible interface. For each high-side driver there is a PWM control register. Direct PWM control is active by default.

• Controlling by Program Execution Engines

Engine control is used when the user wants to create programmed sequences. The program execution engine has higher priority than direct control registers. Therefore if the user has set to PWM register a certain value it will be automatically overridden when the program execution engine controls the driver. LED control and program execution engine operation is described in the chapter Control Register Details.

Master Fader Control

In addition to LED-by-LED PWM register control, the AS3661 is equipped with so called master fader control, which allows the user to fade in or fade out multiple LEDs by writing to only one register. This is an useful function to minimize serial bus traffic between the MCU and the AS3661. The AS3661 has three master fader registers, so it is possible to form three master fader groups. Master fader control can be used with the engines as well.

ams Datasheet Page 27

[v1-31] 2015-Feb-03 Document Feedback

## I<sup>2</sup>C Compatible Control Interface

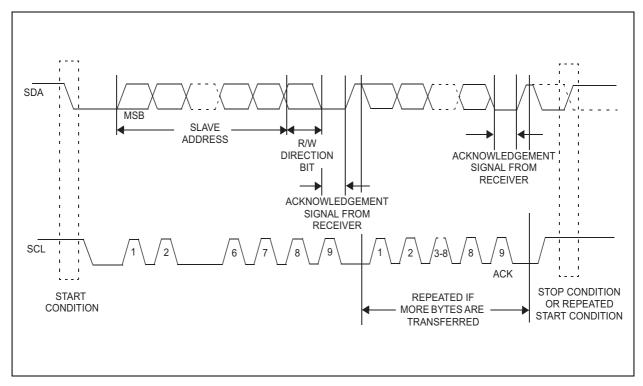

The AS3661 supports the I<sup>2</sup>C bus protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are referred to as slaves. A master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions must control the bus.

The AS3661 operates as a slave on the I<sup>2</sup>C bus. Within the bus specifications a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. The AS3661 works in both modes. Connections to the bus are made through the open-drain I/O lines SDA and SCL Figure 30.

## I<sup>2</sup>C Address Selection

The slave address can be selected depending on the connection of the two address selection pins ASELO and ASEL1. The selected address for reading and writing depending on the state of ASELO and ASEL1 can be found in Figure 30 below.

Figure 30: Chip Address Configuration

| ASEL1           | ASEL0           | Address | 8 bit Hex Address |

|-----------------|-----------------|---------|-------------------|

| ASLLI           | ASELV           | (Hex)   | R/W               |

| GND             | GND             | 32      | 64/65             |

| GND             | V <sub>EN</sub> | 33      | 66/67             |

| V <sub>EN</sub> | GND             | 34      | 68/69             |

| V <sub>EN</sub> | V <sub>EN</sub> | 35      | 6A/6B             |

The following bus protocol has been defined (Figure 31):

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH are interpreted as control signals.

Accordingly, the following bus conditions have been defined:

## **Bus Not Busy**

Both data and clock lines remain HIGH.

#### Start Data Transfer

A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

Page 28

Document Feedback

[v1-31] 2015-Feb-03

#### Stop Data Transfer

A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

#### Data Valid

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions are not limited, and are determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

#### Acknowledge

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

ams Datasheet Page 29

[v1-31] 2015-Feb-03 Document Feedback

Figure 31:

Data Transfer on I<sup>2</sup>C Serial Bus

Depending upon the state of the R/W bit, two types of data transfer are possible:

- Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first.

- 2. **Data transfer from a slave transmitter to a master receiver.** The master transmits the first byte (the slave address). The slave then returns an acknowledge bit, followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a "not acknowledge" is returned. The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus is not released. Data is transferred with the most significant bit (MSB) first.

The AS3661 can operate in the following two modes:

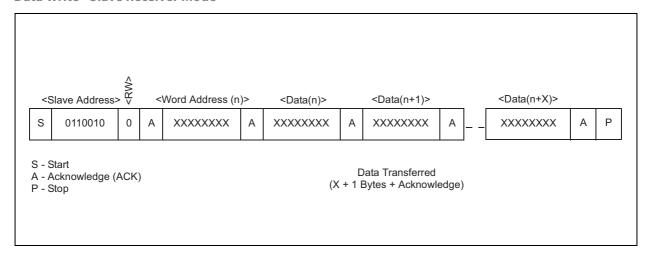

Slave Receiver Mode (Write Mode): Serial data and clock are received through SDA and SCL. After each byte is received an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit (see Figure 32). The slave

Page 30

Document Feedback

[v1-31] 2015-Feb-03

address byte is the first byte received after the master generates the START condition. The slave address byte contains the 7-bit AS3661 address, which is 0110010<sup>1</sup>, followed by the direction bit (R/W), which, for a write, is 0<sup>2</sup>. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA line. After the AS3661 acknowledges the slave address + write bit, the master transmits a register address to the AS3661. This sets the register pointer on the AS3661. The master may then transmit zero or more bytes of data (if more than one data byte is written see also Blockwrite/read boundaries), with the AS3661 acknowledging each byte received. The address pointer will increment after each data byte is transferred. The master generates a STOP condition to terminate the data write.

2. Slave Transmitter Mode (Read Mode): The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit indicates that the transfer direction is reversed. Serial data is transmitted on SDA by the AS3661 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer (Figure 32 and Figure 33). The slave address byte is the first byte received after the master generates a START condition. The slave address byte contains the 7-bit AS3661 address, which is 0110010, followed by the direction bit (R/W), which, for a read, is 1<sup>3</sup>. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA line. The AS3661 then begins to transmit data starting with the register address pointed to by the register pointer (if more than one data byte is read see Blockwrite/read boundaries). If the register pointer is not written to before the initiation of a read mode the first address that is read is the last one stored in the register pointer. The AS3661 must receive a "not acknowledge" to end a read.

ams Datasheet Page 31

[v1-31] 2015-Feb-03 Document Feedback

<sup>1. &#</sup>x27;The I2C address' depends on the external connection of ASEL0 and ASEL1; see Chip Address Configuration.

<sup>2.</sup> The address for writing to the AS3661 is 8Xh = 01100100b - see Figure 30.

<sup>3.</sup> The address for read mode from the AS3661 is 8Xh+1 = 01100101b - Figure 30.

Figure 32:

Data Write - Slave Receiver Mode

Figure 33:

Data Read (Write Pointer, Then Read) - Slave Receive and Transmit

#### **Program Downloading**

First the register page\_select is set to the program page, which should be accessed. Then the program page (part of or full page) can be downloaded to the registers Cmd\_0\_MSB, Cmd\_0\_LSB, Cmd\_1\_MSB, Cmd\_1\_LSB to Cmd\_F\_MSB, Cmd\_F\_LSB (I<sup>2</sup>C registers area 50h to 6Fh).

Page 32

Document Feedback

[v1-31] 2015-Feb-03

Figure 34: Page\_Select Register

|     | Addr: 4Fh   |         |        | Pag         | e_Select Register        |  |

|-----|-------------|---------|--------|-------------|--------------------------|--|

| Bit | Bit Name    | Default | Access | Description |                          |  |

|     |             |         |        | Selects p   | rogram page for download |  |

|     |             |         |        | 000         | page 0 -Addr 00h-0Fh     |  |

|     |             |         |        | 001         | page 1 -Addr 10h-1Fh     |  |

|     |             |         |        | 010         | page 2 -Addr 20h-2Fh     |  |

| 2:0 | page_select | 000b    | R/W    | 011         | page 3 -Addr 30h-3Fh     |  |

|     |             |         |        | 100         | page 4 -Addr 40h-4Fh     |  |

|     |             |         |        | 101         | page 5 -Addr 50h-5Fh     |  |

|     |             |         |        | 110         | Do not use               |  |

|     |             |         |        | 111         | Do not use               |  |

## **Register Set**

The AS3661 is controlled by a set of registers through the two wire serial interface port. Some register bits are reserved for future use. Figure 35 below lists device registers, their addresses and their abbreviations. A more detailed description is given in Control Register Details.

Figure 35: **Description of Registers**

| Hex<br>Add-<br>ress | Register Name             | Bit(s) | Туре  | Default<br>Value After<br>Reset | Description                                     |          |                                                 |                  |

|---------------------|---------------------------|--------|-------|---------------------------------|-------------------------------------------------|----------|-------------------------------------------------|------------------|

|                     |                           |        |       |                                 | CHIP_EN                                         |          |                                                 |                  |

|                     |                           | [6]    | [6]   | R/W                             | R/W                                             | x0xxxxxx | 0 AS3661 not enabled                            |                  |

|                     |                           |        |       |                                 |                                                 |          |                                                 | 1 AS3661 enabled |

| 00                  | ENABLE / ENGINE<br>CNTRL1 | [5:4]  | [5:4] |                                 |                                                 | xx00xxxx | ENGINE1_EXEC Engine 1 program execution control |                  |

|                     |                           | [3:2]  |       | xxxx00xx                        | ENGINE2_EXEC Engine 2 program execution control |          |                                                 |                  |

|                     |                           | [1:0]  |       | xxxxxx00                        | ENGINE3_EXEC Engine 3 program execution control |          |                                                 |                  |

ams Datasheet Page 33 [v1-31] 2015-Feb-03 Document Feedback

| Hex<br>Add-<br>ress | Register Name                     | Bit(s) | Туре | Default<br>Value After<br>Reset | Description                                               |

|---------------------|-----------------------------------|--------|------|---------------------------------|-----------------------------------------------------------|

| 01                  | ENGINE CNTRL2                     | [5:4]  | R/W  | xx00xxxx                        | ENGINE1_MODE<br>ENGINE 1 mode control                     |

|                     |                                   | [3:2]  |      | xxxx00xx                        | ENGINE2_MODE<br>ENGINE 2 mode control                     |

|                     |                                   | [1:0]  |      | xxxxxx00                        | ENGINE3_MODE<br>ENGINE 3 mode control                     |

| 02                  | OUTPUT DIRECT/<br>RATIOMETRIC MSB | [0]    | R/W  | xxxxxxx0                        | LED9_RATIO_EN Enables ratiometric dimming for LED9 output |

| 03                  | OUTPUT DIRECT/<br>RATIOMETRIC LSB | [7]    | R/W  | 0xxxxxxx                        | LED8_RATIO_EN Enables ratiometric dimming for LED8 output |

|                     |                                   | [6]    |      | x0xxxxxx                        | LED7_RATIO_EN Enables ratiometric dimming for LED7 output |

|                     |                                   | [5]    |      | xx0xxxxx                        | LED6_RATIO_EN Enables ratiometric dimming for LED6 output |

|                     |                                   | [4]    |      | xxx0xxxx                        | LED5_RATIO_EN Enables ratiometric dimming for LED5 output |

|                     |                                   | [3]    |      | xxxx0xxx                        | LED4_RATIO_EN Enables ratiometric dimming for LED4 output |

|                     |                                   | [2]    |      | xxxxx0xx                        | LED3_RATIO_EN Enables ratiometric dimming for LED3 output |

|                     |                                   | [1]    |      | xxxxxx0x                        | LED2_RATIO_EN Enables ratiometric dimming for LED2 output |

|                     |                                   | [0]    |      | xxxxxxx0                        | LED1_RATIO_EN Enables ratiometric dimming for LED1 output |

| 04                  | OUTPUT ON/OFF<br>CONTROL MSB      | [0]    | R/W  | xxxxxxx1                        | LED9_ON<br>ON/OFF Control for LED9 output                 |

Page 34

Document Feedback

[v1-31] 2015-Feb-03

| Hex<br>Add-<br>ress | Register Name                  | Bit(s) | Туре  | Default<br>Value After<br>Reset | Description                                                |

|---------------------|--------------------------------|--------|-------|---------------------------------|------------------------------------------------------------|

| 05                  | OUTPUT ON / OFF<br>CONTROL LSB | [7]    | . R/W | 1xxxxxxx                        | LED8_ON ON/OFF Control for LED8 output                     |

|                     |                                | [6]    |       | x1xxxxxx                        | LED7_ON ON/OFF<br>Control for LED7 output                  |

|                     |                                | [5]    |       | xx1xxxxx                        | LED6_ON ON/OFF Control for LED6 output                     |

|                     |                                | [4]    |       | xxx1xxxx                        | LED5_ON<br>ON/OFF Control for LED5 output                  |

|                     |                                | [3]    |       | xxxx1xxx                        | LED4_ON ON/OFF Control for LED4 output                     |

|                     |                                | [2]    |       | xxxxx1xx                        | LED3_ON<br>ON/OFF Control for LED3 output                  |

|                     |                                | [1]    |       | xxxxxx1x                        | LED2_ON ON/OFF Control for LED2 output                     |

|                     |                                | [0]    |       | xxxxxxx1                        | LED1_ON ON/OFF Control for LED1 output                     |

| 06                  | LED1 CONTROL                   | [7:6]  | R/W   | 00xxxxxx                        | MAPPING Mapping for LED1 output                            |

|                     |                                | [5]    |       | xx0xxxxx                        | LOG_EN Logarithmic dimming control for LED1                |

|                     |                                | [4:0]  |       | xxx00000                        | TEMP COMP Temperature compensation control for LED1 output |

| 07                  | LED2 CONTROL                   | [7:6]  | R/W   | 00xxxxxx                        | MAPPING Mapping for LED2 output                            |

|                     |                                | [5]    |       | xx0xxxxx                        | LOG_EN Logarithmic dimming control for LED2 output         |

|                     |                                | [4:0]  |       | xxx00000                        | TEMP COMP Temperature compensation control for LED2 output |

| 08                  | LED3 CONTROL                   | [7:6]  | R/W   | 00xxxxxx                        | MAPPING Mapping for LED3 output                            |

|                     |                                | [5]    |       | xx0xxxxx                        | LOG_EN Logarithmic dimming control for LED3 output         |

|                     |                                | [4:0]  |       | xxx00000                        | TEMP COMP Temperature compensation control for LED3 output |

ams Datasheet Page 35

[v1-31] 2015-Feb-03 Document Feedback

| Hex<br>Add-<br>ress | Register Name | Bit(s) | Туре | Default<br>Value After<br>Reset | Description                                                |

|---------------------|---------------|--------|------|---------------------------------|------------------------------------------------------------|

| 09                  | LED4 CONTROL  | [7:6]  | R/W  | 00xxxxxx                        | MAPPING Mapping for LED4 output                            |

|                     |               | [5]    |      | xx0xxxxx                        | LOG_EN Logarithmic dimming control for LED4 output         |

|                     |               | [4:0]  |      | xxx00000                        | TEMP COMP Temperature compensation control for LED4 output |

|                     | LED5 CONTROL  | [7:6]  | R/W  | 00xxxxxx                        | MAPPING Mapping for LED5 output                            |

| OA                  |               | [5]    |      | xx0xxxxx                        | LOG_EN Logarithmic dimming control for LED5 output         |

|                     |               | [4:0]  |      | xxx00000                        | TEMP COMP Temperature compensation control for LED5 output |

| OB                  | LED6 CONTROL  | [7:6]  | R/W  | 00xxxxxx                        | MAPPING Mapping for LED6 output                            |

|                     |               | [5]    |      | xx0xxxxx                        | LOG_EN Logarithmic dimming control for LED6 output         |

|                     |               | [4:0]  |      | xxx00000                        | TEMP COMP Temperature compensation control for LED6 output |

| 0C                  | LED7 CONTROL  | [7:6]  | R/W  | 00xxxxxx                        | MAPPING Mapping for LED7 output                            |

|                     |               | [5]    |      | xx0xxxxx                        | LOG_EN Logarithmic dimming control for LED7 output         |

|                     |               | [4:0]  |      | xxx00000                        | TEMP COMP Temperature compensation control for LED7 output |

| 0D                  | LED8 CONTROL  | [7:6]  | R/W  | 00xxxxxx                        | MAPPING Mapping for LED8 output                            |

|                     |               | [5]    |      | xx0xxxxx                        | LOG_EN Logarithmic dimming control for LED8 output         |

|                     |               | [4:0]  |      | xxx00000                        | TEMP COMP Temperature compensation control for LED8 output |

Page 36ams DatasheetDocument Feedback[v1-31] 2015-Feb-03

| Hex<br>Add-<br>ress | Register Name           | Bit(s) | Туре | Default<br>Value After<br>Reset | Description                                                                |

|---------------------|-------------------------|--------|------|---------------------------------|----------------------------------------------------------------------------|

|                     |                         | [7:6]  |      | 00xxxxxx                        | MAPPING Mapping for LED9 output                                            |

| 0E                  | LED9 CONTROL            | [5]    | R/W  | xx0xxxxx                        | LOG_EN Logarithmic dimming control for LED9 output                         |

|                     |                         | [4:0]  |      | xxx00000                        | TEMP COMP Temperature compensation control for LED9 output                 |

| 0F to 15            |                         | [7:0]  |      |                                 | Reserved                                                                   |

| 16                  | LED1 PWM                | [7:0]  | R/W  | 00000000                        | PWM duty cycle control for LED1                                            |

| 17                  | LED2 PWM                | [7:0]  | R/W  | 00000000                        | PWM duty cycle control for LED2                                            |

| 18                  | LED3 PWM                | [7:0]  | R/W  | 00000000                        | PWM duty cycle control for LED3                                            |

| 19                  | LED4 PWM                | [7:0]  | R/W  | 00000000                        | PWM duty cycle control for LED4                                            |

| 1A                  | LED5 PWM                | [7:0]  | R/W  | 00000000                        | PWM duty cycle control for LED5                                            |

| 1B                  | LED6 PWM                | [7:0]  | R/W  | 00000000                        | PWM duty cycle control for LED6                                            |

| 1C                  | LED7 PWM                | [7:0]  | R/W  | 00000000                        | PWM duty cycle control for LED7                                            |

| 1D                  | LED8 PWM                | [7:0]  | R/W  | 00000000                        | PWM duty cycle control for LED8                                            |

| 1E                  | LED9 PWM                | [7:0]  | R/W  | 00000000                        | PWM duty cycle control for LED9                                            |

| 1F to 25            |                         | [7:0]  |      |                                 | Reserved                                                                   |

| 26                  | LED1 CURRENT<br>CONTROL | [7:0]  | R/W  | 10101111                        | CURRENT<br>LED1 output current control register.<br>Default 17.5 mA (typ.) |

| 27                  | LED2 CURRENT<br>CONTROL | [7:0]  | R/W  | 10101111                        | CURRENT<br>LED2 output current control register.<br>Default 17.5 mA (typ.) |

| 28                  | LED3 CURRENT<br>CONTROL | [7:0]  | R/W  | 10101111                        | CURRENT<br>LED3 output current control register.<br>Default 17.5 mA (typ.) |

| 29                  | LED4 CURRENT<br>CONTROL | [7:0]  | R/W  | 10101111                        | CURRENT<br>LED4 output current control register.<br>Default 17.5 mA (typ.) |

| 2A                  | LED5 CURRENT<br>CONTROL | [7:0]  | R/W  | 10101111                        | CURRENT<br>LED5 output current control register.<br>Default 17.5 mA (typ.) |

| 2B                  | LED6 CURRENT<br>CONTROL | [7:0]  | R/W  | 10101111                        | CURRENT<br>LED6 output current control register.<br>Default 17.5 mA (typ.) |

| Hex<br>Add-<br>ress | Register Name           | Bit(s) | Туре | Default<br>Value After<br>Reset | Description                                                                |

|---------------------|-------------------------|--------|------|---------------------------------|----------------------------------------------------------------------------|

| 2C                  | LED7 CURRENT<br>CONTROL | [7:0]  | R/W  | 10101111                        | CURRENT<br>LED7 output current control register.<br>Default 17.5 mA (typ.) |

| 0x2D                | LED8 CURRENT<br>CONTROL | [7:0]  | R/W  | 10101111                        | CURRENT<br>LED8 output current control register.<br>Default 17.5 mA (typ.) |

| 0x2E                | LED9 CURRENT<br>CONTROL | [7:0]  | R/W  | 10101111                        | CURRENT<br>LED9 output current control register.<br>Default 17.5 mA (typ.) |

| 2F to 35            |                         | [7:0]  |      |                                 | Reserved                                                                   |

|                     |                         | [7]    |      | 0xxxxxxx                        | VARIABLE_D_SEL Variable LED source selection                               |

|                     |                         | [6]    | R/W  | x1xxxxxx                        | EN_AUTO_INCR<br>Serial bus address auto increment<br>enable                |

|                     |                         | [5]    |      | xx0xxxxx                        | POWERSAVE_EN Powersave mode enable                                         |

| 36                  | MISC                    | [4:3]  |      | xxx00xxx                        | CP_MODE<br>Charge pump gain selection                                      |

|                     |                         | [2]    |      | xxxxx0xx                        | PWM_PS_EN PWM cycle powersave enable                                       |

|                     |                         | [1]    |      | xxxxxx0x                        | CLK_DET_EN External clock detection                                        |

|                     |                         | [0]    |      | xxxxxxx0                        | INT_CLK_EN Clock source selection                                          |

| 37                  | ENGINE1 PC              | [6:0]  | R/W  | x0000000                        | PC Program counter for engine 1                                            |

| 38                  | ENGINE2 PC              | [6:0]  | R/W  | x0000000                        | PC Program counter for engine 2                                            |

| 39                  | ENGINE3 PC              | [6:0]  | R/W  | x0000000                        | PC Program counter for engine 3                                            |

Page 38ams DatasheetDocument Feedback[v1-31] 2015-Feb-03

| Hex<br>Add-<br>ress | Register Name         | Bit(s) | Туре | Default<br>Value After<br>Reset | Description                                                                                   |

|---------------------|-----------------------|--------|------|---------------------------------|-----------------------------------------------------------------------------------------------|

|                     |                       | [7]    |      | 0xxxxxx                         | LEDTEST_MEAS_DONE Indicates when the LED test measurement is done.                            |

|                     |                       | [6]    |      | x1xxxxxx                        | MASK_BUSY Mask bit for interrupts generated by STARTUP_BUSY or ENGINE_BUSY                    |

|                     |                       | [5]    |      | xx0xxxxx                        | STARTUP_BUSY This bit indicates that the start-up sequence is running                         |

| 3A                  | STATUS /<br>INTERRUPT | [4]    | R    | xxx0xxxx                        | ENGINE_BUSY This bit indicates that a program execution engine is clearing internal registers |

|                     | INTERNOFT             | [3]    |      | xxxx0xxx                        | EXT_CLK_USED Indicates when external clock signal is in use                                   |

|                     |                       | [2]    |      | xxxxx0xx                        | ENG1_INT Interrupt bit for program execution engine 1                                         |

|                     |                       | [1]    |      | xxxxxx0x                        | ENG2_INT Interrupt bit for program execution engine 2                                         |

|                     |                       | [0]    |      | xxxxxxx0                        | ENG3_INT Interrupt bit for program execution engine 3                                         |

|                     |                       | [2]    |      | xxxxx0xx                        | INT_CONF INT pin can be configured to function as a GPO with this bit                         |

| 3B                  | GPO                   | [1]    | R/W  | xxxxxx0x                        | GPO pin control                                                                               |

|                     |                       | [0]    |      | xxxxxxx0                        | INT_GPO GPO pin control for INT pin (when INT_CONF is set "1")                                |

| 3C                  | VARIABLE              | [7:0]  | R/W  | 00000000                        | VARIABLE<br>Global 8-bit variable                                                             |

| 3D                  | RESET                 | [7:0]  | R/W  | 00000011                        | RESET Writing 11111111 into this register resets the AS3661                                   |

ams Datasheet Page 39

[v1-31] 2015-Feb-03 Document Feedback

| Hex<br>Add-<br>ress | Register Name         | Bit(s) | Туре | Default<br>Value After<br>Reset | Description                                                       |

|---------------------|-----------------------|--------|------|---------------------------------|-------------------------------------------------------------------|

|                     |                       | [7]    | R    | 0xxxxxx                         | TEMP_MEAS_BUSY Indicates when temperature measurement is active   |

| 3E                  | TEMP ADC              | [2]    |      | xxxxx0xx                        | EN_TEMP_SENSOR Reads the internal temperature sensor once         |

| JL                  | CONTROL               | [1]    | R/W  | xxxxxx0x                        | CONTINUOUS_CONV Continuous temperature measurement selection      |