## **AS3701**

## Micro-PMIC

## **General Description**

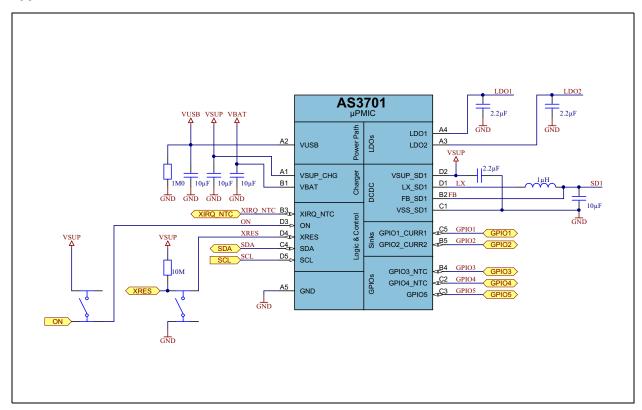

The AS3701 is a small compact PMU for small size and low power applications.

AS3701 features one 500mA DCDC buck converter operating from 1MHz up to 4MHz, two 200mA LDOs, two 40mA current sinks and offers additional GPIO functions. Further, the device contains an integrated linear battery charger with constant current and constant voltage operation. The wide charging current range going from 11mA up to 500mA and the integrated battery temperature monitoring with selectable NTC beta values make this device suitable for a great variety of applications.

The single supply voltage may vary from 2.7V to 5.5V and all functionalities of AS3701 can be controlled via the I<sup>2</sup>C interface.

Ordering Information and Content Guide appear at end of datasheet.

## **Key Benefits & Features**

The benefits and features of AS3701, Micro-PMIC are listed below:

Figure 1: **Added Value of Using AS3701**

| Benefits                                                                                                             | Features                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multiple rails in a compact design for low power applications                                                        | <ul> <li>2 x 200mA universal LDO (1.2V to 3.3V)</li> <li>500mA Step-down DCDC (0.6125V to 3.35V)</li> <li>2 programmable current sources up to 40mA</li> <li>Possible external PWM dimming input</li> </ul>                                                          |

| Self-contained Li-lon battery charger with power path                                                                | <ul> <li>Linear charger with internal transistor</li> <li>500mA max charging current</li> <li>Trickle-, constant current and constant voltage operation (3.82V to 4.44V)</li> <li>Charger timeout and temperature supervision</li> <li>NTC beta selection</li> </ul> |

| Flexible multi-purpose IOs for general control tasks and for standalone operation without I <sup>2</sup> C interface | <ul> <li>Wake-up / Stand-by / Power-down input</li> <li>PWM input/output</li> <li>Interrupt input/output</li> <li>Low battery and Power Good output</li> <li>Charging and USB current setting input</li> <li>Charger control input/output</li> </ul>                 |

| Benefits                                                          | Features                                                                                                                        |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Flexible and fast adaptation to different processors/applications | OTP programmable boot sequence                                                                                                  |

| Power saving control according to the processor's needs           | Stand-by function with programmable voltages                                                                                    |

| Self-contained start-up and safety shutdown feature               | <ul> <li>I<sup>2</sup>C control interface</li> <li>ON-key with 4/8s emergency power-down</li> <li>POR with Reset I/O</li> </ul> |

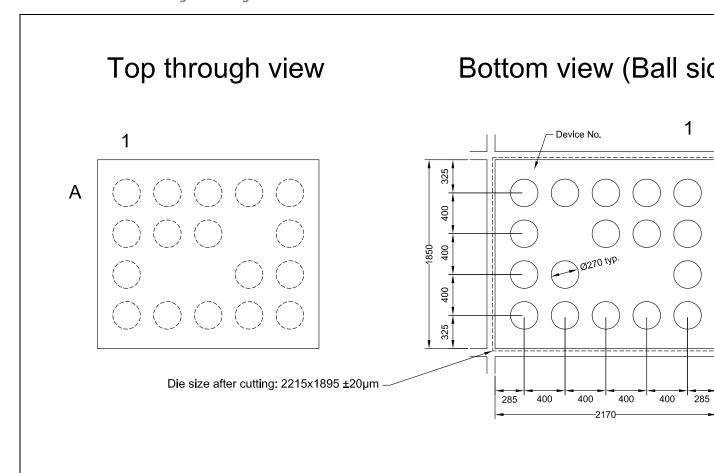

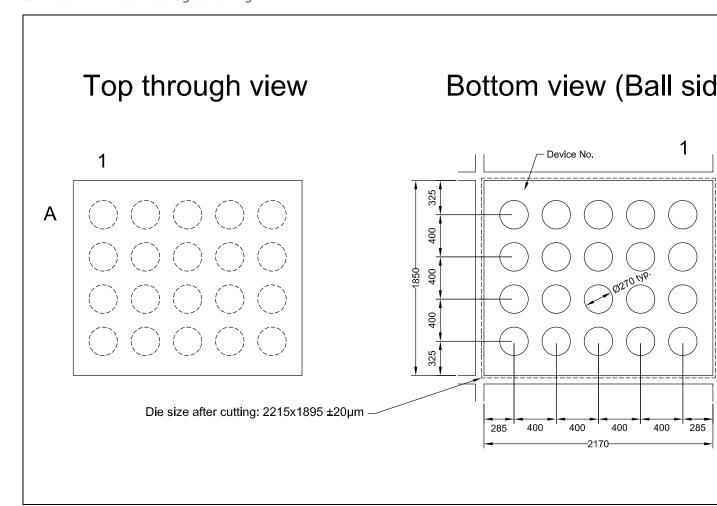

| Cost effective, small package optimized for<br>PCB cost or size   | <ul><li>17-balls WL-CSP with 0.4mm pitch</li><li>20-balls WL-CSP with 0.4mm pitch</li></ul>                                     |

## **Applications**

The device is a PMU for low power applications like sport watches, smart watches, handheld GPS devices, mobile phones and any other 1-cell Li+ powered devices.

Page 2 ams Datasheet

Document Feedback [v1-11] 2016-Dec-14

## **Block Diagram**

The functional blocks of this device are shown below:

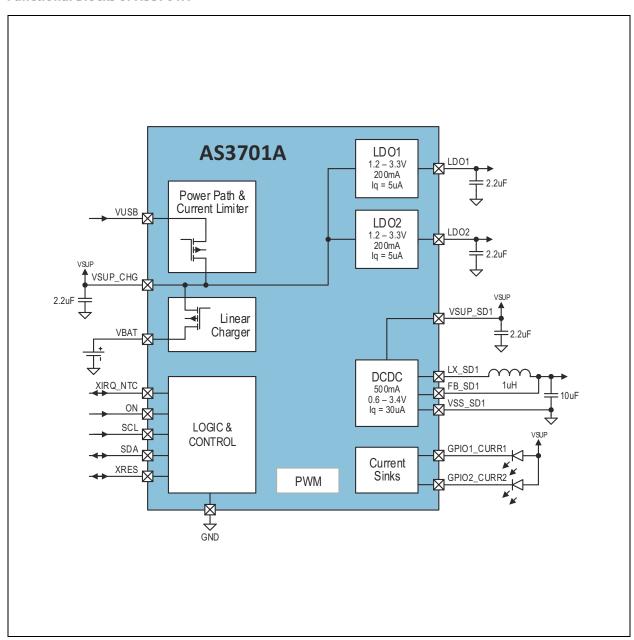

Figure 2: Functional Blocks of AS3701A

Block Diagram: This figure shows the block diagram of the AS3701A

ams Datasheet Page 3

[v1-11] 2016-Dec-14 Document Feedback

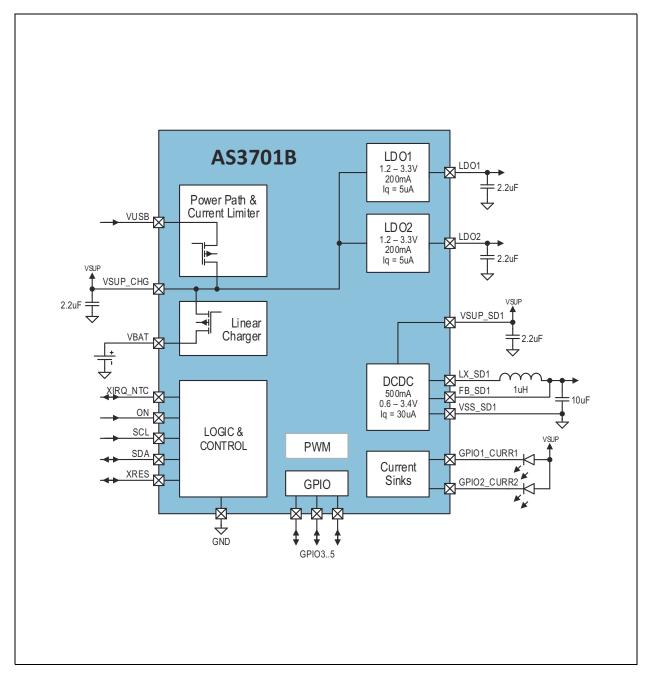

Figure 3: Functional Blocks of AS3701B

**Block Diagram:** This figure shows the block diagram of the AS3701B

Page 4

Document Feedback

[v1-11] 2016-Dec-14

## **Pin Assignments**

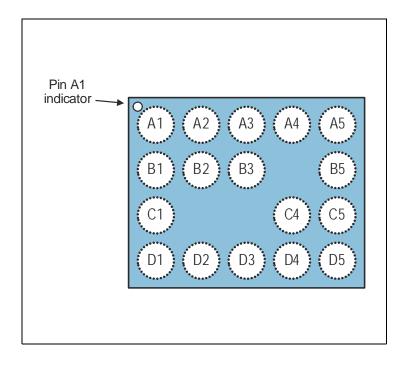

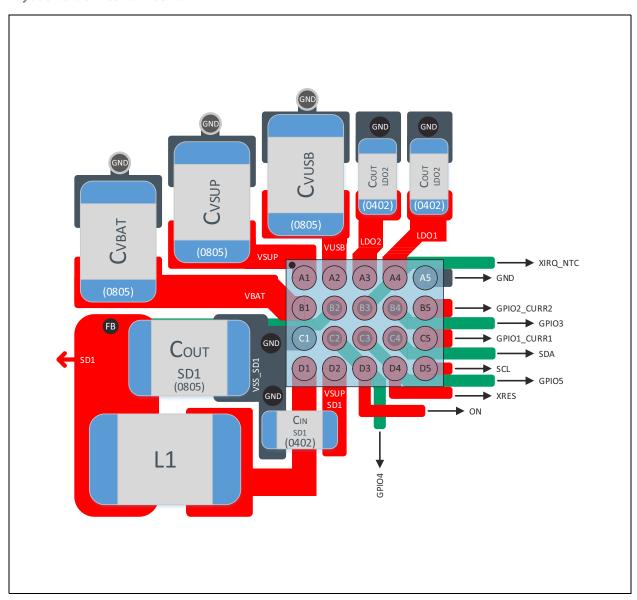

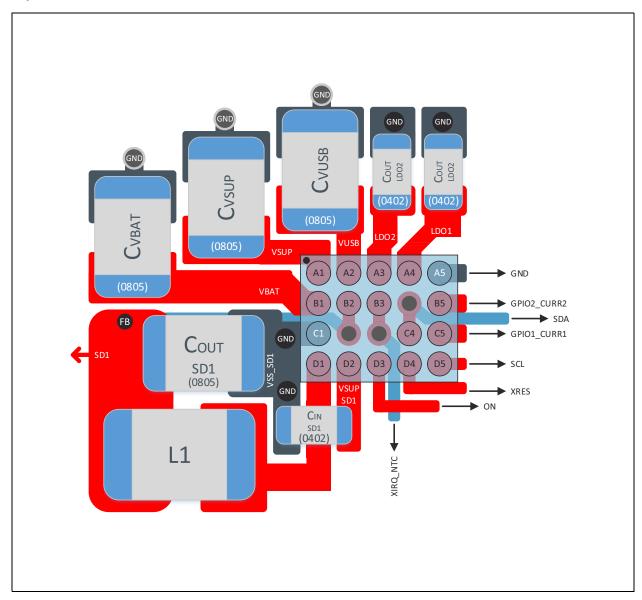

Figure 4: 17-balls WL-CSP Pin Assignment for AS3701A

**Pin Assignments:** Shows the top view pin assignment of the AS3701A

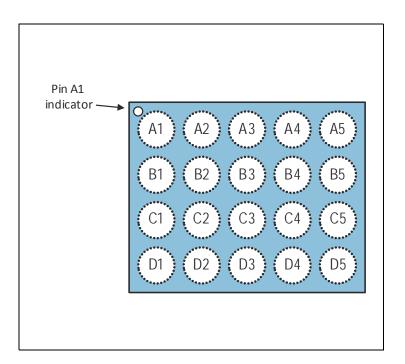

Figure 5: 20-balls WL-CSP Pin Assignment for AS3701B

**Pin Assignments:** Shows the top view pin assignment of the AS3701B

ams Datasheet Page 5

[v1-11] 2016-Dec-14 Document Feedback

## Figure 6: Pin Description

| Pin N       | umber       | D:-             |     |                                                             | Mari            | If No.4             |

|-------------|-------------|-----------------|-----|-------------------------------------------------------------|-----------------|---------------------|

| 17<br>Balls | 20<br>Balls | Pin<br>Name     | I/O | Description                                                 | Max.<br>Voltage | If Not<br>Used      |

| A2          | A2          | VUSB            | S   | Wall adapter or USB Bus Power input (before protection)     | 5.5V            | Pull-down to<br>GND |

| A1          | A1          | VSUP_CHG        | SIO | Current limiter output,<br>LDO1 & LDO2 pos. supply terminal | VSUP            | Mandatory           |

| D2          | D2          | VSUP_SD1        | S   | DCDC pos. supply terminal                                   | VSUP            | Mandatory           |

| B1          | B1          | VBAT            | S   | Li-lon Battery Terminal                                     | 5.5V            | Open                |

| A5          | A5          | GND             | AIO | Reference GND                                               | -               | Mandatory           |

| A4          | A4          | LDO1            | AO  | LDO1 Output                                                 | 3.3V            | Open                |

| А3          | А3          | LDO2            | AO  | LDO2 Output                                                 | 3.3V            | Open                |

| D1          | D1          | LX_SD1          | AIO | DCDC Step Down Switch Output to<br>Coil                     | 5.5V            | Open                |

| B2          | B2          | FB_SD1          | Al  | DCDC Step Down Feedback Pin                                 | 3.6V            | Open                |

| D4          | D4          | XRES            | DIO | Reset IO                                                    | VSUP            | Pull-up to<br>VSUP  |

| D3          | D3          | ON              | DI  | Power Up Input                                              | 5.5V            | Open                |

| В3          | В3          | XIRQ_NTC        | AIO | Interrupt Output or NTC Input                               | VSUP            | Open                |

| D5          | D5          | SCL             | DI  | 2-wire Serial IF Clock Input                                | VSUP            | Pull-up to<br>VSUP  |

| C4          | C4          | SDA             | DIO | 2-wire Serial IF Data I/O                                   | VSUP            | Pull-up to<br>VSUP  |

| C5          | C5          | GPIO1_<br>CURR1 | DIO | General Purpose IO1 or LED Channel 1                        | VSUP            | Open                |

| B5          | B5          | GPIO2_<br>CURR2 | DIO | General Purpose IO2 or LED Channel 2                        | VSUP            | Open                |

| -           | B4          | GPIO3           | DIO | General Purpose IO3                                         | VSUP            | Open                |

| -           | C2          | GPIO4           | DIO | General Purpose IO4                                         | VSUP            | Open                |

| -           | C3          | GPIO5           | DIO | General Purpose IO5                                         | VSUP            | Open                |

| C1          | C1          | VSS_SD1         | AIO | GND connector of DCDC                                       | -               | Mandatory           |

Page 6ams DatasheetDocument Feedback[v1-11] 2016-Dec-14

## **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 7:

Absolute Maximum Ratings

| Symbol             | Parameter                                     | Min      | Max      | Units                 | Comments                                                                                                                                 |  |  |  |  |  |  |

|--------------------|-----------------------------------------------|----------|----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                    | Electrical Parameters                         |          |          |                       |                                                                                                                                          |  |  |  |  |  |  |

| V <sub>GND</sub>   | Supply voltage to ground 5V pins              | -0.5     | 7.0      | V                     | Applicable for pins VSUP_CHG, VSUP_SD1, VBAT, VUSB, LX_SD1, SCL, SDA, ON, XRES, XIRQ_NTC, GPIO3, GPIO4, GPIO5, GPIO1_CURR1, GPIO2_ CURR2 |  |  |  |  |  |  |

| V <sub>GND</sub>   | Supply voltage to ground 3V pins              | -0.5     | 5.0      | V                     | Applicable for pins<br>LDO1, LDO2, FB_SD1                                                                                                |  |  |  |  |  |  |

|                    | Voltage difference between ground terminals   | -0.5     | 0.5      | V                     | Applicable for pins GND, VSS_SD1                                                                                                         |  |  |  |  |  |  |

| I <sub>SCR</sub>   | Input current<br>(latch-up immunity)          | -100     | 100      | mA                    | JEDEC JESD78                                                                                                                             |  |  |  |  |  |  |

|                    | Continuous Po                                 | wer Dis  | sipation | (T <sub>A</sub> = 70° | C)                                                                                                                                       |  |  |  |  |  |  |

| P <sub>T</sub>     | P <sub>T</sub> Continuous power dissipation   |          | 0.96     | W                     | $P_T^{(1)}$ for WL-CSP20 $(R_{THJA} \sim 57K/W)$                                                                                         |  |  |  |  |  |  |

|                    | Electrostatic Discharge                       |          |          |                       |                                                                                                                                          |  |  |  |  |  |  |

| ESD <sub>HBM</sub> | Electrostatic discharge<br>(human body model) | <u>+</u> | -2       | kV                    | JEDEC JESD22-A114F                                                                                                                       |  |  |  |  |  |  |

ams Datasheet Page 7

[v1-11] 2016-Dec-14 Document Feedback

| Symbol            | Parameter                                 | Min | Max | Units | Comments                                |  |  |  |  |  |  |  |

|-------------------|-------------------------------------------|-----|-----|-------|-----------------------------------------|--|--|--|--|--|--|--|

|                   | Temperature Ranges and Storage Conditions |     |     |       |                                         |  |  |  |  |  |  |  |

| T <sub>A</sub>    | Operating temperature                     | -40 | 85  | °C    |                                         |  |  |  |  |  |  |  |

| R <sub>THJA</sub> | Junction to ambient thermal resistance    |     |     | °C/W  | R <sub>THJA</sub> typ. 57K/W            |  |  |  |  |  |  |  |

| T <sub>J</sub>    | Junction temperature                      |     | 125 | °C    |                                         |  |  |  |  |  |  |  |

| T <sub>STRG</sub> | Storage temperature range                 | -55 | 125 | °C    |                                         |  |  |  |  |  |  |  |

| T <sub>BODY</sub> | Package body temperature                  |     | 260 | °C    | IPC/JEDEC J-STD-020 (2)                 |  |  |  |  |  |  |  |

| RH <sub>NC</sub>  | Relative humidity<br>(non-condensing)     | 5   | 85  | %     |                                         |  |  |  |  |  |  |  |

| MSL               | Moisture sensitivity level                | 1   |     |       | Represents an unlimited floor life time |  |  |  |  |  |  |  |

#### Note(s):

- 1. Depending on actual PCB layout and PCB used

- 2. The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non hermetic Solid State Surface Mount Devices"

Page 8ams DatasheetDocument Feedback[v1-11] 2016-Dec-14

## **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 8: Electrical Characteristics

| Symbol                | Parameter                     | Conditions                                   | Min | Тур  | Max | Unit |

|-----------------------|-------------------------------|----------------------------------------------|-----|------|-----|------|

| V <sub>IN</sub>       | Input voltage range           | Pin VSUP                                     | 2.7 |      | 5.5 | ٧    |

| I <sub>Q_ACTIVE</sub> | Active mode quiescent current | Normal operating current                     |     | 26   |     |      |

| le cruis sy           | Stand-by                      | Normal operating current<br>(Oscillator ON)  |     | 26   |     | 4    |

| IQ_STAND-BY           | quiescent current             | Normal operating current<br>(Oscillator OFF) |     | 11.5 |     | μΑ   |

| I <sub>POWEROFF</sub> | Shutdown current              | power_off = 1                                |     | 1.2  |     |      |

**Electrical Characteristics:**  $V_{SUP} = 3.7V$ ,  $V_{OUT} < V_{IN} - 0.5V$ ,  $T_{AMB} = -40$ °C to 85°C, typ. values @  $T_{AMB} = 25$ °C (unless otherwise specified)

ams Datasheet Page 9

[v1-11] 2016-Dec-14 Document Feedback

# Detailed Description – Power Management Functions

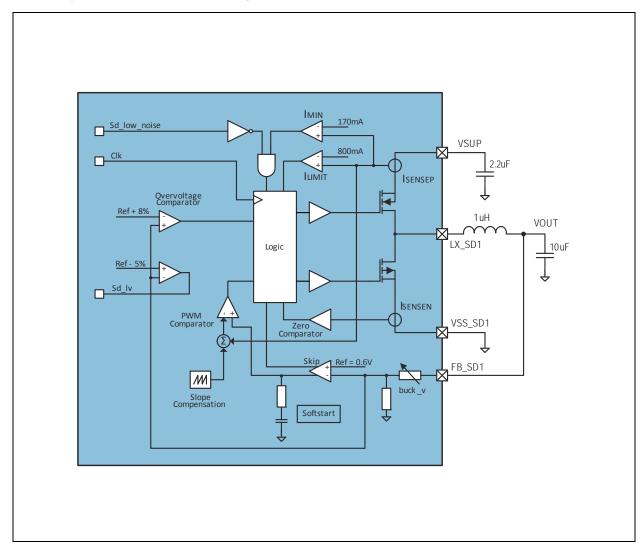

## **Step Down Converter**

The step-down converter is a high-efficiency fixed frequency current mode regulator. By using low resistance internal PMOS and NMOS switches, efficiency up to 95% can be achieved. The fast switching frequency allows using small inductors, without increasing the current ripple. The unique feedback and regulation circuit guarantees optimum load and line regulation over the whole output voltage range, up to the maximum output current, with an output capacitor of only 10µF. The implemented current limitation protects the DCDC Converter and the coil during overload condition.

Figure 9: DCDC Step-Down Converter Block Diagram

Page 10

Document Feedback

[v1-11] 2016-Dec-14

#### **Mode Settings**

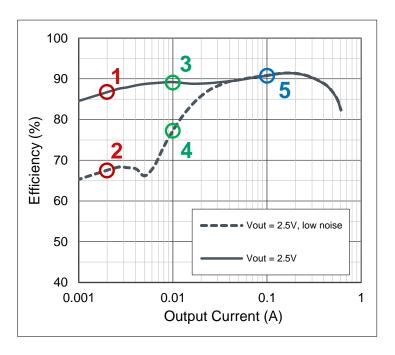

To allow optimized performance in different applications, there are bit settings possible, to get the best compromise between high efficiency and low input/output ripple.

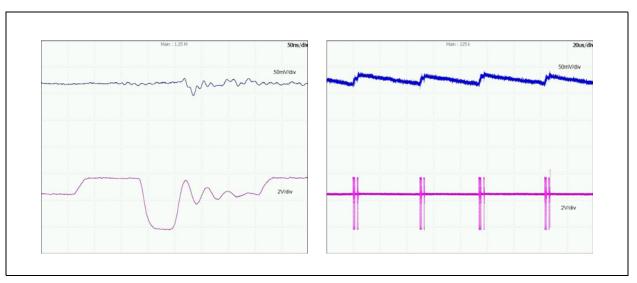

Figure 10: DCDC Step-Down Converter Mode Settings

**Mode Setting:** This graph shows the difference of the efficiency curves for high efficiency and low noise mode setting.  $V_{SUP} = 3.7V$ ,  $V_{OUT} = 2.5V$ ,  $f_{SW} = 3MHz$ ,  $T_{AMB} = 25^{\circ}C$ .

#### Low-Ripple, Low-Noise Operation

Low-ripple, low-noise operation can be enabled by setting the bit  $sd_low_noise$  [SD\_control1] to 1.

In this mode there is no minimum coil current necessary before switching OFF the PMOS. As long as the load current is superior to the ripple current, the device operates in continuous mode. When the load current gets lower, the discontinuous mode is triggered. Resultant the auto-zero comparator stops the NMOS conduction to avoid load discharger and the duty cycle is reduced down to t<sub>MIN\_ON</sub> to keep the regulation loop stable. This results in a very low ripple and noise, but decreased efficiency at light loads, especially at low input to output voltage differences.

ams Datasheet Page 11

[v1-11] 2016-Dec-14 Document Feedback

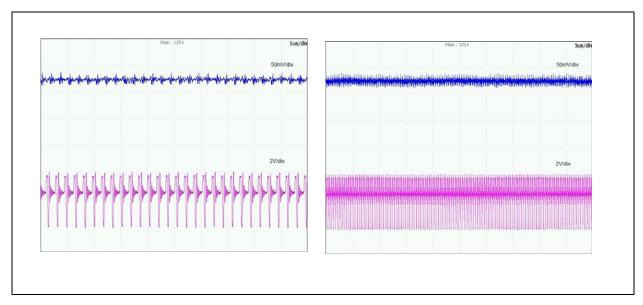

Figure 11: Switching Behavior at Operating Point 4

**Operating Point 4:** These graphs show the switching behavior referring to the operating point 4 from figure 10. Here the mode is set to low noise/low ripple operation and the DCDC is continuously switching at 10mA load current.

Only in the case the load current gets so small, that less than the minimum on time of the PMOS would be needed to keep the loop in regulation, the regulator will enter low power mode operation.

Figure 12: Switching Behavior at Operating Point 2

**Operating Point 2:** These graphs show the switching behavior referring to the operating point 2 from figure 10. Here the mode is set to low noise/low ripple operation and the DCDC has already started to skip pulses, as the minimum PMOS ON time of 40ns has been reached and the load current is further decreasing down to 2mA.

Page 12ams DatasheetDocument Feedback[v1-11] 2016-Dec-14

#### High-Efficiency Operation (Default Setting)

High-efficiency operation is enabled by setting the bit sd\_low\_noise [SD\_control1] to 0.

In this mode there is a minimum coil current necessary before switching OFF the PMOS. Resultant there are less pulses necessary at low output loads, and therefore the efficiency increases. As drawback, this mode increases the ripple up to a higher output current.

Figure 13:

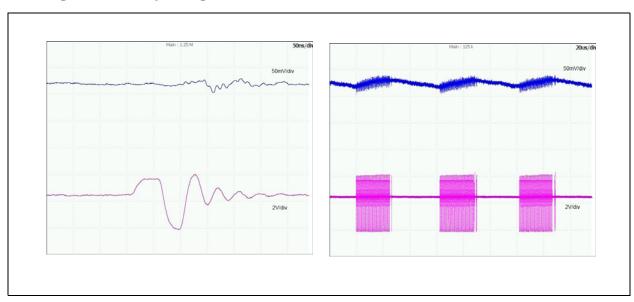

Switching Behavior at Operating Point 1

**Operating Point 1:** These graphs show the switching behavior referring to the operating point 1 from figure 10. Here the mode is set to high efficiency operation and the DCDC is in skipping mode at 2mA load current. Here a minimum coil current during the PMOS ON time is needed, hence more energy can be stored, the duration between the bursts is longer and the efficiency increases.

Figure 14:

Output Voltage Ripple Measurement at Operating Point 3

**Operating Point 3:** These graphs show the switching behavior referring to the operating point 3 from figure 10. Here the mode is set to high efficiency operation and comparing to operating point 4 the DCDC is still in skipping mode at 10mA load current and keeps the efficiency higher.

ams Datasheet Page 13

[v1-11] 2016-Dec-14 Document Feedback

Figure 15:

Output Voltage Ripple Measurement at Operating Point 5

**Operating Point 5:** These graphs show the switching behavior referring to the operating point 5 from figure 10. Here the load current is 100mA and high enough to keep the DCDC always in a continuous switching operation regardless of the mode setting.

#### Low Power Mode Operation (Automatically Controlled)

As soon as the output voltage stays above the desired target value for a certain time, some internal blocks will be powered down leaving the output floating to lower the power consumption. Normal operation starts as soon as the output drops below the target value for a similar amount of time. To minimize the accuracy error some internal circuits are kept powered to assure a minimized output voltage ripple.

Two addition guard bands, based on comparators, are set at  $\pm 5\%$  of the target value to react quickly on large over/undershoots by immediately turning ON the output drivers without the normal time delays. This ensures a minimized ripple also in very extreme load conditions.

## **Dynamic Voltage Management**

To minimize the over-/undershoot during a change of the output voltage, the DVM can be enabled with <code>dvm\_enable[SD\_control2]</code>. With DVM the output voltage will ramp up/down with a selectable slope after the new value was written to the registers. The DVM time can be chosen between 8µs and 16µs by setting the bit <code>dvm\_time[SD\_control2]</code>. Without DVM the slew rate of the output voltage is only determined by external components like the coil and load capacitor as well as the load current.

Page 14

Document Feedback

[v1-11] 2016-Dec-14

#### Fast Regulation Mode

This mode can be used to react faster on sudden load changes and thus minimize the over-/undershoot of the output voltage. This mode needs a  $22\mu F$  output capacitor instead the  $10\mu F$  one to guarantee the stability of the regulator.

The mode is enabled by setting the bit *sd\_fast* [*SD\_control1*] to 1.

#### **Selectable Frequency Operation**

Especially for very low load conditions, e.g. during a sleep mode of a processor, the switching frequency can be reduced to achieve a higher efficiency. The frequency can be set to 1, 2, 3 or 4MHz and this mode is selected by setting  $sd1\_freq$  [SD1Voltage] and  $sd1\_fsel$  [SD\_control1] to the appropriate values.

#### **Parameters**

Figure 16: DCDC Step-Down Converter Electrical Characteristics

| Symbol                | Parameter                | Note                           | Min    | Тур  | Max  | Unit |

|-----------------------|--------------------------|--------------------------------|--------|------|------|------|

| V <sub>IN</sub>       | Input Voltage            | Pin VSUP                       | 2.7    |      | 5.5  | V    |

| V <sub>OUT</sub>      | Regulated Output Voltage |                                | 0.6125 |      | 3.35 | V    |

| V <sub>OUT_TOL</sub>  | Output Voltage Tolerance | min. 40mV                      | -3     |      | +3   | %    |

| I <sub>LIMIT</sub>    | Current Limit            |                                |        | 800  |      | mA   |

| R <sub>PMOS</sub>     | P-switch ON resistance   |                                |        | 0.36 | 1    | Ω    |

| R <sub>NMOS</sub>     | N-switch ON resistance   |                                |        | 0.33 | 1    | Ω    |

| f <sub>SW</sub>       | Switching Frequency      |                                | 1      | 3    | 4    | MHz  |

| I <sub>LOAD</sub>     | Load Current             |                                |        | 500  |      | mA   |

| I <sub>SUP_DCDC</sub> | Current Consumption      | Operating Current without Load |        | 27   |      | μΑ   |

|                       |                          | Shutdown Current               |        | 0.1  |      |      |

| t <sub>MIN_ON</sub>   | Minimum ON Time          |                                |        | 40   |      | ns   |

ams Datasheet Page 15

[v1-11] 2016-Dec-14 Document Feedback

Figure 17: DCDC Step-Down Converter External Components

| Symbol                | Parameter        | Note               | Min | Тур | Max | Unit |

|-----------------------|------------------|--------------------|-----|-----|-----|------|

| C <sub>FB_SD1</sub>   | Output Capacitor | Ceramic X5R or X7R | 8   | 10  |     | μF   |

| C <sub>VSUP_SD1</sub> | Input Capacitor  | Ceramic X5R or X7R |     | 2.2 |     | μF   |

|                       |                  | 4MHz operation     |     | 1   |     |      |

| l coa                 | Inductor         | 3MHz operation     |     | 1   |     | μΗ   |

| L <sub>SD1</sub>      |                  | 2MHz operation     |     | 1   |     | μιι  |

|                       |                  | 1MHz operation     |     | 2.2 |     |      |

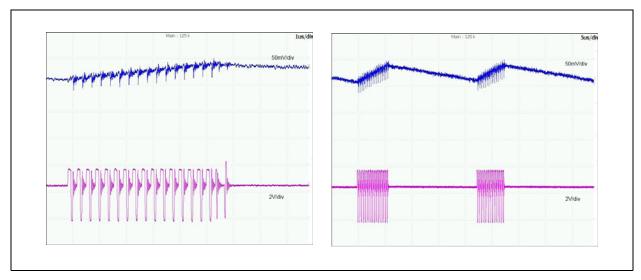

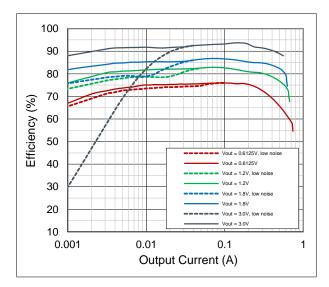

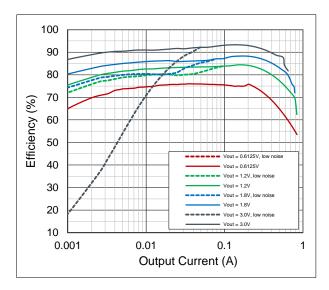

Figure 18: DCDC Step Down Converter Efficiency vs. Load Current at 1MHz

**DCDC Efficiency vs. Output Current:**  $V_{SUP} = 3.7V$ ,  $f_{SW} = 1$ MHz, Murata LQM2HPN2R2MG0L 2.2 $\mu$ H coil,  $T_{AMB} = 25^{\circ}$ C.

Page 16

Document Feedback

[v1-11] 2016-Dec-14

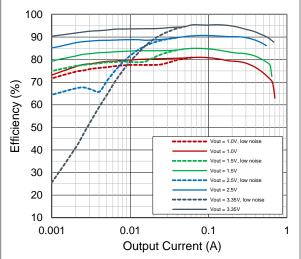

Figure 19: DCDC Step Down Converter Efficiency vs. Load Current at 2MHz

**DCDC Efficiency vs. Output Current:**  $V_{SUP} = 3.7V$ ,  $f_{SW} = 2MHz$ , Murata LQM2HPN1R0MG0L 1 $\mu$ H coil,  $T_{AMB} = 25$ °C.

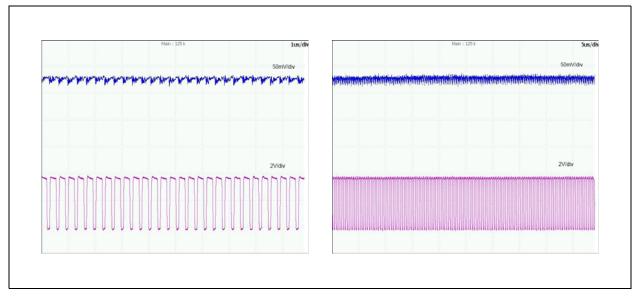

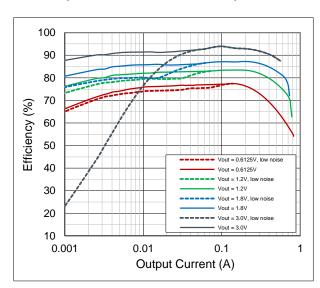

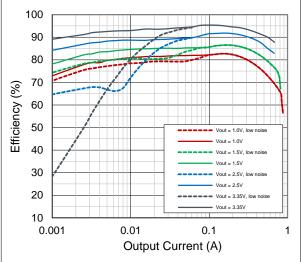

Figure 20: DCDC Step Down Converter Efficiency vs. Load Current at 3MHz

**DCDC Efficiency vs. Output Current:**  $V_{SUP} = 3.7V$ ,  $f_{SW} = 3MHz$ , Murata LQM2HPN1R0MG0L 1 $\mu$ H coil,  $T_{AMB} = 25$ °C.

ams Datasheet Page 17

[v1-11] 2016-Dec-14 Document Feedback

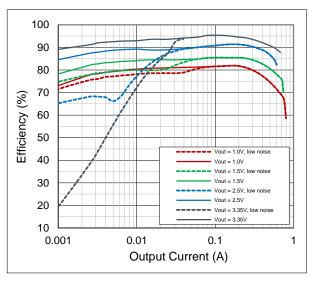

Figure 21: DCDC Step Down Converter Efficiency vs. Load Current at 4MHz

$\textbf{DCDC Efficiency vs. Output Current:} \ V_{SUP} = 3.7V, \ f_{SW} = 4MHz, \ Murata \ LQM2HPN1R0MG0L \ 1 \mu H \ coil, \ T_{AMB} = 25^{\circ}C.$

Page 18ams DatasheetDocument Feedback[v1-11] 2016-Dec-14

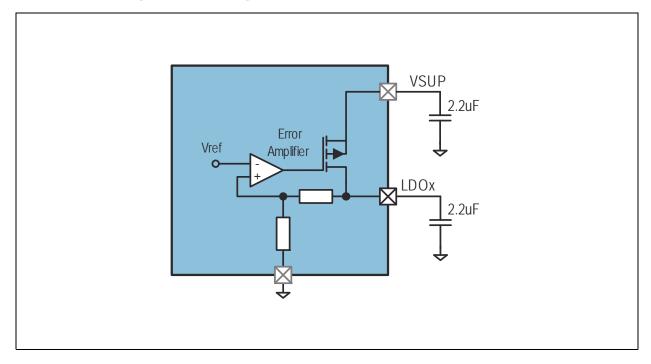

## **Universal IO LDO Regulator**

This LDO is a low-power and low-quiescent current linear-regulator specifically designed for space-limited applications. This device can supply loads up to 200mA and consist of an error amplifier, and a P-channel MOSFET pass transistor.

Figure 22: Universal IO LDO Regulator Block Diagram

## **Parameters**

Figure 23: Universal IO LDO Regulator Electrical Characteristics

| Symbol            | Parameter      | Note                                                                                             | Min  | Тур | Max  | Unit |

|-------------------|----------------|--------------------------------------------------------------------------------------------------|------|-----|------|------|

| V <sub>IN</sub>   | Input voltage  | Pin VSUP                                                                                         | 2.7  |     | 5.5  | V    |

|                   |                | I <sub>OUT</sub> = 1mA, V <sub>OUT</sub> > 2V T <sub>AMB</sub> = 25°C<br>Guaranteed by design    | -2.5 |     | +2.5 | %    |

| ΔV <sub>OUT</sub> | Output voltage | I <sub>OUT</sub> = 100μA to 200mA<br>V <sub>OUT</sub> > 2V                                       | -3   |     | +3   |      |

| 74001             | accuracy       | I <sub>OUT</sub> = 1mA, V <sub>OUT</sub> ≤ 2V<br>T <sub>AMB</sub> = 25°C<br>Guaranteed by design | -20  |     | +20  | mV   |

|                   |                | $I_{OUT} = 100\mu A$ to 200mA<br>$V_{OUT} \le 2V$                                                | -50  |     | +50  |      |

ams Datasheet Page 19

[v1-11] 2016-Dec-14 Document Feedback

| Symbol                | Parameter                  | Note                                                                                                                 | Min | Тур   | Max | Unit   |

|-----------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-------|-----|--------|

| V <sub>OUT</sub>      | Output voltage range       | 1                                                                                                                    |     |       | 3.3 | V      |

| V <sub>LNR</sub>      | Line regulation static     | V <sub>IN</sub> = 2.7V to 5.5V<br>I <sub>OUT</sub> = 1mA                                                             |     | 0.07  |     | %/V    |

| LINK                  | Line regulation<br>dynamic | $V_{IN}$ = 2.7V to 5.5V within 15 $\mu$ s $I_{OUT}$ = 1mA                                                            |     | 20    |     | mV     |

|                       | Load regulation static     | I <sub>OUT</sub> = 100μA to 200mA                                                                                    |     | 0.014 |     | %/mA   |

| V <sub>LDR</sub>      | Load regulation<br>dynamic | $I_{OUT} = 100\mu\text{A}$ to 200mA within 15 $\mu\text{s}$                                                          |     | 30    |     | mV     |

| R <sub>ON</sub>       | ON resistance              |                                                                                                                      |     | 0.5   | 1   | Ω      |

| I <sub>OUT</sub>      | Guaranteed load current    | RMS                                                                                                                  | 200 |       |     | mA     |

| I <sub>LIMIT</sub>    | Short-circuit              | V <sub>OUT</sub> = 0V                                                                                                |     | 230   |     | mA     |

|                       |                            | No Load                                                                                                              |     | 5     |     |        |

| I <sub>Q</sub>        | Quiescent current          | I <sub>OUT</sub> = 100μA                                                                                             |     | 5     |     | μΑ     |

|                       |                            | I <sub>OUT</sub> = 200mA                                                                                             |     | 15    |     |        |

| I <sub>OFF</sub>      | Shutdown supply current    | LDO disabled                                                                                                         |     | 0.1   | 1   | μΑ     |

| aN                    | Output poice               | $BW = 10 \text{Hz to } 100 \text{Hz};$ $V_{OUT} = 1.2 \text{V}; I_{OUT} = 1 \text{mA};$ $C_{OUT} = 2.2 \mu \text{F}$ |     | 112   |     | u\/rms |

| eN                    | Output noise               | $BW = 10 Hz \text{ to } 100 Hz;$ $V_{OUT} = 3.3 V; I_{OUT} = 1 mA;$ $C_{OUT} = 2.2 \mu F$                            |     | 205   |     | μVrms  |

| t <sub>START</sub>    | Startup time               |                                                                                                                      |     | 750   |     | μs     |

| t <sub>SHUTDOWN</sub> | Shutdown time              |                                                                                                                      |     | 500   |     | μs     |

Figure 24: Universal IO LDO Regulator External Components

| Symbol            | Parameter        | Note               | Min | Тур | Max | Unit |

|-------------------|------------------|--------------------|-----|-----|-----|------|

| C <sub>LDOx</sub> | Output capacitor | Ceramic X5R or X7R | 2.2 | 4.7 |     | μF   |

Page 20ams DatasheetDocument Feedback[v1-11] 2016-Dec-14

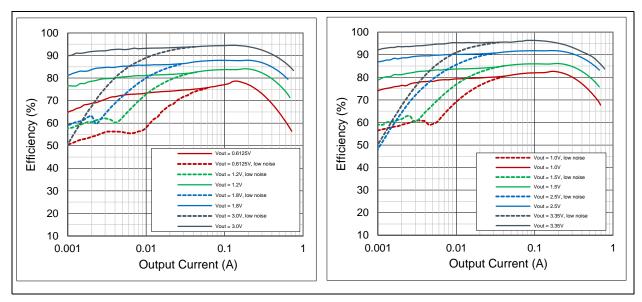

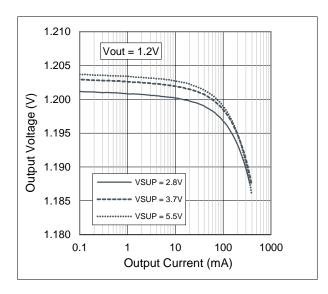

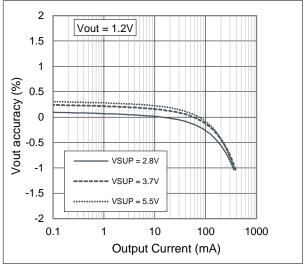

Figure 25: LDO Output Voltage vs. Output Current 1/2

**LDO Output Voltage vs. Output Current:**  $V_{OUT} = 1.2V$ ,  $T_{AMB} = 25$ °C.

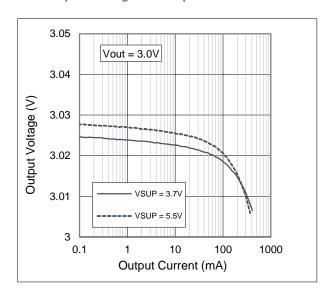

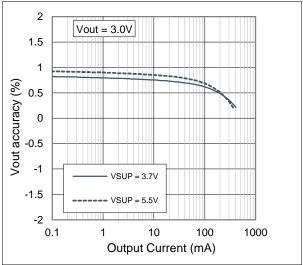

Figure 26: LDO Output Voltage vs. Output Current 2/2

**LDO Output Voltage vs. Output Current:**  $V_{OUT} = 3.0V$ ,  $T_{AMB} = 25$ °C.

ams Datasheet Page 21

[v1-11] 2016-Dec-14 Document Feedback

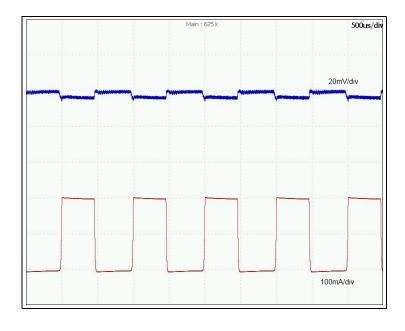

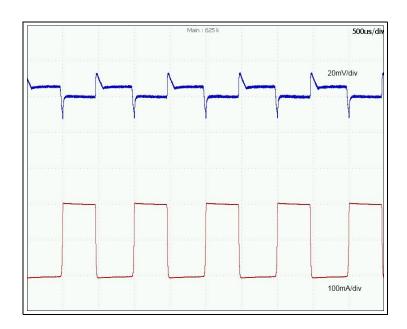

## Figure 27: LDO Load Transient Response 1/2

## **LDO Load Transient Response:**

$$\begin{split} &V_{SUP}=3.7V, V_{OUT}=1.2V, t_{RISE}=15\mu s, \\ &I_{OUT}=100\mu A \text{ to } 200\text{mA}, T_{AMB}=25^{\circ}\text{C}. \\ &(\text{Blue channel: } V_{OUT}; \text{ Red channel: } I_{OUT}) \end{split}$$

Figure 28: LDO Load Transient Response 2/2

#### **LDO Load Transient Response:**

$V_{SUP}=3.7V, V_{OUT}=3.0V, t_{RISE}=15\mu s, \\ I_{OUT}=100\mu A to 200mA, T_{AMB}=25^{\circ}C. \\ (Blue channel: V_{OUT}; Red channel: I_{OUT})$

Page 22ams DatasheetDocument Feedback[v1-11] 2016-Dec-14

## **Linear Charger**

This block can be used to charge Li-lon batteries. Requiring less external components, a full-featured battery charger with a high degree of flexibility can easily be realized. The main features of the controller are:

- Charge adapter detection

- Power Path management for dead battery startup

- Low current Trickle charging

- · Constant current charging

- Constant voltage charging

- Operation without battery

- Battery presence indication

- NTC temperature supervision

- Input current limitation

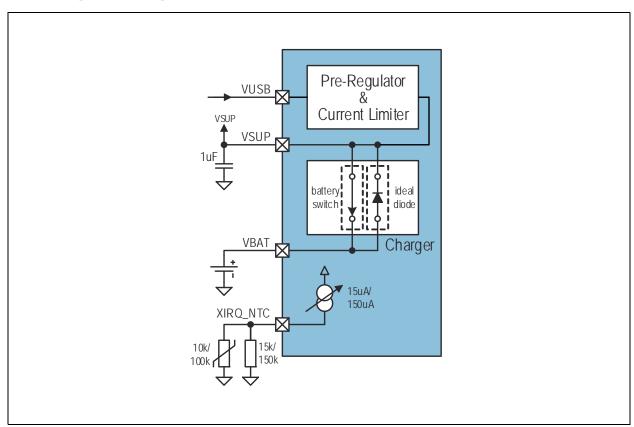

Figure 29: Linear Charger Block Diagram

ams Datasheet Page 23

[v1-11] 2016-Dec-14 Document Feedback

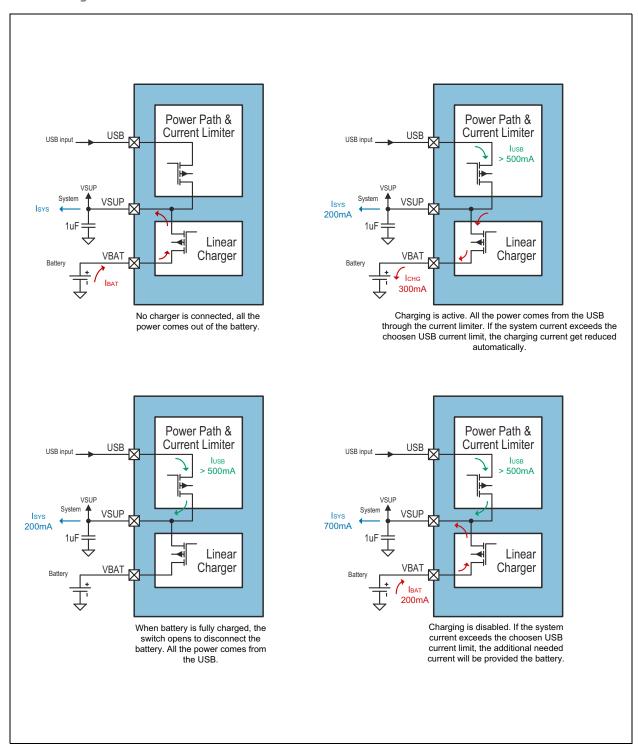

Figure 30: Linear Charger Modes

Charging Modes: This figure describes the 4 different charger modes.

Page 24

Document Feedback [v1-11] 2016-Dec-14

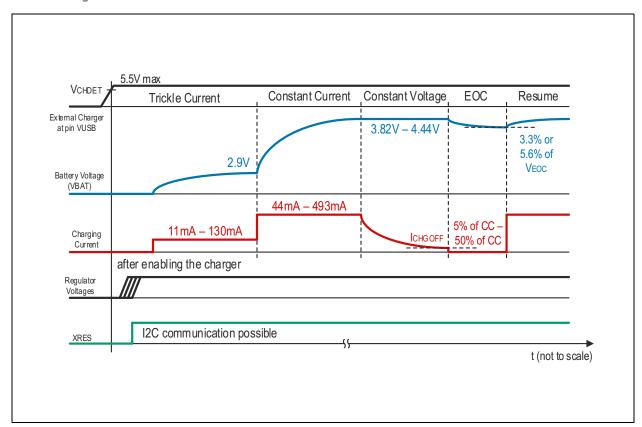

#### **Charging Cycle Description**

#### **Charge Adapter Detection**

The charge controller uses an integrated detection circuit to determine if an external charge adapter has been applied to the VUSB pin. If the adapter voltage exceeds the battery voltage at pin VBAT by V<sub>CHDET</sub> the *ChDet [ChargerStatus2]* will be set. The detection circuit will reset the charge controller (bit *ChDet* is cleared) as soon as the voltage at the VUSB pin drops to only V<sub>CHMIN</sub> above the battery voltage. In case the AS3701 device is reset the charge controller will also be reset, even if a charge adapter is applied to the VUSB pin. The Charger detection can be disabled by setting the bit *chdet\_off [ChargerStatus2]* to "1", which results in a further decrease of internal power consumption.

## Low Current (Trickle) Charging

Trickle charge mode is started when an external charge adapter has been detected, the bit <code>bat\_charging\_enable</code> [ChargerControl] is set and the battery voltage at pin VBAT is below the V<sub>TRICKLE</sub> threshold; bits ChDet and Trickle [ChargerStatus1] will be set. In this mode the charge current will be limited to TrickleCurrent [ChargerCurrentControl] to prevent undue stress in case of deeply discharged batteries. Once V<sub>TRICKLE</sub> has been exceeded, the charger will change over to constant current charging (Trickle is cleared).

#### **Constant Current Charging**

Constant current charging is initiated when <code>bat\_charging\_enable [ChargerControl]</code> and the battery voltage at pin VBAT is above the VTRICKLE and below VCHOFF. The bit CCM [ChargerStatus1] is set when the charger has started, and the charge current will be limited by the battery charge controller. The current for the Constant Current Charging can be selected out of the range defined in ConstantCurrent [ChargerCurrentControl] if the bit cc\_range\_select [ChargerControl] is set to "0" or out of the range defined in TrickleCurrent [ChargerCurrentControl] if the bit cc\_range\_select [ChargerControl] is set to "1". When the battery approaches full charge, its voltage will reach the charge termination threshold VCHOFF. VCHOFF depends on the ChVoltEOC [ChargerVoltageControl] bits settings. Top-OFF charge will be started and the bit CVM [ChargerStatus1] will be set.

## **Constant Voltage Charging**

Constant voltage charge mode is initiated and the bit *CVM* [ChargerStatus1] will be set when the V<sub>CHOFF</sub> threshold has been reached. The charge current is monitored during constant voltage charging. It will be decreasing from its initial value during constant current charging and eventually drops below 5% or 50% of the Constant Current value (depends on the

ams Datasheet Page 25

[v1-11] 2016-Dec-14 Document Feedback

setting of the bit <code>eoc\_current</code> [ChargerCurrentControl]). If the measured charge current is less than or equal to <code>eoc\_current</code>, the charging cycle is terminated and <code>EOC</code> [ChargerStatus1] is set.

#### Resume

If EOC is reached and the bit *AutoResume* [ChargerControl] is set, the charging will immediately start again, if the battery voltage falls below the specified resume voltage ChVoltResume [ChargerConfig1]. This voltage can be set either to 3.33% or 5.56% of ChVoltEOC [ChargerVoltageControl].

Figure 31: Resume Voltage Levels

| ChVoltResume    |       |       | ChVoltEOC |     |       |       |

|-----------------|-------|-------|-----------|-----|-------|-------|

| Cirvoithesuille | 3.82V | 3.84V | <br>4.20V |     | 4.42V | 4.44V |

| 3.33%           | 127mV | 128mV | <br>140mV |     | 147mV | 148mV |

| 5.56%           | 212mV | 213mV | <br>233mV | ••• | 246mV | 247mV |

Figure 32: Linear Charger States

**Charging States:** This figure describes the characteristics of the charging current and the battery voltage for each different charging state.

Page 26

Document Feedback

[v1-11] 2016-Dec-14

#### **Stop Charging Conditions**

There are multiple safety features implemented triggering a stop\_charging condition.

These are the following:

- Battery temperature is too high: If ntc\_high\_on [ChargerSupervision] = 1 and the voltage at pin NTC (GPIO3, GPIO4 or XIRQ\_NTC) is below V<sub>BATTEMP</sub>.

- Battery temperature is too low: If ntc\_low\_on [ChargerSupervision] = 1 and the voltage at pin NTC (GPIO3, GPIO4 or XIRQ\_NTC) is above V<sub>RATTEMP</sub>.

- Charging timeout timer expired: If ch\_timeout

[ChargerConfig2] > 0 and charging time has been

exceeded. (Can be reset by unplugging the charger,

setting bat\_charging\_enable [ChargerControl] = 0 or

writing charging\_tmax [ChargerConfig2] = 0)

- Die temperature > 140°C (ov\_temp\_140 [OvertemperatureControl] is set)

- Reset is initiated (each Reset reason forces a stopping of the charging)

#### **Battery Presence Indication**

After EOC state is reached, a timer for NOBAT detection is started. If there is no battery present, the VBAT voltage will drop to VRESUME. Depending on the load on VBAT and the capacitor on VBAT this might take some milliseconds to 1 second. If *AutoResume* [ChargerControl] is enabled, the charger will restart charging (Constant Current Charging) after 100ms delay.

The 100ms dead time is necessary to get a battery oscillation frequency below 10Hz, if there is no battery present.

If the NOBAT detection timer is below 2 seconds after reaching the EOC state, and this happens 2 times in serial, the bit *NoBat* [ChargerStatus1] is set. If a battery is inserted, the bit will be reset after the timer exceeds the 2 seconds.

#### **NTC Supervision**

#### Configuration

The AS3701 also features a supply for an external NTC resistor to measure the battery temperature while charging. For AS3701A, the pin XIRQ\_NTC can be used as the NTC input pin, whilst AS3701B additionally offers the GPIO3 and GPIO4. With the bit NTC\_input [ChargerSupervision] the NTC Supervision can be configured.

ams Datasheet Page 27

[v1-11] 2016-Dec-14 Document Feedback

Figure 33: NTC Supervision Configuration

| NTC_input |   | NTC Supervision Configuration |

|-----------|---|-------------------------------|

| 0         | 0 | No NTC supervision (1)        |

| 0         | 1 | XIRQ_NTC pin                  |

| 1         | 0 | GPIO3 pin <sup>(2)</sup>      |

| 1         | 1 | GPIO4 pin <sup>(2)</sup>      |

#### Note(s):

1. If no NTC supervision is selected, all NTC relevant bits are ineffective 2. AS3701B only

#### **NTC** Resistor

Depending on the used resistor value of the NTC (10k or 100k) the internal NTC current (150 $\mu$ A for 10k or 15 $\mu$ A for 100k) can be selected via  $ntc_10k$  [ChargerSupervision].

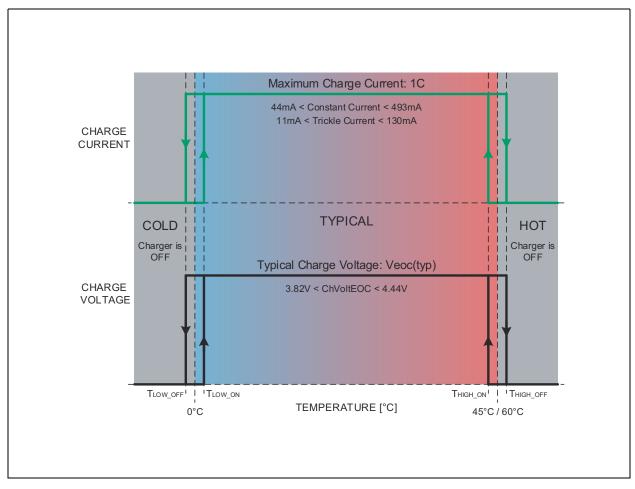

#### High/Low Temperature

The battery high temperature supervision is controlled with the bit  $ntc\_high\_on$  [ChargerSupervision] and this feature is enabled per default. If the temperature is higher than 45°C or 60°C (depending on  $ntc\_mode$  [ChargerSupervision]) the flag  $temp\_cond$  [ChargerStatus1] will be set and the charger will stop operation. When the battery temperature drops and the voltage on NTC pin rises above  $V_{BATTEMP\_HIGH\_OFF}$ , the flag  $temp\_cond$  will be reset and the charger will continue with the charging again.

The battery low temperature supervision is controlled with the bit  $ntc\_low\_on$  [ChargerSupervision] and this feature is disabled per default. If the temperature is lower than 0°C the flag  $temp\_cond$  [ChargerStatus1] will be set and the charger will stop operation. When the battery temperature rises and the voltage on NTC pin falls below  $V_{BATTEMP\_LOW\_OFF}$ , the flag  $temp\_cond$  will be reset and the charger will continue with the charging again.

The detection of a high or low battery temperature can also be indicated with a dedicated interrupt mask bit bat\_temp\_m [InterruptMask2].

For the high and low temperature supervision, a temperature hysteresis is included to avoid an oscillation of the charger.

The supply for the NTC will be on when either the *ntc\_high\_on* or the *ntc\_low\_on* bit is set, no matter if a charger is detected or not. Therefore the battery temperature supervision can be used for charging mode and also for discharging mode.

Page 28

Document Feedback

[v1-11] 2016-Dec-14

## NTC B-Correction

To keep the voltage drop over the whole temperature range inside of the comparator threshold voltage range, a 15k (150k) parallel resistor to the 10k (100k) NTC is needed. With the bit *ntc\_beta* [ChargerSupervision] 4 different ß-values depending on the used NTC resistor can be selected.

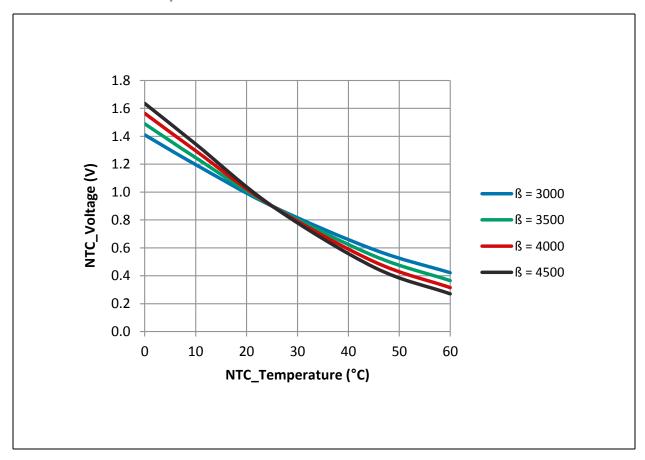

Figure 34: NTC ß Influence Over Temperature

**NTC ß Influence Diagram:** Shows the voltage drop over the NTC resistor depending on the temperature for 4 different ß values using  $R_{NTC}$ =10k $\Omega$ ,  $R_p$ =15k $\Omega$  and  $I_{NTC}$ =150 $\mu$ A.

Figure 35: NTC Threshold Voltages

| Temperature      |      | ß    |      |      |      |      |

|------------------|------|------|------|------|------|------|

|                  |      | 3000 | 3500 | 4000 | 4500 | Unit |

| Low temperature  | 0°C  | 1.41 | 1.49 | 1.56 | 1.63 | V    |

| High temperature | 45°C | 0.59 | 0.54 | 0.50 | 0.46 | V    |

|                  | 60°C | 0.42 | 0.37 | 0.31 | 0.27 | V    |

**NTC Supervision:** Comparator threshold voltages for different temperatures and ß using  $R_{NTC}$ =10 $k\Omega$ ,  $R_p$ =15 $k\Omega$  and  $I_{NTC}$ =150 $\mu$ A.

ams Datasheet Page 29

[v1-11] 2016-Dec-14 Document Feedback

## Charger High/Low Temperature Supervision

Figure 36: **High/Low Temperature Supervision**

**Temperature Supervision Diagram:** Shows the voltage and current settings for the high and low temperature supervision.

Page 30 ams Datasheet [v1-11] 2016-Dec-14

## **Parameters**

Figure 37: Linear Charger Electrical Characteristics

| Symbol                  | Parameter                                                                      | Note                                                                                            | Min  | Тур          | Max  | Unit |

|-------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|--------------|------|------|

| I <sub>TRICKLE</sub>    | Trickle current                                                                | 11 steps<br>programmable                                                                        |      | 11<br>130    |      | mA   |

| V <sub>TRICKLE</sub>    | Trickle to constant current threshold                                          | V <sub>BAT</sub> rising                                                                         |      | 2.9          |      | V    |

|                         |                                                                                | cc_range_select = 0                                                                             |      | 44<br>493    |      | mA   |

| I <sub>CHG</sub>        | Constant current                                                               | cc_range_select = 1                                                                             |      | 11<br>130    |      | mA   |

|                         |                                                                                | @ 70mA                                                                                          | -8%  | 70           | +8%  | mA   |

| V <sub>EOC</sub>        | Charge termination                                                             | Programmable in 20mV steps                                                                      |      | 3.82<br>4.44 |      | V    |

|                         | threshold                                                                      | end of charge is true                                                                           | 4.15 | 4.2          | 4.25 | V    |

| I <sub>EOC</sub>        | EOC current level                                                              | referring to I <sub>CHG</sub><br>(VSUP > 3V)                                                    |      | 5<br>50      |      | %    |

| I <sub>USB_limit</sub>  | VUSB input current limit                                                       | @470mA                                                                                          | 420  | 470          | 500  | mA   |

| V <sub>SUP_prereg</sub> | Voltage supplied from<br>Preregulator                                          | Depending on the bit vsup_voltage                                                               |      | 4.4<br>5.5   |      | V    |

| V <sub>RESUME</sub>     | Resume Voltage limit to start charger                                          | VBAT falling threshold referring to V <sub>EOC</sub> (depending on bit <i>ChVoltResume</i> )    |      | 3.3<br>5.6   |      | %    |

|                         | VSUP level for charging<br>current reduction, to avoid<br>voltage drop on VSUP | Trickle or constant<br>current will be regulated<br>down, if VSUP drops<br>below this threshold | -6%  | 3.9          | +3%  | V    |

| VSUP <sub>MIN</sub>     |                                                                                |                                                                                                 |      | 4.2          |      |      |

|                         |                                                                                |                                                                                                 | 070  | 4.5          |      |      |

|                         |                                                                                |                                                                                                 |      | 4.7          |      |      |

| V <sub>CHDET</sub>      | Charger detection hysteresis                                                   | V <sub>USB</sub> - V <sub>BAT</sub>                                                             | 50   | 75           | 105  | mV   |

| V <sub>CHMIN</sub>      |                                                                                | Hysteresis is > 40mV                                                                            | 0    | 20           | 35   | mV   |

| I <sub>REV_OFF</sub>    | Reverse current shut down                                                      | VSUP = 5V, V <sub>USB</sub> open                                                                |      | <1           |      | uA   |

| R <sub>ON_BATSW</sub>   | Battery switch<br>ON-resistance                                                |                                                                                                 |      | 0.4          |      | Ω    |

ams Datasheet Page 31

[v1-11] 2016-Dec-14 Document Feedback

Figure 38:

Capacitor Selection for VUSB, VSUP\_CHG and VBAT

| Symbol                | Parameter        | Note               | Min | Тур | Max | Unit |

|-----------------------|------------------|--------------------|-----|-----|-----|------|

| C <sub>VUSB</sub>     | Input capacitor  | Ceramic X5R or X7R |     | 10  |     | μF   |

| C <sub>VSUP_CHG</sub> | Output capacitor | Ceramic X5R or X7R |     | 10  |     | μF   |

| C <sub>VBAT</sub>     | Output capacitor | Ceramic X5R or X7R |     | 10  |     | μF   |

## Selection of Bypass Capacitors for the Pins VUSB, VSUP\_CHG and VBAT

In most applications using the ideal capacitance values shown in the table and the application schematic are recommended. After evaluation of the voltage signals on these pins with real system operational conditions at the user's application circuit, the user can determine if this ideal capacitance values needs to be adjusted.

It must be kept in mind that the capacitance value depends strongly on the rated voltage, therefore a selection of the appropriate nominal capacitor value related to the capacitor size is mandatory to achieve best performance under the specific operational voltage and load current condition of the application system.

#### **Current Sinks**

The following description of the Current Sinks refers only to the pins GPIO1\_CURR1 and GPIO2\_CURR2. Hence the suffix "X" stands either for 1 or for 2.

The AS3701 contains 2 GPIO pins (GPIO1\_CURR1 and GPIO2\_CURR2), providing general purpose current sinks when the register *gpioX\_mode* [GPIOXcontrol] is set to CURRx input. Next to this setting, the register *gpioX\_iosf* [GPIOXcontrol] must be set to one of the GPIO output functions (please see the GPIO section in the following chapter "Detailed Description – System Functions").

Page 32

Document Feedback

[v1-11] 2016-Dec-14

## **Parameters**

Figure 39: Current Sinks Electrical Characteristics

| Symbol                 | Parameter                                                       | Note                                             | Min  | Тур | Max                      | Unit |

|------------------------|-----------------------------------------------------------------|--------------------------------------------------|------|-----|--------------------------|------|

| I <sub>CURRx</sub>     | CURR1_current = 01h – FFh<br>CURR2_current = 01h – FFh          | Resolution = 156.86μA                            | 0.16 |     | 40                       | mA   |

| I <sub>CURRx_TOL</sub> | CURR current accuracy                                           | CURRx_current = 40h                              | 9.3  | 10  | 10.7                     | mA   |

| V <sub>CURRx</sub>     | Voltage compliance                                              | During normal operation                          | 0.5  |     | 5.5                      | V    |

| V <sub>PROTECT</sub>   | Maximum voltage at pin<br>CURRx to protect driver<br>transistor | I <sub>SINK</sub> > 20mA<br>guaranteed by design |      |     | V <sub>BAT</sub> +<br>2V | V    |

ams Datasheet Page 33

[v1-11] 2016-Dec-14 Document Feedback

# **Detailed Description – System Functions**

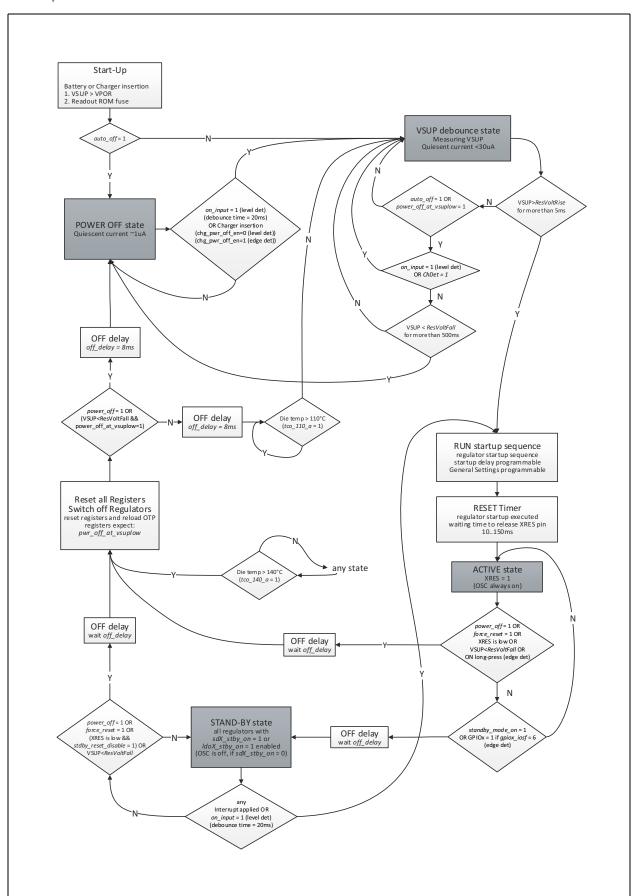

## Start-Up

## **Normal Start-Up**

The following gives a brief description on a start-up from scratch (battery or charger insertion). More details can be found in the start-up flow chart.

A start-up can be activated from 5 different sources:

- Battery insertion from scratch

- Charger insertion from scratch (VBAT < ResVoltFall)

- ON-key has been pulled high in power\_off mode

- · Reset cycle

- ResVoltRise level was reached

During a normal reset cycle a normal startup happens:

- Setting USB current limit and ResVoltRise

- Startup State machine reads out the internal Boot-OTP.

The start-up sequence of SD Converter, LDOs and GPIOs are controlled by the Boot-OTP

- Reset-Timer is set by the Boot-OTP

- The reset is released when the Reset Timer expires (external pin XRES)

#### **Parameter**

## Figure 40: Start-Up Condition

| Symbol                 | Parameter          | Note                            | Min            | Тур | Max            | Unit |

|------------------------|--------------------|---------------------------------|----------------|-----|----------------|------|

| V <sub>ON_IL</sub>     | Low level voltage  | ON pin                          |                |     | 20% of<br>VSUP | ٧    |

| V <sub>ON_IH</sub>     | High level voltage | ON pin                          | 60% of<br>VSUP |     |                | ٧    |

| I <sub>ON_PD</sub> (1) | Pull down current  | Bit on_invert = 0 (active high) | 4              | 12  |                | μΑ   |

#### Note(s):

1. The internal pull-down resistor is just active if the bit on\_invert is set to "0" (active high configuration). If the ON-key works active low (on\_invert = 1) the internal pull-down resistor is deactivated and an external pull-up resistor is needed in push-button configuration!

Page 34

Document Feedback

[v1-11] 2016-Dec-14

Figure 41: Start-Up Flowchart

ams Datasheet Page 35

[v1-11] 2016-Dec-14 Document Feedback

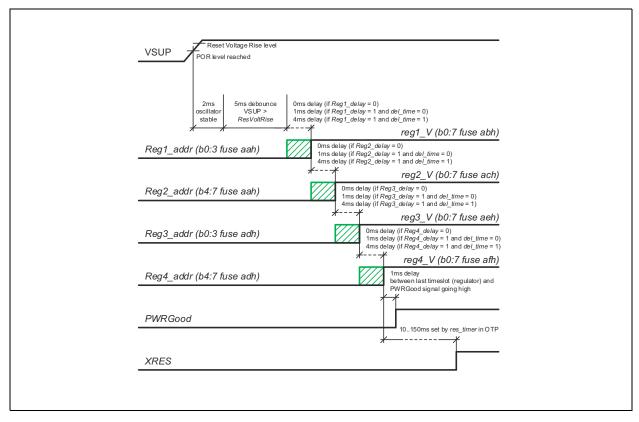

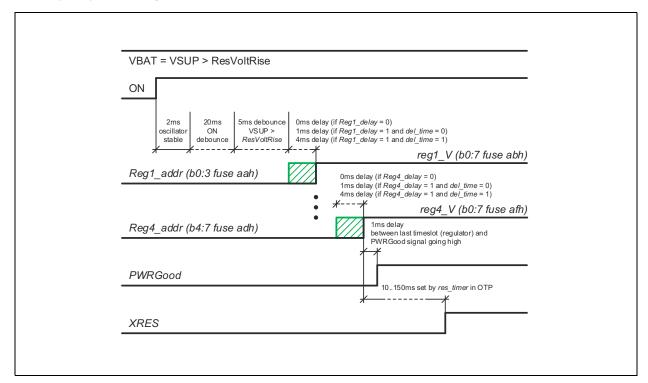

Figure 42: Start-Up Sequence Diagram 1/5

**Start-Up Sequence:** This diagram shows the timing of a startup from scratch (battery or charger insertion)

Figure 43: Start-Up Sequence Diagram 2/5

**Start-Up Sequence:** This diagram shows the timing of a startup from power-off mode via ON key press (battery connected, VSUP > *ResVoltRise*)

Page 36ams DatasheetDocument Feedback[v1-11] 2016-Dec-14

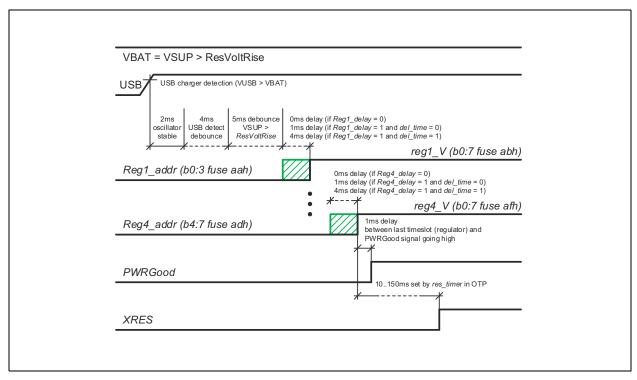

Figure 44: Start-Up Sequence Diagram 3/5

**Start-Up Sequence:** This diagram shows the timing of a startup from power-off mode via USB charger detection event (battery connected, VSUP > *ResVoltRise*)

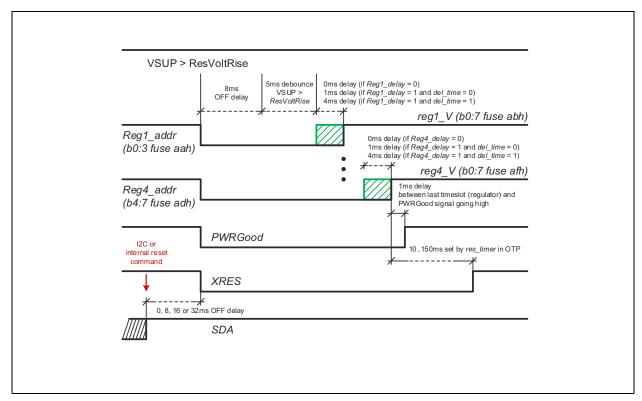

Figure 45: Start-Up Sequence Diagram 4/5

**Start-Up Sequence:** This diagram shows the timing of a I2C or internal initiated reset command followed by a startup (battery and/or USB charger adapter connected, VSUP > ResVoltRise)

ams Datasheet Page 37

[v1-11] 2016-Dec-14 Document Feedback

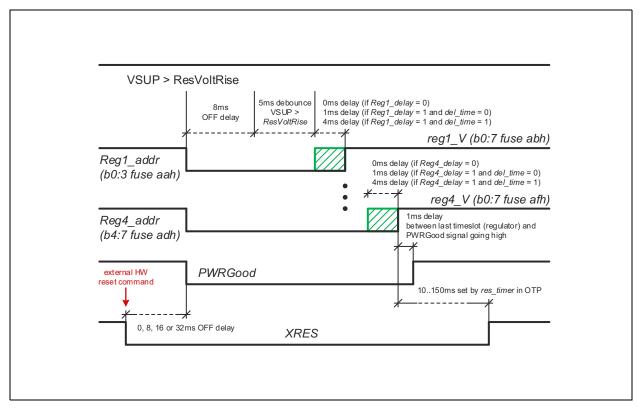

Figure 46: Start-Up Sequence Diagram 5/5

**Start-Up Sequence:** This diagram shows the timing of an external initiated reset command (forcing XRES to low) followed by a startup (battery and/or USB charger adapter connected, VSUP > ResVoltRise)

## Reset

XRES is a low active bi-directional pin. An external pull-up to the periphery supply has to be added. During each reset cycle the following states are controlled by the AS3701:

- · Pin XRES is forced to GND

- Normal startup with programmable power-ON sequence and regulator voltages

- Reset is active until the programmable reset timer (set by res\_timer [ResetTimer]) expires

- All registers are set to their default values after power-ON, except the reset control- and status-registers.

- XRES is pulled high by the external resistor and the whole system is leaving the reset state

Note(s): Programming is controlled by the internal Boot-OTP

Page 38

Document Feedback

[v1-11] 2016-Dec-14

#### **RESET Reasons**

Reset can be activated from the below mentioned different sources:

- VPOR has been reached (VSUP rising from the scratch)

- ResVoltFall was reached (VSUP < ResVoltFall [Battery\_ voltage\_monitor])

- Software forced reset (force\_reset [ResetControl] = 1)

- XRES is pulled to low

- ON-key long press (on\_tast\_sw is set to "0")

- Overtemperature

## **Voltage Detection**

A Reset gets initiated, if VSUP rises from scratch and reaches the V<sub>POR</sub> level. The pin XRES is only released if VSUP is above ResVoltRise.

V<sub>XRES</sub> fall is only accepted if the reset condition is longer than  $V_{XRES\ mask}$ . This guard time is used to avoid a complete reset of the system in case of short drops of VSUP.

Figure 47: **Voltage Detection Reset**

| SupResEn | power_off_at_vsuplow = 0                                                                                                                               |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | A reset is initiated, if VSUP < 2.7V.  If enabled, an interrupt is executed at <i>ResVoltFall</i> .  Automatic restart, if VSUP > <i>ResVoltRise</i> . |

| 1        | A reset is initiated, if VSUP < ResVoltFall. Automatic restart, if VSUP > ResVoltRise.                                                                 |

#### Software Forced Reset

Writing "1" into the register bit force\_reset [ResetControl] immediately starts a reset cycle. The bit force\_reset is automatically cleared by this reset.

# **External Triggered Reset**

If the pin XRES is pulled from high to low by an external source (e.g. microprocessor or button) a reset cycle is started as well.

ams Datasheet Page 39 Document Feedback

## Long ON-Key Press

For a reset initiated with a long ON-key press, this feature must be enabled by setting the bit <code>onkey\_lpress\_en[ResetControl]</code> to "1". When applying a high level on the ON input pin for 4s/8s (depending on <code>on\_lpress\_delay[ReferenceControl]</code>) a reset gets initiated, if the bit <code>onkey\_lpress\_reset[ReferenceControl]</code> is set to "1". This is thought as a safety feature when the SW hangs up. A long ON key reset is just possible, if the ON key works as a push-button (<code>on\_tast\_sw[ReferenceControl]</code> is set to "0")

Figure 48: ON-Key Long Press RESET Behavior

| onkey_<br>lpress_en | onkey_<br>lpress_reset | on_<br>lpress_<br>delay | on_tast_sw | Long Press Behavior                                 |

|---------------------|------------------------|-------------------------|------------|-----------------------------------------------------|

| 0                   | Х                      | X                       | X          | No ON-key long press reset possible                 |

| 1                   | 1                      | 0                       | 0          | 8s long press on the ON-push-button forces a reset  |

| 1                   | 1                      | 1                       | 0          | 4s long press on the ON-push- button forces a reset |

| 1                   | 1                      | Х                       | 1          | No reset possible, if ON-key works as a switch      |

## Overtemperature Reset

A reset cycle is getting started, if the overtemperature threshold is reached and the bit ov\_temp\_140 [OvertemperatureControl] is set.

## **Parameter**

Figure 49: XRES Input Characteristics

| Symbol               | Parameter                | Note | Min | Тур | Max | Unit |

|----------------------|--------------------------|------|-----|-----|-----|------|

| V <sub>XRES_IL</sub> | RESET low level voltage  |      |     |     | 0.4 | V    |

| V <sub>XRES_IH</sub> | RESET high level voltage |      | 1.4 |     |     | V    |

Page 40

Document Feedback

[v1-11] 2016-Dec-14

## Figure 50: Reset Levels

| Symbol                 | Parameter                                                                                   | Note                                                     | Min | Тур                            | Max | Unit        |

|------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------|-----|--------------------------------|-----|-------------|

| V <sub>POR</sub>       | Overall power on reset                                                                      | Monitor on VSUPpower ON reset for all internal functions | 1.5 | 2.0                            | 2.3 | <b>&gt;</b> |

| $V_{XRES\_rise}$       | RESET level for V <sub>SUP</sub> rising                                                     | Monitor voltage on VSUP rising level                     |     | ResVolt<br>Rise <sup>(1)</sup> |     | ٧           |

| V                      | RESET Level for V <sub>SUP</sub> falling                                                    | Monitor voltage on<br>VSUP falling level                 |     | 2.7                            |     | V           |

| V <sub>XRES_fall</sub> | NESET LEVELION VSUPTAINING                                                                  | if SupResEn = 1 only                                     |     | ResVolt<br>Fall <sup>(2)</sup> |     | ٧           |

|                        | Mask time for VXRES_fall Duration for VBAT < ResVoltFall until a reset cycle is started (3) | FastResEn = 0                                            |     | 3                              |     | ms          |

| V <sub>XRES_mask</sub> |                                                                                             | FastResEn = 1                                            |     | 64                             |     | μs          |

#### Note(s):

- 1. The selection of the range and level is done via OTP. It's recommended to set the ResVoltRise level 200mV above the ResVoltFall level to have a hysteresis

- 2. 2.7V is the default value, other levels can be set via SW

- 3. XRES signal is debounced with the specific mask time for rising- and falling slope of  $V_{BAT}$

## Stand-By

Stand-by allows shutting down all rails or just a selected number and can be achieved by one of the following cases:

## **Enter Via GPIO**

To enter the Stand-by mode via GPIO command, the following settings have to be done:

- Enable just these interrupt sources which should lead to leave the stand-by mode

- Make sure that the specified interrupt is inactive (clear the Register *[InterruptStatus]* by register reading)

- Set the *gpioX\_mode* [GPIOxcontrol] to input and the *gpioX\_iosf* [GPIOxcontrol] should be set to Stand-by + vselect input (gpioX\_iosf = 6)

- Set RegX\_select [Reg\_Control] and RegX\_voltage [RegX\_ Voltage] if another voltage is needed during stand-by for up to 2 regulators

- Define which regulators should be kept powered during Stand-by mode (sdX\_stby\_on and ldoX\_stby\_on [Reg\_ standby\_mod1])

- Set the off\_delay [Startup\_Control] for going into stand-by after the GPIO command

- Activate the selected GPIO

ams Datasheet Page 41

[v1-11] 2016-Dec-14 Document Feedback

#### **Enter Via SW**

To enter the Stand-by mode via I<sup>2</sup>C command, the following settings have to be done:

- Enable just these interrupt sources which should lead to leave the stand-by mode

- Make sure that the specified interrupt is inactive (clear the Register [InterruptStatus] by register reading)

- Define which regulators should be kept powered during Stand-by mode (sdX\_stby\_on and ldoX\_stby\_on [Reg\_ standby\_mod1])

- Set the off\_delay [Startup\_Control] for going into stand-by after the I<sup>2</sup>C command

- Set standby\_mode\_on [ReferenceControl] to 1

During Stand-by all regulators are switched OFF, except those, which are selected either with <code>RegX\_select[Reg\_Control]</code> or with <code>sdX\_stby\_on</code> and <code>IdoX\_stby\_on[Reg\_standby\_mod1]</code>. XRES goes active (can be disabled with <code>standby\_reset\_disable[Sartup\_Control]</code>) and pwr\_good goes inactive. Furthermore, to save power especially in this mode, the internal oscillator is just working, when it is needed.

## **Leaving Stand-By**

Stand-by can be terminated by:

- Any kind of interrupt (if it was defined right before going into Stand-by)

- ON-key push-button press (on\_tast\_sw is set to "0")

- Reset

- Power OFF

- Overtemperature

Page 42

Document Feedback

[v1-11] 2016-Dec-14

## **Power OFF**

During power OFF state all circuits are shut-OFF. Thus the current consumption of AS3701 is reduced to about 1µA. Except the reset control registers, all other registers are set to their default value after power-ON.

The chip stays in power OFF mode until

- The external pin ON is pulled high

- The charger is inserted or

- The VPOR level is touched to start a complete reset cycle.

The AS3701 can be set into Power OFF if one of the following conditions occur:

- ResVoltFall was reached (VSUP < ResVoltFall [Battery\_</li> voltage\_monitor])

- Software forced power OFF (power\_off [ResetControl] = 1)

- ON-key long press

- auto\_off [Startup\_Control] is enabled (VSUP rising from the scratch)

#### **Voltage Detection**

If VSUP falls below ResVoltFall for longer than 500ms and the bit power\_off\_at\_vsuplow [Startup\_Control] is set to "1", the PMIC enters the Power Off mode.

Figure 51: **Voltage Detection Power OFF**

| SupResEn | power_off_at_vsuplow = 1                                                                                                                                                                         |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | A power-down is initiated, if VSUP < 2.7V.  If enabled, an interrupt is executed at <i>ResVoltFall</i> .  Restart only possible with ON key or charger insertion, if VSUP > <i>ResVoltRise</i> . |

| 1        | A power-down is initiated, if VSUP < ResVoltFall.  Restart only possible with ON key or charger insertion, if VSUP > ResVoltRise.                                                                |

## Software Forced Power OFF

To put the chip into power off mode, write '1' into power\_off [ResetControl]. In ON-key-switch configuration the AS3701 will startup immediately again, if the switch is in ON position.

The bit power\_off bit is automatically cleared by a startup and its associated reset cycle.

ams Datasheet Page 43 **Document Feedback**

## Long ON-Key Press

For a power OFF asserted with a long ON-key press, this feature must be enabled by setting the bit <code>onkey\_lpress\_en</code> [ResetControl] to "1". When applying a high level on the ON input pin for 4s/8s (depending on <code>on\_lpress\_delay</code> [ReferenceControl]) a power off gets initiated, if the bit <code>onkey\_lpress\_reset</code> [ReferenceControl] is set to "0". A long ON key power off is possible, if the ON key works as a push-button or as a switch.

Figure 52:

ON-Key Long Press Power OFF Behavior

| onkey_<br>lpress_en | onkey_lpress_<br>reset | on_reset_<br>delay | on_tast_sw | Long Press Behavior                                                     |

|---------------------|------------------------|--------------------|------------|-------------------------------------------------------------------------|

| 0                   | Х                      | Х                  | Х          | No ON-key long press power OFF is possible                              |

| 1                   | 0                      | 0                  | 0          | 8s long press on the ON-push-button forces a power OFF (1)              |

| 1                   | 0                      | 1                  | 0          | 4s long press on the ON-push-button forces a power OFF (1)              |

| 1                   | 0                      | 0                  | 1          | Forces a power OFF after 8s, if<br>ON-switch is set to OFF position (2) |

| 1                   | 0                      | 1                  | 1          | Forces a power OFF after 4s, if<br>ON-switch is set to OFF position (2) |

#### Note(s):

- 1. If a USB charger adapter is connected, the ON-key push-button long press would only force a power-off, if the bit chg\_pwr\_off\_en is set to "1"!

- 2. If a USB charger adapter is connected and the bit chg\_pwr\_off\_en is set to "0" (level detection), the ON-key-switch OFF position has no influence. The PMIC will stay in Activemode as long as the USB adapter is present! If a USB adapter is connected and the bit chg\_pwr\_off\_en is set to "1" (edge detection), the PMIC can be set into Power-OFF via I<sup>2</sup>C, if the ON-key switch is also in OFF position!

#### Auto-OFF

If VSUP is rising from the scratch and the bit <code>auto\_off[Startup\_Control]</code> is set to "1", the PMIC enters immediately the Power-OFF mode right after VSUP reaches the <code>ResVoltRise</code>. If the ON-key is in switch configuration the Auto-OFF feature only works, when the switch is in OFF position during VSUP rising from scratch!

Page 44

Document Feedback

[v1-11] 2016-Dec-14

## **Internal References**

# Description

The internal 2.0V reference and the oscillator are powered either via the VUSB input pin or via the VBAT input pin, depending on which level is higher. The internal oscillator is used for PWM, SD frequency and all timings, which are needed for the charger, the startup sequence and reset delays.

## **Parameter**

Figure 53: Reference Parameter

| Symbol           | Parameter                            | Conditions                                             | Min | Тур  | Max | Unit |

|------------------|--------------------------------------|--------------------------------------------------------|-----|------|-----|------|

| f <sub>CLK</sub> | Accuracy of internal reference clock | Adjustable by serial interface register <i>clk_int</i> | -12 | fськ | +12 | %    |

Reference Parameter: Shows the key electrical parameter of the on-chip oscillator

ams Datasheet Page 45

[v1-11] 2016-Dec-14 Document Feedback

## **GPIO Pins**

AS3701A contains 2 GPIO pins and AS3701B offers 5 GPIO pins. Each of the pins can be configured as digital input, digital input (with pull-up or pull-down), push-pull output or open drain output (with or without pull-up). When configured as output the output source can be a register bit, or the PWM generator.

Additional the GPIO1 and GPIO2 can be configured as a Current sink and the GPIO3 and GPIO4 (only available in AS3701B) can offer an input to connect a NTC for supervising the battery temperature.

The polarity of the input and output signals can be inverted with the corresponding *gpioX\_invert* [GPIOXcontrol] bit, all further descriptions refer to normal (non-inverted) mode.

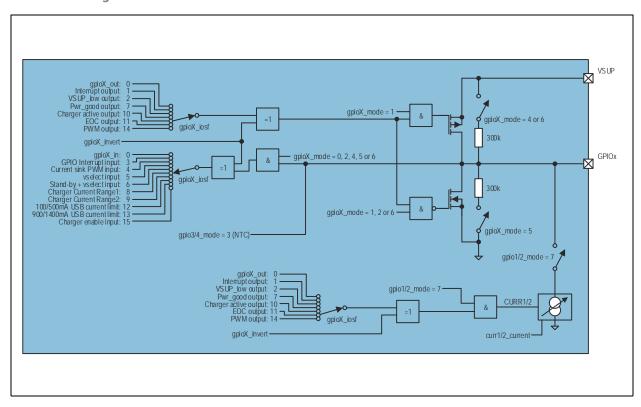

Figure 54: GPIO Block Diagram

**GPIO Block Diagram:** Shows the internal structure of the IO pads

Page 46

Document Feedback

[v1-11] 2016-Dec-14

Figure 55: **GPIO Pin Characteristics**

| Symbol                 | Parameter                 | Note                                               | Min            | Тур | Max            | Unit |

|------------------------|---------------------------|----------------------------------------------------|----------------|-----|----------------|------|

| V <sub>GPIO_max</sub>  | Max voltage on GPIOx pins | Pin VSUP is used as supply for the GPIO pins       |                |     | VSUP + 0.3     | ٧    |

| V <sub>OL</sub>        | Low level output voltage  | I <sub>OL</sub> =+1mA<br>digital output            |                |     | +0.4           | ٧    |

| V <sub>OH</sub>        | High level output voltage | I <sub>OH</sub> =–1mA; digital<br>push-pull output | 0.8*VSUP       |     |                | ٧    |

| V <sub>IL</sub>        | Low level input voltage   | digital input                                      |                |     | 20% of<br>VSUP | ٧    |

| V <sub>IH</sub>        | High level input voltage  | digital input                                      | 60% of<br>VSUP |     |                | ٧    |

| I <sub>LEAKAGE</sub>   | Leakage current           | high impedance                                     |                |     | 1              | μΑ   |

| R <sub>pull-up</sub>   | Pull-up resistance        | if enabled;<br>VSUP = 3.7V                         |                | 300 |                | kΩ   |

| R <sub>pull-down</sub> | Pull-down resistance      | if enabled;<br>VSUP = 3.7V                         |                | 300 |                | kΩ   |

**GPIO Pins:** Shows the key electrical parameter of the GPIO pins. VSUP = 2.7 to 5.5V; unless otherwise mentioned

## **IO Functions**

## **Normal IO Operation**

If set to input, the logic level of the signal present at the GPIOx pin can be read from *apioX* in [GPIOsignal in]. This mode is also used for the ON/OFF control of the DCDC and LDOs. The selection, which regulator is controlled by which GPIO, is done with the gpio\_ctrl\_sdX [GPIO\_ctrl2] or gpio\_ctrl\_ldoX [GPIO\_ ctrl2] bits.

The *apioX\_mode* [GPIOxcontrol] should be set to input. The gpioX\_iosf [GPIOxcontrol] should be set to gpioX\_in.

If the output mode is chosen, *qpioX\_out* [GPIOsignal\_out] specifies the logic level of the GPIOx pin.

The *gpioX\_mode* [GPIOxcontrol] should be set to output. The gpioX\_iosf [GPIOxcontrol] should be set to gpioX\_out.

For GPIO1 and GPIO2, the logic level of the output signal can be visualized via the Current sinks. In this case the *gpioX\_mode* [GPIOxcontrol] should be set to CURRx.

ams Datasheet Page 47 Document Feedback

#### **Interrupt Output**

GPIOx pin logic state is derived from the interrupt signal XIRQ. Whenever an interrupt is present the GPIOx pin will be pulled high.

The *gpioX\_mode* [GPIOxcontrol] should be set to output.

The *gpioX\_iosf* [GPIOxcontrol] should be set to *Interrupt output*.

For GPIO1 and GPIO2, the Interrupt output signal can be visualized via the Current sinks. In this case the *gpioX\_mode* [GPIOxcontrol] should be set to CURRx.

#### VSUP\_low Output

GPIOx pin will go high, if VSUP falls below ResVoltFall and SupResEn [Battery\_voltage\_monitor] = 0.

The *gpioX\_mode* [GPIOxcontrol] should be set to output.

The *gpioX\_iosf* [GPIOxcontrol] should be set to VSUP\_low output.

For GPIO1 and GPIO2, the VSUP\_low output signal can be visualized via the Current sinks. In this case the *gpioX\_mode* [GPIOxcontrol] should be set to CURRx.

## **PWRGOOD Output**

This signal will go high at the end of the start-up sequence. This can be used as a second reset signal to the processor to e.g. start oscillators.

The *gpioX\_mode* [GPIOxcontrol] should be set to output.

The *gpioX\_iosf* [GPIOxcontrol] should be set to Pwr\_good output.

For GPIO1 and GPIO2, the Pwr\_good output signal can be visualized via the Current sinks. In this case the *gpioX\_mode* [GPIOxcontrol] should be set to CURRx.

#### **Charger Active Output**

When selected, the GPIOx will go high if the charger is active. The *gpioX\_mode* [GPIOxcontrol] should be set to output. The *gpioX\_iosf* [GPIOxcontrol] should be set to Charger active output.

For GPIO1 and GPIO2, the Charger active output signal can be visualized via the Current sinks. In this case the *gpioX\_mode* [GPIOxcontrol] should be set to CURRx.

## **EOC Output**

When selected, the GPIOx will go high if the charger has reached the EOC state.

The gpioX\_mode [GPIOxcontrol] should be set to output.

The gpioX\_iosf [GPIOxcontrol] should be set to EOC output.

For GPIO1 and GPIO2, the EOC output signal can be visualized via the Current sinks. In this case the *gpioX\_mode* [GPIOxcontrol] should be set to CURRx.

Page 48

Document Feedback

[v1-11] 2016-Dec-14

#### **PWM Output**

When selected, the GPIOx output provides the PWM signal generated by the internal programmable PWM generator. Its timing is defined by pwm\_h\_time [pwm\_control\_h], pwm\_l\_time [pwm\_control\_l] and pwm\_div [ReferenceControl]. The gpioX\_mode [GPIOxcontrol] should be set to output. The gpioX\_iosf [GPIOxcontrol] should be set to PWM output.

For GPIO1 and GPIO2, the PWM output signal can be visualized via the Current sinks. In this case the *gpioX\_mode* [GPIOxcontrol] should be set to CURRx.

## **GPIO** Interrupt Input

A falling or rising edge will set the *gpio\_int* bit. The *gpioX\_mode* [GPIOxcontrol] should be set to input. The *gpioX\_iosf* [GPIOxcontrol] should be set to GPIO Interrupt input.

#### **Current Sink PWM Input**

The GPIO is used as PWM input for the current sink to control the current. 100% PMW mode will set the current to the value set in *currX\_current* [*currX\_value*] register.

The gpioX\_mode [GPIOxcontrol] should be set to input. The gpioX\_iosf [GPIOxcontrol] should be set to Current sink PWM input.

## Vselect Input

As long as the GPIOx pin is low the DCDC/LDOs operate with the normal register settings. If the GPIOx pin goes high, the settings will change to the ones stored in *RegX\_voltage* [*RegX\_Voltage*].

The gpioX\_mode [GPIOxcontrol] should be set to input.

The gpioX\_iosf [GPIOxcontrol] should be set to vselect input.

GPIO1 and GPIO2 may be used to control two regulators separately.

Figure 56: GPIO Vselect Modes

| gpio1_<br>iosf | gpio2_<br>iosf | gpio3_<br>iosf | gpio4_<br>iosf | gpio5_<br>iosf | Vselect Mode                                                                                         |