# **AS5510** Linear Hall Sensor with I<sup>2</sup>C Output

### **General Description**

The AS5510 is a Linear Hall Sensor with 10 bit resolution and  $I^2C$  interface. It can measure absolute position of lateral movement of a simple 2-pole magnet. Depending on the magnet size, a lateral stroke of 0.5~2mm can be measured with air gaps around 1.0mm. To conserve power, the AS5510 may be switched to a power down state when it is not used. It is available in a WLCSP and SOIC8 package and qualified for an ambient temperature range from -30°C to 85°C.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of AS5510, Linear Hall sensor with I<sup>2</sup>C output are listed below:

Figure 1: Added Value of Using AS5510

| Benefits                           | Features                                                 |

|------------------------------------|----------------------------------------------------------|

| Highest reliability and durability | Contactless position measurement                         |

| Ideal for battery powered devices  | Power down mode                                          |

| Easy to use                        | Simple configuration over the I <sup>2</sup> C interface |

| High-resolution output             | 10bit resolution                                         |

| Operates in wide magnetic range    | Programmable sensitivity                                 |

| Smallest form factor               | Available in two different packages: WLCSP & SOIC8       |

#### Applications

The AS5510 is ideal for:

- Position sensing

- Servo drive feedback

- Camera lens control

- Closed loop position control.

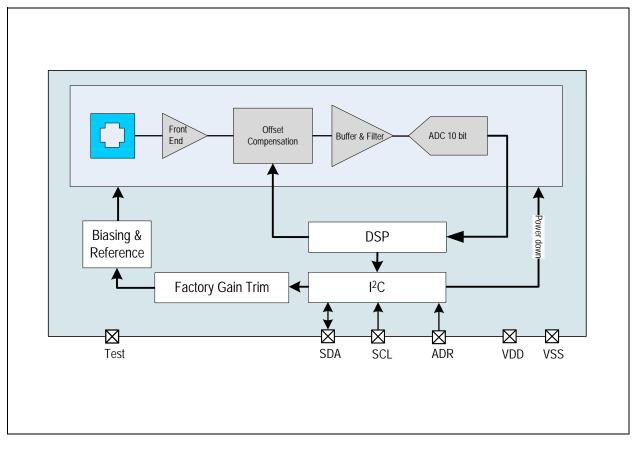

## **Block Diagram**

The functional blocks of this device for reference are shown below:

# **Pin Assignment**

#### The AS5510 pin assignments are described below.

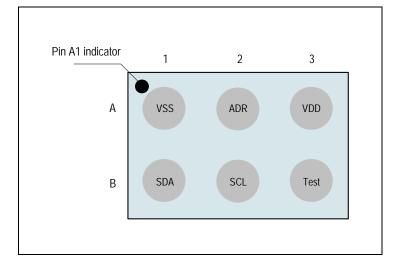

Figure 3: Pin Diagram for WLCSP Package

### Pin Configuration of AS5510 in

**WLCSP Package(Top view):** The AS5510 is available in a 6-pin Chip Scale Package with a ball pitch of 400µm.

**Pin Configuration of AS5510 in SOIC8 Package(Top view):** Package drawing not to scale.

| NC<br>VSS  | 1 () | AS5510 | 8      | NC SCL      |

|------------|------|--------|--------|-------------|

| ADR<br>VDD | 4    | AS     | 6<br>5 | SDA<br>TEST |

Figure 5: Pin Description

| Pin  | Pin Nu | umber | Pin Type                                     | Description                                                                        |

|------|--------|-------|----------------------------------------------|------------------------------------------------------------------------------------|

| Name | WLCSP  | SOIC8 |                                              | Decemption                                                                         |

| NC   | -      | 1     | -                                            | Not Connected                                                                      |

| VSS  | A1     | 2     | Supply pin                                   | Negative supply pin, analog and digital ground                                     |

| ADR  | A2     | 3     | Digital input                                | l <sup>2</sup> C address selection pin<br>Connect to either VSS (56h) or VDD (57h) |

| VDD  | A3     | 4     | Supply pin                                   | Positive supply pin. A capacitor of 100nF should be connected to this pin and VSS  |

| Test | B3     | 5     | Digital input/output                         | Test pin, must be connected to VSS during operation                                |

| SDA  | B1     | 6     | Digital input / Digital<br>output open drain | I <sup>2</sup> C data I/O, 20mA driving capability                                 |

| SCL  | B2     | 7     | Digital input                                | l <sup>2</sup> C clock                                                             |

| NC   | -      | 8     | -                                            | Not Connected                                                                      |

# Absolute Maximum Ratings

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Figure 6: Absolute Maximum Ratings

| Parameter                                      | Min               | Max     | Units | Comments                                                                                                            |

|------------------------------------------------|-------------------|---------|-------|---------------------------------------------------------------------------------------------------------------------|

| DC supply voltage at pin VDD                   | -0.3              | 5       | V     |                                                                                                                     |

| Input pin voltage                              | -0.3              | VDD+0.3 | V     |                                                                                                                     |

| Input current (latchup immunity)               | -100              | 100     | mA    | Norm: JEDEC 78                                                                                                      |

| Electrostatic discharge                        |                   | ±2      | kV    | Norm: MIL 883 E method 3015                                                                                         |

| Storage temperature                            | -55               | 125     | °C    |                                                                                                                     |

| Body temperature (Lead-free package) for WLCSP |                   | 260     |       | The reflow peak soldering temperature<br>(body temperature) specified is in<br>accordance with IPC/ JEDEC J-STD-020 |

| Body temperature (Lead-free package) for SOIC8 | T <sub>Body</sub> | 260     | °C    | "Moisture/Reflow Sensitivity<br>Classification for Non-Hermetic Solid<br>State Surface Mount Devices".              |

| Relative Humidity non-condensing               | 5                 | 85      | %     |                                                                                                                     |

| Moisture Sensitivity Level for WLCSP           | 1                 |         |       | Represents a max. floor life time of                                                                                |

| Moisture Sensitivity Level for SOIC8           |                   | 3       |       | unlimited                                                                                                           |

# **Electrical Characteristics**

Figure 7: Operating Conditions

| Symbol            | Parameter                 | Conditions                 | Min | Тур | Мах | Units |

|-------------------|---------------------------|----------------------------|-----|-----|-----|-------|

| VDD               | Supply voltage at pin VDD |                            | 2.5 | 3   | 3.6 | V     |

| I <sub>supp</sub> | Supply current            | @ 25°C ambient temperature |     | 3.5 |     | mA    |

| I <sub>pd</sub>   | Power down current        |                            |     | 25  |     | μΑ    |

| T <sub>amb</sub>  | Ambient temperature       |                            | -30 |     | 85  | °C    |

# DC Characteristics for Digital Inputs and Outputs

#### **CMOS Input: ADR**

Operating conditions:  $T_{amb} = -30^{\circ}C$  to  $85^{\circ}C$ , VDD = 2.5V to 3.6V (3V operation) unless otherwise noted.

#### Figure 8: Electrical Characteristics ADR Input

| Symbol            | Parameter                | Min       | Тур | Max       | Units |

|-------------------|--------------------------|-----------|-----|-----------|-------|

| V <sub>IH</sub>   | High level input voltage | 0.7 * VDD |     | VDD       | V     |

| V <sub>IL</sub>   | Low level input voltage  | 0         |     | 0.3 * VDD | V     |

| I <sub>LEAK</sub> | Input leakage current    | -1        |     | 1         | μΑ    |

#### CMOS I<sup>2</sup>C: SDA, SCL

Operating conditions: Tamb = -30°C to 85°C, VDD = 2.5V to 3.6V (3V operation) unless otherwise noted.

Figure 9: Electrical Characteristics I<sup>2</sup>C

| Symbol           | Parameter                                                                         | Conditions | Min        | Max                | Units |

|------------------|-----------------------------------------------------------------------------------|------------|------------|--------------------|-------|

| V <sub>IL</sub>  | LOW-level input voltage                                                           |            | -0.5       | 0.3 * VDD          | V     |

| V <sub>IH</sub>  | HIGH-level input voltage                                                          |            | 0.7 * VDD  | VDD +0.5V          | V     |

| V <sub>hys</sub> | Hysteresis of Schmitt Trigger inputs                                              | VDD > 2.5V | 0.05 * VDD |                    | V     |

| V <sub>OL</sub>  | LOW-level output voltage<br>(open-drain or open-collector) at<br>3mA sink current | VDD > 2.5V |            | 0.4V               | v     |

| I <sub>OL</sub>  | LOW-level output current                                                          | VOL = 0.4V | 20         |                    | mA    |

| t <sub>of</sub>  | Output fall time from V <sub>IHmax</sub> to<br>V <sub>ILmax</sub>                 |            |            | 120 <sup>(1)</sup> | ns    |

| t <sub>SP</sub>  | Pulse width of spikes that must be suppressed by the input filter                 |            |            | 50 <sup>(2)</sup>  | ns    |

| li               | Input current at each I/O pin                                                     |            | -10        | +10 <sup>(3)</sup> | μΑ    |

| C <sub>B</sub>   | Total capacitive load for each bus<br>line                                        |            |            | 550                | pF    |

| C <sub>I/O</sub> | I/O capacitance (SDA, SCL) <sup>(4)</sup>                                         |            |            | 10                 | pF    |

#### Note(s) and/or Footnote(s):

- 1. In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used this has to be considered for bus timing.

- 2. Input filters on the SDA and SCL inputs suppress noise spikes of less than 50 ns.

- 3. I/O pins of Fast-mode and Fast-mode plus devices must not obstruct the SDA and SCL lines if VDD is switched OFF.

- 4. Special purpose devices such as multiplexers and switches may exceed this capacitance due to the fact that they connect multiple paths together.

# **Electrical and Magnetic Specifications**

#### Figure 10: Electrical and Magnetic Specifications

| Symbol                | Parameter                                               | Conditions                                                                                                                                       | Тур    | Max  | Units |

|-----------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------|

| RES                   | Resolution                                              |                                                                                                                                                  | 10     |      | bit   |

|                       |                                                         | Default Setting                                                                                                                                  | ±50    |      | mT    |

| Bin                   | Magnetic Input Range                                    |                                                                                                                                                  | ±25    |      | mT    |

| Diri                  | magnetic input Range                                    | Configurable via I <sup>2</sup> C or factory trimming option                                                                                     | ±12.5  |      | mT    |

|                       |                                                         |                                                                                                                                                  | ±18.75 |      | mT    |

| Offset <sub>inp</sub> | Input related offset <sup>(1)</sup>                     |                                                                                                                                                  |        | 0.45 | mT    |

|                       | Linearity error <sup>(2)</sup>                          |                                                                                                                                                  |        | 3    | %     |

| t <sub>PwrUp</sub>    | Initial Power up time<br>from cold start <sup>(3)</sup> | This time is needed for the first<br>power-up of the device until the<br>offset compensation is finished;<br>Includes readout of the PPROM fuses |        | 1.5  | ms    |

| t <sub>PwrOn</sub>    | Power-on time <sup>(4)</sup>                            | Time after switching from<br>power-down mode into active mode<br>until the offset compensation is<br>finished                                    | 250    |      | μs    |

# amu

| Symbol               | Parameter                          | Conditions                                              | Тур | Мах  | Units |  |  |  |

|----------------------|------------------------------------|---------------------------------------------------------|-----|------|-------|--|--|--|

|                      | Fast Mode (Default setting)        |                                                         |     |      |       |  |  |  |

| f <sub>S</sub>       | ADC sampling<br>frequency          | After offset compensation finished                      |     | 50   | KHz   |  |  |  |

| t <sub>delay</sub>   | System propagation<br>delay        |                                                         |     | 20   | μs    |  |  |  |

| Noise <sub>inp</sub> | Input related noise <sup>(5)</sup> | ed noise <sup>(5)</sup> Equivalent to 8 * rms           |     | 0.8  | mTpp  |  |  |  |

|                      | SI                                 | ow Mode (I <sup>2</sup> C command option)               |     |      |       |  |  |  |

| f <sub>S</sub>       | ADC sampling<br>frequency          | After offset compensation finished                      |     | 12.5 | KHz   |  |  |  |

| t <sub>delay</sub>   | System propagation delay           |                                                         |     | 50   | μs    |  |  |  |

| Noise <sub>inp</sub> | Input related noise <sup>(5)</sup> | nput related noise <sup>(5)</sup> Equivalent to 8 * rms |     | 0.5  | mTpp  |  |  |  |

#### Note(s) and/or Footnote(s):

1. Offset  $_{inp}$  = 0.35mT residual offset + 0.1mT earth magnetic field.

2. Linearity error =

$$\lim_{a \to a} \operatorname{error} = 1 - \left( \frac{\operatorname{adc}_{out}(\operatorname{max}B) - \operatorname{adc}_{out}(\operatorname{zero}B)}{2 \times \left( \operatorname{adc}_{out}\left( \frac{\operatorname{max}B}{2} \right) - \operatorname{adc}_{out}(\operatorname{zero}B) \right)} \right) \times 100$$

3. This time is needed for the first power-up of the device until the offset compensation is finished; Includes readout of the PPROM fuses; It depends on the sensitivity setting.

4. Time after switching from power-down mode into active mode until the offset compensation is finished.

5. Input related Noise (Noise $_{Inp}$ ) is the repeatability of the measurement.

# **Detailed Description**

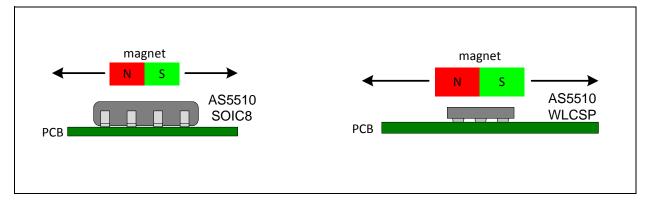

#### Figure 11:

Linear Position Sensor AS5510 + Magnet

**Linear Position Sensor AS5510 + Magnet:** The AS5510 can measure the absolute position of lateral movement in combination with a diametrical two pole magnet.

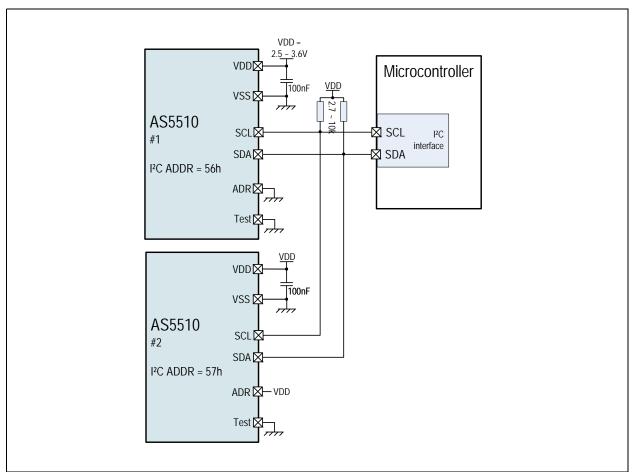

# **Typical Application**

The typical application circuit of AS5510 is shown below:

# I<sup>2</sup>C Interface

The AS5510 includes an I<sup>2</sup>C slave according to the NXP specification UM10204.

- 7-bit slave address **101011x**, the last address bit x is set by the ADR pin (0 or 1)

- Random/Sequential Read

- Byte/Page Write

- Fast-mode plus with 20mA SDA drive strength

- Internal hold time of 120ns for SDA signal is included (Start/Stop detection)

Not implemented:

- 10-bit Slave Address

- Clock Stretching

- General Call Address

- General Call Software Reset

- Read of Device ID

The communication from the AS5510 includes:

- Reading the magnetic field strength in 10-bit data

- Reading the status bits

**Note(s):** The I<sup>2</sup>C address of the chip is selected by hardware (pin ADR). Depending on the state of this pin, the I<sup>2</sup>C address is either:

- Pin ADR = LOW  $\rightarrow$  I<sup>2</sup>C address = 1010110b(56h)

- Pin ADR = HIGH  $\rightarrow$  I<sup>2</sup>C address = 1010111b(57h)

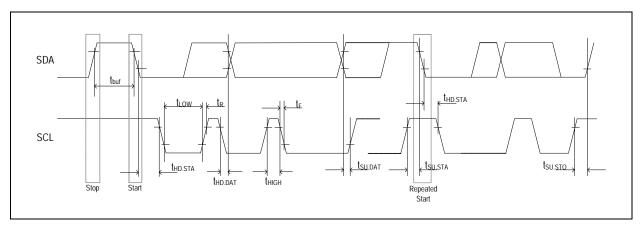

### I<sup>2</sup>C Interface Data

Operating conditions: Tamb = -30 to 85°C, VDD=2.5 to 3.6V (3V operation) unless otherwise noted.

| Symbol              | Parameter                                            |      | Тур | Max  | Units |

|---------------------|------------------------------------------------------|------|-----|------|-------|

| f <sub>SCLK</sub>   | SCL clock frequency                                  |      |     | 1    | MHz   |

| t <sub>BUF</sub>    | Bus free time; time between STOP and START condition | 0.5  |     |      | μs    |

| t <sub>HD.STA</sub> | Hold time; (repeated) START condition <sup>(1)</sup> | 0.26 |     |      | μs    |

| t <sub>LOW</sub>    | LOW period of SCL clock                              | 0.5  |     |      | μs    |

| t <sub>HIGH</sub>   | HIGH period of SCL clock                             | 0.26 |     |      | μs    |

| t <sub>SU.STA</sub> | Setup time for a repeated START condition            | 0.26 |     |      | μs    |

| t <sub>HD.DAT</sub> | Data hold time <sup>(2)</sup>                        |      |     | 0.45 | μs    |

| t <sub>SU.DAT</sub> | Data setup time <sup>(3)</sup>                       | 50   |     |      | ns    |

| t <sub>R</sub>      | Rise time of SDA and SCL signals                     |      |     | 120  | ns    |

| t <sub>F</sub>      | Fall time of SDA and SCL signals <sup>(4)</sup>      |      |     | 120  | ns    |

| t <sub>SU.STO</sub> | Setup time for STOP condition                        | 0.26 |     |      | μs    |

#### Note(s) and/or Footnote(s):

1. After this time the first clock is generated.

2. A device must internally provide a hold time of at least 120ns (Fast-mode Plus) for the SDA signal (referred to the V<sub>IHmin</sub> of the SCL) to bridge the undefined region of the falling edge of SCL.

- 3. A fast-mode device can be used in standard-mode system, but the requirement  $t_{SU,DAT}$  = 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{Rmax} + T_{SU,DAT} = 1000 + 250 = 1250$ ns before the SCL line is released.

- 4. In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used this has to be considered for bus timing.

Figure 13: I<sup>2</sup>C Timings

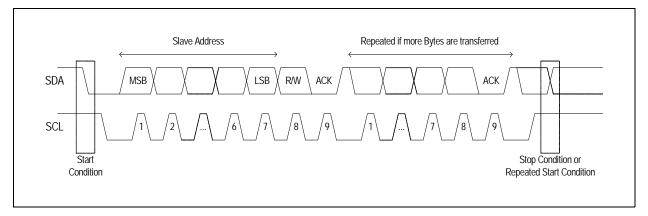

#### Figure 14: I<sup>2</sup>C Timing Diagram

# I<sup>2</sup>C Modes

The AS5510 supports the I<sup>2</sup>C bus protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are referred to as slaves. A master device that generates the serial clock (SCL), controls the bus access and generates the START and STOP conditions must control the bus. The AS5510 operates as a slave on the I<sup>2</sup>C bus. Within the bus specifications a standard mode (100 kHz maximum clock rate) a fast mode (400 kHz maximum clock rate) and fast mode plus (1MHz maximum clock rate) are defined. The AS5510 works in all three modes. Connections to the bus are made through the open-drain I/O lines SDA and the input SCL. Clock stretching is not included.

The following bus protocol has been defined:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH are interpreted as start or stop signals.

Accordingly, the following bus conditions have been defined:

#### **Bus Not Busy**

Both data and clock lines remain HIGH.

#### Start Data Transfer

A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

#### Stop Data Transfer

A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

# amu

#### Data Valid

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data. Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions are not limited, and are determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

#### Acknowledge

Each receiving device, when addressed, is obliged to generate an acknowledge bit after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit. A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of READ access to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

Depending upon the state of the R/W bit, two types of data transfer are possible:

# Data transfer from a Master Transmitter to a Slave Receiver.

The first byte transmitted by the master is the slave address, followed by R/W = 0. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. If the slave does not understand the command or data it sends a "not acknowledge". Data is transferred with the most significant bit (MSB) first.

# Data transfer from a Slave Transmitter to a Master Receiver.

The master transmits the first byte (the slave address). The slave then returns an acknowledge bit, followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a "not acknowledge" is returned. The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus is not released. Data is transferred with the most significant bit (MSB) first.

The AS5510 can operate in the following two modes:

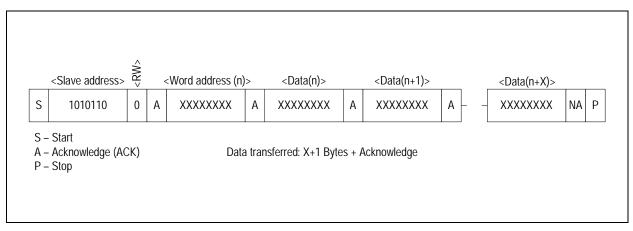

#### Slave Receiver Mode (Write Mode)

Serial data and clock are received through SDA and SCL. Each byte is followed by an acknowledge bit (or by a not acknowledge depending on the address-pointer pointing to a valid position). START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit (see Figure 16). The slave address byte is the first byte received after the START condition. The slave address byte contains the 7-bit AS5510 address. The 7-bit slave address is followed by the direction bit (R/W), which, for a write, is 0. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA. After the AS5510 acknowledges the slave address + write bit, the master transmits a register address to the AS5510. This sets the address pointer on the AS5510. If the address is a valid readable address the AS5510 answers by sending an acknowledge. If the address-pointer points to an invalid position a "not acknowledge" is sent. The master may then transmit zero or more bytes of data. In case of the address pointer pointing to an invalid address the received data are not stored. The address pointer will increment after each byte transferred independent from the address being valid. If the address-pointer reaches a valid position again, the AS5510 answers with an acknowledge and stores the data. The master generates a STOP condition to terminate the data write.

#### Figure 16: Data Write - Slave Receiver Mode

# amu

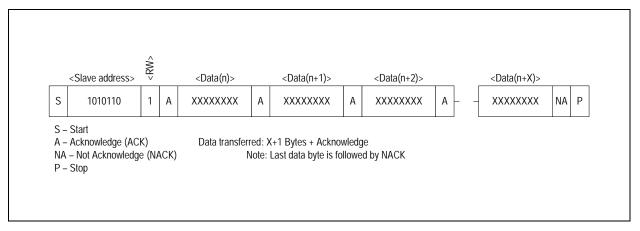

#### Slave Transmitter Mode (Read Mode)

The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit indicates that the transfer direction is reversed. Serial data is transmitted on SDA by the AS5510 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer (Figure 17 and Figure 18). The slave address byte is the first byte received after the master generates a START condition. The slave address byte contains the 7-bit AS5510 address. The 7-bit slave address is followed by the direction bit (R/W), which, for a read, is 1. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA line. The AS5510 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode the first address that is read is the last one stored in the register pointer. The AS5510 must receive a "not acknowledge" to end a read.

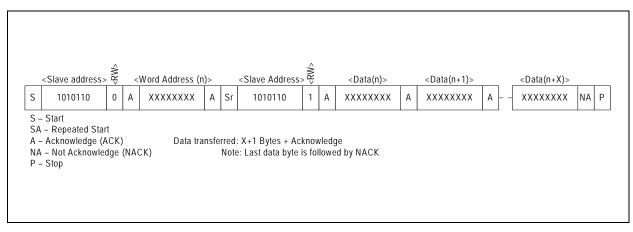

Figure 18: Data Read (Write Pointer, Then Read) - Slave Receive and Transmit

#### Automatic Increment of Address Pointer

The AS5510 slave automatically increments the address pointer after each byte transferred. The increase of the address pointer is independent from the address being valid or not.

#### Invalid Addresses

If the user sets the address pointer to an invalid address, the address byte is not acknowledged. Nevertheless a read or write cycle is possible. The address pointer is increased after each byte.

#### Reading

When reading from a wrong address, the AS5510 slave returns all zero. The address pointer is increased after each byte. Sequential read over the whole address range is possible including address overflow.

#### Write

A write to a wrong address is not acknowledged by the AS5510 slave, although the address pointer is increased. When the address pointer points to a valid address again, a successful write accessed is acknowledged. Page write over the whole address range is possible including address overflow.

#### SDA, SCL Input Filters

Input filters for SDA and SCL inputs are included to suppress noise spikes of less than 50ns. Furthermore the SDA line is delayed by 120ns to provide an internal hold time for Start/Stop detection to bridge the undefined region of the falling edge of SCL. The delay needs to be smaller than tHD.STA 260ns. For Standard-mode and Fast-mode an internal hold time of 300ns is required, which is not covered by the AS5510 slave.

# **Register Description**

Figure 19: Register Map <sup>(1)</sup>

| Register | Bit   |       |       |       |       |                             | Access      |        |      |  |

|----------|-------|-------|-------|-------|-------|-----------------------------|-------------|--------|------|--|

| Address  | 7     | 6     | 5     | 4     | 3     | 2                           | 1           | 0      | Туре |  |

| 00h      | D7    | D6    | D5    | D4    | D3    | D2                          | D1          | D0     | R    |  |

| 01h      |       |       |       |       | OCF   | Parity<br>(even)            | D9          | D8     | R    |  |

| 02h      |       |       |       |       |       | Fast(0)<br>Slow<br>mode (1) | Polarity(0) | PD(0)  | R/W  |  |

| 03h      | Offs7 | Offs6 | Offs5 | Offs4 | Offs3 | Offs2                       | Offs1       | Offs0  | R/W  |  |

| 04h      |       |       |       |       |       |                             | Offs9       | Offs8  | R/W  |  |

| 0Bh      |       |       |       |       |       |                             | Sens 1      | Sens 0 | R/W  |  |

#### Note(s) and/or Footnote(s):

1. Blank or not listed fields may contain factory settings. To change a configuration, read out the register, modify only the desired bits and write the new configuration.

# amu

#### Figure 20: Register Description

| Register Address | Name             | Description                                                                                                                                                                                                                                                                                                                    |

|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h, 01h         | D9 to D0         | 10 Bit ADC output value that corresponds to the magnetic field input                                                                                                                                                                                                                                                           |

| 01h              | Parity           | Even parity bit calculated from D9 to D0                                                                                                                                                                                                                                                                                       |

| 01h              | OCF              | Offset compensation loop status<br>0 = Offset compensation loop in use<br>1 = Offset compensation loop has finished                                                                                                                                                                                                            |

| 02h              | PD               | Power down mode<br>0 = Normal operation (Default)<br>1 = Power Down mode.                                                                                                                                                                                                                                                      |

| 02h              | Polarity         | Output signal polarity<br>0 = Normal polarity (Default)<br>1 = Reversed polarity (reversed magnet)                                                                                                                                                                                                                             |

| 02h              | Fast / Slow mode | 0 = Fast mode (Default)<br>1 = Slow mode. Enables averaging of the output values (reduced<br>noise, better repeatability slower sampling frequency. See<br>Electrical and Magnetic Specifications                                                                                                                              |

| 03h, 04h         | Offs9 to Offs0   | Contains the offset compensation value. For read access only.<br>Don't modify the register values.                                                                                                                                                                                                                             |

| 0Bh Sensitivity  |                  | Sensitivity setting<br>$0h = Input range \pm 50mT \rightarrow Sensitivity = 97.66\muT/LSB (Default)$<br>$1h = Input range \pm 25mT \rightarrow Sensitivity = 48.83\muT/LSB$<br>$2h = Input range \pm 12.5mT \rightarrow Sensitivity = 24.41\muT/LSB$<br>$3h = Input range \pm 18.75mT \rightarrow Sensitivity = 36.62\muT/LSB$ |

# Package Drawings & Markings

### WLCSP Package

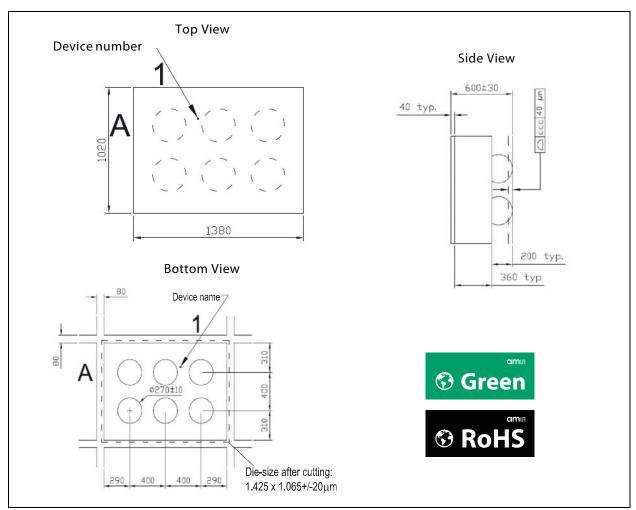

The WLCSP package drawings and markings are shown below:

Figure 21: Package Dimensions (WLCSP)

#### Note(s) and/or Footnote(s):

1. ccc Coplanarity

2. All dimensions in  $\mu m$

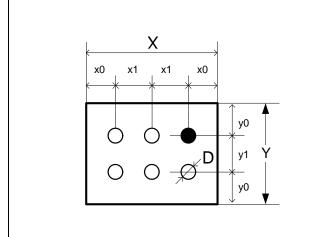

#### Figure 22: Recommended Footprint

| Package Dimensions |      |      |

|--------------------|------|------|

| Symbol             | Тур  | Unit |

| Х                  | 1460 | μm   |

| x0                 | 330  | μm   |

| x1                 | 400  | μm   |

| Y                  | 1100 | μm   |

| у0                 | 350  | μm   |

| y1                 | 400  | μm   |

| D                  | 270  | μm   |

Figure 24: Package Code XXXX

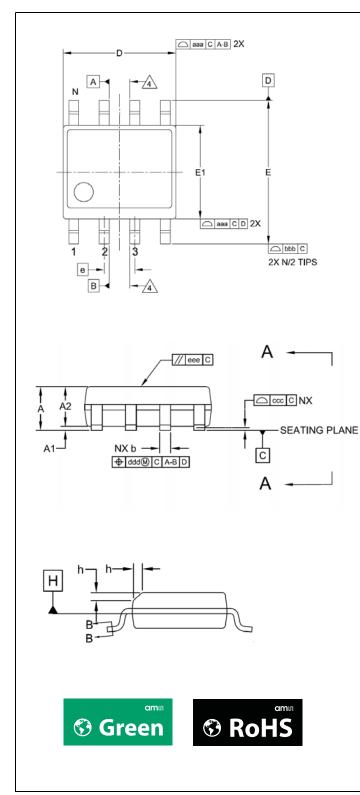

## SOIC8 Package

The SOIC8 package drawings and markings are shown below:

#### Figure 25: Package Dimensions SOIC8

| Symbol     | Min  | Nom      | Max  |

|------------|------|----------|------|

| А          | -    | -        | 1.75 |

| A1         | 0.10 | -        | 0.25 |

| A2         | 1.25 | -        | -    |

| b          | 0.31 | -        | 0.51 |

| с          | 0.17 | -        | 0.25 |

| D          | -    | 4.90 BSC | -    |

| E          | -    | 6.00 BSC | -    |

| E1         | -    | 3.90 BSC | -    |

| e          | -    | 1.27 BSC | -    |

| L          | 0.40 | -        | 1.27 |

| L1         | -    | 1.04 REF | -    |

| L2         | -    | 0.25 BSC | -    |

| R          | 0.07 | -        | -    |

| R1         | 0.07 | -        | -    |

| h          | 0.25 | -        | 0.50 |

| Θ          | 0°   | -        | 8°   |

| Θ1         | 5°   | -        | 15°  |

| Θ2         | 0°   | -        | -    |

| ааа        | -    | 0.10     | -    |

| bbb        | -    | 0.20     | -    |

| ссс        | -    | 0.10     | -    |

| ddd        | -    | 0.25     | -    |

| eee        | -    | 0.10     | -    |

| fff        | -    | 0.15     | -    |

| <u>ggg</u> | -    | 0.15     | -    |

| Ν          |      | 8        |      |

Figure 26: Package Marking (SOIC8)

Figure 27: Package Code XXX@

| ХХХ       | @                 |

|-----------|-------------------|

| Tracecode | Sublot Identifier |

# Ordering & Contact Information

The devices are available as the standard products shown in the figure below.

Figure 28: Ordering Information

| Ordering Code | Package               | Marking | Delivery Form | Delivery Quantity |

|---------------|-----------------------|---------|---------------|-------------------|

| AS5510-DWLT   | 6pin WL-CSP 1.4x1.1mm | AS5510  | Tape & Reel   | 12.000pcs         |

| AS5510-DWLM   | 6pin WL-CSP 1.4x1.1mm | AS5510  | Mini Reel     | 1000pcs           |

| AS5510-DSOT   | 8pin SOIC             | AS5510  | Tape & Reel   | 2.500pcs          |

| AS5510-DSOM   | 8pin SOIC             | AS5510  | Mini Reel     | 500pcs            |

$D \rightarrow Temperature \ Range: -30^\circ C \ to \ 85^\circ C$

$WL \rightarrow Package: WL-CSP Wafer Level - Chip Scale Package$

$SO \rightarrow Package: SOIC 8$

$\mathrm{T} \rightarrow \mathrm{Delivery}$  Form: Tape & Reel

$M \rightarrow Delivery$  Form: Mini Reel

Buy our products or get free samples online at: www.ams.com/ICdirect

Technical Support is available at: www.ams.com/Technical-Support

Provide feedback about this document at: www.ams.com/Document-Feedback

For further information and requests, e-mail us at: ams\_sales@ams.com

For sales offices, distributors and representatives, please visit: www.ams.com/contact

#### Headquarters

ams AG Tobelbaderstrasse 30 8141 Unterpremstaetten Austria, Europe

Tel: +43 (0) 3136 500 0 Website: www.ams.com

# RoHS Compliant & ams Green Statement

**RoHS:** The term RoHS compliant means that ams AG products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, RoHS compliant products are suitable for use in specified lead-free processes.

**ams Green (RoHS compliant and no Sb/Br):** ams Green defines that in addition to RoHS compliance, our products are free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material).

**Important Information:** The information provided in this statement represents ams AG knowledge and belief as of the date that it is provided. ams AG bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. ams AG has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams AG and ams AG suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# amu

# **Copyrights & Disclaimer**

Copyright ams AG, Tobelbader Strasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Devices sold by ams AG are covered by the warranty and patent indemnification provisions appearing inits General Terms of Trade. ams AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein. ams AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with ams AG for current information. This product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by ams AG for each application. This product is provided by ams AG "AS IS" and any express or implied warranties, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose are disclaimed.

ams AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of ams AG rendering of technical or other services.

# **Document Status**

| Document Status          | Product Status  | Definition                                                                                                                                                                                                                                                                     |

|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview          | Pre-Development | Information in this datasheet is based on product ideas in<br>the planning phase of development. All specifications are<br>design goals without any warranty and are subject to<br>change without notice                                                                       |

| Preliminary Datasheet    | Pre-Production  | Information in this datasheet is based on products in the<br>design, validation or qualification phase of development.<br>The performance and parameters shown in this document<br>are preliminary without any warranty and are subject to<br>change without notice            |

| Datasheet                | Production      | Information in this datasheet is based on products in<br>ramp-up to full production or full production which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade                                |

| Datasheet (discontinued) | Discontinued    | Information in this datasheet is based on products which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade, but these products have been superseded and<br>should not be used for new designs |

# **Revision Information**

| Changes from 1-06 (2014-Oct-30) to current revision 1-07 (2015-Feb-27) | Page |

|------------------------------------------------------------------------|------|

| Updated Figure 19                                                      | 19   |

| Updated Figure 20                                                      | 20   |

#### Note(s) and/or Footnote(s):

1. Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

2. Correction of typographical errors is not explicitly mentioned.

#### **Content Guide**

#### 1 General Description

- 1 Key Benefits & Features

- 1 Applications

- 2 Block Diagram

- 3 Pin Assignment

- 5 Absolute Maximum Ratings

#### **6** Electrical Characteristics

- 6 DC Characteristics for Digital Inputs and Outputs

- 6 CMOS Input: ADR

- 7 CMOS I<sup>2</sup>C: SDA, SCL

- 8 Electrical and Magnetic Specifications

#### 10 Detailed Description

- 10 Typical Application

- 11 I<sup>2</sup>C Interface

- 12 l<sup>2</sup>C Interface Data

- 13 I<sup>2</sup>C Modes

- 13 Bus Not Busy

- 13 Start Data Transfer

- 13 Stop Data Transfer

- 13 Data Valid

- 14 Acknowledge

- 14 Data transfer from a Master Transmitter to a Slave Receiver.

- 14 Data transfer from a Slave Transmitter to a Master Receiver.

- 15 Slave Receiver Mode (Write Mode)

- 16 Slave Transmitter Mode (Read Mode)

- 17 Automatic increment of Address Pointer

- 17 Invalid Addresses

- 17 Reading

- 17 Write

- 17 SDA, SCL Input Filters

**18 Register Description**

- 20 Package Drawings & Markings

- 20 WLCSP Package

- 22 SOIC8 Package

- 24 Ordering & Contact Information

- 25 RoHS Compliant & ams Green Statement

- 26 Copyrights & Disclaimer

- 27 Document Status

- 28 Revision Information

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Board Mount Hall Effect/Magnetic Sensors category:

Click to view products by ams manufacturer:

Other Similar products are found below :

HGPRDT005A AH277AZ4-AG1 AV-10379 AV-10448 SS41C AH1894-Z-7 ATS601LSGTN-LT-WU4-T TLE4917 50017859-003 TY-13101 TLE4976L AH49FNTR-G1 SS85CA AH277AZ4-BG1 TLE49614MXTSA1 AH3377-P-B AH211Z4-AG1 AH3360-FT4-7 SS460S-100SAMPLE 50065820-03 TLE4941PLUSCB AH374-P-A AH1806-P-A SS460P-T2 AH1913-W-7 SS413F TLE5046ICAKLRHALA1 TLE49421CHAMA2 TLE4941PLUSCXAMA1 AH1912-W-EVM AH1903-FA-EVM AH3774-W-EVM AH49FNTR-EVM MMC5633NJL AH3360-FA-EVM AH8502-FDC-EVM AH3366Q-SA-EVM AH3774-P-EVM KTH1601SU-ST3 MG910 MG910M MG911 MG610 MW921 TLE4998S3XALA1 TLE5011FUMA1 TLE5027CE6747HAMA1 TLE5109A16E2210XUMA1 TLI4966GHTSA1 TLI4906KHTSA1