# **AS7225**

# Calibrated XYZ Chromatic Smart **Lighting Director**

### **General Description**

The AS7225 Smart Lighting Director incorporates an embedded digital tri-stimulus chromatic 'calibrated for life' nano-optic sensor providing direct CIE1931 XYZ and CIE 1976 u'v' coordinate mapping. Adaptive algorithmic support enables a companion microprocessor to implement closed-loop, autonomous adjustment of variable CCT and daylight responsive LED lamps and luminaires. The AS7225 arrives pre-calibrated, and is designed for rapid integration into white-tunable and daylight responsive luminaire designs, delivering directives to the local microprocessor via an industry-standard I<sup>2</sup>C bus.

An additional on-chip I<sup>2</sup>C master provides native support for select ams sensors, such as the TSL4531 for combining in-looking CCT tunable director functions with outward-looking ambient light sensing and daylighting control. The AS7225 integrates standard-observer filters onto the silicon via nano-optic deposited interference filters which deliver high-stability over time and temperature. The LGA package includes a built in aperture to control light entering the sensor array. Integrated intelligence enables lifetime CCT calibration to within 2-4 Macadam steps.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of this device are listed below:

Figure 1: **Added Value of Using AS7225**

| Benefits                                                                                                                                  | Features                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Provides accurate external host MCU<br>supervision of variable CCT and spectrally<br>tunable lighting                                     | Integrated intelligence with XYZ tri-stimulus color<br>sensing for direct translation to CIE 1931 standard<br>observer color map                                                 |

| Uses accurate XYZ sensed data to provide a host<br>MCU, with its own PWMs, simple to use<br>directives for closed loop tuned LED lighting | Automatically directs external warm and cool white<br>PWM controlled LED strings for chromatic LED<br>luminaire tuning. Also directs dimming (combined<br>with PWM color tuning) |

| Automatic spectral and lumen maintenance<br>over temperature and time                                                                     | Supports autonomous color point and lumen output<br>adjustment resulting in automatic spectral and<br>lumen maintenance                                                          |

| Benefits                                                                                                                                          | Features                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Provides direct register based access to closed loop tuning directives                                                                            | I <sup>2</sup> C slave digital Interface                                                                                      |

| <ul> <li>Used to interface other ams sensors with native<br/>support by the AS7225 (e.g. TSL4531 for adding<br/>Daylighting operation)</li> </ul> | I <sup>2</sup> C master digital interface                                                                                     |

| Rapid luminaire integration                                                                                                                       | Simple register-based commands to control and<br>configure key light-tuning supervisory and IoT sensor<br>expansion functions |

| Complete data on lighting environment                                                                                                             | Readable registers for CIE 1931 and 1975 color-point<br>coordinates, CCT, duv and lux                                         |

| Calibrated sensing with minimal drift over time or temperature                                                                                    | Chromatic white color realized by silicon interference filters                                                                |

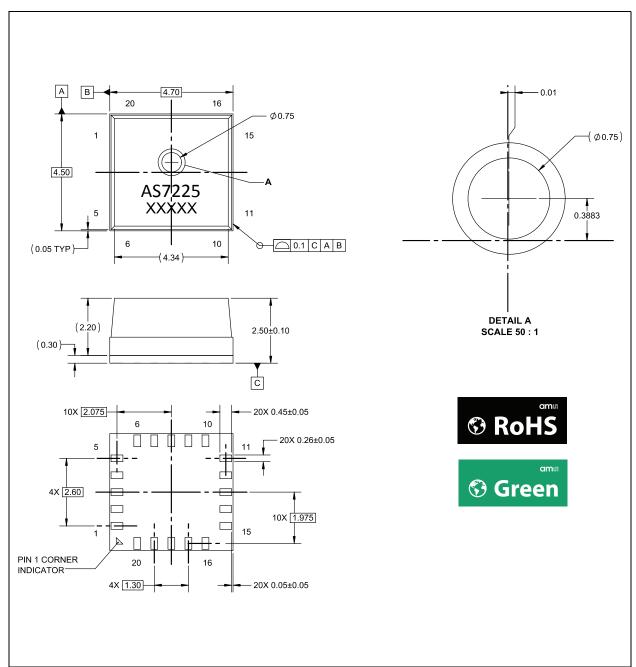

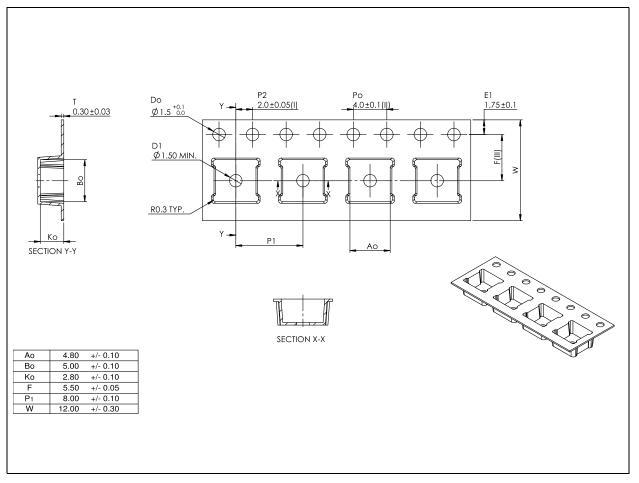

| Small package, with build in aperture                                                                                                             | • 20-pin LGA package 4.5mm x 4.7mm x 2.5mm,<br>-40°C to 85°C                                                                  |

# **Applications**

- Variable CCT chromatic tuning luminaires and systems

- Daylighting-responsive luminaires and systems

- Commercial, retail, and residential white tunable/Kelvin-changing LED lighting systems

- Networked smart lighting systems

Page 2ams DatasheetDocument Feedback[v1-00] 2016-Dec-29

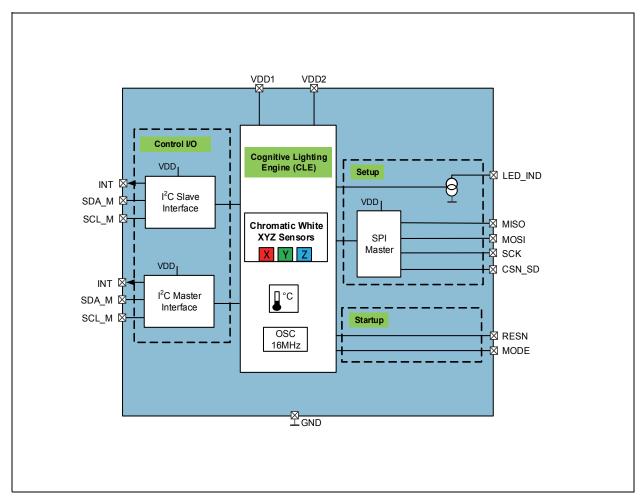

### **Block Diagram**

Figure 2: Functional Blocks of AS7225

**Block Diagram:** The AS7225 Directs real-time closed loop Chromatic White sensing and PWM tuning to an external host MCU via I<sup>2</sup>C.

ams Datasheet Page 3

[v1-00] 2016-Dec-29

Document Feedback

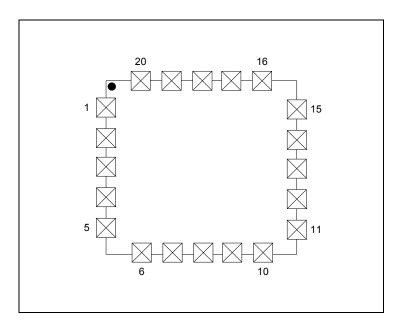

# **Pin Assignments**

Figure 3: Pin Diagram of AS7225 (Top View)

Figure 4: Pin Description of AS7225 (20 pin LGA)

| Pin Number | Pin Name | Description                                                           |

|------------|----------|-----------------------------------------------------------------------|

| 1          | NF       | Not Functional, do not connect or route to pin                        |

| 2          | RESN     | Reset pin, active low                                                 |

| 3          | SCK      | SPI serial clock                                                      |

| 4          | MOSI     | SPI MOSI                                                              |

| 5          | MISO     | SPI MISO                                                              |

| 6          | CSN_EE   | Chip select for the required external serial flash memory, active low |

| 7          | CSN_SD   | Chip select for SD Card interface, active low                         |

| 8          | NF       | Not Functional, do not connect or route to pin                        |

| 9          | SCL_M    | I <sup>2</sup> C master clock pin                                     |

| 10         | SDA_M    | I <sup>2</sup> C master data pin                                      |

| 11         | SCL_S    | I <sup>2</sup> C slave clock pin                                      |

| 12         | SDA_S    | I <sup>2</sup> C slave data pin                                       |

| 13         | INT      | INT (interrupt) is active Low                                         |

| 14         | VDD2     | VDD Voltage Supply                                                    |

Page 4ams DatasheetDocument Feedback[v1-00] 2016-Dec-29

| Pin Number | Pin Name | Description                                                                           |

|------------|----------|---------------------------------------------------------------------------------------|

| 15         | MODE     | Mode selection pin. Set to MODE=0 via $100\Omega$ resistor. Other Modes are reserved. |

| 16         | GND      | Ground                                                                                |

| 17         | VDD1     | VDD Voltage Supply                                                                    |

| 18         | LED_IND  | LED Driver output for Indicator LED, current sink                                     |

| 19         | NF       | Not Functional, do not connect or route to pin                                        |

| 20         | NF       | Not Functional, do not connect or route to pin                                        |

### **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The device is not designed for high energy UV (ultraviolet) environments, including upward looking outdoor applications, which could affect long term optical performance.

Figure 5:

Absolute Maximum Ratings

|                     | - /                                   |          |              |          | •                                                                                                                                                                                                                        |      |             |   |             |

|---------------------|---------------------------------------|----------|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|---|-------------|

| Symbol              | Parameter                             | Min      | Max          | Units    | Comments                                                                                                                                                                                                                 |      |             |   |             |

|                     |                                       | Electri  | cal Paramete | ers      |                                                                                                                                                                                                                          |      |             |   |             |

| V <sub>DD_MAX</sub> | Supply Voltage VDD                    | -0.3 5 V |              | V        | Pins VDD1 and VDD1 must be sourced from the same supply voltage                                                                                                                                                          |      |             |   |             |

| V <sub>DD_IO</sub>  | Input/Output Pin Voltage              | -0.3     | VDD + 0.3    | V        | Low Voltage pins to GND                                                                                                                                                                                                  |      |             |   |             |

| I <sub>SCR</sub>    | Input Current (latch-up immunity)     | ± 100 mA |              | mA       | JESD78D                                                                                                                                                                                                                  |      |             |   |             |

|                     |                                       | Electros | tatic Discha | rge      |                                                                                                                                                                                                                          |      |             |   |             |

| ESD <sub>HBM</sub>  | Electrostatic Discharge<br>HBM        | ±1000    |              | ±1000    |                                                                                                                                                                                                                          | V    | JS-001-2014 |   |             |

| ESD <sub>CDM</sub>  | Electrostatic Discharge<br>CDM        | ±500     |              | ±500     |                                                                                                                                                                                                                          | ±500 |             | V | JSD22-C101F |

|                     | Temperat                              | ure Rang | es and Stora | ge Condi | tions                                                                                                                                                                                                                    |      |             |   |             |

| T <sub>strg</sub>   | Storage Temperature                   | -40      | 85           | °C       |                                                                                                                                                                                                                          |      |             |   |             |

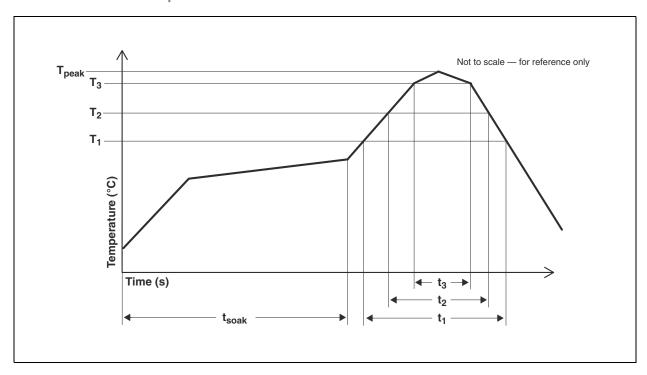

| T <sub>body</sub>   | Package Body<br>Temperature           | 260      |              | ℃        | IPC/JEDEC J-STD-020. The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices" |      |             |   |             |

| RH <sub>NC</sub>    | Relative Humidity<br>(non-condensing) | 5        | 5 85 %       |          |                                                                                                                                                                                                                          |      |             |   |             |

| MSL                 | Moisture Sensitivity Level            |          | 3            |          | Represents a 168 hour max. floor lifetime                                                                                                                                                                                |      |             |   |             |

Page 6

Document Feedback

[v1-00] 2016-Dec-29

### **Electrical Characteristics**

All limits are guaranteed with VDD = VDD1 = VDD2 = 3.3V,  $T_{AMB}$  = 25°C. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

VDD1 and VDD2 must be sourced from the same 2.7-3.6V supply source.

Figure 6: Electrical Characteristics

| Symbol                            | Parameter                                                 | Conditions           | Min      | Тур | Max      | Unit |

|-----------------------------------|-----------------------------------------------------------|----------------------|----------|-----|----------|------|

|                                   | General                                                   | Operating Condition  | S        |     |          |      |

| VDD                               | Low Voltage operating Supply                              |                      | 2.7      | 3.3 | 3.6      | V    |

| T <sub>AMB</sub>                  | Operating Temperature                                     |                      | -40      | 25  | 85       | °C   |

| I <sub>VDD</sub>                  | Operating Current                                         |                      |          |     | 5        | mA   |

|                                   | Inte                                                      | ernal RC Oscillator  |          |     |          |      |

| F <sub>OSC</sub>                  | Internal RC oscillator frequency                          |                      | 15.7     | 16  | 16.3     | MHz  |

| t <sub>JITTER</sub> (1)           | Jitter                                                    | @25°C                |          |     | 1.2      | ns   |

|                                   | Ter                                                       | mperature Sensor     |          |     |          |      |

| D <sub>TEMP</sub>                 | Absolute accuracy of the internal temperature measurement |                      | -8.5     |     | 8.5      | °C   |

|                                   |                                                           | Indicator LED        |          |     |          |      |

| I <sub>IND</sub>                  | LED Current                                               |                      | 1        |     | 8        | mA   |

| I <sub>ACC</sub>                  | Accuracy of Current                                       |                      | -30      |     | 30       | %    |

| V <sub>LED</sub>                  | Voltage range of connected LED                            | Vds of current sink  | 0.3      |     |          | V    |

|                                   | Digita                                                    | l Inputs and Outputs |          |     |          |      |

| V <sub>IH</sub>                   | CMOS Logic High Input                                     |                      | 0.7* VDD |     | VDD      | V    |

| V <sub>IL</sub>                   | CMOS Logic Low Input                                      |                      | 0        |     | 0.3* VDD | V    |

| V <sub>OH</sub>                   | CMOS Logic High Output                                    | I=1mA                |          |     | VDD-0.4  | V    |

| V <sub>OL</sub>                   | CMOS Logic Low Output                                     | I=1mA                |          |     | 0.4      | V    |

| I <sub>lh</sub> , I <sub>IL</sub> | Logic Input Current                                       | Vin=0V or VDD        | -1       |     | 1        | μΑ   |

| t <sub>RISE</sub> (1)             | Current rise time                                         | C(Pad)=30pF          |          |     | 5        | ns   |

| t <sub>FALL</sub> (1)             | Current fall time                                         | C(Pad)=30pF          |          |     | 5        | ns   |

#### Note(s):

ams Datasheet Page 7

[v1-00] 2016-Dec-29 Document Feedback

<sup>1.</sup> Guaranteed, not production tested

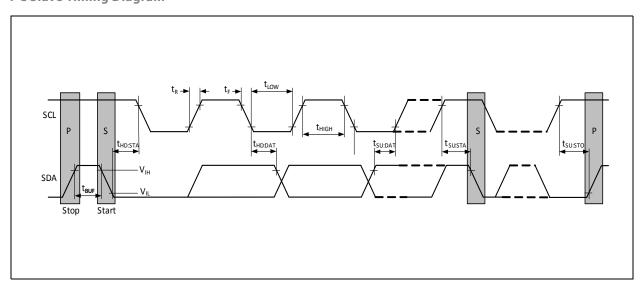

Figure 7: AS7225 I<sup>2</sup>C Slave Timing Characteristics

| Symbol              | Parameter                              | Conditions                                   | Min | Тур | Max | Unit |  |  |  |

|---------------------|----------------------------------------|----------------------------------------------|-----|-----|-----|------|--|--|--|

|                     | I <sup>2</sup> C Interface             |                                              |     |     |     |      |  |  |  |

| f <sub>SCLK</sub>   | SCL Clock Frequency                    |                                              | 0   |     | 400 | kHz  |  |  |  |

| t <sub>BUF</sub>    | Bus Free Time Between a STOP and START |                                              | 1.3 |     |     | μs   |  |  |  |

| t <sub>HD:STA</sub> | Hold Time (Repeated) START             |                                              | 0.6 |     |     | μs   |  |  |  |

| t <sub>LOW</sub>    | LOW Period of SCL Clock                |                                              | 1.3 |     |     | μs   |  |  |  |

| t <sub>HIGH</sub>   | HIGH Period of SCL Clock               |                                              | 0.6 |     |     | μs   |  |  |  |

| t <sub>SU:STA</sub> | Setup Time for a Repeated START        |                                              | 0.6 |     |     | μs   |  |  |  |

| t <sub>HD:DAT</sub> | Data Hold Time                         |                                              | 0   |     | 0.9 | μs   |  |  |  |

| t <sub>SU:DAT</sub> | Data Setup Time                        |                                              | 100 |     |     | ns   |  |  |  |

| t <sub>R</sub>      | Rise Time of Both SDA and SCL          |                                              | 20  |     | 300 | ns   |  |  |  |

| t <sub>F</sub>      | Fall Time of Both SDA and SCL          |                                              | 20  |     | 300 | ns   |  |  |  |

| t <sub>SU:STO</sub> | Setup Time for STOP Condition          |                                              | 0.6 |     |     | μs   |  |  |  |

| C <sub>B</sub>      | Capacitive Load for Each Bus Line      | CB — total capacitance of one bus line in pF |     |     | 400 | pF   |  |  |  |

| C <sub>I/O</sub>    | I/O Capacitance (SDA, SCL)             |                                              |     |     | 10  | pF   |  |  |  |

Figure 8: I<sup>2</sup>C Slave Timing Diagram

Page 8ams DatasheetDocument Feedback[v1-00] 2016-Dec-29

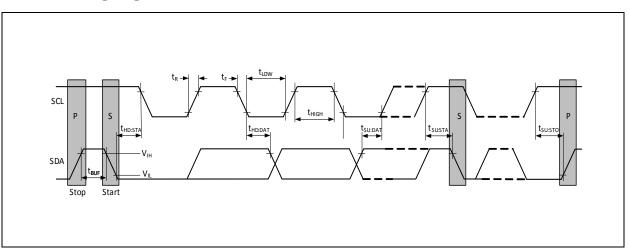

Figure 9: AS7225 I<sup>2</sup>C Master Timing Characteristics

| Symbol              | Parameter                              | Conditions                                   | Min | Тур | Max | Unit |  |  |  |

|---------------------|----------------------------------------|----------------------------------------------|-----|-----|-----|------|--|--|--|

|                     | I <sup>2</sup> C Interface             |                                              |     |     |     |      |  |  |  |

| $f_{SCLK}$          | SCL Clock Frequency                    |                                              |     | 100 | 400 | kHz  |  |  |  |

| t <sub>BUF</sub>    | Bus Free Time Between a STOP and START |                                              | 1.3 |     |     | μs   |  |  |  |

| t <sub>HD:STA</sub> | Hold Time (Repeated)<br>START          |                                              | 0.6 |     |     | μs   |  |  |  |

| t <sub>LOW</sub>    | LOW Period of SCL Clock                |                                              | 1.3 |     |     | μs   |  |  |  |

| t <sub>HIGH</sub>   | HIGH Period of SCL Clock               |                                              | 0.6 |     |     | μs   |  |  |  |

| t <sub>SU:STA</sub> | Setup Time for a Repeated<br>START     |                                              | 0.6 |     |     | μs   |  |  |  |

| t <sub>HD:DAT</sub> | Data Hold Time                         |                                              | 0   |     | 0.9 | μs   |  |  |  |

| t <sub>SU:DAT</sub> | Data Setup Time                        |                                              | 100 |     |     | ns   |  |  |  |

| t <sub>R</sub>      | Rise Time of Both SDA and SCL          |                                              | 20  |     | 300 | ns   |  |  |  |

| t <sub>F</sub>      | Fall Time of Both SDA and SCL          |                                              | 20  |     | 300 | ns   |  |  |  |

| t <sub>SU:STO</sub> | Setup Time for STOP<br>Condition       |                                              | 0.6 |     |     | μs   |  |  |  |

| C <sub>B</sub>      | Capacitive Load for Each<br>Bus Line   | CB — total capacitance of one bus line in pF |     |     | 400 | pF   |  |  |  |

| C <sub>I/O</sub>    | I/O Capacitance (SDA, SCL)             |                                              |     |     | 10  | рF   |  |  |  |

Figure 10: I<sup>2</sup>C Master Timing Diagram

ams Datasheet Page 9

[v1-00] 2016-Dec-29

Document Feedback

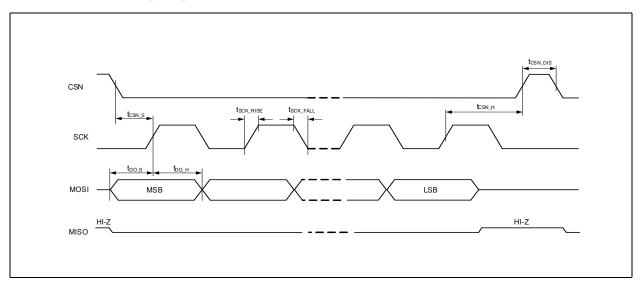

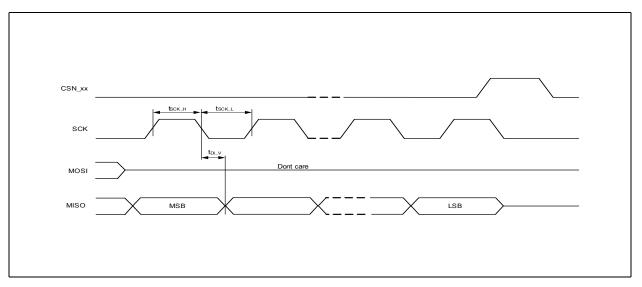

Figure 11: AS7225 SPI Timing Characteristics

| Symbol                | Parameter           | Conditions                                                        | Min | Тур | Max | Unit |  |  |

|-----------------------|---------------------|-------------------------------------------------------------------|-----|-----|-----|------|--|--|

|                       | SPI Interface       |                                                                   |     |     |     |      |  |  |

| f <sub>SCK</sub>      | Clock frequency     |                                                                   | 0   |     | 16  | MHz  |  |  |

| t <sub>SCK_H</sub>    | Clock high time     |                                                                   | 40  |     |     | ns   |  |  |

| t <sub>SCK_L</sub>    | Clock low time      |                                                                   | 40  |     |     | ns   |  |  |

| t <sub>SCK_RISE</sub> | SCK rise time       |                                                                   | 5   |     |     | ns   |  |  |

| t <sub>SCK_FALL</sub> | SCK fall time       |                                                                   | 5   |     |     | ns   |  |  |

| t <sub>CSN_S</sub>    | CSN setup time      | Time between CSN high-low transition to first SCK high transition | 50  |     |     | ns   |  |  |

| t <sub>CSN_H</sub>    | CSN hold time       | Time between last SCK falling edge and CSN low-high transition    | 100 |     |     | ns   |  |  |

| t <sub>CSN_DIS</sub>  | CSN disable time    |                                                                   | 100 |     |     | ns   |  |  |

| t <sub>DO_S</sub>     | Data-out setup time |                                                                   | 5   |     |     | ns   |  |  |

| t <sub>DO_H</sub>     | Data-out hold time  |                                                                   | 5   |     |     | ns   |  |  |

| t <sub>DI_V</sub>     | Data-in valid       |                                                                   | 10  |     |     | ns   |  |  |

Figure 12: SPI Master Write Timing Diagram

Page 10ams DatasheetDocument Feedback[v1-00] 2016-Dec-29

Figure 13: SPI Master Read Timing Diagram

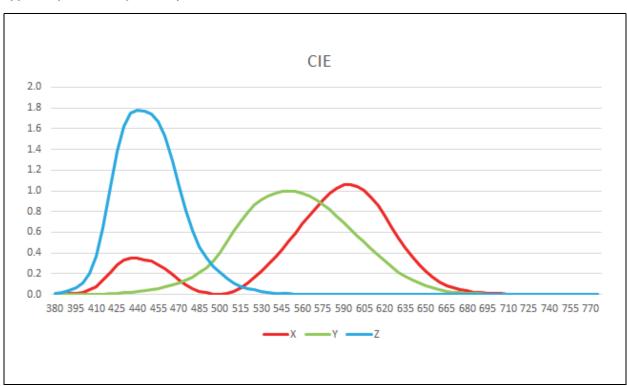

Figure 14: Typical Spectral Responsivity

ams DatasheetPage 11[v1-00] 2016-Dec-29Document Feedback

Figure 15: AS7225 Optical Characteristics

| Symbol                 | Parameter                  | Conditions                                            | Min   | Typ <sup>(1)</sup> | Max   | Unit                             |

|------------------------|----------------------------|-------------------------------------------------------|-------|--------------------|-------|----------------------------------|

| Color_m <sup>(2)</sup> | Color measurement accuracy | White Light<br>CCT = 2700K, 3500K, 4500K<br>and 5700K |       | 0.002              |       | du'v'                            |

| Z_count                | Z channel count accuracy   | White Light<br>CCT = 5700K                            | 3.375 | 4.5                | 5.625 | counts/<br>(μW/cm <sup>2</sup> ) |

#### Note(s):

- 1. Typical values at Lux  $\geq$ 50, Integration time=400.4ms, Gain=1x,  $T_{AMB}$  = 25°C.

- 2. Calibration and measurements are made using diffused light

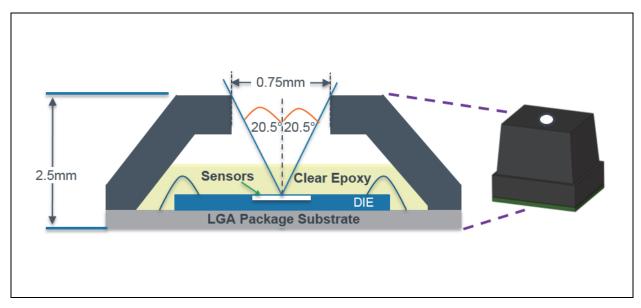

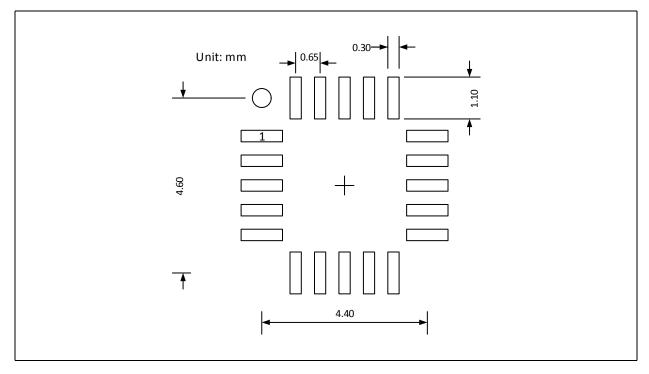

Figure 16: AS7225 LGA Package Field of View

Page 12ams DatasheetDocument Feedback[v1-00] 2016-Dec-29

## **Detailed Description**

#### **AS7225 XYZ Chromatic White Color Director**

The AS7225 serves as a White Color Director for a companion host MCU. This provides high level calculated white color tuning control loop information for external LED channel PWMs via I<sup>2</sup>C registers. Director operation also provides selectable dimming information for either PWM based or independent luminaire dimming designs.

The integrated tri-stimulus sensing element is designed to meet the XYZ standard observer response compliant with the CIE 1931 standard. The device uses a 16-bit integrating analog-to-digital converter which integrates current from photodiodes. To ensure integrity of the data, upon completion of an integration cycle, results are transferred to double-buffered registers.

XYZ color point response is accomplished via standard observer interference filters which are extremely stable over time and temperature. To ensure accuracy, the AS7225 LGA package contains an internal aperture that limits the sensor field of view (PFOV) of  $\pm$  20.5°, as shown in the figure above. External optics can be used as needed to expand or reduce this built in PFOV.

For Daylight operation the AS7225 can be used two ways. As a standalone device pointing out of the luminaire, or if pointing inward for white color, it can support daylighting operation by using an I<sup>2</sup>C master connected **ams** TSL4531 for ambient light sensing. In either case the AS7225 is the Daylighting engine and directs the external MCU.

Overall AS7225 timing generation uses an on chip 16MHz temperature compensated oscillator for master clock timing.

#### **MODE Pin**

The AS7225 MODE pin must be connected to ground (GND) via a  $100\Omega$  resistor (1%) to set the AS7225 mode of operation. All other MODEs (using other resistor values) are reserved.

#### **Indicator LED**

An LED, connected to pin LED\_IND, is used to indicate programming progress of the device. During programming of the AS7225 via an external SD card, the indicator LED starts blinking operation. When programming is finished the indicator LED stays on. The LED\_IND pin is set for 1mA LED operation by the AS7225 factory firmware, and is not under user control.

Refer to the separate **ams** document for a complete description of AS7225 Firmware Update Methodology.

ams Datasheet Page 13

[v1-00] 2016-Dec-29 Document Feedback

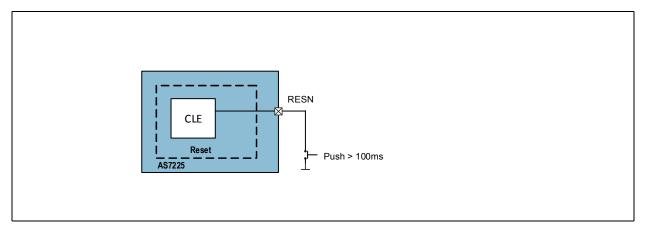

#### Reset

Pulling down the RESN pin for longer than 100ms resets the AS7225.

Figure 17: Reset Circuit

### **Interrupt Operation**

Register bits DATA\_RDY and PWM\_RDY and the INT pin are used to monitor sensor integration activity complete and whether PWM target information is available for the MCU. If the interrupt register bit for either are enabled (RDY\_INT = 1, PWM\_INT = 1) then when either of these activities become active, indicating available data, the INT pin is pulled low in addition to setting the ready register bit(s). The INT Line is released when the appropriate control register (CONV\_Control and/or DIR\_Control) is read. DATA\_RDY is cleared to 0 when any of the sensor registers X, Y, Z are read. For multi-byte sensor data (2 or 4 bytes), after the 1st byte is read the remaining get shadow buffer protected in case an integration cycle completes just after the 1st byte is read.

#### I<sup>2</sup>C Slave Interface

Interface and control can be accomplished through an I<sup>2</sup>C compatible slave interface to a set of registers that access device control functions and output data. These control and output registers on the AS7225 are, in reality, implemented as *virtual* registers in software. The actual I<sup>2</sup>C slave hardware registers number only three and are described in the table below. The steps necessary to access the virtual registers defined in the pages that follow are explained in pseudocode for external I<sup>2</sup>C master writes and reads below.

Page 14

Document Feedback [v1-00] 2016-Dec-29

#### I<sup>2</sup>C Feature List

• Fast mode (400kHz) and standard mode (100kHz) support.

• 7+1-bit addressing mode.

Write format: Byte.Read format: Byte.

Figure 18: I<sup>2</sup>C Slave Device Address and Physical Registers

| Entity               | Description                                                        | Note                                                                                                                                                                                                                                             |

|----------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Slave Address | 8-bit Slave Address                                                | Byte = 1001001x (device address = 49 hex)<br>x= 1 for Master Read (byte = 93 hex)<br>x= 0 for Master Write (byte = 92 hex)                                                                                                                       |

| STATUS Register      | I <sup>2</sup> C slave interface<br>STATUS register.<br>Read-only. | Register Address = 0x00 Bit 1: TX_VALID 0 -> New data may be written to WRITE register 1 -> WRITE register occupied. Do NOT write. Bit 0: RX_VALID 0 -> No data is ready to be read in READ register. 1 -> Data byte available in READ register. |

| WRITE Register       | I <sup>2</sup> C slave interface<br>WRITE register.<br>Write-only. | Register Address = 0x01<br>8-Bits of data written by the I <sup>2</sup> C Master intended<br>for receipt by the I <sup>2</sup> C slave. Used for both <i>virtual</i><br>register addresses and write data.                                       |

| READ Register        | I <sup>2</sup> C slave interface<br>READ register.<br>Read-only.   | Register Address = 0x02<br>8-Bits of data to be read by the I <sup>2</sup> C Master.                                                                                                                                                             |

# I<sup>2</sup>C Virtual Register Write Access

I<sup>2</sup>C Virtual Resister Byte Write, detailed below, shows the pseudocode necessary to write virtual registers on the AS7225. Note that, because the actual registers of interest are realized as virtual registers, a means of indicating whether there is a pending read or write operation of a given virtual register is needed. To convey this information, the most significant bit of the virtual register address is used as a marker. If it is 1, then a write is pending, otherwise the slave is expecting a virtual read operation. The pseudocode illustrates the proper technique for polling of the I<sup>2</sup>C slave status register to ensure the slave is ready for each transaction.

ams Datasheet Page 15

[v1-00] 2016-Dec-29 Document Feedback

#### I<sup>2</sup>C Virtual Register Byte Write

#### Pseudocode

Poll I<sup>2</sup>C slave STATUS register;

If TX\_VALID bit is 0, a write can be performed on the interface;

Send a virtual register address and set the MSB of the register address to 1 to indicate the pending write; Poll I<sup>2</sup>C slave STATUS register;

If TX\_VALID bit is 0, the virtual register address for the write has been received and the data may now be written; Write the data.

#### Sample Code:

```

#define I2C_AS72XX_SLAVE_STATUS_REG

0x00

#define I2C_AS72XX_SLAVE_WRITE_REG

0x01

#define I2C_AS72XX_SLAVE_READ_REG

0x02

#define I2C_AS72XX_SLAVE_TX_VALID

0x02

#define I2C_AS72XX_SLAVE_RX_VALID

0x01

void i2cm_AS72xx_write(uint8_t virtualReg, uint8_t d)

volatile uint8_tstatus;

while (1)

// Read slave I2C status to see if the write buffer is ready.

status = i2cm_read(I2C_AS72XX_SLAVE_STATUS_REG);

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

// No inbound TX pending at slave. Okay to write now.

break;

// Send the virtual register address (setting bit 7 to indicate a pending write).

i2cm_write(I2C_AS72XX_SLAVE_WRITE_REG, (virtualReg | 0x80));

while (1)

// Read the slave I2C status to see if the write buffer is ready.

status = i2cm_read(I2C_AS72XX_SLAVE_STATUS_REG);

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

// No inbound TX pending at slave. Okay to write data now.

break;

// Send the data to complete the operation.

i2cm_write(I2C_AS72XX_SLAVE_WRITE_REG, d);

```

Page 16

Document Feedback

[v1-00] 2016-Dec-29

# I<sup>2</sup>C Virtual Register Read Access

I<sup>2</sup>C Virtual Register Byte Read, detailed below, shows the pseudocode necessary to read virtual registers on the AS7225. Note that in this case, reading a virtual register, the register address is not modified.

#### I<sup>2</sup>C Virtual Register Byte Read

#### Pseudocode

```

Poll I<sup>2</sup>C slave STATUS register;

If TX_VALID bit is 0, the virtual register address for the read may be written;

Send a virtual register address;

Poll I<sup>2</sup>C slave STATUS register;

If RX_VALID bit is 1, the read data is ready;

Read the data.

Sample Code:

uint8_t i2cm_AS72xx_read(uint8_t virtualReg)

volatile uint8_t status, d;

while (1)

// Read slave I2C status to see if the read buffer is ready.

status = i2cm_read(I2C_AS72XX_SLAVE_STATUS_REG);

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

// No inbound TX pending at slave. Okay to write now.

break;

// Send the virtual register address (setting bit 7 to indicate a pending write).

i2cm_write(I2C_AS72XX_SLAVE_WRITE_REG, virtualReg);

while (1)

// Read the slave I2C status to see if our read data is available.

status = i2cm\_read(I2C\_AS72XX\_SLAVE\_STATUS\_REG);

if ((status & I2C_AS72XX_SLAVE_RX_VALID) != 0)

// Read data is ready.

break;

// Read the data to complete the operation.

d = i2cm_read(I2C_AS72XX_SLAVE_READ_REG);

return d;s

}

```

The details of the i2cm read() and i2cm write() functions in previous Figures are dependent upon the nature and implementation of the external I<sup>2</sup>C master device.

ams Datasheet Page 17 **Document Feedback**

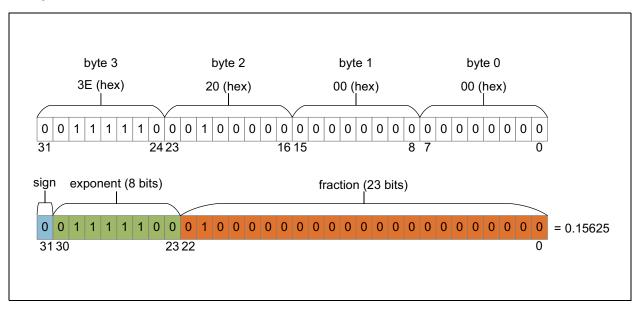

#### 4-Byte Floating-Point (FP) Registers

In addition to single and two byte, several 4 byte registers (hex) are shown in the tables starting below. Here is an example of how the registers are used to represent floating point data (based on the IEEE 754 standard):

Figure 19: Example of the IEEE 754 Standard

The floating point (FP) value assumed by 32 bit binary32 data with a biased exponent e (the 8 bit unsigned integer) and a 23 bit fraction is (for the above example):

(EQ1) FPvalue =

$$(-1)^{\text{sign}} \left(1 + \sum_{i=1}^{23} b_{23-i} 2^{-i}\right) \times 2^{(e-127)}$$

(EQ2) FPvalue =

$$(-1)^0 \left(1 + \sum_{i=1}^{23} b_{23-i} 2^{-i}\right) \times 2^{(124-127)}$$

(EQ3) FPvalue =

$$1 \times (1 + 2^{-2}) \times 2^{(-3)} = 0.15625$$

Page 18

Document Feedback

[v1-00] 2016-Dec-29

# I<sup>2</sup>C Virtual Register Set

The Figure below provides a summary of the AS7225 I<sup>2</sup>C register set. Figures after that provide additional register details. All register data is hex, and all multi-byte entities are Big Endian (most significant byte is situated at the lowest register address).

Multiple byte registers (2 byte integer or 4 byte floating point) must be read in the order of ascending register addresses (low to high). And if capable of being written to, must also be written in the order of ascending register addresses.

Figure 20: I<sup>2</sup>C Virtual Register Overview

| Addr | Name                | <d7></d7> | <d6></d6> | <d5></d5>  | <d4></d4>    | <d3></d3> | <d2></d2> | <d1></d1> | <d0></d0>   |

|------|---------------------|-----------|-----------|------------|--------------|-----------|-----------|-----------|-------------|

|      |                     |           | Dev       | vice Versi | on Registers |           |           |           |             |

| 0x00 | HW_V_H              |           |           |            |              |           |           |           |             |

| 0x01 | HW_V_L              |           |           |            |              |           |           |           |             |

| 0x02 | FW_V_H              |           |           |            |              |           |           |           |             |

| 0x03 | FW_V_L              |           |           |            |              |           |           |           |             |

|      |                     | !         | General S | Setup and  | Control Reg  | isters    | !         | -         |             |

| 0x04 | CONV_Control        | OVFL      | RDY_INT   | C          | SAIN         | RS        | VD        | DATA_RDY  | RST         |

| 0x05 | INTEG_T             |           |           |            |              |           |           |           |             |

| 0x06 | Device_Temp         |           |           |            |              |           |           |           |             |

| 0x08 | LED_String_<br>Init |           |           | RSVD       |              |           | SLH       | LEARN     | FRST        |

|      |                     | 1         | Direc     | tor Opera  | tion Registe | rs        | l         | 1         |             |

| 0x64 | DIR_Control         |           | NUM_CHAN  |            | PWM_INT      | CT_EN     | DL_EN     | START     | PWM_<br>RDY |

| 0x65 | DIR_Setup           |           | RS        | VD         |              | PWM2      | PWM1      | CT_M      | ODE         |

| 0x50 | DIR_CH_1_L          |           |           |            |              |           |           |           |             |

| 0x51 | DIR_CH_1_H          |           |           |            |              |           |           |           |             |

| 0x52 | DIR_CH_2_L          |           |           |            |              |           |           |           |             |

| 0x53 | DIR_CH_2_H          |           |           |            |              |           |           |           |             |

| 0x60 | DIR_CCTT_L          |           |           |            |              |           |           |           |             |

| 0x61 | DIR_CCTT_H          |           |           |            |              |           |           |           |             |

| 0x62 | DIR_LUXT_L          |           |           |            |              |           |           |           |             |

| 0x63 | DIR_LUXT_H          |           |           |            |              |           |           |           |             |

ams Datasheet Page 19 **Document Feedback**

| 0x66          | DIR_LUX_<br>MAX_L |          |          |               |       |  |  |

|---------------|-------------------|----------|----------|---------------|-------|--|--|

| 0x67          | DIR_LUX_<br>MAX_H |          |          |               |       |  |  |

|               |                   |          |          |               |       |  |  |

| 0x44:<br>0x47 | X_Scale           |          |          |               |       |  |  |

| 0x48:<br>0x4B | Y_Scale           |          |          |               |       |  |  |

| 0x4C:<br>0x4F | Z_Scale           |          |          |               |       |  |  |

| 0x70:<br>0x73 | X_D_Scale         |          |          |               |       |  |  |

| 0x74:<br>0x77 | Y_D_Scale         |          |          |               |       |  |  |

| 0x78:<br>0x7B | Z_D_Scale         |          |          |               |       |  |  |

|               |                   | Calibrat | ed Senso | r Result Regi | sters |  |  |

| 0x14:<br>0x17 | Cal_X             |          |          |               |       |  |  |

| 0x18:<br>0x1B | Cal_Y             |          |          |               |       |  |  |

| 0x1C:<br>0x1F | Cal_Z             |          |          |               |       |  |  |

| 0x20:<br>0x23 | Cal_x_1931        |          |          |               |       |  |  |

| 0x24:<br>0x27 | Cal_y_1931        |          |          |               |       |  |  |

| 0x28:<br>0x2B | Cal_u_pri         |          |          |               |       |  |  |

| 0x2C:<br>0x2F | Cal_v_pri         |          |          |               |       |  |  |

| 0x30:<br>0x33 | Cal_u             |          |          |               |       |  |  |

| 0x34:<br>0x37 | Cal_v             |          |          |               |       |  |  |

| 0x38:<br>0x3B | Cal_DUV           |          |          |               |       |  |  |

| 0x3C          | Cal_LUX_L         |          |          |               |       |  |  |

Page 20 Document Feedback

| 0x3D | Cal_LUX_H |  |  |  |  |

|------|-----------|--|--|--|--|

| 0x3E | Cal_CCT_L |  |  |  |  |

| 0x3F | Cal_CCT_H |  |  |  |  |

# **Hardware Version Registers**

These byte registers are used together as HW\_V\_H: HW\_V\_L

Figure 21: Hardware Version Registers

|     | Addr: 0x00  |          |        | HW_V_H                  |

|-----|-------------|----------|--------|-------------------------|

| Bit | Bit Name    | Default  | Access | Bit Description         |

| 7:0 | Device Type | 01000000 | R      | Device type number      |

|     | Addr: 0x01  |          |        | HW_V_L                  |

| Bit | Bit Name    | Default  | Access | Bit Description         |

| 7:0 | HW Version  | 00011001 | R      | Hardware version number |

# **Firmware Version Registers**

These byte registers are used together as FW\_V\_H: FW\_V\_L

Figure 22: Firmware Version Registers

|     | Addr: 0x02    |         | FW_V_H |                     |  |

|-----|---------------|---------|--------|---------------------|--|

| Bit | Bit Name      | Default | Access | Bit Description     |  |

| 7:0 | Major Version | -       | R      | Major version       |  |

| 3:0 | Minor Version | -       | R      | Minor version [5:2] |  |

|     | Addr: 0x03    |         | FW_V_L |                     |  |  |  |

|-----|---------------|---------|--------|---------------------|--|--|--|

| Bit | Bit Name      | Default | Access | Bit Description     |  |  |  |

| 7:6 | Minor Version | -       | R      | Minor version [0:1] |  |  |  |

| 5:0 | Sub Version   | -       | R      | Sub version         |  |  |  |

ams Datasheet Page 21

[v1-00] 2016-Dec-29 Document Feedback

Figure 23: CONV\_Control Register

| Ad  | Addr: 0x04/0x84<br>(R/W) |         |        | CONV_Control                                                                                                                                                                        |  |  |

|-----|--------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name                 | Default | Access | Bit Description                                                                                                                                                                     |  |  |

| 7   | OVFL                     | 0       | R      | 1 = At least one of the sensor channels has saturated (overflow). Solution is to reduce Gain or Integration time. Cleared (=0) after read if set. Cleared (=0) after device reset.  |  |  |

| 6   | RDY_INT                  | 0       | R/W    | 1 = Interrupt pin will be driven low when DATA_RDY bit is set. 0 = DATA_RDY bit does not set interrupt.                                                                             |  |  |

| 5:4 | GAIN                     | 00      | R/W    | Sensor Channel Gain Setting (all sensors, Read/Write 00=1x Gain; 01=3.7x; 10=16x; 11=64x                                                                                            |  |  |

| 3:2 | RSVD                     | 00      |        | Reserved, do not use                                                                                                                                                                |  |  |

| 1   | DATA_RDY                 | 0       | R      | 1= Conversion Data Ready to read, sets INT active if interrupt is enabled. Can be polled independent of INT usage. Cleared (=0) after read if set. Cleared (=0) after device reset. |  |  |

| 0   | RST                      | 0       | R/W    | Soft Reset, set to 1 for soft reset. Goes to 0 when complete.                                                                                                                       |  |  |

Figure 24: INTEG\_T Register

| Ad  | ddr: 0x05/0x85<br>(R/W) |         |        | INTEG_T                                                                   |

|-----|-------------------------|---------|--------|---------------------------------------------------------------------------|

| Bit | Bit Name                | Default | Access | Bit Description                                                           |

| 7:0 | INTEG_T                 | -       | R/W    | Sensor Integration time = <value>*2.8ms (valid value range 1-255)</value> |

Figure 25:

Device\_Temp Register

|     | Addr: 0x06  |         |        | Device_Temp                                                               |  |

|-----|-------------|---------|--------|---------------------------------------------------------------------------|--|

| Bit | Bit Name    | Default | Access | Bit Description                                                           |  |

| 7:0 | Device_Temp | -       | R      | Device internal temperature (1 byte). Byte is a hex integer value, in °C. |  |

Page 22ams DatasheetDocument Feedback[v1-00] 2016-Dec-29

### **LED String Initialization Register**

LED string initialization must be performed at least once, and is initiated by the AS7225 if the SLH bit=0. While in LEARN operation LUX and CCT targets from the host MCU are ignored. Once complete Director based tuning, with MCU set LUX and CCT targets, can begin. String Learn History is stored in persistent memory, so if a FRST is performed a LEARN operation will be initiated. After SLH=1, the MCU can initiate a LEARN by setting LEARN=1.

Figure 26: LED String Initialization Register

| Ad  | ddr: 0x08/0x88<br>(R/W) | LED_String_Init |        |                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-----|-------------------------|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name                | Default         | Access | Bit Description                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 7:3 | RSVD                    | 00000           |        | Reserved, do not use                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 2   | SLH                     | 0               | R      | String Learn History. If set to 1, a prior LEARN operation has been performed. SLH value is stored in persistent memory but will be cleared if a FRST operation is performed.                                                                                                                                                                                            |  |  |

| 1   | LEARN                   | 0               | R/W    | <ul> <li>If=1 Directs the MCU through an LED String Learn operation:</li> <li>Learns Warm and Cool LED string numbers (string 1 or 2)</li> <li>Learns Warm and Cool LED string CCT values</li> <li>Learns max LUX</li> <li>LEARN is set by the AS7225 automatically if SLH=0.</li> <li>After SLH=1, the MCU can set it at any time to initiate another Learn.</li> </ul> |  |  |

| 0   | FRST                    | 0               | R/W    | Factory Reset. Setting to 1 clears persistent memory data and then performs a soft reset. Goes to 0 when complete.                                                                                                                                                                                                                                                       |  |  |

ams Datasheet Page 23

[v1-00] 2016-Dec-29 Document Feedback

Figure 27:

DIR\_Control Register

| Ad  | ddr: 0x64/0xE4<br>(R/W)  | DIR_Control    |                |                                                                                                                                                                                                      |  |

|-----|--------------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit | Bit Name                 | Default        | Access         | Bit Description                                                                                                                                                                                      |  |

|     | All bits except bit 0 ar | e set (or read | l) by the exte | rnal MCU. Bit 0 is read only by the external MCU                                                                                                                                                     |  |

| 7:5 | NUM_CHAN                 | 010            | R/W            | 010 = 2 channels (PWM1-PWM2)<br>001 = 1 channel (PWM1 only, which is used for<br>Daylighting if no TSL4531 is attached. Daylighting bit<br>must be set to 1.)<br>(all other 7:5 values are reserved) |  |

| 4   | PWM_INT                  | 0              | R/W            | When 1 = INT pin will be driven low when PWM_RDY is set 0 = INT pin will not be driven low when PWM_RDY is set                                                                                       |  |

| 3   | CT_EN                    | 1              | R/W            | 1 = overall Color Tuning function enabled<br>0 = disabled                                                                                                                                            |  |

| 2   | DL_EN                    | 1              | R/W            | 1 = Daylighting function enabled<br>0 = disabled                                                                                                                                                     |  |

| 1   | START                    | 0              | R/W            | 1=host MCU has completed last directive and is ready<br>for AS7225 conversion start.<br>Cleared by AS7225 automatically after being set, and<br>at device reset.                                     |  |

| 0   | PWM_RDY                  | 0              | R/W            | 1=New PWM target value directives are ready for the MCU. To return to 0 it must be set to 0 by the host MCU.                                                                                         |  |

Page 24ams DatasheetDocument Feedback[v1-00] 2016-Dec-29

Figure 28:

**DIR\_Setup Register**

| A   | Addr: 0x65/0xE5<br>(R/W) |                | DIR_Setup      |                                                                           |  |  |  |

|-----|--------------------------|----------------|----------------|---------------------------------------------------------------------------|--|--|--|

| Bit | Bit Name                 | Default        | Access         | Bit Description                                                           |  |  |  |

|     | All I                    | oits except bi | ts 7:4 are set | (or read) by the external MCU                                             |  |  |  |

| 7:4 | RSVD                     | 0000           | -              | Reserved, do not use                                                      |  |  |  |

| 3   | PWM2                     | 1              | R/W            | Set =1 for color tuning with PWM2<br>Set =0 for no color tuning with PWM2 |  |  |  |

| 2   | PWM1                     | 1              | R/W            | Set =1 for color tuning with PWM1 Set =0 for no color tuning with PWM1    |  |  |  |

| 1:0 | CT_MODE                  | 00             | R/W            | 00 = Set to CCT Tuning mode<br>(all other 1:0 settings are reserved)      |  |  |  |

# Director Channel\_1 Result Registers

These byte registers are used together as DIR\_CH\_1\_H: DIR\_CH\_1\_L

#### In Color Tuning Operation:

The registers create a 16 bit integer value from 0 to 65535 representing a PWM (Color + Dimming) tuning percentage between 0.00 and 100.00%.

Example: 0001101001001111 = 1A4F= 6735 = 10.28%

#### In Daylighting Operation (single PWM and no TSL4531):

The registers create a 16 bit integer value from 0 to 65535 representing a PWM Lux tuning percentage between 0.00 and 100.00%.

Figure 29:

Director Channel\_1 Result Registers

| P          | Addr: 0x50             |          | DIR_CH_1_L |                             |  |  |  |

|------------|------------------------|----------|------------|-----------------------------|--|--|--|

| Bit        | Bit Name               | Default  | Access     | Bit Description             |  |  |  |

| 7:0        | DIR_CH_1_L             | 00000000 | R          | Channel 1 low byte          |  |  |  |

| Addr: 0x51 |                        |          | DIR_CH_1_H |                             |  |  |  |

| A          | Addr: 0x51             |          |            | DIR_CH_1_H                  |  |  |  |

| Bit        | Addr: 0x51<br>Bit Name | Default  | Access     | DIR_CH_1_H  Bit Description |  |  |  |

ams Datasheet Page 25

[v1-00] 2016-Dec-29

Document Feedback

### Director Channel\_2 Result Registers

These byte registers are used together as DIR\_CH\_2\_H: DIR\_CH\_2\_L

The registers create a 16 bit integer value from 0 to 65535 representing a PWM (Color + Dimming) tuning percentage between 0.00 and 100.00%.

Example: 0001101001001111 = 1A4F= 6735 = 10.28%

Figure 30: Director Channel\_2 Result Registers

| A   | Addr: 0x52 |            |        | DIR_CH_2_L          |

|-----|------------|------------|--------|---------------------|

| Bit | Bit Name   | Default    | Access | Bit Description     |

| 7:0 | DIR_CH_1_L | 00000000   | R      | Channel 2 low byte  |

| A   | Addr: 0x53 | DIR_CH_2_H |        |                     |

| Bit | Bit Name   | Default    | Access | Bit Description     |

| 7:0 | DIR_CH_1_H | 00000000   | R      | Channel 2 high byte |

### **Director Target for CCT Registers**

These byte registers are used together as DIR\_CCTT\_H: DIR\_CCTT\_L

They create a 16 bit integer value for CCT target (Kelvin). Example: 0000101110111000 = 3000 °K

Figure 31:

Director Target for CCT Registers

| Add | : 0x60/0xE0<br>(R/W)   |          |        | DIR_CCTT_L                         |

|-----|------------------------|----------|--------|------------------------------------|

| Bit | Bit Name               | Default  | Access | Bit Description                    |

| 7:0 | DIR_CCTT_L             | 00000000 | R/W    | Director target for CCT, low byte  |

| Add | lr: 0x61/0xE1<br>(R/W) |          |        | DIR_CCTT_H                         |

| Bit | Bit Name               | Default  | Access | Bit Description                    |

| 7:0 | DIR_CCTT_H             | 00000000 | R/W    | Director target for CCT, high byte |

### **Director Target for LUX Registers**

These byte registers are used together as DIR\_LUXT\_H: DIR\_LUXT\_L

Page 26

Document Feedback

[v1-00] 2016-Dec-29

They create a 16 bit integer value for LUX target. Example: 00000011111101000 = 1000 LUX

Note that if LUXT is ever set higher than that set in the LUX MAX registers, it will be reduced to LUX MAX by the AS7225.

Figure 32: Director Target for LUX Registers

| Ado | lr: 0x62/0xE2<br>(R/W) | DIR_LUXT_L |        |                                    |  |

|-----|------------------------|------------|--------|------------------------------------|--|

| Bit | Bit Name               | Default    | Access | Bit Description                    |  |

| 7:0 | DIR_LUXT_L             | 00000000   | R/W    | Director target for LUX, low byte  |  |

| Add | lr: 0x63/0xE3<br>(R/W) |            |        | DIR_LUXT_H                         |  |

| Bit | Bit Name               | Default    | Access | Bit Description                    |  |

| 7:0 | DIR_LUXT_H             | 00000000   | R/W    | Director target for LUX, high byte |  |

ams Datasheet Page 27

[v1-00] 2016-Dec-29 Document Feedback

### **Director LUX Maximum Registers**

These byte registers are used together as DIR\_LUX\_MAX\_H: DIR\_LUX\_MAX\_L

They create a 16 bit integer value for maximum allowed LUX as set by the MCU.

Example: 0000001111101000 = 1000 LUX MAX

Note that the LUXT registers are ever set higher than that set in the LUX MAX registers, they will be reduced to LUX MAX by the AS7225. And if both DIR\_LUX\_MAX\_H and DIR\_LUX\_MAX\_L are set to zero, the LUX MAX function is disabled.

Figure 33: Director LUX Maximum Registers

| Add                   | dr: 0x66/0xE6<br>(R/W) |          |        | DIR_LUX_MAX_L                               |

|-----------------------|------------------------|----------|--------|---------------------------------------------|

| Bit                   | Bit Name               | Default  | Access | Bit Description                             |

| 7:0                   | DIR_LUX_MAX_L          | 00000000 | R/W    | Director setting for LUX maximum, low byte  |

| Addr: 0x67/0xE7 (R/W) |                        |          |        | DIR_LUX_MAX_H                               |

| Bit                   | Bit Name               | Default  | Access | Bit Description                             |

| 7:0                   | DIR_LUX_MAX_H          | 00000000 | R/W    | Director setting for LUX maximum, high byte |

Page 28

Document Feedback

[v1-00] 2016-Dec-29

# **XYZ Scale Registers**

These 4 byte floating point registers can be used as needed by the MCU to individually scale the Cal\_X, Cal\_Y and Cal\_Z data registers.

Figure 34: XYZ Scale Registers

|                                         | Addr:<br>44:0x47 (R)<br>C4:0xC7 (W) |         |        | X_Scale                         |

|-----------------------------------------|-------------------------------------|---------|--------|---------------------------------|

| Bit                                     | Bit Name                            | Default | Access | Bit Description                 |

| 31:0                                    | X_Scale                             | 1.0     | R/W    | X Scale (4 byte floating point) |

|                                         | Addr:<br>48:0x4B (R)<br>C8:0xCB (W) |         |        | Y_Scale                         |

| Bit                                     | Bit Name                            | Default | Access | Bit Description                 |

| 31:0                                    | Y_Scale                             | 1.0     | R/W    | Y Scale (4 byte floating point) |

| Addr:<br>0x4C:0x4F (R)<br>0xCC:0xCF (W) |                                     |         |        | Z_Scale                         |

| Bit                                     | Bit Name                            | Default | Access | Bit Description                 |

| 31:0                                    | Z_Scale                             | 1.0     | R/W    | Z Scale (4 byte floating point) |

ams Datasheet Page 29

[v1-00] 2016-Dec-29 Document Feedback

# **XYZ Diffuser Scale Registers**

These 4 byte floating point registers can be used as needed by the MCU to individually scale for any Diffuser being used in the AS7225 application. They also scale the Cal\_X, Cal\_Y and Cal\_Z data registers.

Figure 35: XYZ Diffuser Scale Registers

|                                         | Addr:<br>70:0x73 (R)<br>F0:0xF3 (W)     |           |           | X_D_Scale                                |  |  |

|-----------------------------------------|-----------------------------------------|-----------|-----------|------------------------------------------|--|--|

| Bit                                     | Bit Name                                | Default   | Access    | Bit Description                          |  |  |

| 31:0                                    | X_D_Scale                               | 1.0       | R/W       | X Diffuser Scale (4 byte floating point) |  |  |

|                                         | Addr:<br>0x74:0x77 (R)<br>0xF4:0xF7 (W) |           | Y_D_Scale |                                          |  |  |

| Bit                                     | Bit Name                                | Default   | Access    | Bit Description                          |  |  |

| 31:0                                    | Y_D_Scale                               | 1.0       | R/W       | Y Diffuser Scale (4 byte floating point) |  |  |

| Addr:<br>0x78:0x7B (R)<br>0xF8:0xFB (W) |                                         | Z_D_Scale |           |                                          |  |  |

| Bit                                     | Bit Name                                | Default   | Access    | Bit Description                          |  |  |

| 31:0                                    | Z_D_Scale                               | 1.0       | R/W       | Z Diffuser Scale (4 byte floating point) |  |  |

Figure 36: Calibrated XYZ Result Registers

| Add             | dr: 0x14:0x17   |         |        | Cal_X                                     |

|-----------------|-----------------|---------|--------|-------------------------------------------|

| Bit             | Bit Name        | Default | Access | Bit Description                           |

| 31:0            | Cal_X           | -       | R      | Calibrated X data (4 byte floating point) |

| Addr: 0x18:0x1B |                 |         |        | Cal_Y                                     |

| Bit             | Bit Name        | Default | Access | Bit Description                           |

| 31:0            | Cal_Y           | -       | R      | Calibrate Y data (4 byte floating point)  |

| Add             | Addr: 0x1C:0x1F |         |        | Cal_Z                                     |

| Bit             | Bit Name        | Default | Access | Bit Description                           |

| 31:0            | Cal_Z           | -       | R      | Calibrated Z data (4 byte floating point) |

Page 30ams DatasheetDocument Feedback[v1-00] 2016-Dec-29

Figure 37: Calibrated CIE 1931 x and y Result Registers

| Add  | dr: 0x20:0x23 |         |        | Cal_x                                     |

|------|---------------|---------|--------|-------------------------------------------|

| Bit  | Bit Name      | Default | Access | Bit Description                           |

| 31:0 | Cal_x         | -       | R      | Calibrated x data (4 byte floating point) |

| Add  | dr: 0x24:0x27 | Cal_y   |        |                                           |

| Bit  | Bit Name      | Default | Access | Bit Description                           |

| 31:0 | Cal_y         | -       | R      | Calibrate y data (4 byte floating point)  |

Figure 38: Calibrated CIE 1976 u', v', u and v Result Registers

| Add  | lr: 0x28:0x2B |         |        | Cal_u_pri                                  |

|------|---------------|---------|--------|--------------------------------------------|

| Bit  | Bit Name      | Default | Access | Bit Description                            |

| 31:0 | Cal_u_pri     | -       | R      | Calibrated u' data (4 byte floating point) |

| Add  | lr: 0x2C:0x2F |         |        | Cal_v_pri                                  |

| Bit  | Bit Name      | Default | Access | Bit Description                            |

| 31:0 | Cal_v_pri     | -       | R      | Calibrate v' data (4 byte floating point)  |

| Add  | dr: 0x30:0x33 |         |        | Cal_u                                      |

| Bit  | Bit Name      | Default | Access | Bit Description                            |

| 31:0 | Cal_u         | -       | R      | Calibrated u data (4 byte floating point)  |

| Add  | dr: 0x34:0x37 |         | Cal_v  |                                          |  |

|------|---------------|---------|--------|------------------------------------------|--|

| Bit  | Bit Name      | Default | Access | Bit Description                          |  |

| 31:0 | Cal_v         | -       | R      | Calibrate v data (4 byte floating point) |  |

Figure 39: Calibrated DUV Result Register

| Add  | dr: 0x38:0x3B |         |        | Cal_DUV                                     |

|------|---------------|---------|--------|---------------------------------------------|

| Bit  | Bit Name      | Default | Access | Bit Description                             |

| 31:0 | Cal_DUV       | -       | R      | Calibrated DUV data (4 byte floating point) |

ams Datasheet Page 31

[v1-00] 2016-Dec-29

Document Feedback

# **Calibrated LUX Result Registers**

These byte registers are used together as CAL\_LUX\_H: CAL\_LUX\_L

They create a 16 bit integer value for calibrated LUX.

Example: 0000001111101000 = 1000 Lux

Figure 40: Calibrated LUX Result Registers

| A   | Addr: 0x3C |         |        | CAL_LUX_L                     |

|-----|------------|---------|--------|-------------------------------|

| Bit | Bit Name   | Default | Access | Bit Description               |

| 7:0 | CAL_LUX_L  | -       | R      | Calibrated LUX data, low byte |

| Addr: 0x3D |           | CAL_LUX_H |        |                                |  |

|------------|-----------|-----------|--------|--------------------------------|--|

| Bit        | Bit Name  | Default   | Access | Bit Description                |  |

| 7:0        | CAL_LUX_H | -         | R      | Calibrated LUX data, high byte |  |

Page 32ams DatasheetDocument Feedback[v1-00] 2016-Dec-29

# **Calibrated CCT Result Registers**

These byte registers are used together as CAL\_CCT\_H: CAL\_CCT\_L

They create a 16 bit integer value for sensed CCT (Kelvin).

Example: 0000101110111000 = 3000 K

Figure 41: Calibrated CCT Result Registers

| Addr: 0x3E |           | CAL_CCT_L |        |                               |  |

|------------|-----------|-----------|--------|-------------------------------|--|

| Bit        | Bit Name  | Default   | Access | Bit Description               |  |

| 7:0        | CAL_CCT_L | -         | R      | Calibrated CCT data, low byte |  |

| Addr: 0x3F |           | CAL_CCT_H |        |                                |  |

|------------|-----------|-----------|--------|--------------------------------|--|

| Bit        | Bit Name  | Default   | Access | Bit Description                |  |

| 7:0        | CAL_CCT_H | -         | R      | Calibrated CCT data, high byte |  |

ams Datasheet Page 33

[v1-00] 2016-Dec-29 Document Feedback

### I<sup>2</sup>C Master Interface (Local Sensor Interface)

The I<sup>2</sup>C Master interface can be used to connect external sensors such as the TSL4531 ambient light sensor (or other external sensors with AS7225 native support). Refer to the separate **ams** Application note for external sensor usage with the AS7225.

#### I<sup>2</sup>C Feature List

- Clock is set to 100kHz

- 7+1-bit addressing mode.

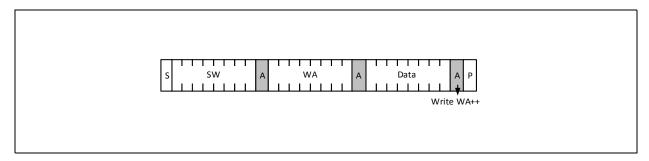

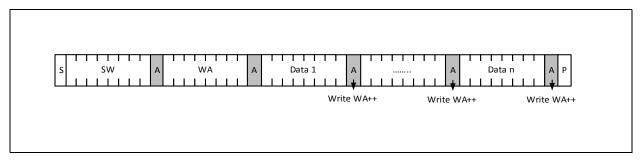

- Write formats: Single-Byte-Write, Page-Write

- Read formats: Random-Read, Sequential-Read

#### I<sup>2</sup>C Protocol

Figure 42: I<sup>2</sup>C Symbol Definition

| Symbol   | Definition                   | RW | Note               |

|----------|------------------------------|----|--------------------|

| S        | Start condition after stop   | R  | 1 bit              |

| Sr       | Repeated start               | R  | 1 bit              |

| SW       | Slave address for write      | R  | Slave address      |

| SR       | Slave address for read       | R  | Slave address      |

| WA       | Word address                 | R  | 8 bit              |

| Α        | Acknowledge                  | W  | 1 bit              |

| N        | No Acknowledge               | R  | 1 bit              |

| Data     | Data/write                   | R  | 8 bit              |

| Data (n) | Data/read                    | W  | 8 bit              |

| Р        | Stop condition               | R  | 1 bit              |

| WA++     | Slave Increment word address | R  | During acknowledge |

The above I<sup>2</sup>C symbol definition table describes the symbols used in the following Read and Write descriptions.

Page 34

Document Feedback [v1-00] 2016-Dec-29

#### I<sup>2</sup>C Write Access

Byte Write and Page Write formats are used to write data to the slave.

Figure 43: I<sup>2</sup>C Byte Write

Figure 44: I<sup>2</sup>C Page Write

The transmission begins with the START condition, which is generated by the master when the bus is in IDLE state (the bus is free). The device-write address is followed by the word address. After the word address any number of data bytes can be sent to the slave. The word address is incremented internally, in order to write subsequent data bytes on subsequent address locations.

For reading data from the slave device, the master has to change the transfer direction. This can be done either with a repeated START condition followed by the device-read address, or simply with a new transmission START followed by the device-read address, when the bus is in IDLE state. The device-read address is always followed by the 1st register byte transmitted from the slave. In Read Mode any number of subsequent register bytes can be read from the slave. The word address is incremented internally.

ams Datasheet Page 35

[v1-00] 2016-Dec-29 Document Feedback

#### I<sup>2</sup>C Read Access

Random, Sequential and Current Address Read are used to read data from the slave.

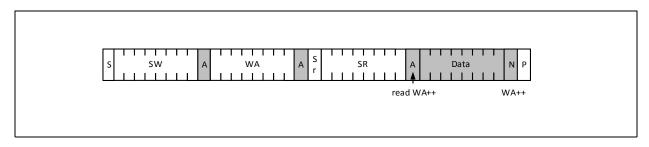

Figure 45: I<sup>2</sup>C Random Read

Random Read and Sequential Read are combined formats. The repeated START condition is used to change the direction after the data transfer from the master.

The word address transfer is initiated with a START condition issued by the master while the bus is idle. The START condition is followed by the device-write address and the word address.

In order to change the data direction a repeated START condition is issued on the 1st SCL pulse after the acknowledge bit of the word address transfer. After the reception of the device-read address, the slave becomes the transmitter. In this state the slave transmits register data located by the previous received word address vector. The master responds to the data byte with a not-acknowledge, and issues a STOP condition on the bus.

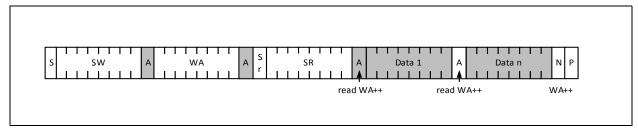

Figure 46: I<sup>2</sup>C Sequential Read

**I<sup>2</sup>C Sequential Read:** Shows the format of an I<sup>2</sup>C sequential read access.

Sequential Read is the extended form of Random Read, as more than one register-data bytes are transferred subsequently. In difference to the Random Read, for a sequential read the transferred register-data bytes are responded by an acknowledgement from the master. The number of data bytes transferred in one sequence is unlimited (consider the behavior of the word-address counter). To terminate the transmission the master has to send a not-acknowledge following the last data byte and generate the STOP condition subsequently.

The AS7225 is compatible to the NXP two wire specifications. http://www.nxp.com/documents/user\_manual/UM10204.pdf

Version 4.0 Feb 2012 for standard mode and fast mode.

Page 36

Document Feedback

[v1-00] 2016-Dec-29

### **Application Information**

#### **Schematics**

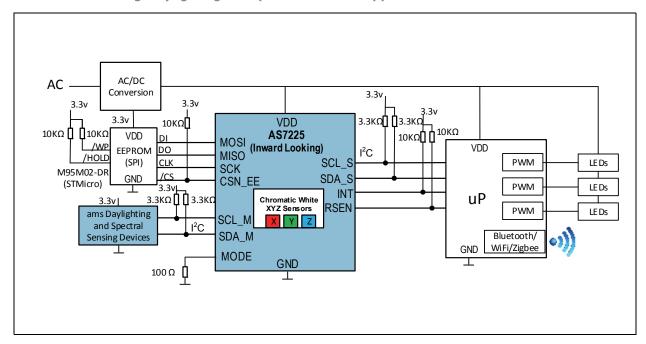

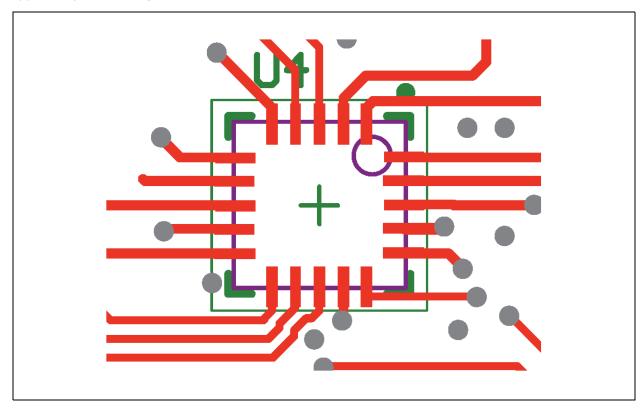

Figure 47:

AS7225 Color Tuning, Daylighting and Spectral Presence Application

**AS7225 Color Tuning, Daylighting and Spectral Presence Application:** AS7225 <u>Inward-looking</u> luminaire integration requires adding supported sensors via I<sup>2</sup>C for daylighting and/or spectral presence.

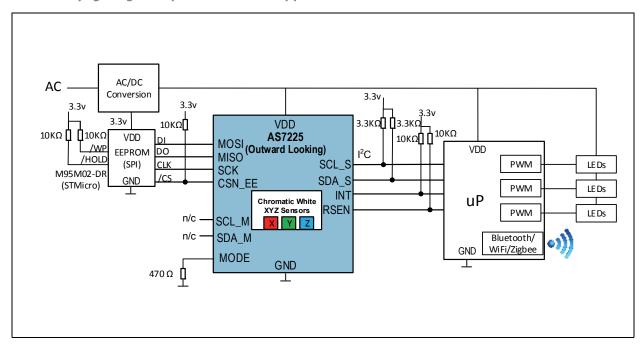

Figure 48:

AS7225 Daylighting and Spectral Presence Application

**AS7225 Daylighting and Spectral Presence Application:** AS7225 Outward-looking luminaire integration uses the internal sensor for daylighting and/or spectral presence. CCT-tuning is not supported for outward looking configurations.

ams Datasheet Page 37

[v1-00] 2016-Dec-29 Document Feedback