# Quad 2-Input NAND Gate with Schmitt-Trigger Inputs High-Performance Silicon-Gate CMOS

## **FEATURES**

Output Drive Capability: 10 LSTTL Loads

Outputs Directly Interface to CMOS, NMOS, and TTL

Operating Voltage Range: 2.0 to 6.0 V

Low Input Current: 1.0 μA

High Noise Immunity Characteristic of CMOS Devices

In Compliance with the Requirements as Defined by JEDEC Standard No. 7A

ESD Performance:

HBM > 2000 V; Machine Model > 200 V

Chip Complexity: 72 FETs or 18 Equivalent Gates

These are Pb-Free Device

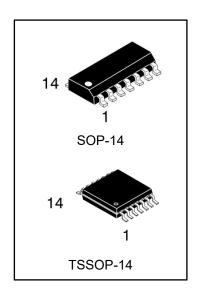

## ORDERING INFORMATION

| DEVICE      | Package Type | MARKING | Packing | Packing Qty  |

|-------------|--------------|---------|---------|--------------|

| 74HC132DRG  | SOP-14       | 74HC132 | REEL    | 2500pcs/reel |

| 74HC132PWRG | TSSOP-14     | HC132   | REEL    | 2500pcs/reel |

## **GENERAL DESCRIPTION**

The 74HC132 is identical in pinout to the LS132. The device nputs are compatible with standard CMOS outputs; with pull-up resistors, they are compatible with LSTTL outputs. The HC132 can be used to enhance noise immunity or to square up slowly changing waveforms.

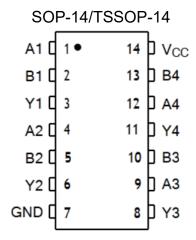

## PIN CONFIGURATION

Figure 1. Pin Assignment

PIN 14 = V<sub>CC</sub>:

PIN 7 = GND

Figure 2. Logic Diagram

## **FUNCTION TABLE**

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | Υ      |

| L      | L | Н      |

| L      | Н | Н      |

| H      | L | Н      |

| H      | Н | L      |

## **MAXIMUM RATINGS**

| Symbol           | Parameter                                           | Value          | Unit   |

|------------------|-----------------------------------------------------|----------------|--------|

| Vcc              | Positive DC Supply Voltage                          | -0.5 to +7.0   | V      |

| V <sub>IN</sub>  | Digital Input Voltage                               | -0.5 to +7.0   | ٧      |

| V <sub>OUT</sub> | DC Output Voltage Output in 3-State                 | -0.5 to +7.0   | V      |

|                  | High or Low State                                   | -0.5toVCC +0.5 |        |

| I <sub>IK</sub>  | Input Diode Current                                 | -20            | mA     |

| I <sub>ok</sub>  | Output Diode Current                                | ±20            | mA     |

| I <sub>OUT</sub> | DC Output Current, per Pin                          | ±25            | mA     |

| Icc              | DC Supply Current, VCC and GND Pins                 | ±75            | mA     |

| GND              | DC Ground Current per Ground Pin                    | ±75            | mA     |

| T <sub>STG</sub> | Storage Temperature Range                           | -65 to +150    | °C     |

| T∟               | Lead Temperature, 1 mm from Case for 10 Seconds     | 245            | °C     |

| TJ               | Junction Temperature Under Bias                     | +125           | °C     |

| $\theta_{JA}$    | Thermal Resistance 14-SOP                           | 125            | °C/W   |

|                  | 14-TSSOP                                            | 170            |        |

| P <sub>D</sub>   | Power Dissipation in Still Air at 85°C SOP          | 500            | mW     |

|                  | TSSOP                                               | 450            |        |

| M <sub>SL</sub>  | Moisture Sensitivity                                | Level 1        |        |

| F <sub>R</sub>   | Flammability Rating Oxygen Index: 30% - 35%         | UL 94 V-0 @    |        |

|                  |                                                     | 0.125 in       |        |

| $V_{ESD}$        | ESD Withstand Voltage Human Body Model (Note 1)     | >2000          | \<br>\ |

|                  | Machine Model (Note 2)                              | >200           |        |

| Latchup          | Latchup Performance Above VCC and Below GND at 85°C | ±300           | mA     |

|                  | (Note 3)                                            |                |        |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1.Tested to EIA/JESD22-A114-A.

- 2.Tested to EIA/JESD22-A115-A.

- 3.Tested to EIA/JESD78.

## RECOMMENDED OPERATING CONDITIONS

| Symbol                          | Parameter                                            | Min | Max     | Unit |

|---------------------------------|------------------------------------------------------|-----|---------|------|

| Vcc                             | DC Supply Voltage (Referenced to GND)                | 2.0 | 6.0     | V    |

| VIN,                            | DC Input Voltage, Output Voltage (Referenced to GND) | 0   | VCC     | V    |

| Vout                            |                                                      |     |         |      |

| Тд                              | Operating Temperature, All Package Types             | -40 | +85     | °C   |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise and Fall Time (Figure 3)                  | _   | NoLimt  | ns   |

|                                 |                                                      |     | (Note5) |      |

<sup>4.</sup>When  $V_{IN} \sim 0.5 \ V_{CC}$ ,  $I_{CC} >>$  quiescent current.

# DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)

|                 |                      |                                                      | VCC | Guaranteed    | l Limit |      |

|-----------------|----------------------|------------------------------------------------------|-----|---------------|---------|------|

| Symbol          | Parameter            | Test Conditions                                      | (V) | -40°C to 25°C | ≤85°C   | Unit |

| VT+max          | Maximum Positive     | V <sub>OUT</sub> = 0.1 V                             | 2.0 | 1.5           | 1.5     |      |

|                 | Going Input          | I <sub>OUT</sub>   ≤ 20 μA                           | 4.5 | 3.15          | 3.15    | V    |

|                 | Threshold Voltage    |                                                      | 6.0 | 4.2           | 4.2     |      |

|                 | (Figure 5)           |                                                      |     |               |         |      |

| VT+min          | Minimum              | V <sub>OUT</sub> = 0.1 V                             | 2.0 | 1.0           | 0.95    |      |

|                 | Positive-Going Input | I <sub>Ο∪Τ</sub>   ≤ 20 μA                           | 4.5 | 2.3           | 2.25    | V    |

|                 | Threshold Voltage    |                                                      | 6.0 | 3.0           | 2.95    |      |

|                 | (Figure 5)           |                                                      |     |               |         |      |

| VT-max          | Maximum              | $V_{OUT} = VCC - 0.1 V$                              | 2.0 | 0.9           | 0.95    |      |

|                 | Negative-Going       | I <sub>OUT</sub>   ≤ 20 μA                           | 4.5 | 2.0           | 2.05    | V    |

|                 | Input Threshold      |                                                      | 6.0 | 2.6           | 2.65    |      |

|                 | Voltage (Figure 5)   |                                                      |     |               |         |      |

| VT–min          | Minimum              | $V_{OUT} = V_{CC} - 0.1 \text{ V}$                   | 2.0 | 0.3           | 0.3     |      |

|                 | Negative-Going       | I <sub>Ο∪Τ</sub>   ≤ 20 μA                           | 4.5 | 0.9           | 0.9     | V    |

|                 | Input Threshold      |                                                      | 6.0 | 1.2           | 1.2     |      |

|                 | Voltage (Figure 5)   |                                                      |     |               |         |      |

| VHmax           | Maximum Hysteresis   | $V_{OUT} = 0.1 \text{ V or } V_{CC} - 0.1 \text{ V}$ | 2.0 | 1.2           | 1.2     |      |

| (Note 7)        | Voltage              | I <sub>Ο∪Τ</sub>   ≤ 20 μA                           | 4.5 | 2.25          | 2.25    | V    |

|                 | (Figure 5)           |                                                      | 6.0 | 3.0           | 3.0     |      |

| VHmin           | Minimum Hysteresis   | $V_{OUT} = 0.1 \text{ V or } V_{CC} - 0.1 \text{ V}$ | 2.0 | 0.2           | 0.2     |      |

| (Note 7)        | Voltage              | I <sub>Ο∪Τ</sub>   ≤ 20 μA                           | 4.5 | 0.4           | 0.4     | V    |

|                 | (Figure 5)           |                                                      | 6.0 | 0.5           | 0.5     |      |

| V <sub>OH</sub> | Minimum High-Level   | V <sub>IN</sub> ≤ VT−min or VT+max                   | 2.0 | 1.9           | 1.9     |      |

|                 | Output Voltage       | I <sub>Ο∪Τ</sub>   ≤ 20 μA                           | 4.5 | 4.4           | 4.4     |      |

|                 |                      |                                                      | 6.0 | 5.9           | 5.9     | V    |

|                 |                      | VIN ≤ -VT-min or VT+max                              |     |               |         |      |

|                 |                      | IOUT  ≤ 4.0 mA                                       | 4.5 | 3.98          | 3.84    |      |

|                 |                      | IOUT  ≤ 5.2 mA                                       | 6.0 | 5.48          | 5.34    |      |

<sup>5.</sup>Unused inputs may not be left open. All inputs must be tied to a high-logic voltage level or a low-logic input voltage level.

| V <sub>OL</sub> | Maximum Low-Level | V <sub>IN</sub> ≥VT+max                  | 2.0 | 0.1  | 0.1  |    |

|-----------------|-------------------|------------------------------------------|-----|------|------|----|

|                 | Output Voltage    | I <sub>OUT</sub>   ≤ 20 μA               | 4.5 | 0.1  | 0.1  |    |

|                 |                   |                                          | 6.0 | 0.1  | 0.1  | V  |

|                 |                   | VIN≥ VT+max I <sub>OUT</sub>   ≤ 4.0 mA  | 4.5 | 0.26 | 0.33 |    |

|                 |                   | I <sub>OUT</sub>   ≤ 5.2 mA              | 6.0 | 0.26 | 0.33 |    |

| I <sub>IN</sub> | Maximum Input     | V <sub>IN</sub> = V <sub>CC</sub> or GND | 6.0 | ±0.1 | ±1.0 | μΑ |

|                 | Leakage Current   |                                          |     |      |      |    |

| Icc             | Maximum Quiescent | V <sub>IN</sub> = V <sub>CC</sub> or GND | 6.0 | 2.0  | 20   | μΑ |

|                 | Supply Current    | Ι <sub>ΟυΤ</sub> = 0 μΑ                  |     |      |      |    |

|                 | (per Package)     |                                          |     |      |      |    |

6.VHmin >  $(V_T + min)$  —  $(V_T - max)$ ;  $V_H max = (V_T + max) + (V_T - min)$ .

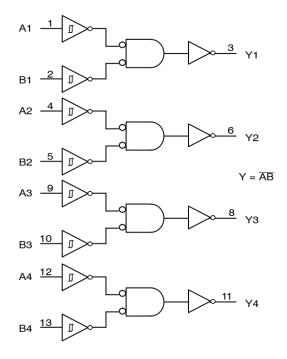

# **AC ELECTRICAL CHARACTERISTICS** (C<sub>L</sub> = 50 pF, Input t<sub>r</sub> = t<sub>f</sub> = 6.0 ns)

| Symbol                              | Parameter                                         | vcc | Guaranteed    | Limit | Hoit |  |

|-------------------------------------|---------------------------------------------------|-----|---------------|-------|------|--|

| Symbol                              | Parameter                                         | (V) | -40°C to 25°C | ≤85°C | Unit |  |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Maximum Propagation Delay, Input A or B to Output | 2.0 | 125           | 155   | ns   |  |

|                                     | Y (Figures 3 and 4)                               | 4.5 | 25            | 31    |      |  |

|                                     |                                                   | 6.0 | 21            | 26    |      |  |

| t <sub>TLH</sub> , t <sub>THL</sub> | Maximum Output Transition Time, Any Output        | 2.0 | 75            | 95    | ns   |  |

|                                     | (Figures 3 and 4)                                 | 4.5 | 15            | 19    |      |  |

|                                     |                                                   | 6.0 | 13            | 16    |      |  |

| Cin                                 | Maximum Input Capacitance                         | 10  | 10            | pF    |      |  |

|                                     | Typical@25°C,VCC=5.0V                             |     |               |       |      |  |

| C <sub>PD</sub>                     | Power Dissipation Capacitance(per Gate)(Note 10)  |     | 24            |       | pF   |  |

Used to determine the no-load dynamic power consumption:  $P_D = C_{PD} V_{CC}^2 f + I_{CC} V_{CC}$

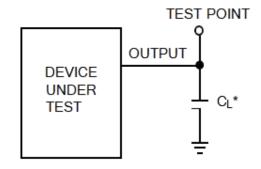

\*Includes all probe and jig capacitance

Figure 3. Switching Waveforms

Figure 4. Test Circuit

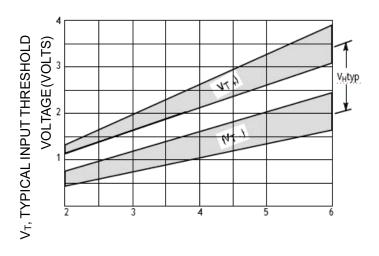

V<sub>CC</sub>,POWER SUPPLY VOLTAE (VOLTS) VHtyp = (VT + typ) - (VT - typ)

Figure 5. Typical Input Threshold, VT+, VT- Versus Power Supply Voltage

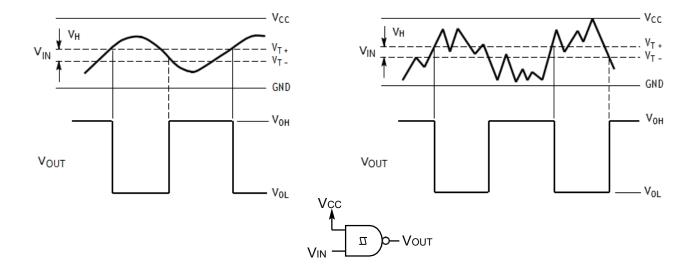

(A)A SCHMITT TRIGGER SQUARES UP INPUTS WITH SLOW RISE AND FALL TIMES

(B) A SCHMITT TRGGER OFFERS MAXIMUM NOSISE IMMUNITY

Figure 6. Typical Schmitt-Trigger Applications

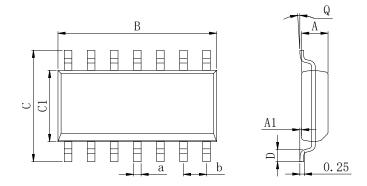

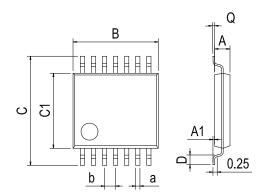

# **PHYSICAL DIMENSIONS**

## SOP-14

| Dimensions In Millimeters(SOP-14) |      |      |      |      |      |      |    |      |          |

|-----------------------------------|------|------|------|------|------|------|----|------|----------|

| Symbol:                           | А    | A1   | В    | С    | C1   | D    | Q  | а    | b        |

| Min:                              | 1.35 | 0.05 | 8.55 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1 07 DCC |

| Max:                              | 1.55 | 0.20 | 8.75 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |

## TSSOP-14

| Dimensions In Millimeters(TSSOP-14) |      |      |      |      |      |      |    |      |          |

|-------------------------------------|------|------|------|------|------|------|----|------|----------|

| Symbol:                             | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |

| Min:                                | 0.85 | 0.05 | 4.90 | 6.20 | 4.30 | 0.40 | 0° | 0.20 | 0.65 BSC |

| Max:                                | 0.95 | 0.20 | 5.10 | 6.60 | 4.50 | 0.80 | 8° | 0.25 | 0.05 650 |

# **REVISION HISTORY**

| DATE      | REVISION                                          | PAGE |

|-----------|---------------------------------------------------|------|

| 2020-3-1  | New                                               | 1-9  |

| 2023-7-21 | Update Lead Temperature、Update encapsulation type | 3、1  |

#### **IMPORTANT STATEMENT:**

Hanschip Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Hanschip Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Hanschip Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: select the appropriate Hanschip Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Hanschip Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Hanschip Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Hanschip Semiconductor, and the user shall not claim any compensation liability against Hanschip Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Hanschip Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Hanschip Semiconductor. Not all parameters of each device need to be tested.

The documentation of Hanschip Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Hanschip Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Hanschip Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Hanschip Semiconductor accepts no liability for any loss or damage caused by infringement.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Logic Gates category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

NLV17SG32DFT2G CD4068BE NL17SG86DFT2G NLX1G11AMUTCG NLX1G97MUTCG 74LS38 74LVC1G08Z-7 CD4025BE

NLV17SZ00DFT2G NLV17SZ126DFT2G NLV27WZ17DFT2G NLV74HC02ADR2G 74HC32S14-13 74LS133 74LVC1G32Z-7

74LVC1G86Z-7 NLV74HC14ADR2G NLV74HC20ADR2G NLVVHC1G09DFT1G NLX2G86MUTCG 74LVC2G32RA3-7

74LVC2G00HD4-7 NL17SG02P5T5G 74LVC2G86HK3-7 NLVVHC1G14DFT2G NLX1G99DMUTWG NLVVHC1G00DFT2G

NLV7SZ57DFT2G NLV74VHC04DTR2G NLV27WZ00USG NLU1G86CMUTCG NLU1G08CMUTCG NL17SZ32P5T5G

NL17SZ00P5T5G NL17SH02P5T5G 74AUP2G00RA3-7 NLVVHC1GT00DFT2G NLV74HC02ADTR2G NLX1G332CMUTCG

NLVHCT132ADTR2G NL17SG86P5T5G NL17SZ05P5T5G NLV74VHC00DTR2G NLVVHC1G02DFT1G NLV74HC86ADR2G

74LVC2G86RA3-7 NL17SZ38DBVT1G NLV18SZ00DFT2G NLVVHC1G07DFT1G NLVVHC1G02DFT2G