# Dual Channel, 128-/256-Position, I<sup>2</sup>C, Nonvolatile Digital Potentiometer

**Data Sheet**

AD5122A/AD5142A

#### **FEATURES**

$10~k\Omega$  and  $100~k\Omega$  resistance options Resistor tolerance: 8% maximum

Wiper current: ±6 mA

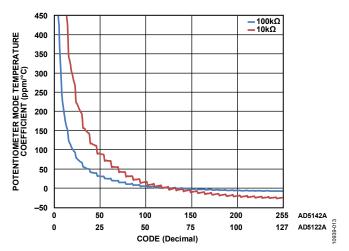

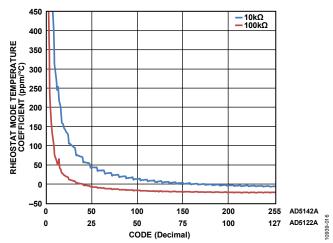

Low temperature coefficient: 35 ppm/°C

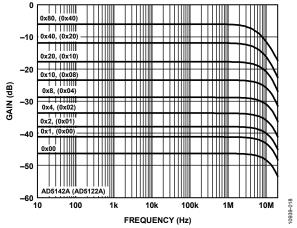

Wide bandwidth: 3 MHz

Fast start-up time < 75 µs

Linear gain setting mode

Single- and dual-supply operation

Independent logic supply: 1.8 V to 5.5 V

Wide operating temperature: -40°C to +125°C

3 mm × 3 mm package option

Qualified for automotive applications

#### **APPLICATIONS**

Portable electronics level adjustment LCD panel brightness and contrast controls Programmable filters, delays, and time constants Programmable power supplies

#### **GENERAL DESCRIPTION**

The AD5122A/AD5142A potentiometers provide a nonvolatile solution for 128-/256-position adjustment applications, offering guaranteed low resistor tolerance errors of  $\pm 8\%$  and up to  $\pm 6$  mA current density in the Ax, Bx, and Wx pins.

The low resistor tolerance and low nominal temperature coefficient simplify open-loop applications as well as applications requiring tolerance matching.

The linear gain setting mode allows independent programming of the resistance between the digital potentiometer terminals, through  $R_{\rm AW}$  and  $R_{\rm WB}$  the string resistors, allowing very accurate resistor matching.

The high bandwidth and low total harmonic distortion (THD) ensure optimal performance for ac signals, making it suitable for filter design.

The low wiper resistance of only 40  $\Omega$  at the ends of the resistor array allows for pin-to-pin connection.

The wiper values can be set through an I<sup>2</sup>C-compatible digital interface that is also used to read back the wiper register and EEPROM contents.

The AD5122A/AD5142A are available in a compact, 16-lead, 3 mm  $\times$  3 mm LFCSP and a 16-lead TSSOP. The parts are guaranteed to operate over the extended industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

#### Rev. B Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

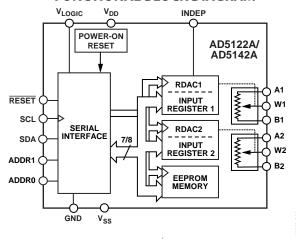

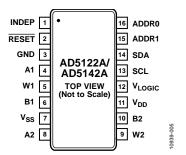

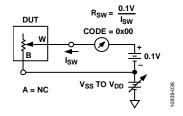

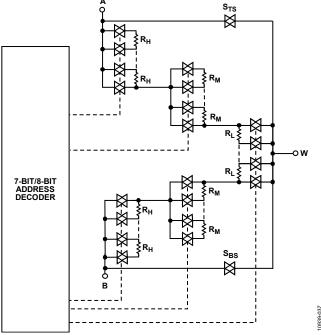

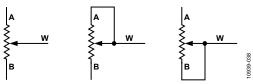

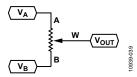

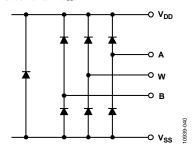

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

Table 1. Family Models

| Model               | Channel | Position | Interface            | Package     |

|---------------------|---------|----------|----------------------|-------------|

| AD5123 <sup>1</sup> | Quad    | 128      | I <sup>2</sup> C     | LFCSP       |

| AD5124              | Quad    | 128      | SPI/I <sup>2</sup> C | LFCSP       |

| AD5124              | Quad    | 128      | SPI                  | TSSOP       |

| AD5143 <sup>1</sup> | Quad    | 256      | I <sup>2</sup> C     | LFCSP       |

| AD5144              | Quad    | 256      | SPI/I <sup>2</sup> C | LFCSP       |

| AD5144              | Quad    | 256      | SPI                  | TSSOP       |

| AD5144A             | Quad    | 256      | I <sup>2</sup> C     | TSSOP       |

| AD5122              | Dual    | 128      | SPI                  | LFCSP/TSSOP |

| AD5122A             | Dual    | 128      | I <sup>2</sup> C     | LFCSP/TSSOP |

| AD5142              | Dual    | 256      | SPI                  | LFCSP/TSSOP |

| AD5142A             | Dual    | 256      | I <sup>2</sup> C     | LFCSP/TSSOP |

| AD5121              | Single  | 128      | SPI/I <sup>2</sup> C | LFCSP       |

| AD5141              | Single  | 256      | SPI/I <sup>2</sup> C | LFCSP       |

<sup>&</sup>lt;sup>1</sup> Two potentiometers and two rheostats.

| TABLE OF CONTENTS                                    |                                                    |    |

|------------------------------------------------------|----------------------------------------------------|----|

| Features 1                                           | RDAC Register and EEPROM                           | 20 |

| Applications1                                        | Input Shift Register                               | 20 |

| Functional Block Diagram                             | I <sup>2</sup> C Serial Data Interface             | 20 |

| General Description                                  | I <sup>2</sup> C Address                           | 20 |

| Revision History                                     | Advanced Control Modes                             | 22 |

| Specifications                                       | EEPROM or RDAC Register Protection                 | 23 |

| Electrical Characteristics—AD5122A                   | INDEP Pin                                          | 23 |

| Electrical Characteristics—AD5142A6                  | RDAC Architecture                                  | 26 |

| Interface Timing Specifications9                     | Programming the Variable Resistor                  | 26 |

| Shift Register and Timing Diagrams10                 | Programming the Potentiometer Divider              | 27 |

| Absolute Maximum Ratings11                           | Terminal Voltage Operating Range                   | 27 |

| Thermal Resistance11                                 | Power-Up Sequence                                  | 27 |

| ESD Caution11                                        | Layout and Power Supply Biasing                    | 27 |

| Pin Configurations and Function Descriptions         | Outline Dimensions                                 | 28 |

| Typical Performance Characteristics                  | Ordering Guide                                     | 29 |

| Test Circuits                                        | Automotive Products                                | 29 |

| Theory of Operation                                  |                                                    |    |

| REVISION HISTORY                                     |                                                    |    |

| 6/2017—Rev. A to Rev. B                              | Changes to Figure 18                               | 16 |

| Changes to Features Section                          | Change to Linear Gain Setting Mode                 |    |

| Changes to Logic Supply Current Parameter, Table 2 4 | Changes to EEPROM or RDAC Register Protection Sect |    |

| Added Note 12 to Data Retention Parameter, Table 2;  | Changes to RDAC Architecture Section               |    |

| Renumbered Sequentially                              | Updated Outline Dimensions                         |    |

| Changes to Logic Supply Current Parameter, Table 3   | Changes to Ordering Guide                          |    |

| Added Note 12 to Data Retention Parameter, Table 3;  | Added Automotive Products Section                  | 29 |

| Renumbered Sequentially                              |                                                    |    |

| Changes to Table 5                                   | 12/2012—Rev. 0 to Rev. A                           |    |

| Changes to Figure 4 and Table 7                      | Changes to Table 9                                 | 20 |

| Changes to Figure 14                                 |                                                    |    |

| Added Figure 15; Renumbered Sequentially             | 10/2012—Revision 0: Initial Version                |    |

# **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS—AD5122A**

$V_{DD} = 2.3 \text{ V to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}; V_{DD} = 2.25 \text{ V to } 2.75 \text{ V}, V_{SS} = -2.25 \text{ V to } -2.75 \text{ V}; V_{LOGIC} = 1.8 \text{ V to } 5.5 \text{ V}, -40 ^{\circ}\text{C} < T_{A} < +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 2.

| Parameter                                                 | Symbol                                        | Test Conditions/Comments       | Min   | Typ <sup>1</sup> | Max   | Unit   |

|-----------------------------------------------------------|-----------------------------------------------|--------------------------------|-------|------------------|-------|--------|

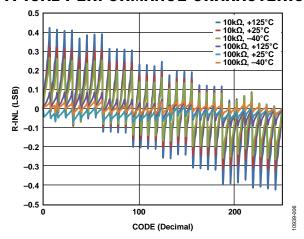

| DC CHARACTERISTICS—RHEOSTAT<br>MODE (ALL RDACs)           |                                               |                                |       |                  |       |        |

| Resolution                                                | N                                             |                                | 7     |                  |       | Bits   |

| Resistor Integral Nonlinearity <sup>2</sup>               | R-INL                                         | $R_{AB} = 10 \text{ k}\Omega$  |       |                  |       |        |

|                                                           |                                               | $V_{DD} \ge 2.7 \text{ V}$     | -1    | ±0.1             | +1    | LSB    |

|                                                           |                                               | $V_{DD}$ < 2.7 V               | -2.5  | ±1               | +2.5  | LSB    |

|                                                           |                                               | $R_{AB} = 100 \text{ k}\Omega$ |       |                  |       |        |

|                                                           |                                               | $V_{DD} \ge 2.7 \text{ V}$     | -0.5  | ±0.1             | +0.5  | LSB    |

|                                                           |                                               | V <sub>DD</sub> < 2.7 V        | -1    | ±0.25            | +1    | LSB    |

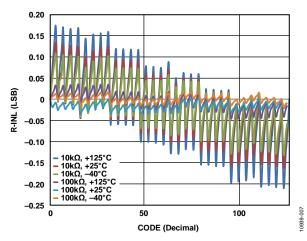

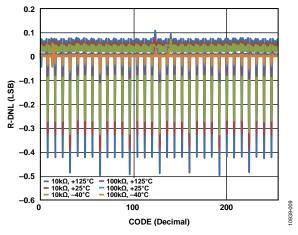

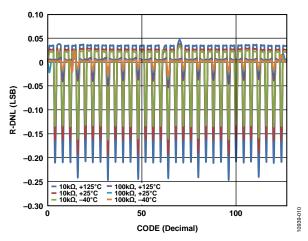

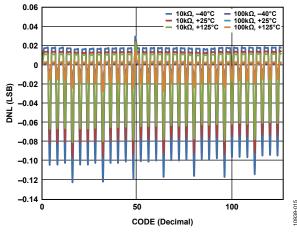

| Resistor Differential Nonlinearity <sup>2</sup>           | R-DNL                                         |                                | -0.5  | ±0.1             | +0.5  | LSB    |

| Nominal Resistor Tolerance                                | $\Delta R_{AB}/R_{AB}$                        |                                | -8    | ±1               | +8    | %      |

| Resistance Temperature Coefficient <sup>3</sup>           | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^6$ | Code = full scale              |       | 35               |       | ppm/°C |

| Wiper Resistance <sup>3</sup>                             | $R_{W}$                                       | Code = zero scale              |       |                  |       |        |

|                                                           |                                               | $R_{AB} = 10 \text{ k}\Omega$  |       | 55               | 125   | Ω      |

|                                                           |                                               | $R_{AB} = 100 \text{ k}\Omega$ |       | 130              | 400   | Ω      |

| Bottom Scale or Top Scale                                 | R <sub>BS</sub> or R <sub>TS</sub>            |                                |       |                  |       |        |

|                                                           |                                               | $R_{AB} = 10 \text{ k}\Omega$  |       | 40               | 80    | Ω      |

|                                                           |                                               | $R_{AB} = 100 \text{ k}\Omega$ |       | 60               | 230   | Ω      |

| Nominal Resistance Match                                  | $R_{AB1}/R_{AB2}$                             | Code = 0xFF                    | -1    | ±0.2             | +1    | %      |

| DC CHARACTERISTICS—POTENTIOMETER DIVIDER MODE (ALL RDACs) |                                               |                                |       |                  |       |        |

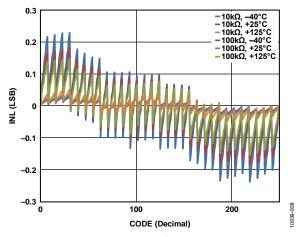

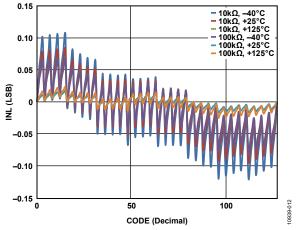

| Integral Nonlinearity <sup>4</sup>                        | INL                                           |                                |       |                  |       |        |

|                                                           |                                               | $R_{AB} = 10 \text{ k}\Omega$  | -0.5  | ±0.1             | +0.5  | LSB    |

|                                                           |                                               | $R_{AB} = 100 \text{ k}\Omega$ | -0.25 | ±0.1             | +0.25 | LSB    |

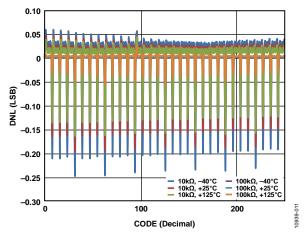

| Differential Nonlinearity <sup>4</sup>                    | DNL                                           |                                | -0.25 | ±0.1             | +0.25 | LSB    |

| Full-Scale Error                                          | $V_{\text{WFSE}}$                             |                                |       |                  |       |        |

|                                                           |                                               | $R_{AB} = 10 \text{ k}\Omega$  | -1.5  | -0.1             |       | LSB    |

|                                                           |                                               | $R_{AB} = 100 \text{ k}\Omega$ | -0.5  | ±0.1             | +0.5  | LSB    |

| Zero-Scale Error                                          | $V_{\text{WZSE}}$                             |                                |       |                  |       |        |

|                                                           |                                               | $R_{AB} = 10 \text{ k}\Omega$  |       | 1                | 1.5   | LSB    |

|                                                           |                                               | $R_{AB} = 100 \text{ k}\Omega$ |       | 0.25             | 0.5   | LSB    |

| Voltage Divider Temperature<br>Coefficient <sup>3</sup>   | $(\Delta V_W/V_W)/\Delta T \times 10^6$       | Code = half scale              |       | ±5               |       | ppm/°C |

| Parameter                                 | Symbol                                               | Test Conditions/Comments                                               | Min                    | Typ <sup>1</sup>   | Max                    | Unit |

|-------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------|------------------------|--------------------|------------------------|------|

| RESISTOR TERMINALS                        |                                                      |                                                                        |                        |                    |                        |      |

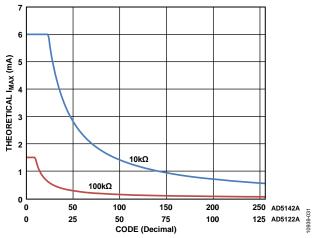

| Maximum Continuous Current                | I <sub>A</sub> , I <sub>B</sub> , and I <sub>W</sub> |                                                                        |                        |                    |                        |      |

|                                           |                                                      | $R_{AB} = 10 \text{ k}\Omega$                                          | -6                     |                    | +6                     | mA   |

|                                           |                                                      | $R_{AB} = 100 \text{ k}\Omega$                                         | -1.5                   |                    | +1.5                   | mΑ   |

| Terminal Voltage Range⁵                   |                                                      |                                                                        | $V_{ss}$               |                    | $V_{DD}$               | ٧    |

| Capacitance A, Capacitance B <sup>3</sup> | $C_A$ , $C_B$                                        | f = 1 MHz, measured to GND,<br>code = half scale                       |                        |                    |                        |      |

|                                           |                                                      | $R_{AB} = 10 \text{ k}\Omega$                                          |                        | 25                 |                        | рF   |

|                                           |                                                      | $R_{AB} = 100 \text{ k}\Omega$                                         |                        | 12                 |                        | рF   |

| Capacitance W <sup>3</sup>                | C <sub>w</sub>                                       | f = 1 MHz, measured to GND,<br>code = half scale                       |                        |                    |                        |      |

|                                           |                                                      | $R_{AB} = 10 \text{ k}\Omega$                                          |                        | 12                 |                        | рF   |

|                                           |                                                      | $R_{AB} = 100 \text{ k}\Omega$                                         |                        | 5                  |                        | рF   |

| Common-Mode Leakage Current <sup>3</sup>  |                                                      | $V_A = V_W = V_B$                                                      | -500                   | ±15                | +500                   | nΑ   |

| DIGITAL INPUTS                            |                                                      |                                                                        |                        |                    |                        |      |

| Input Logic <sup>3</sup>                  |                                                      |                                                                        |                        |                    |                        |      |

| High                                      | V <sub>INH</sub>                                     | $V_{LOGIC} = 1.8 \text{ V to } 2.3 \text{ V}$                          | $0.8 \times V_{LOGIC}$ |                    |                        | ٧    |

|                                           |                                                      | $V_{LOGIC} = 2.3 \text{ V to } 5.5 \text{ V}$                          | $0.7 \times V_{LOGIC}$ |                    |                        | ٧    |

| Low                                       | V <sub>INL</sub>                                     |                                                                        |                        |                    | $0.2 \times V_{LOGIC}$ | ٧    |

| Input Hysteresis <sup>3</sup>             | V <sub>HYST</sub>                                    |                                                                        | $0.1 \times V_{LOGIC}$ |                    |                        | ٧    |

| Input Current <sup>3</sup>                | I <sub>IN</sub>                                      |                                                                        |                        |                    | ±1                     | μΑ   |

| Input Capacitance <sup>3</sup>            | C <sub>IN</sub>                                      |                                                                        |                        | 5                  |                        | рF   |

| DIGITAL OUTPUTS                           |                                                      |                                                                        |                        |                    |                        |      |

| Output High Voltage <sup>3</sup>          | V <sub>OH</sub>                                      | $R_{PULL-UP} = 2.2 \text{ k}\Omega \text{ to } V_{LOGIC}$              |                        | $V_{\text{LOGIC}}$ |                        | ٧    |

| Output Low Voltage <sup>3</sup>           | V <sub>OL</sub>                                      | $I_{SINK} = 3 \text{ mA}$                                              |                        |                    | 0.4                    | V    |

|                                           |                                                      | $I_{SINK} = 6 \text{ mA}, V_{LOGIC} > 2.3 \text{ V}$                   |                        |                    | 0.6                    | V    |

| Three-State Leakage Current               |                                                      |                                                                        | -1                     |                    | +1                     | μΑ   |

| Three-State Output Capacitance            |                                                      |                                                                        |                        | 2                  |                        | рF   |

| POWER SUPPLIES                            |                                                      |                                                                        |                        |                    |                        |      |

| Single-Supply Power Range                 |                                                      | $V_{SS} = GND$                                                         | 2.3                    |                    | 5.5                    | V    |

| Dual-Supply Power Range                   |                                                      |                                                                        | ±2.25                  |                    | ±2.75                  | V    |

| Logic Supply Range                        |                                                      | Single supply, $V_{SS} = GND$                                          | 1.8                    |                    | $V_{DD}$               | V    |

|                                           |                                                      | Dual supply, V <sub>ss</sub> < GND                                     | 2.25                   |                    | $V_{DD}$               | V    |

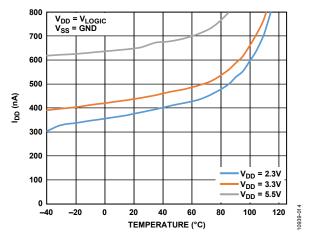

| Positive Supply Current                   | I <sub>DD</sub>                                      | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                 |                        |                    |                        |      |

|                                           |                                                      | $V_{DD} = 5.5 V$                                                       |                        | 0.7                | 5.5                    | μΑ   |

|                                           |                                                      | $V_{DD} = 2.3 \text{ V}$                                               |                        | 400                |                        | nA   |

| Negative Supply Current                   | I <sub>ss</sub>                                      | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                 | -5.5                   | -0.7               |                        | μΑ   |

| EEPROM Store Current <sup>3, 6</sup>      | I <sub>DD_EEPROM_STORE</sub>                         | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                 |                        | 2                  |                        | mA   |

| EEPROM Read Current <sup>3,7</sup>        | I <sub>DD_EEPROM_READ</sub>                          | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                 |                        | 320                |                        | μΑ   |

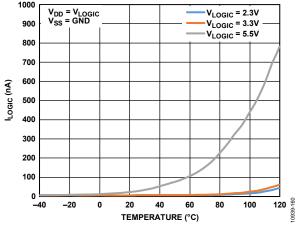

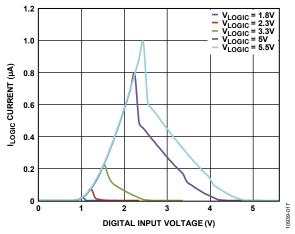

| Logic Supply Current                      | I <sub>LOGIC</sub>                                   | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                 |                        | 0.05               | 1.4                    | μΑ   |

| Power Dissipation <sup>8</sup>            | P <sub>DISS</sub>                                    | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                 |                        | 3.5                |                        | μW   |

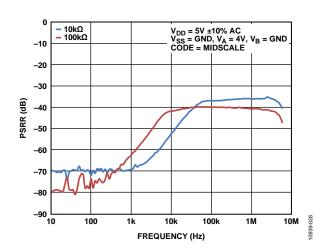

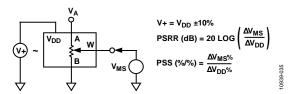

| Power Supply Rejection Ratio              | PSRR                                                 | $\Delta V_{DD}/\Delta V_{SS} = V_{DD} \pm 10\%$ ,<br>code = full scale |                        | -66                | -60                    | dB   |

**Data Sheet**

# AD5122A/AD5142A

| Parameter                                     | Symbol            | Test Conditions/Comments                                                                                              | Min Typ <sup>1</sup> Max | Unit    |

|-----------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------|---------|

| DYNAMIC CHARACTERISTICS <sup>9</sup>          |                   |                                                                                                                       |                          |         |

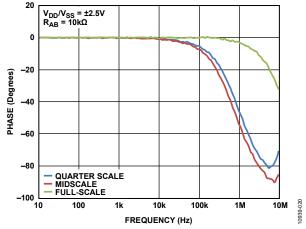

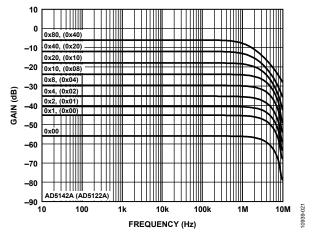

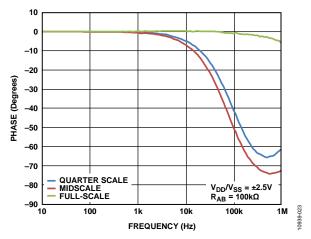

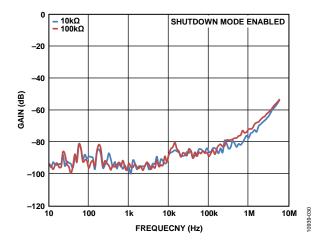

| Bandwidth                                     | BW                | -3 dB                                                                                                                 |                          |         |

|                                               |                   | $R_{AB} = 10 \text{ k}\Omega$                                                                                         | 3                        | MHz     |

|                                               |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        | 0.43                     | MHz     |

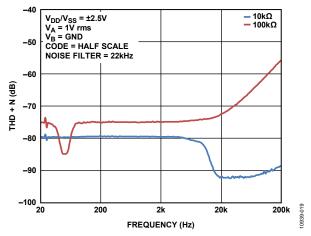

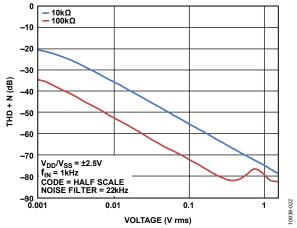

| Total Harmonic Distortion                     | THD               | $V_{DD}/V_{SS} = \pm 2.5 \text{ V, } V_A = 1 \text{ V rms,}$<br>$V_B = 0 \text{ V, } f = 1 \text{ kHz}$               |                          |         |

|                                               |                   | $R_{AB} = 10 \text{ k}\Omega$                                                                                         | -80                      | dB      |

|                                               |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        | -90                      | dB      |

| Resistor Noise Density                        | e <sub>N_WB</sub> | Code = half scale, $T_A = 25$ °C, $f = 10 \text{ kHz}$                                                                |                          |         |

|                                               |                   | $R_{AB} = 10 \text{ k}\Omega$                                                                                         | 7                        | nV/√Hz  |

|                                               |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        | 20                       | nV/√Hz  |

| V <sub>w</sub> Settling Time                  | t <sub>s</sub>    | $V_A = 5 \text{ V}, V_B = 0 \text{ V}, \text{ from}$<br>zero scale to full scale,<br>$\pm 0.5 \text{ LSB}$ error band |                          |         |

|                                               |                   | $R_{AB} = 10 \text{ k}\Omega$                                                                                         | 2                        | μs      |

|                                               |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        | 12                       | μs      |

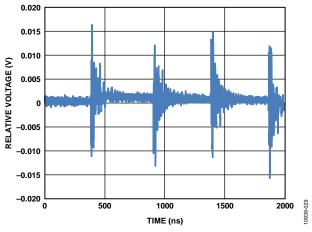

| Crosstalk (C <sub>w1</sub> /C <sub>w2</sub> ) | C <sub>T</sub>    | $R_{AB} = 10 \text{ k}\Omega$                                                                                         | 10                       | nV-sec  |

|                                               |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        | 25                       | nV-sec  |

| Analog Crosstalk                              | C <sub>TA</sub>   |                                                                                                                       | -90                      | dB      |

| Endurance <sup>10</sup>                       |                   | T <sub>A</sub> = 25°C                                                                                                 | 1                        | Mcycles |

|                                               |                   |                                                                                                                       | 100                      | kcycles |

| Data Retention <sup>11, 12</sup>              |                   |                                                                                                                       | 50                       | Years   |

$<sup>^{1}</sup>$  Typical values represent average readings at 25°C,  $V_{DD} = 5 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ , and  $V_{LOGIC} = 5 \text{ V}$ .

<sup>&</sup>lt;sup>2</sup> Resistor integral nonlinearity (R-INL) error is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. The maximum wiper current is limited to (0.7 × V<sub>DD</sub>)/R<sub>AB</sub>.

<sup>&</sup>lt;sup>3</sup> Guaranteed by design and characterization, not subject to production test.

$<sup>^4</sup>$  INL and DNL are measured at V<sub>WB</sub> with the RDAC configured as a potentiometer divider similar to a voltage output DAC. V<sub>A</sub> = V<sub>DD</sub> and V<sub>B</sub> = 0 V. DNL specification limits of  $\pm 1$  LSB maximum are guaranteed monotonic operating conditions.

<sup>&</sup>lt;sup>5</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other. Dual-supply operation enables ground referenced bipolar signal adjustment.

<sup>&</sup>lt;sup>6</sup> Different from operating current; supply current for EEPROM program lasts approximately 30 ms.

<sup>&</sup>lt;sup>7</sup> Different from operating current; supply current for EEPROM read lasts approximately 20 μs.

<sup>&</sup>lt;sup>8</sup>  $P_{DISS}$  is calculated from  $(I_{DD} \times V_{DD}) + (I_{LOGIC} \times V_{LOGIC})$ .

<sup>9</sup> All dynamic characteristics use  $V_{DD} V_{SS} = \pm 2.5 \text{ V}$ , and  $V_{LOGIC} = 2.5 \text{ V}$ .

<sup>10</sup> Endurance is qualified to 100,000 cycles per JEDEC Standard 22, Method A117 and measured at  $-40^{\circ}$ C to  $+125^{\circ}$ C.

<sup>11</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 125°C per JEDEC Standard 22, Method A117. Retention lifetime, based on an activation energy of 1 eV, derates with junction temperature in the Flash/EE memory.

<sup>&</sup>lt;sup>12</sup> 50 years apply to an endurance of 1000 cycles. An endurance of 100,000 cycles has an equivalent retention lifetime of 5 years.

#### **ELECTRICAL CHARACTERISTICS—AD5142A**

$V_{DD}$  = 2.3 V to 5.5 V,  $V_{SS}$  = 0 V;  $V_{DD}$  = 2.25 V to 2.75 V,  $V_{SS}$  = -2.25 V to -2.75 V;  $V_{LOGIC}$  = 1.8 V to 5.5 V, -40°C <  $T_A$  < +125°C, unless otherwise noted.

Table 3.

| Parameter                                                 | Symbol                                              | Test Conditions/Comments       | Min  | Typ <sup>1</sup> | Max  | Unit   |

|-----------------------------------------------------------|-----------------------------------------------------|--------------------------------|------|------------------|------|--------|

| DC CHARACTERISTICS—RHEOSTAT MODE (ALL RDACs)              |                                                     |                                |      |                  |      |        |

| Resolution                                                | N                                                   |                                | 8    |                  |      | Bits   |

| Resistor Integral Nonlinearity <sup>2</sup>               | R-INL                                               | $R_{AB} = 10 \text{ k}\Omega$  |      |                  |      |        |

|                                                           |                                                     | $V_{DD} \ge 2.7 \text{ V}$     | -2   | ±0.2             | +2   | LSB    |

|                                                           |                                                     | $V_{DD} < 2.7 \text{ V}$       | -5   | ±1.5             | +5   | LSB    |

|                                                           |                                                     | $R_{AB} = 100 \text{ k}\Omega$ |      |                  |      |        |

|                                                           |                                                     | $V_{DD} \ge 2.7 \text{ V}$     | -1   | ±0.1             | +1   | LSB    |

|                                                           |                                                     | $V_{DD}$ < 2.7 V               | -2   | ±0.5             | +2   | LSB    |

| Resistor Differential Nonlinearity <sup>2</sup>           | R-DNL                                               |                                | -0.5 | ±0.2             | +0.5 | LSB    |

| Nominal Resistor Tolerance                                | $\Delta R_{AB}/R_{AB}$                              |                                | -8   | ±1               | +8   | %      |

| Resistance Temperature Coefficient <sup>3</sup>           | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^6$       | Code = full scale              |      | 35               |      | ppm/°C |

| Wiper Resistance <sup>3</sup>                             | R <sub>W</sub>                                      | Code = zero scale              |      |                  |      |        |

|                                                           |                                                     | $R_{AB} = 10 \text{ k}\Omega$  |      | 55               | 125  | Ω      |

|                                                           |                                                     | $R_{AB} = 100 \text{ k}\Omega$ |      | 130              | 400  | Ω      |

| Bottom Scale or Top Scale                                 | R <sub>BS</sub> or R <sub>TS</sub>                  |                                |      |                  |      |        |

|                                                           |                                                     | $R_{AB} = 10 \text{ k}\Omega$  |      | 40               | 80   | Ω      |

|                                                           |                                                     | $R_{AB} = 100 \text{ k}\Omega$ |      | 60               | 230  | Ω      |

| Nominal Resistance Match                                  | $R_{AB1}/R_{AB2}$                                   | Code = 0xFF                    | -1   | ±0.2             | +1   | %      |

| DC CHARACTERISTICS—POTENTIOMETER DIVIDER MODE (ALL RDACs) |                                                     |                                |      |                  |      |        |

| Integral Nonlinearity <sup>4</sup>                        | INL                                                 |                                |      |                  |      |        |

|                                                           |                                                     | $R_{AB} = 10 \text{ k}\Omega$  | -1   | ±0.2             | +1   | LSB    |

|                                                           |                                                     | $R_{AB} = 100 \text{ k}\Omega$ | -0.5 | ±0.1             | +0.5 | LSB    |

| Differential Nonlinearity <sup>4</sup>                    | DNL                                                 |                                | -0.5 | ±0.2             | +0.5 | LSB    |

| Full-Scale Error                                          | V <sub>WFSE</sub>                                   |                                |      |                  |      |        |

|                                                           |                                                     | $R_{AB} = 10 \text{ k}\Omega$  | -2.5 | -0.1             |      | LSB    |

|                                                           |                                                     | $R_{AB} = 100 \text{ k}\Omega$ | -1   | ±0.2             | +1   | LSB    |

| Zero-Scale Error                                          | $V_{WZSE}$                                          |                                |      |                  |      |        |

|                                                           |                                                     | $R_{AB} = 10 \text{ k}\Omega$  |      | 1.2              | 3    | LSB    |

|                                                           |                                                     | $R_{AB} = 100 \text{ k}\Omega$ |      | 0.5              | 1    | LSB    |

| Voltage Divider Temperature<br>Coefficient <sup>3</sup>   | $(\Delta V_{\rm W}/V_{\rm W})/\Delta T \times 10^6$ | Code = half scale              |      | ±5               |      | ppm/°C |

| Parameter                                 | Symbol                                               | <b>Test Conditions/Comments</b>                                     | Min                    | Typ <sup>1</sup> | Max                    | Unit |

|-------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------|------------------------|------------------|------------------------|------|

| RESISTOR TERMINALS                        |                                                      |                                                                     |                        |                  |                        |      |

| Maximum Continuous Current                | I <sub>A</sub> , I <sub>B</sub> , and I <sub>W</sub> |                                                                     |                        |                  |                        |      |

|                                           |                                                      | $R_{AB} = 10 \text{ k}\Omega$                                       | -6                     |                  | +6                     | mA   |

|                                           |                                                      | $R_{AB} = 100 \text{ k}\Omega$                                      | -1.5                   |                  | +1.5                   | mA   |

| Terminal Voltage Range⁵                   |                                                      |                                                                     | $V_{ss}$               |                  | $V_{DD}$               | V    |

| Capacitance A, Capacitance B <sup>3</sup> | $C_A$ , $C_B$                                        | f = 1 MHz, measured to GND, code = half scale                       |                        |                  |                        |      |

|                                           |                                                      | $R_{AB} = 10 \text{ k}\Omega$                                       |                        | 25               |                        | рF   |

|                                           |                                                      | $R_{AB} = 100 \text{ k}\Omega$                                      |                        | 12               |                        | рF   |

| Capacitance W <sup>3</sup>                | C <sub>w</sub>                                       | f = 1 MHz, measured to GND, code = half scale                       |                        |                  |                        |      |

|                                           |                                                      | $R_{AB} = 10 \text{ k}\Omega$                                       |                        | 12               |                        | рF   |

|                                           |                                                      | $R_{AB} = 100 \text{ k}\Omega$                                      |                        | 5                |                        | рF   |

| Common-Mode Leakage Current <sup>3</sup>  |                                                      | $V_A = V_W = V_B$                                                   | -500                   | ±15              | +500                   | nA   |

| DIGITAL INPUTS                            |                                                      |                                                                     |                        |                  |                        |      |

| Input Logic <sup>3</sup>                  |                                                      |                                                                     |                        |                  |                        |      |

| High                                      | V <sub>INH</sub>                                     | $V_{LOGIC} = 1.8 \text{ V to } 2.3 \text{ V}$                       | $0.8 \times V_{LOGIC}$ |                  |                        | ٧    |

|                                           |                                                      | $V_{LOGIC} = 2.3 \text{ V to } 5.5 \text{ V}$                       | $0.7 \times V_{LOGIC}$ |                  |                        | V    |

| Low                                       | V <sub>INL</sub>                                     |                                                                     |                        |                  | $0.2 \times V_{LOGIC}$ | V    |

| Input Hysteresis <sup>3</sup>             | V <sub>HYST</sub>                                    |                                                                     | $0.1 \times V_{LOGIC}$ |                  | Louic                  | V    |

| Input Current <sup>3</sup>                | I <sub>IN</sub>                                      |                                                                     |                        |                  | ±1                     | μΑ   |

| Input Capacitance <sup>3</sup>            | C <sub>IN</sub>                                      |                                                                     |                        | 5                |                        | рF   |

| DIGITAL OUTPUTS                           |                                                      |                                                                     |                        |                  |                        |      |

| Output High Voltage <sup>3</sup>          | V <sub>OH</sub>                                      | $R_{PULL-UP} = 2.2 \text{ k}\Omega \text{ to } V_{LOGIC}$           |                        | $V_{LOGIC}$      |                        | V    |

| Output Low Voltage <sup>3</sup>           | V <sub>OL</sub>                                      | I <sub>SINK</sub> = 3 mA                                            |                        |                  | 0.4                    | V    |

|                                           |                                                      | $I_{SINK} = 6 \text{ mA}, V_{LOGIC} > 2.3 \text{ V}$                |                        |                  | 0.6                    | V    |

| Three-State Leakage Current               |                                                      | 5                                                                   | -1                     |                  | +1                     | μΑ   |

| Three-State Output Capacitance            |                                                      |                                                                     |                        | 2                |                        | pF   |

| POWER SUPPLIES                            |                                                      |                                                                     |                        |                  |                        |      |

| Single-Supply Power Range                 |                                                      | $V_{SS} = GND$                                                      | 2.3                    |                  | 5.5                    | V    |

| Dual-Supply Power Range                   |                                                      | 55                                                                  | ±2.25                  |                  | ±2.75                  | V    |

| Logic Supply Range                        |                                                      | Single supply, $V_{SS} = GND$                                       | 1.8                    |                  | $V_{DD}$               | V    |

| 3 11,7 3                                  |                                                      | Dual supply, V <sub>ss</sub> < GND                                  | 2.25                   |                  | $V_{DD}$               | V    |

| Positive Supply Current                   | I <sub>DD</sub>                                      | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                              |                        |                  | DD                     |      |

| 112                                       |                                                      | $V_{DD} = 5.5 \text{ V}$                                            |                        | 0.7              | 5.5                    | μΑ   |

|                                           |                                                      | $V_{DD} = 2.3 \text{ V}$                                            |                        | 400              |                        | nA   |

| Negative Supply Current                   | I <sub>ss</sub>                                      | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                              | -5.5                   | -0.7             |                        | μΑ   |

| EEPROM Store Current <sup>3,6</sup>       | I <sub>DD_EEPROM_STORE</sub>                         | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                              |                        | 2                |                        | mA   |

| EEPROM Read Current <sup>3,7</sup>        | I <sub>DD</sub> EEPROM READ                          | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                              |                        | 320              |                        | μΑ   |

| Logic Supply Current                      | I <sub>LOGIC</sub>                                   | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                              |                        | 0.05             | 1.4                    | μΑ   |

| Power Dissipation <sup>8</sup>            | P <sub>DISS</sub>                                    | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                              |                        | 3.5              | •                      | μW   |

| Power Supply Rejection Ratio              | PSR                                                  | $\Delta V_{DD}/\Delta V_{SS} = V_{DD} \pm 10\%$ , code = full scale |                        | -66              | -60                    | dB   |

| Parameter                            | Symbol            | Test Conditions/Comments                                                                                              | Min | Typ¹ Max | Unit    |

|--------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|-----|----------|---------|

| DYNAMIC CHARACTERISTICS <sup>9</sup> |                   |                                                                                                                       |     |          |         |

| Bandwidth                            | BW                | −3 dB                                                                                                                 |     |          |         |

|                                      |                   | $R_{AB} = 10 \text{ k}\Omega$                                                                                         |     | 3        | MHz     |

|                                      |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        |     | 0.43     | MHz     |

| Total Harmonic Distortion            | THD               | $V_{DD}/V_{SS} = \pm 2.5 \text{ V}, V_A = 1 \text{ V rms}, V_B = 0 \text{ V}, f = 1 \text{ kHz}$                      |     |          |         |

|                                      |                   | $R_{AB} = 10 \text{ k}\Omega$                                                                                         |     | -80      | dB      |

|                                      |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        |     | -90      | dB      |

| Resistor Noise Density               | e <sub>N_WB</sub> | Code = half scale, $T_A = 25$ °C, $f = 10$ kHz                                                                        |     |          |         |

|                                      |                   | $R_{AB} = 10 \text{ k}\Omega$                                                                                         |     | 7        | nV/√Hz  |

|                                      |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        |     | 20       | nV/√Hz  |

| V <sub>W</sub> Settling Time         | t <sub>s</sub>    | $V_A = 5 \text{ V}, V_B = 0 \text{ V}, \text{ from}$<br>zero scale to full scale,<br>$\pm 0.5 \text{ LSB}$ error band |     |          |         |

|                                      |                   | $R_{AB} = 10 \text{ k}\Omega$                                                                                         |     | 2        | μs      |

|                                      |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        |     | 12       | μs      |

| Crosstalk ( $C_{W1}/C_{W2}$ )        | $C_{T}$           | $R_{AB} = 10 \text{ k}\Omega$                                                                                         |     | 10       | nV-sec  |

|                                      |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                                        |     | 25       | nV-sec  |

| Analog Crosstalk                     | C <sub>TA</sub>   |                                                                                                                       |     | -90      | dB      |

| Endurance <sup>10</sup>              |                   | T <sub>A</sub> = 25°C                                                                                                 |     | 1        | Mcycles |

|                                      |                   |                                                                                                                       | 100 |          | kcycles |

| Data Retention <sup>11, 12</sup>     |                   |                                                                                                                       |     | 50       | Years   |

<sup>&</sup>lt;sup>1</sup> Typical values represent average readings at 25°C,  $V_{DD} = 5 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ , and  $V_{LOGIC} = 5 \text{ V}$ .

<sup>&</sup>lt;sup>2</sup> Resistor integral nonlinearity (R-INL) error is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. The maximum wiper current is limited to (0.7 × V<sub>DD</sub>)/R<sub>AB</sub>.

Guaranteed by design and characterization, not subject to production test.

$<sup>^4</sup>$  INL and DNL are measured at V<sub>WB</sub> with the RDAC configured as a potentiometer divider similar to a voltage output DAC. V<sub>A</sub> = V<sub>DD</sub> and V<sub>B</sub> = 0 V. DNL specification limits of  $\pm 1$  LSB maximum are guaranteed monotonic operating conditions.

<sup>&</sup>lt;sup>5</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other. Dual-supply operation enables ground referenced bipolar signal adjustment.

<sup>&</sup>lt;sup>6</sup> Different from operating current; supply current for EEPROM program lasts approximately 30 ms.

<sup>&</sup>lt;sup>7</sup> Different from operating current; supply current for EEPROM read lasts approximately 20 μs.

<sup>&</sup>lt;sup>8</sup>  $P_{DISS}$  is calculated from  $(I_{DD} \times V_{DD}) + (I_{LOGIC} \times V_{LOGIC})$ .

<sup>9</sup> All dynamic characteristics use  $V_{DD} V_{SS} = \pm 2.5 \text{ V}$ , and  $V_{LOGIC} = 2.5 \text{ V}$ .

<sup>10</sup> Endurance is qualified to 100,000 cycles per JEDEC Standard 22, Method A117 and measured at  $-40^{\circ}$ C to  $+125^{\circ}$ C.

<sup>11</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 125°C per JEDEC Standard 22, Method A117. Retention lifetime, based on an activation energy of 1 eV, derates with junction temperature in the Flash/EE memory.

<sup>12 50</sup> years apply to an endurance of 1000 cycles. An endurance of 100,000 cycles has an equivalent retention lifetime of 5 years.

#### INTERFACE TIMING SPECIFICATIONS

$V_{LOGIC}$  = 1.8 V to 5.5 V; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 4.

| Parameter <sup>1</sup>             | Test Conditions/Comments | Min                     | Тур | Max  | Unit | Description                                                                                                                      |

|------------------------------------|--------------------------|-------------------------|-----|------|------|----------------------------------------------------------------------------------------------------------------------------------|

| f <sub>SCL</sub> <sup>2</sup>      | Standard mode            |                         |     | 100  | kHz  | Serial clock frequency                                                                                                           |

|                                    | Fast mode                |                         |     | 400  | kHz  |                                                                                                                                  |

| t <sub>1</sub>                     | Standard mode            | 4.0                     |     |      | μs   | SCL high time, t <sub>HIGH</sub>                                                                                                 |

|                                    | Fast mode                | 0.6                     |     |      | μs   |                                                                                                                                  |

| t <sub>2</sub>                     | Standard mode            | 4.7                     |     |      | μs   | SCL low time, t <sub>LOW</sub>                                                                                                   |

|                                    | Fast mode                | 1.3                     |     |      | μs   |                                                                                                                                  |

| t <sub>3</sub>                     | Standard mode            | 250                     |     |      | ns   | Data setup time, t <sub>su; DAT</sub>                                                                                            |

|                                    | Fast mode                | 100                     |     |      | ns   |                                                                                                                                  |

| t <sub>4</sub>                     | Standard mode            | 0                       |     | 3.45 | μs   | Data hold time, t <sub>HD; DAT</sub>                                                                                             |

|                                    | Fast mode                | 0                       |     | 0.9  | μs   |                                                                                                                                  |

| t <sub>5</sub>                     | Standard mode            | 4.7                     |     |      | μs   | Setup time for a repeated start condition, t <sub>SU; STA</sub>                                                                  |

|                                    | Fast mode                | 0.6                     |     |      | μs   |                                                                                                                                  |

| t <sub>6</sub>                     | Standard mode            | 4                       |     |      | μs   | Hold time (repeated) for a start condition, t <sub>HD; STA</sub>                                                                 |

|                                    | Fast mode                | 0.6                     |     |      | μs   |                                                                                                                                  |

| t <sub>7</sub>                     | Standard mode            | 4.7                     |     |      | μs   | Bus free time between a stop and a start condition, t <sub>BUF</sub>                                                             |

|                                    | Fast mode                | 1.3                     |     |      | μs   |                                                                                                                                  |

| t <sub>8</sub>                     | Standard mode            | 4                       |     |      | μs   | Setup time for a stop condition, t <sub>SU; STO</sub>                                                                            |

|                                    | Fast mode                | 0.6                     |     |      | μs   |                                                                                                                                  |

| t <sub>9</sub>                     | Standard mode            |                         |     | 1000 | ns   | Rise time of SDA signal, t <sub>RDA</sub>                                                                                        |

|                                    | Fast mode                | 20 + 0.1 C <sub>L</sub> |     | 300  | ns   |                                                                                                                                  |

| t <sub>10</sub>                    | Standard mode            |                         |     | 300  | ns   | Fall time of SDA signal, t <sub>FDA</sub>                                                                                        |

|                                    | Fast mode                | 20 + 0.1 C <sub>L</sub> |     | 300  | ns   |                                                                                                                                  |

| t <sub>11</sub>                    | Standard mode            |                         |     | 1000 | ns   | Rise time of SCL signal, t <sub>RCL</sub>                                                                                        |

|                                    | Fast mode                | 20 + 0.1 C <sub>L</sub> |     | 300  | ns   |                                                                                                                                  |

| t <sub>11A</sub>                   | Standard mode            |                         |     | 1000 | ns   | Rise time of SCL signal after a repeated start condition and after an acknowledge bit, t <sub>RCL1</sub> (not shown in Figure 3) |

|                                    | Fast mode                | 20 + 0.1 C <sub>L</sub> |     | 300  | ns   |                                                                                                                                  |

| t <sub>12</sub>                    | Standard mode            |                         |     | 300  | ns   | Fall time of SCL signal, t <sub>FCL</sub>                                                                                        |

|                                    | Fast mode                | 20 + 0.1 C <sub>L</sub> |     | 300  | ns   |                                                                                                                                  |

| t <sub>SP</sub> <sup>3</sup>       | Fast mode                | 0                       |     | 50   | ns   | Pulse width of suppressed spike (not shown in Figure 3)                                                                          |

| t                                  | 0.1                      |                         |     | 10   | μs   | RESET low time (not shown in Figure 3)                                                                                           |

| t <sub>EEPROM_PROGRAM</sub> 4      |                          |                         | 15  | 50   | ms   | Memory program time (not shown in Figure 3)                                                                                      |

| t <sub>EEPROM_READBACK</sub>       |                          |                         | 7   | 30   | μs   | Memory readback time (not shown in Figure 3)                                                                                     |

| t <sub>POWER_UP</sub> <sup>5</sup> |                          |                         |     | 75   | μs   | Power-on EEPROM restore time (not shown in Figure 3)                                                                             |

| t <sub>reset</sub>                 |                          |                         | 30  |      | μs   | Reset EEPROM restore time (not shown in Figure 3)                                                                                |

<sup>&</sup>lt;sup>1</sup> Maximum bus capacitance is limited to 400 pF.

<sup>&</sup>lt;sup>2</sup> The SDA and SCL timing is measured with the input filters enabled. Switching off the input filters improves the transfer rate; however, it has a negative effect on the EMC behavior of the part.

3 Input filtering on the SCL and SDA inputs suppresses noise spikes that are less than 50 ns for fast mode.

4 The EEPROM program time depends on the temperature and EEPROM write cycles. Higher timing is expected at lower temperatures and higher write cycles.

$<sup>^{5}</sup>$  Maximum time after  $V_{\text{DD}} - V_{\text{SS}}$  is equal to 2.3 V.

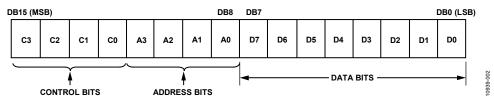

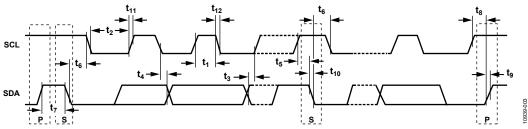

#### **SHIFT REGISTER AND TIMING DIAGRAMS**

Figure 2. Input Shift Register Contents

Figure 3. I<sup>2</sup>C Serial Interface Timing Diagram (Typical Write Sequence)

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

#### Table 5.

| Table 3.                                                 |                                                                                              |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Parameter                                                | Rating                                                                                       |

| V <sub>DD</sub> to GND                                   | -0.3 V to +7.0 V                                                                             |

| V <sub>ss</sub> to GND                                   | +0.3 V to -7.0 V                                                                             |

| $V_{DD}$ to $V_{SS}$                                     | 7 V                                                                                          |

| V <sub>LOGIC</sub> to GND                                | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V or}$<br>+7.0 V (whichever is less)                  |

| $V_A$ , $V_W$ , $V_B$ to GND                             | $V_{SS} - 0.3 \text{ V}, V_{DD} + 0.3 \text{ V} + 7.0 \text{ V} \text{ (whichever is less)}$ |

| $I_A$ , $I_W$ , $I_B$                                    |                                                                                              |

| Pulsed <sup>1</sup>                                      |                                                                                              |

| Frequency > 10 kHz                                       |                                                                                              |

| $R_{AW} = 10 \text{ k}\Omega$                            | $\pm 6 \mathrm{mA/d^2}$                                                                      |

| $R_{AW} = 100 \text{ k}\Omega$                           | ±1.5 mA/d <sup>2</sup>                                                                       |

| Frequency ≤ 10 kHz                                       |                                                                                              |

| $R_{AW} = 10 \text{ k}\Omega$                            | $\pm 6 \text{ mA}/\sqrt{d^2}$                                                                |

| $R_{AW} = 100 \text{ k}\Omega$                           | ±1.5 mA/√d²                                                                                  |

| Digital Inputs                                           | -0.3 V to V <sub>LOGIC</sub> + 0.3 V or<br>+7 V (whichever is less)                          |

| Operating Temperature Range, T <sub>A</sub> <sup>3</sup> | −40°C to +125°C                                                                              |

| Maximum Junction Temperature, $T_J$ Maximum              | 150°C                                                                                        |

| Storage Temperature Range                                | −65°C to +150°C                                                                              |

| Reflow Soldering                                         |                                                                                              |

| Peak Temperature                                         | 260°C                                                                                        |

| Time at Peak Temperature                                 | 20 sec to 40 sec                                                                             |

| Package Power Dissipation                                | $(T_J \max - T_A)/\theta_{JA}$                                                               |

| FICDM                                                    | 1.5 kV                                                                                       |

<sup>&</sup>lt;sup>1</sup> Maximum terminal current is bounded by the maximum current handling of the switches, maximum power dissipation of the package, and maximum applied voltage across any two of the A, B, and W terminals at a given resistance.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{\text{JA}}$  is defined by the JEDEC JESD51 standard, and the value is dependent on the test board and test environment.

**Table 6. Thermal Resistance**

| Package Type  | $\theta_{JA}$      | θ <sub>JC</sub> | Unit |

|---------------|--------------------|-----------------|------|

| 16-Lead LFCSP | 89.5 <sup>1</sup>  | 3               | °C/W |

| 16-Lead TSSOP | 150.4 <sup>1</sup> | 27.6            | °C/W |

<sup>&</sup>lt;sup>1</sup> JEDEC 2S2P test board, still air (0 m/sec airflow).

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> d = pulse duty factor.

<sup>&</sup>lt;sup>3</sup> Includes programming of EEPROM memory.

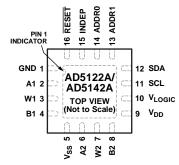

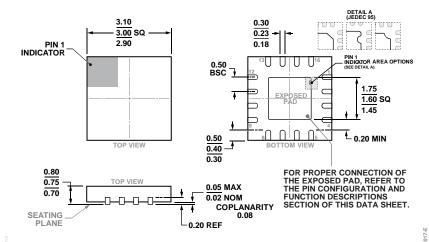

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

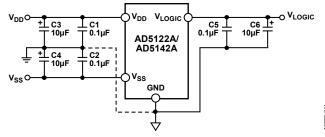

NOTES

1. EXPOSED PAD. CONNECT THE EXPOSED PAD TO THE POTENTIAL OF THE V<sub>SS</sub> PIN, OR, ALTERNATIVELY, LEAVE IT ELECTRICALLY UNCONNECTED. IT IS RECOMMENDED THAT THE PAD BE THERMALLY CONNECTED TO A COPPER PLANE FOR ENHANCED THERMAL PERFORMANCE.

Figure 4. 16-Lead LFCSP Pin Configuration

**Table 7. 16-Lead LFCSP Pin Function Descriptions**

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                 |

|---------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND                | Ground Pin, Logic Ground Reference.                                                                                                                                                                                                         |

| 2       | A1                 | Terminal A of RDAC1. $V_{SS} \le V_A \le V_{DD}$ .                                                                                                                                                                                          |

| 3       | W1                 | Wiper Terminal of RDAC1. $V_{SS} \le V_W \le V_{DD}$ .                                                                                                                                                                                      |

| 4       | B1                 | Terminal B of RDAC1. $V_{SS} \le V_B \le V_{DD}$ .                                                                                                                                                                                          |

| 5       | V <sub>SS</sub>    | Negative Power Supply. Decouple this pin with 0.1 μF ceramic capacitors and 10 μF capacitors.                                                                                                                                               |

| 6       | A2                 | Terminal A of RDAC2. $V_{SS} \le V_A \le V_{DD}$ .                                                                                                                                                                                          |

| 7       | W2                 | Wiper Terminal of RDAC2. $V_{SS} \le V_W \le V_{DD}$ .                                                                                                                                                                                      |

| 8       | B2                 | Terminal B of RDAC2. $V_{SS} \le V_B \le V_{DD}$ .                                                                                                                                                                                          |

| 9       | $V_{\text{DD}}$    | Positive Power Supply. Decouple this pin with 0.1 μF ceramic capacitors and 10 μF capacitors.                                                                                                                                               |

| 10      | V <sub>LOGIC</sub> | Logic Power Supply; 1.8 V to $V_{DD}$ . Decouple this pin with 0.1 $\mu$ F ceramic capacitors and 10 $\mu$ F capacitors.                                                                                                                    |

| 11      | SCL                | Serial Clock Line.                                                                                                                                                                                                                          |

| 12      | SDA                | Serial Data Input/Output.                                                                                                                                                                                                                   |

| 13      | ADDR1              | Programmable Address (ADDR1) for Multiple Package Decoding.                                                                                                                                                                                 |

| 14      | ADDR0              | Programmable Address (ADDR0) for Multiple Package Decoding.                                                                                                                                                                                 |

| 15      | INDEP              | Linear Gain Setting Mode at Power-Up. Each string resistor is loaded from its associated memory location. If INDEP is enabled, it cannot be disabled by the software.                                                                       |

| 16      | RESET              | Hardware Reset Pin. Refresh the RDAC registers from EEPROM. RESET is activated at logic low.  If this pin is not used, tie RESET to VLOGIC.                                                                                                 |

|         | EPAD               | Exposed Pad. Connect this exposed pad to the potential of the $V_{SS}$ pin, or, alternatively, leave it electrically unconnected. It is recommended that the pad be thermally connected to a copper plane for enhanced thermal performance. |

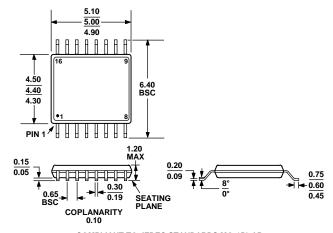

Figure 5. 16-Lead TSSOP Pin Configuration

**Table 8. 16-Lead TSSOP Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                                                                                                                                                                     |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | INDEP           | Linear Gain Setting Mode at Power-Up. Each string resistor is loaded from its associated memory location. If INDEP is enabled, it cannot be disabled by the software.                           |

| 2       | RESET           | Hardware Reset Pin. Refresh the RDAC registers from EEPROM. $\overline{\text{RESET}}$ is activated at logic low. If this pin is not used, tie $\overline{\text{RESET}}$ to $V_{\text{LOGIC}}$ . |

| 3       | GND             | Ground Pin, Logic Ground Reference.                                                                                                                                                             |

| 4       | A1              | Terminal A of RDAC1. $V_{SS} \le V_A \le V_{DD}$ .                                                                                                                                              |

| 5       | W1              | Wiper Terminal of RDAC1. $V_{SS} \le V_W \le V_{DD}$ .                                                                                                                                          |

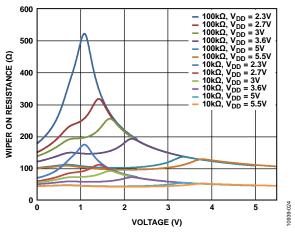

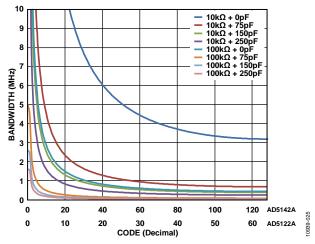

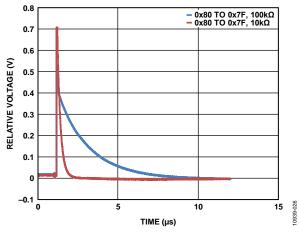

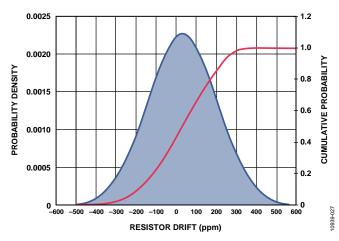

| 6       | B1              | Terminal B of RDAC1. $V_{SS} \le V_B \le V_{DD}$ .                                                                                                                                              |