# Precision, 500 ns Settling BiFET Op Amp

**AD744**

**FEATURES**

**AC PERFORMANCE**

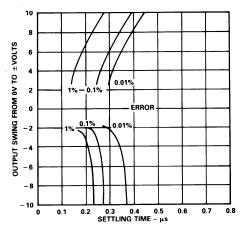

500 ns Settling to 0.01% for 10 V Step

1.5 µs Settling to 0.0025% for 10 V Step

75 V/μs Slew Rate

0.0003% Total Harmonic Distortion (THD)

13 MHz Gain Bandwidth - Internal Compensation

>200 MHz Gain Bandwidth (G = 1000)

**External Decompensation**

>1000 pF Capacitive Load Drive Capability with 10 V/μs Slew Rate – External Compensation

#### **DC PERFORMANCE**

0.5 mV max Offset Voltage (AD744B) 10 μV/°C max Drift (AD744B) 250 V/mV min Open Loop Gain (AD7

250 V/mV min Open-Loop Gain (AD744B)

Available in Plastic Mini-DIP, Plastic SOIC, Hermetic Cerdip, Hermetic Metal Can Packages and Chip Form Surface Mount (SOIC) Package Available in Tape and Reel in Accordance with EIA-481A Standard

#### **APPLICATIONS**

Output Buffers for 12-Bit, 14-Bit and 16-Bit DACs, ADC Buffers, Cable Drivers, Wideband Preamplifiers and Active Filters

#### PRODUCT DESCRIPTION

The AD744 is a fast-settling, precision, FET input, monolithic operational amplifier. It offers the excellent dc characteristics of the AD711 BiFET family with enhanced settling, slew rate, and bandwidth. The AD744 also offers the option of using custom compensation to achieve exceptional capacitive load drive capability.

The single-pole response of the AD744 provides fast settling: 500 ns to 0.01%. This feature, combined with its high dc precision, makes it suitable for use as a buffer amplifier for 12-bit, 14-bit or 16-bit DACs and ADCs. Furthermore, the AD744's low total harmonic distortion (THD) level of 0.0003% and gain bandwidth product of 13 MHz make it an ideal amplifier for demanding audio applications. It is also an excellent choice for use in active filters in 12-bit, 14-bit and 16-bit data acquisition systems.

The AD744 is internally compensated for stable operation as a unity gain inverter or as a noninverting amplifier with a gain of two or greater. External compensation may be applied to the AD744 for stable operation as a unity gain follower. External compensation also allows the AD744 to drive 1000 pF capacitive loads, slewing at  $10~V/\mu s$  with full stability.

Alternatively, external decompensation may be used to increase the gain bandwidth of the AD744 to over 200 MHz at high

#### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

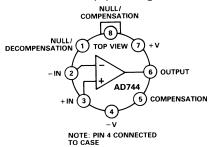

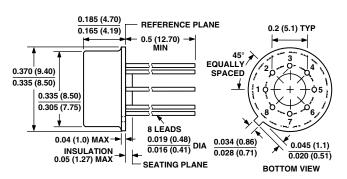

CONNECTION DIAGRAMS TO-99 (H) Package

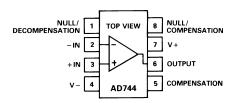

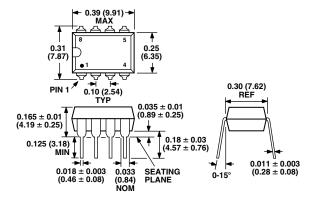

8-Lead Plastic Mini-DIP (N) 8-Lead SOIC (R) Package and 8-Lead Cerdip (Q) Packages

gains. This makes the AD744 ideal for use as ac preamps in digital signal processing (DSP) front ends.

The AD744 is available in five performance grades. The AD744J and AD744K are rated over the commercial temperature range of 0°C to +70°C. The AD744A and AD744B are rated over the industrial temperature range of -40°C to +85°C. The AD744T is rated over the military temperature range of -55°C to +125°C and is available processed to MIL-STD-883B, Rev. C.

The AD744 is available in an 8-lead plastic mini-DIP, 8-lead small outline, 8-lead cerdip or TO-99 metal can.

#### PRODUCT HIGHLIGHTS

- The AD744 is a high-speed BiFET op amp that offers excellent performance at competitive prices. It outperforms the OPA602/OPA606, LF356 and LF400.

- The AD744 offers exceptional dynamic response. It settles to 0.01% in 500 ns and has a 100% tested minimum slew rate of 50 V/μs (AD744B).

- 3. The combination of Analog Devices' advanced processing technology, laser wafer drift trimming and well-matched ionimplanted JFETs provide outstanding dc precision. Input offset voltage, input bias current, and input offset current are specified in the warmed-up condition; all are 100% tested.

# AD744—SPECIFICATIONS (@ $+25^{\circ}$ C and $\pm 15$ V dc, unless otherwise noted)

|                                                                                                                                      |                                                                                                                               | A                     | AD744J/A/S                                             |                                | AI                    | D744K/B/T                                |                                |                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------|--------------------------------|-----------------------|------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------|

| Model                                                                                                                                | Conditions                                                                                                                    | Min                   | Тур                                                    | Max                            | Min                   | Typ                                      | Max                            | Unit                                                                                                             |

| INPUT OFFSET VOLTAGE <sup>1</sup> Initial Offset Offset vs. Temp. vs. Supply <sup>2</sup>                                            | $T_{MIN}$ to $T_{MAX}$                                                                                                        | 82                    | 0.3<br>5<br>95                                         | 1.0<br>2<br>20                 | 88                    | 0.25<br>5<br>100                         | 0.5<br>1.0<br>10               | mV<br>mV<br>μV/°C<br>dB                                                                                          |

| vs. Supply<br>Long-Term Stability                                                                                                    | $T_{MIN}$ to $T_{MAX}$                                                                                                        | 82                    | 15                                                     |                                | 88                    | 15                                       |                                | dB<br>μV/month                                                                                                   |

| INPUT BIAS CURRENT <sup>3</sup> Either Input Either Input @ T <sub>MAX</sub> =                                                       | $V_{CM} = 0 V$ $V_{CM} = 0 V$                                                                                                 |                       | 30                                                     | 100                            |                       | 30                                       | 100                            | pA                                                                                                               |

| J, K A, B, C S, T Either Input Offset Current Offset Current @ T <sub>MAX</sub> =                                                    | 70°C<br>85°C<br>125°C<br>V <sub>CM</sub> = +10 V<br>V <sub>CM</sub> = 0 V<br>V <sub>CM</sub> = 0 V                            |                       | 0.7<br>1.9<br>31<br>40<br>20                           | 2.3<br>6.4<br>102<br>150<br>50 |                       | 0.7<br>1.9<br>31<br>40<br>10             | 2.3<br>6.4<br>102<br>150<br>50 | nA<br>nA<br>nA<br>pA<br>pA                                                                                       |

| J, K<br>A, B, C<br>S, T                                                                                                              | 70°C<br>85°C<br>125°C                                                                                                         |                       | 0.4<br>1.3<br>20                                       | 1.1<br>3.2<br>52               |                       | 0.2<br>0.6<br>10                         | 1.1<br>3.2<br>52               | nA<br>nA<br>nA                                                                                                   |

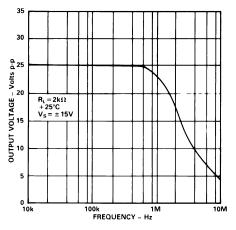

| FREQUENCY RESPONSE Gain BW, Small Signal Full Power Response Slew Rate, Unity Gain Settling Time to 0.01%  Total Harmonic Distortion | G = -1<br>$V_O = 20 \text{ V p-p}$<br>G = -1<br>G = -1<br>f = 1  kHz<br>$R1 \ge 2 \text{ k}\Omega$<br>$V_O = 3 \text{ V rms}$ | 8 45                  | 13<br>1.2<br>75<br>0.5                                 | 0.75                           | 9 50                  | 13<br>1.2<br>75<br>0.5                   | 0.75                           | MHz<br>MHz<br>V/µs<br>µs                                                                                         |

| INPUT IMPEDANCE Differential Common Mode                                                                                             |                                                                                                                               |                       | $3 \times 10^{12} \  5.5$<br>$3 \times 10^{12} \  5.5$ |                                |                       | $3 \times 10^{12}$<br>$3 \times 10^{12}$ | 2  5.5<br>2  5.5               | Ω  pF<br>Ω  pF                                                                                                   |

| INPUT VOLTAGE RANGE Differential <sup>5</sup> Common-Mode Voltage Over Max Operating Range <sup>6</sup> Common-Mode Rejection Ratio  | $V_{CM} = \pm 10 \text{ V}$ $T_{MIN} \text{ to } T_{MAX}$ $V_{CM} = \pm 11 \text{ V}$                                         | -11<br>78<br>76<br>72 | ±20<br>+14.5, -11.5<br>88<br>84<br>84                  | +13                            | -11<br>82<br>80<br>78 | ±20<br>+14.5, -<br>88<br>84<br>84        | ·11.5<br>+13                   | V<br>V<br>V<br>dB<br>dB<br>dB                                                                                    |

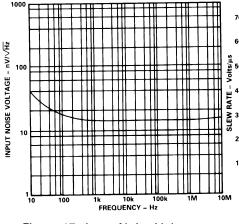

| INPUT VOLTAGE NOISE                                                                                                                  | T <sub>MIN</sub> to T <sub>MAX</sub> 0.1 to 10 Hz f = 10 Hz f = 100 Hz f = 1 kHz f = 10 kHz                                   | 70                    | 80<br>2<br>45<br>22<br>18<br>16                        |                                | 74                    | 80<br>2<br>45<br>22<br>18<br>16          |                                | $\begin{array}{c} dB \\ \mu V \ p-p \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \end{array}$ |

| INPUT CURRENT NOISE                                                                                                                  | f = 1 kHz                                                                                                                     |                       | 0.01                                                   |                                |                       | 0.01                                     |                                | pA/√ <del>Hz</del>                                                                                               |

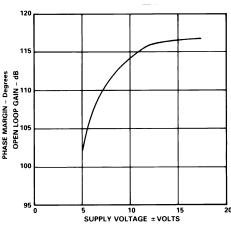

| OPEN LOOP GAIN <sup>7</sup>                                                                                                          | $V_{O} = \pm 10 \text{ V}$ $R_{LOAD} \ge 2 \text{ k}\Omega$ $T_{MIN} \text{ to } T_{MAX}$                                     | 200<br>100            | 400                                                    |                                | 250<br>100            | 400                                      |                                | V/mV<br>V/mV                                                                                                     |

| OUTPUT CHARACTERISTICS Voltage  Current Capacitive Load <sup>8</sup>                                                                 | $\begin{split} R_{LOAD} &\geq 2 \ k\Omega \\ T_{MIN} \ to \ T_{MAX} \\ Short \ Circuit \\ Gain = -1 \end{split}$              | +13, -12.5<br>±12     | +13.9, -13.3<br>+13.8, -13.1<br>25                     | 1000                           | +13, -12.5<br>±12     | +13.9, -<br>+13.8, -<br>25               |                                | V<br>V<br>mA<br>pF                                                                                               |

| POWER SUPPLY Rated Performance Operating Range Quiescent Current                                                                     |                                                                                                                               | ±4.5                  | ±15 3.5                                                | ±18<br>5.0                     | ±4.5                  | ±15                                      | ±18<br>4.0                     | V<br>V<br>mA                                                                                                     |

-2-REV.C

$<sup>^{1}</sup>$ Input offset voltage specifications are guaranteed after 5 minutes of operation at  $T_A$  = +25°C.

<sup>&</sup>lt;sup>2</sup>PSRR test conditions:  $+V_S = 15 \text{ V}$ ,  $-V_S = -12 \text{ V}$  to -18 V and  $+V_S = +12 \text{ V}$  to +18 V,  $-V_S = -15 \text{ V}$ .

<sup>&</sup>lt;sup>3</sup>Bias Current Specifications are guaranteed maximum at either input after 5 minutes of operation at T<sub>A</sub> = +25°C. For higher temperature, the current doubles every 10°C.

<sup>&</sup>lt;sup>4</sup>Gain = -1, R<sub>L</sub> = 2 k, C<sub>L</sub> = 10 pF, refer to Figure 25.

<sup>5</sup>Defined as voltage between inputs, such that neither exceeds ±10 V from ground.

<sup>6</sup>Typically exceeding -14.1 V negative common-mode voltage on either input results in an output phase reversal.

$<sup>^7\</sup>mbox{Open-Loop}$  Gain is specified with  $\mbox{V}_{\mbox{OS}}$  both nulled and unnulled.

<sup>&</sup>lt;sup>8</sup>Capacitive load drive specified for C<sub>COMP</sub> = 20 pF with the device connected as shown in Figure 32. Under these conditions, slew rate = 14 V/µs and 0.01% settling time = 1.5 µs typical. Refer to Table II for optimum compensation while driving a capacitive load.

Specifications subject to change without notice. All min and max specifications are guaranteed.

#### ABSOLUTE MAXIMUM RATINGS1

| Supply Voltage                                     |

|----------------------------------------------------|

| Internal Power Dissipation <sup>2</sup> 500 mW     |

| Input Voltage <sup>3</sup> ±18 V                   |

| Output Short Circuit Duration Indefinite           |

| Differential Input Voltage $+V_S$ and $-V_S$       |

| Storage Temperature Range (Q, H)65°C to +150°C     |

| Storage Temperature Range (N, R)65°C to +125°C     |

| Operating Temperature Range                        |

| AD744J/K0°C to +70°C                               |

| AD744A/B                                           |

| AD744S/T55°C to +125°C                             |

| Lead Temperature Range (Soldering 60 seconds)300°C |

| NOTES                                              |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Thermal Characteristics

8-Lead Plastic Package:  $\theta_{JA} = 100^{\circ}\text{C/Watt}, \, \theta_{JC} = 33^{\circ}\text{C/Watt}$ 8-Lead Cerdip Package:  $\theta_{JA} = 110^{\circ}\text{C/Watt}, \, \theta_{JC} = 22^{\circ}\text{C/Watt}$ 8-Lead Metal Can Package:  $\theta_{JA} = 150^{\circ}\text{C/Watt}, \, \theta_{JC} = 65^{\circ}\text{C/Watt}$ 8-Lead SOIC Package:  $\theta_{JA} = 160^{\circ}\text{C/Watt}, \, \theta_{JC} = 42^{\circ}\text{C/Watt}$ 3-For supply voltages less than  $\pm 18$  V, the absolute maximum input voltage is equal

to the supply voltage.

#### **ORDERING GUIDE**

| Model          | Temperature<br>Range | Package<br>Option* |

|----------------|----------------------|--------------------|

| AD744JN        | 0°C to +70°C         | N-8                |

| AD744KN        | 0°C to +70°C         | N-8                |

| AD744JR        | 0°C to +70°C         | SO-8               |

| AD744KR        | 0°C to +70°C         | SO-8               |

| AD744AQ        | −40°C to +85°C       | Q-8                |

| AD744BQ        | −40°C to +85°C       | Q-8                |

| AD744AH        | –40°C to +85°C       | H-08A              |

| AD744JCHIPS    | 0°C to +70°C         | Die                |

| AD744JR-REEL   | 0°C to +70°C         | Tape/Reel 13"      |

| AD744JR-REEL 7 | 0°C to +70°C         | Tape/Reel 7"       |

| AD744KR-REEL   | 0°C to +70°C         | Tape/Reel 13"      |

| AD744KR-REEL 7 | 0°C to +70°C         | Tape/Reel 7"       |

| AD744TA/883B   | −55°C to +125°C      | H-08               |

<sup>\*</sup>N = Plastic DIP; SO = Small Outline IC; Q = Cerdip; H = TO-99 Metal Can.

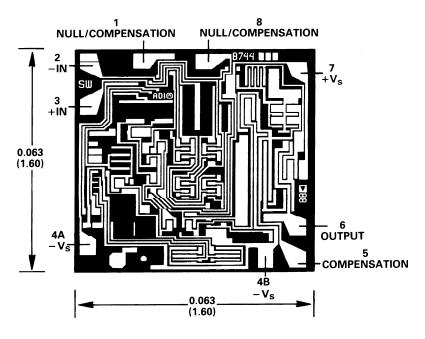

### METALIZATION PHOTOGRAPH

Contact factory for latest dimensions. Dimensions shown in inches and (mm).

REV. C -3-

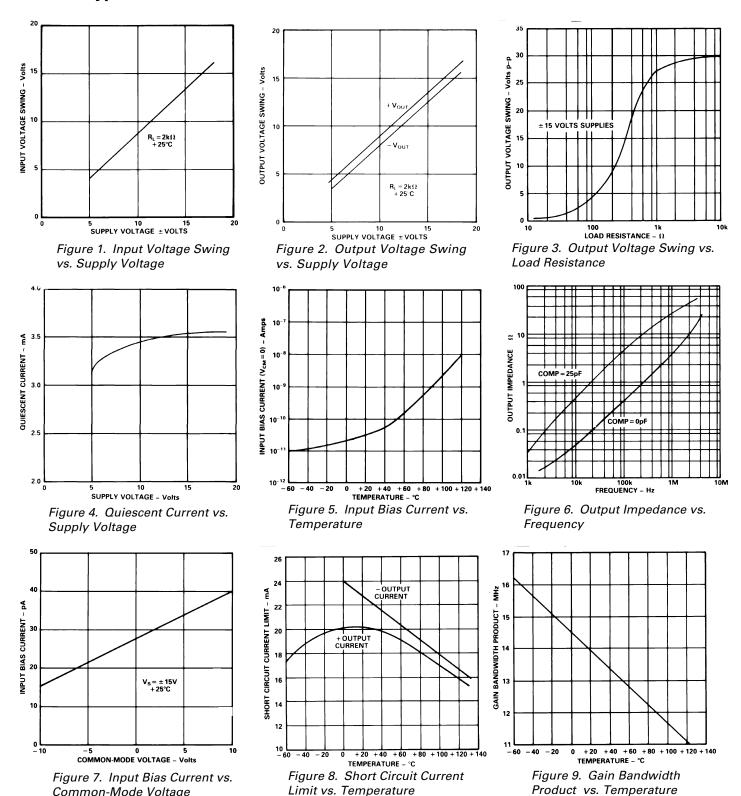

## **AD744**—Typical Characteristics

Common-Mode Voltage

REV. C -4-

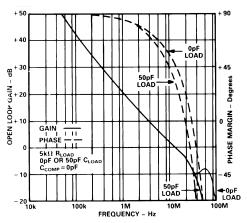

Figure 10. Open-Loop Gain and Phase Margin vs. Frequency  $C_{COMP} = 0$  pF

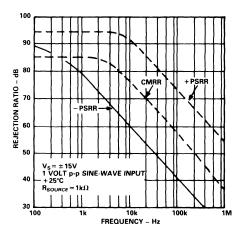

Figure 13. Common-Mode and Power Supply Rejection vs. Frequency

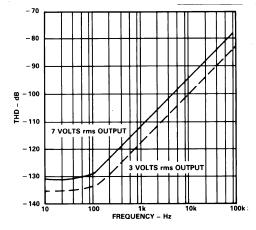

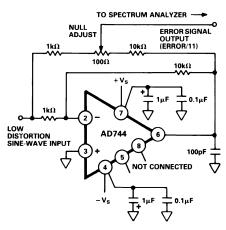

Figure 16. Total Harmonic Distortion vs. Frequency, Circuit of Figure 20 (G = 10)

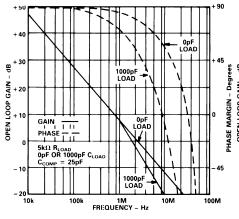

Figure 11. Open Loop Gain and Phase Margin vs. Frequency  $C_{COMP} = 25 \text{ pF}$

Figure 14. Large Signal Frequency Response

Figure 17. Input Noise Voltage Spectral Density

Figure 12. Open-Loop Gain vs. Supply Voltage

Figure 15. Output Swing and Error vs. Settling Time

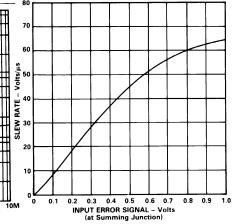

Figure 18. Slew Rate vs. Input Error Signal

## **AD744**—Typical Characteristics

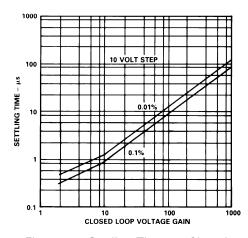

Figure 19. Settling Time vs. Closed Loop Voltage Gain

Figure 20. THD Test Circuit

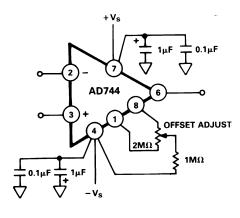

Figure 21. Offset Null Configuration

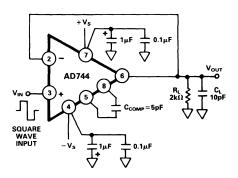

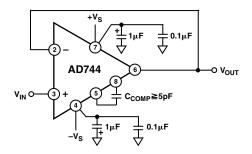

Figure 22a. Unity-Gain Follower

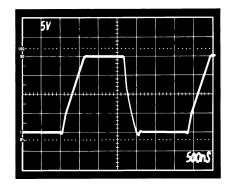

Figure 22b. Unity-Gain Follower Large Signal Pulse Response,  $C_{COMP} = 5 pF$

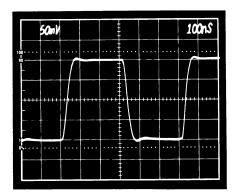

Figure 22c. Unity-Gain Follower Small Signal Pulse Response,  $C_{COMP} = 5 pF$

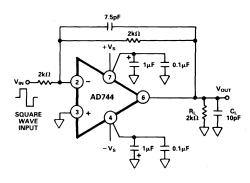

Figure 23a. Unity-Gain Inverter

Figure 23b. Unity-Gain Inverter Large Signal Pulse Response,  $C_{COMP} = 5 pF$

Figure 23c. Unity-Gain Inverter Small Signal Pulse Response,  $C_{COMP} = 0$  pF

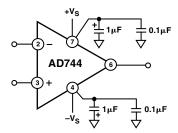

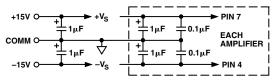

#### POWER SUPPLY BYPASSING

The power supply connections to the AD744 must maintain a low impedance to ground over a bandwidth of 10 MHz or more. This is especially important when driving a significant resistive or capacitive load, since all current delivered to the load comes from the power supplies. Multiple high quality bypass capacitors are recommended for each power supply line in any critical application. A 0.1  $\mu F$  ceramic and a 1  $\mu F$  electrolytic capacitor as shown in Figure 24 placed as close as possible to the amplifier (with short lead lengths to power supply common) will assure adequate high frequency bypassing, in most applications. A minimum bypass capacitance of 0.1  $\mu F$  should be used for any application.

Figure 24. Recommended Power Supply Bypassing

#### **MEASURING AD744 SETTLING TIME**

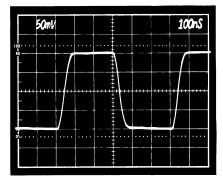

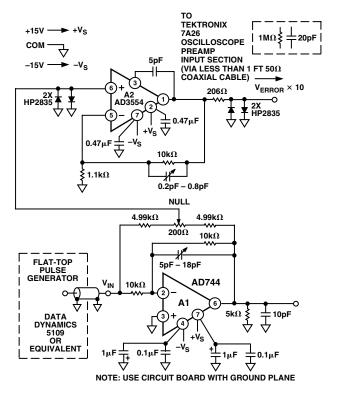

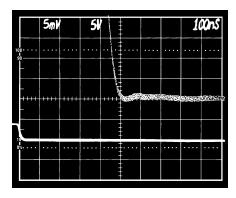

The photos of Figures 26 and 27 show the dynamic response of the AD744 while operating in the settling time test circuit of Figure 25. The input of the settling time fixture is driven by a flat-top pulse generator. The error signal output from the false summing node of A1, the AD744 under test, is clamped, amplified by op amp A2 and then clamped again.

Figure 25. Settling Time Test Circuit

The error signal is thus clamped twice: once to prevent overloading amplifier A2 and then a second time to avoid overloading the oscilloscope preamp. A Tektronix oscilloscope preamp type 7A26 was carefully chosen because it recovers from the approximately 0.4 V overload quickly enough to allow accurate measurement of the AD744's 500 ns settling time. Amplifier A2 is a very high-speed FET-input op amp; it provides a voltage gain of 10, amplifying the error signal output of the AD744 under test.

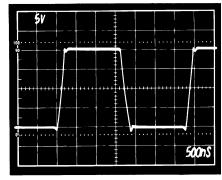

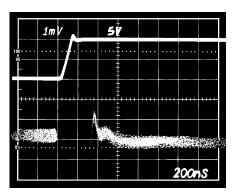

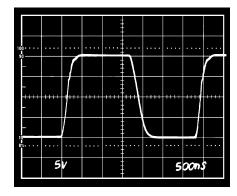

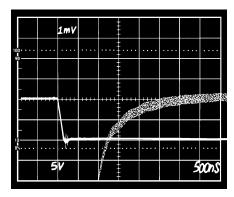

Figure 26. Settling Characteristics 0 to +10 V Step Upper Trace: Output of AD744 Under Test (5 V/div.) Lower Trace: Amplified Error Voltage (0.01%/div.)

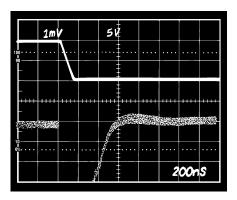

Figure 27. Settling Characteristics 0 to –10 V Step Upper Trace: Output of AD744 Under Test (5 V/div.) Lower Trace: Amplified Error Voltage (0.01%/div.)

REV. C -7-

### **AD744**

#### EXTERNAL FREQUENCY COMPENSATION

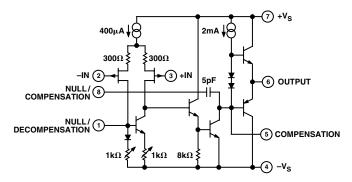

Even though the AD744 is useable without compensation in most applications, it may be externally compensated for even more flexibility. This is accomplished by connecting a capacitor between Pins 5 and 8. Figure 28, a simplified schematic of the AD744, shows where this capacitor is connected. This feature is useful because it allows the AD744 to be used as a unity gain voltage follower. It also enables the amplifier to drive capacitive loads up to 2000 pF and greater.

Figure 28. AD744 Simplified Schematic

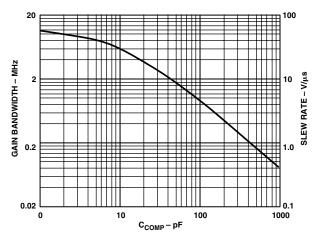

The slew rate and gain bandwidth product of the AD744 are inversely proportional to the value of the compensation capacitor,  $C_{COMP}$ . Therefore, when trying to maximize the speed of the amplifier, the value of  $C_{COMP}$  should be minimized.  $C_{COMP}$  can also be used to slow the amplifier to a point where the slew rate is perfectly symmetrical and well controlled. Figure 29 summarizes the effect of external compensation on slew rate and bandwidth.

Figure 29. Gain Bandwidth and Slew Rate vs. C<sub>COMP</sub>

The following section provides tables to show what  $C_{COMP}$  values will provide the necessary compensation for given circuit configurations and capacitive loads. In each case, the recommended  $C_{COMP}$  is a minimum value. A larger  $C_{COMP}$  can always be used, but slew rate and bandwidth performance will be degraded.

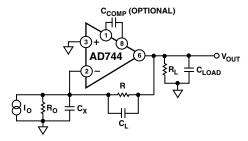

Figure 30 shows the AD744 configured as a unity gain voltage follower. In this case, a minimum compensation capacitor of 5 pF is necessary for stable operation. Larger compensation capacitors can be used for driving larger capacitive loads. Table I outlines recommended minimum values for C<sub>COMP</sub> based on the desired capacitive load. It also gives the slew rate and bandwidth that will be achieved for each case.

Figure 30. AD744 Connected as a Unity Gain Voltage Follower

Table I. Recommended Values of  $C_{\text{COMP}}$  vs. Various Capacitive Loads

| Gain | Max<br>C <sub>LOAD</sub><br>(pF) | C <sub>COMP</sub> (pF) | Slew Rate (V/µs) | -3 dB<br>Bandwidth<br>(MHz) |

|------|----------------------------------|------------------------|------------------|-----------------------------|

| 1    | 50                               | 5                      | 37               | 6.5                         |

| 1    | 150                              | 10                     | 25               | 4.3                         |

| 1    | 2000                             | 25                     | 12.5             | 2.0                         |

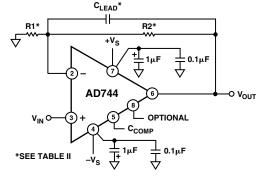

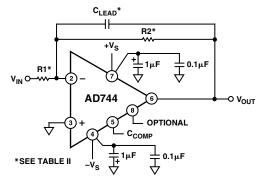

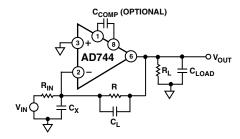

Figures 31 and 32 show the AD744 as a voltage follower with gain and as an inverting amplifier. In these cases, external compensation is not necessary for stable operation. However, compensation may be applied to drive capacitive loads above 50 pF. Table II gives recommended  $C_{\text{COMP}}$  values, along with expected slew rates and bandwidths for a variety of load conditions and gains for the circuits in Figures 31 and 32.

Figure 31. AD744 Connected as a Voltage Follower Operating at Gains of 2 or Greater

-8- REV. C

Table II. Recommended Values of  $C_{COMP}$  vs. Various Load Conditions for the Circuits of Figures 31 and 32.

| R1<br>(Ω)    | R2<br>(Ω) | Gain<br>Follower | Gain<br>Inverter | Max<br>C <sub>LOAD</sub><br>(pF) | C <sub>COMP</sub> (pF) | C <sub>LEAD</sub> (pF) | Slew<br>Rate<br>(V/µs) | -3 dB<br>Bandwidth<br>(MHz) |

|--------------|-----------|------------------|------------------|----------------------------------|------------------------|------------------------|------------------------|-----------------------------|

| 4.99 k       | 4.99 k    | 2                | 1                | 50                               | 0                      | 7                      | 75                     | $2.5^{1}$                   |

| 4.99 k       | 4.99 k    | 2                | 1                | 150                              | 5                      | 7                      | 37                     | $2.3^{1}$                   |

| 4.99 k       | 4.99 k    | 2                | 1                | 1000                             | 20                     | _                      | 14                     | 1.2                         |

| 4.99 k       | 4.99 k    | 2                | 1                | >2000                            | 25                     | _                      | $12.5^{2}$             | 1.0                         |

| $499 \Omega$ | 4.99 k    | 11               | 10               | 270                              | 0                      | _                      | 75                     | 1.2                         |

| $499 \Omega$ | 4.99 k    | 11               | 10               | 390                              | 2                      | _                      | 50                     | 0.85                        |

| $499~\Omega$ | 4.99 k    | 11               | 10               | 1000                             | 5                      | _                      | $37^{2}$               | 0.60                        |

#### NOTES

<sup>&</sup>lt;sup>2</sup>Into large capacitive loads the AD744's 25 mA output current limit sets the slew rate of the amplifier, in V/ $\mu$ s, equal to 0.025 amps divided by the value of  $C_{LOAD}$  in  $\mu$ F. Slew rate is specified into rated max  $C_{LOAD}$  except for cases marked <sup>2</sup>, which are specified with a 50 pF. load.

Figure 32. AD744 Connected as an Inverting Amplifier Operating at Gains of 1 or Greater

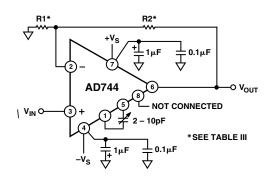

## Using Decompensation to Extend the Gain Bandwidth Product

When the AD744 is used in applications where the closed-loop gain is greater than 10, gain bandwidth product may be enhanced by connecting a small capacitor between Pins 1 and 5 (Figure 33). At low frequencies, this capacitor cancels the effects of the chip's internal compensation capacitor,  $C_{\text{COMP}}$ , effectively decompensating the amplifier.

Due to manufacturing variations in the value of the internal  $C_{COMP}$ , it is recommended that the amplifier's response be optimized for the desired gain by using a 2 to 10 pF trimmer capacitor rather than using a fixed value.

Figure 33. Using the Decompensation Connection to Extend Gain Bandwidth

Table III. Performance Summary for the Circuit of Figure 33

| R1<br>(Ω) | R2<br>(Ω) | Gain<br>Follower | Gain<br>Inverter | -3 dB<br>Bandwidth | Gain/BW<br>Product |

|-----------|-----------|------------------|------------------|--------------------|--------------------|

| 1 k       | 10 k      | 11               | 10               | 2.5 MHz            | 25 MHz             |

| 100       | 10 k      | 101              | 100              | 760 kHz            | 76 MHz             |

| 100       | 100 k     | 1001             | 1000             | 225 kHz            | 225 MHz            |

REV. C -9-

<sup>&</sup>lt;sup>1</sup>Bandwidth with C<sub>LEAD</sub> adjusted for minimum settling time.

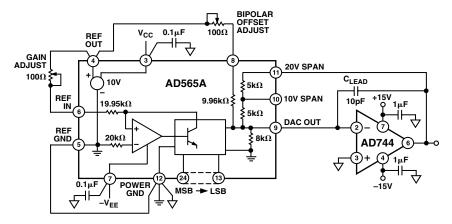

Figure 34. ±10 V Voltage Output Bipolar DAC Using the AD744 as an Output Buffer

# HIGH-SPEED OP AMP APPLICATIONS AND TECHNIQUES

#### DAC Buffers (I-to-V Converters)

Digital-to-analog converters which use bipolar transistors to switch currents into (or out of) their outputs can achieve very fast settling times. The AD565A, for example, is specified to settle to 12 bits in less than 250 ns, with a current output. However, in many applications, a voltage output is desirable, and it would be useful – perhaps essential – that this I-to-V conversion be accomplished without increasing the settling time or without degrading the accuracy of the DAC.

Figure 34 is a schematic of an AD565A DAC using an AD744 output buffer. The 10 pF  $C_{LEAD}$  capacitor compensates for the DAC's output capacitance, plus the 5.5 pF amplifier input capacitance.

Figure 35 is an oscilloscope photo of the AD744's output voltage with a +10 V to 0 V step applied; this corresponds to an all "1s" to all "0s" code change on the DAC. Since the DAC is

Figure 35. Upper Trace: AD744 Output Voltage for a +10 V to 0 V Step, Scale: 5 mV/div. Lower Trace: Logic Input Signal, Scale: 5 V/div.

connected in the 20 V span mode, 1 LSB is equal to 4.88 mV. Output settling time for the AD565/AD744 combination is less than 500 ns to within a 2.44 mV, 1/2 LSB error band.

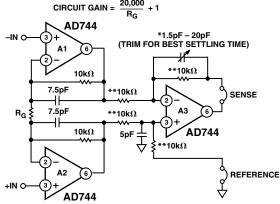

## A HIGH-SPEED, 3 OP AMP INSTRUMENTATION AMPLIFIER CIRCUIT

The instrumentation amplifier circuit shown in Figure 36 can provide a range of gains from unity up to 1000 and higher. The circuit bandwidth is 4 MHz at a gain of 1 and 750 kHz at a gain of 10; settling time for the entire circuit is less than 2  $\mu$ s to within 0.01% for a 10 V step, (G = 10).

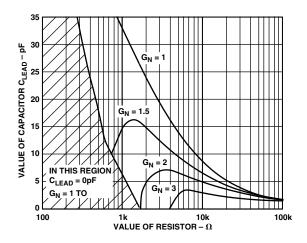

While the AD744 is not stable with 100% negative feedback (as when connected as a standard voltage follower), phase margin and therefore stability at unity gain may be increased to an acceptable level by placing the parallel combination of a resistor and a small lead capacitor between each amplifier's output and its inverting input terminal.

The only penalty associated with this method is a small bandwidth reduction at low gains. The optimum value for  $C_{LEAD}$  may be determined from the graph of Figure 41. This technique can be used in the circuit of Figure 36 to achieve stable operation at gains from unity to over 1000.

\*VOLTRONICS SP20 TRIMMER CAPACITOR OR EQUIVALENT \*\*RATIO MATCHED 1% METAL FILM RESISTORS

FOR OPTIONAL OFFSET ADJUSTMENT: TRIM A1, A3 USING TRIM PROCEDURE SHOWN IN FIGURE 21.

Figure 36. A High Performance, 3 Op Amp Instrumentation Amplifier Circuit

-10- REV. C

Table IV. Performance Summary for the 3 Op Amp Instrumentation Amplifier Circuit

| Gain | RG      | Bandwidth | T Settle (0.01%) |

|------|---------|-----------|------------------|

| 1    | NC      | 3.5 MHz   | 1.5 µs           |

| 2    | 20 kΩ   | 2.5 MHz   | 1.0 µs           |

| 10   | 2.22 kΩ | 1 MHz     | 2 μs             |

| 100  | 202 Ω   | 290 kHz   | 5 μs             |

Figure 37. The Pulse Response of the 3 Op Amp Instrumentation Amplifier. Gain = 1, I Horizontal Scale:  $0.5 \mu V/div.$ , Vertical Scale: 5 V/div. (Gain= 10)

Figure 38. Settling Time of the 3 Op Amp Instrumentation Amplifier. Horizontal Scale: 500 ns/div., Vertical Scale, Pulse Input: 5 V/div., Output Settling: 1 mV/div.

### Minimizing Settling Time in Real-World Applications

An amplifier with a "single pole" or "ideal" integrator open-loop frequency response will achieve the minimum possible settling time for any given unity-gain bandwidth. However, when this "ideal" amplifier is used in a practical circuit, the actual settling time is increased above the minimum value because of added time constants which are introduced due to additional capacitance on the amplifier's summing junction. The following discussion will explain how to minimize this increase in settling time by the selection of the proper value for feedback capacitor,  $C_L$ .

If an op amp is modeled as an ideal integrator with a unity gain crossover frequency, f<sub>0</sub>, Equation 1 will accurately describe the small signal behavior of the circuit of Figure 39. This circuit models an op amp connected as an I-to-V converter.

Equation 1 would completely describe the output of the system if not for the op amp's finite slew rate and other nonlinear effects. Even considering these effects, the fine scale settling to <0.1% will be determined by the op amp's small signal behavior. Equation 1.

$$\frac{V_O}{I_{IN}} = \frac{-R}{\frac{R(C_L + C_X)}{2\pi F_O} s^2 + \left(\frac{G_N}{2\pi F_O} + RC_L\right) s + 1}$$

Where  $F_0$  = the op amp's unity gain crossover frequency

$$G_N =$$

the "noise" gain of the circuit  $\left(1 + \frac{R}{R_O}\right)$

This Equation May Then Be Solved for  $C_L$ : Equation 2.

$$C_{L} = \frac{2 - G_{N}}{R2\pi F_{O}} + \frac{2\sqrt{RC_{X} 2\pi F_{O} + \left(1 - G_{N}\right)}}{R2\pi F_{O}}$$

In these equations, capacitance  $C_X$  is the total capacitance appearing at the inverting terminal of the op amp. When modeling an I-to-V converter application, the Norton equivalent circuit of Figure 39 can be used directly. Capacitance  $C_X$  is the total capacitance of the output of the current source plus the input capacitance of the op amp, which includes any stray capacitance at the op amp's input.

Figure 39. A Simplified Model of the AD744 Used as a Current-to-Voltage Converter

When  $R_O$  and  $I_O$  are replaced with their Thevenin  $V_{\rm IN}$  and  $R_{\rm IN}$  equivalents, the general purpose inverting amplifier model of Figure 40 is created. Here capacitor  $C_X$  represents the input capacitance of the AD744 (5.5 pF) plus any stray capacitance due to wiring and the type of IC package employed.

Figure 40. A Simplified Model of the AD744 Used as an Inverting Amplifier

REV. C –11–

### **AD744**

In either case, the capacitance  $C_X$  causes the system to go from a one-pole to a two-pole response; this additional pole increases settling time by introducing peaking or ringing in the op amp's output. If the value of  $C_X$  can be estimated with reasonable accuracy, Equation 2 can be used to choose the correct value for a small capacitor,  $C_L$ , which will optimize amplifier response. If the value of  $C_X$  is not known,  $C_L$  should be a variable capacitor.

As an aid to the designer, the optimum value of  $C_L$  for one specific amplifier connection can be determined from the graph of Figure 41. This graph has been produced for the case where the AD744 is connected as in Figures 39 and 40 with a practical minimum value for  $C_{STRAY}$  of 2 pF and a total  $C_X$  value of 7.5 pF.

The approximate value of  $C_L$  can be determined for almost any application by solving Equation 2. For example, the AD565/AD744 circuit of Figure 34 constrains all the variables of Equation 2 ( $G_N$  = 3.25, R = 10 k $\Omega$ ,  $F_O$  = 13 MHz, and  $C_X$  = 32.5 pF) Therefore, under these conditions,  $C_L$ = 10.5 pF.

Figure 41. Practical Values of  $C_L$  vs. Resistance of R for Various Amplifier Noise Gains

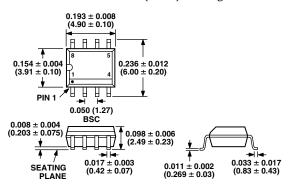

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### TO-99 (H) Package

Mini-DIP (N) Package

#### Cerdip (Q) Package

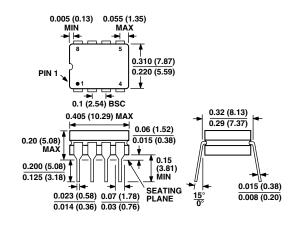

#### Small Outline (SO-8) Package

-12- REV.C

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Precision Amplifiers category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

OPA4187IRUMT

OPA202IDGKT

514327X

561681F

647876R

5962-9080901MCA\*

MAX410CPA

MAX44241AUK+T

LT6230IS6#TR

LT1112S8#TR

OP227GN#PBF

LT6020IDD-1#PBF

LT6023IDD#PBF

LT6013AIDD#PBF

LT6237IMS8#PBF

LT1124CS8#TR

LT1215CS8#TRPBF

ADA4622-1ARZ-R7

NCS21871SQ3T2G

NCS21871SN2T1G

NCV21871SQ3T2G

NCV21871SN2T1G

AD8538WAUJZ-R7

NCS21912DMR2G

TLC27L7CP

TLE2022MD

TLV2473CDR

LT1014DDWR

MCP6V82-EMS

MCP6V92-EMS

MCP6V34-E/ST

MCP6V94-EST

5962-89641012A

5962-8859301M2A

5962-89801012A

5962-9452101M2A

LMC6064IN

LT1013DDR

TL034ACDR

TLC2201AMDG4

TLC274MDRG4

TLE2021QDRG4Q1

TLE2024BMDWG4

AD8691WAUJZ-R7

AD8604ARQZ

TS507IYLT

MAX4238AUT+T

MAX4168EPD

TSZ121ICT