# Quad Input, Five-Output, Dual DPLL Synchronizer and Adaptive Clock Translator

## **Data Sheet**

# AD9542

#### FEATURES

- Dual DPLL synchronizes 2 kHz to 750 MHz physical layer clocks providing frequency translation with jitter cleaning of noisy references

- Complies with ITU-T G.8262 and Telcordia GR-253

- Supports Telcordia GR-1244, ITU-T G.812, G.813, G.823, G.824, and G.825

- Continuous frequency monitoring and reference validation for frequency deviation as low as 50 ppb

- Both DPLLs feature a 24-bit fractional divider with 24-bit programmable modulus

- Programmable digital loop filter bandwidth: 10<sup>-4</sup> Hz to 1850 Hz Automatic and manual holdover and reference switchover,

- providing zero delay, hitless, or phase buildout operation Programmable priority-based reference switching with

- manual, automatic revertive, and automatic nonrevertive modes supported

- 5 pairs of clock output pins with each pair useable as differential LVDS/HCSL/CML or as 2 single-ended outputs (1 Hz to 500 MHz)

- 2 differential or 4 single-ended input references Crosspoint mux interconnects reference inputs to PLLs Supports embedded (modulated) input/output clock signals Fast DPLL locking modes

- Provides internal capability to combine the low phase noise of a crystal resonator or crystal oscillator with the

- frequency stability and accuracy of a TCXO or OCXO External EEPROM support for autonomous initialization Single 1.8 V power supply operation with internal regulation Built in temperature monitor/alarm and temperature

compensation for enhanced zero delay performance

#### APPLICATIONS

SyncE jitter cleanup and synchronization

Optical transport networks (OTN), SDH, and macro and small cell base stations

OTN mapping/demapping with jitter cleaning

Small base station clocking, including baseband and radio Stratum 2, Stratum 3e, and Stratum 3 holdover, jitter

cleanup, and phase transient control

JESD204B support for analog-to-digital converter (ADC) and digital-to-analog converter (DAC) clocking

Cable infrastructures

Carrier Ethernet

#### **GENERAL DESCRIPTION**

The 10 clock outputs of the AD9542 are synchronized to any one of up to four input references. The digital phase-locked loops (DPLLs) reduce timing jitter associated with the external references. The digitally controlled loop and holdover circuitry continuously generate a low jitter output signal, even when all reference inputs fail.

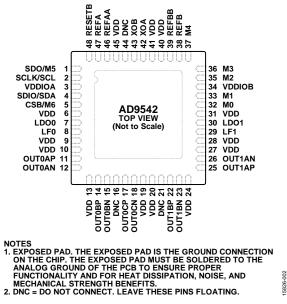

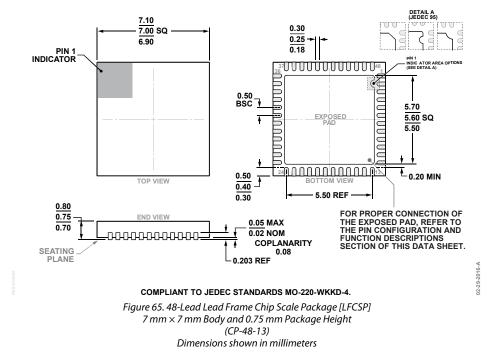

The AD9542 is available in a 48-lead LFCSP (7 mm  $\times$  7 mm) package and operates over the -40 °C to +85 °C temperature range.

Note that throughout this data sheet, multifunction pins, such as SDO/M5, are referred to either by the entire pin name or by a single function of the pin, for example, M5, when only that function is relevant.

Rev. 0

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2017 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features 1                                      |

|-------------------------------------------------|

| Applications                                    |

| General Description                             |

| Revision History                                |

| Functional Block Diagram                        |

| Specifications                                  |

| Supply Voltage 5                                |

| Supply Current                                  |

| Power Dissipation                               |

| System Clock Inputs, XOA and XOB6               |

| Reference Inputs7                               |

| Reference Monitors                              |

| DPLL Phase Characteristics                      |

| Distribution Clock Outputs9                     |

| Time Duration of Digital Functions10            |

| Digital PLL (DPLL0, DPLL1) Specifications       |

| Digital PLL Lock Detection Specifications11     |

| Holdover Specifications11                       |

| Analog PLL (APLL0, APLL1) Specifications11      |

| Output Channel Divider Specifications11         |

| System Clock Compensation Specifications12      |

| Temperature Sensor Specifications               |

| Serial Port Specifications12                    |

| Logic Input Specifications (RESETB, M0 to M6)14 |

| Logic Output Specifications (M0 to M6)14        |

| Jitter Generation (Random Jitter)14             |

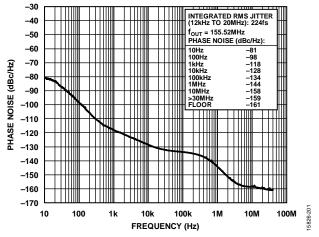

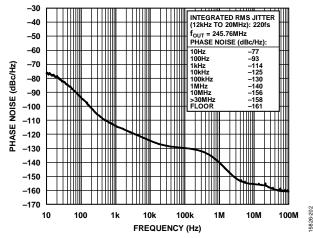

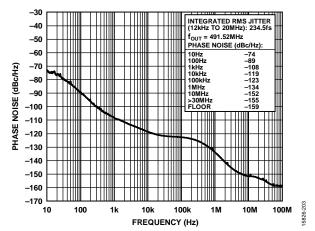

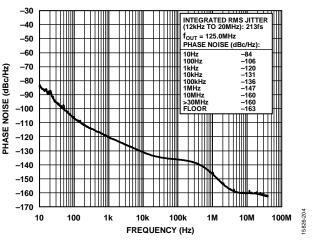

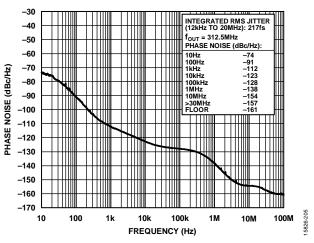

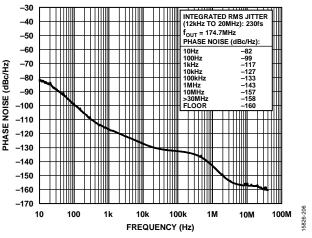

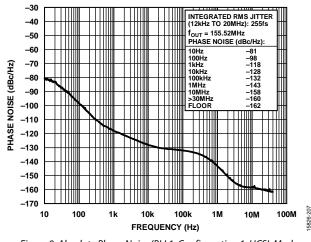

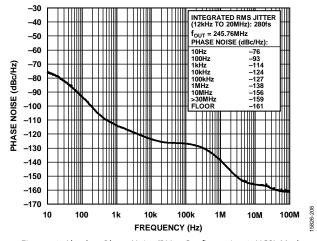

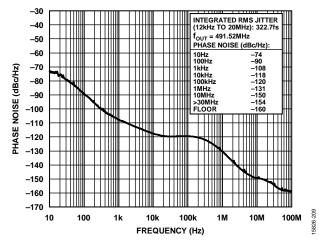

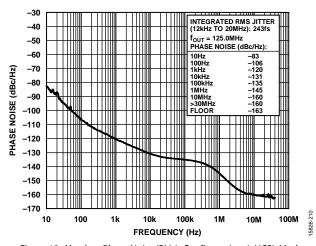

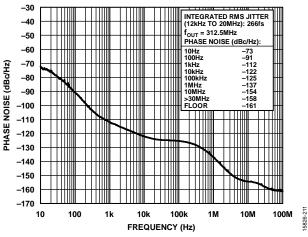

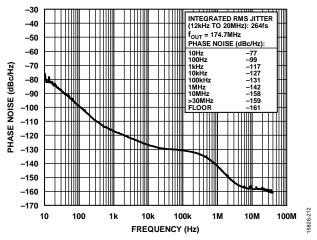

| Phase Noise15                                   |

| Absolute Maximum Ratings                        |

| Thermal Resistance                              |

| ESD Caution                                     |

| Pin Configuration and Function Descriptions19   |

| Typical Performance Characteristics             |

| Terminology25                                   |

| Theory of Operation                             |

| Overview                                        |

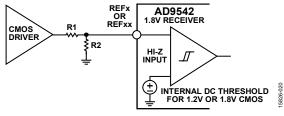

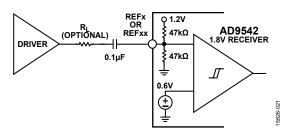

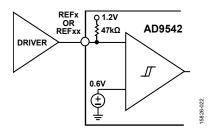

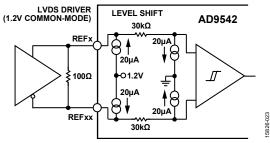

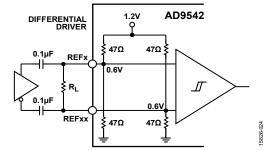

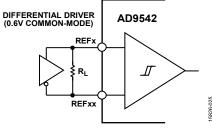

| Reference Input Physical Connections            |

| Input/Output Termination Recommendations        |

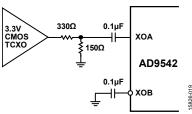

| System Clock Inputs27                           |

| Reference Clock Inputs                          |

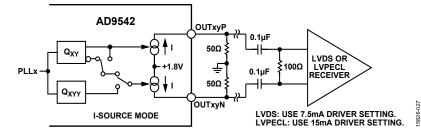

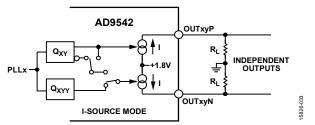

| Clock Outputs                                   |

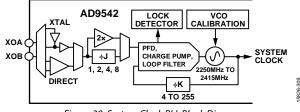

| System Clock PLL                               |

|------------------------------------------------|

| System Clock Input Frequency Declaration       |

| System Clock Source                            |

| 2× Frequency Multiplier                        |

| Prescale Divider                               |

| Feedback Divider                               |

| System Clock PLL Output Frequency              |

| System Clock PLL Lock Detector                 |

| System Clock Stability Timer                   |

| System Clock Input Termination Recommendations |

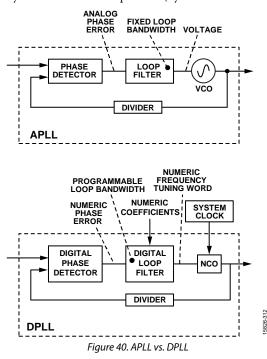

| Digital PLL (DPLL)                             |

| Overview                                       |

| DPLL Phase/Frequency Lock Detectors            |

| DPLL Loop Controller                           |

| Applications Information                       |

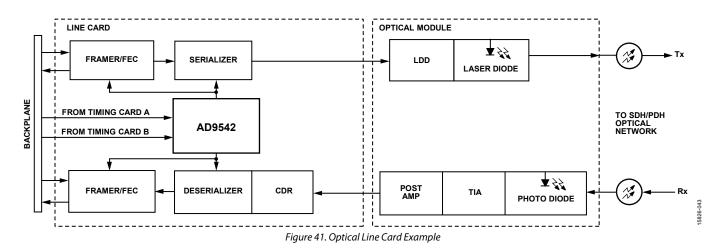

| Optical Networking Line Card 32                |

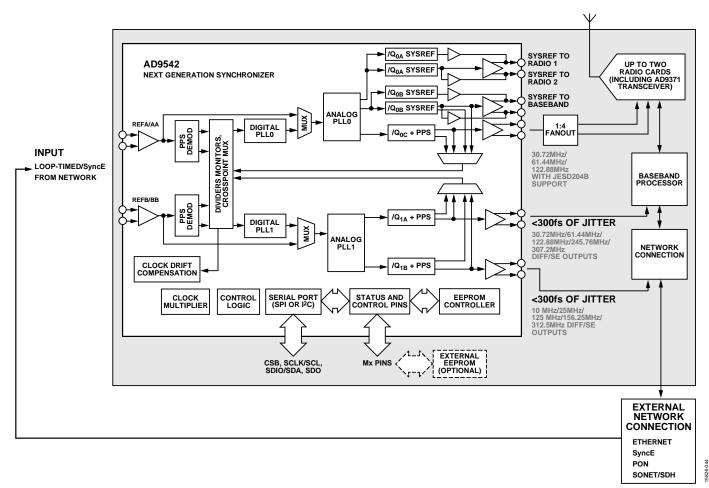

| Small Cell Base Station                        |

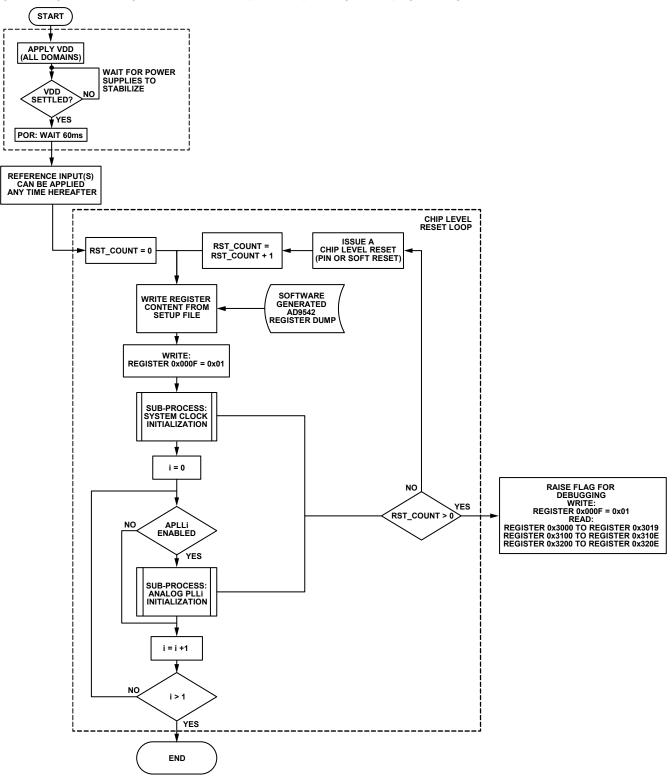

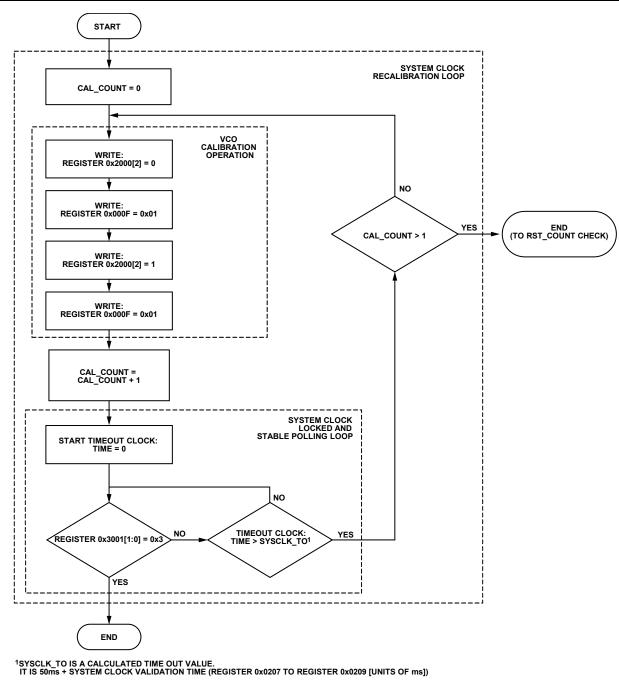

| Initialization Sequence                        |

| Status and Control Pins                        |

| Multifunction Pins at Reset/Power-Up           |

| Status Functionality                           |

| Control Functionality                          |

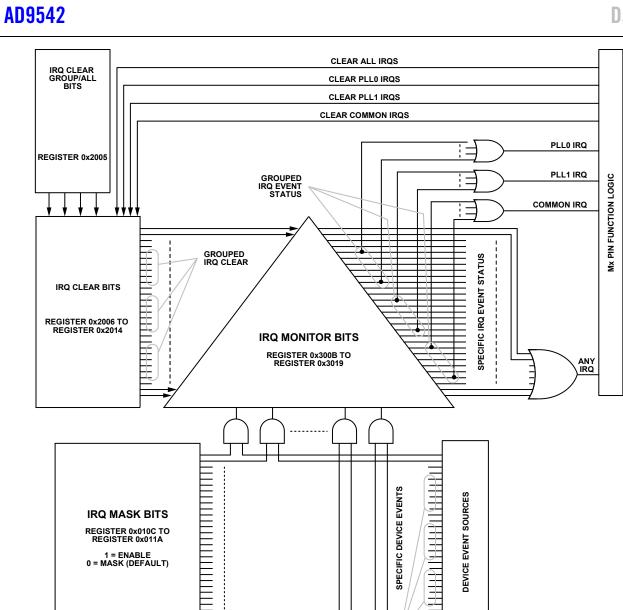

| Interrupt Request (IRQ)                        |

| IRQ Monitor                                    |

| IRQ Mask                                       |

| IRQ Clear                                      |

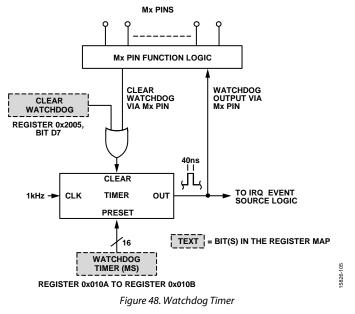

| Watchdog Timer 45                              |

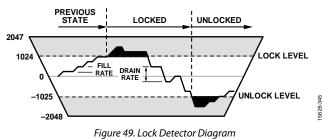

| Lock Detectors                                 |

| DPLL Lock Detectors                            |

| Phase Step Detector                            |

| Phase Step Limit                               |

| Skew Adjustment 49                             |

| EEPROM Usage 50                                |

| Overview 50                                    |

| EEPROM Controller General Operation 50         |

| EEPROM Instruction Set 51                      |

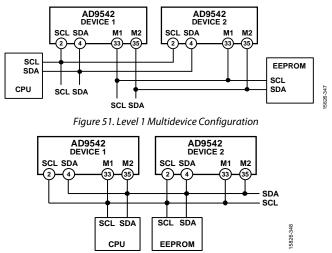

| Multidevice Support                            |

| Serial Control Port 55                         |

| SPI/I <sup>2</sup> C Port Selection55          |

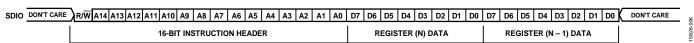

| SPI Serial Port Operation                      |

| Data Sheet                               | AD9542           |

|------------------------------------------|------------------|

| I <sup>2</sup> C Serial Port Operation58 | Ordering Guide61 |

| Outline Dimensions61                     |                  |

#### **REVISION HISTORY**

9/2017—Revision 0: Initial Version

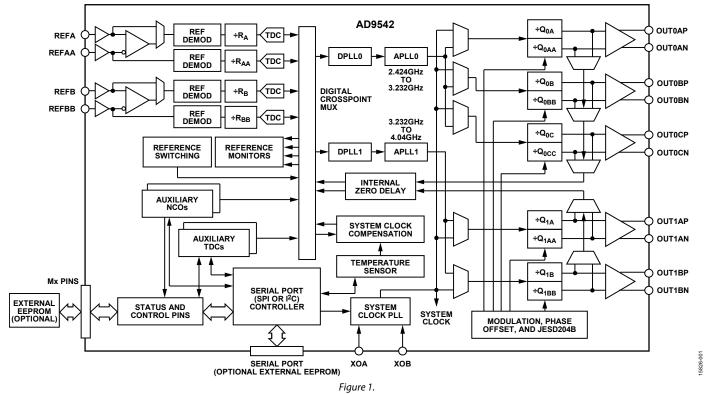

# FUNCTIONAL BLOCK DIAGRAM

## **SPECIFICATIONS**

The minimum and maximum values apply for the full range of supply voltage and operating temperature variations. The typical values apply for VDD = 1.8 V and  $T_A = 25$ °C, unless otherwise noted.

### SUPPLY VOLTAGE

Table 1.

| Parameter      | Min  | Тур | Max   | Unit | Test Conditions/Comments                    |

|----------------|------|-----|-------|------|---------------------------------------------|

| SUPPLY VOLTAGE |      |     |       |      |                                             |

| VDDIOA, VDDIOB | 1.71 | 1.8 | 3.465 | V    | 1.8 V, 2.5 V, and 3.3 V operation supported |

| VDD            | 1.71 | 1.8 | 1.89  | V    |                                             |

#### SUPPLY CURRENT

The maximum supply voltage values given in Table 1 are the basis for the maximum supply current specifications. The typical supply voltage values given in Table 1 are the basis for the typical supply current specifications. The minimum supply voltage values given in Table 1 are the basis for the minimum supply current specifications.

| Parameter                                              | Min | Тур | Max | Unit | Test Conditions/Comments                                                                             |

|--------------------------------------------------------|-----|-----|-----|------|------------------------------------------------------------------------------------------------------|

| SUPPLY CURRENT FOR TYPICAL<br>CONFIGURATION            |     | .76 |     |      | The Typical Configuration specification in Table 3 is the basis for the values shown in this section |

| I <sub>VDDIOx</sub>                                    |     | 5   | 8   | mA   | Aggregate current for all VDDIOx pins (where $x = A$ or B)                                           |

| I <sub>VDD</sub>                                       | 260 | 310 | 355 | mA   | Aggregate current for all VDD pins                                                                   |

| SUPPLY CURRENT FOR ALL BLOCKS<br>RUNNING CONFIGURATION |     |     |     |      | The All Blocks Running condition in Table 3 is the basis for the values shown in this section        |

| I <sub>VDDIOx</sub>                                    |     | 5   | 8   | mA   | Aggregate current for all VDDIOx pins (where $x = A$ or B)                                           |

| I <sub>VDD</sub>                                       | 321 | 390 | 430 | mA   | Aggregate current for all VDD pins                                                                   |

#### **POWER DISSIPATION**

The typical values apply for VDD = 1.8 V, and the maximum values apply for VDD = 1.89 V.

| Table | 3. |

|-------|----|

|       |    |

| Parameter                     | Min | Тур | Max | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                                             |

|-------------------------------|-----|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER DISSIPATION             |     |     |     |      |                                                                                                                                                                                                                                                                                                                                      |

| Typical Configuration         | 445 | 560 | 671 | mW   | System clock = 49.152 MHz crystal; two DPLLs active;<br>two 19.44 MHz input references in differential mode;<br>two ac-coupled PLL0 CML output drivers at 245.76 MHz;<br>and 2 PLL1 CML output drivers at 156.25 MHz                                                                                                                 |

| All Blocks Running            | 548 | 700 | 813 | mW   | System clock = 49.152 MHz crystal; two DPLLs active;<br>two 19.44 MHz input references in differential mode;<br>3 ac-coupled PLL0 HCSL output drivers at 400 MHz; and<br>two PLL1 HCSL output drivers at 400 MHz                                                                                                                     |

| Full Power-Down               |     | 125 |     | mW   | Based on the Typical Configuration specification with the power down all bit set to Logic 1                                                                                                                                                                                                                                          |

| Incremental Power Dissipation |     |     |     |      | Based on the Typical Configuration specification; the values in this section indicate the change in power due to the indicated operation relative to the Typical Configuration specification                                                                                                                                         |

| Complete DPLL/APLL On/Off     |     | 200 |     | mW   | Change in dissipated power relative to the Typical Configuration specification; the blocks, powered down, consist of 1 reference input, 1 DPLL, 1 APLL, 2 channel dividers, and 2 output drivers                                                                                                                                     |

| Incremental Power Dissipation |     |     |     |      |                                                                                                                                                                                                                                                                                                                                      |

| Complete DPLL/APLL On/Off     |     | 200 |     | mW   | Based on the Typical Configuration specification; the values in<br>this section indicate the change in power due to the indicated<br>operation relative to the Typical Configuration specification;<br>the blocks, powered down, consist of one reference input, one<br>DPLL, one APLL, two channel dividers, and two output drivers |

| Parameter                         | Min | Тур | Max | Unit | Test Conditions/Comments     |  |

|-----------------------------------|-----|-----|-----|------|------------------------------|--|

| Input Reference On/Off            |     |     |     |      |                              |  |

| Differential (Normal Mode)        |     | 20  |     | mW   | f <sub>REF</sub> = 19.44 MHz |  |

| Differential (DC-Coupled LVDS)    |     | 21  |     | mW   | f <sub>REF</sub> = 19.44 MHz |  |

| Single-Ended                      |     | 13  |     | mW   | f <sub>REF</sub> = 19.44 MHz |  |

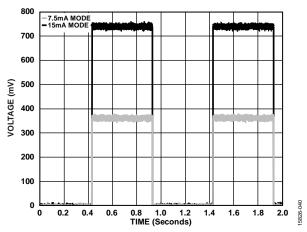

| Output Distribution Driver On/Off |     |     |     |      | At 156.25 MHz                |  |

| 15 mA Mode                        |     | 30  |     | mW   |                              |  |

| 12 mA Mode                        |     | 23  |     | mW   |                              |  |

| 7.5 mA Mode                       |     | 15  |     | mW   |                              |  |

| Auxiliary DPLL On/Off             |     | 1   |     | mW   |                              |  |

#### SYSTEM CLOCK INPUTS, XOA AND XOB

| Parameter                                                                                | Min  | Тур  | Max  | Unit   | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------|------|------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM CLOCK MULTIPLIER                                                                  |      |      |      |        |                                                                                                                                                                                                                                                                                                                                           |

| Output Frequency Range                                                                   | 2250 |      | 2415 | MHz    | The frequency range of the internal voltage controlled<br>oscillator (VCO) places limits on the choice of the system<br>clock input frequency                                                                                                                                                                                             |

| Phase Frequency Detector (PFD) Rate                                                      | 20   |      | 300  | MHz    |                                                                                                                                                                                                                                                                                                                                           |

| SYSTEM CLOCK REFERENCE INPUT PATH<br>Input Frequency Range<br>System Clock Input Doubler |      |      |      |        | System clock input must be ac-coupled                                                                                                                                                                                                                                                                                                     |

| Disabled                                                                                 | 20   |      | 300  | MHz    | Support of oven controlled crystal oscillators (OCXOs) < 20 MHz is possible using the auxiliary DPLL for system clock frequency compensation                                                                                                                                                                                              |

| Enabled                                                                                  | 16   |      | 150  | MHz    |                                                                                                                                                                                                                                                                                                                                           |

| Self Biased Common-Mode Voltage<br>Input Voltage                                         |      | 0.75 |      | V      | Internally generated                                                                                                                                                                                                                                                                                                                      |

| High                                                                                     | 0.9  |      |      | V      | For dc-coupled, single-ended operation                                                                                                                                                                                                                                                                                                    |

| Low                                                                                      |      |      | 0.5  | V      | For dc-coupled, single-ended operation                                                                                                                                                                                                                                                                                                    |

| Differential Input Voltage Sensitivity                                                   | 250  |      |      | mV p-p | Minimum voltage swing required (as measured with a differential probe) across the XOA/XOB pins to ensure switching between logic states; the instantaneous voltage on either pin must not exceed 1.2 V; accommodate the single-ended input by ac grounding the complementary input; 800 mV p-p recommended for optimal jitter performance |

| Slew Rate for Sinusoidal Input                                                           | 50   |      |      | V/µs   | Minimum input slew rate for device operation; oscillators<br>with square wave outputs are recommended if not using a<br>crystal                                                                                                                                                                                                           |

| System Clock Input Divider<br>(J Divider) Frequency                                      | 100  |      |      | MHz    |                                                                                                                                                                                                                                                                                                                                           |

| System Clock Input Doubler<br>Duty Cycle                                                 |      |      |      |        | Tolerable duty cycle variation on the system clock input when using the frequency doubler                                                                                                                                                                                                                                                 |

| 20 MHz to 150 MHz                                                                        | 43   | 50   | 57   | %      |                                                                                                                                                                                                                                                                                                                                           |

| 16 MHz to 20 MHz                                                                         | 47   | 50   | 53   | %      |                                                                                                                                                                                                                                                                                                                                           |

| Input Resistance                                                                         |      | 5    |      | kΩ     |                                                                                                                                                                                                                                                                                                                                           |

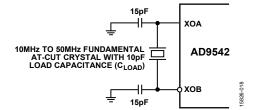

| QUARTZ CRYSTAL RESONATOR PATH                                                            |      |      |      |        |                                                                                                                                                                                                                                                                                                                                           |

| Resonator Frequency Range                                                                | 25   |      | 60   | MHz    | Fundamental mode, AT cut crystal                                                                                                                                                                                                                                                                                                          |

| Crystal Motional Resistance                                                              |      |      | 100  | Ω      | A maximum motional resistance of 50 $\Omega$ , and maximum C_{LOAD} of 8 pF is strongly recommended for crystals >52 MHz                                                                                                                                                                                                                  |

## **REFERENCE INPUTS**

### Table 5.

| Parameter                                           | Min                        | Тур  | Max                   | Unit   | Test Conditions/Comments                                                                                                                                                                                        |

|-----------------------------------------------------|----------------------------|------|-----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIFFERENTIAL MODE                                   |                            |      |                       |        | Differential mode specifications assume ac coupling of the input signal to the reference input pins                                                                                                             |

| Frequency Range                                     |                            |      |                       |        |                                                                                                                                                                                                                 |

| Sinusoidal Input                                    |                            |      | 750                   | MHz    | Lower limit dependent on input slew rate                                                                                                                                                                        |

| LVPECL Input                                        | 2000                       |      | $750 \times 10^{6}$   | Hz     | Lower limit dependent on ac coupling                                                                                                                                                                            |

| LVDS Input                                          | 2000                       |      | 500 × 10 <sup>6</sup> | Hz     | Assumes an LVDS minimum of 494 mV p-p differential amplitude; lower limit dependent on ac coupling                                                                                                              |

| Slew Rate for Sinusoidal input                      | 20                         |      |                       | V/µs   | Minimum input slew rate for device operation; jitter degradation may occur for slew rates < 35 V/µs                                                                                                             |

| Common-Mode Input Voltage                           |                            | 0.64 |                       | V      | Internally generated self bias voltage                                                                                                                                                                          |

| Differential Input Amplitude                        |                            |      |                       |        | Peak-to-peak differential voltage swing across pins<br>required to ensure switching between logic levels as<br>measured with a differential probe; instantaneous<br>voltage on either pin must not exceed 1.3 V |

| f <sub>IN</sub> < 500 MHz                           | 350                        |      | 2100                  | mV p-p |                                                                                                                                                                                                                 |

| $f_{IN} = 500 \text{ MHz}$ to 750 MHz               | 500                        |      | 2100                  | mV p-p |                                                                                                                                                                                                                 |

| Differential Input Voltage Hysteresis               |                            | 55   | 100                   | mV     |                                                                                                                                                                                                                 |

| Input Resistance                                    |                            | 16   |                       | kΩ     | Equivalent differential input resistance                                                                                                                                                                        |

| Input Pulse Width                                   |                            |      |                       |        |                                                                                                                                                                                                                 |

| LVPECL                                              | 600                        |      |                       | ps     |                                                                                                                                                                                                                 |

| LVDS                                                | 900                        |      |                       | ps     |                                                                                                                                                                                                                 |

| DC-COUPLED, LVDS-COMPATIBLE<br>MODE                 |                            |      |                       |        | Applies for dc-coupling to an LVDS source                                                                                                                                                                       |

| Frequency Range                                     | 2000                       |      | $450 \times 10^{6}$   | Hz     |                                                                                                                                                                                                                 |

| Common-Mode Input Voltage                           | 1.125                      |      | 1.375                 | V      |                                                                                                                                                                                                                 |

| Differential Input Amplitude                        | 400                        |      | 1200                  | mV p-p | Differential voltage across pins required to ensure<br>switching between logic levels; instantaneous<br>voltage on either pin must not exceed the supply rails                                                  |

| Differential Input Voltage Hysteresis               |                            | 55   | 100                   | mV     |                                                                                                                                                                                                                 |

| Input Resistance                                    |                            | 16   |                       | kΩ     |                                                                                                                                                                                                                 |

| Input Pulse Width                                   | 1                          |      |                       | ns     |                                                                                                                                                                                                                 |

| SINGLE-ENDED MODE                                   |                            |      |                       |        | Single-ended mode specifications assume dc<br>coupling of the input signal to the reference input<br>pins                                                                                                       |

| Frequency Range                                     |                            |      |                       |        |                                                                                                                                                                                                                 |

| 1.2 V AC-Coupled                                    | 2000                       |      | $500 \times 10^{6}$   | Hz     | Lower limit dependent on ac-coupling                                                                                                                                                                            |

| 1.2 V and 1.8 V CMOS                                | 2000                       |      | $500 \times 10^{6}$   | Hz     | CMOS specifications assume dc coupling of the input signal to the reference input pins                                                                                                                          |

| 1.2 V AC-Coupled Common-Mode<br>Voltage             |                            | 610  |                       | mV     | Internally generated self-bias voltage                                                                                                                                                                          |

| Input Amplitude (Single-Ended,<br>AC-Coupled Mode)  | 360                        |      | 1200                  | mV p-p | Peak-to-peak single-ended voltage swing;<br>instantaneous voltage must not exceed 1.3 V                                                                                                                         |

| 1.2 V and 1.8 V CMOS Input<br>Voltage               |                            |      |                       |        |                                                                                                                                                                                                                 |

| High, V <sub>IH</sub>                               | 0.65 ×<br>V <sub>REF</sub> |      | $1.15 \times V_{REF}$ | V      | $V_{\text{REF}}$ is determined by operating mode of the CMOS input receiver, 1.2 V or 1.8 V                                                                                                                     |

| Low, V <sub>IL</sub>                                |                            |      | $0.35 \times V_{REF}$ | V      |                                                                                                                                                                                                                 |

| Input Resistance<br>DC-Coupled Single-Ended<br>Mode |                            | 30   |                       | kΩ     |                                                                                                                                                                                                                 |

| Mode<br>AC-Coupled Single-Ended<br>Mode             |                            | 15   |                       | kΩ     |                                                                                                                                                                                                                 |

|                                                     |                            |      |                       | 1      |                                                                                                                                                                                                                 |

### **REFERENCE MONITORS**

#### Table 6.

| Parameter                           | Min                  | Тур                                | Max   | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                       |

|-------------------------------------|----------------------|------------------------------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCE MONITORS                  |                      |                                    |       |      |                                                                                                                                                                                                                                                                                |

| Reference Monitor                   |                      |                                    |       |      |                                                                                                                                                                                                                                                                                |

| Loss of Reference<br>Detection Time |                      | $4.9 + 0.13 \times t_{\text{PFD}}$ |       | μs   | $t_{PFD}$ is the nominal phase detector period, R/f_{REF}, where R is the frequency division factor determined by the R divider, and $f_{REF}$ is the frequency of the active reference                                                                                        |

| Frequency Out of<br>Range Limits    | 5 × 10 <sup>-8</sup> |                                    | 0.015 | ppb  | Parts per billion (ppb) is defined as $\Delta f/f_{REF}$ , where $\Delta f$ is the frequency deviation, and $f_{REF}$ is the reference input frequency; programmable with the lower bound, subject to quality of the system clock (or the source of system clock compensation) |

| Validation Timer                    | 0.001                |                                    | 1048  | sec  | Programmable in 1 ms increments                                                                                                                                                                                                                                                |

| Excess Jitter Alarm Threshold       | 1                    |                                    | 65535 | ns   | Programmable in 1 ns increments                                                                                                                                                                                                                                                |

## **DPLL PHASE CHARACTERISTICS**

| Parameter                            | Min   | Тур | Мах  | Unit   | Test Conditions/Comments                                                                                                                                                                                                                                                  |

|--------------------------------------|-------|-----|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAXIMUM OUTPUT PHASE<br>PERTURBATION |       |     |      |        | Assumes a jitter free reference; satisfies Telcordia GR-1244-CORE<br>requirements; 0 ppm frequency difference between references;<br>reference switch initiated via register map (see the AD9542 Register<br>Map Reference Manual) by faulting the active reference input |

| Phase Refinement Disabled            |       |     |      |        | 50 Hz DPLL loop bandwidth; normal phase margin mode; frequency translation = 19.44 MHz to 155.52 MHz; 49.152 MHz signal generator used for system clock source                                                                                                            |

| Peak                                 |       | ±20 | ±140 | ps     |                                                                                                                                                                                                                                                                           |

| Steady State                         |       |     |      |        |                                                                                                                                                                                                                                                                           |

| Phase Buildout Operation             |       | ±18 | ±125 | ps     |                                                                                                                                                                                                                                                                           |

| Hitless Operation                    |       | 0   |      | ps     |                                                                                                                                                                                                                                                                           |

| Phase Refinement Enabled             |       |     |      |        | 50 Hz DPLL loop bandwidth; high phase margin mode; phase<br>refinement iterations = 4; frequency translation = 19.44 MHz to<br>155.52 MHz; 49.152 MHz signal generator used for system clock source                                                                       |

| Peak                                 |       | ±5  | ±40  | ps     |                                                                                                                                                                                                                                                                           |

| Steady State                         |       |     |      |        |                                                                                                                                                                                                                                                                           |

| Phase Buildout Operation             |       | ±4  | ±35  | ps     |                                                                                                                                                                                                                                                                           |

| Hitless Operation                    |       | 0   |      | ps     |                                                                                                                                                                                                                                                                           |

| PHASE SLEW LIMITER                   | 0.001 |     | 250  | µs/sec | See the AN-1420 Application Note, Phase Buildout and Hitless<br>Switchover with Digital Phase-Locked Loops (DPLLs)                                                                                                                                                        |

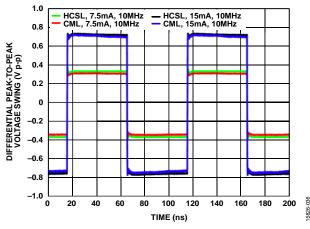

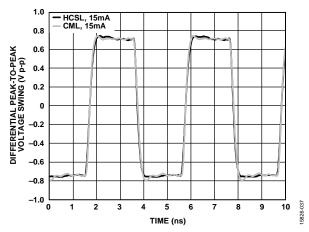

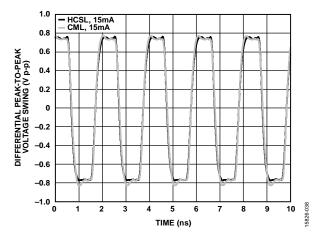

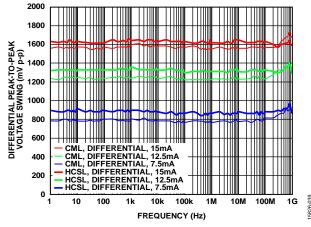

## DISTRIBUTION CLOCK OUTPUTS

#### Table 8.

| Parameter                                             | Min       | Тур       | Max                   | Unit | Test Conditions/Comments                                                                                                                                                                                |

|-------------------------------------------------------|-----------|-----------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIFFERENTIAL MODE                                     |           |           |                       |      | All testing is both ac-coupled and dc-coupled                                                                                                                                                           |

| Output Frequency                                      |           |           |                       |      | Frequency range determined by driver<br>functionality; actual frequency synthesis may be<br>limited by the APLL VCO frequency range                                                                     |

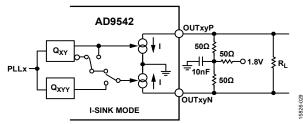

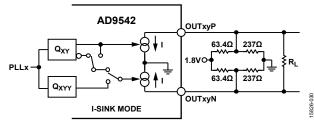

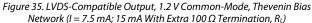

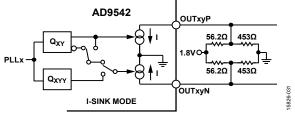

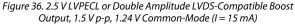

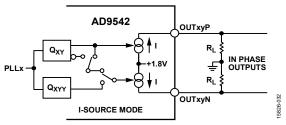

| CML                                                   | 1         |           | $500 \times 10^{6}$   | Hz   | Terminated per Figure 33                                                                                                                                                                                |

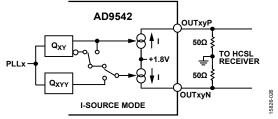

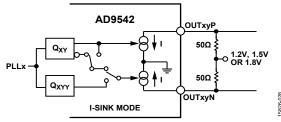

| HCSL                                                  | 1         |           | $500 \times 10^{6}$   | Hz   | Terminated per Figure 32                                                                                                                                                                                |

| Differential Output Voltage Swing                     |           |           |                       |      | Voltage between output pins measured with<br>output driver static; peak-to-peak differential<br>output amplitude is twice that shown when driver<br>is toggling and measured using a differential probe |

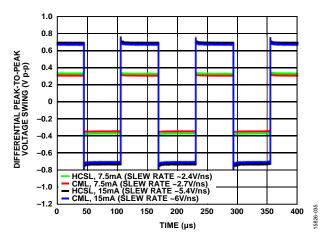

| Output Current = 7.5 mA                               |           |           |                       |      |                                                                                                                                                                                                         |

| HCSL                                                  | 312       | 368       | 402                   | mV   | Terminated per Figure 32                                                                                                                                                                                |

| CML                                                   | 257       | 348       | 408                   | mV   | Terminated to VDD (nominal 1.8 V) per Figure 33                                                                                                                                                         |

| Output Current = 15 mA                                |           |           |                       |      |                                                                                                                                                                                                         |

| HCSL                                                  | 631       | 745       | 809                   | mV   | Terminated per Figure 32                                                                                                                                                                                |

| CML                                                   | 578       | 729       | 818                   | mV   | Terminated to VDD (nominal 1.8V) per Figure 33                                                                                                                                                          |

| Common-Mode Output Voltage<br>Output Current = 7.5 mA |           |           |                       |      |                                                                                                                                                                                                         |

| HCSL                                                  | 155       | 184       | 201                   | mV   | Terminated per Figure 32                                                                                                                                                                                |

| CML                                                   | VDD – 208 | VDD – 188 | VDD – 169             | mV   | Terminated to VDD (nominal 1.8 V) per Figure 33                                                                                                                                                         |

|                                                       | VDD - 208 | VDD - 188 | VDD - 109             | IIIV | (maximum common-mode voltage case occurs at<br>the minimum amplitude)                                                                                                                                   |

| Output Current = 15 mA                                |           |           |                       |      |                                                                                                                                                                                                         |

| HCSL                                                  | 316       | 372       | 405                   | mV   | Terminated per Figure 32                                                                                                                                                                                |

| CML                                                   | VDD – 416 | VDD – 371 | VDD – 327             | mV   | Terminated to VDD (nominal 1.8V) per Figure 33<br>(maximum common-mode voltage case occurs at<br>the minimum amplitude)                                                                                 |

| SINGLE-ENDED MODE                                     | 1         |           |                       |      | · · ·                                                                                                                                                                                                   |

| Output Frequency                                      | 1         |           | 500 × 10 <sup>6</sup> | Hz   | Frequency range determined by driver<br>functionality; actual frequency synthesis may be<br>limited by the APLL VCO frequency range                                                                     |

| Output Current = 12 mA                                |           |           |                       |      |                                                                                                                                                                                                         |

| Voltage Swing (Peak-to-Peak)                          |           |           |                       |      |                                                                                                                                                                                                         |

| HCSL Driver Mode                                      | 509       | 584       | 634                   | mV   | Each output terminated per Figure 37 with $R_L = 50 \Omega$                                                                                                                                             |

| CML Driver Mode                                       | 456       | 565       | 644                   | mV   | Each output terminated per Figure 37 with $R_L = 50 \Omega$ connected to VDD (nominal 1.8 V) instead of GND                                                                                             |

| Voltage Swing Midpoint                                |           |           |                       |      |                                                                                                                                                                                                         |

| HCSL Driver Mode                                      | 255       | 292       | 317                   | mV   | Each output terminated per Figure 37 with $R_L = 50 \Omega$                                                                                                                                             |

| CML Driver Mode                                       | VDD – 325 | VDD – 291 | VDD – 266             | mV   | Each output terminated per Figure 37 with $R_L = 50 \Omega$ connected to VDD (nominal 1.8 V) instead of GND                                                                                             |

| Output Current = 15 mA                                |           |           |                       |      |                                                                                                                                                                                                         |

| Voltage Swing (Peak-to-Peak)                          |           |           |                       |      |                                                                                                                                                                                                         |

| HCSL Driver Mode                                      | 645       | 734       | 796                   | mV   | Each output terminated per Figure 37 with $R_{\!_L}{=}50\Omega$                                                                                                                                         |

| CML Driver Mode                                       | 589       | 721       | 815                   | mV   | Each output terminated per Figure 37 with $R_L = 50 \Omega$ connected to VDD (nominal 1.8 V) instead of GND                                                                                             |

| Voltage Swing Midpoint                                |           |           |                       |      |                                                                                                                                                                                                         |

| HCSL Driver Mode                                      | 322       | 367       | 398                   | mV   | Each output terminated per Figure 37 with $R_L$ = 50 $\Omega$                                                                                                                                           |

| CML Driver Mode                                       | VDD – 411 | VDD – 367 | VDD - 334             | mV   | Each output terminated per Figure 37 with $R_L = 50 \Omega$ connected to VDD (nominal 1.8 V) instead of GND                                                                                             |

## TIME DURATION OF DIGITAL FUNCTIONS

#### Table 9.

| Parameter                                                                | Min | Тур | Max | Unit             | Test Conditions/Comments                                                                                                                                                                                                              |

|--------------------------------------------------------------------------|-----|-----|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIME DURATION OF DIGITAL<br>FUNCTIONS                                    |     |     |     |                  |                                                                                                                                                                                                                                       |

| EEPROM to Register Download<br>Time                                      |     | 10  |     | ms               | Using the Typical Configuration from Table 3                                                                                                                                                                                          |

| Power-On Reset (POR)                                                     |     |     | 25  | ms               | Time from power supplies > 80% to release of internal reset                                                                                                                                                                           |

| Mx Pin to RESETB Rising Edge<br>Setup Time                               |     |     | 1   | ns               | Mx refers to Pin M0 through Pin M6                                                                                                                                                                                                    |

| Mx Pin to RESETB Rising Edge<br>Hold Time                                |     |     | 2   | ns               |                                                                                                                                                                                                                                       |

| Multiple Mx Pin Timing Skew                                              |     |     | 39  | ns               | Applies only to multibit Mx pin functions                                                                                                                                                                                             |

| RESETB Falling Edge to Mx Pin<br>High-Z Time                             |     |     | 14  | ns               |                                                                                                                                                                                                                                       |

| TIME FROM START OF DPLL<br>ACTIVATION TO ACTIVE PHASE<br>DETECTOR OUTPUT |     |     |     |                  |                                                                                                                                                                                                                                       |

| Untagged Operation                                                       |     |     | 10  | t <sub>PFD</sub> | $t_{\mbox{\tiny PFD}}$ is the nominal phase detector period given by R/f_{\mbox{\tiny REF}} where R is the frequency division factor determined by the R divider, and $f_{\mbox{\tiny REF}}$ is the frequency of the active reference |

| Tagged Operation                                                         |     |     | 10  | Tag<br>period    | Tag period = (tag ratio/ $f_{TAG}$ ), where $f_{TAG}$ is either $f_{REF}$ (for tagged reference mode) or $f_{FEEDBACK}$ (for all other tagged modes); the tag ratio corresponds to the selection of $f_{TAG}$                         |

## DIGITAL PLL (DPLL0, DPLL1) SPECIFICATIONS

#### Table 10.

| Parameter                                             | Min    | Тур  | Max   | Unit    | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------|--------|------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL PLL                                           |        |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Digital Phase Detector (DPD)<br>Input Frequency Range | 1      |      | 2×10⁵ | Hz      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Loop Filter                                           |        |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Profile 0                                             |        |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bandwidth                                             | 0.0001 |      | 1850  | Hz      | Programmable design parameter; $(f_{PFD}/bandwidth) \ge 20$                                                                                                                                                                                                                                                                                                                                                                                                       |

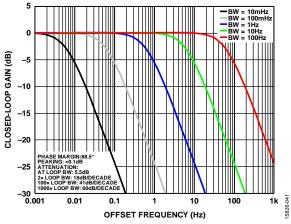

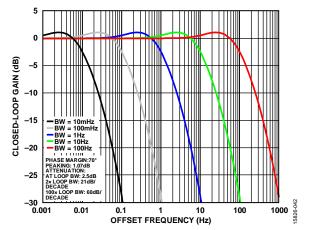

| Phase Margin                                          |        | 70   |       | Degrees |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Closed-Loop Peaking                                   |        | 1.1  |       | dB      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Profile 1                                             |        |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bandwidth                                             | 0.0001 |      | 305   | Hz      | Programmable design parameter; $(f_{PFD}/bandwidth) \ge 20$                                                                                                                                                                                                                                                                                                                                                                                                       |

| Phase Margin                                          |        | 88.5 |       | Degrees |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Closed-Loop Peaking                                   |        |      | 0.1   | dB      | In accordance with Telcordia GR-253-CORE jitter transfer specifications                                                                                                                                                                                                                                                                                                                                                                                           |

| DIGITAL PLL NCO Division Ratio                        |        |      |       |         | These specifications cover limitations on the DPLLx frequency<br>tuning word (FTW0); the AD9542 evaluation software frequency<br>planning wizard sets these values automatically for the user, and<br>the AD9542 evaluation software is available for download from<br>the AD9542 product page at www.analog.com/AD9542; NCO<br>division = $2^{48}$ /FTW0, which takes the form INT.FRAC, where INT is<br>the integer portion, and FRAC is the fractional portion |

| NCO Integer                                           | 7      |      | 13    |         | This is the integer portion of NCO division                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NCO Fraction                                          | 0.05   |      | 0.95  |         | This is the fractional portion of NCO division                                                                                                                                                                                                                                                                                                                                                                                                                    |

## DIGITAL PLL LOCK DETECTION SPECIFICATIONS

#### Table 11.

| Parameter                   | Min | Тур | Max                 | Unit | Test Conditions/Comments                         |

|-----------------------------|-----|-----|---------------------|------|--------------------------------------------------|

| PHASE LOCK DETECTOR         |     |     |                     |      |                                                  |

| Threshold Programming Range | 10  |     | 2 <sup>24</sup> – 1 | ps   |                                                  |

| Threshold Resolution        |     | 1   |                     | ps   |                                                  |

| FREQUENCY LOCK DETECTOR     |     |     |                     |      |                                                  |

| Threshold Programming Range | 10  |     | 2 <sup>24</sup> – 1 | ps   |                                                  |

| Threshold Resolution        |     | 1   |                     | ps   |                                                  |

| PHASE STEP DETECTOR         |     |     |                     |      |                                                  |

| Threshold Programming Range | 100 |     | 2 <sup>32</sup> – 1 | ps   | Setting this value too low causes false triggers |

| Threshold Resolution        |     | 1   |                     | ps   |                                                  |

#### HOLDOVER SPECIFICATIONS

Table 12.

| Parameter                                       | Min   | Тур   | Max    | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------|-------|-------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLDOVER SPECIFICATIONS                         |       |       |        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Initial Frequency Accuracy                      |       | ±0.01 | ±0.1   | ррb  | AD9542 is configured using Configuration 1 from Table 21;<br>excludes frequency drift of system clock (SYSCLK) source;<br>excludes frequency drift of input reference prior to<br>entering holdover; 160 ms history timer; history holdoff<br>setting of 8; three holdover history features (bits) are<br>enabled: delay history until frequency lock bit, delay<br>history until phase lock bit, and delay holdover history<br>accumulation until not phase slew limited bit |

| Relative Frequency Accuracy<br>Between Channels |       |       |        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cascaded Operation                              |       | 0     |        | ppb  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| History Averaging Window                        | 0.001 |       | 268435 | sec  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## ANALOG PLL (APLL0, APLL1) SPECIFICATIONS

| Table 13.                                            |      |     |      |         |

|------------------------------------------------------|------|-----|------|---------|

| Parameter                                            | Min  | Тур | Max  | Unit    |

| VCO FREQUENCY RANGE                                  |      |     |      |         |

| Analog PLL0 (APLL0)                                  | 2424 |     | 3232 | MHz     |

| Analog PLL1 (APLL1)                                  | 3232 |     | 4040 | MHz     |

| PHASE FREQUENCY DETECTOR (PFD) INPUT FREQUENCY RANGE | 162  |     | 350  | MHz     |

| LOOP BANDWIDTH                                       |      | 260 |      | kHz     |

| PHASE MARGIN                                         |      | 68  |      | Degrees |

#### **OUTPUT CHANNEL DIVIDER SPECIFICATIONS**

Table 14.

| Parameter                     | Min | Тур | Max | Unit             | Test Conditions/Comments                             |

|-------------------------------|-----|-----|-----|------------------|------------------------------------------------------|

| OUTPUT PHASE ADJUST STEP SIZE | 1   |     |     | t <sub>vco</sub> | $t_{VCO} = 1/(APLLx VCO frequency)$ , where x = 0, 1 |

### SYSTEM CLOCK COMPENSATION SPECIFICATIONS

| Parameter                                 | Min | Тур   | Max               | Unit | <b>Test Conditions/Comments</b>        |

|-------------------------------------------|-----|-------|-------------------|------|----------------------------------------|

| DIRECT COMPENSATION                       |     |       |                   |      |                                        |

| Resolution                                |     | 0.028 |                   | ppt  | ppt is parts per trillion $(10^{-12})$ |

| CLOSED-LOOP COMPENSATION (AUXILIARY DPLL) |     |       |                   |      |                                        |

| Phase Detector Frequency                  | 2   |       | 200               | kHz  |                                        |

| Loop Bandwidth                            | 0.1 |       | $2 \times 10^{3}$ | Hz   |                                        |

| Reference Monitor Threshold               |     | 5     |                   | %    |                                        |

#### **TEMPERATURE SENSOR SPECIFICATIONS**

| Parameter       | Min Typ | Max | Unit | Test Conditions/Comments                         |

|-----------------|---------|-----|------|--------------------------------------------------|

| TEMPERATURE     |         |     |      |                                                  |

| Accuracy        |         |     |      |                                                  |

| Absolute        | 5       |     | °C   | $T_{A} = -50^{\circ}C \text{ to } +110^{\circ}C$ |