# ANALOG Polyphase Multifunction Energy Metering IC DEVICES with Harmonic and Fundamental Information with Harmonic and Fundamental Information

Data Sheet

# ADE7854/ADE7858/ADE7868/ADE7878

### **FEATURES**

Highly accurate; supports EN 50470-1, EN 50470-3, IEC 62053-21, IEC 62053-22, and IEC 62053-23 standards Compatible with 3-phase, 3- or 4-wire (delta or wye), and other 3-phase services

Supplies total (fundamental and harmonic) active, reactive (ADE7878, ADE7868, and ADE7858 only), and apparent energy, and fundamental active/reactive energy (ADE7878 only) on each phase and on the overall system

Less than 0.1% error in active and reactive energy over a dynamic range of 1000 to 1 at  $T_A = 25$ °C

Less than 0.2% error in active and reactive energy over a dynamic range of 3000 to 1 at  $T_A = 25$ °C

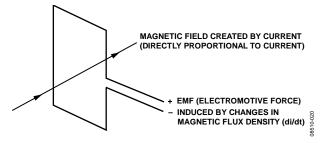

Supports current transformer and di/dt current sensors Dedicated ADC channel for neutral current input (ADE7868 and ADE7878 only)

Less than 0.1% error in voltage and current rms over a dynamic range of 1000 to 1 at  $T_A = 25$ °C

Supplies sampled waveform data on all three phases and on neutral current

Selectable no load threshold levels for total and fundamental active and reactive powers, as well as for apparent powers

Low power battery mode monitors phase currents for antitampering detection (ADE7868 and ADE7878 only)

Battery supply input for missing neutral operation Phase angle measurements in both current and voltage channels with a typical 0.3° error

Wide-supply voltage operation: 2.4 V to 3.7 V Reference: 1.2 V (drift ±5 ppm/°C typical) with external overdrive capability

Single 3.3 V supply

40-lead lead frame chip scale package (LFCSP), Pb-free Operating temperature: -40°C to +85°C Flexible I2C, SPI, and HSDC serial interfaces

### **APPLICATIONS**

**Energy metering systems**

### **GENERAL DESCRIPTION**

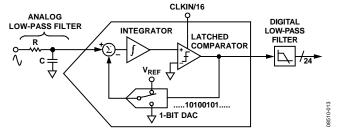

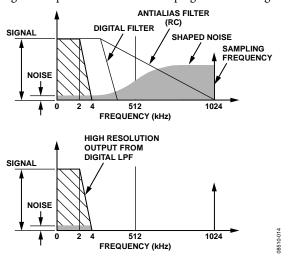

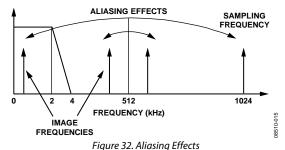

The ADE7854/ADE7858/ADE7868/ADE7878 are high accuracy, 3-phase electrical energy measurement ICs with serial interfaces and three flexible pulse outputs. The ADE78xx devices incorporate second-order sigma-delta  $(\Sigma - \Delta)$  analog-to-digital converters (ADCs), a digital integrator, reference circuitry, and all of the signal processing required to perform total (fundamental and

harmonic) active, reactive (ADE7878, ADE7868, and ADE7858), and apparent energy measurement and rms calculations, as well as fundamental-only active and reactive energy measurement (ADE7878) and rms calculations. A fixed function digital signal processor (DSP) executes this signal processing. The DSP program is stored in the internal ROM memory.

The ADE7854/ADE7858/ADE7868/ADE7878 are suitable for measuring active, reactive, and apparent energy in various 3-phase configurations, such as wye or delta services, with both three and four wires. The ADE78xx devices provide system calibration features for each phase, that is, rms offset correction, phase calibration, and gain calibration. The CF1, CF2, and CF3 logic outputs provide a wide choice of power information: total active, reactive, and apparent powers, or the sum of the current rms values, and fundamental active and reactive powers.

The ADE7854/ADE7858/ADE7868/ADE7878 contain waveform sample registers that allow access to all ADC outputs. The devices also incorporate power quality measurements, such as short duration low or high voltage detections, short duration high current variations, line voltage period measurement, and angles between phase voltages and currents. Two serial interfaces, SPI and I<sup>2</sup>C, can be used to communicate with the ADE78xx. A dedicated high speed interface, the high speed data capture (HSDC) port, can be used in conjunction with I<sup>2</sup>C to provide access to the ADC outputs and real-time power information. The ADE7854/ADE7858/ADE7868/ADE7878 also have two interrupt request pins, IRQ0 and IRQ1, to indicate that an enabled interrupt event has occurred. For the ADE7868/ADE7878, three specially designed low power modes ensure the continuity of energy accumulation when the ADE7868/ADE7878 is in a tampering situation. See Table 1 for a quick reference chart listing each part and its functions. The ADE78xx are available in the 40-lead LFCSP, Pb-free package.

**Table 1. Part Comparison**

| Part No. | WATT | VAR | IRMS,<br>VRMS,<br>and<br>VA | di/dt | Fundamental<br>WATT and<br>VAR | Tamper<br>Detect and<br>Low Power<br>Modes |

|----------|------|-----|-----------------------------|-------|--------------------------------|--------------------------------------------|

| ADE7878  | Yes  | Yes | Yes                         | Yes   | Yes                            | Yes                                        |

| ADE7868  | Yes  | Yes | Yes                         | Yes   | No                             | Yes                                        |

| ADE7858  | Yes  | Yes | Yes                         | Yes   | No                             | No                                         |

| ADE7854  | Yes  | No  | Yes                         | Yes   | No                             | No                                         |

# **Data Sheet**

## ADE7854/ADE7858/ADE7868/ADE7878

## **TABLE OF CONTENTS**

| Features                                        | 1    |

|-------------------------------------------------|------|

| Applications                                    | 1    |

| General Description                             | 1    |

| Revision History                                | 3    |

| Functional Block Diagrams                       | 5    |

| Specifications                                  | 9    |

| Timing Characteristics                          | . 12 |

| Absolute Maximum Ratings                        | . 15 |

| Thermal Resistance                              | . 15 |

| ESD Caution                                     | . 15 |

| Pin Configuration and Function Descriptions     | . 16 |

| Typical Performance Characteristics             | . 18 |

| Test Circuit                                    | . 21 |

| Terminology                                     | . 22 |

| Power Management                                | . 23 |

| PSM0—Normal Power Mode (All Parts)              | . 23 |

| PSM1—Reduced Power Mode (ADE7868, ADE7878 Only) | 23   |

| PSM2—Low Power Mode (ADE7868, ADE7878 Only)     | . 23 |

| PSM3—Sleep Mode (All Parts)                     | . 24 |

| Power-Up Procedure                              | . 26 |

| Hardware Reset                                  | . 27 |

| Software Reset Functionality                    | . 27 |

| Theory of Operation                             | . 28 |

| Analog Inputs                                   | . 28 |

| Analog-to-Digital Conversion                    | . 28 |

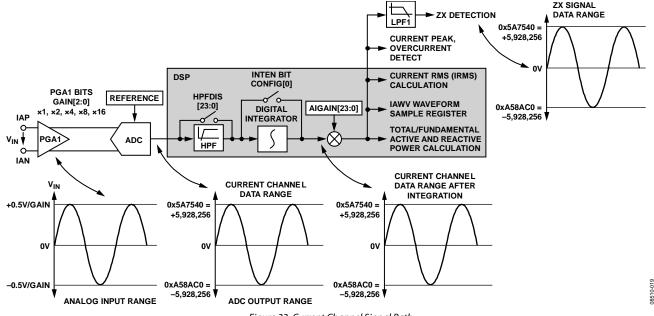

| Current Channel ADC                             | . 29 |

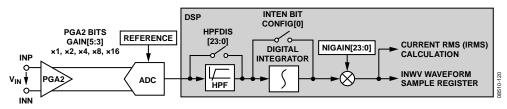

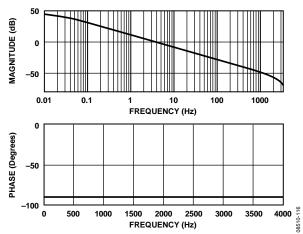

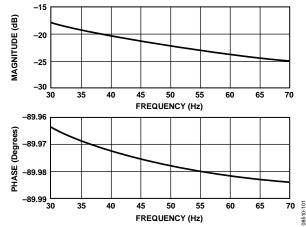

| di/dt Current Sensor and Digital Integrator     | . 31 |

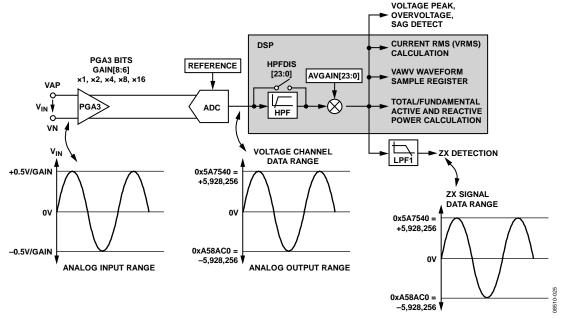

| Voltage Channel ADC                             | . 32 |

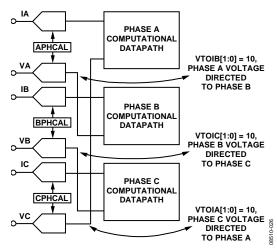

| Changing Phase Voltage Datanath                 | 33   |

| Power Quality Measurements34                                      |

|-------------------------------------------------------------------|

| Phase Compensation                                                |

| Reference Circuit                                                 |

| Digital Signal Processor                                          |

| Root Mean Square Measurement                                      |

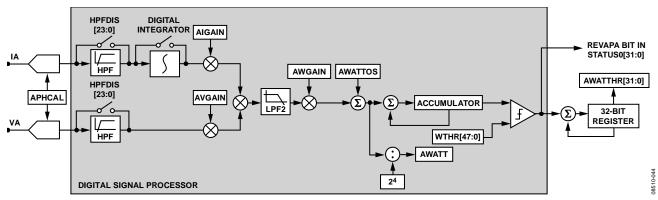

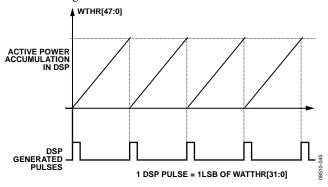

| Active Power Calculation                                          |

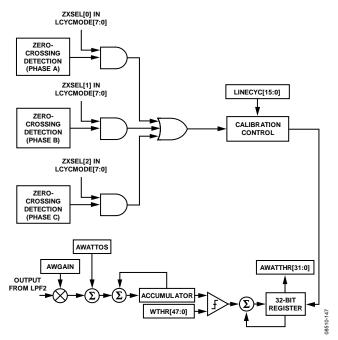

| Reactive Power Calculation—ADE7858, ADE7868, ADE7878<br>Only      |

| Apparent Power Calculation57                                      |

| Waveform Sampling Mode60                                          |

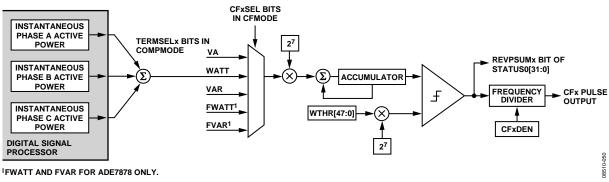

| Energy-to-Frequency Conversion                                    |

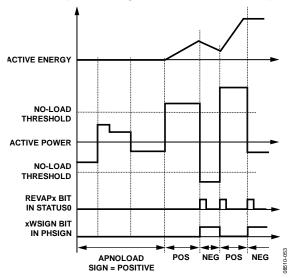

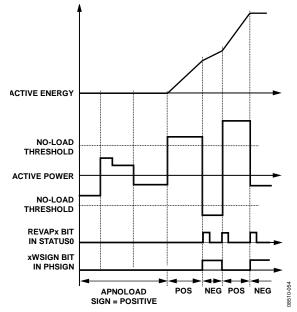

| No Load Condition                                                 |

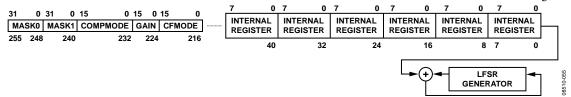

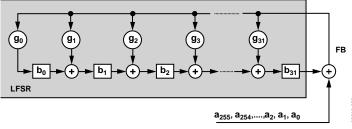

| Checksum Register65                                               |

| Interrupts66                                                      |

| Serial Interfaces                                                 |

| Quick Setup as Energy Meter75                                     |

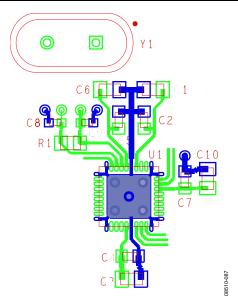

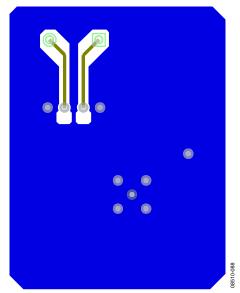

| Layout Guidelines                                                 |

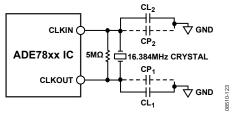

| Crystal Circuit                                                   |

| ADE7878 Evaluation Board76                                        |

| Die Version                                                       |

| Silicon Anomaly                                                   |

| ADE7854/ADE7858/ADE7868/ADE7878 Functionality Issues              |

| Functionality Issues                                              |

| Section 1. ADE7854/ADE7858/ADE7868/ADE7878 Functionality Issues79 |

| Registers List                                                    |

| Outline Dimensions                                                |

| Ordering Guide                                                    |

### **REVISION HISTORY**

| 4/14—Rev. G to Rev. H                                                                       |   |

|---------------------------------------------------------------------------------------------|---|

| Changes to Power-Up Procedure Section                                                       |   |

| 10/13—Rev. F to Rev. G                                                                      |   |

| Changes to Product Title and Features Section                                               |   |

| Changes to Table 2                                                                          |   |

| Deleted Junction Temperature; Table 6                                                       |   |

| Changes to NC and CLKIN Pin Descriptions16                                                  |   |

| Replaced Typical Performance Characteristics Section18 Added Text to Test Circuit Section21 |   |

| Changes to Terminology Section22                                                            | , |

| Changes to PSM2—Low Power Mode (ADE7868, ADE7878                                            |   |

| Only) Section and Added Figure 2524                                                         | Ŀ |

| Changes to Changing Phase Voltage Datapath Section and                                      |   |

| Figure 42                                                                                   | ; |

| Changes to Reference Circuit Section; Added Figure 56,                                      |   |

| Figure 57, and Figure 58; Renumbered Sequentially41                                         |   |

| Changes to Current RMS Compensation Section44                                               |   |

| Changes to Current Mean Absolute Value Calculation—                                         |   |

| ADE7868 and ADE7878 Only and Figure 6045                                                    |   |

| Changes to Voltage RMS Offset Compensation Section                                          |   |

| Changes to Line Cycle Active Energy Accumulation Mode                                       |   |

| Section                                                                                     |   |

| Changes to Quick Setup as Energy Meter Section and                                          |   |

| Figure 9575                                                                                 |   |

| Changes to Figure 96 and Figure 97; Added Crystal Circuit                                   |   |

| Section                                                                                     | , |

| Changes to Address 0xE520 Description; Table 3384                                           |   |

| Changes to Bit 11, Bit 12, Bit 13 Descriptions; Table 4391                                  |   |

| Updated Outline Dimensions                                                                  |   |

| 10/12—Rev. E to Rev. F                                                                      |   |

| •                                                                                           |   |

| Changes to Figure 1                                                                         |   |

| Changes to Figure 2                                                                         |   |

| Changes to Figure 3                                                                         |   |

| Changes to Figure 4                                                                         |   |

| Changes to Table 2                                                                          |   |

| Changes to Figure 5                                                                         |   |

| Added Text under Table 6                                                                    |   |

| Changes to Figure 9 and to Table 8                                                          |   |

| Changes to Power-Up Procedure Section                                                       |   |

| Changes to Figure 31 and Figure 32                                                          |   |

| Changes to Figure 39                                                                        |   |

| Changes to Voltage Waveform Gain Register Section31                                         |   |

| Changes to Figure 41                                                                        |   |

| Changes to Phase Compensation Section                                                       |   |

| Changes to Digital Signal Processor Section                                                 |   |

| Changes to Equation 1240                                                                    |   |

| Changes to Current RMS Offset Compensation Section42                                        |   |

| Changes to Voltage Channel RMS Calculation Section43                                        | i |

| Changes to Voltage RMS Offset Compensation Section and                                      |   |

| to Figure 5944                                                                              |   |

| Changes to Equation 20 and to Equation 21                     | 4  |

|---------------------------------------------------------------|----|

| Changes to Active Energy Calculation Section                  | 40 |

| Changes to Figure 62 and to following text and to Equation 25 | 47 |

| Changes to Equation 32, Equation 34, and to Reactive          |    |

| Power Gain Calibration Section                                | 50 |

| Changes to Reactive Energy Calculation Section                |    |

| Changes to Figure 66                                          |    |

| Changes to Energy Accumulation Modes Sections and to          |    |

| Caption for Figure 67                                         | 53 |

| Changes to Equation 40                                        |    |

| Changes to Apparent Power Calculation Using VNOM Section.     |    |

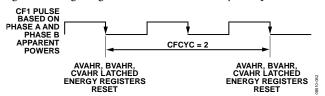

| Changes to CF Outputs for Various Accumultation Modes         |    |

| Section                                                       | 60 |

| Changes to Sign of Sum-of-Phase Powers in the CFx             |    |

| Datapath Section and to Equation 47                           | 6  |

| Changes to Equation 48                                        |    |

| Changes to Checksum Register Section and to Table 23          |    |

| Changes to Figure 81                                          |    |

| Changes to Figure 82                                          |    |

| Changes to Figure 32                                          |    |

|                                                               |    |

| Changes to HSDC Interface Section                             |    |

| Changes to Figure 89, added Quick Setup as Energy Meter       | /. |

|                                                               |    |

| Section, added Layout Guidelines, and added Figure 90;        | 7  |

| Renumbered Sequentially                                       |    |

| Added Figure 91 and Figure 92                                 |    |

| Changes to Table 30                                           |    |

| Changes to Table 33                                           |    |

| Changes to Table 46                                           | 90 |

| 4/11—Rev. D to Rev. E                                         |    |

| Changes to Input Clock FrequencyParameter, Table 2            | 10 |

| Changes to Current RMS Offset Compensation Section            |    |

| Changes to Voltage RMS Offset Compensation Section            |    |

| Changes to Note 2, Table 30                                   |    |

| Changes to Address 0xE707, Table 33                           |    |

| Changes to Table 45                                           |    |

| Changes to Table 46                                           |    |

| Changes to Bit Location 7:3, Default Value, Table 54          |    |

| 2/11—Rev. C to Rev. D                                         |    |

|                                                               |    |

| Changes to Figure 1                                           |    |

| Changes to Figure 2                                           |    |

| Changes to Figure 3                                           |    |

| Changes to Figure 4                                           |    |

| Changes to Table 2                                            |    |

| Changed SCLK Edge to HSCLK Edge, Table 5                      |    |

| Change to Current Channel HPF Section                         |    |

| Change to di/dt Current Sensor and Digital Integrator Section |    |

| Changes to Digital Signal Processor Section                   |    |

| Changes to Figure 59                                          |    |

| Changes to Figure 62                                          |    |

| Changes to Figure 65                                          |    |

| Changes to Figure 66                                          | 52 |

# **Data Sheet**

# ADE7854/ADE7858/ADE7868/ADE7878

| Changes to Line Cycle Reactive Energy Accumulation Mode  |

|----------------------------------------------------------|

| Section and to Figure 6753                               |

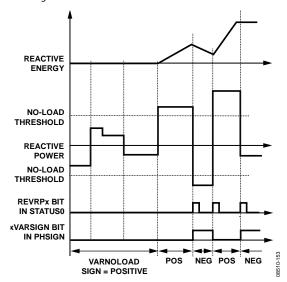

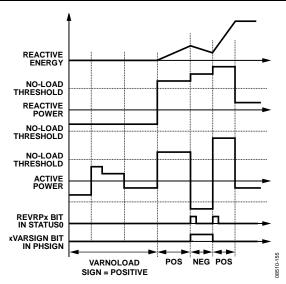

| No Load Detection Based On Total Active, Reactive Powers |

| Section                                                  |

| Change to Equation 5063                                  |

| Changes to the HSDC Interface Section                    |

| Changes to Figure 87 and Figure 8871                     |

| Changes to Figure 89                                     |

| Changes to Table 30                                      |

| Changes to Table 46                                      |

| 11/10—Rev. B to Rev. C                                   |

| Change to Signal-to-Noise-and-Distortion Ratio, SINAD    |

| Parameter, Table 1                                       |

| Changes to Figure 18                                     |

| Changes to Figure 22                                     |

| Changes to Silicon Anomaly Section                       |

| Added Table 28 to Silicon Anomaly Section                |

| 8/10—Rev. A to Rev. B                                    |

| Changes to Figure 14                                     |

| Changes to Figure 25                                     |

| Changes to Figure 36                                     |

| Changes to Figure 4                                      |

| Change to Table 8                                        |

| Changes to Power-Up Procedure Section23                  |

| Changes to Equation 6 and Equation 7                     |

| Changes to Equation 1743                                 |

| Changes to Active Power Offset Calibration Section45     |

| Changes to Figure 63                                     |

| Changes to Reactive Power Offset Calibration Section     |

| Changes to Figure 82                                     |

| Added Silicon Anomaly Section, Renumbered Tables         |

| Sequentially71                                           |

### 3/10—Rev. 0 to Rev. A

| Added ADE7854, ADE7858, and ADE7878                  | Universal |

|------------------------------------------------------|-----------|

| Reorganized Layout                                   | Universal |

| Added Table 1, Renumbered Sequentially               | 1         |

| Added Figure 1, Renumbered Sequentially              | 3         |

| Added Figure 2                                       | 4         |

| Added Figure 3                                       |           |

| Changes to Specifications Section                    | 7         |

| Changes to Figure 9 and changes to Table 8           | 14        |

| Changes to Typical Performance Characteristics Secti | on 16     |

| Changes to Figure 22                                 | 18        |

| Changes to the Power Management Section              | 20        |

| Changes to the Theory of Operation Section           | 25        |

| Changes to Figure 31 and Figure 32                   | 27        |

| Change to Equation 28                                | 47        |

| Changes to Figure 83                                 | 66        |

| Changes to Figure 86                                 | 68        |

| Changes to the Registers List Section                | 72        |

| Changes to Ordering Guide                            | 91        |

### 2/10—Revision 0: Initial Version

## **FUNCTIONAL BLOCK DIAGRAMS**

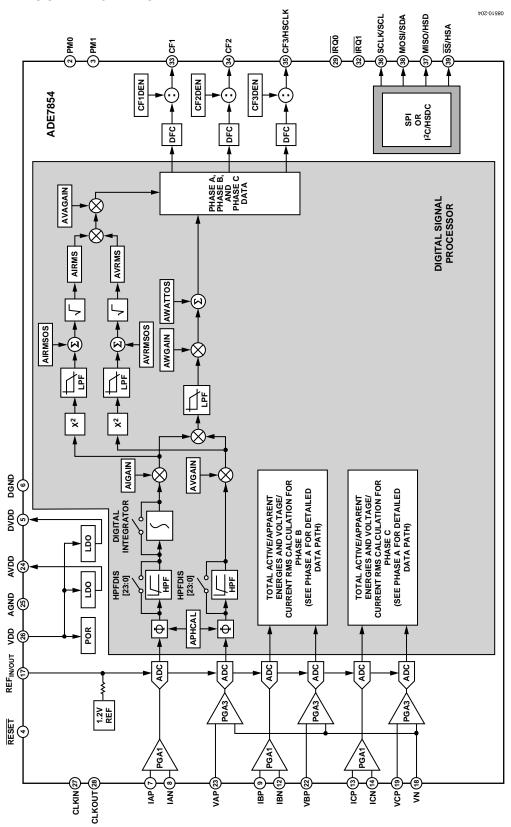

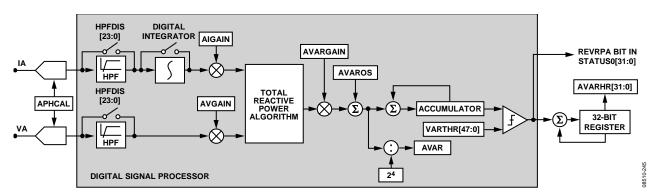

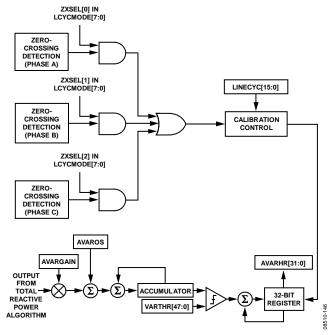

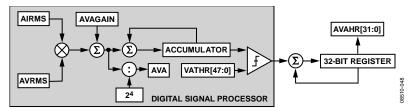

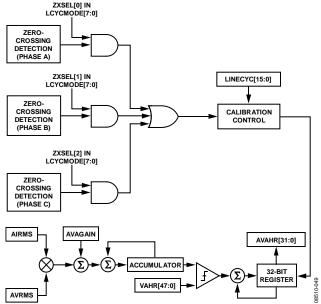

Figure 1. ADE7854 Functional Block Diagram

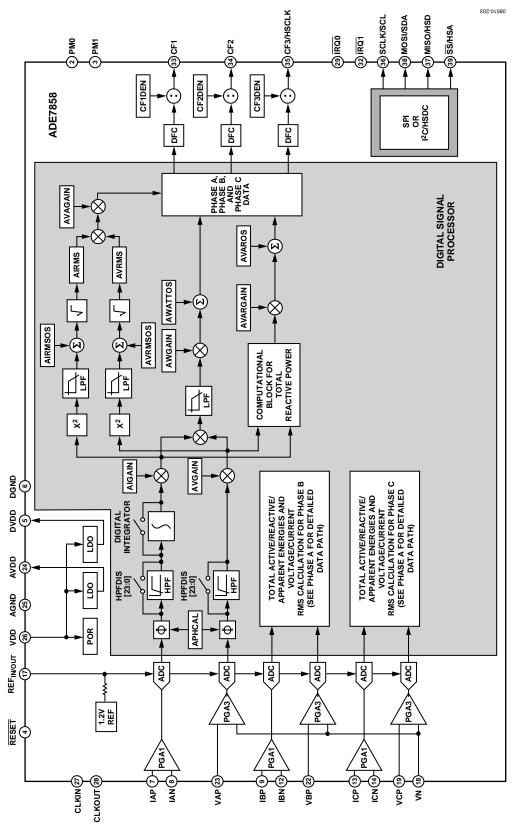

Figure 2. ADE7858 Functional Block Diagram

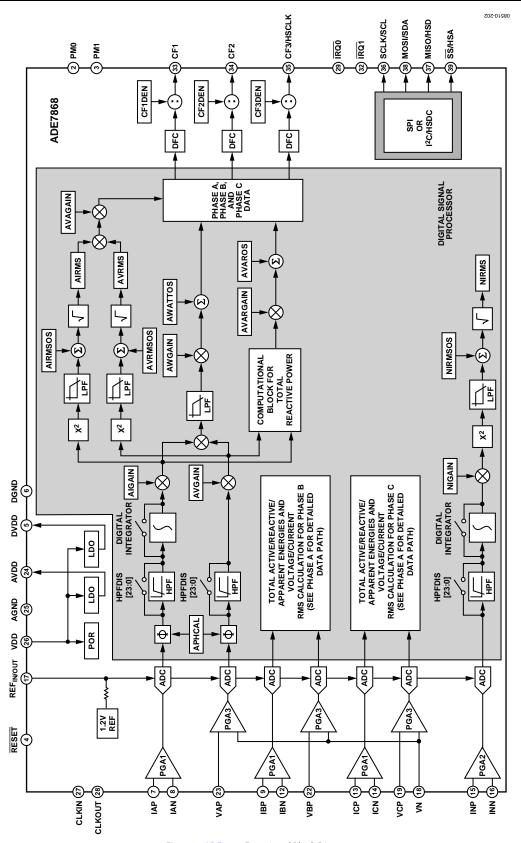

Figure 3. ADE7868 Functional Block Diagram

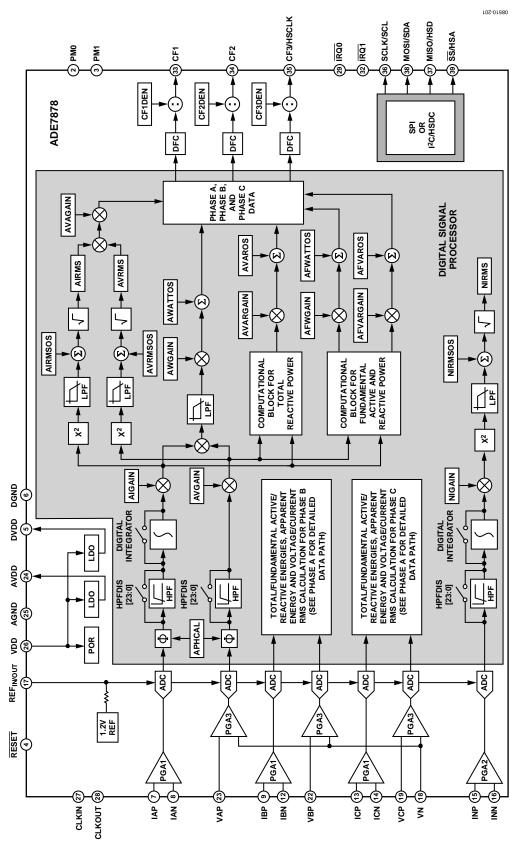

Figure 4. ADE7878 Functional Block Diagram

## **SPECIFICATIONS**

$VDD = 3.3~V \pm 10\%, AGND = DGND = 0~V, on-chip~reference, CLKIN = 16.384~MHz, T_{MIN}~to~T_{MAX} = -40^{\circ}C~to~+85^{\circ}C, T_{TYP} = 25^{\circ}C.$

Table 2.

| Parameter <sup>1, 2</sup>                                   | Min Typ | Max Unit | Test Conditions/Comments                                                |

|-------------------------------------------------------------|---------|----------|-------------------------------------------------------------------------|

| ACCURACY                                                    |         |          |                                                                         |

| Active Energy Measurement                                   |         |          |                                                                         |

| Active Energy Measurement Error<br>(per Phase)              |         |          |                                                                         |

| Total Active Energy                                         | 0.1     | %        | Over a dynamic range of 1000 to 1, PGA = 1, 2, 4; integrator off        |

|                                                             | 0.2     | %        | Over a dynamic range of 3000 to 1, PGA = 1, 2, 4; integrator off        |

|                                                             | 0.1     | %        | Over a dynamic range of 500 to 1, PGA = 8, 16; integrator on            |

| Fundamental Active Energy<br>(ADE7878 Only)                 | 0.1     | %        | Over a dynamic range of 1000 to 1, PGA = 1, 2, 4; integrator off        |

|                                                             | 0.2     | %        | Over a dynamic range of 3000 to 1, PGA = 1, 2, 4; integrator off        |

|                                                             | 0.1     | %        | Over a dynamic range of 500 to 1, PGA = 8, 16; integrator on            |

| AC Power Supply Rejection                                   |         |          | VDD = 3.3 V + 120 mV rms/120 Hz/100 Hz, IPx =                           |

| Output Frequency Variation                                  | 0.01    | %        | $VPx = \pm 100 \text{ mV rms}$                                          |

| DC Power Supply Rejection                                   |         |          | $VDD = 3.3 V \pm 330 \text{ mV dc}; IPx = VPx = \pm 100 \text{ mV rms}$ |

| Output Frequency Variation                                  | 0.01    | %        |                                                                         |

| Total Active Energy Measurement<br>Bandwidth                | 2       | kHz      |                                                                         |

| REACTIVE ENERGY MEASUREMENT (ADE7858, ADE7868, AND ADE7878) |         |          |                                                                         |

| Reactive Energy Measurement Error (per Phase)               |         |          |                                                                         |

| Total Reactive Energy                                       | 0.1     | %        | Over a dynamic range of 1000 to 1, PGA = 1, 2, 4; integrator off        |

|                                                             | 0.2     | %        | Over a dynamic range of 3000 to 1, PGA = 1, 2, 4; integrator off        |

|                                                             | 0.1     | %        | Over a dynamic range of 500 to 1, PGA = 8, 16; integrator on            |

| Fundamental Reactive Energy (ADE7878 Only)                  | 0.1     | %        | Over a dynamic range of 1000 to 1, PGA = 1, 2, 4; integrator off        |

|                                                             | 0.2     | %        | Over a dynamic range of 3000 to 1, PGA = 1, 2, 4; integrator off        |

|                                                             | 0.1     | %        | Over a dynamic range of 500 to 1, PGA = 8, 16; integrator on            |

| AC Power Supply Rejection Output Frequency Variation        | 0.01    | %        | VDD = 3.3 V + 120 mV rms/120 Hz/100 Hz, IPx =<br>VPx = ±100 mV rms      |

| DC Power Supply Rejection                                   | 0.01    | /0       | VDD = 3.3 V ± 330 mV dc; IPx = VPx =<br>±100 mV rms                     |

| Output Frequency Variation                                  | 0.01    | %        | 2100 1110 11110                                                         |

| Total Reactive Energy Measurement<br>Bandwidth              | 2       | kHz      |                                                                         |

| RMS MEASUREMENTS                                            |         |          |                                                                         |

| I rms and V rms Measurement<br>Bandwidth                    | 2       | kHz      |                                                                         |

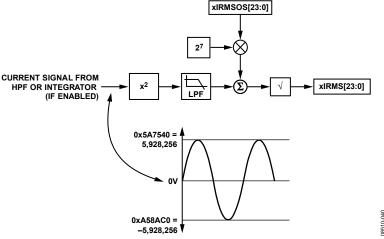

| I rms and V rms Measurement Error (PSM0 Mode)               | 0.1     | %        | Over a dynamic range of 1000 to 1, PGA = 1                              |

| Parameter <sup>1, 2</sup>                                    | Min   | Тур                    | Max   | Unit    | Test Conditions/Comments                                                                                                                                                            |

|--------------------------------------------------------------|-------|------------------------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEAN ABSOLUTE VALUE (MAV) MEASUREMENT (ADE7868 AND ADE7878)  |       |                        |       |         |                                                                                                                                                                                     |

| I mav Measurement Bandwidth (PSM1<br>Mode)                   |       | 260                    |       | Hz      |                                                                                                                                                                                     |

| I mav Measurement Error (PSM1 Mode)                          |       | 0.5                    |       | %       | Over a dynamic range of 100 to 1, PGA = 1, 2, 4, 8                                                                                                                                  |

| ANALOG INPUTS                                                |       |                        |       |         | , , , , , , , , , ,                                                                                                                                                                 |

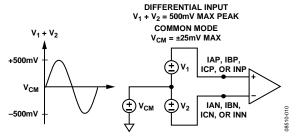

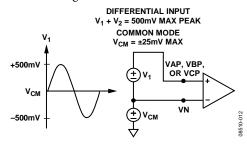

| Maximum Signal Levels                                        |       |                        | ±500  | mV peak | PGA = 1, differential inputs between the following pins: IAP and IAN, IBP and IBN, ICP and ICN; single-ended inputs between the following pins: VAP and VN, VBP and VN, VCP, and VN |

| Input Impedance (DC) IAP, IAN, IBP, IBN, ICP, ICN, VAP, VBP, | 400   |                        |       | kΩ      |                                                                                                                                                                                     |

| and VCP Pins                                                 | 120   |                        |       | 1.0     |                                                                                                                                                                                     |

| VN Pin                                                       | 130   | 24                     |       | kΩ      |                                                                                                                                                                                     |

| ADC Offset                                                   |       | -24                    |       | mV      | PGA = 1, uncalibrated error, see the Terminology section                                                                                                                            |

| Gain Error                                                   |       | ±4                     |       | %       | External 1.2 V reference                                                                                                                                                            |

| WAVEFORM SAMPLING                                            |       |                        |       |         | Sampling CLKIN/2048, 16.384 MHz/2048 = 8 kSPS                                                                                                                                       |

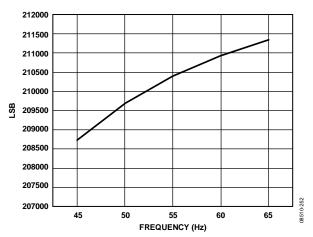

| Current and Voltage Channels<br>Signal-to-Noise Ratio, SNR   |       | 74                     |       | dB      | See the Waveform Sampling Mode section PGA = 1, fundamental frequency: 45 Hz to                                                                                                     |

| Signal-to-Noise-and-Distortion Ratio,<br>SINAD               |       | 74                     |       | dB      | 65 Hz, see the Terminology section PGA = 1; fundamental frequency: 45 Hz to 65 Hz, see the Terminology section                                                                      |

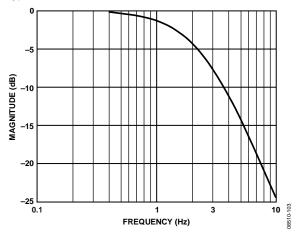

| Bandwidth (–3 dB)                                            |       | 2                      |       | kHz     | 03 112, see the leffilliology section                                                                                                                                               |

| TIME INTERVAL BETWEEN PHASES                                 |       |                        |       | KIIZ    |                                                                                                                                                                                     |

| Measurement Error                                            |       | 0.3                    |       | Degrees | Line frequency = 45 Hz to 65 Hz, HPF on                                                                                                                                             |

| CF1, CF2, CF3 PULSE OUTPUTS                                  |       |                        |       | 9       |                                                                                                                                                                                     |

| Maximum Output Frequency                                     |       | 8                      |       | kHz     | WTHR = VARTHR = VATHR = PMAX = 33,516,139                                                                                                                                           |

| Duty Cycle                                                   |       | 50                     |       | %       | If CF1, CF2, or CF3 frequency > 6.25 Hz and CFDEN is even and > 1                                                                                                                   |

|                                                              |       | (1 + 1/CFDEN)<br>× 50% |       |         | If CF1, CF2, or CF3 frequency > 6.25 Hz and CFDEN is odd and > 1                                                                                                                    |

| Active Low Pulse Width                                       |       | 80                     |       | ms      | If CF1, CF2, or CF3 frequency < 6.25 Hz                                                                                                                                             |

| Jitter                                                       |       | 0.04                   |       | %       | For CF1, CF2, or CF3 frequency = 1 Hz and nominal phase currents are larger than 10% of full scale                                                                                  |

| REFERENCE INPUT                                              |       |                        |       |         |                                                                                                                                                                                     |

| REF <sub>IN/OUT</sub> Input Voltage Range                    | 1.1   |                        | 1.3   | V       | Minimum = $1.2 \text{ V} - 8\%$ ; maximum = $1.2 \text{ V} + 8\%$                                                                                                                   |

| Input Capacitance                                            |       |                        | 10    | pF      |                                                                                                                                                                                     |

| ON-CHIP REFERENCE                                            |       |                        |       |         | Nominal 1.2 V at the REF <sub>IN/OUT</sub> pin at $T_A = 25^{\circ}C$                                                                                                               |

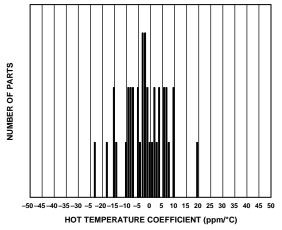

| PSM0 and PSM1 Modes Temperature Coefficient                  | -50   | ±5                     | +50   | ppm/°C  | Drift across the entire temperature range of -40°C to +85°C is calculated with reference to 25°C; see the Reference Circuit section for more details                                |

| CLKIN                                                        | 1     |                        |       |         | All specifications CLKIN of 16.384 MHz. See the                                                                                                                                     |

|                                                              |       |                        |       |         | Crystal Circuit section for more details.                                                                                                                                           |

| Input Clock Frequency                                        | 16.22 | 16.384                 | 16.55 | MHz     |                                                                                                                                                                                     |

| LOGIC INPUTS—MOSI/SDA, SCLK/SCL, SS, RESET, PMO, AND PM1     |       |                        |       |         |                                                                                                                                                                                     |

| Input High Voltage, V <sub>INH</sub>                         | 2.0   |                        |       | V       | VDD = 3.3 V ± 10%                                                                                                                                                                   |

| Input Low Voltage, V <sub>INL</sub>                          |       |                        | 0.8   | V       | VDD = 3.3 V ± 10%                                                                                                                                                                   |

| Input Current, I <sub>IN</sub>                               |       |                        | -8.7  | μA      | Input = 0 V, VDD = 3.3 V                                                                                                                                                            |

| • • • • • • • • • • • • • • • • • • • •                      |       |                        | 3     | μΑ      | Input = VDD = 3.3 V                                                                                                                                                                 |

| Input Capacitance, C <sub>IN</sub>                           |       | 10                     |       | pF      | ·                                                                                                                                                                                   |

# **Data Sheet**

# ADE7854/ADE7858/ADE7868/ADE7878

| Parameter <sup>1, 2</sup>                 | Min  | Тур  | Max  | Unit | Test Conditions/Comments                                            |

|-------------------------------------------|------|------|------|------|---------------------------------------------------------------------|

| LOGIC OUTPUTS—IRQ0, IRQ1, MISO/HSD        |      |      |      |      | VDD = 3.3 V ± 10%                                                   |

| Output High Voltage, V <sub>он</sub>      | 2.4  |      |      | V    | VDD = 3.3 V ± 10%                                                   |

| Isource                                   |      |      | 800  | μΑ   |                                                                     |

| Output Low Voltage, Vol                   |      |      | 0.4  | V    | VDD = 3.3 V ± 10%                                                   |

| Isink                                     |      |      | 2    | mA   |                                                                     |

| CF1, CF2, CF3/HSCLK                       |      |      |      |      |                                                                     |

| Output High Voltage, Vон                  | 2.4  |      |      | V    | VDD = 3.3 V ± 10%                                                   |

| Isource                                   |      |      | 500  | μΑ   |                                                                     |

| Output Low Voltage, Vol                   |      |      | 0.4  | V    | VDD = 3.3 V ± 10%                                                   |

| I <sub>SINK</sub>                         |      |      | 2    | mA   |                                                                     |

| POWER SUPPLY                              |      |      |      |      | For specified performance                                           |

| PSM0 Mode                                 |      |      |      |      |                                                                     |

| VDD Pin                                   | 2.97 |      | 3.63 | V    | Minimum = $3.3 \text{ V} - 10\%$ ; maximum = $3.3 \text{ V} + 10\%$ |

| I <sub>DD</sub>                           |      | 24.4 | 27.2 | mA   |                                                                     |

| PSM1 and PSM2 Modes (ADE7868 and ADE7878) |      |      |      |      |                                                                     |

| VDD Pin                                   | 2.4  |      | 3.7  | V    |                                                                     |

| $I_{DD}$                                  |      |      |      |      |                                                                     |

| PSM1 Mode                                 |      | 6.0  |      | mA   |                                                                     |

| PSM2 Mode                                 |      | 0.2  |      | mA   |                                                                     |

| PSM3 Mode                                 |      |      |      |      |                                                                     |

| VDD Pin                                   | 2.4  |      | 3.7  | V    |                                                                     |

| I <sub>DD</sub> in PSM3 Mode              |      | 1.7  |      | μΑ   |                                                                     |

<sup>&</sup>lt;sup>1</sup> See the Typical Performance Characteristics section. <sup>2</sup> See the Terminology section for a definition of the parameters.

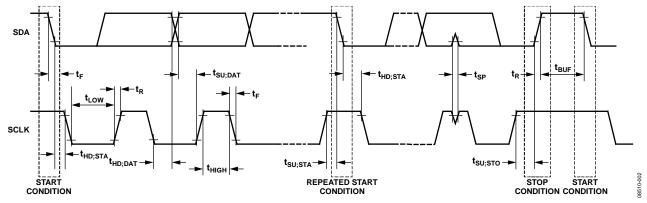

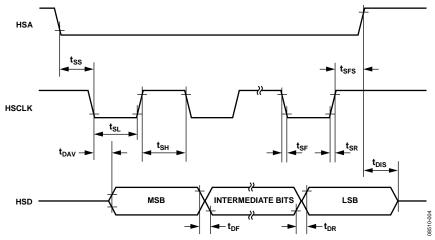

### **TIMING CHARACTERISTICS**

$VDD = 3.3~V \pm 10\%$ , AGND = DGND = 0 V, on-chip reference, CLKIN = 16.384 MHz,  $T_{MIN}$  to  $T_{MAX} = -40$ °C to +85°C. Note that dual function pin names are referenced by the relevant function only within the timing tables and diagrams; see the Pin Configuration and Function Descriptions section for full pin mnemonics and descriptions.

Table 3. I<sup>2</sup>C-Compatible Interface Timing Parameter

|                                                  |                     | Standard Mode    |      | Fast Mode |     |      |

|--------------------------------------------------|---------------------|------------------|------|-----------|-----|------|

| Parameter                                        | Symbol              | Min              | Max  | Min       | Max | Unit |

| SCL Clock Frequency                              | f <sub>SCL</sub>    | 0                | 100  | 0         | 400 | kHz  |

| Hold Time (Repeated) Start Condition             | t <sub>HD;STA</sub> | 4.0              |      | 0.6       |     | μs   |

| Low Period of SCL Clock                          | t <sub>LOW</sub>    | 4.7              |      | 1.3       |     | μs   |

| High Period of SCL Clock                         | t <sub>HIGH</sub>   | 4.0              |      | 0.6       |     | μs   |

| Set-Up Time for Repeated Start Condition         | t <sub>SU;STA</sub> | 4.7              |      | 0.6       |     | μs   |

| Data Hold Time                                   | t <sub>HD;DAT</sub> | 0                | 3.45 | 0         | 0.9 | μs   |

| Data Setup Time                                  | t <sub>SU;DAT</sub> | 250              |      | 100       |     | ns   |

| Rise Time of Both SDA and SCL Signals            | $t_{R}$             |                  | 1000 | 20        | 300 | ns   |

| Fall Time of Both SDA and SCL Signals            | t <sub>F</sub>      |                  | 300  | 20        | 300 | ns   |

| Setup Time for Stop Condition                    | t <sub>SU;STO</sub> | 4.0              |      | 0.6       |     | μs   |

| Bus Free Time Between a Stop and Start Condition | t <sub>BUF</sub>    | 4.7              |      | 1.3       |     | μs   |

| Pulse Width of Suppressed Spikes                 | t <sub>SP</sub>     | N/A <sup>1</sup> |      |           | 50  | ns   |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

Figure 5. I<sup>2</sup>C-Compatible Interface Timing

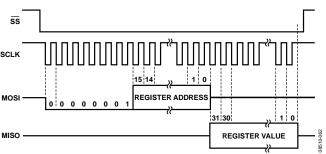

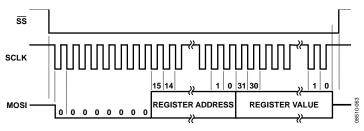

**Table 4. SPI Interface Timing Parameters**

| Parameter                              | Symbol           | Min | Max               | Unit |

|----------------------------------------|------------------|-----|-------------------|------|

| SS to SCLK Edge                        | t <sub>SS</sub>  | 50  |                   | ns   |

| SCLK Period                            |                  | 0.4 | 4000 <sup>1</sup> | μs   |

| SCLK Low Pulse Width                   | t <sub>SL</sub>  | 175 |                   | ns   |

| SCLK High Pulse Width                  | t <sub>SH</sub>  | 175 |                   | ns   |

| Data Output Valid After SCLK Edge      | t <sub>DAV</sub> |     | 100               | ns   |

| Data Input Setup Time Before SCLK Edge | t <sub>DSU</sub> | 100 |                   | ns   |

| Data Input Hold Time After SCLK Edge   | t <sub>DHD</sub> | 5   |                   | ns   |

| Data Output Fall Time                  | t <sub>DF</sub>  |     | 20                | ns   |

| Data Output Rise Time                  | t <sub>DR</sub>  |     | 20                | ns   |

| SCLK Rise Time                         | t <sub>SR</sub>  |     | 20                | ns   |

| SCLK Fall Time                         | t <sub>SF</sub>  |     | 20                | ns   |

| MISO Disable After SS Rising Edge      | t <sub>DIS</sub> |     | 200               | ns   |

| SS High After SCLK Edge                | t <sub>SFS</sub> | 0   |                   | ns   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design.

Figure 6. SPI Interface Timing

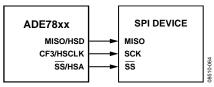

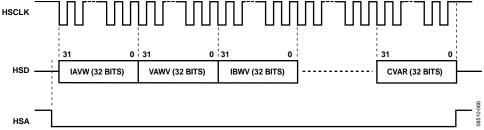

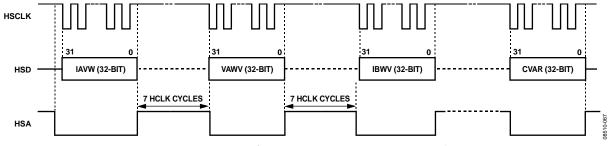

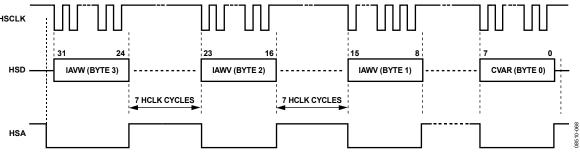

**Table 5. HSDC Interface Timing Parameter**

| Parameter                          | Symbol           | Min | Max | Unit |

|------------------------------------|------------------|-----|-----|------|

| HSA to HSCLK Edge                  | t <sub>ss</sub>  | 0   |     | ns   |

| HSCLK Period                       |                  | 125 |     | ns   |

| HSCLK Low Pulse Width              | t <sub>SL</sub>  | 50  |     | ns   |

| HSCLK High Pulse Width             | t <sub>sн</sub>  | 50  |     | ns   |

| Data Output Valid After HSCLK Edge | t <sub>DAV</sub> |     | 40  | ns   |

| Data Output Fall Time              | t <sub>DF</sub>  |     | 20  | ns   |

| Data Output Rise Time              | t <sub>DR</sub>  |     | 20  | ns   |

| HSCLK Rise Time                    | t <sub>SR</sub>  |     | 10  | ns   |

| HSCLK Fall Time                    | t <sub>SF</sub>  |     | 10  | ns   |

| HSD Disable After HSA Rising Edge  | t <sub>DIS</sub> | 5   |     | ns   |

| HSA High After HSCLK Edge          | t <sub>SFS</sub> | 0   |     | ns   |

Figure 7. HSDC Interface Timing

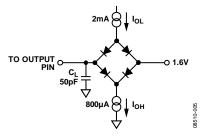

Figure 8. Load Circuit for Timing Specifications

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

#### Table 6.

| 1 4010 01                                                                           |                       |

|-------------------------------------------------------------------------------------|-----------------------|

| Parameter                                                                           | Rating                |

| VDD to AGND                                                                         | -0.3 V to +3.7 V      |

| VDD to DGND                                                                         | -0.3 V to +3.7 V      |

| Analog Input Voltage to AGND, IAP,<br>IAN, IBP, IBN, ICP, ICN, VAP, VBP, VCP,<br>VN | -2 V to +2 V          |

| Analog Input Voltage to INP and INN                                                 | -2 V to +2 V          |

| Reference Input Voltage to AGND                                                     | -0.3 V to VDD + 0.3 V |

| Digital Input Voltage to DGND                                                       | -0.3 V to VDD + 0.3 V |

| Digital Output Voltage to DGND                                                      | -0.3 V to VDD + 0.3 V |

| Operating Temperature                                                               |                       |

| Industrial Range                                                                    | -40°C to +85°C        |

| Storage Temperature Range                                                           | −65°C to +150°C       |

| Lead Temperature (Soldering, 10 sec)                                                | 300°C                 |

Note that, regarding the temperature profile used in soldering RoHS compliant parts, Analog Devices advises that reflow profiles should conform to J-STD 20 from JEDEC. Refer to www.jedec.org for the latest revision.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified equal to 29.3°C/W;  $\theta_{JC}$  is specified equal to 1.8°C/W.

Table 7. Thermal Resistance

| Package Type  | θιΑ  | θις | Unit |

|---------------|------|-----|------|

| 40-Lead LFCSP | 29.3 | 1.8 | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

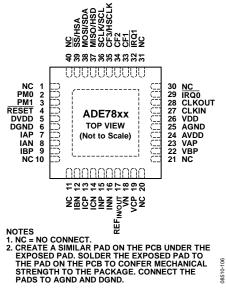

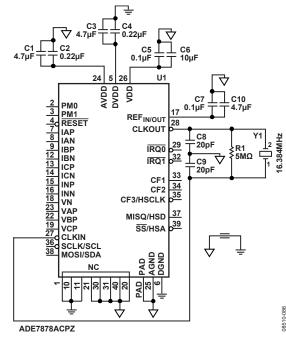

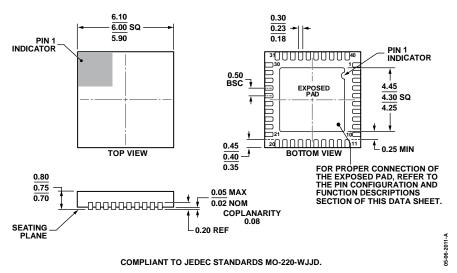

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 9. Pin Configuration

**Table 8. Pin Function Descriptions**

| Pin No.                          | Mnemonic              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 10, 11, 20,<br>21, 30, 31, 40 | NC                    | No Connect. These pins are not connected internally. It is recommended to ground these pins.                                                                                                                                                                                                                                                                                                                                                                                                |

| 2                                | PM0                   | Power Mode Pin 0. This pin, combined with PM1, defines the power mode of the ADE7854/ADE7858/ADE7868/ADE7878, as described in Table 9.                                                                                                                                                                                                                                                                                                                                                      |

| 3                                | PM1                   | Power Mode Pin 1. This pin defines the power mode of the ADE7854/ADE7858/ADE7868/ADE7878 when combined with PMO, as described in Table 9.                                                                                                                                                                                                                                                                                                                                                   |

| 4                                | RESET                 | Reset Input, Active Low. In PSM0 mode, this pin should stay low for at least 10 $\mu$ s to trigger a hardware reset.                                                                                                                                                                                                                                                                                                                                                                        |

| 5                                | DVDD                  | 2.5 V output of the digital low dropout regulator (LDO). Decouple this pin with a 4.7 $\mu$ F capacitor in parallel with a ceramic 220 nF capacitor. Do not connect external active circuitry to this pin.                                                                                                                                                                                                                                                                                  |

| 6                                | DGND                  | Ground Reference. This pin provides the ground reference for the digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7, 8                             | IAP, IAN              | Analog Inputs for Current Channel A. This channel is used with the current transducers and is referenced in this document as Current Channel A. These inputs are fully differential voltage inputs with a maximum differential level of $\pm 0.5$ V. This channel also has an internal PGA equal to the ones on Channel B and Channel C.                                                                                                                                                    |

| 9, 12                            | IBP, IBN              | Analog Inputs for Current Channel B. This channel is used with the current transducers and is referenced in this document as Current Channel B. These inputs are fully differential voltage inputs with a maximum differential level of $\pm 0.5$ V. This channel also has an internal PGA equal to the ones on Channel C and Channel A.                                                                                                                                                    |

| 13, 14                           | ICP, ICN              | Analog Inputs for Current Channel C. This channel is used with the current transducers and is referenced in this document as Current Channel C. These inputs are fully differential voltage inputs with a maximum differential level of $\pm 0.5$ V. This channel also has an internal PGA equal to the ones on Channel A and Channel B.                                                                                                                                                    |

| 15, 16                           | INP, INN              | Analog Inputs for Neutral Current Channel N. This channel is used with the current transducers and is referenced in this document as Current Channel N. These inputs are fully differential voltage inputs with a maximum differential level of $\pm 0.5$ V. This channel also has an internal PGA, different from the ones found on the A, B, and C channels. The neutral current channel is available in the ADE7878 and ADE7868. In the ADE7858 and ADE7854, connect these pins to AGND. |

| 17                               | REF <sub>IN/OUT</sub> | This pin provides access to the on-chip voltage reference. The on-chip reference has a nominal value of 1.2 V. An external reference source with 1.2 V $\pm$ 8% can also be connected at this pin. In either case, decouple this pin to AGND with a 4.7 $\mu$ F capacitor in parallel with a ceramic 100 nF capacitor. After reset, the on-chip reference is enabled.                                                                                                                       |

| Pin No.        | Mnemonic               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18, 19, 22, 23 | VN, VCP, VBP, VAP      | Analog Inputs for the Voltage Channel. This channel is used with the voltage transducer and is referenced as the voltage channel in this document. These inputs are single-ended voltage inputs with a maximum signal level of $\pm 0.5$ V with respect to VN for specified operation. This channel also has an internal PGA.                                                                                                                                                                                                                    |

| 24             | AVDD                   | 2.5 V output of the analog low dropout regulator (LDO). Decouple this pin with a 4.7 $\mu$ F capacitor in parallel with a ceramic 220 nF capacitor. Do not connect external active circuitry to this pin.                                                                                                                                                                                                                                                                                                                                        |

| 25             | AGND                   | Ground Reference. This pin provides the ground reference for the analog circuitry. Tie this pin to the analog ground plane or to the quietest ground reference in the system. Use this quiet ground reference for all analog circuitry, for example, antialiasing filters, current, and voltage transducers.                                                                                                                                                                                                                                     |

| 26             | VDD                    | Supply Voltage. This pin provides the supply voltage. In PSM0 (normal power mode), maintain the supply voltage at 3.3 V $\pm$ 10% for specified operation. In PSM1 (reduced power mode), PSM2 (low power mode), and PSM3 (sleep mode), when the ADE7868/ADE7878 is supplied from a battery, maintain the supply voltage between 2.4 V and 3.7 V. Decouple this pin to AGND with a 10 $\mu\text{F}$ capacitor in parallel with a ceramic 100 nF capacitor. The only modes available on the ADE7858 and ADE7854 are the PSM0 and PSM3 power modes. |

| 27             | CLKIN                  | Master Clock. An external clock can be provided at this logic input. Alternatively, a crystal can be connected across CLKIN and CLKOUT to provide a clock source for the ADE7854/ADE7858/ADE7868/ADE7868. The clock frequency for specified operation is 16.384 MHz. See the Crystal Circuit section for details on choosing a suitable crystal.                                                                                                                                                                                                 |

| 28             | CLKOUT                 | A crystal can be connected across this pin and CLKIN (as previously described with Pin 27 in this table) to provide a clock source for the ADE7854/ADE7858/ADE7868/ADE7878.                                                                                                                                                                                                                                                                                                                                                                      |

| 29, 32         | ĪRQ0, ĪRQ1             | Interrupt Request Outputs. These are active low logic outputs. See the Interrupts section for a detailed presentation of the events that can trigger interrupts.                                                                                                                                                                                                                                                                                                                                                                                 |

| 33, 34, 35     | CF1, CF2,<br>CF3/HSCLK | Calibration Frequency (CF) Logic Outputs. These outputs provide power information based on the CF1SEL[2:0], CF2SEL[2:0], and CF3SEL[2:0] bits in the CFMODE register. These outputs are used for operational and calibration purposes. The full-scale output frequency can be scaled by writing to the CF1DEN, CF2DEN, and CF3DEN registers, respectively (see the Energy-to-Frequency Conversion section). CF3 is multiplexed with the serial clock output of the HSDC port.                                                                    |

| 36             | SCLK/SCL               | Serial Clock Input for SPI Port/Serial Clock Input for I <sup>2</sup> C Port. All serial data transfers are synchronized to this clock (see the Serial Interfaces section). This pin has a Schmidt trigger input for use with a clock source that has a slow edge transition time, for example, opto-isolator outputs.                                                                                                                                                                                                                           |

| 37             | MISO/HSD               | Data Out for SPI Port/Data Out for HSDC Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 38             | MOSI/SDA               | Data In for SPI Port/Data Out for I <sup>2</sup> C Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 39             | SS/HSA                 | Slave Select for SPI Port/HSDC Port Active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| EP             | Exposed Pad            | Create a similar pad on the PCB under the exposed pad. Solder the exposed pad to the pad on the PCB to confer mechanical strength to the package. Connect the pads to AGND and DGND.                                                                                                                                                                                                                                                                                                                                                             |

### TYPICAL PERFORMANCE CHARACTERISTICS

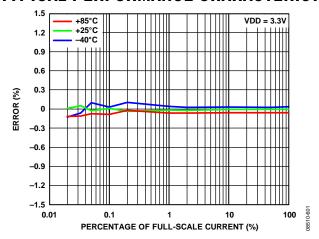

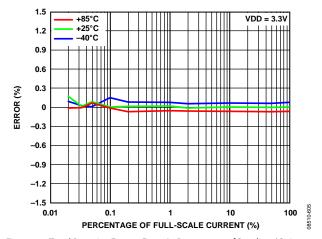

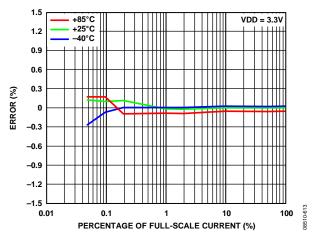

Figure 10. Total Active Energy Error As Percentage of Reading (Gain = +1, Power Factor = 1) over Temperature with Internal Reference and Integrator Off

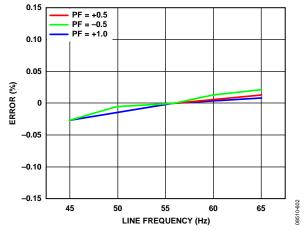

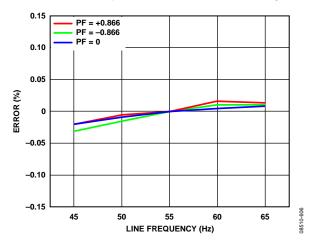

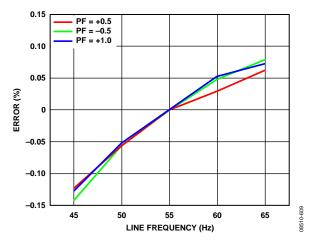

Figure 11. Total Active Energy Error As Percentage of Reading (Gain = +1) over Frequency with Internal Reference and Integrator Off

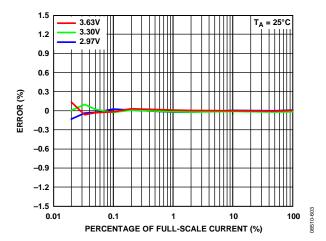

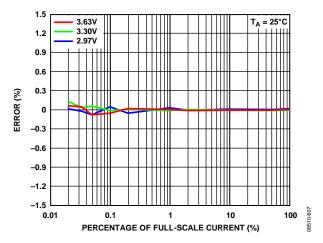

Figure 12. Total Active Energy Error As Percentage of Reading (Gain = +1, Power Factor = 1) over Power Supply with Internal Reference and Integrator Off

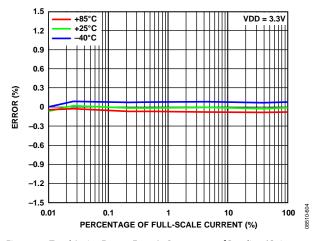

Figure 13. Total Active Energy Error As Percentage of Reading (Gain = +16, Power Factor = 1) over Temperature with Internal Reference and Integrator On

Figure 14. Total Reactive Energy Error As Percentage of Reading (Gain = +1, Power Factor = 0) over Temperature with Internal Reference and Integrator Off

Figure 15. Total Reactive Energy Error As Percentage of Reading (Gain = +1) over Frequency with Internal Reference and Integrator Off

Figure 16. Total Reactive Energy Error As Percentage of Reading (Gain = +1, Power Factor = 0) over Power Supply with Internal Reference and Integrator Off

Figure 17. Total Reactive Energy Error As Percentage of Reading (Gain = +16, Power Factor = 0) over Temperature with Internal Reference and Integrator On

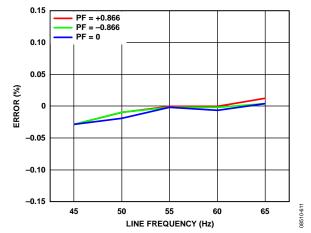

Figure 18. Fundamental Active Energy Error As Percentage of Reading (Gain = +1) over Frequency with Internal Reference and Integrator Off

Figure 19. Fundamental Active Energy Error As Percentage of Reading (Gain = +16) over Temperature with Internal Reference and Integrator On

Figure 20. Fundamental Reactive Energy Error As Percentage of Reading (Gain = +1) over Frequency with Internal Reference and Integrator Off

Figure 21. Fundamental Reactive Energy Error As Percentage of Reading (Gain = +16) over Temperature with Internal Reference and Integrator On

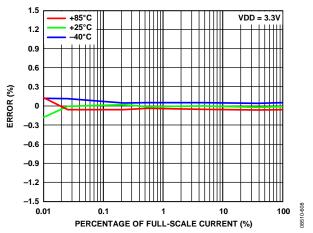

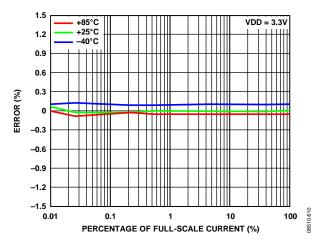

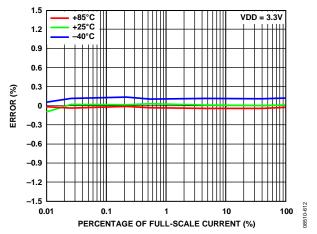

Figure 22. IRMS Error as Percentage of Reading (Gain = +1, Power Factor = 1) over Temperature with Internal Reference and Integrator Off

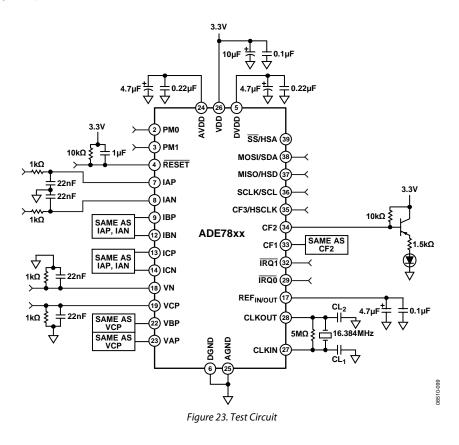

## **TEST CIRCUIT**

Note that in Figure 23, the PM1 and PM0 pins are pulled up internally to 3.3 V. Select the mode of operation by using a microcontroller to programmatically change the pin values.

### **TERMINOLOGY**

### **Measurement Error**

The error associated with the energy measurement made by the ADE7854/ADE7858/ADE7868/ADE7878 is defined by

Measurement Error =

$$\frac{Energy\ Registered\ by\ ADE78xx - True\ Energy}{True\ Energy} \times 100\% \qquad (1)$$

### Power Supply Rejection (PSR)

This quantifies the ADE7854/ADE7858/ADE7868/ADE7878 measurement error as a percentage of reading when the power supplies are varied. For the ac PSR measurement, a reading at nominal supplies (3.3 V) is taken. A second reading is obtained with the same input signal levels when an ac signal (120 mV rms at twice the fundamental frequency) is introduced onto the supplies. Any error introduced by this ac signal is expressed as a percentage of reading—see the Measurement Error definition.

For the dc PSR measurement, a reading at nominal supplies (3.3 V) is taken. A second reading is obtained with the same input signal levels when the power supplies are varied  $\pm 10\%$ . Any error introduced is expressed as a percentage of the reading.

### **ADC Offset Error**

This refers to the dc offset associated with the analog inputs to the ADCs. It means that with the analog inputs connected to AGND, the ADCs still see a dc analog input signal. The magnitude of the offset depends on the gain and input range selection However, the HPF removes the offset from the current and voltage channels and the power calculation remains unaffected by this offset.

#### **Gain Error**

The gain error in the ADCs of the ADE7854/ADE7858/ADE7868/ADE7878 is defined as the difference between the measured ADC output code (minus the offset) and the ideal output code (see the Current Channel ADC section and the Voltage Channel ADC section). The difference is expressed as a percentage of the ideal code.

### **CF Jitter**

The period of pulses at one of the CF1, CF2, or CF3 pins is continuously measured. The maximum, minimum, and average values of four consecutive pulses are computed as follows:

$$\begin{aligned} &Maximum = max(Period_0, Period_1, Period_2, Period_3) \\ &Minimum = min(Period_0, Period_1, Period_2, Period_3) \\ &Average = \frac{Period_0 + Period_1 + Period_2 + Period_3}{4} \end{aligned}$$

The CF jitter is then computed as

$$CF_{JITTER} = \frac{Maximum - Minimum}{Average} \times 100\%$$

(2)

### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below 2 kHz, excluding harmonics and dc. The input signal contains only the fundamental component. The spectral components are calculated over a 2 sec window. The value for SNR is expressed in decibels.

### Signal-to-(Noise and Distortion) Ratio (SINAD)

SINAD is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below 2 kHz, including harmonics but excluding dc. The input signal contains only the fundamental component. The spectral components are calculated over a 2 sec window. The value for SINAD is expressed in decibels.

### **POWER MANAGEMENT**

The ADE7868/ADE7878 have four modes of operation, determined by the state of the PM0 and PM1 pins (see Table 9). The ADE7854/ADE7858 have two modes of operation. These pins provide complete control of the ADE7854/ADE7858/ADE7868/ADE7878 operation and can easily be connected to an external microprocessor I/O. The PM0 and PM1 pins have internal pullup resistors. See Table 11 and Table 12 for a list of actions that are recommended before and after setting a new power mode.

**Table 9. Power Supply Modes**

| Power Supply Modes                    | PM1 | PM0 |

|---------------------------------------|-----|-----|

| PSM0, Normal Power Mode               | 0   | 1   |

| PSM1, Reduced Power Mode <sup>1</sup> | 0   | 0   |

| PSM2, Low Power Mode <sup>1</sup>     | 1   | 0   |

| PSM3, Sleep Mode                      | 1   | 1   |

<sup>&</sup>lt;sup>1</sup> Available in the ADE7868 and ADE7878.

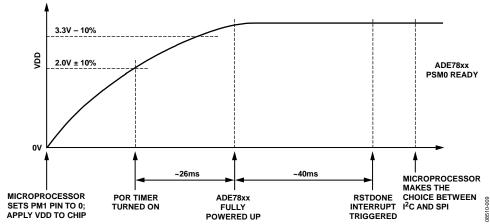

### PSM0—NORMAL POWER MODE (ALL PARTS)

In PSM0 mode, the ADE7854/ADE7858/ADE7868/ADE7878 are fully functional. The PM0 pin is set to high and the PM1 pin is set to low for the ADE78xx to enter this mode. If the ADE78xx is in one of PSM1, PSM2, or PSM3 modes and is switched into PSM0 mode, then all control registers take the default values with the exception of the threshold register, LPOILVL, which is used in PSM2 mode, and the CONFIG2 register, both of which maintain their values.

The ADE7854/ADE7858/ADE7868/ADE7878 signal the end of the transition period by triggering the  $\overline{IRQ1}$  interrupt pin low and setting Bit 15 (RSTDONE) in the STATUS1 register to 1. This bit is 0 during the transition period and becomes 1 when the transition is finished. The status bit is cleared and the  $\overline{IRQ1}$  pin is set back to high by writing to the STATUS1 register with the corresponding bit set to 1. Bit 15 (RSTDONE) in the interrupt mask register does not have any functionality attached even if the  $\overline{IRQ1}$  pin goes low when Bit 15 (RSTDONE) in the STATUS1 register is set to 1. This makes the RSTDONE interrupt unmaskable.

# PSM1—REDUCED POWER MODE (ADE7868, ADE7878 ONLY)

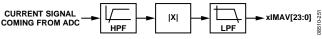

The reduced power mode, PSM1, is available on the ADE7868 and ADE7878 only. In this mode, the ADE7868/ADE7878 measure the mean absolute values (mav) of the 3-phase currents and store the results in the AIMAV, BIMAV, and CIMAV 20-bit registers. This mode is useful in missing neutral cases in which the voltage supply of the ADE7868 or ADE7878 is provided by an external battery. The serial ports, I<sup>2</sup>C or SPI, are enabled in this mode; the active port can be used to read the AIMAV, BIMAV, and CIMAV registers. It is not recommended to read any of the other registers because their values are not guaranteed in this mode. Similarly, a write operation is not taken into account by the ADE7868/ADE7878 in this mode.

In summary, in this mode, it is not recommended to access any register other than AIMAV, BIMAV, and CIMAV. The circuit that measures these estimates of rms values is also active during PSM0; therefore, its calibration can be completed in either PSM0 mode or in PSM1 mode. Note that the ADE7868 and ADE7878 do not provide any register to store or process the corrections resulting from the calibration process. The external microprocessor stores the gain values in connection with these measurements and uses them during PSM1 (see the Current Mean Absolute Value Calculation—ADE7868 and ADE7878 Only section for more details on the xIMAV registers).

The 20-bit mean absolute value measurements done in PSM1, although available also in PSM0, are different from the rms measurements of phase currents and voltages executed only in PSM0 and stored in the xIRMS and xVRMS 24-bit registers. See the Current Mean Absolute Value Calculation—ADE7868 and ADE7878 Only section for details.

If the ADE7868/ADE7878 is set in PSM1 mode while still in the PSM0 mode, the ADE7868/ADE7878 immediately begin the mean absolute value calculations without any delay. The xIMAV registers are accessible at any time; however, if the ADE7878 or ADE7868 is set in PSM1 mode while still in PSM2 or PSM3 modes, the ADE7868/ADE7878 signal the start of the mean absolute value computations by triggering the  $\overline{1RQ1}$  pin low. The xIMAV registers can be accessed only after this moment.

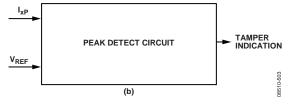

# PSM2—LOW POWER MODE (ADE7868, ADE7878 ONLY)

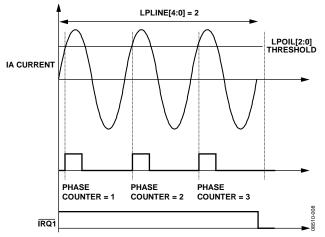

The low power mode, PSM2, is available on the ADE7868 and ADE7878 only. In this mode, the ADE7868/ADE7878 compare all phase currents against a threshold for a period of  $0.02 \times (LPLINE[4:0] + 1)$  seconds, independent of the line frequency. LPLINE[4:0] are Bits[7:3] of the LPOILVL register (see Table 10).

Table 10. LPOILVL Register

| Bit   | Mnemonic    | Default | Description                                                                    |

|-------|-------------|---------|--------------------------------------------------------------------------------|

| [2:0] | LPOIL[2:0]  | 111     | Threshold is put at a value corresponding to full scale multiplied by LPOIL/8. |

| [7:3] | LPLINE[4:0] | 00000   | The measurement period is (LPLINE[4:0] + 1)/50 sec.                            |

The threshold is derived from Bits[2:0] (LPOIL[2:0]) of the LPOILVL register as LPOIL[2:0]/8 of full scale. Every time one phase current becomes greater than the threshold, a counter is incremented. If every phase counter remains below LPLINE[4:0] + 1 at the end of the measurement period, then the  $\overline{IRQ0}$  pin is triggered low. If a single phase counter becomes greater or equal to LPLINE[4:0] + 1 at the end of the measurement period, the  $\overline{IRQ1}$  pin is triggered low. Figure 24 illustrates how the ADE7868/ADE7878 behave in PSM2 mode when LPLINE[4:0] = 2 and LPOIL[2:0] = 3. The test period is three 50 Hz cycles (60 ms), and the Phase A current rises above the LPOIL[2:0] threshold three times. At the end of the test period, the  $\overline{IRQ1}$  pin is triggered low.

Figure 24. PSM2 Mode Triggering  $\overline{IRQ1}$  Pin for LPLINE[4:0] = 2 (50 Hz Systems)

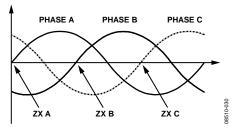

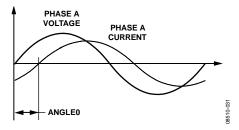

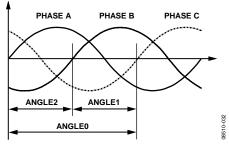

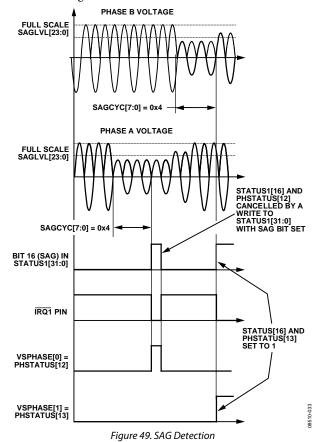

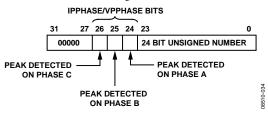

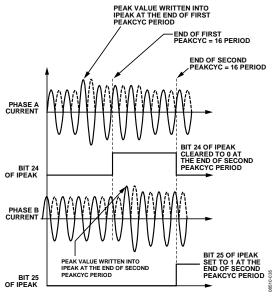

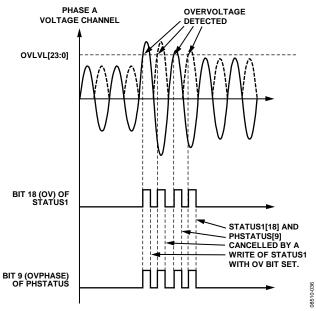

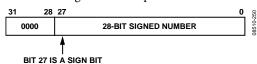

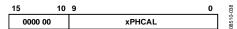

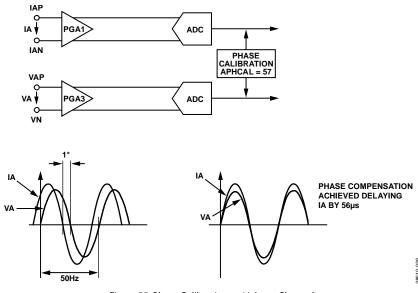

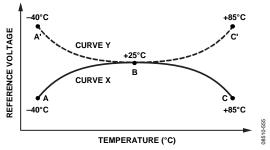

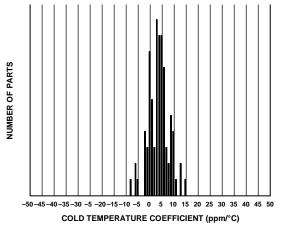

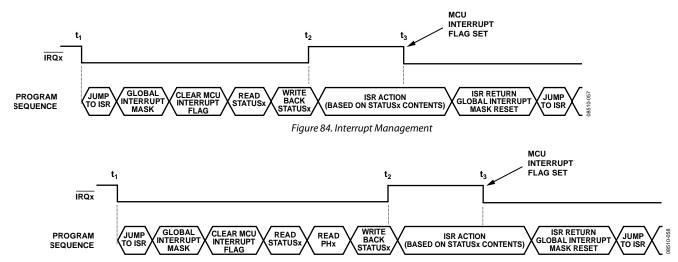

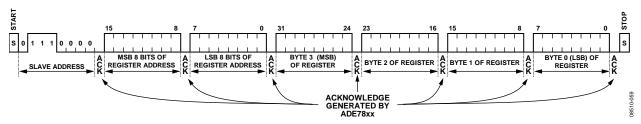

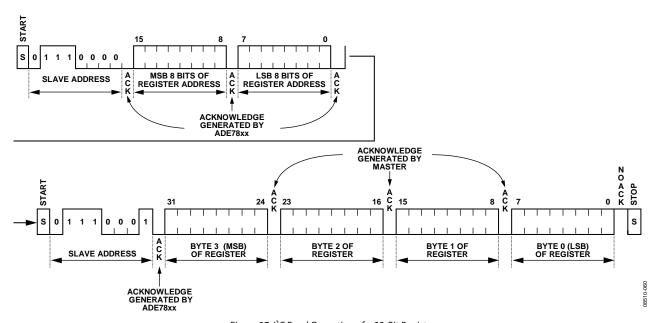

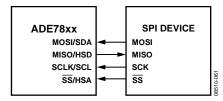

Figure 25. PSM2 Low Power Mode Peak Detection