# Isolated Energy Metering Chipset for Polyphase Shunt Meters

ADE7978/ADE7933/ADE7932/ADE7923

### **FEATURES**

**Data Sheet**

Enables shunt current sensors in polyphase energy meters Immune to magnetic tampering Highly accurate; supports EN 50470-1, EN 50470-3, IEC 62053-21, IEC 62053-22, IEC 62053-23, ANSI C12.20, and IEEE 1459 standards

Compatible with 3-phase, 3- or 4-wire (delta or wye) meters and other 3-phase services

Computes active, reactive, and apparent energy on each phase and on the overall system

Less than 0.2% error in active and reactive energy over a dynamic range of 2000 to 1 at  $T_A = 25^{\circ}C$

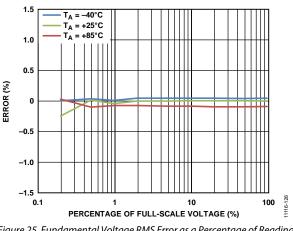

Less than 0.1% error in voltage rms over a dynamic range of 500 to 1 at  $T_A = 25^{\circ}C$

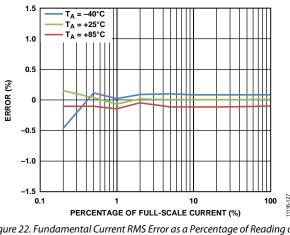

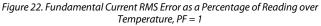

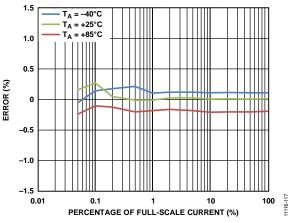

Less than 0.25% error in current rms over a dynamic range of 500 to 1 at  $T_A = 25^{\circ}C$

Power quality measurements including total harmonic distortion (THD)

Single 3.3 V supply

Rev. D

Operating temperature: -40°C to +85°C

### Flexible I<sup>2</sup>C, SPI, and HSDC serial interfaces Safety and regulatory approvals UL recognition 5000 V rms for 1 minute per UL 1577 CSA Component Acceptance Notice 5A

IEC 61010-1: 300 V rms maximum working voltage VDE certificate of conformity DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 V<sub>IORM</sub> = 846 V peak

Optional isolated (ADE7933/ADE7932) or nonisolated (ADE7923) neutral

### **APPLICATIONS**

Shunt-based polyphase meters Power quality monitoring Solar inverters Process monitoring Protective devices Isolated sensor interfaces Industrial PLCs

<sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; 7,075,329; 6,262,600; 7,489,526; 7,558,080; and 8,892,933. Other patents are pending.

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013–2018 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

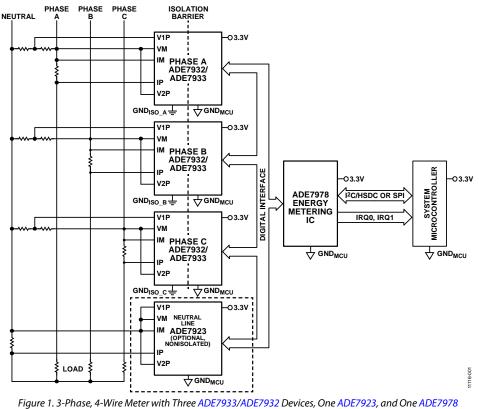

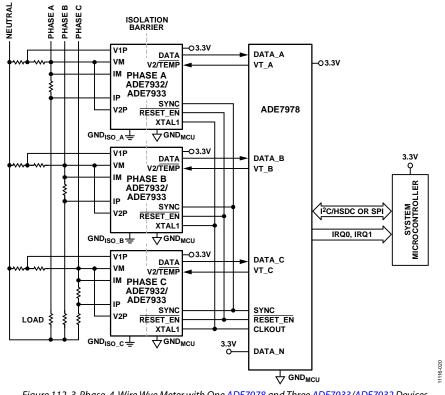

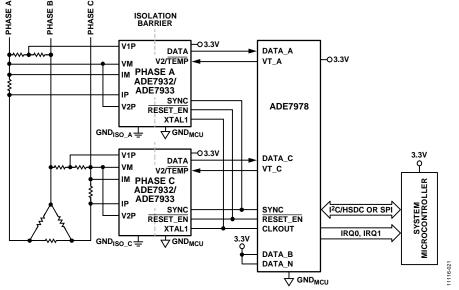

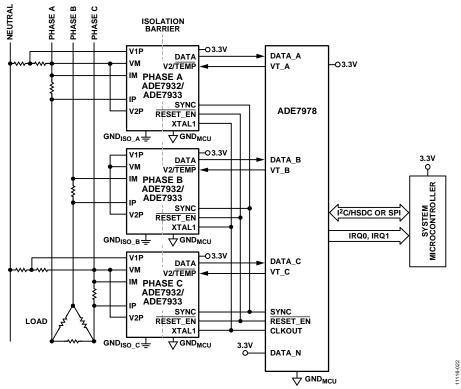

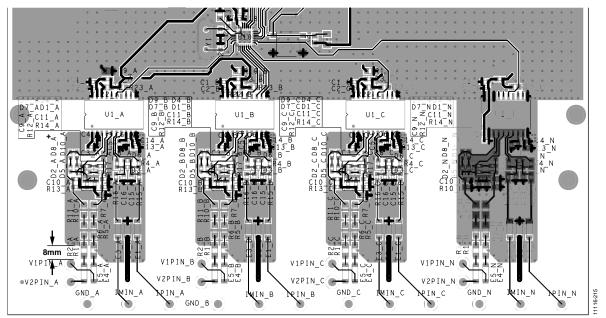

### **TYPICAL APPLICATION CIRCUIT**

# TABLE OF CONTENTS

| Features                                                                                |

|-----------------------------------------------------------------------------------------|

| Applications1                                                                           |

| Typical Application Circuit1                                                            |

| Revision History 4                                                                      |

| General Description                                                                     |

| Functional Block Diagrams                                                               |

| Specifications                                                                          |

| System Specifications, ADE7978 and ADE7933/ADE7932/ADE7923                              |

| ADE7978 Specifications10                                                                |

| ADE7933/ADE7932 Specifications14                                                        |

| ADE7923 Specifications17                                                                |

| Absolute Maximum Ratings19                                                              |

| Thermal Resistance                                                                      |

| ESD Caution19                                                                           |

| Pin Configurations and Function Descriptions                                            |

| Typical Performance Characteristics                                                     |

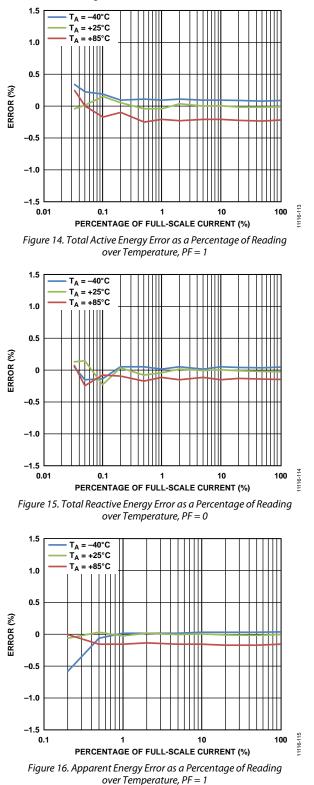

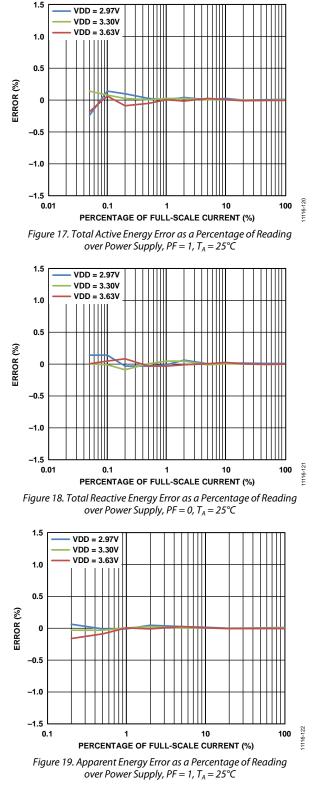

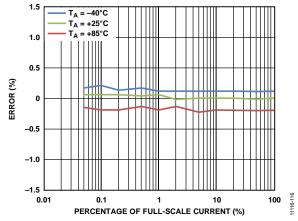

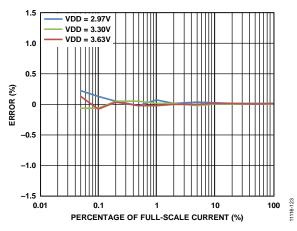

| Total Energy Linearity over Supply and Temperature                                      |

| Fundamental Energy and RMS Linearity with Fifth<br>Harmonic over Supply and Temperature |

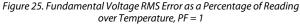

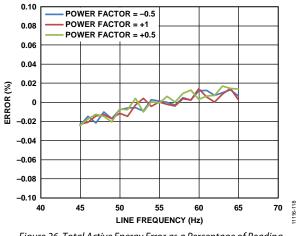

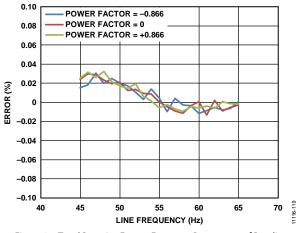

| Total Energy Error over Frequency                                                       |

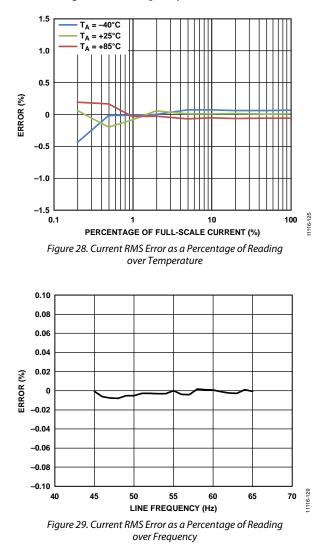

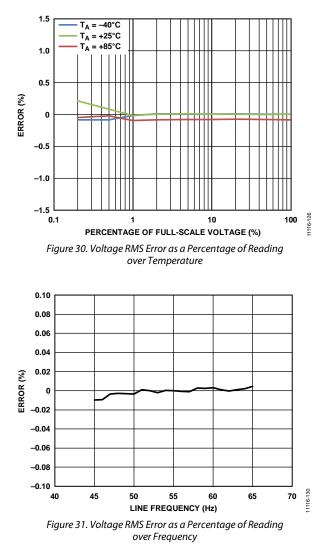

| RMS Linearity over Temperature and RMS Error over                                       |

| Frequency                                                                               |

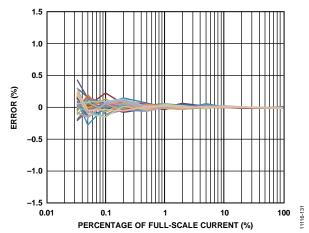

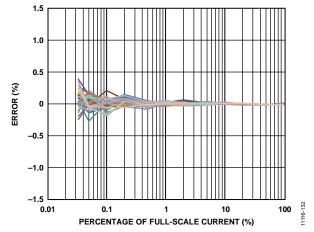

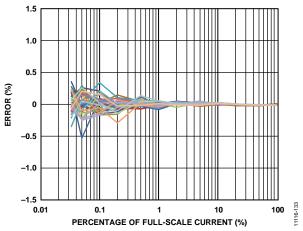

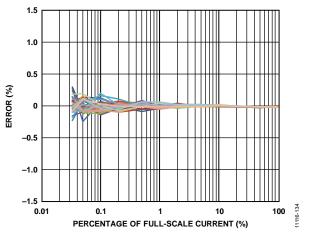

| Energy Linearity Repeatability                                                          |

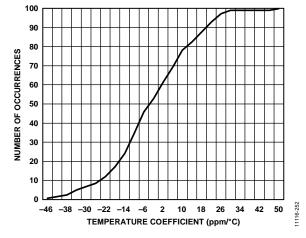

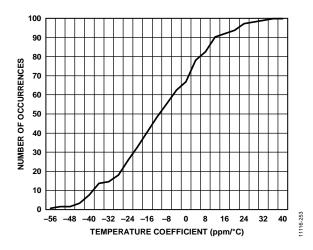

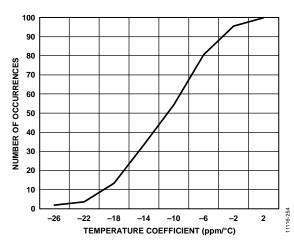

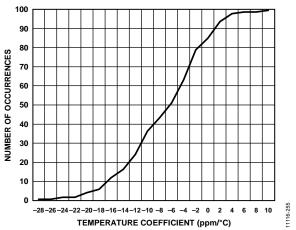

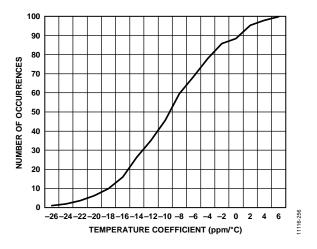

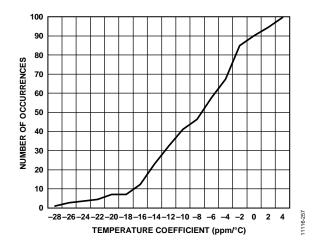

| Cumulative Histograms of ADC Gain Temperature<br>Coefficients                           |

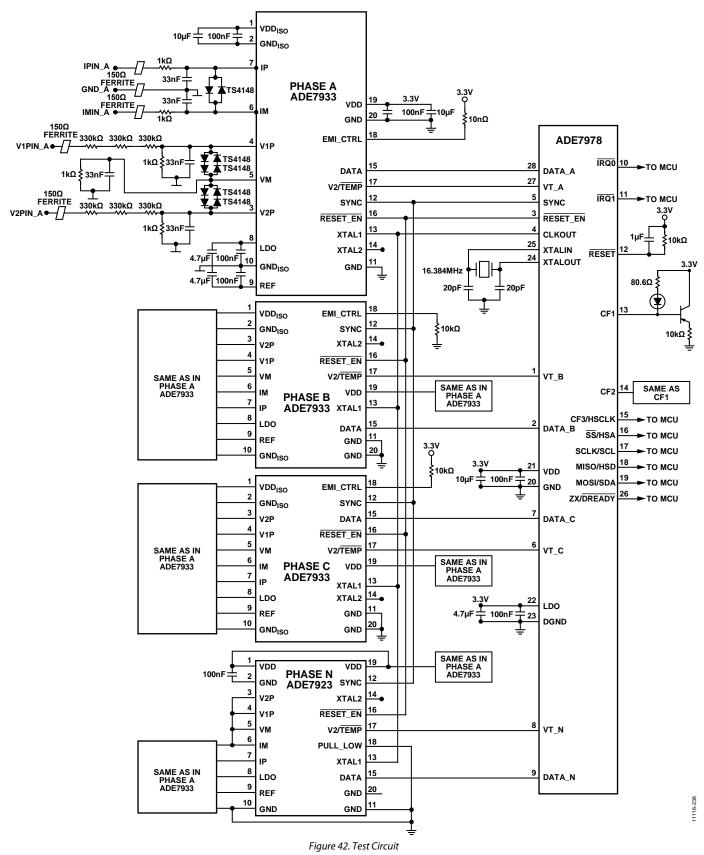

| Test Circuit                                                                            |

| Terminology                                                                             |

| Theory of Operation                                                                     |

| ADE7933/ADE7932/ADE7923 Analog Inputs                                                   |

| Analog-to-Digital Conversion                                                            |

| Current Channel ADC                                                                     |

| Voltage Channel ADCs                                                                    |

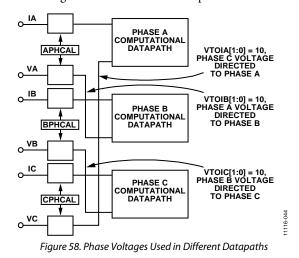

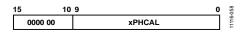

| Changing the Phase Voltage Datapath                                                     |

| Reference Circuits                                                                      |

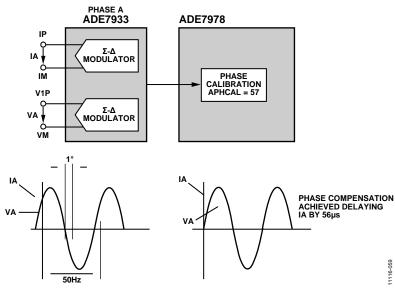

| Phase Compensation                                                                      |

| Digital Signal Processor                                                                |

| Power Quality Measurements                                                              |

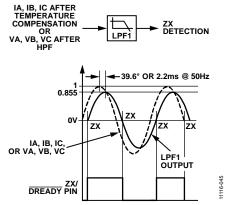

| Zero-Crossing Detection                                                                 |

| Period Measurement                                                                      |

| Phase Voltage Sag Detection                                                             |

|   | Peak Detection                                                        | . 51 |

|---|-----------------------------------------------------------------------|------|

|   | Overvoltage and Overcurrent Detection                                 | . 52 |

|   | Neutral Current Mismatch                                              | . 53 |

| ] | Root Mean Square Measurement                                          | . 54 |

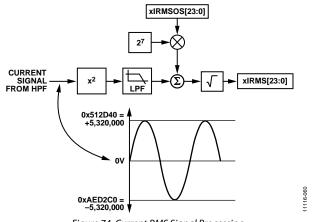

|   | Current RMS Calculation                                               | . 54 |

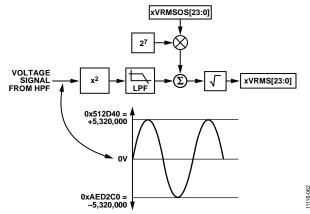

|   | Voltage RMS Calculation                                               | . 55 |

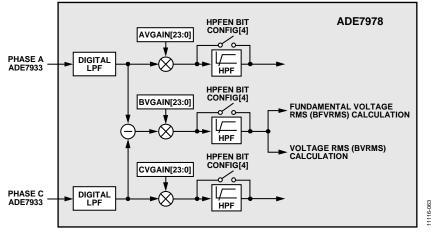

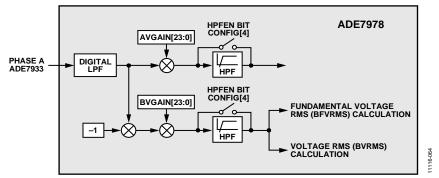

|   | Voltage RMS in Delta Configurations                                   | . 56 |

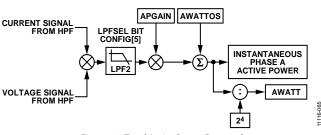

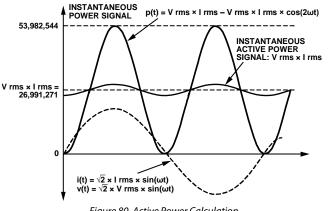

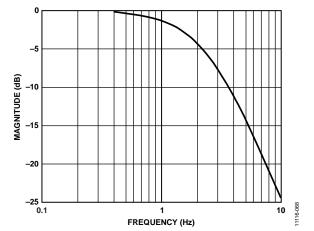

|   | Active Power Calculation                                              | . 57 |

|   | Total Active Power Calculation                                        | . 57 |

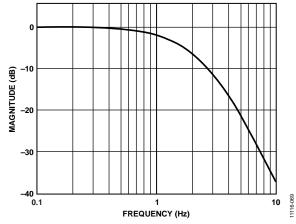

|   | Fundamental Active Power Calculation                                  | . 58 |

|   | Active Power Gain Calibration                                         | . 58 |

|   | Active Power Offset Calibration                                       | . 59 |

|   | Sign of Active Power Calculation                                      | . 59 |

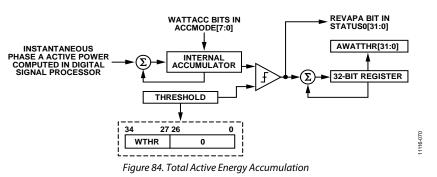

|   | Active Energy Calculation                                             | . 59 |

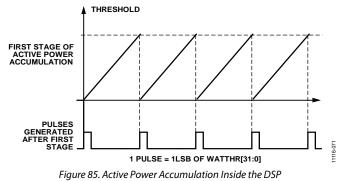

|   | Integration Time Under Steady Load                                    | . 60 |

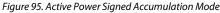

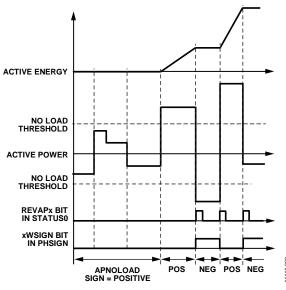

|   | Energy Accumulation Modes                                             | . 61 |

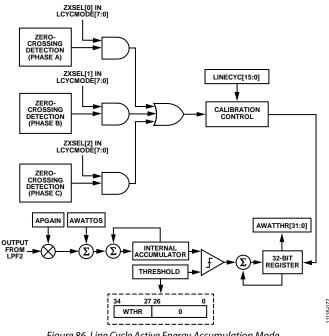

|   | Line Cycle Active Energy Accumulation Mode                            | . 61 |

| ] | Reactive Power Calculation                                            | . 63 |

|   | Total Reactive Power Calculation                                      | . 63 |

|   | Fundamental Reactive Power Calculation                                | . 63 |

|   | Reactive Power Gain Calibration                                       | . 63 |

|   | Reactive Power Offset Calibration                                     | . 63 |

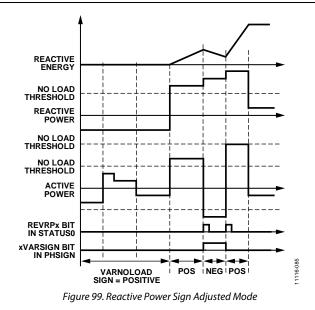

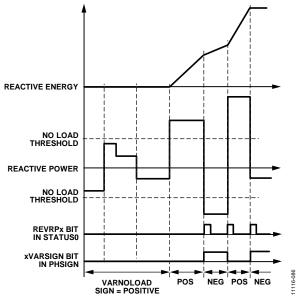

|   | Sign of Reactive Power Calculation                                    | . 64 |

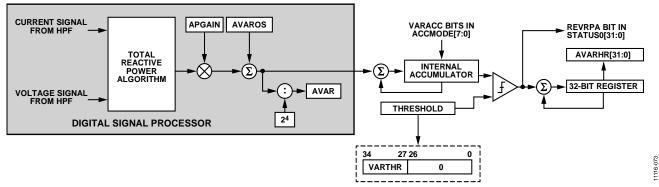

|   | Reactive Energy Calculation                                           | . 64 |

|   | Integration Time Under Steady Load                                    | . 65 |

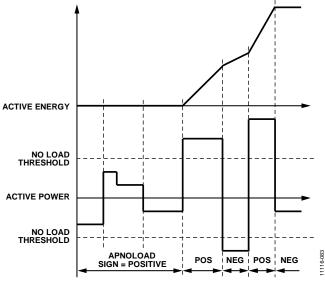

|   | Energy Accumulation Modes                                             | . 66 |

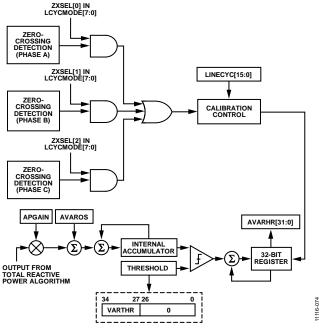

|   | Line Cycle Reactive Energy Accumulation Mode                          | . 66 |

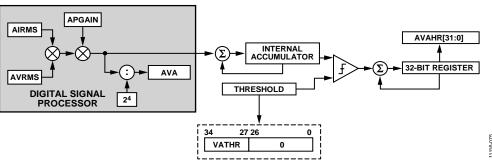

|   | Apparent Power Calculation                                            | . 67 |

|   | Apparent Power Gain Calibration                                       | . 67 |

|   | Apparent Power Offset Calibration                                     | . 67 |

|   | Apparent Power Calculation Using VNOM                                 | . 67 |

|   | Apparent Energy Calculation                                           | . 68 |

|   | Integration Time Under Steady Load                                    | . 69 |

|   | Energy Accumulation Mode                                              | . 69 |

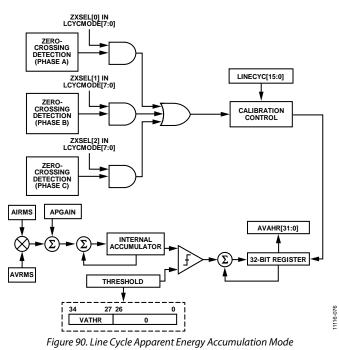

|   | Line Cycle Apparent Energy Accumulation Mode                          | . 69 |

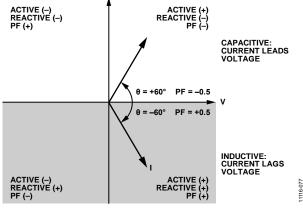

|   | Power Factor Calculation and Total Harmonic Distortion<br>Calculation | . 70 |

|   | Power Factor Calculation                                              | . 70 |

|   | Total Harmonic Distortion Calculation                                 | . 71 |

| 1 | Waveform Sampling Mode                                                | . 72 |

|   | 1 6                                                                   |      |

## **Data Sheet**

# ADE7978/ADE7933/ADE7932/ADE7923

| Low Power Mode                                                               | 86  |

|------------------------------------------------------------------------------|-----|

| Applications Information                                                     | 87  |

| Differences Between the ADE7923 and the ADE7933/ADE7932                      | 87  |

| ADE7978, ADE7933/ADE7932 and ADE7923 in Polypl<br>Energy Meters              |     |

| ADE7978 Quick Setup as an Energy Meter                                       | 90  |

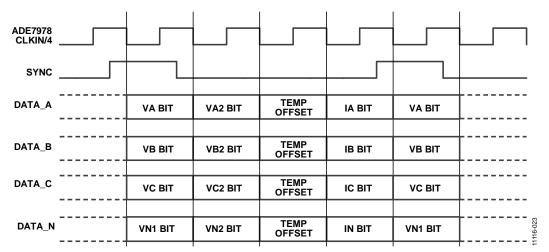

| Bit Stream Communication Between the ADE7978 and ADE7933/ADE7932 and ADE7923 |     |

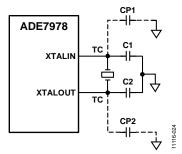

| ADE7978, ADE7933/ADE7932, and ADE7923 Clocks                                 | 92  |

| Insulation Lifetime                                                          | 92  |

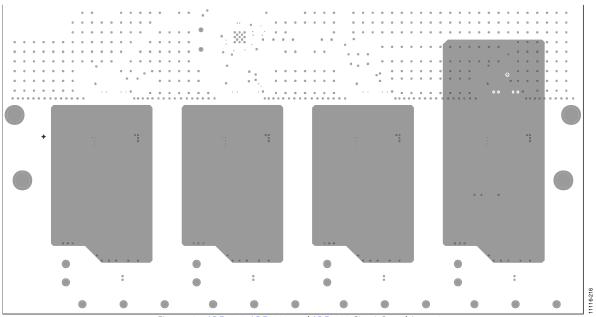

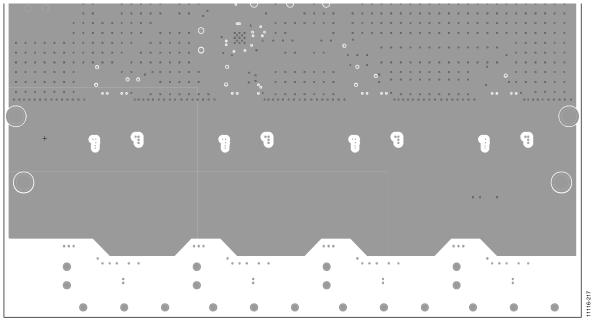

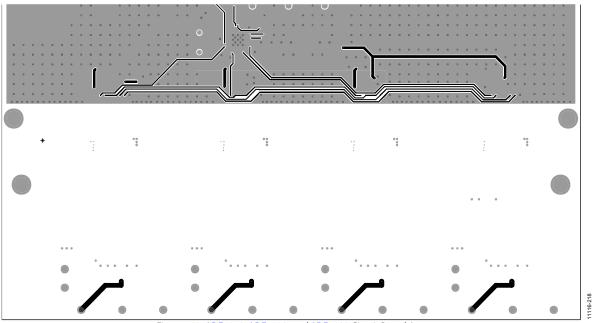

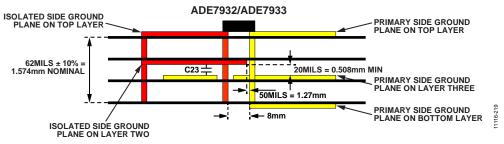

| Layout Guidelines                                                            | 93  |

| ADE7978 and ADE7933/ADE7932 Evaluation Board                                 | 96  |

| ADE7978 Die Version                                                          | 96  |

| Serial Interfaces                                                            | 97  |

| Serial Interface Selection                                                   | 97  |

| Communication Verification                                                   | 97  |

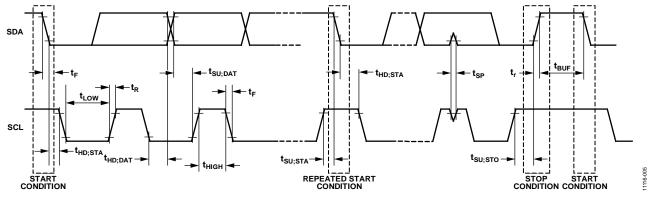

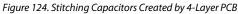

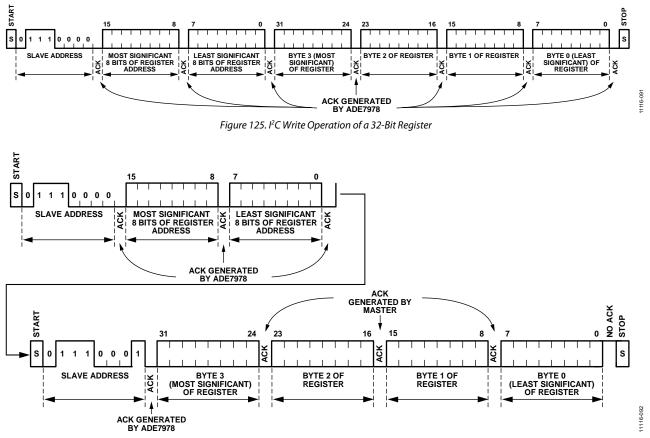

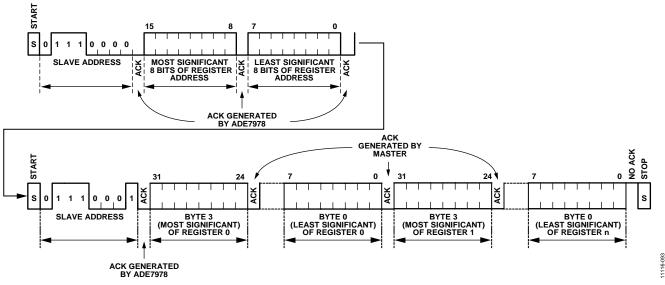

| I <sup>2</sup> C-Compatible Interface                                        | 97  |

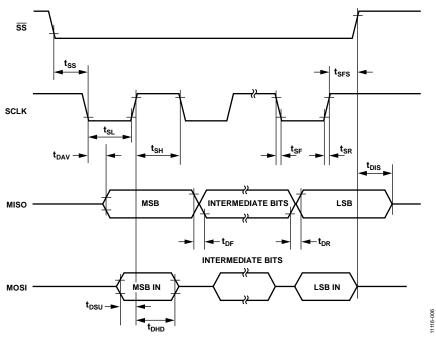

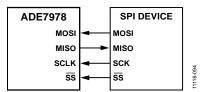

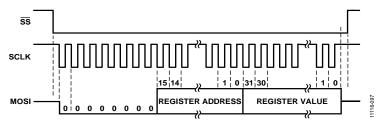

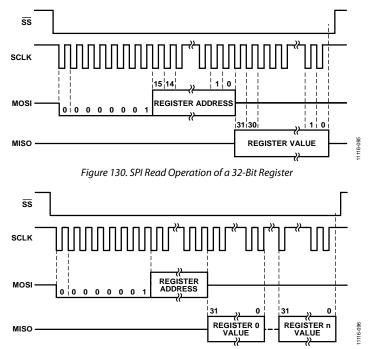

| SPI-Compatible Interface                                                     | 100 |

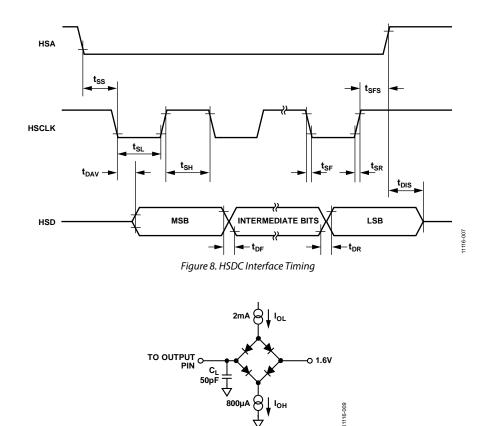

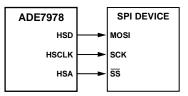

| HSDC Interface                                                               | 102 |

| Checksum Register                                                            | 104 |

| Register List                                                                | 105 |

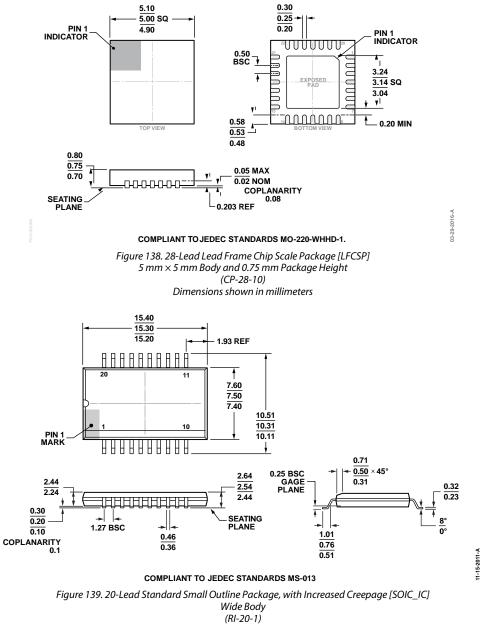

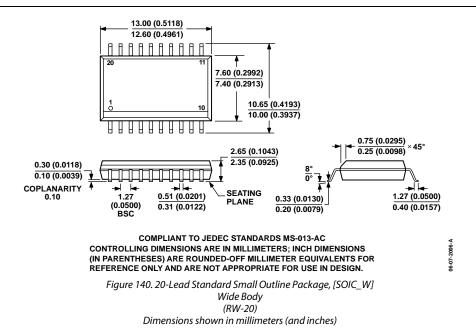

| Outline Dimensions                                                           | 124 |

| Ordering Guide                                                               | 125 |

|                                                                              |     |

### **REVISION HISTORY**

| 2/2018—Rev. C to Rev. D    |     |

|----------------------------|-----|

| Changes to Table 7         |     |

| Updated Outline Dimensions |     |

| Changes to Ordering Guide  | 125 |

### 12/2016—Rev. B to Rev. C

| Changed CP-28-6 to CP-28-10 Throughout                   |

|----------------------------------------------------------|

| Change to Note 1 1                                       |

| Change to Clock Frequency, XTAL 1 Parameter and XTAL 1   |

| Duty Cycle Parameter 17                                  |

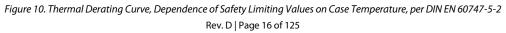

| Changes to Figure 11 20                                  |

| Changes to Table 15 22                                   |

| Changes to Table 16                                      |

| Changes to Terminolgy Section                            |

| Changes to Figure 9775                                   |

| Changes to DC-to-DC Converter Section 82                 |

| Changes to Applications Information Section              |

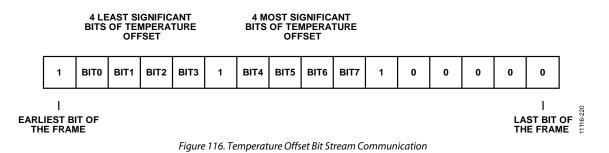

| Changes to Bit Stream Communications Between the ADE7978 |

| and the ADE7933/ADE7932 and AD7923 Section, Figure 115,  |

| and Figure 116                                           |

| Updated Outline Dimensions 124                           |

| Changes to Ordering Guide 125                            |

|                                                          |

### 3/2015-Rev. A to Rev. B

| Changes to Features Section1                                   |

|----------------------------------------------------------------|

| Changed Fundamental Active Power to Fundamental Active         |

| Energy; Table 1                                                |

| Changes to Table 614                                           |

| Changes to Regulatory Approvals Section and Table 7 15         |

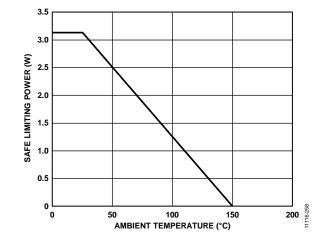

| Changes to Table 9 and Figure 1016                             |

| Changes to Table 13 and Related Text 19                        |

| Added Cumulative Histograms of ADC Gain Temperature            |

| Coefficients Section                                           |

| Change to Terminology Section                                  |

| Changes to ADC Transfer Function Section                       |

| Changes to Insulation Lifetime Section and Deleted Figure 114; |

| Renumbered Sequentially                                        |

| Changes to Layout Guidelines Section                           |

| Changes to Address 0xE701, Address 0xE709, Address 0xE70A,     |

| Address 0xE70B, and Address 0xE70C; Table 42110                |

| Changes to Bit 7 Default Value; Table 57121                    |

#### 12/2014—Rev. 0 to Rev. A

| Added ADE7923                            | Universal |

|------------------------------------------|-----------|

| Reorganized Layout                       | Universal |

| Changes to Features Section and Figure 1 | 1         |

| Changes to General Description Section   |           |

| Moved Revision History Section           |           |

| Changes to Figure 3 and Figure 4         | 7         |

| Changes to Table 18Changes to Table 614Change to Climatic Classification Parameter, Table 815Added ADE7923 Specifications Section and Table 10;7Renumbered Sequentially17Changes to Table 1420Changes to Figure 1223Added Total Energy Linearity over Supply and TemperatureSection25Changes to Figure 17, Figure 18, and Figure 1925Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error over7Frequency Section28Added Energy Linearity Repeatability Section29Changes to Figure 4630Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Voltage Channel ADCs Section38Changes to Figure 4969Changes to Figure 10133Changes to Figure 10284Changes to Figure 10373Changes to Figure 10486Changes to Figure 10586Changes to Figure 10681Changes to Figure 10781Changes to Figure 10886Changes to Figure 10984Changes to Figure 10183Changes to Figure 10284Changes to Figure 10373Changes to Figure 10586                                                                                                                                                 | Added Figure 5; Renumbered Sequentially                  | 8     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------|

| Change to Climatic Classification Parameter, Table 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Changes to Table 1                                       | 8     |

| Added ADE7923 Specifications Section and Table 10;Renumbered Sequentially17Changes to Table 1420Changes to Figure 1223Added Figure 13 and Table 1624Added Total Energy Linearity over Supply and Temperature25Changes to Figure 17, Figure 18, and Figure 1925Changes to Figure 21, Figure 18, and Figure 1926Added Total Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error over29Changes to Figure 3630Changes to Figure 4134Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Figure 4536Changes to Voltage Channel ADCs Section38Changes to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10384Changes to Figure 104ADE7933/ADE7932 and ADE7932 and ADE7923 inPolyphase Energy Meters Section36Changes to Figure 10587Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 115 and Figure 11894Changes to Figure 117 and Figure 11894Changes to Figure 117 and Figure 11693Changes t                                                                    | Changes to Table 6                                       | 14    |

| Renumbered Sequentially17Changes to Table 1420Changes to Figure 1223Added Figure 13 and Table 1624Added Total Energy Linearity over Supply and TemperatureSection25Changes to Figure 17, Figure 18, and Figure 1925Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added Energy Linearity over Temperature and RMS Error over29Changes to Figure 3630Changes to Figure 3630Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Figure 4969Changes to Figure 8773Changes to Figure 8773Changes to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10386Changes to Figure 10486Changes to Figure 10587Changes to Figure 10587Changes to Figure 115 and Figure 11693Changes to Figure 115 and Figure 11894Changes to                                                                                                                          | Change to Climatic Classification Parameter, Table 8     | 15    |

| Renumbered Sequentially17Changes to Table 1420Changes to Figure 1223Added Figure 13 and Table 1624Added Total Energy Linearity over Supply and TemperatureSection25Changes to Figure 17, Figure 18, and Figure 1925Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added Energy Linearity over Temperature and RMS Error over29Changes to Figure 3630Changes to Figure 3630Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Figure 4969Changes to Figure 8773Changes to Figure 8773Changes to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10386Changes to Figure 10486Changes to Figure 10587Changes to Figure 10587Changes to Figure 115 and Figure 11693Changes to Figure 115 and Figure 11894Changes to                                                                                                                          | -                                                        |       |

| Changes to Table 1420Changes to Figure 1223Added Figure 13 and Table 1624Added Total Energy Linearity over Supply and Temperature25Changes to Figure 17, Figure 18, and Figure 1925Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added Total Energy Error over Frequency Section27Added Energy Linearity over Temperature and RMS Error over29Changes to Figure 3630Changes to Figure 3630Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Versampling Section35Changes to Figure 4969Changes to Figure 8773Changes to Figure 8773Changes to Figure 8773Changes to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10386Changes to Figure 10486Changes to Figure 10587Changes to Figure 10587Changes to Figure 10587Changes to Figure 115 and Figure 11693Changes to Figure 11781Changes to Figure 115 and Figure 11894Changes to Figure 11995Changes to Figure 115 and Figure 11894Changes to Figure 115 and Figure 11894Changes to                                                                                                                                    | -                                                        | 17    |

| Changes to Figure 1223Added Figure 13 and Table 1624Added Total Energy Linearity over Supply and TemperatureSection25Changes to Figure 17, Figure 18, and Figure 1925Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error overFrequency Section28Added Energy Linearity Repeatability Section29Changes to Figure 3630Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Vortage Channel ADCs Section37Changes to Figure 4536Changes to Figure 4969Changes to Figure 8773Changes to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10381Changes to Figure 10483Changes to Figure 10586Changes to Figure 10386Changes to Figure 10483Changes to Figure 10586Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Figure 117 and Figure 11894Changes to Figure 115 and Figure 11894Changes to Figure 115 and Figure 11693Changes to Figure 115 and Fig                                                                                                                 | - ,                                                      |       |

| Added Figure 13 and Table 1624Added Total Energy Linearity over Supply and TemperatureSection25Changes to Figure 17, Figure 18, and Figure 1925Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error over28Frequency Section29Changes to Figure 3630Changes to Figure 3630Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Voltage Channel ADCs Section38Changes to Figure 4536Changes to Figure 4536Changes to Figure 8773Changes to Figure 8773Changes to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10386Added Difference Between the ADE7923 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 119 and Figure 11693Changes to Figure 119 and Figure 11894Changes to Figure 11995Changes to Figure 11995Changes to Figure 11995Changes to Fig                                                                                                        |                                                          |       |

| Added Total Energy Linearity over Supply and TemperatureSection25Changes to Figure 17, Figure 18, and Figure 1925Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error over28Frequency Section28Added Energy Linearity Repeatability Section29Changes to Figure 3630Changes to Figure 3630Changes to Figure 4134Changes to Figure 4536Changes to Versampling Section35Changes to Vortage Channel ADCs Section38Changes to Figure 4536Changes to Figure 8773Changes to Figure 8773Changes to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10387Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section36Added Difference Between the ADE7923 and theAdded Singure 115 and Figure 11693< |                                                          |       |

| Section25Changes to Figure 17, Figure 18, and Figure 1925Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error overFrequency Section28Added Energy Linearity Repeatability Section29Changes to Figure 3630Changes to Figure 3630Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Versampling Section35Changes to Voltage Channel ADCs Section38Changes to Figure 8773Changes to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10183Changes to Figure 10284Changes to Figure 10371Changes to Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section92Changes to Figure 10587Changes to Figure 10587Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Table 61122Updated Outline Dimensions123Added Figure 145124                                                                                                                                                                                                                                       | -                                                        |       |

| Changes to Figure 17, Figure 18, and Figure 19.25Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 24.26Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error over29Frequency Section28Added Energy Linearity Repeatability Section29Changes to Figure 36.30Changes to Figure 41.34Changes to Figure 45.36Changes to Figure 45.36Changes to Figure 45.36Changes to Voltage Channel ADCs Section38Changes to Figure 87.73Changes to Figure 87.73Changes to Figure 101.83Changes to Figure 102.84Changes to Figure 103.71Changes to Figure 104. and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section36Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 115 and Figure 116.93Changes to Figure 117 and Figure 118.94Changes to Figure 119.95Changes to Figure 1145.124                                                                                                                                                                                                                                                                                                           |                                                          |       |

| Added Fundamental Energy and RMS Linearity with FifthHarmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error over28Added Energy Linearity Repeatability Section29Changes to Figure 3630Changes to Figure 3630Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Voltage Channel ADCs Section37Changes to Figure 4969Changes to Figure 8773Change to Figure 8773Change to Figure 10183Changes to Figure 10284Changes to Figure 10387Changes to Figure 10484Changes to Figure 10586Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Figure 11925Changes to Figure 11925Changes to Figure 11925Changes to Figure 114124                                                                                                                                                                                                                                                                                                                                                           |                                                          |       |

| Harmonic over Supply and Temperature Section26Changes to Figure 21 and Figure 2426Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error over29Changes to Figure 3630Changes to Figure 3630Changes to Figure 4134Changes to Figure 4536Changes to Figure 4536Changes to Voltage Channel ADCs Section37Changes to Figure 4969Changes to Figure 8773Changes to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10387Changes to Figure 10483Changes to Figure 10584Changes to Figure 10587Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Figure 115124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Added Fundamental Energy and RMS Linearity with Fifth    | h     |

| Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error overFrequency Section28Added Energy Linearity Repeatability Section29Changes to Figure 3630Change to Crosstalk Section32Changes to Figure 4134Changes to Figure 4536Changes to Oversampling Section35Changes to Figure 4536Changes to Voltage Channel ADCs Section38Changes to Figure 4969Changes to Reference Circuits Section43Change to Figure 8773Change to Figure 10183Changes to Figure 10284Changes to Figure 10384Changes to Figure 10284Changes to Figure 10386Added Difference Between the ADE7923 and the86Added Difference Between the ADE7923 and the86ADE7933/ADE7932 Section86Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Figure 11995Changes to Figure 119124                                                                                                                                                                                                                                                                                                                                                                                                                      | e                                                        |       |

| Added Total Energy Error over Frequency Section27Added RMS Linearity over Temperature and RMS Error overFrequency Section28Added Energy Linearity Repeatability Section29Changes to Figure 3630Change to Crosstalk Section32Changes to Figure 4134Changes to Figure 4536Changes to Oversampling Section35Changes to Figure 4536Changes to Voltage Channel ADCs Section38Changes to Figure 4969Changes to Reference Circuits Section43Change to Figure 8773Change to Figure 10183Changes to Figure 10284Changes to Figure 10384Changes to Figure 10284Changes to Figure 10386Added Difference Between the ADE7923 and the86Added Difference Between the ADE7923 and the86ADE7933/ADE7932 Section86Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Figure 11995Changes to Figure 119124                                                                                                                                                                                                                                                                                                                                                                                                                      | Changes to Figure 21 and Figure 24                       | 26    |

| Added RMS Linearity over Temperature and RMS Error overFrequency Section28Added Energy Linearity Repeatability Section29Changes to Figure 3630Change to Crosstalk Section32Changes to Figure 4134Changes to Figure 4134Changes to Figure 4536Changes to Oversampling Section35Changes to Voltage Channel ADCs Section38Changes to Figure 4969Changes to Figure 8773Change to Figure 8773Change to Figure 10183Changes to Figure 10284Changes to Figure 10384Changes to Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Figure 119124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |       |

| Frequency Section28Added Energy Linearity Repeatability Section29Changes to Figure 3630Change to Crosstalk Section32Changes to Figure 4134Changes to Figure 4134Changes to Oversampling Section35Changes to Figure 4536Changes to Current Waveform Gain Registers Section37Changes to Voltage Channel ADCs Section38Changes to Figure 4969Changes to Reference Circuits Section43Change to Figure 8773Change to Figure 8773Changes to Figure 10183Changes to Figure 10284Changes to Figure 10284Changes to Figure 103Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 in86Polyphase Energy Meters Section86Added Difference Between the ADE7923 and the86ADE7933/ADE7932 Section86Changes to Figure 10587Changes to Figure 117 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 117 and Figure 11894Changes to Table 61122Updated Outline Dimensions123Added Figure 145124                                                                                                                                                                                                                                                                                                                                                         |                                                          |       |

| Added Energy Linearity Repeatability Section29Changes to Figure 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | • =                                                      |       |

| Changes to Figure 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 1                                                      |       |

| Change to Crosstalk Section32Changes to Figure 41.34Changes to Figure 41.35Changes to Oversampling Section35Changes to Figure 45.36Changes to Current Waveform Gain Registers Section37Changes to Voltage Channel ADCs Section38Changes to Figure 49.69Changes to Reference Circuits Section43Change to Figure 8773Change to Figure 8773Change to Figure 10183Changes to Figure 10284Changes to Figure 10284Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 115 and Figure 116.93Changes to Figure 117 and Figure 118.94Changes to Figure 117 and Figure 118.94Changes to Figure 119.95Changes to Table 61.122Updated Outline Dimensions123Added Figure 145.124                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |       |

| Changes to Figure 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |       |

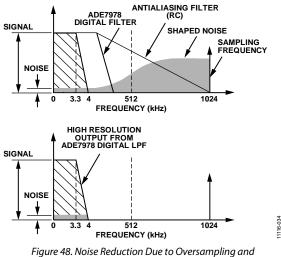

| Changes to Oversampling Section35Changes to Figure 45.36Changes to Current Waveform Gain Registers Section37Changes to Voltage Channel ADCs Section38Changes to Figure 49.69Changes to Reference Circuits Section43Change to Figure 8773Change to DC-to-DC Converter Section81Changes to Figure 10183Changes to Figure 10284Changes to Figure 10284Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 115 and Figure 116.93Changes to Figure 117 and Figure 118.94Changes to Figure 119.95Changes to Table 61.122Updated Outline Dimensions123Added Figure 145.124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                        |       |

| Changes to Figure 45.36Changes to Current Waveform Gain Registers Section37Changes to Voltage Channel ADCs Section38Changes to Figure 49.69Changes to Reference Circuits Section43Change to Figure 8773Change to DC-to-DC Converter Section81Changes to Figure 10183Changes to Figure 10284Changes to Figure 10284Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 105.87Changes to Figure 115 and Figure 116.93Changes to Figure 117 and Figure 118.94Changes to Figure 119.95Changes to Table 61.122Updated Outline Dimensions.123Added Figure 145.124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |       |

| Changes to Current Waveform Gain Registers Section37Changes to Voltage Channel ADCs Section38Changes to Figure 4969Changes to Reference Circuits Section43Change to Figure 8773Change to DC-to-DC Converter Section81Changes to Figure 10183Changes to Figure 10284Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 10587Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Table 61122Updated Outline Dimensions123Added Figure 145124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |       |

| Changes to Voltage Channel ADCs Section38Changes to Figure 4969Changes to Reference Circuits Section43Change to Figure 8773Change to DC-to-DC Converter Section81Changes to Figure 10183Changes to Figure 10284Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 10587Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Table 61122Updated Outline Dimensions123Added Figure 145124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |       |

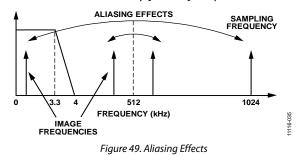

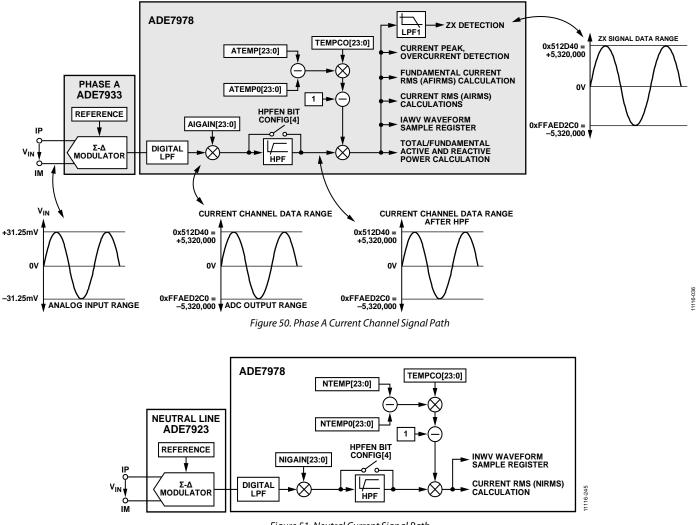

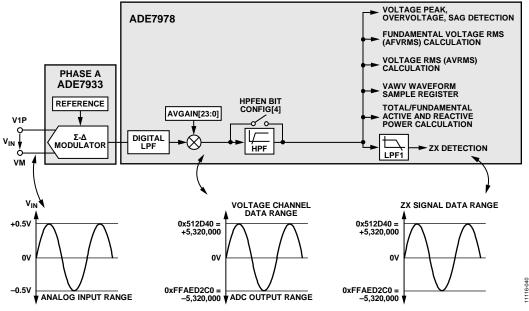

| Changes to Figure 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |       |

| Change to Figure 8773Change to DC-to-DC Converter Section81Changes to Figure 10183Changes to Figure 10284Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 105.87Changes to Figure 115 and Figure 116.93Changes to Figure 117 and Figure 118.94Changes to Figure 119.95Changes to Table 61.122Updated Outline Dimensions123Added Figure 145.124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |       |

| Change to Figure 8773Change to DC-to-DC Converter Section81Changes to Figure 10183Changes to Figure 10284Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 105.87Changes to Figure 115 and Figure 116.93Changes to Figure 117 and Figure 118.94Changes to Figure 119.95Changes to Table 61.122Updated Outline Dimensions123Added Figure 145.124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Changes to Reference Circuits Section                    | 43    |

| Changes to Figure 10183Changes to Figure 10284Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 10587Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Table 61122Updated Outline Dimensions123Added Figure 145124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |       |

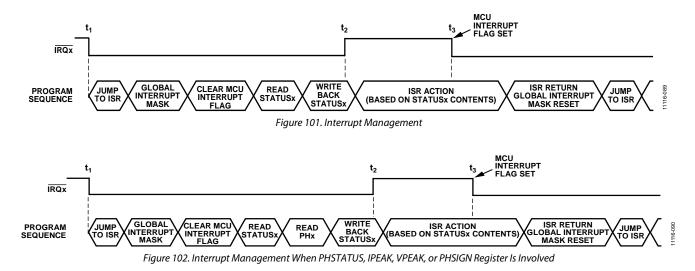

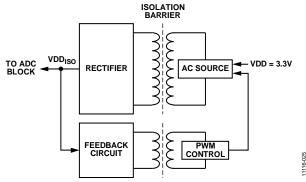

| Changes to Figure 10284Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 10587Changes to Figure 10592Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Table 61122Updated Outline Dimensions123Added Figure 145124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Change to DC-to-DC Converter Section                     | 81    |

| Changes to Applications Information Section, Figure 103,Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters SectionRoled Difference Between the ADE7923 and theADE7933/ADE7932 SectionRole Changes to Figure 105.Changes to Figure 105.Changes to Figure 115 and Figure 116.93Changes to Figure 117 and Figure 118.94Changes to Figure 119.95Changes to Table 61.122Updated Outline Dimensions.123Added Figure 145.124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Changes to Figure 101                                    | 83    |

| Figure 104, and ADE7978, ADE7933/ADE7932 and ADE7923 inPolyphase Energy Meters Section86Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 105.87Changes to Layout Guidelines Section92Changes to Figure 115 and Figure 116.93Changes to Figure 117 and Figure 118.94Changes to Figure 119.95Changes to Table 61.122Updated Outline Dimensions.123Added Figure 145.124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |       |

| Polyphase Energy Meters Section86Added Difference Between the ADE7923 and the86ADE7933/ADE7932 Section86Changes to Figure 10587Changes to Layout Guidelines Section92Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Table 61122Updated Outline Dimensions123Added Figure 145124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Changes to Applications Information Section, Figure 103, |       |

| Added Difference Between the ADE7923 and theADE7933/ADE7932 Section86Changes to Figure 10587Changes to Layout Guidelines Section92Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Table 61122Updated Outline Dimensions123Added Figure 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 104, and ADE7978, ADE7933/ADE7932 and ADE79       | 23 in |

| ADE7933/ADE7932 Section86Changes to Figure 10587Changes to Layout Guidelines Section92Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Table 61122Updated Outline Dimensions123Added Figure 145124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Polyphase Energy Meters Section                          | 86    |

| Changes to Figure 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Added Difference Between the ADE7923 and the             |       |

| Changes to Layout Guidelines Section92Changes to Figure 115 and Figure 11693Changes to Figure 117 and Figure 11894Changes to Figure 11995Changes to Table 61122Updated Outline Dimensions123Added Figure 145124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ADE7933/ADE7932 Section                                  | 86    |

| Changes to Figure 115 and Figure 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Changes to Figure 105                                    | 87    |

| Changes to Figure 117 and Figure 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Changes to Layout Guidelines Section                     | 92    |

| Changes to Figure 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Changes to Figure 115 and Figure 116                     |       |

| Changes to Table 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Changes to Figure 117 and Figure 118                     | 94    |

| Changes to Table 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |       |

| Updated Outline Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |       |

| Added Figure 145 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |       |

| 8 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Changes to Ordering Guide                                |       |

11/2013—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

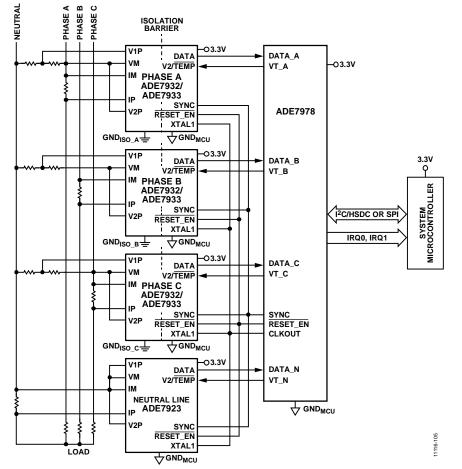

The ADE7978, the ADE7933/ADE7932, and ADE7923 form a chipset dedicated to measuring 3-phase electrical energy using shunts as current sensors.

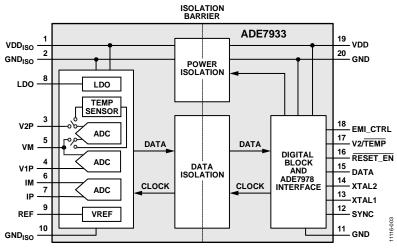

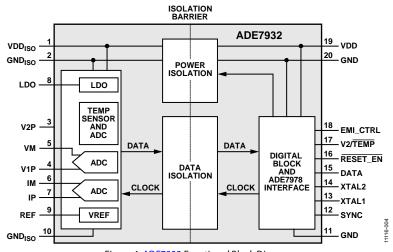

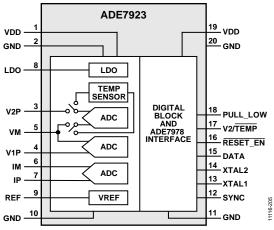

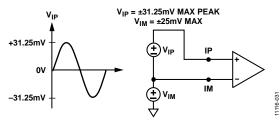

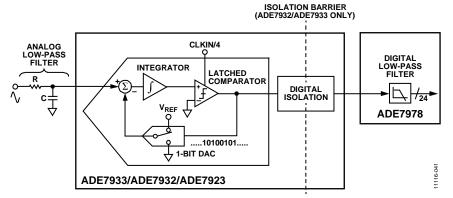

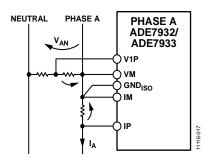

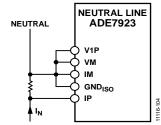

The ADE7933/ADE7932 are isolated, 3-channel sigma-delta analog-to-digital converters ( $\Sigma$ - $\Delta$  ADCs) for polyphase energy metering applications that use shunt current sensors. The ADE7923 is a nonisolated, 3-channel  $\Sigma$ - $\Delta$  ADC for the neutral line that uses a shunt current sensor. The ADE7932 features two ADCs, and the ADE7933 and ADE7923 feature three ADCs.

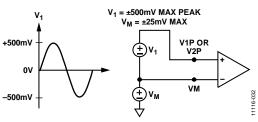

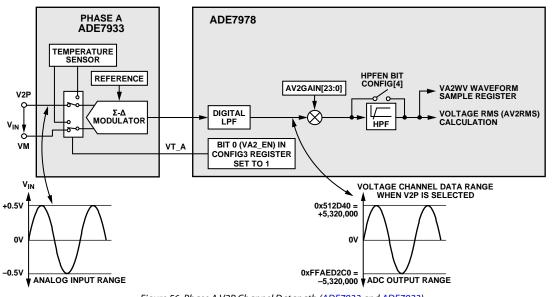

One channel is dedicated to measuring the voltage across the shunt when a shunt is used for current sensing. This channel provides a signal-to-noise ratio (SNR) of 67 dB over a 3.3 kHz signal bandwidth. Up to two additional channels are dedicated to measuring voltages, which are usually sensed using resistor dividers.

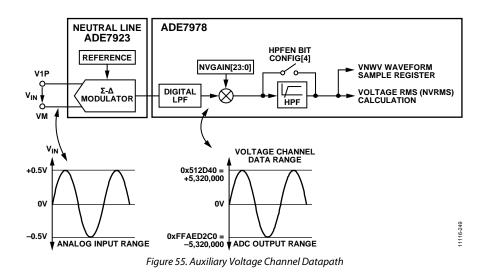

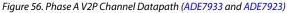

The unused voltage channels on the neutral ADE7923 can be used for auxiliary voltage measurements. These channels provide an SNR of 75 dB over a 3.3 kHz signal bandwidth. One voltage channel can be used to measure the temperature of the die via an internal sensor.

The ADE7933 and ADE7923 include three channels: one current channel and two voltage channels. The ADE7932 includes one current channel and one voltage channel, but is otherwise identical to the ADE7933.

The ADE7933/ADE7932 include *iso*Power\*, an integrated, isolated dc-to-dc converter. Based on the Analog Devices, Inc., *i*Coupler\* technology, the dc-to-dc converter provides the regulated power required by the first stage of the ADCs at a 3.3 V input supply. The ADE7933/ADE7932 eliminate the need for an external dc-to-dc isolation block. The *i*Coupler chip scale transformer technology is used to isolate the logic signals between the first and second stages of the ADC. The result is a small form factor, total isolation solution. The ADE7923 is the nonisolated version of the ADE7933 that can be used for neutral current measurement when isolation from the neutral line is not required.

The ADE7933/ADE7932 and ADE7923 contain a digital interface that is specially designed to interface with the ADE7978. Using this interface, the ADE7978 accesses the ADC outputs and configuration settings of the ADE7933/ADE7932 and ADE7923.

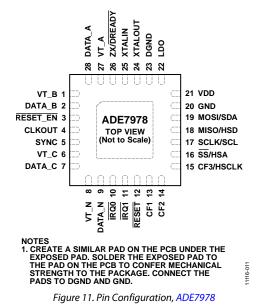

The ADE7933/ADE7932 are available in a 20-lead, Pb-free, widebody SOIC package with increased creepage. The ADE7923 is available in a similar 20-lead, Pb-free, wide-body SOIC package without the increased creepage.

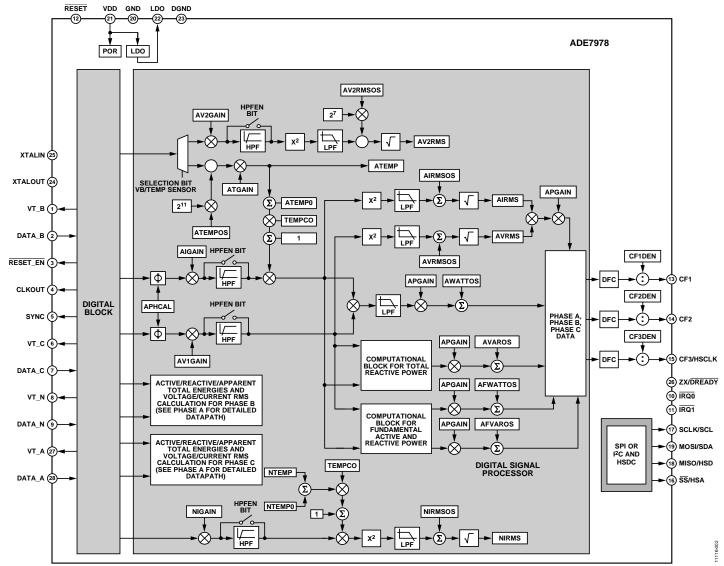

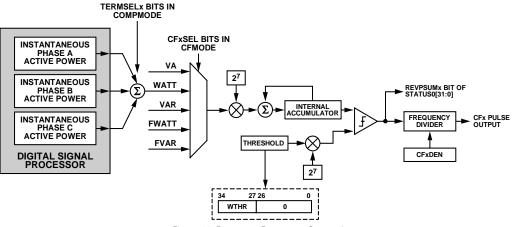

The ADE7978 is a high accuracy, 3-phase electrical energy measurement IC with serial interfaces and three flexible pulse outputs. The ADE7978 can interface with up to four ADE7933/ ADE7932 and ADE7923 devices. The ADE7978 incorporates all the signal processing required to perform total (fundamental and harmonic) active, reactive, and apparent energy measurement and rms calculations, as well as fundamental-only active and reactive energy measurement and rms calculations. A fixed function digital signal processor (DSP) executes this signal processing.

The ADE7978 measures the active, reactive, and apparent energy in various 3-phase configurations, such as wye or delta services, with both three and four wires. The ADE7978 provides system calibration features for each phase, gain calibration, and optional offset correction. Phase compensation is also available, but it is not necessary because the currents are sensed using shunts. The CF1, CF2, and CF3 logic outputs provide a wide selection of power information: total active, reactive, and apparent powers; the sum of the current rms values; and fundamental active and reactive powers.