# 26.5 GHz, Integer N/Fractional-N, PLL Synthesizer

Data Sheet ADF41513

#### **FEATURES**

1 GHz to 26.5 GHz bandwidth Ultralow noise PLL

Integer N = -235 dBc/Hz, fractional-N = -231 dBc/Hz High maximum PFD frequency

Integer N = 250 MHz, fractional-N = 125 MHz 25-bit fixed/49-bit variable fractional modulus mode

23-bit fixed/49-bit variable fractional modulus mo Single-ended reference input

3.3 V power supply, 3.3 V charge pump

Integrated 1.8 V logic capability Phase resync

Programmable charge pump currents: 16× range

Digital lock detect

3-wire serial interface with register readback option Hardware and software power-down mode Operating range from -40°C to +105°C

#### **APPLICATIONS**

Test equipment and instrumentation

Wireless infrastructure

Microwave point to point and multipoint radios

Very small aperture terminal (VSAT) radios

Aerospace and defense

#### **GENERAL DESCRIPTION**

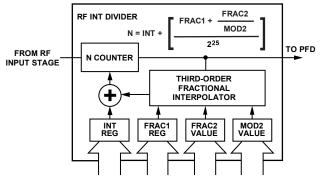

The ADF41513 is an ultralow noise frequency synthesizer that can be used to implement local oscillators (LOs) as high as 26.5 GHz in the upconversion and downconversion sections of wireless receivers and transmitters.

The ADF41513 is designed on a high performance silicon geranium (SiGe), bipolar complementary metal-oxide semiconductor (BiCMOS) process, achieving a normalized phase noise floor of -235 dBc/Hz. The phase frequency detector (PFD) operates up to 250 MHz (integer N mode)/ 125 MHz (fractional-N mode) for improved phase noise and spur performance. The variable modulus,  $\Sigma\text{-}\Delta$  modulator allows extremely fine resolution when using a 49-bit divide value. The ADF41513 can be used as an integer N phase-locked loop (PLL), or it can be used as a fractional-N PLL with either a fixed modulus for subhertz frequency resolution or variable modulus for subhertz exact frequency resolution.

A complete PLL is implemented when the synthesizer is used with an external loop filter and voltage controlled oscillator (VCO). The 26.5 GHz bandwidth eliminates the need for a frequency doubler or divider stage, simplifying system architecture and reducing cost. The ADF41513 is packaged in a compact, 24-lead, 4 mm × 4 mm LFCSP.

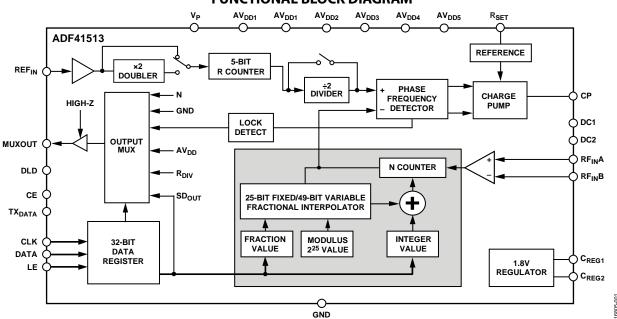

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **TABLE OF CONTENTS**

| Features                                   | 1  |

|--------------------------------------------|----|

| Applications                               | 1  |

| General Description                        | 1  |

| Functional Block Diagram                   | 1  |

| Revision History                           | 2  |

| Specifications                             | 3  |

| Timing Characteristics                     | 5  |

| Absolute Maximum Ratings                   | 6  |

| Thermal Resistance                         | 6  |

| ESD Caution                                | 6  |

| Pin Configuration and Function Description | 7  |

| Typical Performance Characteristics        | 9  |

| Theory of Operation                        | 11 |

| Reference Input                            | 11 |

| RF Input Stage                             | 11 |

| N Divider and R Counter                    | 11 |

| R Counter                                  | 12 |

| PFD and Charge Pump                        | 12 |

| MUXOUT                                     | 12 |

| Lock Detector                              | 12 |

| Readback                                   | 13 |

| Input Shift Registers                      | 13 |

| Program Modes                              | 13 |

|                                            |    |

| Register Maps                              | 14 |

| Register MapsRegister 0 (R0) Map           |    |

|   | Register 2 (R2) Map                                          | 18 |

|---|--------------------------------------------------------------|----|

|   | Register 3 (R3) Map                                          | 18 |

|   | Register 4 (R4) Map                                          | 19 |

|   | Register 5 (R5) Map                                          | 19 |

|   | Register 6 (R6) Map                                          | 21 |

|   | Register 7 (R7) Map                                          | 23 |

|   | Register 8 (R8) Map                                          | 24 |

|   | Register 9 (R9) Map                                          | 24 |

|   | Register 10 (R10) Map                                        | 25 |

|   | Register 11 (R11) Map                                        | 25 |

|   | Register 12 (R12) Map                                        | 26 |

|   | Register 13 (R13) Map                                        | 27 |

| A | pplications information                                      | 28 |

|   | Initialization Sequence                                      | 28 |

|   | RF Synthesizer: A Worked Example of 25-Bit Fixed Modult Mode |    |

|   | RF Synthesizer: A Worked Example of Variable Modulus         |    |

|   | Mode                                                         | 28 |

|   | Modulus                                                      | 28 |

|   | Reference Doubler and Reference Divider                      | 28 |

|   | Spur Mechanisms                                              | 29 |

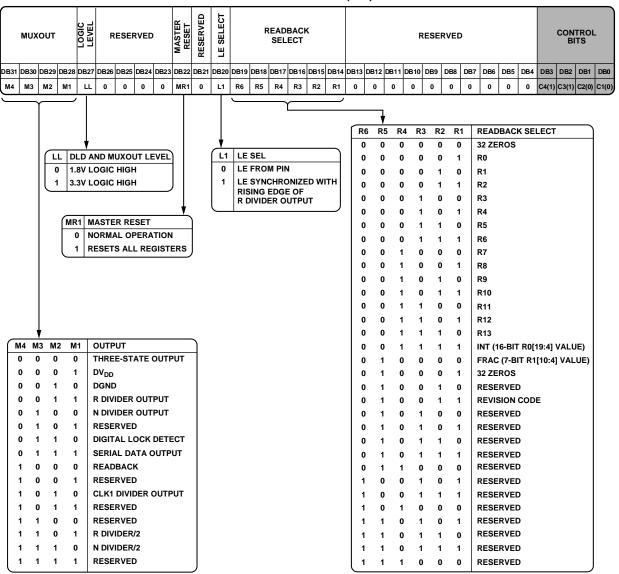

|   | Phase Resync                                                 | 29 |

| О | outline Dimensions                                           | 30 |

|   | Ordering Guide                                               | 30 |

# **REVISION HISTORY**

1/2019—Revision 0: Initial Version

# **SPECIFICATIONS**

$AV_{DDx} = AV_{DD1} = AV_{DD2} = AV_{DD3} = AV_{DD4} = AV_{DD5} = V_P = 3.3 \ V \pm 5\%, GND = 0 \ V, R_{SET} = 1.8 \ k\Omega, dBm \ referred \ to \ 50 \ \Omega, T_A = T_{MIN} \ (-40^{\circ}C)$  to  $T_{MAX} \ (+105^{\circ}C)$ , unless otherwise noted.

Table 1.

| Parameter                                     | Min | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                                                                                            |

|-----------------------------------------------|-----|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RADIO FREQUENCY (RF) CHARACTERISTICS          |     |      |      |      |                                                                                                                                                                                                     |

| 8/9 Prescaler                                 |     |      |      |      |                                                                                                                                                                                                     |

| RF Input Frequency (f <sub>RFIN</sub> ) Range | 1   |      | 26.5 | GHz  | Recommended input power of –5 dBm to<br>+5 dBm, operation at this frequency range is<br>limited to 70°C to T <sub>MIN</sub>                                                                         |

|                                               | 1   |      | 24   | GHz  | Operation at this frequency range is $T_{MAX}$ to $T_{MIN}$                                                                                                                                         |

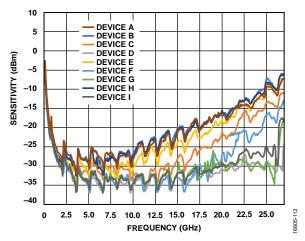

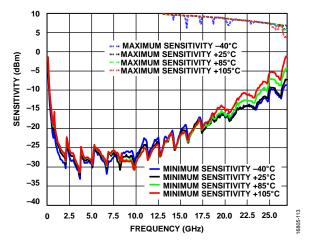

| RF Input Sensitivity                          |     | -11  |      | dBm  | Refer to Figure 10 and Figure 11 for more information                                                                                                                                               |

| 4/5 Prescaler                                 |     |      |      |      |                                                                                                                                                                                                     |

| f <sub>rfin</sub> Range                       | 1   |      | 16   | GHz  | For lower frequencies, ensure slew rate > 320 V/µs                                                                                                                                                  |

| RF Input Sensitivity Range                    | -7  |      | +5   | dBm  | Measured single-ended to RF <sub>IN</sub> A via a 1 pF series capacitor, 1 pF capacitor to GND on RF <sub>IN</sub> B                                                                                |

| INPUT REFERENCE FREQUENCY                     |     |      |      |      |                                                                                                                                                                                                     |

| (REF <sub>IN</sub> ) CHARACTERISTICS          |     |      |      |      |                                                                                                                                                                                                     |

| REF <sub>IN</sub> Input                       | 4.0 |      | 000  |      |                                                                                                                                                                                                     |

| Frequency                                     | 10  |      | 800  | MHz  |                                                                                                                                                                                                     |

| Voltage Range                                 | 0   |      | 1.8  | V    | Di 1 (4)(/ )                                                                                                                                                                                        |

| Sensitivity Range                             | -10 |      | 8    | dBm  | Biased at 1 V (ac coupling ensures 1 V bias), use square wave at low power and/or frequency to ensure slew rate is > 320 V/μs; for best inband phase noise performance, ensure slew rate > 500 V/μs |

| Capacitance                                   |     |      | 10   | рF   |                                                                                                                                                                                                     |

| Current                                       |     |      | ±150 | μΑ   |                                                                                                                                                                                                     |

| Doubler Input Frequency                       |     |      | 225  | MHz  | Maximum reference frequency when the doubler is enabled                                                                                                                                             |

| MAXIMUM PFD FREQUENCY                         |     |      |      |      |                                                                                                                                                                                                     |

| Integer N Mode                                |     |      | 250  | MHz  |                                                                                                                                                                                                     |

| Fractional-N Mode                             |     |      | 125  | MHz  |                                                                                                                                                                                                     |

| N DIVIDER RANGE                               |     |      |      |      |                                                                                                                                                                                                     |

| 16-Bit N Divider Range                        |     |      |      |      |                                                                                                                                                                                                     |

| Integer N Mode                                | 20  |      | 511  |      | 4/5 prescaler                                                                                                                                                                                       |

|                                               | 64  |      | 1023 |      | 8/9 prescaler                                                                                                                                                                                       |

| Fractional-N Mode                             | 23  |      | 511  |      | 4/5 prescaler                                                                                                                                                                                       |

|                                               | 75  |      | 1023 |      | 8/9 prescaler                                                                                                                                                                                       |

| CHARGE PUMP (CP)                              |     |      |      |      |                                                                                                                                                                                                     |

| CP Current (I <sub>CP</sub> ) Sink and Source |     |      |      |      | Programmable                                                                                                                                                                                        |

| High Value                                    |     | 7.2  |      | mA   | With $R_{SET} = 1.8 \text{ k}\Omega$                                                                                                                                                                |

| Low Value                                     |     | 0.45 |      | mA   |                                                                                                                                                                                                     |

| Absolute Accuracy                             |     | 5    |      | %    | With $R_{SET} = 1.8 \text{ k}\Omega$                                                                                                                                                                |

| R <sub>SET</sub> Range                        | 1.8 | 2.7  | 10   | kΩ   | 5% accuracy                                                                                                                                                                                         |

| I <sub>CP</sub> Three-State Leakage           |     | 2    |      | nA   | $V_{CP} = 0.9  V, T_A = 25^{\circ} C$                                                                                                                                                               |

| Sink and Source Current Matching              |     | 5    |      | %    | $0.7 \text{ V} \leq \text{CP voltage } (V_{CP}) \leq V_P - 0.7 \text{ V}$                                                                                                                           |

| $I_{CP}$ vs. $V_{CP}$                         |     | 5    |      | %    | $0.7  \text{V} \le \text{V}_{\text{CP}} \le \text{V}_{\text{P}} - 0.7  \text{V}$                                                                                                                    |

| I <sub>CP</sub> vs. Temperature               |     | 5    |      | %    | $V_{CP} = V_P/2$                                                                                                                                                                                    |

| Parameter                                                                       | Min   | Тур  | Max   | Unit   | Test Conditions/Comments                                                          |

|---------------------------------------------------------------------------------|-------|------|-------|--------|-----------------------------------------------------------------------------------|

| LOGIC INPUTS                                                                    |       |      |       |        |                                                                                   |

| Input Voltage                                                                   |       |      |       |        |                                                                                   |

| High (V <sub>IH</sub> )                                                         | 1.4   |      |       | V      | The serial port interface (SPI) block can accept both 1.8 V or 3.3 V logic inputs |

| Low (V <sub>IL</sub> )                                                          |       |      | 0.6   | V      |                                                                                   |

| Input Current (I <sub>INH</sub> , I <sub>INL</sub> )                            |       |      | ±1    | μΑ     |                                                                                   |

| Input Capacitance (C <sub>IN</sub> )                                            |       |      | 10    | pF     |                                                                                   |

| LOGIC OUTPUTS                                                                   |       |      |       |        |                                                                                   |

| Output Voltage                                                                  |       |      |       |        |                                                                                   |

| High (V <sub>OH</sub> )                                                         | 1.4   |      |       | V      | MUXOUT voltage = 1.8 V, DLD voltage = 1.8 V                                       |

| -                                                                               | 2.6   |      |       | V      | MUXOUT voltage = 3.3 V, DLD voltage = 3.3 V                                       |

| Low (V <sub>OL</sub> )                                                          |       |      | 0.4   | V      |                                                                                   |

| Output High Current, Output Low<br>Current (I <sub>OH</sub> , I <sub>OL</sub> ) |       |      | 500   | μΑ     |                                                                                   |

| POWER SUPPLIES                                                                  |       |      |       |        |                                                                                   |

| $AV_{DD1}$ , $AV_{DD2}$ , $AV_{DD3}$ , $AV_{DD4}$ , $AV_{DD5}$ , $V_P$          | 3.135 | 3.3  | 3.465 | V      |                                                                                   |

| $I_{DD1}^{1}$                                                                   |       | 2    | 3.2   | mA     | Current drawn by AV <sub>DD1</sub>                                                |

| $I_{DD2}^{1}$                                                                   |       | 63.5 | 88    | mA     | Current drawn by AV <sub>DD2</sub>                                                |

| $I_{DD3}^{1}$                                                                   |       | 2.1  | 3.6   | mA     | Current drawn by AV <sub>DD3</sub>                                                |

| I <sub>DD4</sub> <sup>1</sup>                                                   |       | 1.45 | 2     | mA     | Current drawn by AV <sub>DD4</sub>                                                |

| I <sub>DD5</sub> <sup>1</sup>                                                   |       | 20   | 25    | mA     | Current drawn by AV <sub>DD5</sub>                                                |

| I <sub>P</sub>                                                                  |       | 6    | 7     | mA     | Current drawn by V <sub>P</sub>                                                   |

| I <sub>TOTAL</sub>                                                              |       | 95.1 | 128.8 | mA     | Total current drawn by AV <sub>DDx</sub> and V <sub>P</sub>                       |

| Power-Down Mode                                                                 |       |      | 100   | μΑ     | $T_A = 25$ °C, CE is low, total of all rails                                      |

| NOISE CHARACTERISTICS                                                           |       |      |       |        |                                                                                   |

| Normalized Phase Noise Floor<br>(PN <sub>SYNTH</sub> )                          |       |      |       |        |                                                                                   |

| In Integer N Mode <sup>2</sup>                                                  |       | -235 |       | dBc/Hz | PLL loop bandwidth (BW) = 1 MHz (Integer N mode)                                  |

| In Fractional-N Mode <sup>3</sup>                                               |       | -231 |       | dBc/Hz | PLL loop BW = 1 MHz (fractional-N mode)                                           |

| Normalized 1/f Noise (PN <sub>1_f</sub> ) <sup>3</sup>                          |       | -128 |       | dBc/Hz | 10 kHz offset, normalized to 1 GHz                                                |

| SPURIOUS SIGNALS                                                                |       |      |       |        |                                                                                   |

| Reference Spurious                                                              |       | -90  |       | dBc    | At reference = 100 MHz, PLL loop BW = 40 kHz                                      |

| PFD Spurious                                                                    |       | -87  |       | dBc    | At PFD = 50 MHz, PLL loop BW = 40 kHz                                             |

| In-Band Integer Boundary<br>Spurious                                            |       | -45  |       | dBc    | 10 kHz offset, PLL loop BW = 250 kHz                                              |

$<sup>^{1}</sup>$  T<sub>A</sub> = 25°C, AV<sub>DDx</sub> = 3.3 V (where x = 1, 2, 3, or 4), prescaler (P) = 8/9, f<sub>RFIN</sub> = 26.5 GHz, REF<sub>IN</sub> = 124 MHz, PFD frequency input (f<sub>PFD</sub>) = 124 MHz.

<sup>&</sup>lt;sup>1</sup> The synthesizer phase noise floor is estimated by measuring the inband phase noise at the output of the VCO and subtracting 20 log N (where N is the N divider value) and 10 log f<sub>FFD</sub>. PN<sub>SyNTH</sub> is the total phase noise measured at the VCO output (PN<sub>TOT</sub>) – 10 log f<sub>FFD</sub> – 20 log N.

<sup>3</sup> The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency, f<sub>RF</sub>, and at a frequency offset, f, is given by phase noise (PN) = P<sub>1\_f</sub> + 10 log(10 kHz/f) + 20 log(f<sub>RF</sub>/1 GHz). Both the normalized phase noise floor and flicker noise are modeled in the ADIsimPLL.

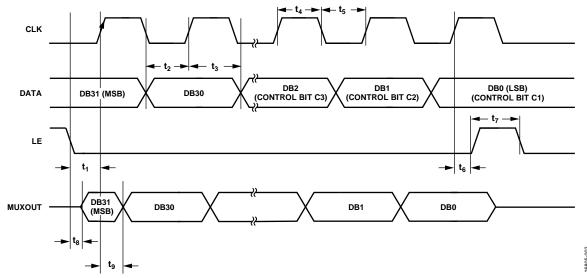

# **TIMING CHARACTERISTICS**

$AV_{\mathrm{DDx}} = AV_{\mathrm{DD1}} = AV_{\mathrm{DD2}} = AV_{\mathrm{DD3}} = AV_{\mathrm{DD4}} = AV_{\mathrm{DD5}} = V_{\mathrm{P}} = 3.3 \ \mathrm{V} \pm 5\%, \ GND = 0 \ \mathrm{V}, \ R_{\mathrm{SET}} = 1.8 \ \mathrm{k}\Omega, \ dBm \ referred \ to \ 50 \ \Omega, \ T_{\mathrm{A}} = T_{\mathrm{MIN}} \ (-40^{\circ}\mathrm{C})$  to  $T_{\mathrm{MAX}} \ (+105^{\circ}\mathrm{C})$ , unless otherwise noted.

Table 2. Read and Write Timing

| Parameter             | Limit at T <sub>MIN</sub> to T <sub>MAX</sub> | Unit   | Test Conditions/Comments                                         |

|-----------------------|-----------------------------------------------|--------|------------------------------------------------------------------|

| t <sub>1</sub>        | 10                                            | ns min | LE setup time                                                    |

| $t_2$                 | 5                                             | ns min | DATA to CLK setup time                                           |

| $t_3$                 | 5                                             | ns min | DATA to CLK hold time                                            |

| t <sub>4</sub>        | 12.5                                          | ns min | CLK high duration                                                |

| <b>t</b> <sub>5</sub> | 12.5                                          | ns min | CLK low duration                                                 |

| t <sub>6</sub>        | 5                                             | ns min | CLK to LE setup time                                             |

| t <sub>7</sub>        | 10                                            | ns min | LE pulse width                                                   |

| t <sub>8</sub>        | 20                                            | ns max | LE setup time to MUXOUT when MUXOUT is configured as SPI output  |

| t <sub>9</sub>        | 20                                            | ns max | CLK setup time to MUXOUT when MUXOUT is configured as SPI output |

# **Timing Diagram**

Figure 2. Read and Write Timing

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| 14016 51                                              |                                              |

|-------------------------------------------------------|----------------------------------------------|

| Parameter                                             | Rating                                       |

| $AV_{DDx}$ to $GND^1$                                 | -0.3 V to +3.6 V                             |

| $V_P$ to GND                                          | −0.3 V to +3.6 V                             |

| $V_P$ to $AV_{DDx}$                                   | −0.3 V to +0.3 V                             |

| Digital Input/Output Voltage to GND                   | $-0.3 \text{ V to AV}_{DDx} + 0.3 \text{ V}$ |

| Analog Input/Output Voltage to GND                    | $-0.3 \text{ V to V}_P + 0.3 \text{ V}$      |

| RF <sub>IN</sub> A, RF <sub>IN</sub> B to GND         | −0.3 V to +3.6 V                             |

| RF <sub>IN</sub> A to RF <sub>IN</sub> B <sup>1</sup> | ±1.4 V                                       |

| REF <sub>IN</sub> to GND                              | -0.3 V to +2.1 V                             |

| Operating Temperature Range                           |                                              |

| Industrial                                            | -40°C to +105°C                              |

| Storage Temperature Range                             | −65°C to +125°C                              |

| Maximum Junction Temperature                          |                                              |

| Operational                                           | 125°C                                        |

| Reflow Soldering                                      |                                              |

| Peak Temperature                                      | 260°C                                        |

| Time at Peak Temperature                              | 40 sec                                       |

| Electrostatic Discharge (ESD)                         |                                              |

| Charged Device Model                                  | 1250 V                                       |

| Human Body Model                                      | 1500 V                                       |

| Transistor Count                                      |                                              |

| CMOS                                                  | 215,726                                      |

| Bipolar                                               | 1625                                         |

$<sup>^{\</sup>text{1}}$  Approximately 13 dBm into a 50  $\Omega$  input.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

This device is a high performance RF IC with an electrostatic discharge (ESD) rating of <2 kV, and the device is ESD sensitive. Take proper precautions for handling and assembly.

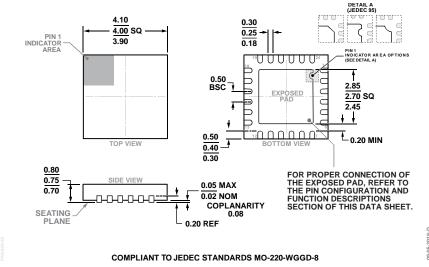

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

**Table 4. Thermal Resistance**

| Package Type         | θ <sub>JA</sub> | θις | Unit |

|----------------------|-----------------|-----|------|

| CP-24-8 <sup>1</sup> | 48              | 38  | °C/W |

<sup>&</sup>lt;sup>1</sup> The thermal resistance values are defined per the JESD51 standard.

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

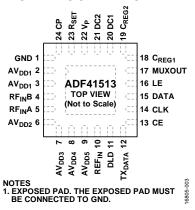

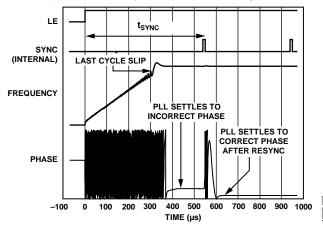

# PIN CONFIGURATION AND FUNCTION DESCRIPTION

Figure 3. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND                | Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2, 3    | AV <sub>DD1</sub>  | PFD and Up and Down Digital Driver Power Supply. Pin 2 and Pin 3 can be tied together. With Pin 2 and Pin 3 tied together, place three parallel capacitors as close as possible to the AV <sub>DD1</sub> pins: 10 μF, 100 nF, and 100 pF.                                                                                                                                                                                                                                                                                                                                                   |

| 4       | RF <sub>IN</sub> B | Complementary Input to the RF Prescaler. In single-ended mode, decouple this pin to the ground plane with a small bypass capacitor, typically 100 pF.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5       | RF <sub>IN</sub> A | Input to the RF Prescaler. AC-couple this signal to the external VCO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6       | AV <sub>DD2</sub>  | RF Buffer and Prescaler Power Supply. Place three parallel capacitors as close as possible to the AV <sub>DD2</sub> pin: 10 $\mu$ F, 100 nF, and 100 pF.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7       | AV <sub>DD3</sub>  | N Divider Power Supply. Place three parallel capacitors as close as possible to the $AV_{DD3}$ pin: 10 $\mu$ F, 100 nF, and 100 pF.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8       | AV <sub>DD4</sub>  | R Divider and Lock Detector Power Supply. Place three parallel capacitors as close as possible to the AV <sub>DD4</sub> pin: 10 µF, 1 µF, and 100 nF. Pin 8 powers the internal low dropout (LDO) regulator for the reference divider.                                                                                                                                                                                                                                                                                                                                                      |

| 9       | AV <sub>DD5</sub>  | $\Sigma$ - $\Delta$ Modulator and SPI Power Supply. Place three parallel capacitors as close as possible to the AV <sub>DDS</sub> pin: 10 μF, 1 μF, and 100 nF. This pin powers the internal LDO regulator for the $\Sigma$ - $\Delta$ modulator.                                                                                                                                                                                                                                                                                                                                           |

| 10      | REF <sub>IN</sub>  | Reference Input. The reference can accept either a single-ended CMOS (dc-coupled) or single-ended sine wave (ac-coupled). The single-ended input has a nominal threshold of 1 V and a dc equivalent input resistance of 20 k $\Omega$                                                                                                                                                                                                                                                                                                                                                       |

| 11      | DLD                | Digital Lock Detect Pin. A logic high on this pin indicates PLL lock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12      | TX <sub>DATA</sub> | Transmit Data Pin. Pin 12 is not used. Connect Pin 12 to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13      | CE                 | Chip Enable. A logic low on this pin powers down the device and puts the charge pump output into three-state mode. Registers do not hold their values when CE is low. This pin only supports 3.3 V logic inputs.                                                                                                                                                                                                                                                                                                                                                                            |

| 14      | CLK                | Serial Clock Input. CLK clocks in the serial data to the registers. The data is latched into the 32-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15      | DATA               | Serial Data Input. The serial data is loaded most significant bit (MSB) first with the two least significant bits (LSBs) at the control bits. This input is a high impedance CMOS input.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 16      | LE                 | Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches. Select the latch using the control bits.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17      | MUXOUT             | Multiplexer Output. This multiplexer output allows the lock detect, the scaled RF, the scaled reference frequency, logic high, logic low, or register readback data to be accessed externally.                                                                                                                                                                                                                                                                                                                                                                                              |

| 18      | C <sub>REG1</sub>  | Internal 1.8 V Regulator Output Pin. Place three parallel capacitors as close to the C <sub>REG1</sub> pin as possible: 4.7 µF, 100 nF, and 1 nF.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19      | C <sub>REG2</sub>  | Internal 1.8 V Regulator Output Pin. Place three parallel capacitors as close to the $C_{REG2}$ pin as possible: 4.7 $\mu$ F, 100 nF, and 1 nF.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20      | DC1                | DC Bias Pin 1. Place a 1 µF capacitor in parallel with a 1 nF capacitor to ground, as close as possible to the DC1 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 21      | DC2                | DC Bias Pin 2. Place a 1 µF capacitor in parallel with a 1 nF capacitor to ground, as close as possible to the DC2 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22      | $V_P$              | Charge Pump Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 23      | R <sub>SET</sub>   | Maximum Charge Pump Current Setting Resistor. Connecting a resistor between the $R_{SET}$ pin and GND sets the maximum charge pump output current. The nominal voltage potential at the $R_{SET}$ pin is 0.66 V. The relationship between $I_{CP}$ and $R_{SET}$ is $I_{CP\_MAX} = 12.96/R_{SET}$ . For example, with $R_{SET} = 2.7 \text{ k}\Omega$ , $I_{CP\_MAX} = 4.8 \text{ m}A$ . The relationship between bleed current ( $I_{BLEED\_MIN}$ and $R_{SET}$ is $I_{BLEED\_MIN} = 0.0103/R_{SET}$ . For example, with $R_{SET} = 2.7 \text{ k}\Omega$ , $I_{BLEED\_MIN} = 3.81 \mu A$ . |

| Pin No. | Mnemonic | Description                                                                                                                                   |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 24      | СР       | Charge Pump Output. When enabled, this pin provides $\pm I_{\mathbb{CP}}$ to the external loop filter, which in turn drives the external VCO. |

|         | EPAD     | Exposed Pad. The exposed pad must be connected to GND.                                                                                        |

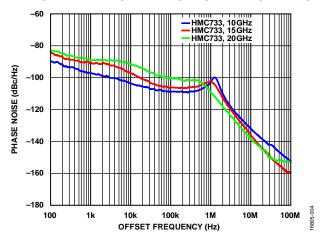

# TYPICAL PERFORMANCE CHARACTERISTICS

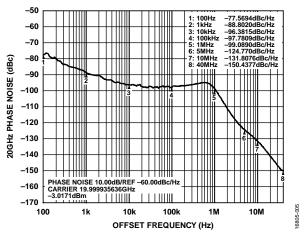

Figure 4. Phase Noise vs. Offset Frequency at 10 GHz, 15 GHz, and 20 GHz with the HMC733,  $I_{CP} = 3.5$  mA, Integer N Mode

Figure 5. 20 GHz Phase Noise vs. Offset Frequency with the HMC733,  $I_{CP} = 3.5$  mA, Fractional-N Mode

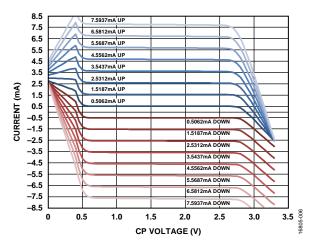

Figure 6. Current vs. CP Voltage, Charge Pump Compliance,  $R_{SET} = 1.8 \text{ k}\Omega$

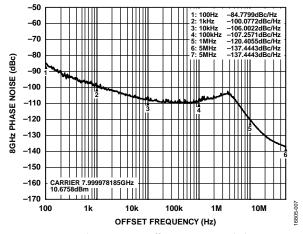

Figure 7. 8 GHz Phase Noise vs. Offset Frequency with the HMC509,  $I_{CP} = 3.5$  mA, Fractional-N Mode

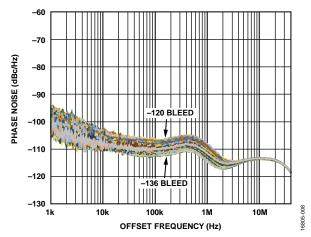

Figure 8. Phase Noise vs. Offset Frequency for Various Bleeds

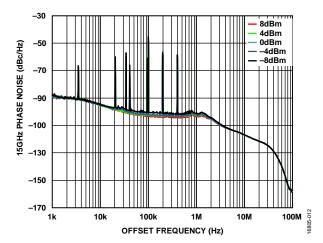

Figure 9. 15 GHz Phase Noise vs. Offset Frequency at Various REF $_{\rm IN}$  Powers, Fractional-N Mode, PFD = 100 MHz

Figure 10. Sensitivity vs. Frequency for Multiple Soldered Devices

Figure 11. Sensitivity vs. Frequency at Various Temperatures for Device A

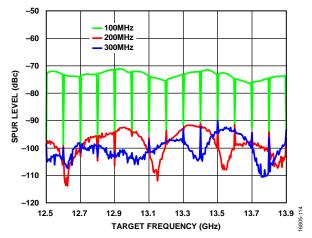

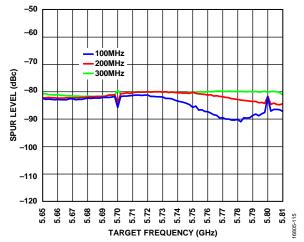

Figure 12. Spur Level vs. Target Frequency with the HMC584 VCO,  $REF_{IN} = 100$  MHz, PFD = 100 MHz, PLL Loop BW = 80 kHz

Figure 13. Spur Level vs. Target Frequency with Z-Communications  $V940ME03\ VCO$ ,  $REF_{IN}=100\ MHz$ ,  $PFD=100\ MHz$ ,  $PLL\ Loop\ BW=80\ kHz$

# THEORY OF OPERATION

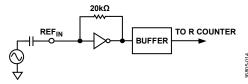

# **REFERENCE INPUT**

The reference input stage is shown in Figure 14. The reference input accepts an ac-coupled, single-ended signal. During power-down, this circuit remains active and draws the same current from  $AV_{\rm DD4}$  as during normal operation. With no reference connected,  $AV_{\rm DD4}$  drops to approximately 600  $\mu A$ .

Figure 14. Reference Input Stage

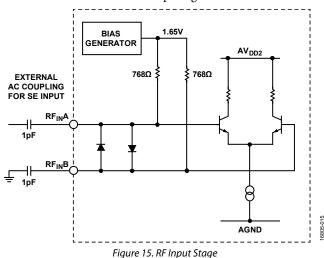

#### **RF INPUT STAGE**

The RF input stage is shown in Figure 15. A two-stage limiting amplifier follows the RF input stage to generate the current mode logic (CML) clock levels needed for the prescaler. The RF $_{\rm IN}$ A and RF $_{\rm IN}$ B inputs require dc blocking capacitors to isolate the 1.65 V bias level from the input signal.

rigare is in mpactor

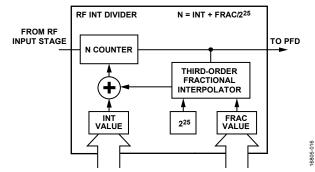

#### N DIVIDER AND R COUNTER

The N divider is used to divide the RF input signal down to the PFD frequency ( $f_{PFD}$ ).

$$f_{PFD} = REF_{IN} \times ((1+D)/(R \times (1+T)))$$

(1)

where:

$REF_{IN}$  is the reference input frequency.

D is the REF<sub>IN</sub> doubler bit value (0 or 1).

*R* is the preset divide ratio of the binary 5-bit programmable reference counter (1 to 32).

T is the REF<sub>IN</sub> divide by 2 bit value (0 or 1).

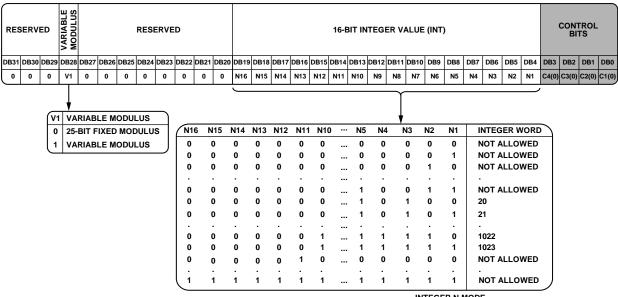

The N divider value is generated by a  $\Sigma$ - $\Delta$  modulator. The ADF41513 contains two selectable  $\Sigma$ - $\Delta$  modulators. One modulator has a 25-bit fixed modulus (see Figure 16) and one has a variable modulus up to 49 bits (see Figure 17). Register 0, Bit 28 selects the modulator.

Figure 16. Fixed Modulus N Divider

Figure 17. Variable Modulus N Divider

# 25-Bit Fixed Modulus (Register 0, Bit 28 = 0)

For the 25-bit fixed modulus, the RF VCO frequency (RF  $_{\mbox{\scriptsize OUT}})$  equation is

$$RF_{OUT} = f_{PFD} \times (INT + (FRAC/2^{25}))$$

(2)

where:

$RF_{OUT}$  is the RF VCO frequency.

INT is a 16-bit value set by Bits[19:4] in Register 0. In Integer N mode, INT is 20 to 511 for a 4/5 prescaler and 64 to 1023 for a 8/9 prescaler, and in fractional-N mode, INT is 23 to 511 for a 4/5 prescaler and 75 to 1023 for a 8/9 prescaler.

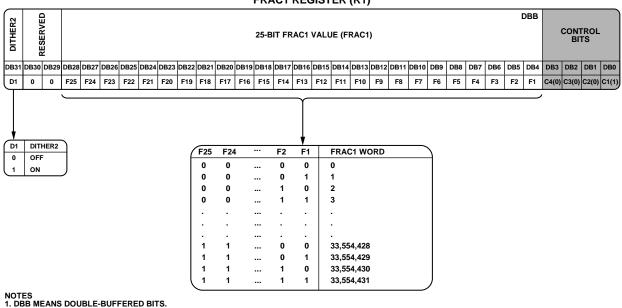

FRAC is a 25-bit value set by Bits[28:4], FRAC1, in Register 1.

The minimum RF output resolution is set by  $f_{PFD}/2^{25}$ . For example, if  $f_{PFD}=100$  MHz, the minimum resolution is 2.98 Hz.

By default, due to the architecture of the  $\Sigma$ - $\Delta$  modulator, there is a fixed ( $f_{PFD}/2^{26}$ ) offset added or subtracted from the programmed output frequency. To remove this offset, set LSB\_PI (Register 5, Bit 24).

#### $Variable\ Modulus\ (R0, DB28 = 1)$

For the variable modulus, the RF VCO frequency (RF $_{\text{OUT}}$ ) equation is

$$RF_{OUT} = f_{PFD} \times (INT + (FRAC1 + (FRAC2/MOD2))/2^{25}) \quad (3)$$

where:

*RF*<sub>OUT</sub> is the output frequency of external VCO.

INT is a 16-bit value set by Bits[19:4] in Register 0. In Integer N mode, INT is 20 to 511 for a 4/5 prescaler and 64 to 1023 for a 8/9 prescaler, and in fractional-N mode, INT is 23 to 511 for a 4/5 prescaler and 75 to 1023 for a 8/9 prescaler.

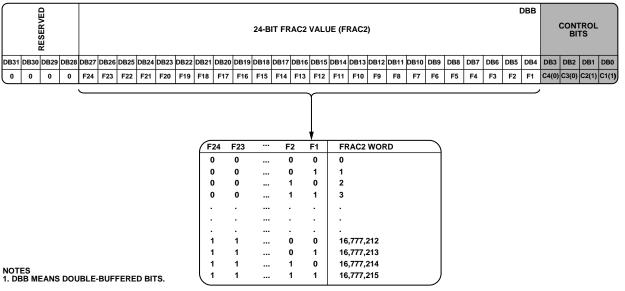

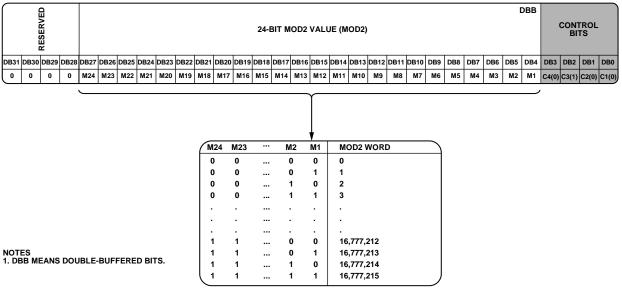

FRAC1 is a 25-bit value set by Bits[28:4] in Register 1. FRAC2 is a 24-bit value set by Bits[27:4] in Register 3. MOD2 is a 24-bit value set by Bits[27:4] in Register 4.

The minimum RF output resolution is set by  $f_{PFD}/2^{49}$ . Therefore, for  $f_{PFD}=100$  MHz, the minimum resolution is 0.1776  $\mu$ Hz. To achieve this resolution, MOD2 must be set to its maximum of  $(2^{24}-1)$ , which is 16,777,215.

# Integer N Mode

When FRAC1 and FRAC2 are both equal to 0, the ADF41513 can operate in purely integer N mode, which improves the phase noise performance of the PLL and sets the frequency resolution to f<sub>PFD</sub>. This feature is not automatic and must be manually set for Integer N channels. Bleed must also be disabled when using the ADF41513 in Integer N operation. See the Register 12 (R12) Map section for more information on programming the ADF41513 for Integer N operation.

#### **R COUNTER**

The 5-bit R counter allows  $REF_{IN}$  to be divided down to produce the reference clock to the PFD. Division ratios from 1 to 32 are allowed.

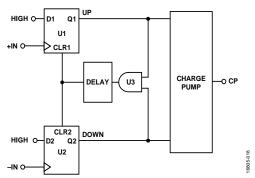

#### PFD AND CHARGE PUMP

The PFD takes inputs from the R counter and N counter and produces an output proportional to the phase and frequency difference between these inputs. Figure 18 shows a PFD simplified schematic. The PFD includes a fixed delay element that sets the width of the antibacklash pulse, which is typically 1 ns. This pulse ensures that there is no dead zone in the PFD transfer function and produces a consistent reference spur level.

Figure 18. PFD Simplified Schematic

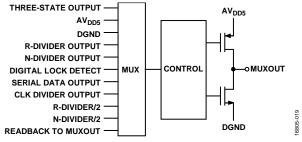

#### **MUXOUT**

The output multiplexer on the ADF41513 allows the user to access various internal nodes on the chip. The M4, M3, M2, and M1 bits in Register 12 (see the Register 12 (R12) Map section) controls the state of MUXOUT. Figure 19 shows the MUXOUT section in block diagram form. Many of these access points are useful for debugging. For example, select the N divider output to check if the N divider is functioning correctly. Most of the access points are self explanatory. Set the  $CLK_1$  divider output signal to access the internal  $CLK_1$  divider signal used for phase resync. During power-down (CE = logic low), MUXOUT is set to GND.

Figure 19. MUXOUT Schematic

#### **LOCK DETECTOR**

The lock detector compares the PFD output pulse width against a lock detector window. Measurements are performed every PFD comparison cycle when LD\_CLK\_SEL = 0 or every 32<sup>nd</sup> cycle when LD\_CLK\_SEL = 1. If the pulse width falls within the lock window, a counter is incremented. If the counter reaches the count set by LD\_COUNT without an up or down pulse width exceeding the lock detect window and without a cycle slip occurring, lock is then declared by the lock detector.

When the lock detector has declared lock, the main mechanism to declare a loss of lock is for a cycle slip to occur. This cycle slip is usually caused by a frequency error at the phase detector input, causing the phase error to grow until the error exceeds 360°. The phase error then wraps around to 0°. This phase wrap around is a cycle slip.

A high level on MUXOUT indicates the PLL is in lock.

The lock detector window size, LD\_COUNT, and LD\_CLK\_SEL all affect the sensitivity of the lock detector. Larger windows, smaller LD\_COUNT values, and LD\_CLK\_SEL = 0 shorten the overall lock detect time and increase sensitivity. Smaller windows, larger LD\_COUNT values, and LD\_CLK\_SEL = 1 increase the overall lock detect time and reduce sensitivity. Excessive lock detector sensitivity can cause multiple transitions between a locked state and out of lock state during frequency changes. Insufficient lock detector sensitivity can cause the detector to indicate an out of lock state when, in fact, the PLL is locked.

The window size can be adjusted between 0.9 ns and 11.5 ns with LDP, Bits [9:8] in Register 6 and LD bias, Bits [31:30] in Register 9. The ideal window size is halfway between the maximum window, set by the phase comparison period,  $t_{PFD}$  (10 ns for 100 MHz reference and R=1), and the minimum is set by

$$(I_{BLEED}/I_{CP}) \times t_{PFD}$$

(4)

LD\_COUNT can range from 2 counts to 8192 counts. The fastest lock indication requires two measurement cycles (20 ns with 100 MHz reference, R = 1, and LD\_CLK\_SEL = 0). In practice, the lock indication takes much longer because of the loop filter on the phase comparator. When LD\_CLK\_SEL = 1, a minimum 64 measurements are required (640 ns).

#### **READBACK**

Register data can be read by setting MUXOUT to serial data output. In this mode, the MUXOUT line concurrently transfers 32 bits of the previous written register value while clocking in 32 bits of write data.

To read back a specific register, chip revision code, or bit pattern, write 1000b to Bits[31:28], Register 12. Bits[19:14] in Register 12 set the data that is output from the MUXOUT pin when in readback mode.

To prevent spurious writes, the DATA pin must be held at logic low while a readback is taking place.

# **INPUT SHIFT REGISTERS**

The ADF41513 contains a programmable digital block. Data is clocked into the 32-bit shift register on each rising edge of CLK. The data is clocked in MSB first. Data is transferred from the shift register to the chosen register on the rising edge of LE. The destination latch is determined by the state of the four control bits (C4, C3, C2, and C1) in the shift register. The following are the four LSBs: DB3, DB2, DB1, and DB0. The truth table for these bits is shown in Table 6. Figure 20 through Figure 22 show a summary of how the registers are programmed.

#### **PROGRAM MODES**

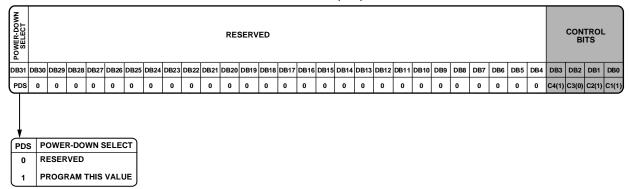

Table 6 and Figure 23 through Figure 36 show how to set up the program modes in the ADF41513.

Several settings in the ADF41513 are double buffered. These settings include MOD2, FRAC1, FRAC2, R counter value, reference doubler, CP current setting, RDIV2, phase word, prescaler, and CLK<sub>1</sub> divider. Two events must occur before the device uses a new value for any of the double buffered settings. First, the new value is latched into the device by writing to the appropriate register. Second, a new write must be performed on Register 0. For example, updating the FRAC1 value requires a write to Register 1 and a write to Register 0. Write to Register 1 first, followed by the write to Register 0. The frequency change begins after the write to Register 1 do not take effect until after the write to Register 0.

Table 6. C4, C3, C2, and C1 Truth Table

|    | Coi | ntrol Bits |            |          |  |

|----|-----|------------|------------|----------|--|

| C4 | C3  | C2         | <b>C</b> 1 | Register |  |

| 0  | 0   | 0          | 0          | R0       |  |

| 0  | 0   | 0          | 1          | R1       |  |

| 0  | 0   | 1          | 0          | R2       |  |

| 0  | 0   | 1          | 1          | R3       |  |

| 0  | 1   | 0          | 0          | R4       |  |

| 0  | 1   | 0          | 1          | R5       |  |

| 0  | 1   | 1          | 0          | R6       |  |

| 0  | 1   | 1          | 1          | R7       |  |

| 1  | 0   | 0          | 0          | R8       |  |

| 1  | 0   | 0          | 1          | R9       |  |

| 1  | 0   | 1          | 0          | R10      |  |

| 1  | 0   | 1          | 1          | R11      |  |

| 1  | 1   | 0          | 0          | R12      |  |

| 1  | 1   | 0          | 1          | R13      |  |

# **REGISTER MAPS**

# INT REGISTER (R0)

|      | RESERVED |      | VARIABLE | RESERVED |      |      |      |      |      |      |      |      |      |      |      |      | 16-E | BIT IN | ITEGI | ER V | ALUE | (INT | )   |     |     |     |     | CONTROL<br>BITS |       |       |       |

|------|----------|------|----------|----------|------|------|------|------|------|------|------|------|------|------|------|------|------|--------|-------|------|------|------|-----|-----|-----|-----|-----|-----------------|-------|-------|-------|

| DB31 | DB30     | DB29 | DB28     | DB27     | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13   | DB12  | DB11 | DB10 | DB9  | DB8 | DB7 | DB6 | DB5 | DB4 | DB3             | DB2   | DB1   | DB0   |

| 0    | 0        | 0    | V1       | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | N16  | N15  | N14  | N13  | N12  | N11  | N10    | N9    | N8   | N7   | N6   | N5  | N4  | N3  | N2  | N1  | C4(0)           | C3(0) | C2(0) | C1(0) |

# FRAC1 REGISTER (R1)

| ß    | í    | Eυ          |      |                                                                                                                         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |    |    |    |    |    |    | DBB |       |       |       |       |

|------|------|-------------|------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|----|----|----|----|----|----|-----|-------|-------|-------|-------|

| ¥    |      | Ž<br>K      |      | 25-BIT FRAC1 VALUE (FRAC1)                                                                                              |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | CONT |    |    |    |    |    |    |     |       |       |       |       |

| =    | L    | X<br>T<br>X |      |                                                                                                                         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |    |    |    |    |    |    |     |       |       |       |       |

| DB31 | DB30 | DB29        | DB28 | B28 DB27 DB26 DB25 DB24 DB23 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 D |     |     |     |     |     |     |     |     |     |     |     |     | DB3 | DB2 | DB1 | DB0  |    |    |    |    |    |    |     |       |       |       |       |

| D1   | 0    | 0           | F25  | F24                                                                                                                     | F23 | F22 | F21 | F20 | F19 | F18 | F17 | F16 | F15 | F14 | F13 | F12 | F11 | F10 | F9  | F8   | F7 | F6 | F5 | F4 | F3 | F2 | F1  | C4(0) | C3(0) | C2(0) | C1(1) |

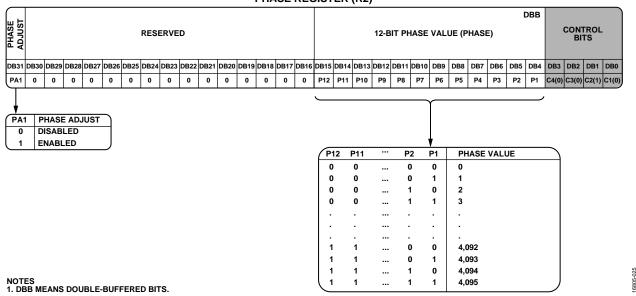

# PHASE REGISTER (R2)

| [ <b>L</b>      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |       |      |     |       |      |     | ı   | DBB |       |       |       |       |

|-----------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|-----|-------|------|-----|-----|-----|-------|-------|-------|-------|

| PHASE<br>ADJUST |      |      |      |      |      |      | RESI | ERVE | D    |      |      |      |      |      |      |      |      |      | 12-B | IT PH | IASE | VAL | JE (P | HASE | ≣)  |     |     |       | CONT  |       |       |

| DB31            | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11  | DB10 | DB9 | DB8   | DB7  | DB6 | DB5 | DB4 | DB3   | DB2   | DB1   | DB0   |

| PA1             | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | P12  | P11  | P10  | P9   | P8    | P7   | P6  | P5    | P4   | P3  | P2  | P1  | C4(0) | C3(0) | C2(1) | C1(0) |

# FRAC2 REGISTER (R3)

| $\bigcap$ |        | <u> </u> |      |      |      |      |      |      |      |      |      |      |      |       |      |      |        |      |      |      |      |     |     |     |     | ı   | DBB |       |            |       |       |

|-----------|--------|----------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|--------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|------------|-------|-------|

|           |        | RESERV   |      |      |      |      |      |      |      |      |      |      | 24-B | IT FR | AC2  | VALU | JE (FI | RAC2 | )    |      |      |     |     |     |     |     |     |       | CONT<br>BI |       |       |

| DB3       | 1 DB30 | DB29     | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17  | DB16 | DB15 | DB14   | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2        | DB1   | DB0   |

| O         | 0      | 0        | 0    | F24  | F23  | F22  | F21  | F20  | F19  | F18  | F17  | F16  | F15  | F14   | F13  | F12  | F11    | F10  | F9   | F8   | F7   | F6  | F5  | F4  | F3  | F2  | F1  | C4(0) | C3(0)      | C2(1) | C1(1) |

# MOD2 REGISTER (R4)

|      |      |          |      |      |      |      |      |      |      |      |      |      |      |       |      |      | ,     | ,    |      |      |      |     |     |     |     |     |     |       |                  |            |       |

|------|------|----------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|-------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|------------------|------------|-------|

|      |      | ESERVED  |      |      |      |      |      |      |      |      |      |      | 24-1 | BIT N | IOD2 | VALU | JE (M | OD2) |      |      |      |     |     |     |     | I   | OBB |       | CON <sup>-</sup> | TROL<br>TS |       |

| DB31 | DB30 | <u>~</u> | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17  | DB16 | DB15 | DB14  | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2              | DB1        | DB0   |

| T    | 0    | 0        | 0    | M24  | M23  | M22  | M21  | M20  | M19  | M18  | M17  | M16  | M15  | M14   | M13  | M12  | M11   | M10  | М9   | M8   | М7   | М6  | М5  | M4  | МЗ  | M2  | M1  | C4(0) | C3(1)            | C2(0)      | C1(0) |

NOTES

1. DBB MEANS DOUBLE-BUFFERED BITS.

Figure 20. Register Summary for Register 0 (R0) to Register 4 (R4)

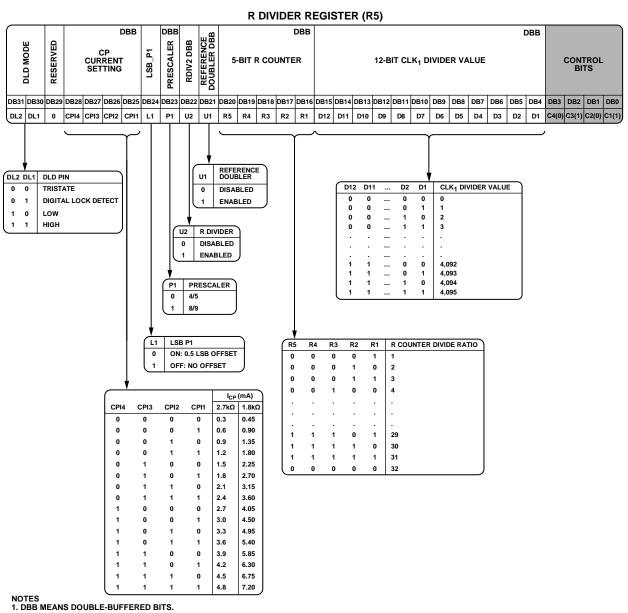

# R DIVIDER REGISTER (R5)

| $\bigcap$ | -,,         |      |                                                 | RESCALE A PARTIES AND A PARTIE |      |      |      |      |      |      |      |      |      |      | DBB  |      |      |      |            |      |      |      |     |     |     |     |     |     |       |       |       |       |

|-----------|-------------|------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|-------|-------|

|           | DI DI MODES |      | CP CURRENT BB COUNTER 12-BIT CLK1 DIVIDER VALUE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |      |      |      |      |      | LUE  |      |      |      |      |      | TROL<br>TS |      |      |      |     |     |     |     |     |     |       |       |       |       |

| DE        | 331         | DB30 | DB29                                            | DB28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13       | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1   | DB0   |

|           | L2          | DL1  | 0                                               | CPI4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CPI3 | CPI2 | CPI1 | L1   | P1   | U2   | U1   | R5   | R4   | R3   | R2   | R1   | D12  | D11  | D10        | D9   | D8   | D7   | D6  | D5  | D4  | D3  | D2  | D1  | C4(0) | C3(1) | C2(0) | C1(1) |

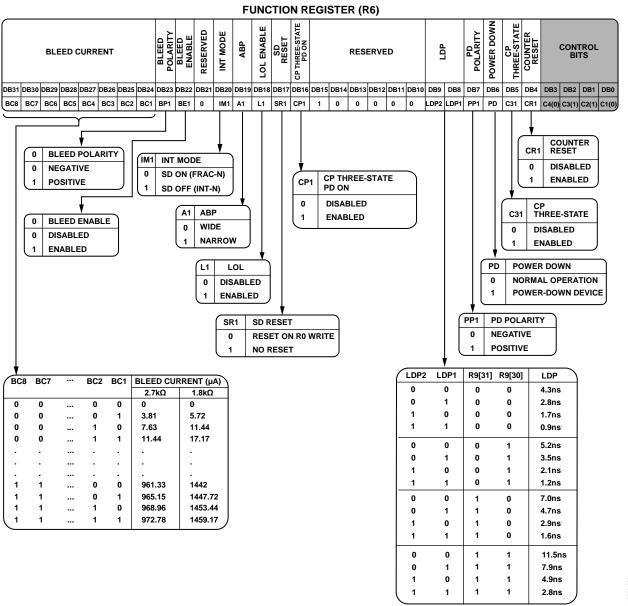

# **FUNCTION REGISTER (R6)**

|     | BLEED CURRENT    A |      |      |      |      |      |      |      |      |      | RES  | ERVE | ĒD   |      |      | Ì    | PD<br>POLARITY | POWER DOWN | CP<br>THREE-STATE | COUNTER |      | CON <sup>1</sup><br>BI |      |     |     |     |     |       |       |       |       |

|-----|--------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|----------------|------------|-------------------|---------|------|------------------------|------|-----|-----|-----|-----|-------|-------|-------|-------|

| DB3 | 1 DB30             | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14           | DB13       | DB12              | DB11    | DB10 | DB9                    | DB8  | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1   | DB0   |

| BC8 | вс7                | BC6  | BC5  | BC4  | всз  | BC2  | BC1  | BP1  | BE1  | 0    | IM1  | A1   | LOL1 | SD1  | CP1  | 1    | 0              | 0          | 0                 | 0       | 0    | LDP2                   | LDP1 | PP1 | PD  | C31 | CR1 | C4(0) | C3(1) | C2(1) | C1(0) |

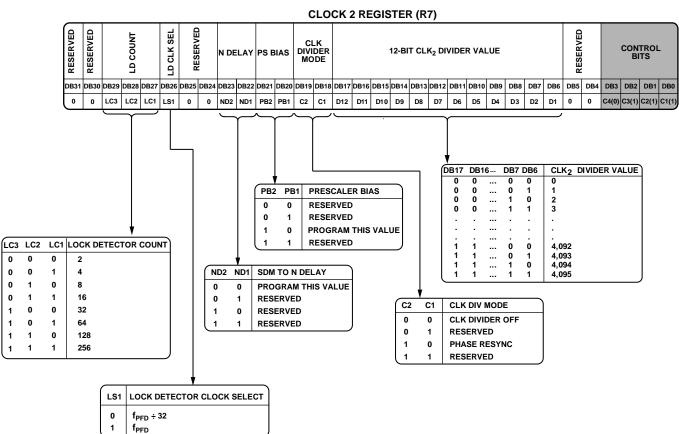

# **CLOCK 2 REGISTER (R7)**

|      | KESEKVED |      | LD_COUNT |      | LD_CLK_SEL |      | RESERVED | 2    | N DELA | PCRIAC |      | CL<br>DIVI<br>MO | DER  |      |      | ,    | 12-BI | T CL | K <sub>2</sub> DI | VIDE | R VAI | _UE |     |     |     | CI K DIV SEI |     |       |       | TROL<br>TS | -     |

|------|----------|------|----------|------|------------|------|----------|------|--------|--------|------|------------------|------|------|------|------|-------|------|-------------------|------|-------|-----|-----|-----|-----|--------------|-----|-------|-------|------------|-------|

| DB31 | DB30     | DB29 | DB28     | DB27 | DB26       | DB25 | DB24     | DB23 | DB22   | DB21   | DB20 | DB19             | DB18 | DB17 | DB16 | DB15 | DB14  | DB13 | DB12              | DB11 | DB10  | DB9 | DB8 | DB7 | DB6 | DB5          | DB4 | DB3   | DB2   | DB1        | DB0   |

| 0    | 0        | CN3  | CN2      | CN1  | LD1        | 0    | 0        | ND2  | ND1    | PB2    | PB1  | C2               | C1   | D12  | D11  | D10  | D9    | D8   | D7                | D6   | D5    | D4  | D3  | D2  | D1  | CS2          | CS1 | C4(0) | C3(1) | C2(1)      | C1(1) |

# **RESERVED REGISTER (R8)**

|     |       |      |      |      |      |      |      |      |      | RE   | ESER | VED  |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       | CON<br>BI | TROL<br>TS |       |

|-----|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-----------|------------|-------|

| DB3 | 1 DB3 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2       | DB1        | DB0   |

| [o  | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(1) | C3(0)     | C2(0)      | C1(0) |

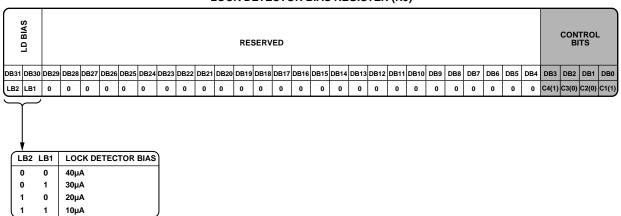

# **RESERVED REGISTER (R9)**

|      | LD BIAS |      |      |      |      |      |      |      |      |      |      |      | RES  | ERVE | Đ    |      |      |      |      |      |      |     |     |     |     |     |     |       | CON'  | TROL<br>TS |       |

|------|---------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|------------|-------|

| DB31 | DB30    | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1        | DB0   |