# **ADF4368**

# Microwave Wideband Synthesizer with Integrated VCO

#### **FEATURES**

- ▶ Output frequency range: 800 MHz to 12.8 GHz

- Jitter < 30 fs<sub>RMS</sub> f<sub>OUT</sub> = 9.001 GHz, f<sub>REF</sub> = f<sub>PFD</sub> = 250 MHz, fractional mode

- ▶ Wideband phase noise floor: -160 dBc/Hz at 12.8 GHz

- PLL specifications

- Normalized in-band phase noise floor

- ► -239 dBc/Hz: integer, -237 dBc/Hz: fractional mode

- Normalized 1/f phase noise floor

- ► -287 dBc/Hz: normalized to 1 Hz

- ▶ -147 dBc/Hz: normalized to 1 GHz at 10 kHz

- ▶ 625 MHz phase detector frequency integer mode

- 250 MHz phase detector frequency fractional mode

- 25-bit fixed, 49-bit combined fractional modulus

- 4 GHz reference input frequency

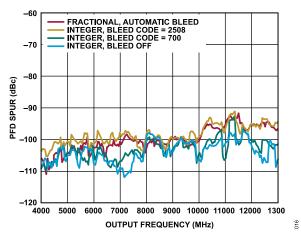

- ► Typical -95 dBc PFD spurs

- Reference to output delay specifications

- ▶ Temperature coefficient: 0.06 ps/°C

- Adjustment step size: <1 ps</p>

- Multichip output phase alignment

- ► Through SYNC pin or by EZSync method

- ▶ 3.3 V and 5 V power supplies

- ► ADIsimPLL<sup>™</sup> loop filter design tool support

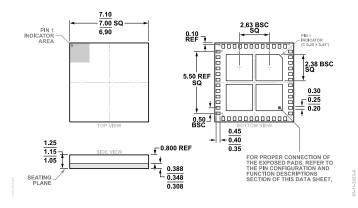

- Available in 48-lead, 7 mm × 7 mm LGA package

- -40°C to +125°C operating junction temperature

### **APPLICATIONS**

- Wireless infrastructure (MC-GSM, 5G)

- Test and measurement

- Aerospace and defense

### **GENERAL DESCRIPTION**

The ADF4368 is a high performance, ultra-low jitter, integer-N and fractional-N phase-locked loop (PLL) with integrated VCO ideally suited for frequency conversion applications.

The high performance PLL has a figure of merit of -239 dBc/Hz, very low 1/f noise of normalized -287 dBc/Hz and high PFD frequency that can achieve ultra-low in-band noise and integrated jitter. The ADF4368 can generate any frequency from 800 MHz to 12.8 GHz without an internal doubler, which eliminates the need for sub-harmonic filters. The  $\Sigma$ - $\Delta$  modulator includes a 25-bit fixed modulus that allows hertz frequency resolution and an additional 17-bit variable modulus, which allows even finer resolution and flexibility for frequency planning. The 9 dBm output power at 12.8 GHz in single-ended configuration with 16 step power adjust feature makes it very useful for any application.

For multiple frequency conversion applications, such as phase array radar or massive MIMO systems, the outputs of multiple ADF4368 can be aligned by using the SYNC input or EZSync<sup>™</sup>. The EZSync method is used when it is difficult to distribute the SYNC signal to all devices precisely. For applications that require deterministic delay or delay adjustment capability, a programmable reference to output delay with <1 ps resolution is provided. The reference to output delay is guaranteed across multiple devices and temperature, allowing for predictable and precise multichip alignment.

The simplicity of the ADF4368 block diagram eases development time with a simplified serial-peripheral interface (SPI) register map, external SYNC input, and repeatable multichip phase alignment both in integer mode and fractional mode.

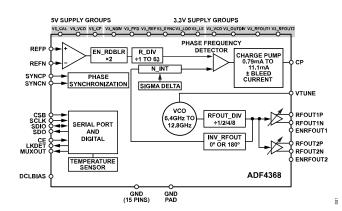

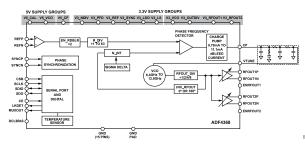

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1. ADF4368 Block Diagram

Rev. 0

DOCUMENT FEEDBACK

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### TABLE OF CONTENTS

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Functional Block Diagram                    |    |

| Specifications                              | 3  |

| Serial Interface Timing Characteristics     | 7  |

| Timing Diagrams                             | 7  |

| Absolute Maximum Ratings                    | 8  |

| Transistor Count                            | 8  |

| Thermal Resistance                          | 8  |

| Electrostatic Discharge (ESD) Ratings       | 8  |

| ESD Caution                                 | 8  |

| Pin Configuration and Function Descriptions | 9  |

| Typical Performance Characteristics         | 11 |

| Theory of Operation                         | 16 |

### **REVISION HISTORY**

3/2023—Revision 0: Initial Version

| Introduction                         | 16 |

|--------------------------------------|----|

| Output Frequency                     | 16 |

| Circuit Description                  |    |

| Applications Information             | 22 |

| Loop Filter Design                   | 22 |

| Reference Source Considerations      |    |

| Output Phase Noise Characteristics   | 23 |

| Power-Up and Initialization Sequence | 23 |

| Power Supply and Bypassing           | 26 |

| Register Maps                        | 27 |

| Register Details                     |    |

| Outline Dimensions                   |    |

| Ordering Guide                       | 54 |

| Evaluation Boards                    |    |

|                                      |    |

$V_{3.3V\_1} = V_{3.3V\_2} = 3.15$  V to 3.45 V,  $V_{V5\_VCO} = V_{V5\_CP} = V_{V5\_CAL} = 4.75$  V to 5.25 V, all voltages are with respect to GND,  $T_A = -40^{\circ}$ C to 105°C operating temperature range, unless otherwise noted.

#### Table 1. Electrical Specifications

| Parameter                                      | Symbol            | Min              | Тур          | Max              | Unit             | Test Conditions/Comments                                                   |

|------------------------------------------------|-------------------|------------------|--------------|------------------|------------------|----------------------------------------------------------------------------|

| REFERENCE INPUTS (REFP, REFN)                  |                   |                  |              |                  |                  |                                                                            |

| Input Frequency                                | f <sub>REF</sub>  | 10               |              | 4000             | MHz              |                                                                            |

| Input Signal Level                             | V <sub>REF</sub>  | 0.5              |              | 2.6              | V p-p            | Differential                                                               |

| Min Input Slew Rate                            |                   |                  | 100          |                  | V/µs             |                                                                            |

| Input Duty Cycle                               |                   |                  | 50           |                  | %                |                                                                            |

| Self-Bias Voltage                              |                   |                  | 1.85         |                  | V                |                                                                            |

| Input Resistance                               |                   |                  | 3            |                  | kΩ               | Differential                                                               |

| Input Capacitance                              |                   |                  | 1            |                  | pF               | Differential                                                               |

| Input Current                                  |                   |                  | 2            |                  | μA               |                                                                            |

| REFERENCE PEAK DETECTOR                        |                   |                  |              |                  |                  |                                                                            |

| Input Frequency                                |                   | 10               |              | 4000             | MHz              |                                                                            |

| Minimum Input Signal Detected (REF_OK = 1)     |                   |                  | 200          |                  | mV <sub>pp</sub> | f <sub>REF</sub> = 100 MHz, single-ended sine wave                         |

| Maximum Input Signal Not Detected (REF_OK = 0) |                   |                  | 160          |                  | mV <sub>pp</sub> | f <sub>REF</sub> = 100 MHz, single-ended sine wave                         |

| SYNC INPUTS (SYNCP, SYNCN)                     |                   |                  |              |                  | FF               |                                                                            |

| Input Signal Level                             | V <sub>REF</sub>  | 0.4 <sup>1</sup> |              | 2.6 <sup>1</sup> | V р-р            | LVDS mode, differential                                                    |

|                                                | V <sub>REF</sub>  | 0.5 <sup>1</sup> |              | 2.6 <sup>1</sup> | V p-p            | CML mode, differential                                                     |

| Self-Bias Voltage                              |                   |                  | 1.3          |                  | V                | LVDS mode                                                                  |

|                                                |                   |                  | 1.85         |                  | V                | CML mode                                                                   |

| Input Resistance                               |                   |                  | 3            |                  | kΩ               | Differential                                                               |

| Input Capacitance                              |                   |                  | 1            |                  | pF               | Differential                                                               |

| Input Current                                  |                   |                  | 3            |                  | μΑ               |                                                                            |

| REFERENCE DIVIDER (R)                          |                   | _                |              |                  |                  |                                                                            |

| R                                              |                   | 1                |              | 63               |                  | All integers included                                                      |

| REFERENCE DOUBLER                              |                   |                  |              |                  |                  |                                                                            |

| Input Frequency                                | f <sub>RDBL</sub> | 10               |              | 250              | MHz              | EN_RDBLR = 1                                                               |

| PHASE/FREQUENCY DETECTOR (PFD)                 | RODE              |                  |              |                  |                  |                                                                            |

| Input Frequency                                | f <sub>PFD</sub>  |                  |              |                  |                  |                                                                            |

|                                                |                   | 3 <sup>1</sup>   |              | 625              | MHz              | Integer mode                                                               |

|                                                |                   | 3 <sup>1</sup>   |              | 250              | MHz              | Fractional mode sync or non-sync                                           |

|                                                |                   | 3 <sup>1</sup>   |              | 250 <sup>1</sup> | MHz              | applications<br>Fractional mode phase resync applications                  |

|                                                |                   | 75 <sup>1</sup>  |              | 250 <sup>1</sup> | MHz              | when f <sub>OUT</sub> ≥ 3 GHz<br>Fractional mode phase resync applications |

|                                                |                   |                  |              | 200              |                  | when f <sub>OUT</sub> < 3 GHz                                              |

| CHARGE PUMP (CP)                               |                   |                  |              |                  |                  |                                                                            |

| Output Current Range                           | I <sub>CP</sub>   |                  | 0.79 to 11.1 |                  | mA               | Set by CP_I                                                                |

| Output Current Source/Sink Accuracy            |                   |                  | ±2           |                  | %                | All setting, = $V_{CP} = V_{V5\_CP} / 2$                                   |

| Output Current Source/Sink Matching            |                   |                  | ±2           |                  | %                | All setting, $V_{CP} = V_{V5_CP} / 2$                                      |

| Output Current vs. Output Volt Sensitivity     |                   |                  | 0.2          |                  | %V/V             | $1.4 V < V_{V5_{CP}} < V_{CP-5V} - 1.6 V$                                  |

| Output Current vs. Temperature                 |                   |                  | 400          |                  | ppm/C            | $V_{CP} = V_{V5_{CP}} / 2$                                                 |

| Output High-Z Leakage Current                  |                   |                  | -0.01        |                  | μA               | Minimum I <sub>CP</sub> , 1.4 V < $V_{V5_{CP}}$ < $V_{CP-5V}$ – 1.6 V      |

| Output High-Z Leakage Current                  |                   | _                | -0.3         |                  | μA               | Maximum I <sub>CP</sub> , 1.4 V < $V_{V5_{CP}}$ < $V_{CP-5V}$ – 1.6 V      |

| VCO                                            |                   |                  |              |                  |                  |                                                                            |

| Frequency Range                                | f <sub>VCO</sub>  | 6.4              |              | 12.8             | GHz              |                                                                            |

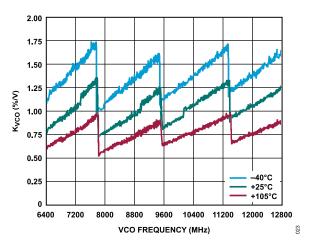

| Tuning Sensitivity <sup>2, 3</sup>             | K <sub>VCO</sub>  |                  | 0.75 to 1.25 |                  | %Hz/V            |                                                                            |

### Table 1. Electrical Specifications (Continued)

| Parameter                                      | Symbol                                 | Min                     | Тур                                      | Мах  | Unit  | Test Conditions/Comments                                                                                                                       |

|------------------------------------------------|----------------------------------------|-------------------------|------------------------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

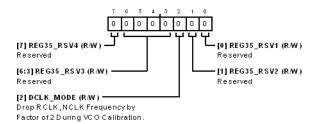

| DIV_RCLK VCO Calibration Frequency             | f <sub>DIV_RCLK</sub>                  |                         |                                          | 125  | MHz   | Must set DCLK_MODE = 1, when f <sub>DIV_RCLK</sub> > 80 MHz                                                                                    |

| FEEDBACK (N) AND OUTPUT DIVIDER (O)            |                                        |                         |                                          |      |       |                                                                                                                                                |

| Ν                                              |                                        | 4                       |                                          | 4095 |       | Integer mode                                                                                                                                   |

|                                                |                                        | 19                      |                                          | 4095 |       | Fractional mode                                                                                                                                |

| 0                                              |                                        | 1                       |                                          | 8    |       | 1, 2, 4, 8                                                                                                                                     |

| RF OUTPUTS (RFOUT1P/N, RFOUT2P/N)              |                                        |                         |                                          |      |       | Differential termination = 100 Ω for all RF output specifications, unless noted                                                                |

| Output Frequency                               | f <sub>OUT</sub>                       | 0.8                     |                                          | 12.8 | GHz   |                                                                                                                                                |

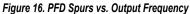

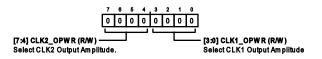

| Output Single-Ended Power                      | V <sub>OD</sub>                        |                         | 9                                        |      | dBm   | CLK1_OPWR = CLK2_OPWR = 15, f <sub>OUT</sub> = 4<br>GHz to 12.8 GHz                                                                            |

|                                                |                                        |                         | 5.5                                      |      | dBm   | CLK1_OPWR = CLK2_OPWR = 10, f <sub>OUT</sub> = 4<br>GHz to 12.8 GHz                                                                            |

|                                                |                                        |                         | 1.5                                      |      | dBm   | CLK1_OPWR = CLK2_OPWR = 5, f <sub>OUT</sub> = 4<br>GHz to 12.8 GHz                                                                             |

|                                                |                                        |                         | -2                                       |      | dBm   | CLK1_OPWR = CLK2_OPWR = 0, f <sub>OUT</sub> = 4<br>GHz to 12.8 GHz                                                                             |

| Output Resistance                              |                                        |                         | 100                                      |      | Ω     | Differential                                                                                                                                   |

| Output Common Mode                             |                                        |                         | V <sub>3.3V_2</sub> -<br>V <sub>OD</sub> |      | V     | No pull-up inductor                                                                                                                            |

|                                                |                                        |                         | V <sub>3.3V_2</sub>                      |      | V     | With pull-up inductor                                                                                                                          |

| Output Rise Time                               | t <sub>R</sub>                         |                         | 18                                       |      | ps    | 20%-80%, CLK1_OPWR = CLK2_OPWR = 10,                                                                                                           |

| Output Fall Time                               | t <sub>F</sub>                         |                         | 18                                       |      | ps    | 80%-20%, CLK1_OPWR = CLK2_OPWR = 10,                                                                                                           |

| Output Duty Cycle                              |                                        |                         | 50                                       |      | %     |                                                                                                                                                |

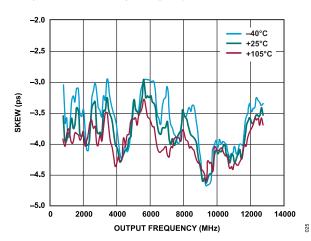

| Skew, RFOUT1 to RFOUT2                         |                                        |                         | 3 ± 1                                    |      | ps    | One ADF4368 device                                                                                                                             |

|                                                |                                        |                         | 3±1                                      |      | ps    | Across multiple ADF4368 devices, T <sub>J</sub><br>within 10°C, same R_DIV, CLKOUT_DIV,<br>EN_RDBLR used                                       |

| REFERENCE INPUT TO OUTPUT DELAY                |                                        |                         |                                          |      |       | Device setup for all delay specifications,<br>unless noted, measure rising reference edge<br>at REFP input to rising edge at RFOUT1P<br>output |

| Propagation Delay                              | t <sub>PD</sub>                        |                         | 190                                      |      | ps    | REF_SEL = 0, R = 1, doubler = disabled                                                                                                         |

| Propagation Delay Temperature Coefficient      | t <sub>PD</sub>                        |                         | 0.06                                     |      | ps/°C | REF_SEL = 0                                                                                                                                    |

| LOGIC INPUTS (CSB, SCLK, SDIO, ENCLK1, ENCLK2) |                                        |                         |                                          |      |       |                                                                                                                                                |

| Input High Voltage                             | V <sub>INH</sub>                       | 1.2                     |                                          |      | V     |                                                                                                                                                |

| Input Low Voltage                              | V <sub>INL</sub>                       |                         |                                          | 0.6  | V     |                                                                                                                                                |

| Input Current (High, Low)                      | I <sub>IH</sub> /I <sub>IL</sub>       |                         |                                          | ±1   | μA    |                                                                                                                                                |

| Input Capacitance                              | CIN                                    |                         | 2                                        |      | pF    |                                                                                                                                                |

| LOGIC INPUT (CE)                               |                                        |                         |                                          |      |       |                                                                                                                                                |

| Input High Voltage                             | V <sub>INH-3V</sub>                    | 1.8                     |                                          |      | V     |                                                                                                                                                |

| Input Low Voltage                              | V <sub>INL-3V</sub>                    |                         |                                          | 0.8  | V     |                                                                                                                                                |

| Input Current (High, Low)                      | I <sub>IH-3V</sub> /I <sub>IL-3V</sub> |                         |                                          | ±1   | μA    |                                                                                                                                                |

| Input Capacitance                              | C <sub>IN-3V</sub>                     |                         | 1                                        |      | pF    |                                                                                                                                                |

| LOGIC OUTPUTS (SDIO, SDO, LKDET, MUXOUT)       |                                        |                         |                                          |      |       |                                                                                                                                                |

| Output High Voltage                            | V <sub>OH</sub>                        | 1.5                     | 1.8                                      |      | V     | I <sub>OH</sub> = 500 μA, 1.8 V output selected (default setting)                                                                              |

| Output High Voltage                            | V <sub>OH-3V</sub>                     | V <sub>3.3V</sub> - 0.4 |                                          |      |       | $I_{OH}$ = 500 µA, 3.3 V output selected, set by voltage on V_LDO pin                                                                          |

#### Table 1. Electrical Specifications (Continued)

| Parameter                          | Symbol                           | Min  | Тур | Мах  | Unit | Test Conditions/Comments                                                                                                                      |

|------------------------------------|----------------------------------|------|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Output Low Voltage                 | V <sub>OL</sub>                  |      |     | 0.4  | V    | I <sub>OL</sub> = 500 μA                                                                                                                      |

| SDO High-Z Leakage                 | I <sub>ZH</sub> /I <sub>ZL</sub> |      |     | ±1   | μA   |                                                                                                                                               |

| POWER SUPPLIES                     |                                  |      |     |      |      | Device setup is default configuration for all<br>supply current specifications, unless noted                                                  |

| V5_VCO Supply Range                | V <sub>V5_VCO</sub>              | 4.75 | 5   | 5.25 | V    |                                                                                                                                               |

| V5_CAL Supply Range                | V <sub>V5_CAL</sub>              | 4.75 | 5   | 5.25 | V    |                                                                                                                                               |

| V5_CP Supply Range                 | V <sub>V5_CP</sub>               | 4.75 | 5   | 5.25 | V    |                                                                                                                                               |

| V <sub>3.3V_1</sub> Supply Range   | V <sub>3.3V_1</sub>              | 3.15 | 3.3 | 3.45 | V    | Group 1: V3_LS, V3_LDO, V3_REF, V3_PFD<br>V3_NDIV, V3_SYNC                                                                                    |

| V <sub>3.3V_2</sub> Supply Range   | V <sub>3.3V_2</sub>              | 3.15 | 3.3 | 3.45 | V    | Group 2: V3_RFOUT1, V3_RFOUT2,<br>V3_VCO, V3_CLKDIV                                                                                           |

| V5_VCO Supply Current              | I <sub>V5_VCO</sub>              |      | 98  |      | mA   | f <sub>OUT</sub> = 12.8 GHz                                                                                                                   |

|                                    | _                                |      | 173 | 220  | mA   | f <sub>OUT</sub> = 6.4 GHz                                                                                                                    |

| V5_CAL Supply Current              | I <sub>V5_CAL</sub>              |      | 50  |      | μA   |                                                                                                                                               |

|                                    |                                  |      | 8   |      | mA   | During VCO calibration                                                                                                                        |

| V5_CP Supply Current               | I <sub>V5_CP</sub>               |      | 58  | 67   | mA   | I <sub>CP</sub> = 11.1 mA, CP I = 15                                                                                                          |

| ,                                  |                                  |      | 41  |      | mA   | $I_{CP} = 0.79 \text{ mA}, CP \text{ I} = 0$                                                                                                  |

|                                    |                                  |      | 3.2 |      | mA   | Additional current when EN_BLEED = 1,<br>BLEED_I = 8191                                                                                       |

| V <sub>3.3V_1</sub> Supply Current | I <sub>3.3V_1</sub>              |      | 185 | 210  | mA   | f <sub>REF</sub> = 122.88 MHz, f <sub>PFD</sub> = 245.76 MHz,<br>fractional mode, CP_I = 15, PD_SYNC = 1<br>(sync disabled)                   |

|                                    |                                  |      | 4   |      | mA   | Additional current when PD_LD = 0                                                                                                             |

|                                    |                                  |      | 4   |      | mA   | Additional current when PD_RDET = 1                                                                                                           |

| V3_SYNC Supply Current             | I <sub>V3_SYNC</sub>             |      | 15  |      | mA   | PD_SYNC = 0 (synchronization is enabled)                                                                                                      |

| V3 RFOUTx Supply Current           | I <sub>V3_RFOUT</sub>            |      | 35  |      | mA   | CLKx OPWR = 0                                                                                                                                 |

|                                    | V3_11 001                        |      | 47  |      | mA   | CLKx_OPWR = 4                                                                                                                                 |

|                                    |                                  |      | 65  |      | mA   | CLKx_OPWR = 8                                                                                                                                 |

|                                    |                                  |      | 90  |      | mA   | CLKx_OPWR = 12                                                                                                                                |

|                                    |                                  |      | 105 |      | mA   | CLKx_OPWR = 15                                                                                                                                |

| V3 OUTDIV Supply Current           | I <sub>V3_OUTDIV</sub>           |      | 108 |      | mA   | CLKOUT_DIV = 0 (divide by 1)                                                                                                                  |

|                                    | .03_001010                       |      | 132 |      | mA   | CLKOUT_DIV = 3 (divide by 8)                                                                                                                  |

| V <sub>3.3V_2</sub> Supply Current | I <sub>3.3V_2</sub>              |      | 149 |      | mA   | ENRFOUT1 = low, CLK2_OPWR = 0<br>(minimum power), CLKOUT_DIV = 0, f <sub>OUT</sub> =<br>9.6 GHz                                               |

|                                    |                                  |      | 218 |      | mA   | ENRFOUT1 = low, CLK2_OPWR = 15<br>(maximum power), CLKOUT_DIV = 0, f <sub>OUT</sub> =<br>9.6 GHz                                              |

|                                    |                                  |      | 172 |      | mA   | ENRFOUT1 = low, CLK2_OPWR = 0<br>(minimum power), CLKOUT_DIV = 1, f <sub>OUT</sub> = 5.6 GHz                                                  |

|                                    |                                  |      | 241 |      | mA   | ENRFOUT1 = low, CLK2_OPWR = 15<br>(maximum power), CLKOUT_DIV = 1, f <sub>OUT</sub> = 5.6 GHz                                                 |

| Typical Power Dissipation          | P <sub>DIS</sub>                 |      | 2.3 |      | W    | ENRFOUT1 = low, CLK2_OPWR = 15<br>(maximum power), CLKOUT_DIV = 0, f <sub>OUT</sub><br>= 9.6 GHz, SYNC block powered down,<br>fractional mode |

|                                    |                                  |      | 2.1 |      | W    | ENRFOUT1 = low, CLK2_OPWR = 15<br>(maximum power), CLKOUT_DIV = 1, f <sub>OUT</sub>                                                           |

#### Table 1. Electrical Specifications (Continued)

| Parameter                                                                                      | Symbol                  | Min | Тур  | Мах  | Unit              | Test Conditions/Comments                                              |

|------------------------------------------------------------------------------------------------|-------------------------|-----|------|------|-------------------|-----------------------------------------------------------------------|

|                                                                                                |                         |     |      |      |                   | = 5.6 GHz, SYNC block powered down,<br>fractional mode                |

| Typical Power Down Current, 3.3 V                                                              |                         |     | 11   | 15   | mA                | PD_ALL = 1, I <sub>3.3V_1</sub> + I <sub>3.3V_2</sub>                 |

| Typical Power Down Current, 5 V Supplies                                                       |                         |     | 350  | 750  | μA                | $PD_ALL = 1, I_{V5_VCO} + I_{V5_CAL} + I_{V5_CP}$                     |

| Typical Disable Current, 3.3 V Supplies                                                        |                         |     | 100  | 1500 | μA                | CE = low, $I_{3.3V_1} + I_{3.3V_2}$                                   |

| Typical Disable Current, 5 V Supplies                                                          |                         |     | 350  | 750  | μA                | $CE = Iow, I_{V5_VCO} + I_{V5_CAL} + I_{V5_CP}$                       |

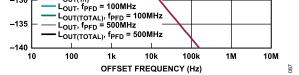

| RF OUTPUT NOISE CHARACTERISTICS                                                                |                         |     |      |      |                   |                                                                       |

| 12.8 GHz Output Frequency                                                                      |                         |     |      |      |                   | $f_{REF} = f_{PFD} = 250 \text{ MHz}$ , fractional mode, CP_I = 15    |

| Phase Noise Floor                                                                              |                         |     | -160 |      | dBc/Hz            |                                                                       |

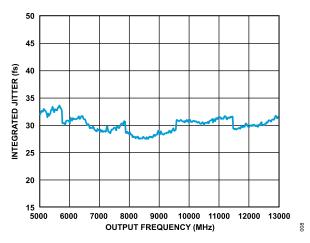

| RMS Jitter, 100 Hz to 100 MHz Integration                                                      |                         |     | 32   |      | fs <sub>RMS</sub> |                                                                       |

| 9.001 GHz Output Frequency                                                                     |                         |     |      |      |                   | $f_{REF} = f_{PFD} = 250 \text{ MHz}$ , fractional mode, CP_I = 15    |

| Phase Noise Floor                                                                              |                         |     | -160 |      | dBc/Hz            |                                                                       |

| RMS Jitter, 100 Hz to 100 MHz Integration                                                      |                         |     | 29   |      | fs <sub>RMS</sub> |                                                                       |

| 7.6 GHz Output Frequency                                                                       |                         |     |      |      |                   | $f_{REF} = f_{PFD} = 250 \text{ MHz}$ , fractional mode, CP_I = 15    |

| Phase Noise Floor                                                                              |                         |     | -160 |      | dBc/Hz            |                                                                       |

| RMS Jitter, 100 Hz to 100 MHz Integration                                                      |                         |     | 31   |      | fs <sub>RMS</sub> |                                                                       |

| 6.4 GHz Output Frequency                                                                       |                         |     |      |      |                   | $f_{REF} = f_{PFD} = 250 \text{ MHz}$ , fractional mode, CP_I = 15    |

| Phase Noise Floor                                                                              |                         |     | -161 |      | dBc/Hz            |                                                                       |

| RMS Jitter, 100 Hz to 100 MHz Integration                                                      |                         |     | 30   |      | fs <sub>RMS</sub> |                                                                       |

| 5.025 GHz Output Frequency                                                                     |                         |     |      |      |                   | $f_{REF} = f_{PFD} = 250 \text{ MHz}$ , fractional mode, CP_I<br>= 15 |

| Phase Noise Floor                                                                              |                         |     | -163 |      | dBc/Hz            |                                                                       |

| RMS Jitter, 100 Hz to 100 MHz Integration<br>Normalized In-Band Phase Noise Floor <sup>4</sup> |                         |     | 33   |      | fs <sub>RMS</sub> |                                                                       |

| L <sub>NORM-INT</sub>                                                                          |                         |     | -239 |      | dBc/Hz            |                                                                       |

| L <sub>NORM-FRC</sub>                                                                          |                         |     | -237 |      | dBc/Hz            |                                                                       |

| Normalized 1/f Phase Noise Floor <sup>4, 5</sup>                                               |                         |     |      |      |                   |                                                                       |

| $L_{1/f}^5$                                                                                    |                         |     | -287 |      | dBc/Hz            | Normalized to 1 Hz                                                    |

| L <sub>1/f_1G_10k</sub> <sup>5</sup>                                                           |                         |     | -147 |      | dBc/Hz            | Normalized to 1 GHz at 10 kHz offset                                  |

| Integer Boundary Spurs (Filtered)                                                              | IBS                     |     | -95  |      | dBc               | Spur is out of the loop bandwidth                                     |

| Integer Boundary Spurs (Unfiltered)                                                            | IBS                     |     | -60  |      | dBc               | Measured at 5 kHz offset from integer channe                          |

| PFD Spur                                                                                       |                         |     | -95  |      | dBc               | Ŭ                                                                     |

| TEMPERATURE SENSOR (ADC)                                                                       |                         |     |      |      |                   |                                                                       |

| ADC Clock Frequency                                                                            | f <sub>ADC_CLK</sub>    |     |      | 400  | kHz               | ADC clock divider output                                              |

| ADC Clock Divider Frequency                                                                    | f <sub>ADC_CLKDIV</sub> |     |      | 125  | MHz               | ADC clock divider input                                               |

| Resolution                                                                                     |                         |     |      | 8    | Bits              | ,                                                                     |

<sup>1</sup> Based on design and characterization.

<sup>2</sup> Valid for 1.60 V  $\leq$  V<sub>VTUNE</sub>  $\leq$  2.85 V with device calibrated after a power cycle or software power-on reset.

<sup>3</sup> Based on characterization.

<sup>4</sup> These numbers are modeled in ADIsimPLL.

<sup>5</sup> Integration Range 1 kHz to f<sub>OUT</sub>.

### SERIAL INTERFACE TIMING CHARACTERISTICS

$V_{3.3V\_1} = V_{3.3V\_2} = 3.15$  V to 3.45 V,  $V_{V5\_VCO} = V_{V5\_CP} = V_{V5\_CAL} = 4.75$  V to 5.25 V, all voltages are with respect to GND,  $T_A = -40^{\circ}$ C to +105°C operating temperature range, unless otherwise noted.

#### Table 2. Serial Interface Timing Characteristics

| Parameter                                | Symbol                   | Min | Тур | Max | Unit | Test Conditions/Comments             |

|------------------------------------------|--------------------------|-----|-----|-----|------|--------------------------------------|

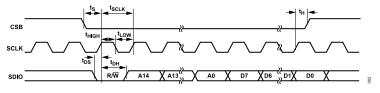

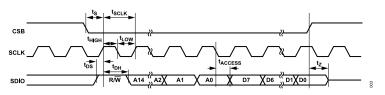

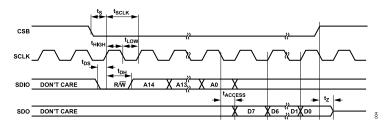

| SERIAL INTERFACE (CSB, SCLK, SDIO, SDO)  |                          |     |     |     |      | See Figure 2, Figure 3, and Figure 4 |

| SCLK Frequency                           | f <sub>SCLK</sub>        |     |     | 65  | MHz  |                                      |

| SCLK Pulse Width High                    | t <sub>HIGH</sub>        | 7.6 |     |     | ns   |                                      |

| SCLK Pulse Width Low                     | t <sub>LOW</sub>         | 7.6 |     |     | ns   |                                      |

| SDIO Setup Time                          | t <sub>DS</sub>          | 3   |     |     | ns   |                                      |

| SDIO Hold Time                           | t <sub>DH</sub>          | 3   |     |     | ns   |                                      |

| SCLK Fall Edge to SDIO Valid Prop Delay  | t <sub>ACCESS_SDIO</sub> | 7.6 |     |     | ns   |                                      |

| SCLK Fall Edge to SDO Valid Prop Delay   | t <sub>ACCESS_SDO</sub>  | 7.6 |     |     | ns   |                                      |

| CSB Rising Edge to SDIO High-Z           | tz                       | 7.6 |     |     | ns   |                                      |

| CSB Falling Edge to SCLK Rise Setup Time | t <sub>S</sub>           | 3   |     |     | ns   |                                      |

| SCLK Rising Edge to CSB Rise Hold Time   | t <sub>H</sub>           | 3   |     |     | ns   |                                      |

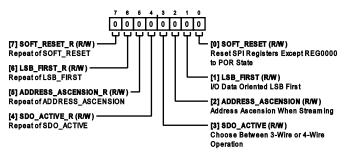

### TIMING DIAGRAMS

Figure 2. Write Timing Diagram

Figure 3. 3-Wire Read Timing Diagram (SDO\_ACTIVE = 0)

Figure 4. 4-Wire Read Timing Diagram (SDO\_ACTIVE = 1)

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3. Absolute Maximum Ratings

| Parameter                                                           | Rating                                                              |

|---------------------------------------------------------------------|---------------------------------------------------------------------|

| V <sub>3.3V_1</sub> (V3_LS, V3_LDO, V3_REF, V3_PFD, V3_NDIV) to GND | -0.3 V to +3.6 V                                                    |

| $V_{3.3V\_2}$ (V3_VCO, V3_OUTDIV, V3_RFOUT1, V3_FOUT2) to GND       | -0.3 V to +3.6 V                                                    |

| V <sub>5V</sub> (V5_CAL, V5_VCO, V5_CP) to GND                      | -0.3 V to +5.5 V                                                    |

| Voltage on CP Pin                                                   | -0.3 V to V5_CP + 0.3 V                                             |

| Digital Outputs (MUXOUT, LKDET, SDO, SDIO)                          | 5 mA                                                                |

| RFOUT1P, RFOUT1N, RFOUT2P, RFOUT2N                                  | Maximum (GND - 0.3 V, $V_{3.3V_2}$ - 1.2 V) to $V_{3.3V_2}$ + 0.3 V |

| REFP, REFN                                                          | -0.65 V to V <sub>3.3V 1</sub> + 0.65 V                             |

| Voltage on all Other Pins                                           | $-0.3$ V to V <sub>3.3V</sub> $^{-1}_{1}$ + 0.3 V                   |

| REFP to REFN and SYNCP to SYNCN                                     | ±1.35 V                                                             |

| Temperature                                                         |                                                                     |

| Operating Junction Range <sup>1</sup>                               | -40°C to +125°C                                                     |

| Storage Range                                                       | -65°C to +125°C                                                     |

| Maximum Junction                                                    | 125°C                                                               |

| Reflow Soldering                                                    |                                                                     |

| Peak Temperature                                                    | 260°C                                                               |

| Time at Peak Temperature                                            | 30 sec                                                              |

<sup>1</sup> Device is guaranteed to meet the specified performance limits over the full operating junction temperature range.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### TRANSISTOR COUNT

The transistor count for the ADF4368 is 199076 (CMOS) and 3366 (bipolar).

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction-to-case thermal resistance.

#### Table 4. Thermal Resistance

| Package Type          | θ <sub>JA</sub> | θ <sub>JC-TOP</sub> | θ <sub>JC-</sub><br>воттом | θ <sub>JB</sub> | $\Psi_{JT}$ | Ψ <sub>JB</sub> | Unit |

|-----------------------|-----------------|---------------------|----------------------------|-----------------|-------------|-----------------|------|

| CC-48-13 <sup>1</sup> | 22.38           | 16.86               | 5.1                        | 8.33            | 1.35        | 7.89            | °C/W |

<sup>1</sup> Test Condition 1: thermal impedance simulated values are based on use of a 4-layer PCB with the thermal impedance paddle soldered to a ground plane.

### **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDDEC JS-001. Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

#### **ESD Ratings for ADF4368**

#### Table 5. ESD Ratings for ADF4368

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| НВМ       | 4000                    | 3A    |

| CDM       | 1000                    | C3    |

#### ESD CAUTION

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

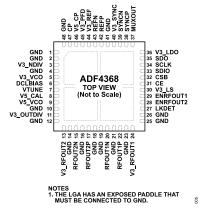

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

#### Table 6. Pin Function Descriptions

| Pin Number                                                       | Mnemonic            | Description                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 4, 10, 12,<br>14, 16, 18, 19,<br>21, 23, 25, 26,<br>41, 48 | GND                 | Negative Power Supply (Ground). These pins must be tied directly to the ground pad.                                                                                                                                                                                                                                                                                      |

| 3                                                                | V3_NDIV             | 3.15 V to 3.45 V Positive Power Supply Pin for the PLL Feedback Divider Circuitry. Short this pin to the other pins in 3.3 V power supply group 1.                                                                                                                                                                                                                       |

| 5                                                                | V3_VCO              | 3.15 V to 3.45 V Positive Power Supply Pin for the 3.3 V Portion of the VCO Circuitry. Short this pin to the other pins in 3.3 V power supply group 2.                                                                                                                                                                                                                   |

| 6                                                                | DCLBIAS             | Do not connect to this pin.                                                                                                                                                                                                                                                                                                                                              |

| 7                                                                | VTUNE               | VCO Tuning Input. This frequency control pin is normally connected to the external loop filter.                                                                                                                                                                                                                                                                          |

| 8                                                                | V5_CAL              | 4.75 V to 5.25 V Positive Power Supply Pin for VCO Calibration Circuitry. This pin can be shorted to the V5_VCO supply plane.                                                                                                                                                                                                                                            |

| 9                                                                | V5_VCO              | 4.75 V to 5.25 V Positive Power Supply Pin for the 5 V Portion of the VCO Circuitry.                                                                                                                                                                                                                                                                                     |

| 11                                                               | V3_OUTDIV           | 3.15 V to 3.45 V Positive Power Supply Pin for the Output Divider Circuitry. Short this pin to the other pins in 3.3 V power supply group 2.                                                                                                                                                                                                                             |

| 13                                                               | V3_RFOUT2           | 3.15 V to 3.45 V Positive Power Supply Pin for the RF Output 2 Buffer Circuitry. Short this pin to the other pins in 3.3 V power supply group 2.                                                                                                                                                                                                                         |

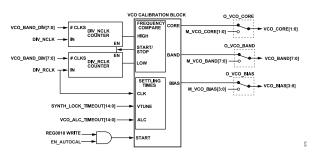

| 15, 17                                                           | RFOUT2N,<br>RFOUT2P | RF Output 2 Signal. The VCO output divider is buffered and presented differentially on these pins. The outputs have 50 $\Omega$ (typical) output resistance per side (100 $\Omega$ differential). The far end of the transmission line is typically terminated with 100 $\Omega$ connected across the outputs. The output amplitude is programmable via the serial port. |

| 20, 22                                                           | RFOUT1N,<br>RFOUT1P | RF Output 1 Signal. The VCO Output Divider is buffered and presented differentially on these pins. The outputs have 50 $\Omega$ (typical) output resistance per side (100 $\Omega$ differential). The far end of the transmission line is typically terminated with 100 $\Omega$ connected across the outputs. The output amplitude is programmable via the serial port. |

| 24                                                               | V3_RFOUT1           | 3.15 V to 3.45 V Positive Power Supply Pin for the RF Output 1 Buffer Circuitry. Short this pin to the other pins in 3.3 V power supply group 2.                                                                                                                                                                                                                         |

| 27                                                               | LKDET               | PLL Lock Detect. This output presents the lock status of the PLL. PLL is locked when LKDET is a logic high.                                                                                                                                                                                                                                                              |

| 28                                                               | ENRFOUT2            | Enable RF Output 2 Buffer. 3.3 V CMOS input. When ENRFOUT2 = high, the RFOUT2P and RFOUT2N output buffer is active. When ENRFOUT2 = low, RFOUT2P and RFOUT2N are powered down.                                                                                                                                                                                           |

| 29                                                               | ENRFOUT1            | Enable RF Output 1 Buffer. 3.3 V CMOS input. When ENRFOUT1 = high, the RFOUT1P and RFOUT1N output buffer is active. When ENRFOUT2 = low, RFOUT1P and RFOUT1N are powered down.                                                                                                                                                                                           |

| 30                                                               | V3_LS               | 3.15 V to 3.45 V Positive Power Supply Pin for the Internal Level Shift Circuitry. Short this pin to the other pins in 3.3 V power supply group 1.                                                                                                                                                                                                                       |

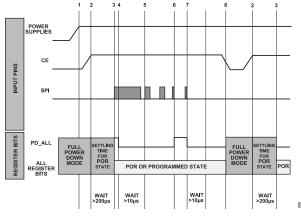

| 31                                                               | CE                  | Chip-Enable. Does not support 1.8 V CMOS levels. This CMOS input enables the device when driven high. A logic low disables the device, putting the device in a full power down state causing the register to reset. Conversely, the PD_ALL bit powers down the device, but does not reset the registers.                                                                 |

| 32                                                               | CSB                 | Serial Port Chip Select. 1.8 V and 3.3 V compatible CMOS input. This CMOS input initiates a serial port communication burst when driven low, ending the burst when driven back high.                                                                                                                                                                                     |

| 33                                                               | SDIO                | Serial Data Input/Output. 1.8 V and 3.3 V programmable CMOS input/output. When configured as an input, the serial port uses this CMOS input for data. In 3-wire readback mode (default mode), this pin outputs data from the serial port during a read communication burst.                                                                                              |

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

# Pin Number Mnemonic Description 34 SCLK Serial Port Clock. 1.8 V and 3.3 V compatible. This CMOS input clocks serial port input data on its rising edge.

#### Table 6. Pin Function Descriptions (Continued)

| 07          | OOLIN        | Condition of Clock. 1.5 V and 0.5 V compatible. This Ower Clocks Sonal porting a data of its fising dage.                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35          | SDO          | Optional Serial Data Output. 1.8 V and 3.3 V programmable CMOS output. In 3-wire mode (default mode), this three-state CMOS pin remains in a high impedance state. In 4-wire readback mode, this pin presents data from the serial port during a read communication burst. When the CSB is deasserted, SDO returns to a high impedance. Optionally, attach a resistor of >200 k $\Omega$ to prevent a floating output.                                                   |

| 36          | V3_LDO       | 3.15 V to 3.45 V Positive Power Supply Pin for the Internal LDO Circuitry. Short this pin to the other pins in 3.3 V power supply group 1.                                                                                                                                                                                                                                                                                                                               |

| 37          | MUXOUT       | Internal Device Mux Output. This output pin can be connected to multiple internal nodes for factory test and debug purposes.                                                                                                                                                                                                                                                                                                                                             |

| 38, 39      | SYNCP, SYNCN | Synchronization Input Signals. Both RF output signals are synchronized to an input signal at this pin. It is used for multichip phase synchronization. This differential input can accept both high and low common mode input signals (based on a SPI bit setting).                                                                                                                                                                                                      |

| 40          | V3_SYNC      | 3.15 V to 3.45 V Positive Power Supply for the Synchronization Circuitry. Short this pin to the other pins in 3.3 V power supply group 1.                                                                                                                                                                                                                                                                                                                                |

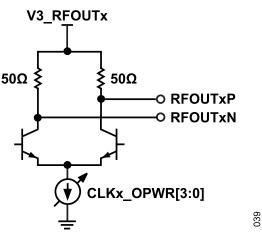

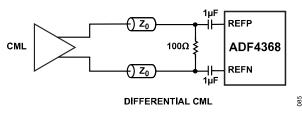

| 42, 43      | REFP, REFN   | Reference Input Signal. This differential input is buffered with a delay matched amplifier (DMA) for well controlled reference to output propagation delays (default mode, REF_SEL = 0). For low slew rate reference input signals, an alternate low noise amplifier (LNA) can be selected via the serial port (REF_SEL = 1). Reference inputs are self-biased and must be AC-coupled with 1 µF capacitors. Reference inputs accept differential or single-ended inputs. |

| 44          | V3_REF       | 3.15 V to 3.45 V Positive Power Supply Pin for the PLL Reference Circuitry. Short this pin to the other pins in 3.3 V power supply group 1.                                                                                                                                                                                                                                                                                                                              |

| 45          | V3_PFD       | 3.15 V to 3.45 V Positive Power Supply Pin for PFD Circuitry. Short this pin to the other pins in 3.3 V power supply group 1.                                                                                                                                                                                                                                                                                                                                            |

| 46          | V5_CP        | 4.75 V to 5.25 V Positive Power Supply Pin for Charge Pump Circuitry. Isolate this pin from the V5_VCO supply plane.                                                                                                                                                                                                                                                                                                                                                     |

| 47          | CP           | Charge Pump Output. This bidirectional current output is normally connected to the external loop filter.                                                                                                                                                                                                                                                                                                                                                                 |

| Exposed Pad | EP           | Exposed Pad. The LGA has an exposed paddle that must be connected to GND (Negative power supply). The exposed pad must be soldered directly to the PCB land. The PCB land pattern must have multiple thermal vias to the ground plane for both low ground inductance and also low thermal resistance.                                                                                                                                                                    |

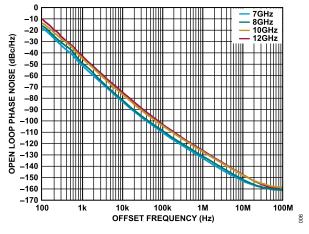

Figure 6. Open Loop VCO Phase Noise vs. Offset Frequency at Various Frequencies

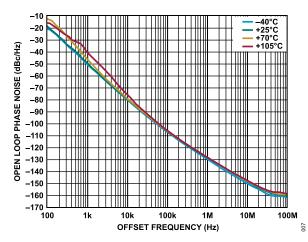

Figure 7. 12 GHz Open Loop VCO Phase Noise vs. Offset Frequency at Various Temperatures

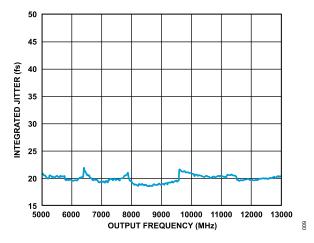

Figure 8. 1 kHz to 100 MHz Integrated Jitter in Fractional Mode  $f_{PFD}$  = 250 MHz

Figure 9. 1 kHz to 100 MHz Integrated Jitter in Integer Mode  $f_{PFD}$  = 500 MHz

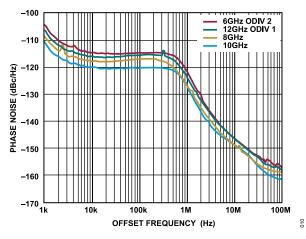

Figure 10. Close Loop Phase Noise at Various Frequencies

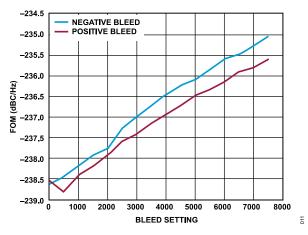

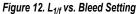

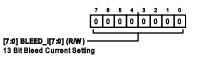

Figure 11. L<sub>NORM-INT</sub> vs. Bleed Setting

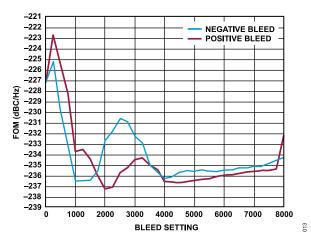

Figure 13.  $L_{NORM-FRC}$ ,  $f_{REF}$  = 500 MHz,  $f_{PFD}$  = 250 MHz,  $RF_{Out}$  = 12,001 MHz vs. Bleed Setting

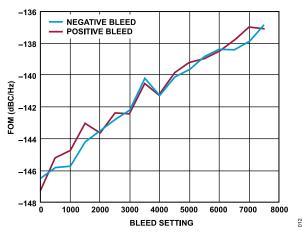

Figure 14. L<sub>NORM-FRC</sub> vs. Bleed Setting

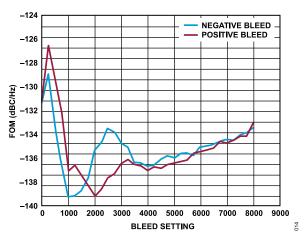

Figure 15. Worst Case IBS measured at 5 kHz, 50 kHz, 200 kHz, 300 kHz, 400 kHz, 960 kHz, 10 MHz offsets, f<sub>PFD</sub> = 245.76 MHz

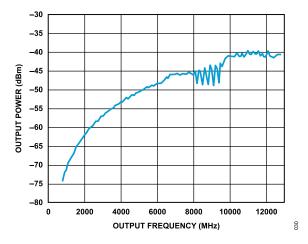

Figure 17. De-Embedded Single-Ended Output Power at Various Output Power Settings

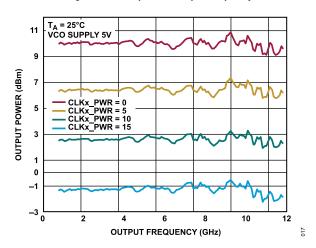

Figure 18. De-Embedded Single-Ended Output Power vs. Output Frequency over Temperature and Supply

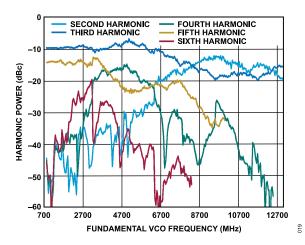

Figure 19. Output Harmonics vs. VCO Frequency

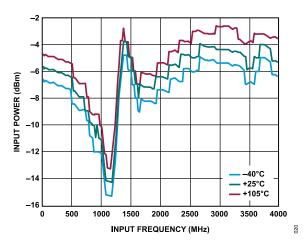

Figure 20. Minimum Input Signal for REF\_OK = 1 for DMA Buffer

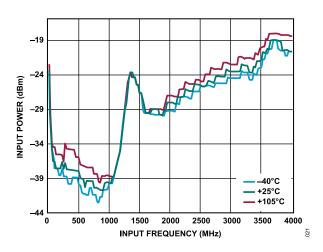

Figure 21. LNA Reference Input Sensitivity vs. Temperature

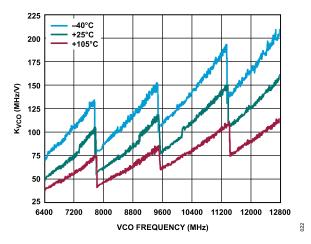

Figure 22. K<sub>VCO</sub> vs. VCO Frequency at Various Temperatures

Figure 23. K<sub>VCO</sub> Sensitivity Percentage vs. VCO Frequency at Various Temperatures

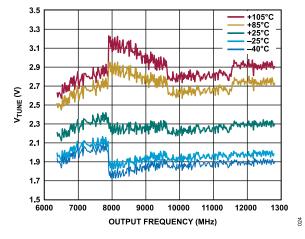

Figure 24. V<sub>TUNE</sub> vs. Output Frequency when Part Locked at 25°C

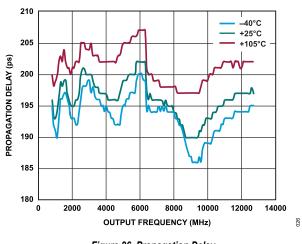

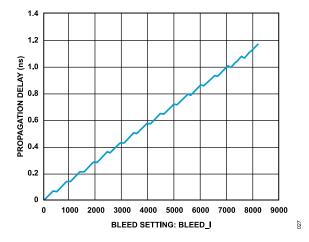

Figure 26. Propagation Delay

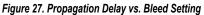

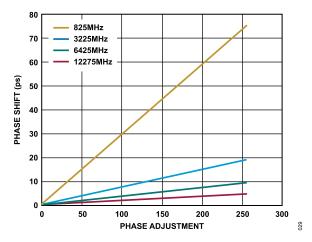

Figure 28. Phase Shift vs. Phase Adjustment, RF<sub>Out</sub> = 12,775 MHz at Various Temperatures

Figure 29. Phase Shift vs. Phase Adjustment at Various Frequencies

Figure 30. Output Power When Buffer Is Powered Down (PD\_CLKOUTx = 1)

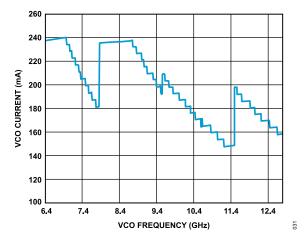

Figure 31. VCO Current vs. VCO Frequency

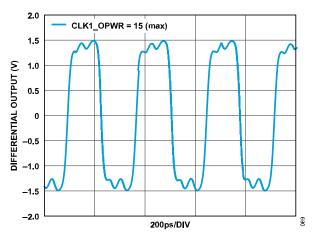

Figure 32. Differential Output at 3 GHz

#### INTRODUCTION

A PLL is a complex feedback system that may conceptually be considered a frequency multiplier. The system multiplies the frequency input at REFP and REFN and outputs a higher frequency at RFOUT1P, RFOUT2P, RFOUT1N, and RFOUT2N. The PFD, charge pump, output divider, feedback divider, VCO, and external loop filter forms a feedback loop to accurately control the output frequency (see Figure 33). The reference divider or reference doubler is used to set the frequency resolution.

Figure 33. PLL Loop Diagram

#### **OUTPUT FREQUENCY**

When the loop is locked, the  $f_{VCO}$  (in Hz) produced at the output of the VCO is determined by the reference frequency ( $f_{REF}$ ) and the O, R, and N values given by the following equation.

$$f_{VCO} = f_{REF} \times \frac{D \times N \times O}{R} \tag{1}$$

Where N is given by:

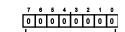

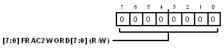

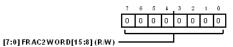

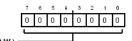

$$N = N_{INT} + \frac{FRAC \, 1WORD + \frac{FRAC \, 2WORD}{MOD \, 2WORD}}{MOD \, 1WORD}$$

(2)

Here, the PFD frequency (f<sub>PFD</sub>) produced is given by:

$$f_{PFD} = \frac{f_{REF} \times D}{R} \tag{3}$$

f<sub>VCO</sub> may be alternatively expressed as:

$$f_{VCO} = f_{PFD} \times N \times O \tag{4}$$

The output frequency, f<sub>RFOUT</sub>, produced at the output of the output divider is given by:

$$f_{RFOUT} = \frac{f_{VCO}}{O} \tag{5}$$

### **CIRCUIT DESCRIPTION**

#### **Reference Input Buffer**

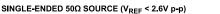

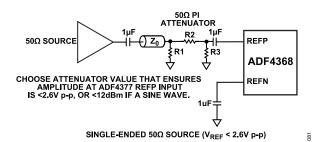

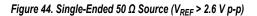

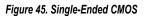

The reference frequency of the PLL is applied differentially on the REFP and REFN pin. These high impedance inputs are self-biased and must be AC-coupled with 1  $\mu$ F capacitors (for a simplified schematic, see Figure 34). Alternatively, the inputs may be used as single-ended by applying the reference frequency at REFP and bypassing REFN to GND with a 1  $\mu$ F capacitor.

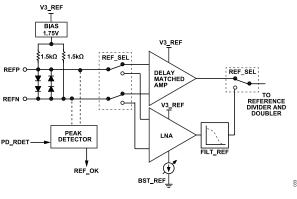

Figure 34. Reference Input Stage

A high quality signal must be applied to the REFP and REFN inputs because they provide the frequency reference to the entire PLL. To achieve the in-band phase noise performance of the device, apply a continuous wave signal or a square wave with a slew rate of at least 1000 V/µs. For more information on reference input signal requirements and interfacing, see the Applications Information section.

When the REF\_SEL bit is set to 0, the DMA buffer is selected. The DMA is optimized for high slew rate signals, such as square waves or higher frequency and higher amplitude sine waves. The DMA has a controlled propagation delay from the reference input to clock output, which eases time zero and over temperature multichip clock alignment.

When the REF\_SEL bit is set to 1, the LNA is selected. The LNA is optimized for low slew rate signals, such as lower frequency or lower amplitude sine waves.

The REF\_SEL bit must be set correctly to optimize the in-band phase noise performance and propagation delay. For recommend-ed settings, see Table 7.

#### Table 7. REF\_SEL Programming

| REF_SEL | Sine Wave Slew Rate (V/µs) | Square Wave    | Optimized t <sub>PD</sub> |

|---------|----------------------------|----------------|---------------------------|

| 0       | ≥1000                      | Preferred      | Yes                       |

| 1       | <1000                      | Not applicable | Not applicable            |

To calculate the slew rate of sine wave:

Slew Rate =  $2 \times \pi \times f \times V$

Where:

f = sine wave frequency

V = sine wave amplitude (in  $V_{PK}$ )

The FILT\_REF bit controls the low-pass filter of the reference input LNA and must be set for sine wave signals based on  $f_{REF}$  to limit the wideband noise of the reference. The FILT\_REF bit must be set correctly to reach the L<sub>NORM</sub> normalized in-band phase noise floor. For recommended settings, see Table 8. Square wave inputs have FILT\_REF set to 0.

(6)

#### Table 8. FILT\_REF Programming

| FILT_REF | Sine Wave f <sub>REF</sub> | Square Wave f <sub>REF</sub> |

|----------|----------------------------|------------------------------|

| 0        | ≥ 20 MHz                   | All f <sub>REF</sub>         |

| 1        | < 20 MHz                   | Not applicable               |

The BST\_REF bit must be set based on the input signal level to prevent the LNA reference input buffer from saturating. The BST\_REF programming is the same whether the input is a sine wave or a square wave. For recommended settings, see Table 9 and for programming examples, see the Applications Information section.

#### Table 9. BST\_REF Programming

| BST_REF | Sine Wave f <sub>REF</sub> |

|---------|----------------------------|

| 0       | ≥ 1.6 V <sub>PP</sub>      |

| 1       | < 1.6 V <sub>PP</sub>      |

#### **Reference Peak Detector**

A reference input peak detection circuit is provided on the REFP and REFN inputs to detect the presence of a reference signal and provides the REF\_OK status flag available through serial port register REG0058. The circuit has hysteresis to prevent the REF\_OK flag from chattering at the detection threshold.

The peak detector approximates an RMS detector. Therefore, sine and square wave inputs give different detection thresholds by a factor of  $4/\pi$ . For REF\_OK detection values, see Table 10.

| Table 10. REF OI | K Status Output vs. | REF INPUT |

|------------------|---------------------|-----------|

|------------------|---------------------|-----------|

| REF_OK | Sine Wave f <sub>REF</sub> | Square Wave f <sub>REF</sub> |

|--------|----------------------------|------------------------------|

| 1      | ≥ 200 mV <sub>PP</sub>     | ≥ 155 mV <sub>PP</sub>       |

| 0      | < 180 mV <sub>PP</sub>     | < 140 mV <sub>PP</sub>       |

### Reference Divider (R) and Doubler (D)

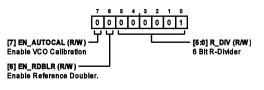

When the EN\_RDBLR bit is set to 1, a frequency multiplier is used to double the frequency driven to the reference divider. A 6-bit divider, R\_DIV, in series with the reference doubler is used to reduce the frequency seen at the PFD. The reference divide ratio, R, may be set to any integer from 1 to 63. Use the R\_DIV bits found in REG0020 to directly program the R divide ratio. For the relationship between R, D, and the f<sub>REF</sub>, f<sub>PFD</sub>, f<sub>VCO</sub>, and f<sub>OUT</sub> frequencies, see the Output Frequency section.

### **Phase/Frequency Detector (PFD)**

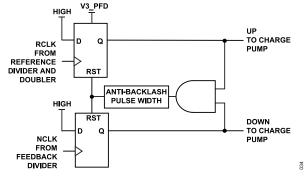

The phase/frequency detector (PFD), with the charge pump, produces source and sink current pulses proportional to the phase difference between the outputs of the reference divider or reference doubler and the feedback divider. This action provides the necessary feedback to phase lock the loop, forcing a phase alignment at the inputs of the PFD. For a simplified schematic of the PFD, see Figure 35.

Figure 35. Simplified PFD Schematic

### **Charge Pump**

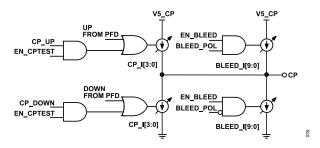

The charge pump, controlled by the PFD, forces sink (down) or source (up) current pulses onto the CP pin, which must be connected to an appropriate loop filter. For a simplified schematic of the charge pump, see Figure 36.

Figure 36. Simplified Charge Pump Schematic

The output current magnitude ( $I_{CP}$ ) may be set from 0.79 mA to 11.1 mA using the CP\_I bits found in REG001F. A larger  $I_{CP}$  can result in lower in-band noise due to the lower impedance of the loop filter components, and a smaller  $I_{CP}$  can result in better spurious performance. For programming specifics, see Table 11, and for information on designing a loop filter, see the Applications Information section.

| Table | 11. | СР | Program | nming |

|-------|-----|----|---------|-------|

|-------|-----|----|---------|-------|

| CP_I | I <sub>CP</sub> |

|------|-----------------|

| 0    | 0.79 mA         |

| 1    | 0.99 mA         |

| 2    | 1.19 mA         |

| 3    | 1.38 mA         |

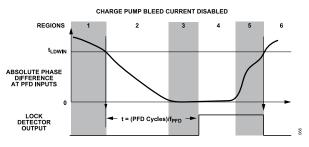

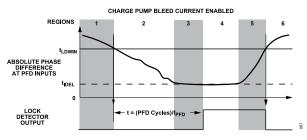

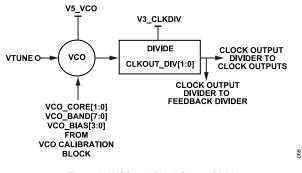

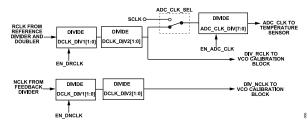

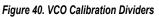

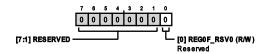

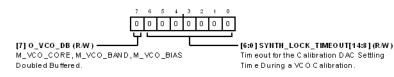

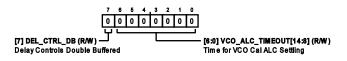

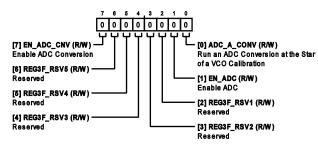

| 4    | 1.59 mA         |