# Microwave Wideband Synthesizer with Integrated VCO

**Data Sheet**

# ADF5610

#### FEATURES

RF output frequency range: 57 MHz to 14,600 MHz RFOUT: 7300 MHz to 14,600 MHz PDIV/NDIV: 57 MHz to 14,600 MHz Fractional-N synthesizer and Integer N synthesizer modes 24-bit fractional modulus Exact frequency mode for 0 Hz frequency error Typical PFD spurious: <-105 dBc Integrated rms jitter: <40 fs Normalized inband phase noise floor FOM High current mode: -232 dBc/Hz (integer) and -229 dBc/Hz (fractional) Normal mode: -229 dBc/Hz (integer) and -226 dBc/Hz (fractional) Maintains frequency lock over -40°C to +85°C (lock and leave) Low phase noise VCO -115 dBc/Hz typical at 100 kHz (7.3 GHz) -114 dBc/Hz typical at 100 kHz (10 GHz) -109 dBc/Hz typical at 100 kHz (14.6 GHz) **RFOUT power: 5 dBm** Programmable divide by 1, 2, 4, 8, 16, 32, 64, or 128 output Programmable output power level Typical power dissipation: 815 mW Programmable low current and power dissipation: <700 mW Fast frequency hopping (autocalibration enabled): <40 µs 48-terminal, 7 mm × 7 mm LGA package: 49 mm<sup>2</sup>

#### APPLICATIONS

Military and defense Test equipment Clock generation Wireless infrastructure Satellite and very small aperture terminal (VSAT) Microwave radio

#### **GENERAL DESCRIPTION**

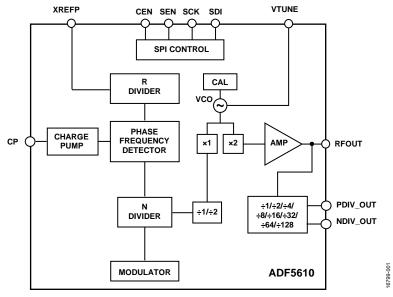

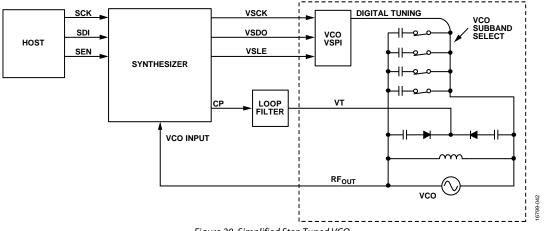

The ADF5610 allows implementation of fractional-N or Integer N phase-locked loop (PLL) frequency synthesizers when used with an external loop filter and an external reference source. The wideband microwave voltage controlled oscillator (VCO) design permits frequency operation from 7300 MHz to 14600 MHz at a single radio frequency (RF) output. A series of frequency dividers with a differential frequency output allows operation from 57 MHz to 14600 MHz. Analog and digital power supplies for the PLL circuitry range from 3.1 V to 3.5 V, and the VCO supplies are between 4.75 V and 5.25 V. The charge pump supply voltage can be extended up to 3.6 V for improved frequency band overlap and extended upper frequency range.

The ADF5610 has an integrated VCO with a fundamental frequency of 3650 MHz to 7300 MHz. These frequencies are internally doubled and routed to the RFOUT pin. An additional differential output allows the doubled VCO frequency to be divided by 1, 2, 4, 8, 16, 32, 64, or 128, allowing the user to generate RF output frequencies as low as 57 MHz. A simple 3-wire serial port interface (SPI) provides control of all on-chip registers. To conserve power, this divider block can be disabled when not needed through the SPI interface. Likewise, the output power for both the single-ended output and the differential output are programmable via the VCO register settings. The ADF5610 also contains various power-down modes for the VCO circuitry and PLL circuitry.

The integrated phase detector (PD) and delta-sigma ( $\Delta$ - $\Sigma$ ) modulator, capable of operating at up to 100 MHz, permit wide loop bandwidths and fast frequency tuning with a typical spurious level of -100 dBc.

With phase noise levels from -115 dBc/Hz at 7.3 GHz to -109 dBc/Hz at 14.6 GHz, the ADF5610 is equipped to minimize blocker effects, and to improve receiver sensitivity and transmitter spectral purity. The low phase noise floor eliminates any contribution to modulator and mixer noise floor in transmitter applications.

The ADF5610 is a PLL with integrated VCO. The device features an innovative programmable performance technology that enables the ADF5610 to tailor current consumption and corresponding noise performance to individual applications by selecting either a low current consumption mode or a high performance mode for improved phase noise performance.

Additional features of the ADF5610 include approximately 3 dB of RFOUT gain control in 1.5 dB steps and 5 dB of control on the differential port in approximately 2.5 dB steps. Finally, the  $\Delta$ - $\Sigma$  modulator with exact frequency mode enables users to generate output frequencies with 0 Hz frequency error.

Rev. 0

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2019 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

### TABLE OF CONTENTS

| Features 1                                     |

|------------------------------------------------|

| Applications1                                  |

| General Description                            |

| Revision History 2                             |

| Functional Block Diagram 3                     |

| Specifications                                 |

| Timing Specifications9                         |

| Absolute Maximum Ratings10                     |

| Thermal Resistance                             |

| ESD Caution10                                  |

| Pin Configuration and Function Descriptions11  |

| Typical Performance Characteristics            |

| Theory of Operation16                          |

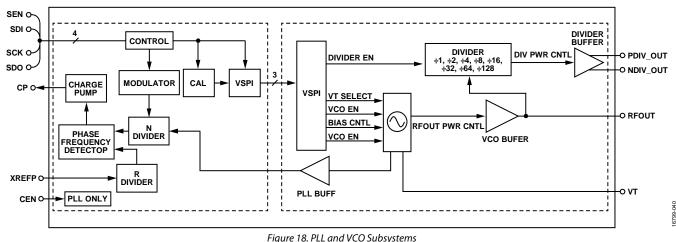

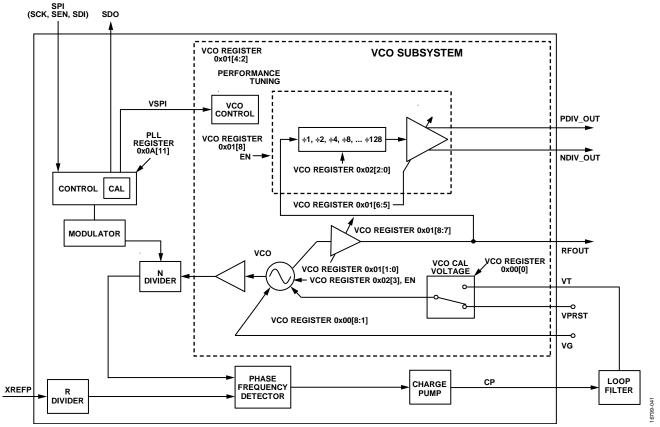

| PLL Subsystem Overview16                       |

| VCO Subsystem Overview16                       |

| SPI Configuration of PLL and VCO Subsystems 17 |

| VCO Subsystem 18                               |

| PLL Subsystem                                  |

| Soft Reset and Power-On Reset 32               |

| Power-Down Mode                                |

| General-Purpose Output (GPO)                   |

| Chip Identification                            |

| Power Supply                                   |

| Programmable Performance Technology            |

| Loop Filter and Frequency Changes              |

| Mute Mode                                      |

| Serial Port Interface                          |

| SPI Modes of Operation                         |

| Register 0x00 Modes35                          |

| Serial Port Mode Decision After Power-On Reset |

| Serial Port Legacy Mode35                      |

| Serial Port Legacy Mode: Single PLL            |

| Serial Port Open Mode                          |

| Legacy Mode: Serial Port Write Operation       |

### ID Register, Reset Strobe Register, and Open Mode Read Reference Divider (RDIV) Register ...... 39 Frequency Register, Integer Part ...... 40 Frequency Register, Fractional Part...... 40 VCO SPI Register ...... 40 Analog Enable (EN) Register...... 42 Charge Pump Register ...... 43 Phase Detector (PD) Register ...... 44 Exact Frequency Mode Register...... 44 General-Purpose, SPI, and Reference Divider (GPO\_SPI\_RDIV) Register ..... 44 VCO Tune Register ...... 45 Successive Approximation Register ...... 46 General-Purpose 2 Register ...... 46 Built In Self Test (BIST) Register...... 46 VCO Subsystem Register Map..... 47 VCO Power Control Register ...... 47 VCO Differential Output Divider Register...... 48 Applications Information ...... 50 Evaluation Printed Circuit Board (PCB) ...... 50 Evaluation Kit Contents ...... 50

#### **REVISION HISTORY**

2/2019—Revision 0: Initial Version

## FUNCTIONAL BLOCK DIAGRAM

Figure 1.

### **SPECIFICATIONS**

Analog supply (AVDD) = digital power supply (DVDD) =  $3.3 V \pm 5\%$ , power supply for charge pump digital section (VDDLS), power supply for charge pump (VPPCP), reference path supply (RVDD), phase detector supply (VCCPD), prescaler supply (VCCPS), power supply for PLL RF section (VCCHF) =  $3.3 V \pm 5\%$ , bias for VCO digital logic, SPI buffer, and input buffer to PLL (VDD1), reference voltage supply (VDD2), differential output divider supply (VDD3) =  $3.3 V \pm 5\%$ , VCO supply (VCOVCC) =  $5.0 V \pm 5\%$ , ground (GND) = 0 V, minimum and maximum specifications across the temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Table 1.

| Parameter                                       | Symbol | Test Conditions/Comments                                                                                                                               | Min  | Тур | Max    | Unit |

|-------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------|------|

| RF OUTPUT                                       |        |                                                                                                                                                        |      |     |        |      |

| CHARACTERISTICS                                 |        |                                                                                                                                                        |      |     |        |      |

| RFOUT Frequency                                 |        |                                                                                                                                                        | 7300 |     | 14,600 | MHz  |

| VCO Frequency at PLL<br>Input                   |        |                                                                                                                                                        | 3650 |     | 7300   | MHz  |

| Frequency Range for<br>PDIV_OUT and<br>NDIV_OUT |        |                                                                                                                                                        | 57   |     | 14,600 | MHz  |

| OUTPUT POWER                                    |        |                                                                                                                                                        |      |     |        |      |

| RFOUT Power                                     |        | Across all frequencies, high performance<br>mode (VCO Register 0x01, Bits[4:2] = 0x3),<br>maximum gain setting (VCO Register 0x01,<br>Bits[1:0] = 0x3) | 0    | 5   | 10     | dBm  |

| RFOUT Power Control<br>Range                    |        | 1 dB steps                                                                                                                                             |      | 4   |        | dB   |

| RFOUT Power Variation vs.<br>Temperature        |        |                                                                                                                                                        |      | ±1  |        | dBm  |

| RFOUT Power Variation vs.<br>Frequency          |        |                                                                                                                                                        |      | ±2  |        | dBm  |

| PDIV_OUT and NDIV_OUT<br>Power                  |        | Maximum gain setting (VCO Register 0x01,<br>Bits[6:5] = 0x3), single-ended                                                                             | -6   | 0   | 6      | dBm  |

|                                                 |        | Divide by 2 to divide by 128                                                                                                                           |      | 2   |        | dBm  |

| PDIV_OUT and NDIV_OUT<br>Control Range          |        | Three settings, bypass mode (divide by 1)                                                                                                              |      | 6   |        | dB   |

| HARMONICS (RFOUT)                               |        |                                                                                                                                                        |      |     |        |      |

| 1/2 Harmonic                                    |        | 3650 MHz to 7300 MHz                                                                                                                                   |      | -20 |        | dBc  |

| 1.5 Harmonic                                    |        |                                                                                                                                                        |      | -30 |        | dBc  |

| Second Harmonic                                 |        |                                                                                                                                                        |      | -30 |        | dBc  |

| 2.5 Harmonic                                    |        |                                                                                                                                                        |      | -35 |        | dBc  |

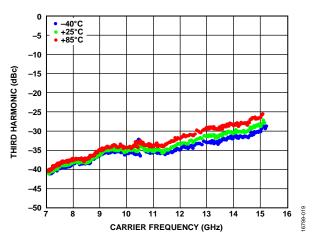

| Third Harmonic                                  |        |                                                                                                                                                        |      | -30 |        | dBc  |

| HARMONICS (PDIV_OUT and NDIV_OUT)               |        |                                                                                                                                                        |      |     |        |      |

| Single-Ended                                    |        |                                                                                                                                                        |      |     |        |      |

| 1/2 Harmonic                                    |        | Fundamental feedthrough                                                                                                                                |      |     |        |      |

|                                                 |        | N = divide by 1                                                                                                                                        |      | -20 |        | dBc  |

|                                                 |        | N = divide by 2                                                                                                                                        | 1    | -60 |        | dBc  |

| Second Harmonic                                 |        | Push/push feedthrough                                                                                                                                  | 1    |     |        |      |

|                                                 |        | N = divide by 1                                                                                                                                        | 1    | -26 |        | dBc  |

|                                                 |        | N = divide by 2                                                                                                                                        | 1    | -24 |        | dBc  |

| Third Harmonic                                  |        | N = divide by 1                                                                                                                                        | 1    | -24 |        | dBc  |

|                                                 |        | N = divide by 2                                                                                                                                        | 1    | -17 |        | dBc  |

| Differential                                    |        |                                                                                                                                                        | 1    |     |        |      |

| 1/2 Harmonic                                    |        | Fundamental feedthrough ( $N = 1$ )                                                                                                                    |      | -20 |        | dBc  |

|                                                 |        | Push/push feedthrough (N = 2)                                                                                                                          | 1    | -52 |        | dBc  |

| Second Harmonic                                 |        | N = divide by 1                                                                                                                                        | 1    | -31 |        | dBc  |

|                                                 |        | N = divide by 2                                                                                                                                        | 1    | -27 |        | dBc  |

## **Data Sheet**

# ADF5610

| Parameter                                    | Symbol | Test Conditions/Comments                                                                                       | Min  | Тур  | Мах     | Unit                                    |

|----------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------|------|------|---------|-----------------------------------------|

| Third Harmonic                               |        | N = divide by 1                                                                                                |      | -30  |         | dBc                                     |

|                                              |        | N = divide by 2                                                                                                |      | -16  |         | dBc                                     |

| VCO Supply Pushing<br>(VDD1) <sup>1</sup>    |        | RFOUT (VT = 1.65 V)                                                                                            |      | 67   |         | MHz/V                                   |

| VCO Supply Pushing<br>(VCOVCC) <sup>1</sup>  |        | RFOUT (VT = 1.65 V)                                                                                            |      | 1.0  |         | MHz/V                                   |

| VCO Load Pulling (2.0:1) <sup>2</sup>        |        | RFOUT (VT = $1.65$ V)                                                                                          |      | 1.0  |         | MHz p-p                                 |

| VCO Frequency Drift                          |        | RFOUT (VT = 1.65 V)                                                                                            |      |      |         |                                         |

|                                              |        | Operating at 7.3 GHz                                                                                           |      | 0.5  |         | MHz/°C                                  |

|                                              |        | Operating at 14.6 GHz                                                                                          |      | 1.02 |         | MHz/°C                                  |

| PLL RF INPUT PRESCALER                       |        |                                                                                                                |      |      |         |                                         |

| Input Frequency Range                        |        | Approximate drive level = $-10 \text{ dBm}$                                                                    | 57   |      | 4000    | MHz                                     |

| PLL RF DIVIDER<br>CHARACTERISTICS            |        |                                                                                                                |      |      |         |                                         |

| 19-Bit N Divider Range<br>(Integer N)        |        | $Maximum = 2^{19} - 1$                                                                                         | 16   |      | 524,287 |                                         |

| 19-Bit N Divider Range                       |        | Fractional nominal divide ratio varies (±4)                                                                    | 20   |      | 524,283 |                                         |

| (Fractional-N)                               |        | dynamically maximum                                                                                            | 20   |      | 524,205 |                                         |

| REFERENCE INPUT                              |        |                                                                                                                |      |      |         |                                         |

| CHARACTERISTICS                              |        |                                                                                                                |      |      |         |                                         |

| Maximum XREFP Input                          |        |                                                                                                                | DC   | 50   | 350     | MHz                                     |

| Frequency                                    |        |                                                                                                                |      |      |         |                                         |

| XREFP Input Level                            |        | AC-coupled <sup>3</sup>                                                                                        | -6   |      | +12     | dBm                                     |

| XREFP Input Capacitance                      |        |                                                                                                                |      |      | 5       | рF                                      |

| 14-Bit R Divider Range                       |        |                                                                                                                | 1    |      | 16,383  |                                         |

| PHASE DETECTOR (PD) <sup>4</sup>             |        |                                                                                                                |      |      |         |                                         |

| PD Frequency Fractional<br>Mode <sup>5</sup> |        | Fractional Mode B                                                                                              | DC   |      | 100     | MHz                                     |

| PD Frequency Integer<br>Mode                 |        |                                                                                                                | DC   |      | 100     | MHz                                     |

| CHARGE PUMP                                  |        |                                                                                                                |      |      |         |                                         |

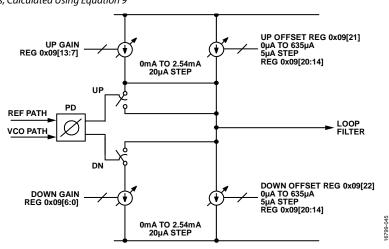

| Output Current                               |        |                                                                                                                | 0.02 |      | 2.54    | mA                                      |

| Charge Pump Gain Step                        |        |                                                                                                                |      | 20   |         | μA                                      |

| Size                                         |        |                                                                                                                |      |      |         | 1                                       |

| LOGIC INPUTS                                 |        |                                                                                                                |      |      |         |                                         |

| Logic Switching Threshold<br>(Vsw)           |        | Input high voltage (V <sub>IH</sub> ) and input low voltage (V <sub>IL</sub> ) within 50 mV of V <sub>SW</sub> | 40   | 50   | 60      | % of<br>DVDD                            |

| SDO LOGIC OUTPUT                             |        |                                                                                                                |      |      |         |                                         |

| Output High Voltage                          |        |                                                                                                                |      |      |         |                                         |

|                                              |        |                                                                                                                |      |      |         |                                         |

|                                              |        | Complementary metal-oxide semiconductor<br>(CMOS) 3.3 V mode (Register 0x0F, Bits[9:8] =<br>00b)               | -0.2 |      |         | V                                       |

|                                              |        | Open-drain mode (Register 0x0F, Bits[9:8] = 01b) <sup>6</sup>                                                  |      |      | 3.3     | v                                       |

| Output Low Voltage (V <sub>OL</sub> )        |        | CMOS mode (Register 0x0F, Bits[9:8] = 00b)                                                                     |      |      | 0.1     | v                                       |

|                                              |        | Open-drain mode (Register 0x0F, Bits[9:8] = $01b$ ) <sup>7</sup>                                               |      | 0.4  | 0.1     | , i i i i i i i i i i i i i i i i i i i |

| Serial Clock (SCK)<br>Frequency Rate         |        | CMOS mode (Register 0x0F, Bits[9:8] = 00b) <sup>8</sup>                                                        |      | 6    | 50      | MHz                                     |

| riequency hate                               |        | Opon-drain mode (Persister 0x05[0.9] - 016)9                                                                   |      | 5    | 10      |                                         |

| Conscitive Land                              |        | Open-drain mode (Register $0x0F[9:8] = 01b)^9$                                                                 |      | 5    | 10      | MHz                                     |

| Capacitive Load                              |        | CMOS mode (Register 0x0F, Bits[9:8] = 00b)                                                                     |      | 10   | 20      | pF                                      |

|                                              |        | Open-drain mode (Register 0x0F, Bits[9:8] = 01b) <sup>10</sup>                                                 |      |      | 10      | pF                                      |

| Load Current                                 |        | CMOS mode (Register $0x0F$ , Bits[9:8] = $00b$ ) <sup>11</sup>                                                 | 1    |      | 3.6     | mA                                      |

| Parameter                                                  | Symbol | Test Conditions/Comments                                                    | Min  | Тур                                | Max       | Unit |

|------------------------------------------------------------|--------|-----------------------------------------------------------------------------|------|------------------------------------|-----------|------|

|                                                            |        | Open-drain mode (Register 0x0F, Bits[9:8] = 01b) <sup>12</sup>              |      |                                    | 7.2       | mA   |

| Output Resistance When<br>Driver Is Low (R <sub>ON</sub> ) |        | Open-drain mode (Register 0x0F, Bits[9:8] = 01b)                            |      | 100                                | 200       | Ω    |

| Pull-Up Resistor (R <sub>UP</sub> )                        |        | Open-drain mode (Register 0x0F, Bits[9:8] = 01b)                            | 500  | 1000                               |           | Ω    |

| Rise Time                                                  |        | CMOS mode (Register 0x0F, Bits[9:8] = $00b$ ) <sup>13</sup>                 |      | $0.5 + 0.3 \times C_{LOAD}$        | 7         | ns   |

| Fall Time                                                  |        | CMOS mode (Register 0x0F, Bits[9:8] = $00b$ ) <sup>13</sup>                 |      | $1.5 + 0.2 \times C_{LOAD}$        | 10        | ns   |

| SCK to SDO Turnaround<br>Time                              |        | CMOS mode (Register 0x0F, Bits[9:8] = $00b$ ) <sup>13</sup>                 |      | $0.9 + 0.1 \times C_{\text{LOAD}}$ | 12        | ns   |

| RF Divider Input Below<br>4 GHz, Integer Mode              |        | 19-bit, all values <sup>14</sup>                                            | 16   |                                    | 524,287   |      |

| RF Divider Input Above<br>4 GHz, Integer Mode              |        | 19-bit, even values only                                                    | 32   |                                    | 1,048,574 |      |

| RF Divider Input Below<br>4 GHz, Fractional Mode           |        | 19-bit, all values                                                          | 20   |                                    | 524,283   |      |

| RF Divider Input Above<br>4 GHz, Fractional Mode           |        | 19-bit, even values only                                                    | 40   |                                    | 1,048,566 |      |

| POWER SUPPLY VOLTAGES                                      |        |                                                                             |      |                                    |           |      |

| 3.3 V Supplies                                             |        | AVDD, VCCHF, VCCPS, VCCPD, RVDD, DVDD, VPPCP, VDDLS, VDD1, VDD2, VDD3       | 3.1  | 3.3                                | 3.5       | V    |

| 5.0 V Supplies                                             |        | VCOVCC                                                                      | 4.75 | 5.0                                | 5.25      | V    |

| POWER DISSIPATION                                          |        |                                                                             |      |                                    |           |      |

| Typical Power Dissipation                                  |        |                                                                             |      | 815                                |           | mW   |

| Programmable Low<br>Current and Power<br>Dissipation       |        |                                                                             |      | <700                               |           | mW   |

| POWER SUPPLY CURRENTS                                      |        |                                                                             |      |                                    |           |      |

| AVDD                                                       |        | 3.3 V                                                                       |      | 1.6                                |           | mA   |

| RVDD                                                       |        | 3.3 V                                                                       |      | 6                                  |           | mA   |

| VCCHF                                                      |        | 3.3 V                                                                       |      | 4                                  |           | mA   |

| VCCPS                                                      |        | 3.3 V                                                                       |      | 29.7                               |           | mA   |

| VCCPD                                                      |        | 3.3 V                                                                       |      | 1.0                                |           | mA   |

| DVDD                                                       |        | 3.3 V                                                                       |      | 11.9                               |           | mA   |

| VPPCP <sup>15</sup>                                        |        | 3.3 V                                                                       |      | 5.6                                |           | mA   |

| VDDLS <sup>15</sup>                                        |        | 3.3 V                                                                       |      | 0.6                                |           | mA   |

| VDD1                                                       |        | 3.3 V                                                                       |      | 3                                  |           | mA   |

| VDD2                                                       |        | 3.3 V                                                                       |      | 1                                  |           | mA   |

| VDD3                                                       |        | Divide by 1                                                                 |      | 62                                 |           | mA   |

|                                                            |        | Divide by 2                                                                 |      | 73.7                               |           | mA   |

|                                                            |        | Divide by 4                                                                 |      | 78.8                               |           | mA   |

|                                                            |        | Divide by 8                                                                 |      | 82.4                               |           | mA   |

|                                                            |        | Divide by 16                                                                |      | 85.9                               |           | mA   |

|                                                            |        | Divide by 32                                                                |      | 88.1                               |           | mA   |

|                                                            |        | Divide by 64                                                                |      | 90                                 |           | mA   |

|                                                            |        | Divide by 128                                                               |      | 92                                 |           | mA   |

| VCOVCC                                                     |        | 5.0 V                                                                       |      | 110                                |           | mA   |

| Power-Down                                                 |        |                                                                             |      |                                    |           |      |

| PLL <sup>16</sup>                                          |        | Power down via SPI Register 0x01, Bit 0 = 0<br>and Register 0x01, Bit 1 = 0 |      | 100                                |           | μΑ   |

| VCOVCC <sup>17</sup>                                       |        | Power down using VCO Register 0x02,<br>Bit 3 = 1                            |      | 13                                 |           | mA   |

| Divider <sup>17</sup>                                      |        | Power down using VCO Register 0x01,<br>Bit 8 = 0                            |      | 1.5                                |           | mA   |

# Data Sheet

| Parameter                                                                         | Symbol | Test Conditions/Comments                                                                                                                      | Min | Тур І                                                  | Max | Unit  |

|-----------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------|-----|-------|

| POWER-ON RESET                                                                    |        |                                                                                                                                               |     |                                                        |     | T     |

| Typical Reset Voltage on<br>DVDD                                                  |        |                                                                                                                                               |     | 700                                                    |     | mV    |

| Minimum DVDD Voltage<br>for No Reset                                              |        |                                                                                                                                               | 1.5 |                                                        |     | V     |

| Power-On Reset Delay                                                              |        |                                                                                                                                               |     | 250                                                    |     | μs    |

| VCO OPEN-LOOP PHASE<br>NOISE                                                      |        |                                                                                                                                               |     |                                                        |     |       |

| RFOUT at 7.3 GHz                                                                  |        |                                                                                                                                               |     |                                                        |     |       |

| 10 kHz Offset                                                                     |        |                                                                                                                                               |     | -92                                                    |     | dBc/H |

| 100 kHz Offset                                                                    |        |                                                                                                                                               |     | -115                                                   |     | dBc/H |

| 1 MHz Offset                                                                      |        |                                                                                                                                               |     | -135                                                   |     | dBc/H |

| 10 MHz Offset                                                                     |        |                                                                                                                                               |     | -155                                                   |     | dBc/H |

| 100 MHz Offset                                                                    |        |                                                                                                                                               |     | -168                                                   |     | dBc/H |

| RFOUT at 10 GHz                                                                   |        |                                                                                                                                               |     |                                                        |     |       |

| 10 kHz Offset                                                                     |        |                                                                                                                                               |     | -92                                                    |     | dBc/H |

| 100 kHz Offset                                                                    |        |                                                                                                                                               |     | -114                                                   |     | dBc/H |

| 1 MHz Offset                                                                      |        |                                                                                                                                               |     | -135                                                   |     | dBc/H |

| 10 MHz Offset                                                                     |        |                                                                                                                                               |     | -155                                                   |     | dBc/H |

| 100 MHz Offset                                                                    |        |                                                                                                                                               |     | -164                                                   |     | dBc/H |

| RFOUT at 11 GHz                                                                   |        |                                                                                                                                               |     |                                                        |     |       |

| 10 kHz Offset                                                                     |        |                                                                                                                                               |     | -89                                                    |     | dBc/H |

| 100 kHz Offset                                                                    |        |                                                                                                                                               |     | -112                                                   |     | dBc/H |

| 1 MHz Offset                                                                      |        |                                                                                                                                               |     | -132                                                   |     | dBc/H |

| 10 MHz Offset                                                                     |        |                                                                                                                                               |     | -152                                                   |     | dBc/H |

| 100 MHz Offset                                                                    |        |                                                                                                                                               |     | -161                                                   |     | dBc/H |

| RFOUT at 14.6 GHz                                                                 |        |                                                                                                                                               |     |                                                        |     |       |

| 10 kHz Offset                                                                     |        |                                                                                                                                               |     | -87                                                    |     |       |

| 100 kHz Offset                                                                    |        |                                                                                                                                               |     | -109                                                   |     | dBc/H |

| 1 MHz Offset                                                                      |        |                                                                                                                                               |     | -130                                                   |     | dBc/H |

| 10 MHz Offset                                                                     |        |                                                                                                                                               |     | -150                                                   |     | dBc/H |

| 100 MHz Offset                                                                    |        |                                                                                                                                               |     | -163                                                   |     | dBc/H |

| PLL                                                                               |        |                                                                                                                                               |     |                                                        |     |       |

| Phase Noise at 20 kHz<br>Offset, 50 MHz Phase<br>Frequency Detector<br>(PFD) Rate |        | Over process with 3.3 V power supply at 25°C, measured with >200 kHz loop bandwidth                                                           |     |                                                        |     |       |

| Fast Frequency Hopping<br>(Autocalibration<br>Enabled)                            |        |                                                                                                                                               |     | <40                                                    |     | μs    |

| Lock Time                                                                         |        | Depends on loop filter bandwidth, PFD rate,<br>definition of lock (to within ±Hz or ±degrees<br>of settling), and Register 0x0A configuration |     | 100                                                    |     | μs    |

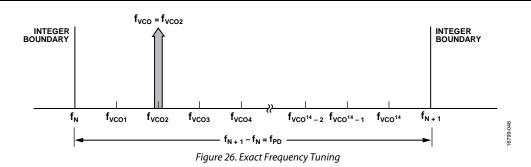

| Frequency Resolution                                                              |        | Depends on PFD rate and VCO output divider setting                                                                                            |     | $f_{PD}/2^{24}$                                        |     | Hz    |

| Fundamental Mode                                                                  |        | 3.5 GHz to 7.5 GHz output, at typical phase detector frequency ( $f_{PD}$ ) of 50 MHz, typical resolution = 3 Hz                              |     |                                                        |     |       |

| Divider Mode                                                                      |        | <3.5 GHz output, resolution depends on VCO output divider setting                                                                             |     | f <sub>PD</sub> /(2 <sup>24</sup> × output<br>divider) |     | Hz    |

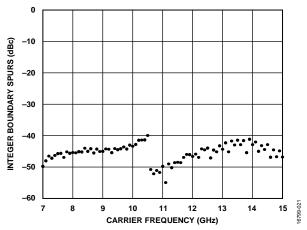

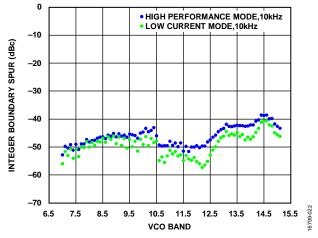

| Integer Boundary Spurs                                                            |        |                                                                                                                                               |     | -45                                                    |     | dBc   |

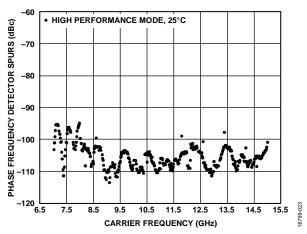

| Phase Detector Spurs                                                              |        |                                                                                                                                               |     | -105                                                   |     | dBc   |

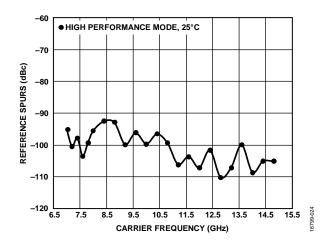

| Reference Spurs                                                                   |        |                                                                                                                                               |     | -100                                                   |     | dBc   |

| Normalized Inband Phase<br>Noise Floor Figure of<br>Merit (FOM)                   |        | Normalized to 1 Hz                                                                                                                            |     |                                                        |     |       |

| Parameter                                                 | Symbol | Test Conditions/Comments                           | Min | Тур  | Max | Unit   |

|-----------------------------------------------------------|--------|----------------------------------------------------|-----|------|-----|--------|

| Floor Integer Mode                                        |        |                                                    |     | -229 |     | dBc/Hz |

| Floor High Current Mode <sup>18</sup><br>Integer Mode     |        |                                                    |     | -232 |     | dBc/Hz |

| Floor Fractional Mode                                     |        |                                                    |     | -226 |     | dBc/Hz |

| Floor High Current Mode<br>Fractional Mode                |        |                                                    |     | -229 |     | dBc/Hz |

| Flicker Noise (Integer<br>Mode and Fractional<br>Mode)    |        |                                                    |     | -268 |     | dBc/Hz |

| Integrated RMS Jitter                                     |        |                                                    |     | <40  |     | fs     |

| VCO CHARACTERISTICS<br>VCO Tuning Sensitivity at<br>RFOUT |        | Measured on RFOUT (VT = 1.65 V)                    |     |      |     |        |

| 7300 MHz                                                  |        |                                                    |     | 101  |     | MHz/V  |

| 9000 MHz                                                  |        |                                                    |     | 80   |     | MHz/V  |

| 11000 MHz                                                 |        |                                                    |     | 128  |     | MHz/V  |

| 13000 MHz                                                 |        |                                                    |     | 109  |     | MHz/V  |

| 14600 MHz                                                 |        |                                                    |     | 96   |     | MHz/V  |

| Tune Port Capacitance                                     |        | VT = 0.5 V dc                                      |     | 175  |     | рF     |

|                                                           |        | VT = 1.65 V dc                                     |     | 154  |     | рF     |

|                                                           |        | VT = 2.8 V dc                                      |     | 135  |     | рF     |

| Autocalibration Delay<br>(Enable or Disable)              |        | VCO Register 0x00, Bit 0 switch time (VT to VPRST) |     | 10   |     | ns     |

| VCO OUTPUT DIVIDER                                        |        |                                                    |     |      |     |        |

| VCO RF Divider Range                                      |        | 1, 2, 4, 6, 8, 128                                 | 1   |      | 128 |        |

| VCO Supply Pushing<br>(VCOVCC) <sup>1</sup>               |        | PDIV_OUT and NDIV_OUT, divide by 1, VT = 1.65 V    |     | 0.7  |     | MHz/V  |

| VCO Supply Pushing<br>(VDD1) <sup>17</sup>                |        | PDIV_OUT and NDIV_OUT, divide by 1, VT = 1.65 V    |     | 67   |     | MHz/V  |

| RETURN LOSS                                               |        |                                                    |     |      |     |        |

| RFOUT                                                     |        |                                                    |     | 5    |     | dB     |

| PDIV_OUT (N > 1)                                          |        |                                                    |     | 14   |     | dB     |

| NDIV_OUT (N > 1)                                          |        |                                                    |     | 14   |     | dB     |

<sup>1</sup> Pushing refers to a change in VCO frequency due to a change in the power supply voltage. To derive pushing at other divide ratios, divide the nominal pushing value by the divide ratio.

<sup>2</sup> Pulling refers to a change in VCO frequency due to a change in the load impedance.

<sup>3</sup> Measured with 100  $\Omega$  external termination. See the Reference Input Stage section for more details.

<sup>4</sup> Slew rate of ≥0.5 ns/V is recommended. See the Reference Input Stage section for more details. Frequency is guaranteed across process voltage and temperature from −40°C to +85°C.

<sup>5</sup> This maximum PD frequency can only be achieved if the minimum N value is respected. For example, in the case of fractional mode, the maximum PD frequency = f<sub>Vco</sub>/20 or 100 MHz, whichever is less.

<sup>6</sup> External 1 kΩ pull-up resistor to 1.8 V.

<sup>7</sup> Limited by the 1 k $\Omega$  pull-up resistor and NMOS R<sub>ON</sub>.

<sup>8</sup> 10 pF load capacitor.

<sup>9</sup> 10 pF load capacitor, 1 kΩ pull-up resistor. In general, open-drain mode can support higher frequencies at the expense of maximum V<sub>oL</sub>. The maximum frequency for a given pull-up resistor and load capacitor is approximately  $1/(10 \times R_{PULL-UP} \times C_{LOAD})$ . For example, a 10 pF load capacitor and 1 kΩ pull-up resistor can support up to 10 MHz, where V<sub>oL</sub> maximum = V<sub>DD</sub> × R<sub>ON</sub>/(1 kΩ + R<sub>ON</sub>) ≈ 164 mV. With a 500 Ω pull-up resistance and a 10 pF load, a 20 MHz maximum frequency is possible, and the maximum V<sub>oL</sub> increases to 300 mV.

<sup>10</sup> 1 kΩ pull-up resistor.

$^{11}$  The minimum resistive load to ground in CMOS mode is 1 k $\!\Omega$ .

<sup>12</sup> The SDO pin does not have short-circuit protection. Do not exceed the maximum current of 7.2 mA under any condition.

$^{13}$  CLOAD is the capacitive load in pF. CLOAD maximum = 20 pF. For example, with a 5 pF capacitive load, the rise time is 0.5 + 0.3 × 5 = 2 ns.

$^{\rm 14}$  Values shown are the product of the prescaler divide ratio  $\times\,N$  counter value.

<sup>15</sup> VCCPD and VDDLS can be operated at 3.6 V maximum to increase band and VCO core overlap and extend the upper end of the frequency range. The typical current is expected to be less than 1.5 mA. Both must be equal. Therefore, if one changes, so must the other. Exceeding 3.6 V results in ESD diodes drawing current.

<sup>16</sup> Reference disconnected.

<sup>17</sup> Some circuits remain on.

<sup>18</sup> High current mode is a register setting that is enabled and works in conjunction with the functional mode in which the device is operating (integer mode or fractional mode).

#### TIMING SPECIFICATIONS

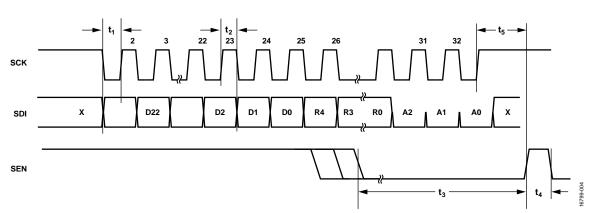

#### SPI Open Mode: Write Timing Characteristics

AVDD = DVDD = 3.3 V, exposed pad (EPAD) = 0 V. See Figure 30.

#### Table 2.

| Parameter      | Test Conditions/Comments                              | Min | Тур | Мах | Unit |

|----------------|-------------------------------------------------------|-----|-----|-----|------|

| t1             | Serial data input (SDI) setup time to SCK rising edge | 3   |     |     | ns   |

| t <sub>2</sub> | Serial clock (SCK) rising edge to SDI hold time       | 3   |     |     | ns   |

| t3             | Serial enable (SEN) low duration                      | 10  |     |     | ns   |

| t4             | SEN high duration                                     | 10  |     |     | ns   |

| t5             | SCK 32 <sup>nd</sup> rising edge to SEN rising edge   | 10  |     |     | ns   |

| t <sub>6</sub> | Recovery time (not shown in Figure 30)                | 20  |     |     | ns   |

| fscк           | Maximum SPI clock speed                               |     | 50  |     | MHz  |

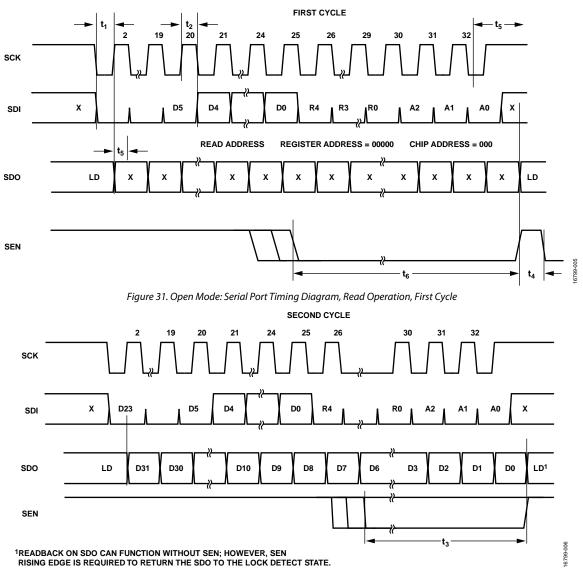

#### SPI Open Mode: Read Timing Characteristics

AVDD = DVDD = 3.3 V, EPAD = 0 V. See Figure 31 and Figure 32.

Table 3.

| Parameter       | Test Conditions/Comments                                      | Min | Тур | Max | Unit |

|-----------------|---------------------------------------------------------------|-----|-----|-----|------|

| <b>t</b> 1      | SDI setup time to SCK rising edge.                            | 3   |     |     | ns   |

| t <sub>2</sub>  | SCK rising edge to SDI hold time.                             | 3   |     |     | ns   |

| t <sub>3</sub>  | SEN low duration.                                             | 10  |     |     | ns   |

| t4              | SEN high duration.                                            | 10  |     |     | ns   |

| t5 <sup>1</sup> | SCK rising edge to SDO time. Add 0.2 ns for each pF of CLOAD. |     |     | 8.2 | ns   |

| t <sub>6</sub>  | Recovery time.                                                | 10  |     |     | ns   |

| t7              | SCK 32 <sup>nd</sup> rising edge to SEN rising edge.          | 10  |     |     | ns   |

<sup>1</sup> An extra 0.2 ns delay is required for every 1 pF load on SDO.

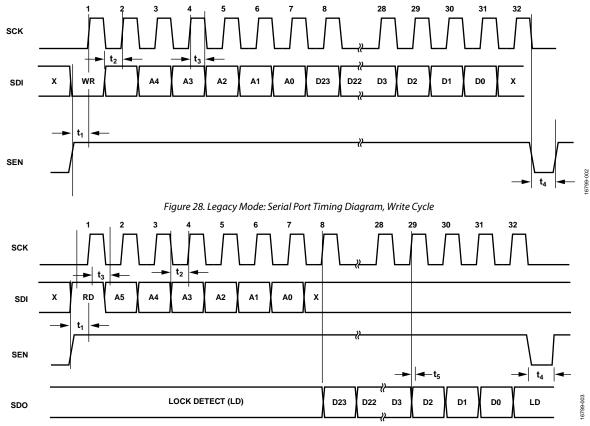

#### SPI Legacy Mode: Write Timing Characteristics

$AVDD = DVDD = 3.3 V \pm 10\%$ , analog ground (AGND) = digital ground (DGND) = 0 V. See Figure 28.

Table 4.

| Parameter                   | Test Conditions/Comments | Min | Тур | Max | Units |

|-----------------------------|--------------------------|-----|-----|-----|-------|

| t1                          | SEN to SCK setup time    | 8   |     |     | ns    |

| t <sub>2</sub>              | SDI to SCK setup time    | 3   |     |     | ns    |

| t₃                          | SCK to SDI hold time     | 3   |     |     | ns    |

| t4                          | SEN low duration         | 20  |     |     | ns    |

| Maximum SPI Clock Frequency |                          |     |     | 50  | MHz   |

#### SPI Legacy Mode: Read Timing Characteristics

$AVDD = DVDD = 3.3 V, \pm 10\%, AGND = DGND = 0 V.$  See Figure 29.

Table 5.

| Parameter             | Test Conditions/Comments                          | Min | Тур | Max | Units |

|-----------------------|---------------------------------------------------|-----|-----|-----|-------|

| t1                    | SEN to SCK setup time                             | 8   |     |     | ns    |

| <b>t</b> <sub>2</sub> | SDI to SCK setup time                             | 3   |     |     | ns    |

| t <sub>3</sub>        | SCK to SDI hold time                              | 3   |     |     | ns    |

| t4                    | SEN low duration                                  | 20  |     |     | ns    |

| ts                    | SCK to SDO delay. Add 0.2 ns for each pF of CLOAD |     |     | 8.2 | ns    |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

| Parameter                                         | Rating                     |

|---------------------------------------------------|----------------------------|

| AVDD to GND, DVDD to GND                          | –0.3 V to +3.6 V           |

| AVDD to DVDD                                      | –0.5 V to +0.5 V           |

| VDDLS, VPPCP to GND                               | –0.3 V to +3.8 V           |

| VDDLS to VPPCP <sup>1</sup>                       | –0.5 V to +0.5 V           |

| RVDD, VCCPD, VCCPS, VCCHF to GND                  | –0.3 V to +3.6 V           |

| XREFP                                             | 18 dBm, 5.6 V peak         |

| Minimum Digital Load                              | 1.0 kΩ                     |

| Digital Input 1.4 V to 1.7 V Minimum Rise<br>Time | 20 ns                      |

| Digital Input Voltage Range                       | –0.25 V to DVDD +<br>0.5 V |

| VDD1, VDD2, VDD3                                  | –0.3 V to +3.6 V           |

| VCOVCC                                            | –0.3 V to +5.5 V           |

| Operating Temperature Range                       | -40°C to +85°C             |

| Storage Temperature Range                         | –65°C to +120°C            |

| Maximum Junction Temperature                      | 150°C                      |

| Reflow Soldering                                  |                            |

| Peak Temperature                                  | 260°C                      |

| Time at Peak Temperature                          | 40 sec                     |

| Electrostatic Discharge (ESD)                     |                            |

| Charged Device Model                              | 500 V                      |

| Human Body Model                                  | 1000 V                     |

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA} \text{ is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure. } \theta_{JC} \text{ is the junction to case thermal resistance.}$

#### Table 7. Thermal Resistance

| Package Type <sup>1</sup> | θ <sub>JA</sub> | θις | Unit |

|---------------------------|-----------------|-----|------|

| CC-48-1                   | 31.2            | 6.9 | °C/W |

$^1$  Thermal impedance measured values are based on use of a 2S2P board with the thermal impedance pad (EPAD) soldered to GND (GND = 0 V). A cold plate is set to 20°C and attached to the bottom side of the PCB using 100  $\mu m$  thermal interface material (3.56 W/mK).

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>1</sup> VDDLS must be equal to VPPCP.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

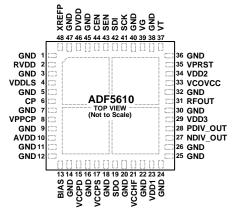

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

NOTES

1. EXPOSED PAD. THE EXPOSED PAD OR GROUND PADDLE ON THE BACKSIDE OF THE PACKAGE MUST BE TIED TO DC GROUND FOR ELECTRICAL, MECHANICAL, AND THERMAL REASONS. NOTE THAT RF GROUND AND DC GROUND ARE THE SAME IN THIS CASE.

Figure 2. Pin Configuration

#### **Table 8. Pin Function Descriptions**

| Pin No.                                                                                  | Mnemonic | Description                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 7, 9, 11, 12, 14, 16,<br>18, 20, 22, 24 to 26,<br>30, 32, 36, 38, 40, 45,<br>47 | GND      | Ground.                                                                                                                                                                                                                                                                                                                           |

| 2                                                                                        | RVDD     | Reference Path Supply. 3.3 V $\pm$ 5%.                                                                                                                                                                                                                                                                                            |

| 4                                                                                        | VDDLS    | Power Supply for Charge Pump Digital Section. 3.3 V $\pm$ 5% typical, 3.6 V maximum. VDDLS must be equal to VPPCP.                                                                                                                                                                                                                |

| 6                                                                                        | СР       | Charge Pump Output. Place first pole of low-pass loop filter close to this pin if loop filter path is electrically long.                                                                                                                                                                                                          |

| 8                                                                                        | VPPCP    | Power Supply for Charge Pump. 3.3 V $\pm$ 5% typical, 3.6 V maximum. VPPCP must be equal to VDDLS.                                                                                                                                                                                                                                |

| 10                                                                                       | AVDD     | Analog Supply. 3.3 V $\pm$ 5%. AVDD must be equal to DVDD.                                                                                                                                                                                                                                                                        |

| 13                                                                                       | BIAS     | External Bypass Decoupling for Precision Bias Circuits. Note that the 1.920 V $\pm$ 20 mV reference voltage is generated internally and cannot drive an external load. The reference voltage must be measured with a 10 G $\Omega$ meter, such as the Agilent 34410A. A normal 10 M $\Omega$ digital voltmeter reads erroneously. |

| 15                                                                                       | VCCPD    | Phase Detector Supply. 3.3 V $\pm$ 5%.                                                                                                                                                                                                                                                                                            |

| 17                                                                                       | VCCPS    | Prescaler Supply. 3.3 V $\pm$ 5%.                                                                                                                                                                                                                                                                                                 |

| 19                                                                                       | SDO      | Serial Data Output. Lock detect and various other functions are available via an internal mux.                                                                                                                                                                                                                                    |

| 21                                                                                       | VCCHF    | Power Supply for PLL RF Section. 3.3 V $\pm$ 5%. Place a decoupling capacitor as close as possible to this pin.                                                                                                                                                                                                                   |

| 23                                                                                       | VDD1     | Bias for VCO Digital Logic, VG Pin, SPI Buffer, and Input Buffer to PLL. Nominally 3.3 V $\pm$ 5%. Retain bias to hold the VCO register contents when the VCO is powered down.                                                                                                                                                    |

| 27                                                                                       | NDIV_OUT | Complementary Output of Differential Frequency Divider. N = 1, 2, 4, 8, 16, 32, 64, or 128. DC block required. A broadband 100 nF capacitor is recommended.                                                                                                                                                                       |

| 28                                                                                       | PDIV_OUT | Primary Output of Differential Frequency Divider. N = 1, 2, 4, 8, 16, 32, 64, or 128. DC block required. A broadband 100 nF capacitor is recommended.                                                                                                                                                                             |

| 29                                                                                       | VDD3     | Differential Output Divider Supply. 3.3 V $\pm$ 5%.                                                                                                                                                                                                                                                                               |

| 31                                                                                       | RFOUT    | RF Output (7300 MHz to 14,600 MHz). Internal dc block. DC block using a broadband 100 nF capacitor.                                                                                                                                                                                                                               |

| 33                                                                                       | VCOVCC   | VCO Power Supply. 5.0 V $\pm$ 5%.                                                                                                                                                                                                                                                                                                 |

| 34                                                                                       | VDD2     | Reference Voltage Supply. 3.3 V $\pm$ 5%.                                                                                                                                                                                                                                                                                         |

| 35                                                                                       | VPRST    | Temperature Dependent, Calibration Preset. Decouple with a 470 nF capacitor.                                                                                                                                                                                                                                                      |

| 37                                                                                       | VT       | VCO Tuning Port. 0 V to 3.6 V, $\pm$ 5%. Place last pole of low-pass filtered charge pump output close to this pin if loop filter path is electrically long.                                                                                                                                                                      |

| Pin No. | Mnemonic | Description                                                                                                                                                                                                          |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39      | VG       | Gate Voltage Bypassing. Decouple to GND with a low effective series resistance (ESR), 10 $\mu\text{F}$ capacitor.                                                                                                    |

| 41      | SCK      | Serial Port Interface Clock Input.                                                                                                                                                                                   |

| 42      | SDI      | Serial Port Data Input.                                                                                                                                                                                              |

| 43      | SEN      | Serial Port Interface Enable Input. Active high.                                                                                                                                                                     |

| 44      | CEN      | Hardware Chip Enable Input. Active high. Logic low powers down the PLL section.                                                                                                                                      |

| 46      | DVDD     | Digital Power Supply. 3.3 V $\pm$ 5%. Retain bias to hold the PLL register contents when powering down the PLL.                                                                                                      |

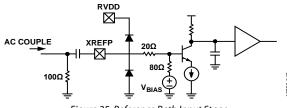

| 48      | XREFP    | External Reference Input. For 50 $\Omega$ match, ac couple to the XREFP pin using a low reactance capacitor value and add a 100 $\Omega$ resistor to ground.                                                         |

|         | EPAD     | Exposed Pad. The exposed pad or ground paddle on the backside of the package must be tied to dc ground for electrical, mechanical, and thermal reasons. Note that RF ground and dc ground are the same in this case. |

### TYPICAL PERFORMANCE CHARACTERISTICS

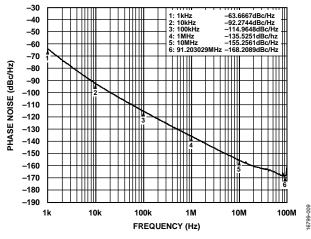

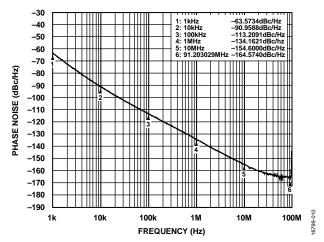

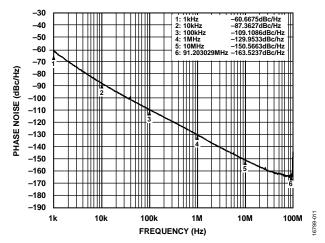

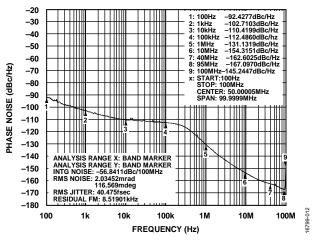

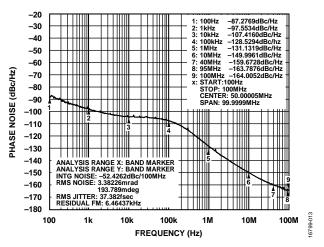

For Figure 3 through Figure 7, Agilent E5052B is the test equipment used to measure the phase noise.

Figure 3. Open-Loop VCO Phase Noise at 7300 MHz, RFOUT, High Performance Mode (VCO Register 0x01, Bits[4:2] = 7 (Decimal)

Figure 4. Open-Loop VCO Phase Noise at 10000 MHz, RFOUT, High Performance Mode (VCO Register 0x01, Bits[4:2] = 7 (Decimal))

Figure 5. Open-Loop VCO Phase Noise 14.6 GHz, RFOUT, High Performance Mode (VCO Register 0x01, Bits[4:2] = 7 (Decimal))

Figure 6. Closed-Loop Phase Noise Illustrating Low Jitter Capability at 8.0 GHz, Wenzel 100 MHz Reference, 100 MHz PFD, RFOUT, High Performance Mode (VCO Register 0x01, Bits[4:2] = 7 (Decimal)), 25°C

Figure 7. Closed-Loop Phase Noise Illustrating Low Jitter Capability at 14.4 GHz, Wenzel 100 MHz Reference, 100 MHz PFD, RFOUT, High Performance Mode (VCO Register 0x01, Bits[4:2] = 7 (Decimal)), 25°C

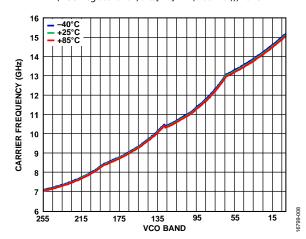

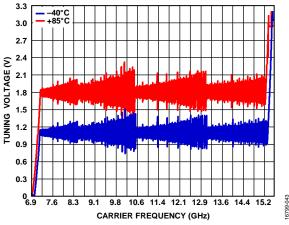

Figure 8. Carrier Frequency vs. VCO Band, Autocalibration Enabled, VDDLS = 3.3 V, VPPCP = 3.3 V

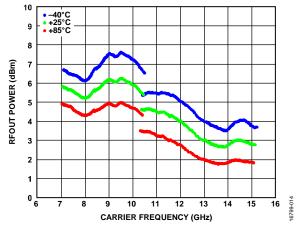

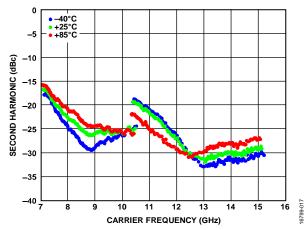

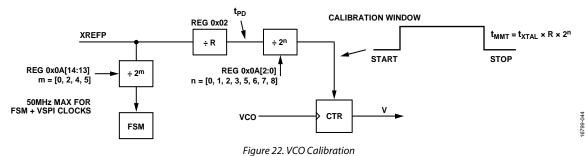

Figure 9. RFOUT Power vs. Carrier Frequency, Maximum Output Gain = (VCO Register 0x01, Bits[1:0] = 3 (Decimal)), High Performance Mode (VCO Register 0x01, Bits[4:2] = 7 (Decimal))

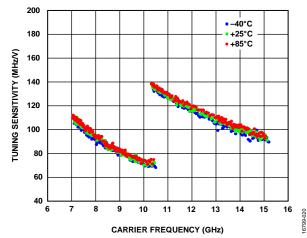

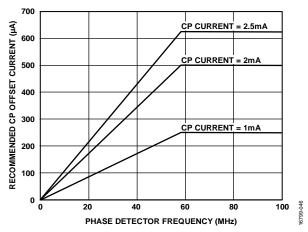

Figure 10. Tuning Sensitivity vs. Carrier Frequency, VT = 1.65 V, Maximum Output Gain (VCO Register 0x01, Bits[1:0] = 3 (Decimal)), High Performance Mode (VCO Register 0x01, Bits[4:2] = 7 (Decimal))

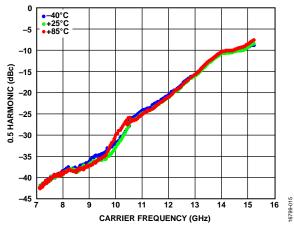

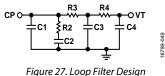

Figure 11. 0.5 Harmonic vs. Carrier Frequency (Fundamental Feedthrough at RFOUT), Maximum Output Gain = (VCO Register 0x01, Bits[1:0] = 3 (Decimal)), High Performance Mode (VCO Register 0x01, Bits[4:2] = 7 (Decimal))