# CMOS, Low Voltage Serially Controlled, Octal SPST Switches

**Data Sheet**

**ADG714/ADG715**

#### **FEATURES**

SPI/QSPI/MICROWIRE-compatible interface (ADG714)

ADG715: I<sup>2</sup>C-compatible interface (ADG715)

2.7 V to 5.5 V single supply

±2.5 V dual supply

2.5 Ω on resistance

0.6 Ω on resistance flatness

0.1 nA leakage currents

Octal SPST

Power-on reset

Fast switching times

TTL/CMOS compatible

#### **APPLICATIONS**

Data acquisition systems Communication systems Relay replacement Audio and video switching

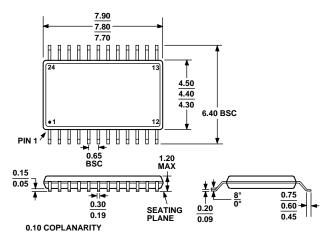

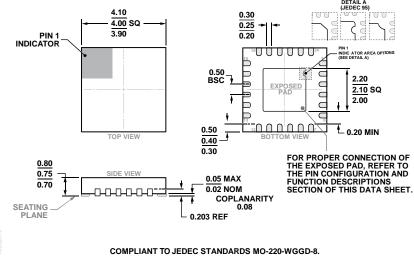

24-lead TSSOP and 24-lead LFCSP

#### **GENERAL DESCRIPTION**

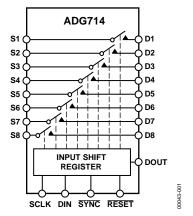

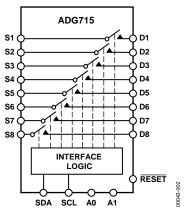

The ADG714/ADG715 are complementary metal-oxide semiconductor (CMOS), octal single-pole, single-throw (SPST) switches, controlled via either a 2- or 3-wire serial interface. On resistance is closely matched between the switches and is flat over the full signal range. Each switch conducts equally well in both directions, and the input signal range extends to the supplies. Data is written to these devices in the form of 8 bits, each bit corresponding to one channel.

The ADG714 uses a 3-wire serial interface that is compatible with serial peripheral interface (SPI), QSPI<sup>™</sup>, MICROWIRE<sup>™</sup> interface standards, and most digital signal processing (DSP) interface standards. The output of the shift register DOUT enables a number of these devices to be daisy-chained.

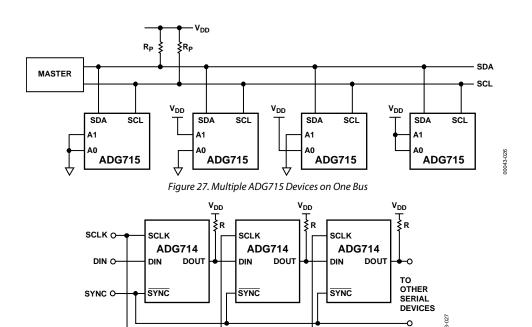

The ADG715 uses a 2-wire serial interface that is compatible with the  $I^2C$  interface standard. The ADG715 has four hardwired addresses, selectable from two external address pins (A0 and A1). The pins allow the two LSBs of the 7-bit slave address to be set by the user. A maximum of four of these devices may be connected to the bus.

On power-up of these devices, all switches are in the off condition, and the internal registers contain all zeros.

A low power consumption and operating supply range of 2.7 V to 5.5 V make these devices ideal for many applications. These devices can also be supplied from a dual ±2.5 V supply. The ADG714 is available in a 24-lead TSSOP and a 24-lead LFCSP,

Rev. E

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

#### **FUNCTIONAL BLOCK DIAGRAMS**

Figure 1. ADG714 Functional Block Diagram

Figure 2. ADG715 Functional Block Digaram

and the ADG715 is available in a 24-lead TSSOP.

#### **PRODUCT HIGHLIGHTS**

- 1. 2- or 3-wire serial interface.

- Single-/dual-supply operation.

The ADG714 and ADG715 are fully specified and guaranteed with 3 V, 5 V, and ±2.5 V supply rails.

- 3. Low on resistance, typically 2.5  $\Omega$ .

- 4. Low leakage.

- 5. Power-on reset.

- A 24-lead TSSOP for both the ADG714 and the ADG715.

A 24-lead LFCSP for the ADG714.

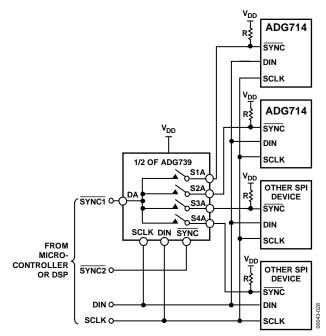

#### TABLE OF CONTENTS Applications......1 General Description \_\_\_\_\_\_1 Product Highlights ......1 3 V Single Supply......4 ±2.5 V Dual Supply ...... 5 Decoding Multiple ADG714 Devices Using the ADG739 ... 20 Thermal Resistance 9 ESD Caution 9 **REVISION HISTORY** 6/2018-Rev. D to Rev. E 10/2015-Rev. C to Rev. D Changes to ADG714 Timing Characteristics Table and Figure 1 ......5 Changes to Features Section, General Description Section, and 1/2013—Rev. B to Rev. C Changes to Dual Supply Table Summary and IDD Test Added 3 V Single Supply Section ...... 4 Conditions/Comments......4 Changes to Table 2......4 Changed Dual Supply Section to ±2.5 V Dual Supply Section .. 5 Changes to ±2.5 V Dual Supply Section and Table 3......5 11/2002-Rev. A to Rev. B Changed ADG714 Timing Characteristics Section to Timing Edits to Features.....1 Edits to General Description ......1 Changes to ADG714 Section, Table 4, ADG715 Section, and Edits to Product Highlights.....1 Added Timing Diagrams Section...... 8 Changes to Table 6......9 Added Thermal Resistance Section and Table 7; Renumbered Sequentially ......9 4/2000—Revision 0: Initial Version Changes to Figure 5......10 Added Figure 6 and Table 9......11 Changes to Figure 14 Caption, Figure 16 Caption, Figure 17 Caption, Figure 18, and Figure 19......14

## SPECIFICATIONS 5 V SINGLE SUPPLY

$V_{DD}$  = 5 V  $\pm$  10%,  $V_{SS}$  = 0 V, and GND = 0 V, unless otherwise noted. Temperature range is  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Table 1.

| Parameter                                              | +25°C                | -40°C to +85°C         | Unit    | Test Conditions/Comments                                                       |

|--------------------------------------------------------|----------------------|------------------------|---------|--------------------------------------------------------------------------------|

| ANALOG SWITCH                                          |                      |                        |         |                                                                                |

| Analog Signal Range                                    |                      | 0 V to V <sub>DD</sub> | V       |                                                                                |

| On Resistance, R <sub>ON</sub>                         | 2.5                  |                        | Ωtyp    | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA}$                            |

|                                                        | 4.5                  | 5                      | Ω max   |                                                                                |

| On Resistance Match Between Channels, ΔR <sub>ON</sub> |                      | 0.4                    | Ω typ   |                                                                                |

|                                                        |                      | 0.8                    | Ω max   | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA}$                            |

| On Resistance Flatness, RFLAT(ON)                      | 0.6                  |                        | Ωtyp    | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA}$                            |

|                                                        |                      | 1.2                    | Ω max   |                                                                                |

| LEAKAGE CURRENTS                                       |                      |                        |         | $V_{DD} = 5.5 \text{ V}$                                                       |

| Source Off Leakage, I <sub>S (OFF)</sub>               | ±0.01                |                        | nA typ  | $V_D = 4.5 \text{ V}/1 \text{ V}, V_S = 1 \text{ V}/4.5 \text{ V}$             |

|                                                        | ±0.1                 | ±0.3                   | nA max  |                                                                                |

| Drain Off Leakage, ID (OFF)                            | ±0.01                |                        | nA typ  | $V_D = 4.5 \text{ V}/1 \text{ V}, V_S = 1 \text{ V}/4.5 \text{ V}$             |

|                                                        | ±0.1                 | ±0.3                   | nA max  |                                                                                |

| Channel On Leakage, ID (ON), IS (ON)                   | ±0.01                |                        | nA typ  | $V_D = V_S = 1 \text{ V or } 4.5 \text{ V}$                                    |

|                                                        | ±0.1                 | ±0.3                   | nA max  |                                                                                |

| DIGITAL INPUTS                                         |                      |                        |         |                                                                                |

| Input Voltage                                          |                      |                        |         |                                                                                |

| High, V <sub>INH</sub>                                 |                      | 2.4                    | V min   |                                                                                |

| Low, V <sub>INL</sub>                                  |                      | 0.8                    | V max   |                                                                                |

| High or Low Input Current, IINH or IINL                | 0.005                |                        | μA typ  | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                         |

| -                                                      |                      | ±0.1                   | μA max  |                                                                                |

| Digital Input Capacitance, C <sub>IN</sub>             | 3                    |                        | pF typ  |                                                                                |

| DIGITAL OUTPUT, ADG714, DOUT                           |                      |                        |         |                                                                                |

| Output Voltage Low, Vol                                |                      | 0.4                    | V max   | I <sub>SINK</sub> = 6 mA                                                       |

| Digital Output Capacitance, Co∪T                       | 4                    |                        | pF typ  |                                                                                |

| DIGITAL INPUTS, SCL, SDA                               |                      |                        | 1 71    |                                                                                |

| Input Voltage                                          |                      |                        |         |                                                                                |

| High, V <sub>INH</sub>                                 |                      | $0.7 \times V_{DD}$    | V min   |                                                                                |

| <b>3</b>                                               |                      | $V_{DD} + 0.3$         | V max   |                                                                                |

| High, V <sub>INH</sub>                                 |                      | -0.3                   | V min   |                                                                                |

| <b>3</b>                                               |                      | $0.3 \times V_{DD}$    | V max   |                                                                                |

| Input Leakage Current, I <sub>IN</sub>                 | 0.005                |                        | μA typ  | $V_{IN} = 0 V \text{ to } V_{DD}$                                              |

| 1                                                      |                      | ±1                     | μA max  |                                                                                |

| Input Hysteresis, V <sub>HYST</sub>                    | $0.05 \times V_{DD}$ |                        | V min   |                                                                                |

| Input Capacitance, C <sub>IN</sub>                     | 6                    |                        | pF typ  |                                                                                |

| LOGIC OUTPUT, SDA                                      | -                    |                        | F: -7 P |                                                                                |

| Output Voltage Low, V <sub>OL</sub>                    |                      | 0.4                    | V max   | I <sub>SINK</sub> = 3 mA                                                       |

| Jack Straige Lotty Vol.                                |                      | 0.6                    | V max   | $I_{SINK} = 6 \text{ mA}$                                                      |

| DYNAMIC CHARACTERISTICS                                |                      | 0.0                    | * IIIux | ISHN OTHER                                                                     |

| On Time, ton                                           |                      |                        |         |                                                                                |

| ADG714                                                 | 20                   |                        | ns typ  | $V_S = 3 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$                     |

| דו עסטוד                                               | 20                   | 32                     |         | ν <sub>5</sub> – 5 ν, ιι <sub>ι</sub> – 500 <u>1</u> 2, C <sub>ι</sub> – 55 βΓ |

| ADG715                                                 | 95                   | J2                     | ns max  | $V_S = 3 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$                     |

| כו /מטח                                                | 33                   | 140                    | ns typ  | $v_S = 3 v, n_L = 300 \Omega_L, C_L = 35 pr$                                   |

|                                                        |                      | 140                    | ns max  |                                                                                |

| Parameter                                                        | +25°C | -40°C to +85°C | Unit    | Test Conditions/Comments                                   |

|------------------------------------------------------------------|-------|----------------|---------|------------------------------------------------------------|

| Off Time, t <sub>OFF</sub>                                       |       |                |         |                                                            |

| ADG714                                                           | 8     |                | ns typ  | $V_S = 3 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$ |

|                                                                  |       | 15             | ns max  |                                                            |

| ADG715                                                           | 85    |                | ns typ  | $V_S = 3 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$ |

|                                                                  |       | 130            | ns max  |                                                            |

| Break-Before-Make Time Delay, t₀                                 | 8     |                | ns typ  | $V_S = 3 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$ |

|                                                                  |       | 1              | ns min  |                                                            |

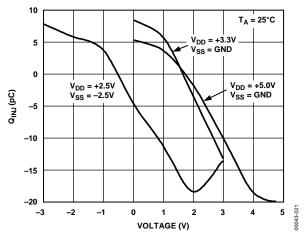

| Charge Injection, Q <sub>INJ</sub>                               | ±3    |                | pC typ  | $V_S = 2 V$ , $R_S = 0 \Omega$ , $C_L = 1 nF$              |

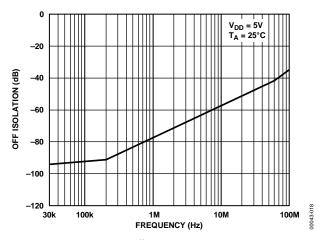

| Off Isolation                                                    | -60   |                | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$            |

|                                                                  | -80   |                | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$             |

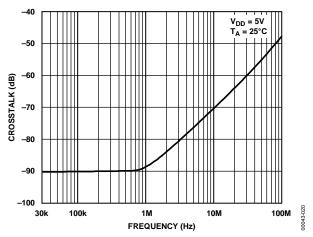

| Channel to Channel Crosstalk                                     | -70   |                | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$            |

|                                                                  | -90   |                | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$             |

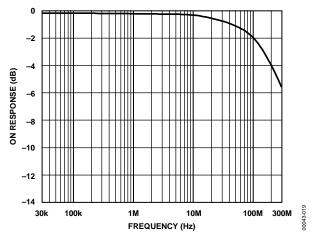

| –3 dB Bandwidth                                                  | 155   |                | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$                           |

| Insertion Loss                                                   | -0.3  |                | dB typ  |                                                            |

| Off Switch Source Capacitance, C <sub>S (OFF)</sub>              | 11    |                | pF typ  |                                                            |

| Off Switch Drain Capacitance, CD (OFF)                           | 11    |                | pF typ  |                                                            |

| On Switch Capacitance, C <sub>D (ON)</sub> , C <sub>S (ON)</sub> | 22    |                | pF typ  |                                                            |

| POWER REQUIREMENTS                                               |       |                |         | $V_{DD} = 5.5 \text{ V}$                                   |

| Positive Power Supply Current, IDD                               | 10    |                | μA typ  | Digital inputs = 0 V or 5.5 V                              |

|                                                                  |       | 20             | μA max  |                                                            |

#### **3 V SINGLE SUPPLY**

$V_{DD}$  = 3 V  $\pm$  10%,  $V_{SS}$  = 0 V, and GND = 0 V, unless otherwise noted. Temperature range is  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Table 2.

| Parameter                                                     | +25°C | -40°C to +85°C         | Unit   | Test Conditions/Comments                                       |

|---------------------------------------------------------------|-------|------------------------|--------|----------------------------------------------------------------|

| ANALOG SWITCH                                                 |       |                        |        |                                                                |

| Analog Signal Range                                           |       | 0 V to V <sub>DD</sub> | V      |                                                                |

| On Resistance, R <sub>ON</sub>                                | 6     |                        | Ω typ  | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA}$            |

|                                                               | 11    | 12                     | Ω max  |                                                                |

| On Resistance Match Between Channels, $\Delta R_{\text{ON}}$  |       | 0.4                    | Ω typ  | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA}$            |

|                                                               |       | 1.2                    | Ω max  |                                                                |

| On Resistance Flatness, R <sub>FLAT(ON)</sub>                 |       | 3.5                    | Ω typ  | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA}$            |

| LEAKAGE CURRENTS                                              |       |                        |        | $V_{DD} = 3.3 \text{ V}$                                       |

| Source OFF Leakage, I <sub>S (OFF)</sub>                      | ±0.01 |                        | nA typ | $V_S = 3 \text{ V}/1 \text{ V}, V_D = 1 \text{ V}/3 \text{ V}$ |

|                                                               | ±0.1  | ±0.3                   | nA max |                                                                |

| Drain OFF Leakage, I <sub>D (OFF)</sub>                       | ±0.01 |                        | nA typ | $V_S = 1 \text{ V/3 V}, V_D = 3 \text{ V/1 V}$                 |

|                                                               | ±0.1  | ±0.3                   | nA max |                                                                |

| Channel ON Leakage, I <sub>D (ON)</sub> , I <sub>S (ON)</sub> | ±0.01 |                        | nA typ | $V_S = V_D = 1 \text{ V or } 3 \text{ V}$                      |

|                                                               | ±0.1  | ±0.3                   | nA max |                                                                |

| DIGITAL INPUTS                                                |       |                        |        |                                                                |

| Input Voltage                                                 |       |                        |        |                                                                |

| High, V <sub>INH</sub>                                        |       | 2.0                    | V min  |                                                                |

| Low, V <sub>INL</sub>                                         |       | 0.8                    | V max  |                                                                |

| High or Low Input Current, IINH or IINL                       | 0.005 |                        | μA typ | $V_{IN} = V_{INL} \text{ or } V_{INH}$                         |

|                                                               |       | ±0.1                   | μA max |                                                                |

| Digital Input Capacitance, C <sub>IN</sub>                    | 3     |                        | pF typ |                                                                |

| DIGITAL OUTPUT, ADG714, DOUT                                  |       |                        |        |                                                                |

| Output Voltage Low, Vol                                       |       | 0.4                    | V max  | Isink = 6 mA                                                   |

| Digital Output Capacitance, Cout                              | 4     |                        | pF typ |                                                                |

| Parameter                                           | +25°C                | -40°C to +85°C      | Unit     | Test Conditions/Comments                                              |

|-----------------------------------------------------|----------------------|---------------------|----------|-----------------------------------------------------------------------|

| DIGITAL INPUTS, SCL, SDA                            |                      |                     |          |                                                                       |

| Input Voltage                                       |                      |                     |          |                                                                       |

| High, V <sub>INH</sub>                              |                      | $0.7 \times V_{DD}$ | V min    |                                                                       |

|                                                     |                      | $V_{DD} + 0.3$      | V max    |                                                                       |

| Low, V <sub>INL</sub>                               |                      | -0.3                | V min    |                                                                       |

|                                                     |                      | $0.3 \times V_{DD}$ | V max    |                                                                       |

| Input Leakage Current, I <sub>IN</sub>              | 0.005                |                     | μA typ   | $V_{IN} = 0 V to V_{DD}$                                              |

|                                                     |                      | ±1                  | μA max   |                                                                       |

| Input Hysteresis, V <sub>HYST</sub>                 | $0.05 \times V_{DD}$ |                     | V min    |                                                                       |

| Input Capacitance, C <sub>IN</sub>                  | 6                    |                     | pF typ   |                                                                       |

| LOGIC OUTPUT, (SDA)                                 |                      |                     | . ,,     |                                                                       |

| Output Voltage Low, Vol                             |                      | 0.4                 | V max    | I <sub>SINK</sub> = 3 mA                                              |

| , , , , , , , , , , , , , , , , , , ,               |                      | 0.6                 | V max    | I <sub>SINK</sub> = 6 mA                                              |

| DYNAMIC CHARACTERISTICS                             |                      |                     |          |                                                                       |

| On Time, ton                                        |                      |                     |          |                                                                       |

| ADG714                                              | 35                   |                     | ns typ   | $V_S = 2 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$            |

|                                                     |                      | 65                  | ns max   | 13 2 1,112 300 12, 02 30 p.                                           |

| ADG715                                              | 130                  |                     | ns typ   | $V_S = 2 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$            |

| 7,0 (7,13                                           | 150                  | 200                 | ns max   | V <sub>5</sub> = 2 V, N <sub>L</sub> = 300 12, C <sub>L</sub> = 33 pt |

| Off Time, t <sub>OFF</sub>                          |                      | 200                 | 115 THUX |                                                                       |

| ADG714                                              | 11                   |                     | ns typ   | $V_S = 2 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$            |

|                                                     |                      | 20                  | ns max   |                                                                       |

| ADG715                                              | 115                  |                     | ns typ   | $V_S = 2 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$            |

| , 15 6, 15                                          | 113                  | 180                 | ns max   | 13 2 1/112 300 12/ CE 33 PI                                           |

| Break-Before-Make Time Delay, t <sub>D</sub>        | 8                    | 100                 | ns typ   | $V_S = 2 \text{ V, } R_L = 300 \Omega, C_L = 35 \text{ pF}$           |

| break before make time belay, to                    |                      | 1                   | ns min   | V3 = 2 V, NE = 300 12, CE = 33 pr                                     |

| Charge Injection, Q <sub>INJ</sub>                  | ±2                   | '                   | pC typ   | $V_S = 1.5 \text{ V, } R_S = 0 \Omega, C_L = 1 \text{ nF}$            |

| Off Isolation                                       | <del>-60</del>       |                     | dB typ   | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$                       |

| on isolation                                        | -80                  |                     | dB typ   | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$                        |

| Channel to Channel Crosstalk                        | -70                  |                     | dB typ   | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 10 \text{ MHz}$       |

| Charmer to Charmer Crosstant                        | -90                  |                     | dB typ   | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 1 \text{ MHz}$        |

| –3 dB Bandwidth                                     | 155                  |                     | MHz typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$                                      |

| Insertion Loss                                      | -0.4                 |                     | dB typ   | 11. 30 12, CL = 3 pi                                                  |

| Off Switch Source Capacitance, C <sub>S (OFF)</sub> | 11                   |                     | pF typ   |                                                                       |

| Off Switch Drain Capacitance, C <sub>D (OFF)</sub>  | 11                   |                     | pF typ   |                                                                       |

| On Switch Capacitance, $C_D(ON)$ , $C_S(ON)$        | 22                   |                     | pF typ   |                                                                       |

| POWER REQUIREMENTS                                  |                      |                     | Pi typ   | $V_{DD} = 3.3 \text{ V}$                                              |

| Positive Power Supply Current, IDD                  | 10                   |                     | μΑ typ   | Digital inputs = 0 V or 3.3 V                                         |

| rositive rower supply current, lob                  | 10                   | 20                  | . ,.     | Digital Inputs – 0 v of 5.3 v                                         |

|                                                     |                      | 20                  | μA max   |                                                                       |

#### ±2.5 V DUAL SUPPLY

$V_{DD}$  = +2.5 V  $\pm$  10%,  $V_{SS}$  = -2.5 V  $\pm$  10%, and GND = 0 V, unless otherwise noted. Temperature range is -40°C to +85°C.

Table 3.

| Parameter                                              | +25°C | -40°C to +85°C       | Unit  | Test Conditions/Comments                      |

|--------------------------------------------------------|-------|----------------------|-------|-----------------------------------------------|

| ANALOG SWITCH                                          |       |                      |       |                                               |

| Analog Signal Range                                    |       | $V_{SS}$ to $V_{DD}$ | V     |                                               |

| On Resistance, Ron                                     | 2.5   |                      | Ω typ | $V_S = V_{SS}$ to $V_{DD}$ , $I_{DS} = 10$ mA |

|                                                        | 4.5   | 5                    | Ω max |                                               |

| On Resistance Match Between Channels, ΔR <sub>ON</sub> |       | 0.4                  | Ω typ | $V_S = V_{SS}$ to $V_{DD}$ , $I_{DS} = 10$ mA |

|                                                        |       | 0.8                  | Ω max |                                               |

| On Resistance Flatness, R <sub>FLAT(ON)</sub>          | 0.6   |                      | Ω typ | $V_S = V_{SS}$ to $V_{DD}$ , $I_{DS} = 10$ mA |

|                                                        |       | 1                    | Ω max |                                               |

Rev. E | Page 5 of 21

| Parameter                                                       | +25°C                | -40°C to +85°C      | Unit    | Test Conditions/Comments                                                       |

|-----------------------------------------------------------------|----------------------|---------------------|---------|--------------------------------------------------------------------------------|

| LEAKAGE CURRENTS                                                |                      |                     |         | $V_{DD} = +2.75 \text{ V}, V_{SS} = -2.75 \text{ V}$                           |

| Source Off Leakage, Is (OFF)                                    | ±0.01                |                     | nA typ  | $V_S = +2.25 \text{ V/}-1.25 \text{ V}, V_D = -1.25 \text{ V/}+2.25 \text{ V}$ |

|                                                                 | ±0.1                 | ±0.3                | nA max  |                                                                                |

| Drain Off Leakage, ID (OFF)                                     | ±0.01                |                     | nA typ  | $V_S = +2.25 \text{ V/}-1.25 \text{ V}, V_D = -1.25 \text{ V/}+2.25 \text{ V}$ |

|                                                                 | ±0.1                 | ±0.3                | nA max  |                                                                                |

| Channel On Leakage, ID (ON), Is (ON)                            | ±0.01                |                     | nA typ  | $V_S = V_D = +2.25 \text{ V/}-1.25 \text{ V}$                                  |

|                                                                 | ±0.1                 | ±0.3                | nA max  |                                                                                |

| DIGITAL INPUTS                                                  |                      |                     |         |                                                                                |

| Input Voltage                                                   |                      |                     |         |                                                                                |

| High, V <sub>INH</sub>                                          |                      | 1.7                 | V min   |                                                                                |

| Low, V <sub>INL</sub>                                           |                      | 0.7                 | V max   |                                                                                |

| High or Low Input Current, I <sub>INH</sub> or I <sub>INL</sub> | 0.005                |                     | μA typ  | V <sub>IN</sub> = V <sub>INL</sub> or V <sub>INH</sub>                         |

| , ,                                                             |                      | ±0.1                | μA max  |                                                                                |

| Digital Input Capacitance, C <sub>IN</sub>                      | 3                    |                     | pF typ  |                                                                                |

| DIGITAL OUTPUT, ADG714, DOUT                                    |                      |                     | F 7 F   |                                                                                |

| Output Voltage Low, Vol                                         |                      | 0.4                 | V max   | I <sub>SINK</sub> = 6 mA                                                       |

| Digital Output Capacitance, Cout                                | 4                    |                     | pF typ  | 5                                                                              |

| DIGITAL INPUTS, SCL, SDA                                        | <u> </u>             |                     | F. 7F   |                                                                                |

| Input Voltage                                                   |                      |                     |         |                                                                                |

| High, V <sub>INH</sub>                                          |                      | $0.7 \times V_{DD}$ | V min   |                                                                                |

| THISTI, VINH                                                    |                      | $V_{DD} + 0.3$      | V max   |                                                                                |

| High V                                                          |                      | -0.3                | V min   |                                                                                |

| High, V <sub>INH</sub>                                          |                      |                     |         |                                                                                |

| Invest Lealing Comment I                                        | 0.005                | $0.3 \times V_{DD}$ | V max   | V 0V4-V                                                                        |

| Input Leakage Current, I <sub>IN</sub>                          | 0.005                |                     | μA typ  | $V_{IN} = 0 V \text{ to } V_{DD}$                                              |

|                                                                 |                      | ±1                  | μA max  |                                                                                |

| Input Hysteresis, V <sub>HYST</sub>                             | $0.05 \times V_{DD}$ |                     | V min   |                                                                                |

| Input Capacitance, C <sub>IN</sub>                              | 6                    |                     | pF typ  |                                                                                |

| LOGIC OUTPUT, SDA                                               |                      |                     |         |                                                                                |

| Output Voltage                                                  |                      |                     |         |                                                                                |

| Low, V <sub>OL</sub>                                            |                      | 0.4                 | V max   | I <sub>SINK</sub> = 3 mA                                                       |

|                                                                 |                      | 0.6                 | V max   | $I_{SINK} = 6 \text{ mA}$                                                      |

| DYNAMIC CHARACTERISTICS                                         |                      |                     |         |                                                                                |

| On Time, t <sub>ON</sub>                                        |                      |                     |         |                                                                                |

| ADG714                                                          | 20                   |                     | ns typ  | $V_S = 1.5 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$                   |

|                                                                 |                      | 32                  | ns max  |                                                                                |

| ADG715                                                          | 133                  |                     | ns typ  | $V_S = 1.5 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$                   |

|                                                                 |                      | 200                 | ns max  |                                                                                |

| Off Time, t <sub>OFF</sub>                                      |                      |                     |         |                                                                                |

| ADG714                                                          | 8                    |                     | ns typ  | $V_S = 1.5 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$                   |

|                                                                 |                      | 18                  | ns max  | ·                                                                              |

| ADG715                                                          | 124                  |                     | ns typ  | $V_S = 1.5 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$                   |

|                                                                 |                      | 190                 | ns max  |                                                                                |

| Break-Before-Make Time Delay, t <sub>D</sub>                    | 8                    |                     | ns typ  | $V_S = 1.5 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF}$                   |

| 2                                                               |                      | 1                   | ns min  | ,                                                                              |

| Charge Injection, Q <sub>INJ</sub>                              | ±3                   |                     | pC typ  | $V_{S} = 0 \text{ V}, R_{S} = 0 \Omega, C_{L} = 1 \text{ nF}$                  |

| Off Isolation                                                   | -60                  |                     | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$                                |

| On 1301ation                                                    | -80<br>-80           |                     | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 10 \text{ MHz}$                |

| Channel to Channel Creatally                                    |                      |                     |         | · ·                                                                            |

| Channel to Channel Crosstalk                                    | -70<br>-00           |                     | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$                                |

| 2 10 0 1 1 141                                                  | -90<br>155           |                     | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$                                 |

| –3 dB Bandwidth                                                 | 155                  |                     | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$                                               |

| Insertion Loss                                                  | -0.3                 |                     | dB typ  |                                                                                |

| Parameter                                                       | +25°C | -40°C to +85°C | Unit   | Test Conditions/Comments                             |

|-----------------------------------------------------------------|-------|----------------|--------|------------------------------------------------------|

| Off Switch Source Capacitance, C <sub>S (OFF)</sub>             | 11    |                | pF typ |                                                      |

| Off Switch Drain Capacitance, C <sub>D (OFF)</sub>              | 11    |                | pF typ |                                                      |

| On Switch Capacitance, C <sub>D</sub> (ON), C <sub>S</sub> (ON) | 22    |                | pF typ |                                                      |

| POWER REQUIREMENTS                                              |       |                |        | $V_{DD} = +2.75 \text{ V}, V_{SS} = -2.75 \text{ V}$ |

| Positive Power Supply Current, IDD                              | 15    |                | μA typ | Digital inputs = 0 V or V <sub>DD</sub>              |

|                                                                 |       | 25             | μA max |                                                      |

| Negative Power Supply Current, Iss                              | 15    |                | μA typ |                                                      |

|                                                                 |       | 25             | μA max |                                                      |

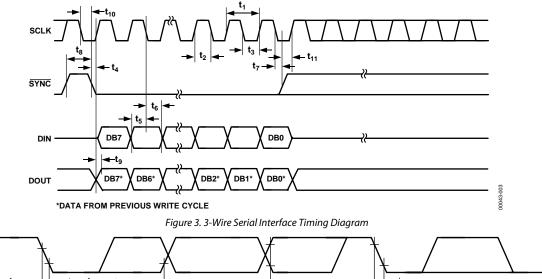

## TIMING CHARACTERISTICS ADG714

$V_{DD}$  = 2.7 V to 5.5 V. All specifications are from -40°C to +85°C, unless otherwise noted. See Figure 3. All input signals are specified with  $t_R$  =  $t_F$  = 5 ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

Table 4.

| Parameter             | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Conditions/Comments                    |

|-----------------------|----------------------------------------------|---------|----------------------------------------|

| f <sub>SCLK</sub>     | 30                                           | MHz max | SCLK cycle frequency                   |

| $t_1$                 | 33                                           | ns min  | SCLK cycle time                        |

| $t_2$                 | 13                                           | ns min  | SCLK high time                         |

| t <sub>3</sub>        | 13                                           | ns min  | SCLK low time                          |

| $t_4$                 | 0                                            | ns min  | SYNC to SCLK rising edge setup time    |

| <b>t</b> <sub>5</sub> | 5                                            | ns min  | Data setup time                        |

| t <sub>6</sub>        | 4.5                                          | ns min  | Data hold time                         |

| $t_7$                 | 0                                            | ns min  | SCLK falling edge to SYNC rising edge  |

| t <sub>8</sub>        | 33                                           | ns min  | Minimum SYNC high time                 |

| $t_9^1$               | 20                                           | ns max  | SCLK rising edge to DOUT valid         |

| t <sub>10</sub>       | 0                                            | ns min  | SCLK falling edge to SYNC falling edge |

| t <sub>11</sub>       | 6                                            | ns max  | SYNC rising edge to SCLK rising edge   |

$<sup>^{1}</sup>$   $C_{L}$  = 20 pF,  $R_{L}$  = 1 k $\!\Omega.$

#### ADG715

$V_{\text{DD}}$  = 2.7 V to 5.5 V. All specifications are from -40°C to +85°C, unless otherwise noted. See Figure 4.

Table 5.

| Parameter             | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Conditions/Comments                                                |

|-----------------------|----------------------------------------------|---------|--------------------------------------------------------------------|

| f <sub>SCL</sub>      | 400                                          | kHz max | SCL clock frequency                                                |

| t <sub>1</sub>        | 2.5                                          | μs min  | SCL cycle time                                                     |

| $t_2$                 | 0.6                                          | μs min  | SCL high time, t <sub>HIGH</sub>                                   |

| t <sub>3</sub>        | 1.3                                          | μs min  | SCL low time, t <sub>LOW</sub>                                     |

| $t_4$                 | 0.6                                          | μs min  | Start/repeated start condition hold time, t <sub>HD, STA</sub>     |

| <b>t</b> <sub>5</sub> | 100                                          | ns min  | Data setup time, t <sub>SU, DAT</sub>                              |

| $t_6^1$               | 0.9                                          | μs max  | Data hold time, t <sub>HD, DAT</sub>                               |

|                       | 0                                            | μs min  |                                                                    |

| <b>t</b> <sub>7</sub> | 0.6                                          | μs min  | Setup time for repeated start, t <sub>SU, STA</sub>                |

| t <sub>8</sub>        | 0.6                                          | μs min  | Stop condition setup time, t <sub>SU, STO</sub>                    |

| t <sub>9</sub>        | 1.3                                          | μs min  | Bus free time between a stop condition and a start condition, tBUF |

| t <sub>10</sub>       | 300                                          | ns max  | Rise time of both SCL and SDA when receiving, t <sub>R</sub>       |

|                       | $20 + 0.1C_b^2$                              | ns min  |                                                                    |

| t <sub>11</sub>       | 250                                          | ns max  | Fall time of SDA when receiving, t₁                                |

| t <sub>11</sub>       | 300                                          | ns max  | Fall time of SDA when transmitting, t <sub>F</sub>                 |

|                       | 0.1C <sub>b</sub> <sup>2</sup>               | ns min  |                                                                    |

| Parameter      | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Conditions/Comments               |

|----------------|----------------------------------------------|--------|-----------------------------------|

| C <sub>b</sub> | 400                                          | pF max | Capacitive load for each bus line |

| $t_{SP}^3$     | 50                                           | ns max | Pulse width of spike suppressed   |

<sup>1</sup> A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the Vill min of the SCL signal) to bridge the undefined region of the falling edge of SCL.  $^2$  C<sub>b</sub> is the total capacitance of one bus line in pF.  $t_R$  and  $t_F$  measured between  $0.3 \times V_{DD}$  and  $0.7 \times V_{DD}$ .

#### **Timing Diagrams**

SDA SCL REPEATED START START STOP CONDITION CONDITION CONDITION

Figure 4. 2-Wire Serial Interface Timing Diagram

<sup>&</sup>lt;sup>3</sup> Input filtering on both the SCL and SDA inputs suppress noise spikes that are less than 50 ns.

#### ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C, unless otherwise noted.

Table 6.

|                                      | 1                                                                       |

|--------------------------------------|-------------------------------------------------------------------------|

| Parameter                            | Rating                                                                  |

| V <sub>DD</sub> to V <sub>SS</sub>   | 7 V                                                                     |

| V <sub>DD</sub> to GND               | −0.3 V to +7 V                                                          |

| V <sub>SS</sub> to GND               | +0.3 V to -3.5 V                                                        |

| Analog Inputs <sup>1</sup>           | $V_{SS}$ $-0.3$ V to $V_{DD}$ $+0.3$ V or 30 mA, whichever occurs first |

| Digital Inputs <sup>1</sup>          | -0.3 V to V <sub>DD</sub> +0.3 V or 30 mA, whichever occurs first       |

| Peak Current, Sx or Dx               | 100 mA (pulsed at 1 ms, 10% duty cycle maximum)                         |

| Continuous Current, Sx or Dx         | 30 mA                                                                   |

| Operating Temperature Range          | -40°C to +85°C                                                          |

| Storage Temperature Range            | −65°C to +150°C                                                         |

| Junction Temperature                 | 150°C                                                                   |

| Lead Temperature, Soldering (10 sec) | 300℃                                                                    |

| Infrared Reflow (20 sec)             | 235°C                                                                   |

<sup>&</sup>lt;sup>1</sup> Overvoltages at the DIN pin, Sx, or Dx are clamped by internal diodes. Limit current to the given maximum ratings.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment.

Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

**Table 7. Thermal Resistance**

| Package Type | $\boldsymbol{\theta}_{JA}$ | θ <sub>JC</sub>    | Unit |

|--------------|----------------------------|--------------------|------|

| RU-24        | 128                        | 42                 | °C/W |

| CP-24-10     | 127.99 <sup>1</sup>        | 15.38 <sup>2</sup> | °C/W |

<sup>&</sup>lt;sup>1</sup>Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board. See JEDEC JESD-51.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Thermal impedance simulated values are based on a cool plate location at the top of the package and measured at the bottom of the exposed paddle of the LFCSP.

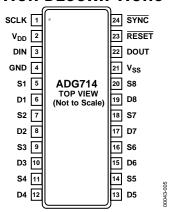

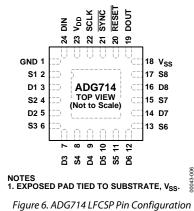

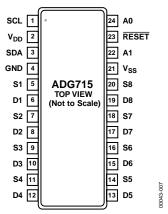

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 5. ADG714 TSSOP Pin Configuration

#### **Table 8. ADG714 Pin Function Descriptions**

| Pin No.                      | Mnemonic | Description                                                                                                                                                                                                                                                                                                       |  |

|------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                            | SCLK     | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. These devices accommodate serial input rates of up to 30 MHz.                                                                                                                                    |  |

| 2                            | $V_{DD}$ | Positive Analog Supply Voltage.                                                                                                                                                                                                                                                                                   |  |

| 3                            | DIN      | Serial Data Input. Data is clocked into the 8-bit input register on the falling edge of the serial clock input.                                                                                                                                                                                                   |  |

| 4                            | GND      | Ground Reference.                                                                                                                                                                                                                                                                                                 |  |

| 5, 7, 9, 11, 14, 16, 18, 20  | Sx       | Source. These pins may be an input or an output.                                                                                                                                                                                                                                                                  |  |

| 6, 8, 10, 12, 13, 15, 17, 19 | Dx       | Drain. These pins may be an input or an output.                                                                                                                                                                                                                                                                   |  |

| 21                           | $V_{SS}$ | Negative Analog Supply Voltage. For single-supply operation, tie this pin to ground.                                                                                                                                                                                                                              |  |

| 22                           | DOUT     | Serial Data Output. This pin allows a number of devices to be daisy-chained. Data is clocked or of the input shift register on the rising edge of SCLK. DOUT is an open-drain output that is pull to the supply with an external pull-up resistor.                                                                |  |

| 23                           | RESET    | Active Low Control Input. This pin clears the input register and turns all switches to the off condition.                                                                                                                                                                                                         |  |

| 24                           | SYNC     | Active Low Control Input. This pin is the frame synchronization signal for the input data. When SYNC goes low, this pin powers on the SCLK and DIN buffers and the input shift register is enabled. Data is transferred on the falling edges of the following clock cycle. Taking SYNC high updates the switches. |  |

**Table 9. ADG714 Pin Function Descriptions**

| Pin No.                    | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                                                 |  |

|----------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                          | GND             | Ground (0 V) Reference.                                                                                                                                                                                                                                                                                                                                                     |  |

| 2, 4, 6, 8, 11, 13, 15, 17 | Sx              | Source. These pins may be an input or an output.                                                                                                                                                                                                                                                                                                                            |  |

| 3, 5, 7, 9, 10, 12, 14, 16 | Dx              | Drain. These pins may be an input or an output.                                                                                                                                                                                                                                                                                                                             |  |

| 18                         | V <sub>SS</sub> | Most Negative Power Supply Potential. In single-supply applications, Vss is connected to ground.                                                                                                                                                                                                                                                                            |  |

| 19                         | DOUT            | Serial Data Output. This pin is used for daisy-chaining a number of these devices together or for reading back data in the shift register for diagnostic purposes. The serial data is transferred on the rising edge of SCLK and is valid on the falling edge of the clock. Pull this open-drain output to the supply with an external resistor.                            |  |

| 20                         | RESET           | RESET. Under normal operation, drive the RESET pin with a 2.7 V to 5 V supply. Pull the pin low (<0.8 V) for a short period (15 ns is sufficient) to complete a hardware reset. All switches are opened and the appropriate registers are cleared to 0. When using the RESET pin to complete a hardware reset, all other SPI pins (SYNC, SCLK, and DIN) must be driven low. |  |

| 21                         | SYNC            | Active Low Control Input. This pin is the frame synchronization signal for the input data. When SYNC goes low, this pin powers on the SCLK and DIN buffers and enables the input shift register. Data is transferred in on the falling edges of the following clock cycle. Taking SYNC high updates the switch condition.                                                   |  |

| 22                         | SCLK            | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data is transferred at rates of up to 50 MHz.                                                                                                                                                                                                              |  |

| 23                         | $V_{DD}$        | Most Positive Power Supply Potential.                                                                                                                                                                                                                                                                                                                                       |  |

| 24                         | DIN             | Serial Data Input. This device has an 8-bit shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                |  |

| EP                         | EP              | Exposed Pad. Exposed pad tied to the substrate, Vss.                                                                                                                                                                                                                                                                                                                        |  |

Figure 7. ADG715 Pin Configuration

**Table 10. ADG715 Pin Function Descriptions**

| Pin No.                      | Mnemonic        | Description                                                                                                                                                                                                                                                                                                            |  |

|------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                            | SCL             | Serial Clock Line. This pin is used in conjunction with the SDA line to clock data into the 8-bit in shift register. Clock rates of up to 400 kbps are accommodated with this 2-wire serial interface.                                                                                                                 |  |

| 2                            | $V_{DD}$        | Positive Analog Supply Voltage.                                                                                                                                                                                                                                                                                        |  |

| 3                            | SDA             | Serial Data Line. This pin is used in conjunction with the SCL line to clock data into the 8-bit input shift register during the write cycle and used to read back one byte of data during the read cycle. SDA is a bidirectional open-drain data line that is pulled to the supply with an external pull-up resistor. |  |

| 4                            | GND             | Ground Reference.                                                                                                                                                                                                                                                                                                      |  |

| 5, 7, 9, 11, 14, 16, 18, 20  | Sx              | Source. These pins may be an input or an output.                                                                                                                                                                                                                                                                       |  |

| 6, 8, 10, 12, 13, 15, 17, 19 | Dx              | Drain. These pins may be an input or an output.                                                                                                                                                                                                                                                                        |  |

| 21                           | V <sub>SS</sub> | Negative Analog Supply Voltage. For single-supply operation, tie this pin to ground.                                                                                                                                                                                                                                   |  |

| 22                           | A1              | Address Input. This pin sets the second LSB of the 7-bit slave address.                                                                                                                                                                                                                                                |  |

| 23                           | RESET           | Active Low Control Input. This pin clears the input register and turns all switches to the off condition.                                                                                                                                                                                                              |  |

| 24                           | A0              | Address Input. This pin sets the LSB of the 7-bit slave address.                                                                                                                                                                                                                                                       |  |

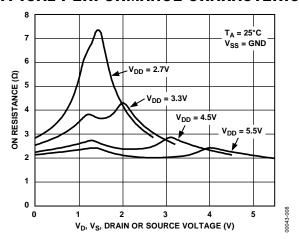

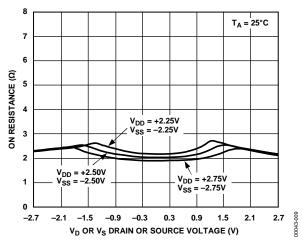

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 8. On Resistance as a Function of  $V_D$  ( $V_S$ ), Single Supply

Figure 9. On Resistance as a Function of  $V_D$  ( $V_S$ ), Dual Supply

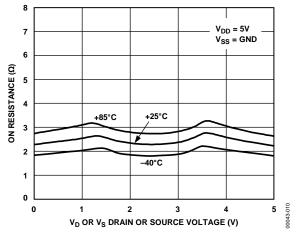

Figure 10. On Resistance as a Function of  $V_D$  ( $V_S$ ) for Different Temperatures,  $V_{DD}$  = 5 V

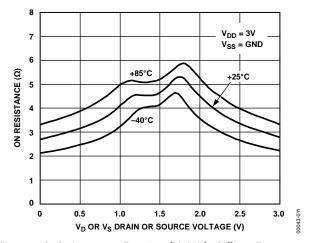

Figure 11. On Resistance as a Function of  $V_D$  ( $V_S$ ) for Different Temperatures,  $V_{DD} = 3~V$

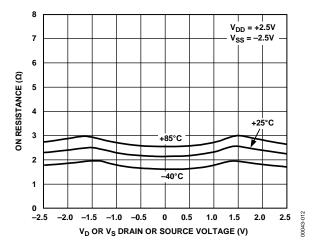

Figure 12. On Resistance as a Function of  $V_D$  ( $V_S$ ) for Different Temperatures, Dual Supply

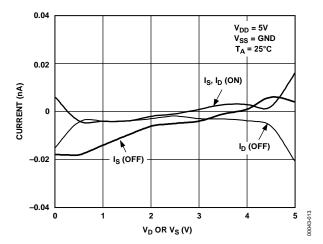

Figure 13. Leakage Currents as a Function of  $V_D$  ( $V_S$ )

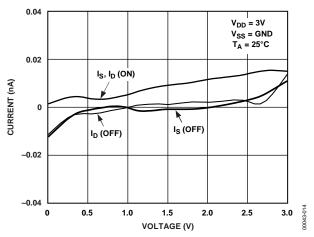

Figure 14. Leakage Currents as a Function of  $V_D$  ( $V_S$ ), Single Supply

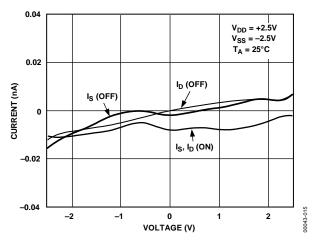

Figure 15. Leakage Currents as a Function of  $V_D$  ( $V_S$ ), Dual Supply

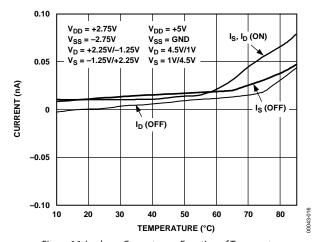

Figure 16. Leakage Currents as a Function of Temperature at ±2.75 V Dual Supply and +5 V Single Supply

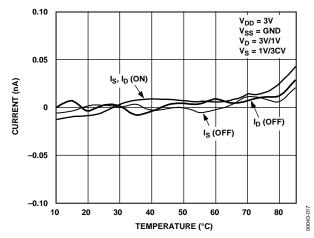

Figure 17. Leakage Currents as a Function of Temperature at 3 V Single Supply

Figure 18. Off Isolation vs. Frequency

Figure 19. On Response vs. Frequency

Figure 20. Crosstalk vs. Frequency

Figure 21. Q<sub>INJ</sub> vs. Source/Drain Voltage

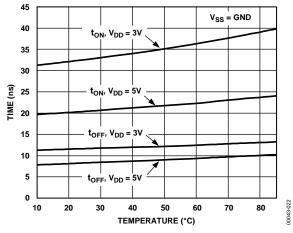

Figure 22. ton/toff Times vs. Temperature for the ADG714

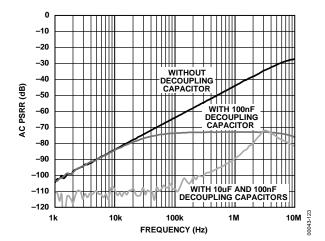

Figure 23. AC Power Supply Rejection Ratio (AC PSRR) vs. Frequency, 5 V Single Supply

#### **TERMINOLOGY**

$V_{DD}$

Most positive power supply potential.

$\mathbf{V}_{ss}$

Most negative power supply in a dual-supply application. In single-supply applications, tie this pin to ground.

$\mathbf{I}_{\mathrm{DD}}$

Positive supply current.

$\mathbf{I}_{ss}$

Negative supply current.

**GND**

Ground (0 V) reference.

Sx

Source terminal. May be an input or an output.

Dx

Drain terminal. May be an input or an output.

Ron

Ohmic resistance between Dx and Sx.

$\Delta R_{ON}$

On resistance match between any two channels, for example,  $R_{\rm ON}$  max -  $R_{\rm ON}$  min.

R<sub>FLAT(ON)</sub>

Flatness is defined as the difference between the maximum and minimum values of on resistance as measured over the specified analog signal range.

Is (OFF)

Source leakage current with the off switch.

I<sub>D</sub> (OFF)

Drain leakage current with the off switch.

$I_{D (ON)}$ ,  $I_{S (ON)}$

Channel leakage current with the on switch.

$V_D, V_S$

Analog voltage on the Dx and Sx terminals.

$C_{s\,(off)}$

Off switch source capacitance.  $C_{S\,(OFF)}$  is measured with reference to ground.

$C_{D (OFF)}$

Off switch drain capacitance.  $C_{D\,(\text{OFF})}$  is measured with reference to ground.

$C_{D (ON)}$ ,  $C_{S (ON)}$

On switch capacitance.  $C_{D (ON)}$ ,  $C_{S (ON)}$  is measured with reference to ground.

$C_{IN}$

Digital input capacitance.

ton

Delay time between loading new data to the shift register and selected switches switching on.

$t_{OFF}$

Delay time between loading new data to the shift register and selected switches switching off.

#### **Off Isolation**

A measure of unwanted signal coupling through an off switch.

#### Crosstalk

A measure of unwanted signal that is coupled through from one channel to another because of parasitic capacitance.

#### **Charge Injection**

A measure of the glitch impulse transferred from the digital input to the analog output during switching.

#### Bandwidth

The frequency at which the output is attenuated by -3 dB.

#### On Response

The frequency response of the on switch.

#### **Insertion Loss**

The loss due to the on resistance of the switch. Insertion loss =  $20 \log_{10}$  (V<sub>OUT</sub> with switch and V<sub>OUT</sub> without switch).

$V_{INL}$

Maximum input voltage for Logic 0.

$V_{INH}$

Minimum input voltage for Logic 1.

IINL, IINH

Input current of the digital input.

Inn

Positive supply current.

#### THEORY OF OPERATION

The ADG714 and ADG715 are serially controlled, octal SPST switches, controlled by either a 2- or 3-wire interface. Each bit of the 8-bit serial word corresponds to one switch of the device. A Logic 1 in the bit position turns the switch on, and a Logic 0 turns the switch off. Each switch is independently controlled by an individual bit, which provides the option of having any, all, or none of the switches on.

When changing the switch conditions, a new 8-bit word is written to the input shift register. Some of the bits may be the same as the previous write cycle because the user may not change the state of some switches. To minimize glitches on the output of these switches, the devices compare the state of switches from the previous write cycle. When the switches are already in the on condition and are required to stay on, there are minimal glitches on the output of the switch.

#### **POWER-ON RESET**

On power-up of the device, all switches are in the off condition, the internal shift register is filled with zeros, and the register remains so until a valid write takes place.

#### **SERIAL INTERFACE**

#### 3-Wire Serial Interface

The ADG714 has a 3-wire serial interface (SYNC, SCLK, and DIN), that is compatible with SPI, QSPI, MICROWIRE interface standards, and most DSP interface standards. Figure 3 shows the timing diagram of a typical write sequence.

Data is written to the 8-bit shift register via DIN under the control of the SYNC and SCLK signals. Data may be written to the shift register in more or less than eight bits. In each case, the shift register retains the last eight written bits.

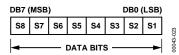

When SYNC goes low, the input shift register is enabled. Data from DIN is clocked into the shift register on the falling edge of SCLK. Each bit of the 8-bit word corresponds to one of the eight switches. Figure 24 shows the contents of the input shift register. Data appears on the DOUT pin on the rising edge of SCLK suitable for daisy chaining, delayed by eight bits. When all eight bits have been written into the shift register, the SYNC line is brought high again. The switches are updated with the new configuration, and the input shift register is disabled. With SYNC held high, the input shift register is disabled so that further data or noise on the DIN line has no effect on the shift register.

Figure 24. Input Shift Register Contents

#### 2-Wire Serial Interface

The ADG715 is controlled via an  $I^2C$ -compatible serial bus. This device is connected to the bus as a slave device (no clock is generated by the switch).

The ADG715 has a 7-bit slave address. The five MSBs are 10010 and the two LSBs are determined by the state of the A0 and A1 pins.

The 2-wire serial bus protocol operates as follows:

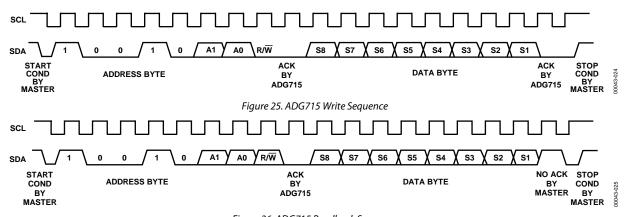

- The master initiates data transfer by establishing a start condition, which is when a high to low transition on the SDA line occurs while SCL is high. The following byte is the address byte, which consists of a 7-bit slave address followed by an R/W bit (this bit determines whether data is read from or written to the slave device).

The slave whose address corresponds to the transmitted address responds by pulling the SDA line low during the ninth clock pulse (the pulling of SDA line is termed the acknowledge bit). At this stage, all other devices on the bus remain idle while the selected device waits for data to be written to or read from its serial register. If the R/W bit is high, the master reads from the slave device. If the R/W bit is low, the master writes to the slave device.

- Data is transmitted over the serial bus in sequences of nine clock pulses (eight data bits followed by an acknowledge bit). The transitions on the SDA line must occur during the low period of SCL and remain stable during the high period of SCL.

- 3. When all data bits are read or written, a stop condition is established by the master. A stop condition is defined as a low to high transition on the SDA line while SCL is high. In write mode, the master pulls the SDA line high during the tenth clock pulse to establish a stop condition. In read mode, the master issues a no acknowledge for the ninth clock pulse, and the SDA line remains high. The master brings the SDA line low before the tenth clock pulse and then high during the tenth clock pulse to establish a stop condition.

See Figure 25 for an ADG715 write sequence.

A repeated write function gives the user the flexibility to update the matrix switch a number of times after addressing the device only once. During the write cycle, each data byte updates the configuration of the switches. For example, after the matrix switch acknowledges its address byte and receives one data byte, the switches update after the data byte. If another data byte is written to the matrix switch while still in the same addressed slave device, this data byte also causes a switch configuration update. Repeating the read of the matrix switch is also allowed.

#### **Input Shift Register**