# CMOS Low Power Dual 2:1 Mux/Demux USB 2.0 (480 Mbps)/USB 1.1 (12 Mbps)

### **Data Sheet**

### FEATURES

USB 2.0 (480 Mbps) and USB 1.1 (12 Mbps) signal switching compliant Tiny 10-lead 1.3 mm × 1.6 mm mini LFCSP package and 12-lead 3 mm × 3 mm LFCSP package 2.7 V to 3.6 V single-supply operation Typical power consumption: <0.1 μW RoHS compliant

### **APPLICATIONS**

USB 2.0 signal switching circuits Cellular phones PDAs MP3 players Battery-powered systems Headphone switching Audio and video signal routing Communications systems

### **GENERAL DESCRIPTION**

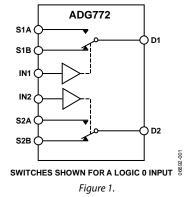

The ADG772 is a low voltage CMOS device that contains two independently selectable single-pole, double throw (SPDT) switches. It is designed as a general-purpose switch and can be used for routing both USB 1.1 and USB 2.0 signals.

This device offers a data rate of 1260 Mbps, making the device suitable for high frequency data switching. Each switch conducts equally well in both directions when on and has an input signal range that extends to the supplies. The ADG772 exhibits break-before-make switching action.

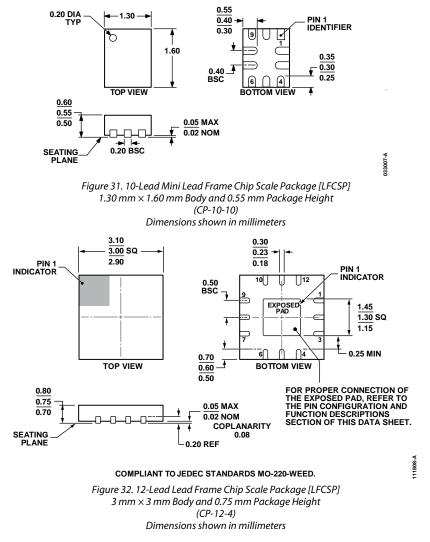

The ADG772 is available in a 12-lead LFCSP and a 10-lead mini LFCSP. These packages make the ADG772 the ideal solution for space-constrained applications.

## **ADG772**

### FUNCTIONAL BLOCK DIAGRAM

### **PRODUCT HIGHLIGHTS**

- 1. 1.6 mm × 1.3 mm mini LFCSP package.

- 2. USB 1.1 (12 Mbps) and USB 2.0 (480 Mbps) compliant.

- 3. Single 2.7 V to 3.6 V operation.

- 4. 1.8 V logic compatible.

- 5. RoHS compliant.

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                 | 1 |

|--------------------------|---|

| Applications             | 1 |

| Functional Block Diagram | 1 |

| General Description      | 1 |

| Product Highlights       | 1 |

| Revision History         | 2 |

| Specifications           | 3 |

| Absolute Maximum Ratings | 4 |

### **REVISION HISTORY**

| 5/16—Rev. B to Rev. C      |   |

|----------------------------|---|

| Changes to Figure 3        | 5 |

| Updated Outline Dimensions | 2 |

| Changes to Ordering Guide  | 2 |

### 4/13—Rev. A to Rev. B

| Added EPAD Notation        | . 5 |

|----------------------------|-----|

| Changes to Figure 10       |     |

| Updated Outline Dimensions |     |

| Changes to Ordering Guide  | 12  |

### 6/08—Rev. 0 to Rev. A

| Changes to Product Highlights                                            | 1 |

|--------------------------------------------------------------------------|---|

| Changes to Input High Voltage, $V_{\ensuremath{\text{INH}}}$ , Parameter | 3 |

### 8/07—Revision 0: Initial Version

| ESD Caution                                 | 4  |

|---------------------------------------------|----|

| Pin Configuration and Function Descriptions | 5  |

| Truth Table                                 | 5  |

| Typical Performance Characteristics         | 6  |

| Test Circuits                               | 9  |

| Terminology                                 | 11 |

| Outline Dimensions                          |    |

| Ordering Guide                              |    |

## **Specifications**

$V_{\rm DD}$  = 2.7 V to 3.6 V, GND = 0 V, unless otherwise noted.

### Table 1.

| Parameter                                         | +25°C | -40°C to +85°C         | Unit     | Test Conditions/Comments                                                              |

|---------------------------------------------------|-------|------------------------|----------|---------------------------------------------------------------------------------------|

| ANALOG SWITCH                                     |       |                        |          |                                                                                       |

| Analog Signal Range                               |       | 0 V to V <sub>DD</sub> | V        |                                                                                       |

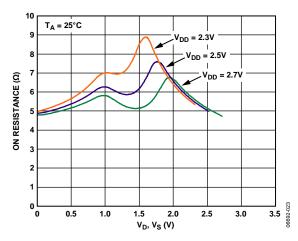

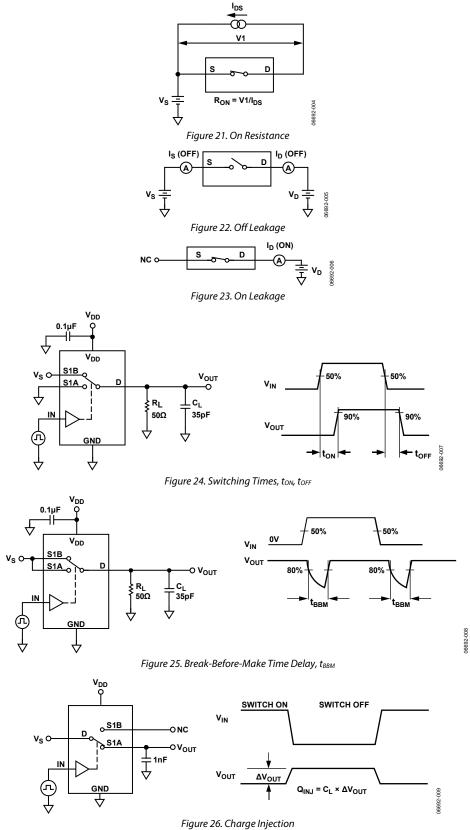

| On-Resistance (R <sub>ON</sub> )                  | 6.7   |                        | Ωtyp     | $V_{DD} = 2.7 V$ , $V_{S} = 0 V$ to $V_{DD}$ , $I_{DS} = 10 m$ A; see Figure 21       |

|                                                   |       | 8.8                    | Ωmax     |                                                                                       |

| On-Resistance Match                               | 0.04  |                        | Ωtyp     | $V_{DD} = 2.7 V$ , $V_{S} = 1.5 V$ , $I_{DS} = 10 mA$                                 |

| Between Channels (ΔR <sub>ON</sub> )              |       | 0.2                    | Ωmax     |                                                                                       |

| On Resistance Flatness (R <sub>FLAT (ON)</sub> )  | 3.3   |                        | Ωtyp     | $V_{DD} = 2.7 V$ , $V_S = 0 V$ to $V_{DD}$ , $I_{DS} = 10 mA$                         |

|                                                   |       | 3.6                    | Ωmax     |                                                                                       |

| LEAKAGE CURRENTS                                  |       |                        |          | V <sub>DD</sub> = 3.6 V                                                               |

| Source Off Leakage Is (Off)                       | ±0.2  |                        | nA typ   | $V_{s} = 0.6 V/3.3 V$ , $V_{D} = 3.3 V/0.6 V$ ; see Figure 22                         |

| Channel On Leakage I <sub>D</sub> , Is (On)       | ±0.2  |                        | nA typ   | $V_s = V_D = 0.6 V$ or 3.3 V; see Figure 23                                           |

| DIGITAL INPUTS                                    |       |                        |          |                                                                                       |

| Input High Voltage, VINH                          |       | 1.35                   | V min    |                                                                                       |

| Input Low Voltage, VINL                           |       | 0.8                    | V max    |                                                                                       |

| Input Current, IINL or IINH                       | 0.005 |                        | μA typ   | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                                |

|                                                   |       | ±0.1                   | μA max   | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                                |

| Digital Input Capacitance, C <sub>IN</sub>        | 2     |                        | pF typ   |                                                                                       |

| DYNAMIC CHARACTERISTICS <sup>1</sup>              |       |                        |          |                                                                                       |

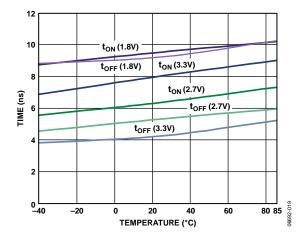

| t <sub>on</sub>                                   | 9     |                        | ns typ   | $R_L = 50 \Omega$ , $C_L = 35 pF$                                                     |

|                                                   | 12.5  | 13.5                   | ns max   | Vs = 2 V; see Figure 24                                                               |

| t <sub>OFF</sub>                                  | 6     |                        | ns typ   | $R_L = 50 \Omega$ , $C_L = 35 pF$                                                     |

|                                                   | 9.5   | 10                     | ns max   | Vs = 2 V; see Figure 24                                                               |

| Propagation Delay                                 | 250   |                        | ps typ   | $R_L = 50 \Omega$ , $C_L = 35 pF$                                                     |

| Propagation Delay Skew, t <sub>skew</sub>         | 20    |                        | ps typ   | $R_L = 50 \Omega$ , $C_L = 35 pF$                                                     |

| Break-Before-Make Time Delay ( $t_{\text{BBM}}$ ) | 5     |                        | ns typ   | $R_L = 50 \Omega$ , $C_L = 35 pF$                                                     |

|                                                   | 3.4   | 2.9                    | ns min   | $V_{S1} = V_{S2} = 2 V$ ; see Figure 25                                               |

| Charge Injection                                  | 0.5   |                        | pC typ   | $V_D = 1.25 V$ , $R_s = 0 \Omega$ , $C_L = 1 nF$ ; see Figure 26                      |

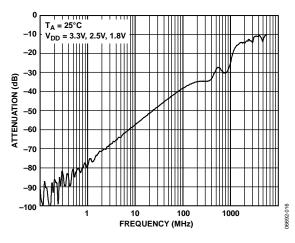

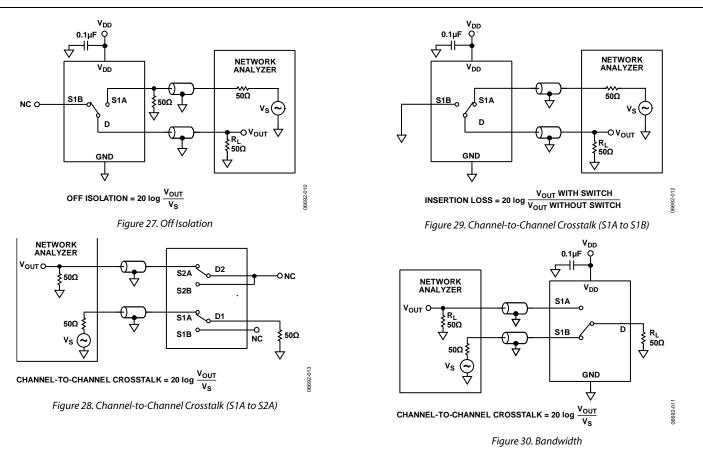

| Off Isolation                                     | 73    |                        | dB typ   | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 27                        |

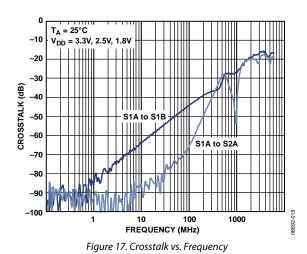

| Channel-to-Channel Crosstalk                      | -90   |                        | dB typ   | S1A to S2A/S1B to S2B; $R_L = 50 \Omega$ , $C_L = 5 pF$ ,<br>f = 1 MHz; see Figure 28 |

|                                                   | -80   |                        | dB typ   | S1A to S1B/S2A to S2B; $R_L = 50 \Omega$ , $C_L = 5 pF$ ,<br>f = 1 MHz; see Figure 29 |

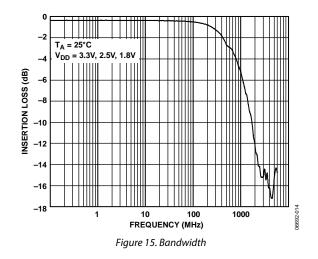

| –3 dB Bandwidth                                   | 630   |                        | MHz typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 30                                      |

| Data Rate                                         | 1260  |                        | Mbps typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 30                                      |

| C <sub>s</sub> (Off)                              | 2.4   |                        | pF typ   |                                                                                       |

| C <sub>D</sub> , C <sub>s</sub> (On)              | 6.9   |                        | pF typ   |                                                                                       |

| POWER REQUIREMENTS                                |       | 1                      |          | V <sub>DD</sub> = 3.6 V                                                               |

| I <sub>DD</sub>                                   | 0.006 |                        | μA typ   | Digital inputs = 0 V or 3.6 V                                                         |

|                                                   |       | 1                      | µA max   |                                                                                       |

<sup>1</sup> Guaranteed by design, not subject to production test.

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 2.

| Parameter                                                  | Rating                                                                |  |  |  |

|------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| V <sub>DD</sub> to GND                                     | -0.3 V to +4.6 V                                                      |  |  |  |

| Analog Inputs, <sup>1</sup> Digital Inputs                 | –0.3 V to V <sub>DD</sub> + 0.3 V or<br>10 mA, whichever occurs first |  |  |  |

| Peak Current, Pin S1A, Pin S2A,<br>Pin D1, or Pin D2       | 100 mA (pulsed at 1 ms, 10%<br>duty cycle max)                        |  |  |  |

| Continuous Current, Pin S1A,<br>Pin S2A, Pin D1, or Pin D2 | 30 mA                                                                 |  |  |  |

| Operating Temperature<br>Industrial Range (B Version)      | –40°C to +85°C                                                        |  |  |  |

| Storage Temperature Range                                  | –65°C to +150°C                                                       |  |  |  |

| Junction Temperature                                       | 150°C                                                                 |  |  |  |

| θ <sub>JA</sub> Thermal Impedance<br>(4-Layer Board)       |                                                                       |  |  |  |

| 10-Lead Mini LFCSP                                         | 131.6°C/W                                                             |  |  |  |

| 12-Lead LFCSP                                              | 61°C/W                                                                |  |  |  |

| Pb-Free Temperature,<br>Soldering, IR Reflow               |                                                                       |  |  |  |

| Peak Temperature                                           | 260(+0/-5)°C                                                          |  |  |  |

| Time at Peak Temperature                                   | 10 sec to 40 sec                                                      |  |  |  |

<sup>1</sup> Overvoltages at the IN1, IN2, S1A, S2A, D1, or D2 pin are clamped by internal diodes. Current must be limited to the maximum ratings given.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

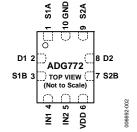

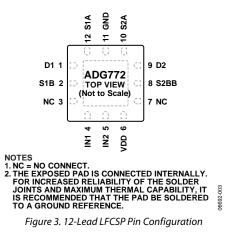

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. 10-Lead Mini LFCSP Pin Configuration

#### **Table 3. Pin Function Descriptions**

| Pin No.                          |      |          |                                                                                                                                                                                                        |  |  |

|----------------------------------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 10-Lead Mini LFCSP 12-Lead LFCSP |      | Mnemonic | Description                                                                                                                                                                                            |  |  |

| 1                                | 12   | S1A      | Source Terminal. Can be an input or an output.                                                                                                                                                         |  |  |

| 2                                | 1    | D1       | Drain Terminal. Can be an input or an output.                                                                                                                                                          |  |  |

| 3                                | 2    | S1B      | Source Terminal. Can be an input or an output.                                                                                                                                                         |  |  |

| 4                                | 4    | IN1      | Logic Control Input. This pin controls Switch S1A and Switch S1B to D1.                                                                                                                                |  |  |

| 5                                | 5    | IN2      | Login Control Input. This pin controls Switch S2A and Switch S2B to D2.                                                                                                                                |  |  |

| 6                                | 6    | VDD      | Most Positive Power Supply Potential.                                                                                                                                                                  |  |  |

| 7                                | 8    | S2B      | Source Terminal. Can be an input or an output.                                                                                                                                                         |  |  |

| 8                                | 9    | D2       | Drain Terminal. Can be an input or an output.                                                                                                                                                          |  |  |

| 9                                | 10   | S2A      | Source Terminal. Can be an input or an output.                                                                                                                                                         |  |  |

| 10                               | 11   | GND      | Ground (0 V) Reference.                                                                                                                                                                                |  |  |

| Not applicable                   | 3, 7 | NC       | No Connect.                                                                                                                                                                                            |  |  |

| Not applicable                   | 13   | EPAD     | Exposed Pad. The exposed pad is connected internally. For increased reliability of the solder joints and maximum thermal capability, it is recommended that the pad be soldered to a ground reference. |  |  |

### **TRUTH TABLE**

Table 4.

| Logic (IN1 or IN2) | Switch A (S1A or S2A) | Switch B (S1B or S2B) |

|--------------------|-----------------------|-----------------------|

| 0                  | Off                   | On                    |

| 1                  | On                    | Off                   |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

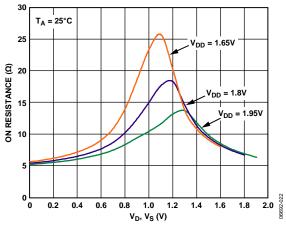

Figure 4. On Resistance vs.  $V_{Dr}$ ,  $V_{S}$ ;  $V_{DD}$  = 3.3 V ± 0.3 V

Figure 5. On Resistance vs.  $V_D$ ,  $V_S$ ;  $V_{DD} = 2.5 V \pm 0.2 V$

Figure 6. On Resistance vs.  $V_D$ ,  $V_S$ ;  $V_{DD} = 1.8 V \pm 0.15 V$

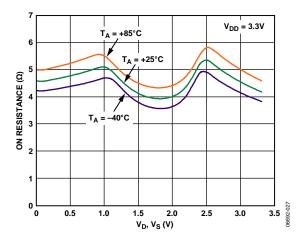

Figure 7. On Resistance vs.  $V_D$ ,  $V_S$  for Different Temperatures;  $V_{DD} = 3.3 V$

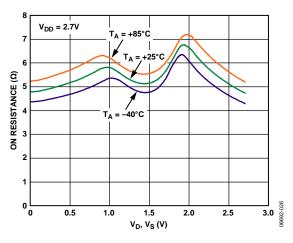

Figure 8. On Resistance vs.  $V_D$ ,  $V_S$  for Different Temperatures;  $V_{DD} = 2.7 V$

Figure 9. On Resistance vs.  $V_D$ ,  $V_S$  for Different Temperatures;  $V_{DD} = 1.8 V$

## Data Sheet

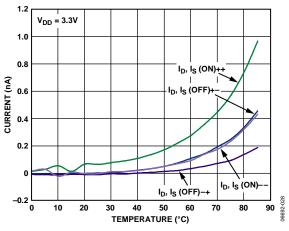

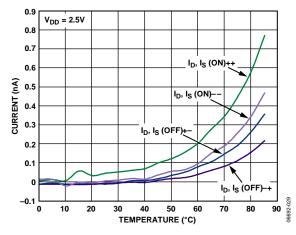

Figure 10. Leakage Current vs. Temperature; V<sub>DD</sub> = 3.3 V

Figure 11. Leakage Current vs. Temperature;  $V_{DD} = 2.5 V$

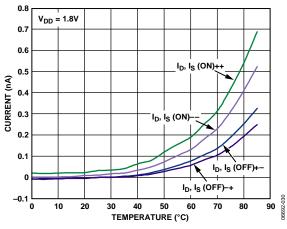

Figure 12. Leakage Current vs. Temperature; V<sub>DD</sub> = 1.8 V

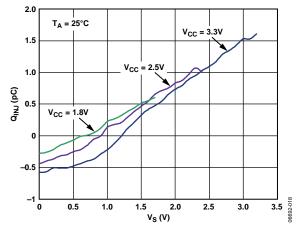

Figure 13. Charge Injection vs. Source Voltage

## ADG772

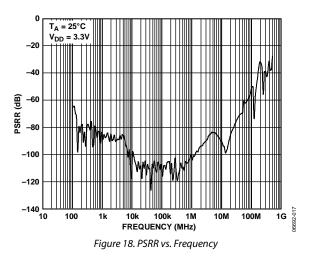

Figure 16. Off Isolation vs. Frequency

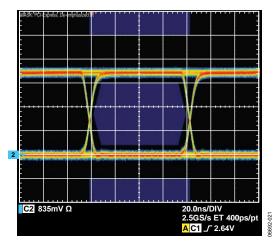

Figure 19. USB 1.1 Eye Diagram

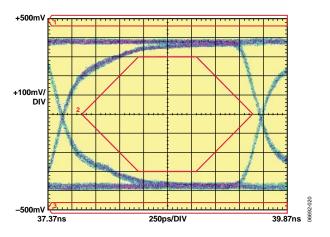

Figure 20. USB 2.0 Eye Diagram

## **TEST CIRCUITS**

## ADG772

## TERMINOLOGY

$I_{\rm DD}$

Positive supply current.

V<sub>D</sub>,V<sub>s</sub> Analog voltage on Terminal D and Terminal S.

**R**<sub>ON</sub> Ohmic resistance between Terminal D and Terminal S.

**R**<sub>FLAT</sub> (**On**) The difference between the maximum and minimum values of on resistance as measured on the switch.

$\label{eq:dron} \Delta R_{\text{ON}}$  On resistance match between any two channels.

Is (Off) Source leakage current with the switch off.

I<sub>D</sub> (Off) Drain leakage current with the switch off.

I<sub>D</sub>, I<sub>S</sub> (On) Channel leakage current with the switch on.

V<sub>INL</sub> Maximum input voltage for Logic 0.

$\mathbf{V}_{\text{INH}}$ Minimum input voltage for Logic 1.

$I_{INL}, I_{INH}$  Input current of the digital input.

C<sub>s</sub> (Off) Off switch source capacitance. Measured with reference to ground.

$C_D$  (Off) Off switch drain capacitance. Measured with reference to ground.

C<sub>D</sub>, C<sub>s</sub> (On) On switch capacitance. Measured with reference to ground.  $C_{IN}$

Digital input capacitance.

ton

Delay time between the 50% and 90% points of the digital input and switch on condition.

$t_{\rm OFF}$  Delay time between the 50% and 90% points of the digital input and switch off condition.

**t**<sub>BBM</sub> On or off time measured between the 80% points of both switches when switching from one to another.

**Charge Injection** Measure of the glitch impulse transferred from the digital input to the analog output during on/off switching.

**Off Isolation** Measure of unwanted signal coupling through an off switch.

**Crosstalk** Measure of unwanted signal that is coupled from one channel to another as a result of parasitic capacitance.

**–3 dB Bandwidth** Frequency at which the output is attenuated by 3 dB.

**On Response** Frequency response of the on switch.

**Insertion Loss** The loss due to the on resistance of the switch.

**THD + N** Ratio of the harmonics amplitude plus noise of a signal to the fundamental.

T<sub>skew</sub>

The measure of the variation in propagation delay between each channel.

## ADG772

### **OUTLINE DIMENSIONS**

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                | Package Option | Branding |

|--------------------|-------------------|----------------------------------------------------|----------------|----------|

| ADG772BCPZ-1REEL   | -40°C to +85°C    | 12-Lead Lead Frame Chip Scale Package [LFCSP]      | CP-12-4        | S2P      |

| ADG772BCPZ-REEL7   | -40°C to +85°C    | 10-Lead Mini Lead Frame Chip Scale Package [LFCSP] | CP-10-10       | В        |

| EVAL-ADG772EBZ     | -40°C to +85°C    | Evaluation Board                                   |                |          |

<sup>1</sup> Z = RoHS Compliant Part.

©2007–2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D06692-0-5/16(C)

www.analog.com

Rev. C | Page 12 of 12

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Multiplexer Switch ICs category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

NLV74HC4066ADR2G HEF4051BP MC74HC4067ADTG DG508AAK/883B NLV14051BDG 016400E PI3V512QE 7705201EC PI2SSD3212NCE NLAS3257CMX2TCG PI3DBS12412AZLEX PI3V512QEX PI3DBS16213ZLEX PI3DBS16415ZHEX MUX36S16IRSNR 74LVC1G3157GM-Q10X TC7W53FK,LF CD4053BM96 MC74HC4053ADWR2G SN74LV4051APWR HEF4053BT.653 ADG5408BRUZ-REEL7 ADG1404YRUZ-REEL7 ADG1208YRZ-REEL7 MAX4704EUB+T ADG1406BRUZ-REEL7 LTC4305IDHD#PBF CD4053BPWRG4 74HC4053D.653 74HCT4052PW.118 74LVC2G53DP.125 74HC4052DB.112 74HC4052PW.112 74HC4053DB.112 74HC4067DB.112 74HC4351DB.112 74HCT4052D.112 74HCT4052DB.112 74HCT4053DB.112 74HCT4067D.112 74HC4053DB.112 74HC4067DB.112 FSA1256L8X\_F113 PI5V330QE PI5V331QE 5962-8771601EA 5962-87716022A ADG5249FBRUZ ADG1438BRUZ AD7506JNZ