# Secondary-Side Controller with Current Share and Housekeeping

# ADM1041

#### **PRODUCT FEATURES**

Digital calibration via internal EEPROM Supports SSI specification Comprehensive fault detection Reduced component count on secondary side Standalone or microcontroller control

#### SECONDARY-SIDE FEATURES

Generates error signal for primary-side PWM Output voltage adjustment and margining Current sharing Current limit adjustment OrFET control Programmable soft-start slew rate Standalone or microcontroller operation Differential load voltage sense AC mains undervoltage detection (ac sense) Overvoltage protection

## INTERFACE AND INTERNAL FEATURES

SMBus interface (I<sup>2</sup>C compatible) Low-drift precision 2.5 V reference Voltage error amplifier Differential current sense Sense resistor or current transformer option Overvoltage protection Undervoltage protection Overcurrent protection Overtemperature protection Start-up undervoltage blanking Programmable digital debounce and delays 352-byte EEPROM available for field data 160-byte EEPROM for calibration Ground continuity monitoring

#### **APPLICATIONS**

Network servers Web servers Power supply control

#### Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703

© 2004 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Specifications                                |

|-----------------------------------------------|

| Absolute Maximum Ratings                      |

| ESD Caution                                   |

| Pin Configuration and Function Descriptions14 |

| Terminology                                   |

| Theory of Operation                           |

| Power Management                              |

| Gain Trimming and Configuration19             |

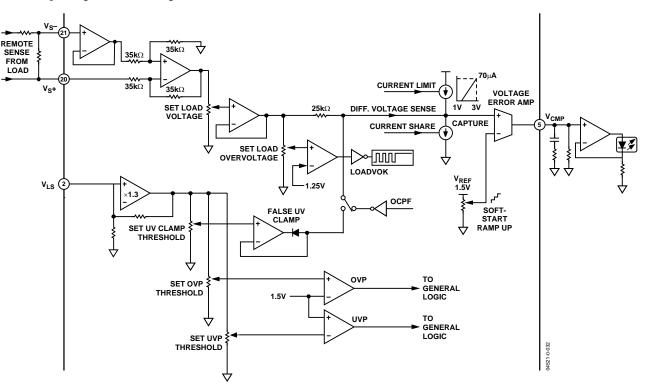

| Differential Remote Sense Amplifier           |

| Set Load Voltage                              |

| Load Overvoltage (OV)                         |

| Local Voltage Sense                           |

| Local OverVoltage Protection (OVP)            |

| Local UnderVoltage Protection (UVP)           |

| False UV Clamp                                |

| Voltage Error Amplifier                       |

| Main Voltage Reference                        |

| Current Sense Amplifier21                     |

| Current Sensing                               |

| Current Transformer Input                     |

| Current Sense Calibration22                   |

| Current Limit Error Amplifier22               |

| Overcurrent Protection                        |

| Current Share                                 |

| Current Share Offset                          |

| I <sub>share</sub> Drive Amplifier24          |

| Differential Sense Amplifier24                |

| I <sub>share</sub> Error Amplifier            |

| Ishare Clamp24                                |

| Share_ok Detector                             |

| Pulse/AC <sub>SENSE</sub> 2                   |

|    | Pulse                              | 27 |

|----|------------------------------------|----|

|    | AC <sub>SENSE</sub>                | 27 |

|    | OrFET Gate Drive                   | 28 |

| 0  | scillator and Timing Generators    | 30 |

|    | Logic I/O and Monitor Pins         | 30 |

|    | SMBus Serial Port                  | 33 |

|    | Microprocessor Support             | 33 |

|    | Broadcasting                       | 34 |

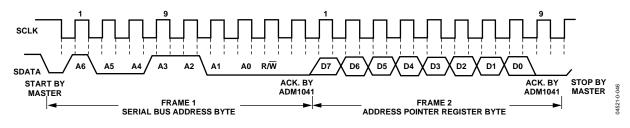

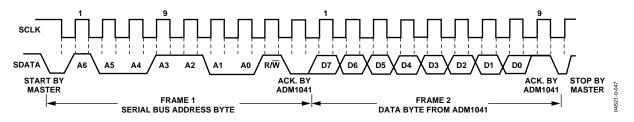

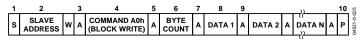

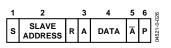

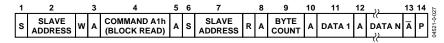

|    | SMBus Serial Interface             | 34 |

|    | General SMBus Timing               | 34 |

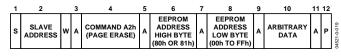

|    | SMBus Protocols for RAM and EEPROM | 36 |

|    | SMBus Read Operations              | 38 |

|    | SMBus Alert Response Address (ARA) | 39 |

|    | Support for SMBus 1.1              | 39 |

|    | Layout Considerations              | 39 |

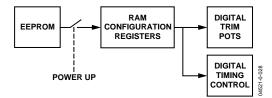

|    | Power-Up Auto-Configuration        | 39 |

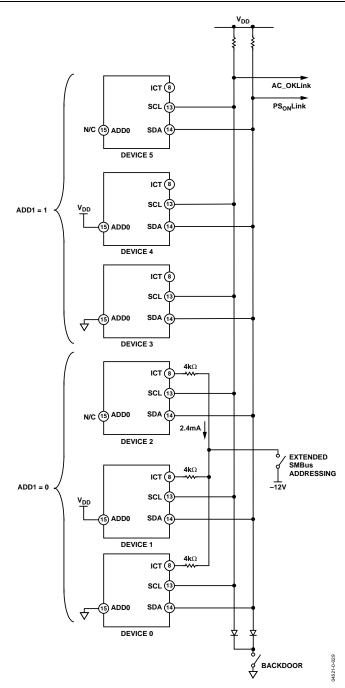

|    | Extended SMBus Addressing          | 40 |

|    | Backdoor Access                    | 40 |

| R  | egister Listing                    | 41 |

| D  | etailed Register Descriptions      | 42 |

|    | Manufacturing Data                 | 51 |

| М  | licroprocessor Support             | 52 |

| Tı | rim Table                          | 54 |

| Aj | ppendix A—Configuration Table      | 55 |

| Aj | ppendix B—Test Name Table          | 61 |

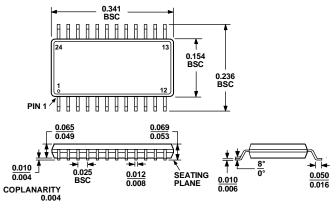

| 0  | utline Dimensions                  | 64 |

|    | Ordering Guide                     | 64 |

|    |                                    |    |

## **REVISION HISTORY**

3/04-Revision Sp0: Initial Version5/04-Changed from Rev. Sp0 to Rev. A

#### **GENERAL DESCRIPTION**

The ADM1041 is a secondary-side and management IC specifically designed to minimize external component counts and to eliminate the need for manual calibration or adjustment on the secondary-side controller. The principle application of this IC is to provide voltage control, current share, and housekeeping functions for single output in N+1 server power supplies.

The ADM1041 is manufactured with a 5 V CMOS process and combines digital and analog circuitry. An internal EEPROM provides added flexibility in the trimming of timing and voltage and selection of various functions. Programming is done via an SMBus serial port that also allows communication capability with a microprocessor or microcontroller.

The usual configuration using this IC is on a one per output basis. Outputs from the IC can be wire-ORed together or bused in parallel and read by a microprocessor. A key feature on this IC is support for an OrFET circuit when higher efficiency or power density is required.

#### SAMPLE APPLICATION CIRCUIT DESCRIPTION

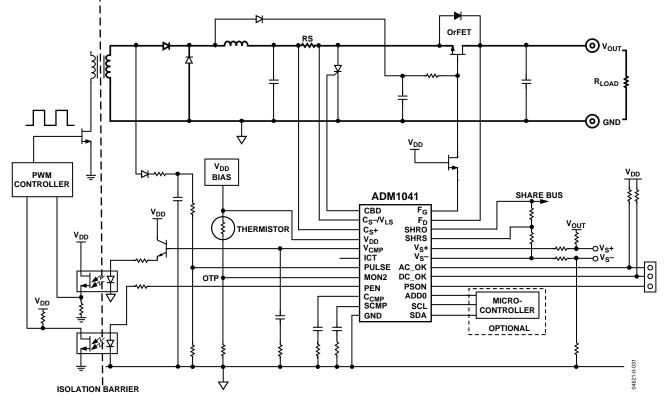

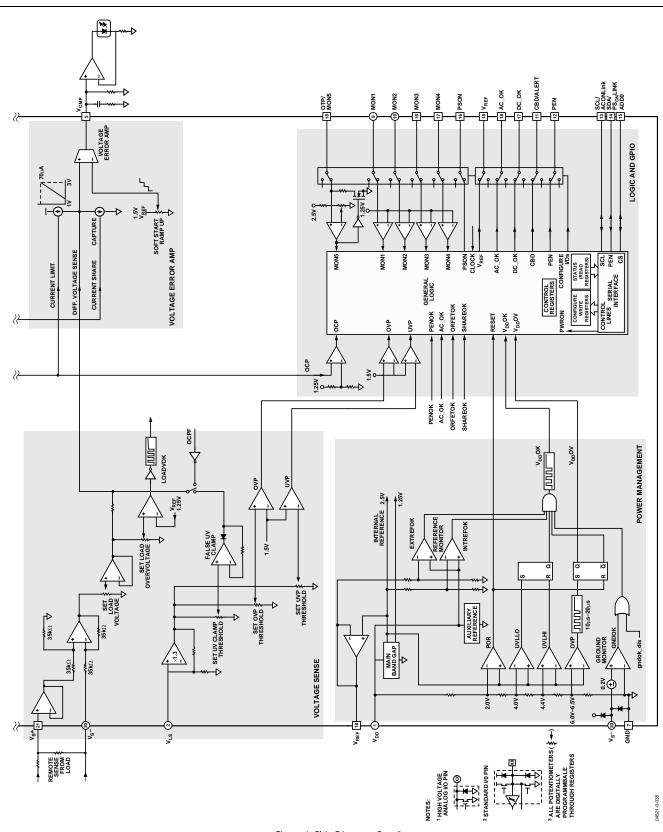

Figure 1 shows a sample application circuit using the ADM1041. The primary side is not detailed and the focus is on the secondary side of the power supply.

The ADM1041 controls the output voltage from the power supply to the designed programmed value. This programmed value is determined during power supply design and is digitally adjusted via the serial interface. Digital adjustment of the current sense and current limit is also calibrated via the serial interface, as are all of the internal timing specifications.

The control loop consists of a number of elements, notably the inputs to the loop and the output of the loop. The ADM1041 takes the loop inputs and determines what, if any, adjustments

are needed to maintain a stable output. To maintain a stable loop, the ADM1041 uses three main inputs:

- Remote voltage sense

- Load current sense

- Current sharing information

In this example, a resistor divider senses the output current as a voltage drop across a sense resistor (RS) and feeds a portion into the ADM1041. Remote local voltage sense is monitored via  $V_{s+}$  and  $V_{s-}$  pins. Finally, current sharing information is fed back via the share bus. These three elements are summed together to generate a control signal ( $V_{CMP}$ ), which closes the loop via an optocoupler to the primary side PWM controller.

Another key feature of the ADM1041 is its control of an OrFET. The OrFET causes lower power dissipation across the ORing diode. The main function of the OrFET is to disconnect the power supply from the load in the event of a fault occurring during steady state operation, for example, if a filter capacitor or rectifier fails and causes a short. This eliminates the risk of bringing down the load voltage that is supplied by the redundant configuration of other power supplies. In the case of a short, a reverse voltage is generated across the OrFET. This reverse voltage is detected by the ADM1041 and the OrFET is shut down via the F<sub>G</sub> pin. This intervention prevents any interruption on the power supply bus. The ADM1041 can then be interrogated via the serial interface to determine why the power supply has shut down.

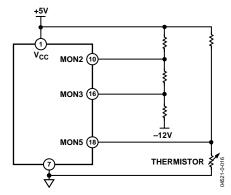

This application circuit also demonstrates how temperature can be monitored within a power supply. A thermistor is connected between the  $V_{DD}$  and MON2 pins. The thermistor's voltage varies with temperature. The MON2 input can be programmed to trip a flag at a voltage corresponding to an overheating power supply. The resulting action may be to turn on an additional cooling fan to help regulate the temperature within the power supply.

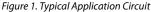

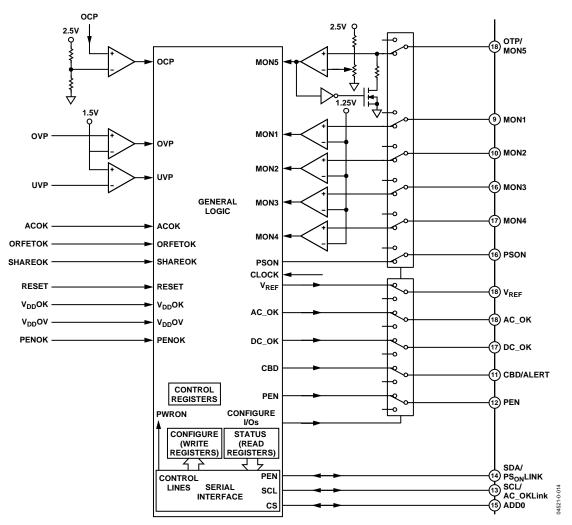

Figure 2. Application Block Diagram

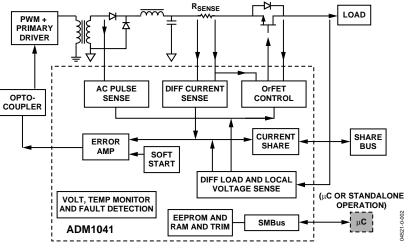

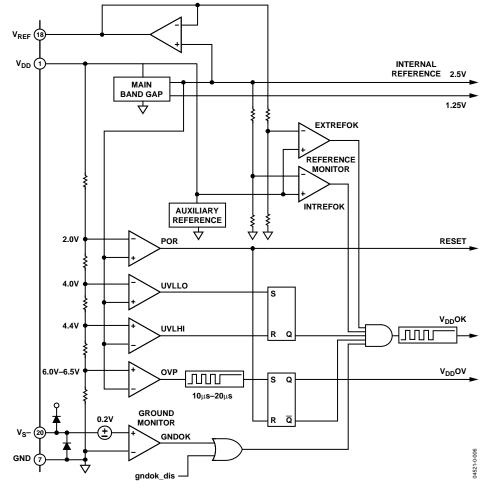

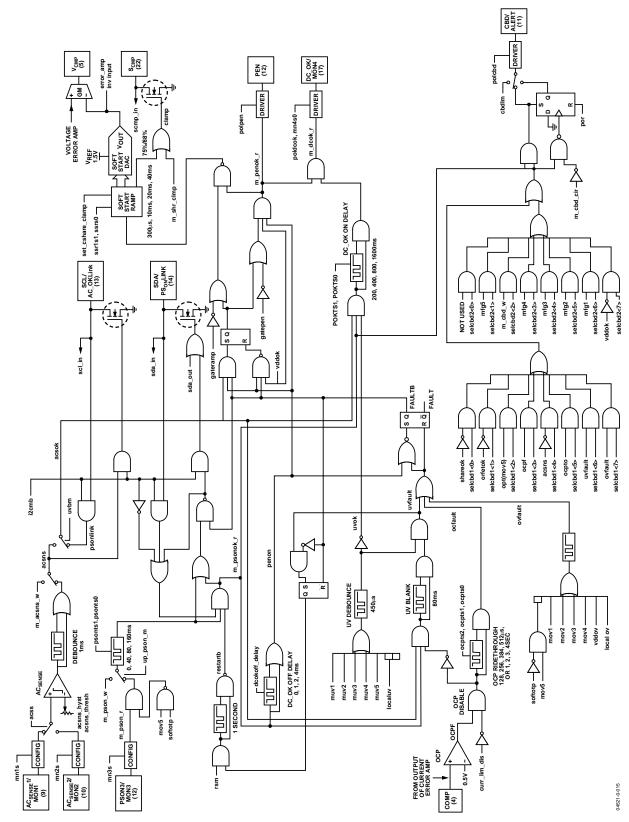

Figure 3. Chip Diagram, Part 1

# **SPECIFICATIONS**

$T_{\rm A}$  = –40 to +85°C,  $V_{\rm DD}$  = 5 V  $\pm$  10%, unless otherwise noted.

#### Table 1.

| Parameter                                                        | Min  | Тур        | Max                 | Unit    | <b>Test Conditions/Comments</b>                                         |

|------------------------------------------------------------------|------|------------|---------------------|---------|-------------------------------------------------------------------------|

| SUPPLIES                                                         |      |            |                     |         |                                                                         |

| V <sub>DD</sub>                                                  | 4.5  | 5.0        | 5.5                 | V       |                                                                         |

| I <sub>DD</sub> , Current Consumption                            |      | 6          | 10                  | mA      |                                                                         |

| Peak I <sub>DD</sub> , during EEPROM Erase Cycle <sup>1, 2</sup> |      |            | 40                  | mA      |                                                                         |

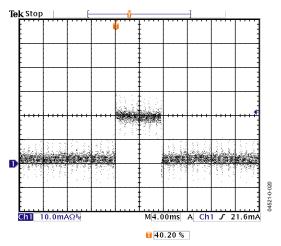

|                                                                  |      |            |                     |         | See Figure 9.                                                           |

| Start-Up Threshold                                               | 4    | 4.3        | 4.5                 | v       |                                                                         |

| Stop Threshold                                                   | 3.7  | 4          | 4.2                 | V       |                                                                         |

| Hysteresis                                                       |      | 0.3        |                     | V       |                                                                         |

| VREF, 2.5 VREFOUT                                                |      |            |                     |         | Reg 0Fh[4:2] = 111. See Table 24.                                       |

| Output Voltage                                                   | 2.49 | 2.50       | 2.51                | v       | $I_{REF} = 1 \text{ mA}, T_A = 25^{\circ}\text{C}$                      |

| Line Regulation                                                  | -5   | 0          | +5                  | mV      | $4.5 V \le V_{DD} \le 5.5 V$                                            |

| Load Regulation                                                  | -5   | 0          | +5                  | mV      | $0 \text{ mA} \le I_{\text{REF}} \le 2 \text{ mA}$                      |

| Temperature Stability <sup>2</sup>                               | 5    | ±100       | 15                  | ppm/°C  | $I_{\text{REF}} = 1 \text{ mA}$                                         |

| Long-Term Stability <sup>2</sup>                                 |      | ±5         |                     | mV      | Over 1,000 hr, $T_J = 125^{\circ}C$                                     |

| Current Limit                                                    |      | 10         | 20                  | mA      | $V_{REF} = 2.4 V$                                                       |

| Output Resistance <sup>2</sup>                                   |      | 0.5        |                     | Ω       |                                                                         |

| Load Capacitance                                                 |      | 1          |                     | nF      | Recommended for stability                                               |

| Ripple Due to Autozero <sup>2</sup>                              |      | ±5         |                     | mV p-p  | V <sub>REF</sub> refreshed at 30 kHz                                    |

| POWER BLOCK PROTECTION                                           |      | <u>_</u> J |                     | mpp     |                                                                         |

| V <sub>DD</sub> Overvoltage                                      | 5.8  | 6.2        | 6.5                 | v       |                                                                         |

| $V_{DD}$ Overvoltage Debounce                                    | 10   | 0.2        | 20                  | μs      | Latching                                                                |

| V <sub>REF</sub> Overvoltage                                     | 10   | 2.9        | 20                  | V       | Internal                                                                |

| V <sub>REF</sub> OVERVOITage                                     |      | 2.9        |                     | V       | External                                                                |

| Open Ground                                                      | 0.1  | 0.2        | 0.35                | V       | $V_{GND}$ positive with respect to $V_{s-}$                             |

| Debounce                                                         | 100  | 0.2        | 200                 |         | V <sub>DD</sub> OK                                                      |

| POWER-ON RESET                                                   | 100  |            | 200                 | μs      | VDDOR                                                                   |

| DC Level                                                         | 1.5  | 2.2        | 2.75                | v       | V ricing                                                                |

| DIFFERENTIAL LOAD VOLTAGE SENSE INPUT,                           | 1.5  | 2.2        | 2.75                | v       | $V_{DD}$ rising<br>See Figure 6. $V_{NOM} = (V_{S} + - V_{S} -)$        |

| $(V_{s-}, V_{s+})$                                               |      |            |                     |         | -                                                                       |

|                                                                  |      |            | 0.5                 | v       | V <sub>NOM</sub> is typically 2 V                                       |

| Vs- Input Voltage                                                |      |            |                     |         | Voltage on Pin 20                                                       |

| Vs+ Input Voltage                                                |      | 25         | V <sub>DD</sub> – 2 | V       | Voltage on Pin 21                                                       |

| Vs– Input Resistance                                             | 500  | 35         |                     | kΩ      |                                                                         |

| Vs+Input Resistance                                              | 500  | 17. 22     |                     | kΩ      |                                                                         |

| V <sub>NOM</sub> Adjustment Range                                |      | 1.7 to 2.3 |                     | V       |                                                                         |

| Set Load Voltage Trim Step                                       |      | 0.10 to 0. |                     | %       | $1.7 \text{ V} \le \text{V}_{\text{NOM}} \le 2.3 \text{ V} \text{ typ}$ |

|                                                                  |      | 1.74 -> 3  | .18                 | mV      | 8 bits, 255 steps                                                       |

|                                                                  |      | 10         | •                   | <i></i> | Reg 19h[7:0]. See Table 34                                              |

| Set Load Overvoltage Trim Range                                  |      | 105 to 12  | 0                   | %       | $1.7 \text{ V} \le \text{V}_{\text{NOM}} \le 2.3 \text{ V} \text{ min}$ |

| Set Load Overvoltage Trim Step                                   |      | 0.09       |                     | %       | 8 bits, 255 step/s                                                      |

|                                                                  |      | 1.6        |                     | mV      | Reg 08h[7:0]. See Table 17.                                             |

|                                                                  |      |            |                     |         | $V_{s}$ + = 2.24 V                                                      |

| Recover from Load OV False to $F_{G}$ True                       |      | 100        |                     | μs      | Reg 03h[1:0] = 00. See Table 12.                                        |

|                                                                  |      | 200        |                     | μs      | Reg 03h[1:0] = 01. See Table 12.                                        |

|                                                                  |      | 300        |                     | μs      | Reg 03h[1:0] = 10. See Table 12.                                        |

|                                                                  |      | 400        |                     | μs      | Reg 03h[1:0] = 11. See Table 12.                                        |

| Operate Time from Load OV to F <sub>G</sub> False                |      | 2          |                     | μs      |                                                                         |

| Parameter                                                        | Min  | Тур      | Max                | Unit  | <b>Test Conditions/Comments</b>                   |

|------------------------------------------------------------------|------|----------|--------------------|-------|---------------------------------------------------|

| LOCAL VOLTAGE SENSE, VLs,<br>AND FALSE UV CLAMP                  |      |          |                    |       | See Figure 9.                                     |

| Input Voltage Range <sup>3</sup>                                 |      | 2.3      | V <sub>DD</sub> -2 | V     | Set by external resistor divider.                 |

| Stage Gain                                                       |      | 1.3      |                    |       | At $V_{LS} = 1.8 V$                               |

| False UV Clamp, $V_{LS}$ , Input Voltage Nominal, and Trim Range | 1.3  | 1.85     | 2.1                | V     |                                                   |

| Clamp Trim Step                                                  |      | 0.2      |                    | %     | VRANGE                                            |

| Clamp Trim Step                                                  |      | 3.1      |                    | mV    | 8 bits, 255 steps, Reg 18h[7:0].<br>See Table 33. |

| Local Overvoltage                                                | 1.9  | 2.4      | 2.85               | V     |                                                   |

| Nominal and Trim Range                                           |      |          |                    |       |                                                   |

| OV Trim Step                                                     |      | 0.15     |                    | %     | VRANGE                                            |

| OV Trim Step                                                     |      | 3.7      |                    | mV    | 8 bits, 255 steps Reg 0Ah[7:0].<br>See Table 33.  |

| Noise Filter, for OVP Function Only                              | 5    |          | 25                 | μs    |                                                   |

| Local Undervoltage                                               | 1.3  | 1.7      | 2.1                | V     |                                                   |

| Nominal and Trim Range                                           |      |          |                    |       |                                                   |

| UV Trim Step                                                     |      | 0.18     |                    | %     | V <sub>RANGE</sub>                                |

| UV Trim Step                                                     |      | 3.1      |                    | mV    | 8 bits, 255 steps, Reg 09h[7:0].<br>See Table 18. |

| Noise Filter, for UVP Function Only                              | 300  |          | 600                | μs    |                                                   |

| VOLTAGE ERROR AMPLIFIER, V <sub>CMP</sub>                        |      |          |                    |       | See Figure 14.                                    |

| Reference Voltage VREF_SOFT_START                                | 1.49 |          | 1.51               | V     | $T_A = 25^{\circ}C$                               |

| Temperature Stability <sup>2</sup>                               |      | ±100     |                    | μV/°C | $-40^{\circ}C \le T_A \le 85^{\circ}C$            |

| Long-Term Voltage Stability <sup>2</sup>                         |      | ±0.2     |                    | %     | Over 1,000 hr, TJ = 125°C                         |

| Soft-start Period Range                                          | 0    |          | 40                 | ms    | Ramp is 7 bit, 127 steps                          |

| Set Soft-start Period                                            |      | 300      |                    | μs    | Reg 10h[3:2] = 00. See Table 25.                  |

|                                                                  |      | 10       |                    | ms    | Reg 10h[3:2] = 01. See Table 25.                  |

|                                                                  |      | 20       |                    | ms    | Reg 10h[3:2] = 10. See Table 25.                  |

|                                                                  |      | 40       |                    | ms    | Reg 10h[3:2] = 11. See Table 25.                  |

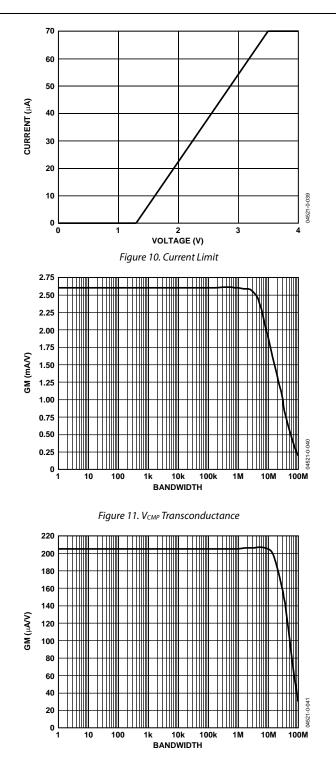

| Unity Gain Bandwidth, GBW                                        |      | 1        |                    | MHz   | See Figure 11.                                    |

| Transconductance                                                 | 1.9  | 2.7      | 3.5                | mA/V  | At $I_{VCMP} = \pm 180 \ \mu A$                   |

| Source Current                                                   | 250  |          |                    | μΑ    | At $V_{VCMP} > 1 V$                               |

| Sink Current                                                     | 250  |          |                    | μA    | At $V_{VCMP} < V_{DD} - 1 V$                      |

| DIFFERENTIAL CURRENT SENSE INPUT,                                |      |          |                    |       | Reg 17h[7] = 0. See Table 18.                     |

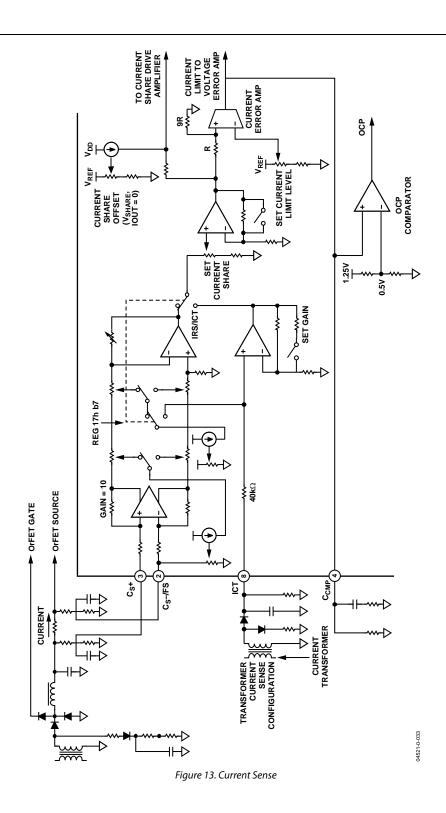

| Cs-, Cs+                                                         |      |          |                    |       | I <sub>SENSE</sub> mode. See Figure 13.           |

| Common-Mode Range                                                | 0    | _        | V <sub>DD</sub> -2 | V     | Set by external divider                           |

| External Divider Tolerance Trim Range                            |      | -5       |                    | mV    | Reg 16h[5:3] = 000. See Table 31.                 |

| (with respect to input)                                          |      | 10       |                    |       |                                                   |

|                                                                  |      | -10      |                    | mV    | Reg 16h[5:3] = 001. See Table 31.                 |

|                                                                  |      | -20      |                    | mV    | Reg 16h[5:3] = 010. See Table 31.                 |

|                                                                  |      | 5        |                    | mV    | Reg 16h[5:3] = 100. See Table 31.                 |

|                                                                  |      | 10       |                    | mV    | Reg 16h[5:3] = 101. See Table 31.                 |

| External Divider Televice - Trive Char C                         |      | 20       |                    | mV    | Reg 16h[5:3] = 110. See Table 31.                 |

| External Divider Tolerance Trim Step Size                        |      | 20       |                    | μV    | $V_{CM} = 2.0 V$                                  |

| (with respect to input)                                          |      | 39<br>70 |                    | μV    | 8 bits, 255 steps                                 |

|                                                                  |      | 78       |                    | μV    | Reg 14h[7:0]. See Table 29.                       |

|      | 8<br>15<br>30 |                                                       | mV<br>mV                                              | Reg 17h[2:0] = 000. See Table 32 .<br>Reg 17h[2:0] = 001. See Table 32.                                                           |

|------|---------------|-------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|      | -30           |                                                       | mV                                                    | Reg  17h[2.0] = 0.01 See Table 32                                                                                                 |

|      |               |                                                       |                                                       | 1 - 1 - 2 - 2 - 1 - 1 - 2 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 1 - 2 - 2 |

|      | 0             |                                                       | mV                                                    | Reg 17h[2:0] = 010. See Table 32.                                                                                                 |

|      | 8             |                                                       | mV                                                    | Reg 17h[2:0] = 100. See Table 32.                                                                                                 |

|      | 15            |                                                       | mV                                                    | Reg $17h[2:0] = 101$ . See Table 32.                                                                                              |

|      | 30            |                                                       | mV                                                    | Reg $17h[2:0] = 110$ . See Table 32.                                                                                              |

|      | 30            |                                                       | μV                                                    | $V_{CM} = 2.0 \text{ V}, V_{DIFF} = 0 \text{ V}$                                                                                  |

|      |               |                                                       |                                                       | 8 bits, 255 steps                                                                                                                 |

|      |               |                                                       |                                                       |                                                                                                                                   |

|      | 120           |                                                       | μν                                                    | Reg 15h[7:0]. See Table 30.                                                                                                       |

|      |               |                                                       |                                                       |                                                                                                                                   |

|      |               |                                                       |                                                       | $V_{CSCM} = 2.0V, 0^{\circ}C \le T_A \le 85^{\circ}C \text{ SHRS} =$<br>SHRO = 2 V. Gain = 230x                                   |

|      | _             |                                                       |                                                       |                                                                                                                                   |

|      |               |                                                       |                                                       | Chopper ON                                                                                                                        |

|      | ±6            |                                                       | %                                                     | Chopper OFF                                                                                                                       |

|      |               |                                                       |                                                       | Input voltage range at Cs+, Cs-                                                                                                   |

|      | 65            |                                                       | V/V                                                   | $34.0 \text{ mV} - 44.5 \text{ mV}$ . Gain = $65 \times$                                                                          |

|      | 85            |                                                       | V/V                                                   | 26.0 mV – 34.0 mV. Gain = 85×                                                                                                     |

|      | 110           |                                                       | V/V                                                   | 20.0 mV – 26.0 mV. Gain = 110×                                                                                                    |

|      | 135           |                                                       | V/V                                                   | 16.0 mV – 20.0 mV. Gain = 135×                                                                                                    |

|      | 175           |                                                       | V/V                                                   | 12.0 mV – 16.0 mV. Gain = 175×                                                                                                    |

|      |               |                                                       |                                                       | 9.5 mV – 12.0 mV. Gain = 230×                                                                                                     |

|      | 200           |                                                       | .,.                                                   |                                                                                                                                   |

|      | 2.0           |                                                       | v                                                     | $V_{ZO} = 0$                                                                                                                      |

|      |               |                                                       |                                                       | Reg 06h[7:1]. See Table 15.                                                                                                       |

|      |               |                                                       |                                                       | SHRS = SHRO = 1 V                                                                                                                 |

|      |               |                                                       |                                                       |                                                                                                                                   |

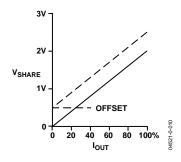

| -    | 0             |                                                       |                                                       | 7 bits, 127 steps I <sub>SHARE</sub> slope                                                                                        |

| -5   |               | +5                                                    | %0                                                    | $0 \text{ V} \le \text{V}_{\text{CSCM}} \le 0.3 \text{ V}. \text{ Gain} = 65 \times 10^{-10} \text{ Gain}$                        |

| _    |               | _                                                     |                                                       | $V_{CSCM} = $ Input Common Mode                                                                                                   |

| -5   | ±1            | +5                                                    | %                                                     | $V_{CSCM}=2.0V, 0^{\circ}C \leq T_{A} \leq 85^{\circ}C$                                                                           |

|      |               |                                                       |                                                       | $Gain = 135 \times$                                                                                                               |

| -2.5 | ±0.5          | +2.5                                                  | %                                                     | $V_{CSCM} = 2.0 \text{ V}, 0^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$                                                    |

|      |               |                                                       |                                                       | $Gain = 65 \times$                                                                                                                |

|      |               |                                                       |                                                       | See Figure 13.                                                                                                                    |

| 1.25 |               |                                                       | V                                                     | Reg 17h[7] = 1. See Table 32.                                                                                                     |

|      |               |                                                       |                                                       | Reg 17h[5] = 1. See Table 32.                                                                                                     |

|      |               |                                                       |                                                       | $0 \le V_{\text{TRIM}} \le 1.25 \text{ V}$                                                                                        |

|      | 0.4           |                                                       | %                                                     | 8 bits, 255 steps, $V_{CT} = 1.0 V$                                                                                               |

|      | 5.5           |                                                       | mV                                                    | Reg 05h[7:0]. See Table 14.                                                                                                       |

|      |               |                                                       |                                                       | Reg 17h[7] = 1. See Table 32.                                                                                                     |

|      |               |                                                       |                                                       | Reg $06h = FEh$ . See Table 15.                                                                                                   |

|      | 4.5           |                                                       | V/V                                                   | Reg 17h[5] = 0, $V_{\text{SHARE}}$ = 2 V. Table 3                                                                                 |

|      | 2.57          |                                                       | V/V                                                   | Reg $17h[5] = 1$ . See Table 32.                                                                                                  |

|      |               |                                                       |                                                       | Reg 15h = 05h, approx 1 $\mu$ A.                                                                                                  |

|      |               |                                                       |                                                       | See Table 30. $V_{\text{share}} = 2 \text{ V}.$                                                                                   |

| 0.45 | 0.5           | 0.68                                                  | V                                                     | Gain setting $= 4.5$                                                                                                              |

|      |               |                                                       |                                                       | Gain setting = $2.57$                                                                                                             |

|      |               |                                                       |                                                       |                                                                                                                                   |

| 20   |               |                                                       |                                                       | See Current Transformer Input                                                                                                     |

|      | 2.0           |                                                       | μΑ                                                    | Section.                                                                                                                          |

|      | 170           |                                                       | nA                                                    | 15 steps Reg 15h[3:0].                                                                                                            |

|      | 170           |                                                       | 1174                                                  | See Table 30.                                                                                                                     |

| 25   | r             | 7                                                     |                                                       |                                                                                                                                   |

| 3.5  | 5             | /                                                     | mA                                                    | See Figure 38. See Absolute<br>Maximum Ratings.                                                                                   |

| _    |               | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{ c c c c c c c c } & 120 & & & & & & & & \\ & & & & & & & & & & $                                                  |

| Parameter                             | Min                  | Тур  | Max               | Unit | <b>Test Conditions/Comments</b>                                                                          |

|---------------------------------------|----------------------|------|-------------------|------|----------------------------------------------------------------------------------------------------------|

| CURRENT LIMIT ERROR AMPLIFIER         |                      |      |                   |      | See Figure 13                                                                                            |

| Current Limit Trim Range <sup>2</sup> | 105                  |      | 130               | %    | After I <sub>SHARE</sub> calibration                                                                     |

| Current Limit Trim Step               |                      | 1.1  |                   | %    |                                                                                                          |

| Current Limit Trim Step               |                      | 26.5 |                   | mV   | $2.0 \le V_{SHARE} \le 2.8 V$ typ. 5 bits, 31 steps<br>Reg 04h[7:3]. See Table 13.                       |

| Transconductance                      | 100                  | 200  | 300               | μA/V | $I_{CCMP} = \pm 20 \ \mu A.$ See Figure 12.                                                              |

| Output Source Current                 |                      | 40   |                   | μA   | $V_{CCMP} = > 1 V$                                                                                       |

| Output Sink Current                   |                      | 40   |                   | μA   | $V_{CCMP} = \langle V_{DD} - 1 V \rangle$                                                                |

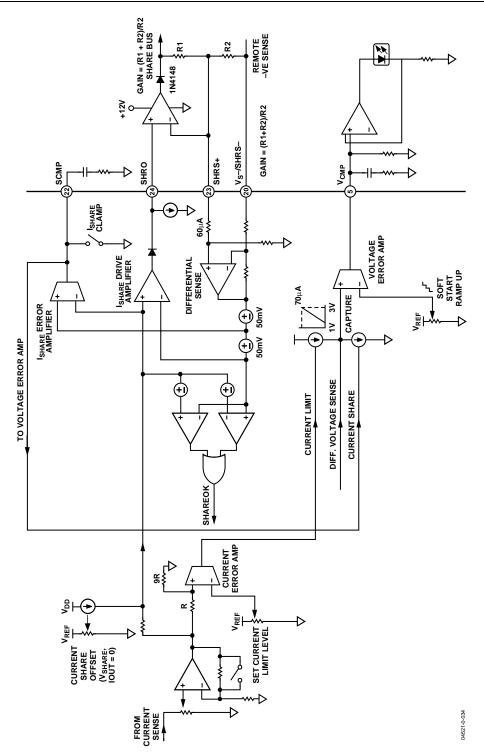

| CURRENT SHARE DRIVER                  |                      |      |                   |      | See Figure 14.                                                                                           |

| Output Voltage <sup>6</sup>           | V <sub>DD</sub> – 0. | .4   |                   | V    | $R_L = 1 \ k\Omega, V_{SHRS} \le V_{DD} - 2 \ V$                                                         |

| Short Circuit Source Current          |                      |      | 55                | mA   |                                                                                                          |

| Source Current                        |                      |      | 15                | mA   | Current at which V <sub>OUT</sub> does not drop by more than 5%                                          |

| Sink Current                          |                      | 60   | 100               | μA   | $V_{SHARE} = 2.0 V$                                                                                      |

| CURRENT SHARE DIFFERENTIAL SENSE      |                      |      |                   | · ·  | See Figure 14.                                                                                           |

| AMPLIFIER                             |                      |      |                   |      |                                                                                                          |

| Vs– Input Voltage                     |                      |      | 0.5               | V    | Voltage on Pin 20                                                                                        |

| V <sub>SHRS</sub> Input Voltage       |                      |      | $V_{\text{DD}}-2$ | V    | Voltage on Pin 23                                                                                        |

| Input Impedance <sup>2</sup>          | 65                   | 100  |                   | kΩ   | $V_{SHRS} = 0.5 V, V_{S} - = 0.5 V$                                                                      |

| Gain                                  |                      | 1.0  |                   | V/V  |                                                                                                          |

| CURRENT SHARE ERROR AMPLIFIER         |                      |      |                   |      |                                                                                                          |

| Transconductance, SHRS to SCMP        | 100                  | 200  | 300               | μA/V | $I_{SCMP} = \pm 20 \ \mu A$                                                                              |

| Output Source Current                 |                      | 40   |                   | μA   | $V_{SCMP} > 1 V$                                                                                         |

| Output Sink Current                   |                      | 40   |                   | μA   | $V_{SCMP} < V_{DD} - 1 V$                                                                                |

| Input Offset Voltage                  | 40                   | 50   | 60                | mV   | Master/slave arbitration                                                                                 |

| Share OK Window Comparator Threshold  |                      |      |                   |      | SHRS = 2 V $\pm$ SHR <sub>THRESH</sub>                                                                   |

| (Share Drive Error)                   |                      | ±100 |                   | mV   | Reg 04h[1:0] = 00. See Table 13.                                                                         |

|                                       |                      | ±200 |                   | mV   | Reg 04h[1:0] = 01. See Table 13.                                                                         |

|                                       |                      | ±300 |                   | mV   | Reg 04h[1:0] = 10. See Table 13.                                                                         |

|                                       |                      | ±400 |                   | mV   | Reg 04h[1:0] = 11. See Table 13.                                                                         |

| CURRENT LIMIT                         |                      |      |                   |      |                                                                                                          |

|                                       |                      |      |                   |      | Figure 10.                                                                                               |

| Current Limit Control Lower Threshold | 1.3                  |      |                   | V    | $V_{CCMP} = 0.7 \text{ V}, \text{ V}_{S} + = 1.5 \text{ V}$                                              |

| Current Limit Control Upper Threshold |                      |      | 3.5               | V    | $V_{S}$ + = 0 V, $V_{SCMP}$ = 0 V                                                                        |

| CURRENT SHARE CAPTURE                 |                      |      |                   |      | $V_{SCMP} = 3.5 V.$                                                                                      |

| Current Share Capture Range           | 0.7                  | 1    | 1.3               | %    | Reg 10h[5:4] = 00. See Table 25.                                                                         |

|                                       | 1.4                  | 2    | 2.6               | %    | Reg 10h[5:4] = 01. See Table 25.                                                                         |

|                                       | 2.1                  | 3    | 3.9               | %    | Reg 10h[5:4] = 10. See Table 25.                                                                         |

|                                       | 2.8                  | 4    | 5.2               | %    | Reg 10h[5:4] = 11. See Table 25.                                                                         |

| Capture Threshold                     | 0.6                  | 1.0  | 1.4               | V    |                                                                                                          |

| FET OR GATE DRIVE                     |                      |      |                   |      | Open-drain N-channel FET                                                                                 |

| Output Low Level (On)                 |                      |      | 0.4               | V    | $I_{IO} = 5 \text{ mA}$                                                                                  |

|                                       |                      |      | 0.8               | V    | $I_{IO} = 10 \text{ mA}$                                                                                 |

| Output Leakage Current                | -5                   |      | +5                | μA   |                                                                                                          |

| REVERSE VOLTAGE COMPARATOR, FS, FD    |                      |      |                   |      | $V_{CS-} = FS$                                                                                           |

| Common-Mode Range                     | 0.25                 | 2.0  | $V_{\text{DD}}-2$ | V    | Voltage set by C <sub>s</sub> resistor divider<br>Voltage on C <sub>s</sub> - pin. $T_A = 25^{\circ}C$ . |

| Parameter                                   | Min  | Тур     | Max  | Unit | <b>Test Conditions/Comments</b>                              |

|---------------------------------------------|------|---------|------|------|--------------------------------------------------------------|

| Reverse Voltage Detector Turn-Off Threshold | 1    |         |      |      | $V_{CS-} = 2 V$ for threshold specs                          |

|                                             |      | 100     |      | mV   | Reg 03h[7:6] = 00. See Table 12.                             |

|                                             |      | 150     |      | mV   | Reg 03h[7:6] = 01. See Table 12.                             |

|                                             |      | 200     |      | mV   | Reg 03h[7:6] = 10. See Table 12.                             |

|                                             |      | 250     |      | mV   | Reg $03h[7:6] = 11$ . See Table 12.                          |

| Reverse Voltage Detector Turn-On Threshold  |      | 250     |      | IIIV | $V_{CS-} = 2 V$ for threshold specs                          |

| Reverse voltage Detector Turn-On Threshold  |      | 20      |      |      | -                                                            |

|                                             |      | 20      |      | mV   | Reg 03h[5:4] = 00. See Table 12.                             |

|                                             |      | 30      |      | mV   | Reg 03h[5:4] = 01. See Table 12.                             |

|                                             |      | 40      |      | mV   | Reg 03h[5:4] = 10. See Table 12.                             |

|                                             |      | 50      |      | mV   | Reg 03h[5:4] = 11. See Table 12.                             |

| FD Input Impedance                          | 500  |         |      | kΩ   |                                                              |

| FS Input Impedance                          |      | 20      |      | kΩ   |                                                              |

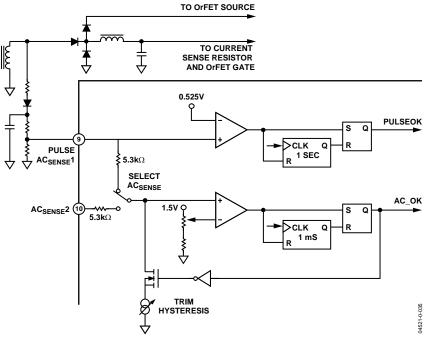

| ACsense1/ACsense2 COMPARATOR                |      |         |      |      | Reg 12h[2] = 0                                               |

|                                             |      |         |      |      | Reg 0Dh[3:2] = 00. See Table 22 .                            |

| (AC or Bulk Sense)                          |      |         |      |      | Reg  12h[2] = 1                                              |

| · · · · · · · · · · · · · · · · · · ·       |      |         |      |      | Reg $0Eh[7:6] = 00$ . See Table 23.                          |

| Threshold Voltage                           |      | 1.25    |      | v    |                                                              |

| Threshold Adjust Range                      | 1.10 | 1.23    | 1.40 | v    | Min: $DAC = 0$                                               |

| Theshold Aujust hange                       | 1.10 |         | 1.40 | v    |                                                              |

| Thus shall Trins Cr                         |      | 0.0     |      | 01   | Max: DAC = Full Scale                                        |

| Threshold Trim Step                         |      | 0.8     |      | %    | $1.10 \le V_{TRIM} \le 1.4 V$                                |

|                                             |      | 10      |      | mV   | 5 bits, 31 steps                                             |

|                                             |      |         |      |      | Reg 0Ch[7:3]. See Table 21.                                  |

| Hysteresis Adjust Range                     |      | 200–550 |      | mV   | VACSENSE > 1 V, RTHEVENIN = 909R                             |

| Hysteresis Trim Step                        |      | 50      |      | mV   | $200 \le V_{\text{TRIM}} \le 550 \text{ mV}.7 \text{ steps}$ |

|                                             |      |         |      |      | Reg 0Ch[2:0]. See Table 21.                                  |

| Noise Filter                                | 0.6  | 1       | 1.2  | ms   |                                                              |

| PULSE-IN                                    |      |         |      |      |                                                              |

| Threshold Voltage                           |      | 0.525   |      | V    |                                                              |

| PULSE_OK On Delay                           |      | 1       |      | μs   |                                                              |

| PULSE_OK Off Delay                          | 0.8  | 1       | 1.2  | s    |                                                              |

| OSCILLATOR                                  | -5   |         | +5   | %    | Unless otherwise specified                                   |

| ОСР                                         |      |         |      |      |                                                              |

| OCP Threshold Voltage <sup>2</sup>          | 0.3  | 0.5     | 0.7  | V    | Force $C_{CMP}$ for drop in $V_{CMP}$                        |

|                                             |      |         |      |      | Reg 11h[2] = 0. See Table 26.                                |

| OCP Shutdown Delay Time (Continuous         |      | 1       |      | s    | Reg 12h[4:3] = 00. See Table 27.                             |

| Period in Current Limit)                    |      |         |      | -    |                                                              |

|                                             |      | 2       |      | s    | Reg 12h[4:3] = 01. See Table 27.                             |

|                                             |      | 3       |      | s    | Reg $12h[4:3] = 10$ . See Table 27.                          |

|                                             |      | 4       |      | s    | Reg $12h[4:3] = 11$ . See Table 27.                          |

| OCP Fast Shutdown Delay Time                | 0    | •       | 100  | ms   | Reg $11h[2] = 1$ . See Table 26.                             |

|                                             |      |         | 100  | 1115 | $VC_{CMP} = 1.5 V$                                           |

|                                             |      |         |      |      | VCCMP - 1.3 V                                                |

| MON1, MON2, MON3, MON4                      | 1.24 | 1.05    | 1.20 |      |                                                              |

| Sense Voltage                               | 1.21 | 1.25    | 1.29 | V    |                                                              |

| Hysteresis                                  |      | 0.1     |      | V    |                                                              |

| OVP Noise Filter                            | 5    |         | 25   | μs   |                                                              |

| UVP Noise Filter                            | 300  |         | 600  | μs   |                                                              |

| OTP (MON5)                                  |      |         |      |      | Reg 0Fh[4:2] = 01x or 10x. Table 24                          |

| Sense Voltage Range                         | 2.2  |         | 2.45 | V    |                                                              |

|                                             |      | 24      |      | mV   | $2.1 \le V_{\text{TRIM}} \le 2.45 \text{ V}$                 |

|                                             |      |         |      |      |                                                              |

| OTP Trim Step                               |      |         |      |      | 4 bits, 15 steps, Reg 0Rh[7·4]                               |

|                                             |      |         |      |      | 4 bits, 15 steps, Reg 0Bh[7:4].<br>See Table 20.             |

| Parameter                                          | Min                  | Тур                | Мах  | Unit     | <b>Test Conditions/Comments</b>                         |

|----------------------------------------------------|----------------------|--------------------|------|----------|---------------------------------------------------------|

| OVP Noise Filter                                   | 5                    |                    | 25   | μs       | Reg 0Fh[4:2] = 010 or 100.<br>See Table 24.             |

| UVP Noise Filter                                   | 300                  |                    | 600  | μs       | Reg 0Fh[4:2] = 011 or 101.<br>See Table 24.             |

| PSON <sup>7</sup>                                  |                      |                    |      |          | Reg 0Eh[4:2] = 00x. See Table 23.                       |

| Input Low Level <sup>8</sup>                       |                      |                    | 0.8  | v        | 5                                                       |

| Input High Level <sup>8</sup>                      | 2.0                  |                    |      | v        |                                                         |

| Debounce                                           |                      | 80                 |      | ms       | Reg 0Fh[1:0] = 00. See Table 24.                        |

|                                                    |                      | 0                  |      | ms       | Reg 0Fh[1:0] = 01. See Table 24.                        |

|                                                    |                      | 40                 |      | ms       | Reg 0Fh[1:0] = 10. See Table 24.                        |

|                                                    |                      | 160                |      | ms       | Reg 0Fh[1:0] = 11. See Table 24.                        |

| PEN <sup>7</sup> , DC_OK <sup>7</sup> , CBD, AC_OK |                      |                    |      |          |                                                         |

| Open-Drain N-Channel Option                        |                      |                    |      |          |                                                         |

| Output Low Level = On <sup>8</sup>                 |                      |                    | 0.4  | V        | $I_{SINK} = 4 \text{ mA}$                               |

| Open-Drain P-Channel                               |                      |                    |      |          | V <sub>OH_PEN</sub>                                     |

| Output High Level = On <sup>8</sup>                | 2.4                  |                    |      | V        | $I_{\text{SOURCE}} = 4 \text{ mA}$                      |

| Leakage Current                                    | -5                   |                    | +5   | μΑ       |                                                         |

| DC_OK <sup>7</sup>                                 |                      |                    |      |          | Reg 0Fh[7:5] = 00x. See Table 24.                       |

| DC_OK, On Delay (Power-On and OK Delay)            |                      | 400                |      | ms       | Reg 0Eh[1:0] = 00. See Table 23.                        |

| ,                                                  |                      | 200                |      | ms       | Reg $0Eh[1:0] = 01.See Table 23.$                       |

|                                                    |                      | 800                |      | ms       | Reg 0Eh[1:0] = 10. See Table 23.                        |

|                                                    |                      | 1600               |      | ms       | Reg 0Eh[1:0] = 11. See Table 23.                        |

| DC_OK, Off Delay (Power-Off Early Warning)         |                      | 2                  |      | ms       | Reg 10h[7:6] = 00. See Table 25.                        |

|                                                    |                      | 0                  |      | ms       | Reg 10h[7:6] = 01. See Table 25.                        |

|                                                    |                      | 1                  |      | ms       | Reg 10h[7:6] = 10. See Table 25.                        |

|                                                    |                      | 4                  |      | ms       | Reg $10h[7:6] = 11$ . See Table 25.                     |

| SMBus, SDL/SCL                                     |                      |                    |      |          |                                                         |

| Input Voltage Low <sup>8</sup>                     |                      |                    | 0.8  | V        |                                                         |

| Input Voltage High <sup>8</sup>                    | 2.2                  |                    |      | V        |                                                         |

| Output Voltage Low <sup>8</sup>                    |                      |                    | 0.4  | V        | $V_{DD} = 5 \text{ V}, \text{ I}_{SINK} = 4 \text{ mA}$ |

| Pull-Up Current                                    | 100                  |                    | 350  | μΑ       |                                                         |

| Leakage Current                                    | -5                   |                    | +5   | μA       |                                                         |

| ADD0, HARDWIRED ADDRESS BIT                        |                      |                    |      |          |                                                         |

| ADD0 Low Level <sup>8</sup>                        |                      |                    | 0.4  | V        |                                                         |

| ADD0 Floating                                      |                      | V <sub>DD</sub> /2 |      | V        | Floating                                                |

| ADD0 High <sup>8</sup>                             | $V_{\text{DD}} - 0.$ | 5                  |      | V        |                                                         |

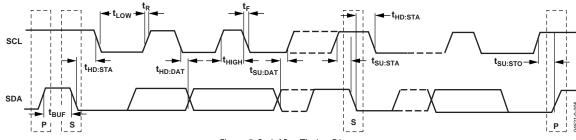

| SERIAL BUS TIMING                                  |                      |                    |      |          | See Figure 5.                                           |

| Clock Frequency                                    |                      |                    | 400  | kHz      |                                                         |

| Glitch Immunity, t <sub>sw</sub>                   |                      |                    | 50   | ns       |                                                         |

| Bus Free Time, t <sub>BUF</sub>                    | 4.7                  |                    |      | μs       |                                                         |

| Start Setup Time, tsu;sta                          | 4.7                  |                    |      | μs       |                                                         |

| Start Hold Time, t <sub>HD;STA</sub>               | 4                    |                    |      | μs       |                                                         |

| SCL Low Time, t <sub>Low</sub>                     | 4.7                  |                    |      | μs       |                                                         |

| SCL High Time, t <sub>HIGH</sub>                   | 4                    |                    |      | μs       |                                                         |

| SCL, SDA Rise Time, t <sub>R</sub>                 |                      |                    | 1000 | ns       |                                                         |

| SCL, SDA Fall Time, t <sub>F</sub>                 |                      |                    | 300  | ns       |                                                         |

| Data Setup Time, t <sub>su;Dat</sub>               | 250                  |                    |      | ns       |                                                         |

| Data Hold Time, t <sub>HD;DAT</sub>                | 300                  |                    |      | ns       |                                                         |

| EEPROM RELIABILITY                                 | -                    |                    |      |          |                                                         |

| Endurance <sup>9</sup>                             | 100                  | 250                |      | k cycles |                                                         |

| Data Retention <sup>10</sup>                       | 100                  |                    |      | Years    |                                                         |

<sup>1</sup> This specification is a measure of I<sub>DD</sub> during an EEPROM page erase cycle. The current is a dynamic. Refer to Figure 29 for a typical I<sub>DD</sub> plot during an EEPROM page erase.

<sup>2</sup> Specification is not production tested, but is supported by characterization data at initial product release.

<sup>3</sup> Four external divider resistors are the same ration, which is selected to produce 2.0 V nominal at Pin 21 while at zero load current. Recommended values are

|         | 3.3 V | 5.0 V | 12 V |

|---------|-------|-------|------|

| RTOP    | 680R  | 1K.5  | 5K1  |

| Rвоттом | 1K    | 1K    | 1K   |

<sup>4</sup> Chopper off.

<sup>5</sup> The maximum specification here is the maximum source current of Pin 8 as specified by the Absolute Maximum Ratings.

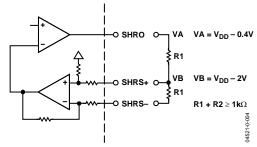

<sup>6</sup> All internal amplifiers accept inputs with common range from GND to  $V_{DD} - 2 V$ . The output is rail to rail but the input is limited to GND to  $V_{DD} - 2 V$ . See Figure 6. <sup>7</sup> These pins can be configured as open-drain N-channel or P-channel, (except PSON) and as normal or inverted logic polarity. Refer to Table 45.

<sup>8</sup> A logic true or false is defined strictly according to the signal name. Low and high refer to the pin or signal voltages.

<sup>9</sup> Endurance is qualified to 100,000 cýcles as per JEDEC std. 22 method A117, and measured at  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C. Typical endurance at 25°C is 250,000 cycles. <sup>10</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 55°C as per JEDEC std. 22 method A117. Retention lifetime based on an activation energy of 0.6 V. Derates with junction temperature.

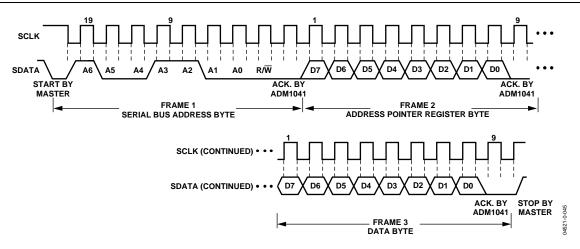

Figure 5. Serial Bus Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| 1.0010 20                                          |                                         |

|----------------------------------------------------|-----------------------------------------|

| Parameter                                          | Rating                                  |

| Supply Voltage (Continuous), V <sub>DD</sub>       | 6.5 V                                   |

| Data Pins SDA, SCL, VDATA                          | V <sub>DD</sub> + 0.5 V,<br>GND – 0.3 V |

| Continuous Power at 25°C, P <sub>D-QSOP24</sub>    | 450 mW                                  |

| Operating Temperature, TAMB                        | -40°C to +85°C                          |

| Junction Temperature, T                            | 150°C                                   |

| Storage Temperature, T <sub>STG</sub>              | –60°C to +150°C                         |

| Lead Temperature                                   | 300°C                                   |

| (Soldering, 10 Seconds), T∟                        |                                         |

| ESD Protection on All Pins, VESD                   | 2 kV                                    |

| Thermal Resistance, Junction to Air, $\theta_{JA}$ | 150°C/W                                 |

| I <sub>CT</sub> Source Current <sup>1</sup>        | 7 mA                                    |

<sup>1</sup> This is the maximum current that can be sourced out from Pin 8 (I<sub>cT</sub> pin).

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### Thermal Characteristics

24-Lead QSOP Package:  $\theta_{JA} = 150^{\circ}C/W$

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

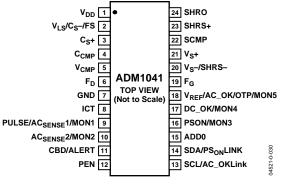

Figure 7. Pin Configuration

#### Table 3. Pin Function Descriptions

| Pin No. | Mnemonic                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD</sub>                      | Positive Supply for the ASIC. Normal range is 4.5 V to 5.5 V. Absolute maximum rating is 6.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2       | V <sub>LS</sub> /C <sub>S</sub> –/FS | Inverting Differential Current Sense Input, Local Voltage Sense Pin, and OrFET Source. These three functions are served by a common divider. The local voltage sense input is used for local overvoltage and undervoltage sensing. This pin also provides an input to the false UV clamp that prevents shutdown during an external load overvoltage condition. When supporting an OrFET circuit, this pin represents the FET source and is the inverting input of a differential amplifier looking for the presence of a reverse voltage across the FET, which might indicate a failure mode.                     |

| 3       | Cs+                                  | Noninverting Differential Current Sense Input. The differential sensitivity of C <sub>s</sub> + and C <sub>s</sub> - is normally around 10 mV to 40 mV at the input to the ASIC. Nulling any external divider offset is achieved by injecting a trimmable amount of current into either the inverting or noninverting input of the second stage of the current sense amplifier. A compensation circuit is used to ensure the amount of current for zero-offset tracks the common-mode voltage. Nulling of any amplifier offset is done in a similar manner except that it does not track the common-mode voltage. |

| 4       | Ссмр                                 | Current Error Amplifier Compensation. This pin is the output of the current limit transconductance error amplifier. A series resistor and a capacitor to ground are required for loop compensation.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5       | VCMP                                 | Voltage Error Amplifier Compensation. This is the output of a voltage error transconductance<br>amplifier. Compensate with a series capacitor and resistor to ground. An external emitter-follower or<br>buffer is typically used to drive an optocoupler. Output voltage positioning may be obtained by<br>placing a second resistor directly to ground. Refer to Analog Devices applications notes on voltage<br>positioning.                                                                                                                                                                                   |

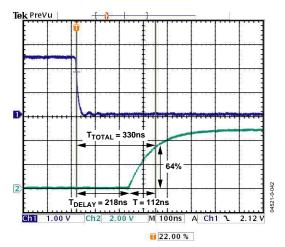

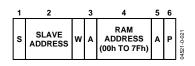

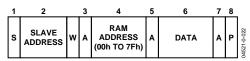

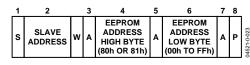

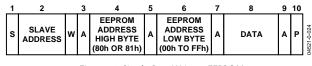

| 6       | FD                                   | A divider from the OrFET drain is connected here. A differential amplifier is then used to detect the presence of a reverse voltage across the FET, which indicates a fault condition and causes the OrFET gate to be pulled low.                                                                                                                                                                                                                                                                                                                                                                                 |