## ANALOG Cascadable Super Sequencer with Margin Control and Fault Recording **Control and Fault Recording**

**ADM1266 Data Sheet**

#### **FEATURES**

Complete supervisory and sequencing solution for up to 17 supplies

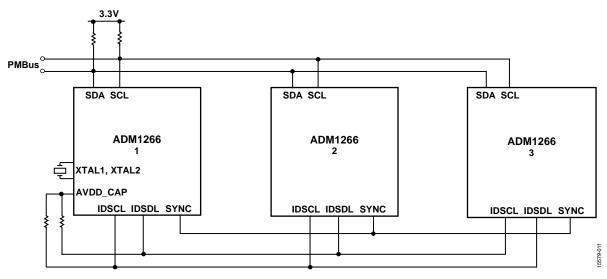

Expandable to 257 supplies with additional ADM1266 ICs connected to the 2-wire interdevice bus

Fully programmable sequencing engine

17 supply fault detectors enable real time supervision of supplies

0.4 V to 15 V on VH1 to VH4 (VHx)

0.4 V to 5 V on VP1 to VP13 (VPx)

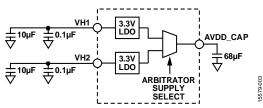

Device powered by the higher of VH1 and VH2 inputs for improved operating redundancy

12-bit ADC for readback of all supervised voltages Black box nonvolatile fault recording

16 PDIOs

9 GPIOs

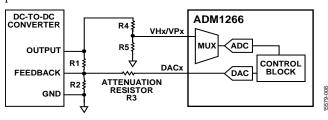

9 voltage output 8-bit DACs allow voltage margining adjustment via dc-to-dc converter trim/feedback node Main and backup memory **Industry standard PMBus interface compliant** Available in a 9 mm × 9 mm, 64-lead package

#### **APPLICATIONS**

**Communications infrastructure** Industrial test and measurement

#### **GENERAL DESCRIPTION**

The ADM1266 Super Sequencer® is a configurable supervisory/ sequencing device that offers a single-chip solution for supply monitoring and sequencing in systems with up to 17 supplies. For systems with more supplies (up to 257), the operation of up to 16 ADM1266 devices can be synchronized through a proprietary 2-wire interface (interdevice bus).

The sequencing engine (SE) monitors the supply fault detectors (SFDs), programmable driver input/outputs (PDIOs), generalpurpose inputs/outputs (GPIOs), and timers, and controls the PDIOs and GPIOs to sequence the supplies up and down as required. The logical core of the device is an Arm<sup>®</sup> Cortex-M3 microcontroller. The firmware is supplied by Analog Devices, Inc., and all configuration is performed through an intuitive graphic user interface (GUI).

Additionally, the ADM1266 integrates an analog-to-digital converter (ADC) and voltage output digital-to-analog converters (DACs) that can be used to adjust either the feedback node or reference of a dc-to-dc converter to implement a closed-loop, autonomous, margining system.

A block of nonvolatile EEPROM is available to record voltage, time, and fault information when instructed to by the sequencing engine configuration.

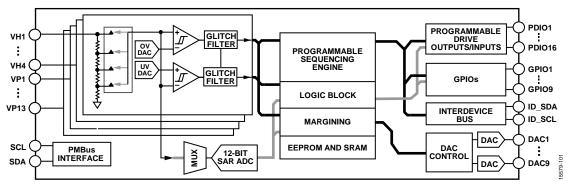

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## **TABLE OF CONTENTS**

| 1   | System Logic Block                                                                                       | 26 |

|-----|----------------------------------------------------------------------------------------------------------|----|

| 1   | Password Protection                                                                                      | 27 |

| 1   | Unlocking the Device                                                                                     | 27 |

| 1   | Locking the Device                                                                                       | 27 |

| 3   | Changing the Password                                                                                    | 27 |

| 4   | Memory                                                                                                   | 28 |

| 5   | Overview                                                                                                 | 28 |

| 11  | Power-Up                                                                                                 | 28 |

| 11  | Manual CRC Calculations                                                                                  | 28 |

| 11  | Refresh                                                                                                  | 28 |

| 12  | Auto Refresh                                                                                             | 28 |

| 14  | Acceleration Factor                                                                                      | 28 |

| 15  | Internal Watchdog Timer                                                                                  | 30 |

| 15  | Applications Information                                                                                 | 31 |

| 16  | Overview                                                                                                 | 31 |

| 17  | Powering the ADM1266                                                                                     | 31 |

| 18  | PCB Assembly and Layout Suggestions                                                                      | 31 |

| 20  | Capacitors                                                                                               | 31 |

| 20  | Ground Connections                                                                                       | 31 |

| 20  | PMBus/I <sup>2</sup> C                                                                                   | 31 |

| 20  | IDB                                                                                                      | 31 |

| 20  | Voltage Sensing                                                                                          | 31 |

| 20  | PDIOs and GPIOs                                                                                          | 31 |

| 21  | DAC Outputs                                                                                              | 31 |

| 21  | Clock                                                                                                    | 31 |

| 22  | Unused Pins                                                                                              | 31 |

| 22  | PMBus Digital Communication                                                                              | 32 |

| 24  | PMBus Features                                                                                           | 32 |

| n n | Overview                                                                                                 | 32 |

| 24  | Transfer Protocol                                                                                        | 32 |

| 24  | Data Transfer Commands                                                                                   | 33 |

| 24  | Group Command Protocol                                                                                   | 34 |

| 24  | Clock Generation and Stretching                                                                          | 34 |

| 24  | Start and Stop Conditions                                                                                | 34 |

| 24  | Repeated Start Condition                                                                                 | 34 |

| 25  | General Call Support                                                                                     | 34 |

| 25  | PMBus Address Selection                                                                                  | 35 |

| 25  | Fast Mode                                                                                                | 35 |

| 25  | 10-Bit Addressing                                                                                        | 35 |

| 25  | Packet Error Checking                                                                                    | 35 |

|     | 111345 11 11 11 12 14 15 15 16 17 18 20 20 20 20 20 20 20 21 21 22 22 24 7 24 24 24 24 24 24 25 25 25 25 | 1  |

| Electrical Specifications35                      | Outline Dimensions68                                |

|--------------------------------------------------|-----------------------------------------------------|

| PMBus Commands36                                 | Ordering Guide68                                    |

| Standard PMBus Command Descriptions38            |                                                     |

| Standard PMBus Commands38                        |                                                     |

| REVISION HISTORY                                 |                                                     |

| 6/2021—Rev. B to Rev. C                          | Added Table 510                                     |

| Changed CP-64-15 to CP-64-23 Throughout          | Change to Setting UNIX Time Using SET_RTC Section24 |

| Added PDIOx Control over PMBus Section and GPIOx | Changes to Refresh Section27                        |

| Control over PMBus Section18                     | Changes to Acceleration Factor Section28            |

| Added State Machine Control via PMBus Section21  | Added Table 1228                                    |

| Changes to System Logic Block Section26          | Changes to Table 5142                               |

| Added Internal Watchdog Timer Section30          | Changes to Table 8052                               |

| Added Table 15; Renumbered Sequentially36        | Changes to Table 8353                               |

| Added WDT_CONFIGURATION Section and Table 10963  | Changes to Table 8854                               |

| Added PDIO_OUTPUT_STATE Section, Table 110, and  | Changes to Table 10459                              |

| Table 11164                                      | Changes to Ordering Guide63                         |

| Added GPIO_OUTPUT_STATE Section, Table 112, and  |                                                     |

| Table 11365                                      | 8/2018—Rev. 0 to Rev. A                             |

| Changes to VAR_VALUE Section66                   | Added Applications Section1                         |

| Added Table 11966                                | Change to Bytes[3:1] Description Column, Table 5041 |

| Updated Outline Dimensions68                     | Changes to Byte 1 Description Column, Table 9054    |

| Changes to Ordering Guide68                      | Change to Byte Column, Table 9455                   |

|                                                  | Changes to Byte 1 Description Column, Table 10057   |

| 7/2019—Rev. A to Rev. B                          |                                                     |

| Added Table 3; Renumbered Sequentially7          | 5/2018—Revision 0: Initial Version                  |

| Change to Table 4 Summary8                       |                                                     |

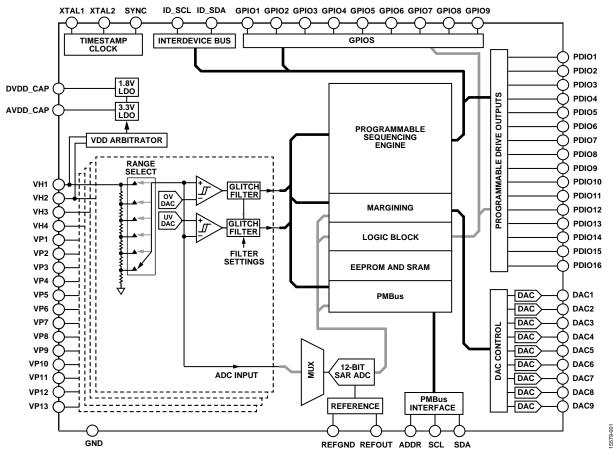

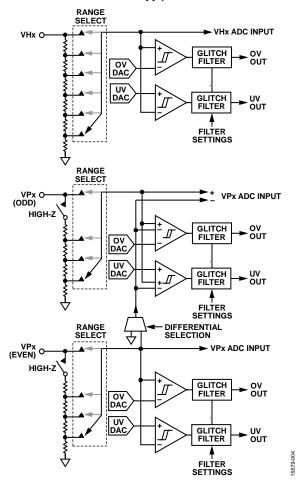

## DETAILED FUNCTIONAL BLOCK DIAGRAM

Figure 2.

## **SPECIFICATIONS**

$T_{J}=0 ^{\circ}\text{C to } +85 ^{\circ}\text{C, VH1 and VH2} > 3 \text{ V, unless otherwise noted. Accuracy (\%)} = (\text{measured voltage} - \text{applied voltage}) \times 100/\text{applied voltage}.$

Table 1.

| Parameter                               | Min | Тур | Max   | Unit | Test Conditions/Comments |

|-----------------------------------------|-----|-----|-------|------|--------------------------|

| ADC, SINGLE-ENDED                       |     | •   |       |      |                          |

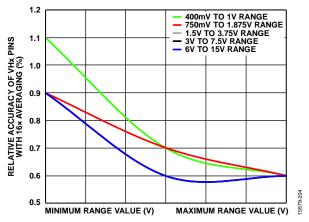

| Accuracy of VHx Pins with 16× Averaging |     |     |       |      |                          |

| 6 V to 15 V                             |     |     | ±0.64 | %    | VHx = 10.623 V           |

| 3 V to 7.5 V                            |     |     | ±0.64 | %    | VHx = 5.311 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.62 | %    | VHx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.66 | %    | VHx = 1.328 V            |

| 400 mV to 1 V                           |     |     | ±0.69 | %    | VHx = 708 mV             |

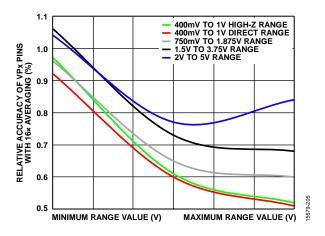

| Accuracy of VPx Pins with 16× Averaging |     |     |       |      |                          |

| 2 V to 5 V                              |     |     | ±0.79 | %    | VPx = 3.541 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.79 | %    | VPx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.70 | %    | VPx = 1.328 V            |

| 400 mV to 1 V                           |     |     |       |      |                          |

| Direct                                  |     |     | ±0.67 | %    | VPx = 708 mV             |

| High-Z                                  |     |     | ±0.66 | %    | VPx = 708 mV             |

| SUPPLY FAULT DETECTORS                  |     |     |       |      |                          |

| Accuracy of VHx Pins                    |     |     |       |      |                          |

| 6 V to 15 V                             |     |     | ±0.65 | %    | VHx = 10.623 V           |

| 3 V to 7.5 V                            |     |     | ±0.65 | %    | VHx = 5.311 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.64 | %    | VHx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.79 | %    | VHx = 1.328 V            |

| 400 mV to 1 V                           |     |     | ±1.02 | %    | VHx = 708 mV             |

| Accuracy of VPx Pins                    |     |     |       |      |                          |

| 2 V to 5 V                              |     |     | ±1.05 | %    | VPx = 3.541 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.89 | %    | VPx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.76 | %    | VPx = 1.328 V            |

| 400 mV to 1 V                           |     |     |       |      |                          |

| Direct                                  |     |     | ±0.76 | %    | VPx = 708 mV             |

| High-Z                                  |     |     | ±0.71 | %    | VPx = 708 mV             |

| ADC, DIFFERENTIAL                       |     |     |       |      |                          |

| Accuracy of VPx Pins with 16× Averaging |     |     |       |      |                          |

| 2 V to 5 V                              |     |     | ±0.90 | %    | VPx = 3.541 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.72 | %    | VPx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.64 | %    | VPx = 1.328 V            |

| 400 mV to 1 V                           |     |     |       |      |                          |

| Direct                                  |     |     | ±0.63 | %    | VPx = 708 mV             |

| High-Z                                  |     |     | ±0.61 | %    | VPx = 708 mV             |

$T_{J} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C}, \text{VH1 and VH2} > 3 \text{ V, unless otherwise noted. Accuracy (\%)} = (\text{measured voltage} - \text{applied voltage}) \times 100 / \text{applied voltage}.$

Table 2.

| Parameter                               | Min | Тур | Max   | Unit | Test Conditions/Comments |

|-----------------------------------------|-----|-----|-------|------|--------------------------|

| ADC, SINGLE-ENDED                       |     |     |       |      |                          |

| Accuracy of VHx Pins                    |     |     |       |      |                          |

| 6 V to 15 V                             |     |     | ±0.64 | %    | VHx = 10.623 V           |

| 3 V to 7.5 V                            |     |     | ±0.64 | %    | VHx = 5.311 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.62 | %    | VHx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.66 | %    | VHx = 1.328 V            |

| 400 mV to 1 V                           |     |     | ±0.69 | %    | VHx = 708 mV             |

| Accuracy of VPx Pins                    |     |     |       |      |                          |

| 2 V to 5 V                              |     |     | ±0.90 | %    | VPx = 3.541 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.79 | %    | VPx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.70 | %    | VPx = 1.328 V            |

| 400 mV to 1 V                           |     |     |       |      |                          |

| Direct                                  |     |     | ±0.67 | %    | VPx = 708 mV             |

| High-Z                                  |     |     | ±0.66 | %    | VPx = 708 mV             |

| SUPPLY FAULT DETECTORS                  |     |     |       |      |                          |

| Accuracy of VHx Pins                    |     |     |       |      |                          |

| 6 V to 15 V                             |     |     | ±0.73 | %    | VHx = 10.623 V           |

| 3 V to 7.5 V                            |     |     | ±0.67 | %    | VHx = 5.311 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.64 | %    | VHx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.79 | %    | VHx = 1.328 V            |

| 400 mV to 1 V                           |     |     | ±1.02 | %    | VHx = 708 mV             |

| Accuracy of VPx Pins                    |     |     |       |      |                          |

| 2 V to 5 V                              |     |     | ±1.15 | %    | VPx = 3.541 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.98 | %    | VPx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.85 | %    | VPx = 1.328 V            |

| 400 mV to 1 V                           |     |     |       |      |                          |

| Direct                                  |     |     | ±0.80 | %    | VPx = 708 mV             |

| High-Z                                  |     |     | ±0.78 | %    | VPx = 708 mV             |

| ADC, DIFFERENTIAL                       |     |     |       |      |                          |

| Accuracy of VPx Pins with 16× Averaging |     |     |       |      |                          |

| 2 V to 5 V                              |     |     | ±0.99 | %    | VPx = 3.541 V            |

| 1.5 V to 3.75 V                         |     |     | ±0.82 | %    | VPx = 2.656 V            |

| 750 mV to 1.875 V                       |     |     | ±0.64 | %    | VPx = 1.328 V            |

| 400 mV to 1 V                           |     |     |       |      |                          |

| Direct                                  |     |     | ±0.63 | %    | VPx = 708 mV             |

| High-Z                                  |     |     | ±0.61 | %    | VPx = 708 mV             |

$T_{J} = -40 ^{\circ}\text{C to} + 105 ^{\circ}\text{C}, \text{VH1 and VH2} > 3 \text{ V, unless otherwise noted. Accuracy (\%)} = (\text{measured voltage} - \text{applied voltage}) \times 100 / \text{applied voltage}.$

Table 3.

| Parameter                               | Min | Тур | Max   | Unit | <b>Test Conditions/Comments</b> |

|-----------------------------------------|-----|-----|-------|------|---------------------------------|

| ADC, SINGLE-ENDED                       |     |     |       |      |                                 |

| Accuracy of VHx Pins                    |     |     |       |      |                                 |

| 6 V to 15 V                             |     |     | ±0.74 | %    | VHx = 10.623 V                  |

| 3 V to 7.5 V                            |     |     | ±0.73 | %    | VHx = 5.311 V                   |

| 1.5 V to 3.75 V                         |     |     | ±0.76 | %    | VHx = 2.656 V                   |

| 750 mV to 1.875 V                       |     |     | ±0.73 | %    | VHx = 1.328 V                   |

| 400 mV to 1 V                           |     |     | ±0.77 | %    | VHx = 708 mV                    |

| Accuracy of VPx Pins                    |     |     |       |      |                                 |

| 2 V to 5 V                              |     |     | ±0.95 | %    | VPx = 3.541 V                   |

| 1.5 V to 3.75 V                         |     |     | ±0.86 | %    | VPx = 2.656 V                   |

| 750 mV to 1.875 V                       |     |     | ±0.78 | %    | VPx = 1.328 V                   |

| 400 mV to 1 V                           |     |     |       |      |                                 |

| Direct                                  |     |     | ±0.75 | %    | VPx = 708 mV                    |

| High-Z                                  |     |     | ±0.74 | %    | VPx = 708 mV                    |

| SUPPLY FAULT DETECTORS                  |     |     |       |      |                                 |

| Accuracy of VHx Pins                    |     |     |       |      |                                 |

| 6 V to 15 V                             |     |     | ±0.98 | %    | VHx = 10.623 V                  |

| 3 V to 7.5 V                            |     |     | ±1.00 | %    | VHx = 5.311 V                   |

| 1.5 V to 3.75 V                         |     |     | ±0.98 | %    | VHx = 2.656 V                   |

| 750 mV to 1.875 V                       |     |     | ±1.13 | %    | VHx = 1.328 V                   |

| 400 mV to 1 V                           |     |     | ±1.28 | %    | VHx = 708 mV                    |

| Accuracy of VPx Pins                    |     |     |       |      |                                 |

| 2 V to 5 V                              |     |     | ±1.15 | %    | VPx = 3.541 V                   |

| 1.5 V to 3.75 V                         |     |     | ±1.03 | %    | VPx = 2.656 V                   |

| 750 mV to 1.875 V                       |     |     | ±1.01 | %    | VPx = 1.328 V                   |

| 400 mV to 1 V                           |     |     |       |      |                                 |

| Direct                                  |     |     | ±0.97 | %    | VPx = 708 mV                    |

| High-Z                                  |     |     | ±0.97 | %    | VPx = 708 mV                    |

| ADC, DIFFERENTIAL                       |     |     |       |      |                                 |

| Accuracy of VPx Pins with 16× Averaging |     |     |       |      |                                 |

| 2 V to 5 V                              |     |     | ±0.99 | %    | VPx = 3.541 V                   |

| 1.5 V to 3.75 V                         |     | 1   | ±0.82 | %    | VPx = 2.656 V                   |

| 750 mV to 1.875 V                       |     | 1   | ±0.73 | %    | VPx = 1.328 V                   |

| 400 mV to 1 V                           |     |     |       |      |                                 |

| Direct                                  |     | 1   | ±0.94 | %    | VPx = 708 mV                    |

| High-Z                                  |     |     | ±0.75 | %    | VPx = 708 mV                    |

$T_J = -40$ °C to +105°C, VH1 and VH2 > 3 V, unless otherwise noted.

Table 4.

| Parameter                                                                | Min  | Тур  | Max      | Unit | Test Conditions/Comments                                                                        |

|--------------------------------------------------------------------------|------|------|----------|------|-------------------------------------------------------------------------------------------------|

| POWER SUPPLY                                                             |      |      |          |      |                                                                                                 |

| VH1 and VH2                                                              | 3.0  |      | 15.0     | V    | Minimum supply required on one of VH1/VH2 pins                                                  |

| Supply Current, I <sub>VH1/VH2</sub>                                     |      | 16   | 50       | mA   | Depends on pin configuration                                                                    |

| VH1 and VH2 Undervoltage Lockout<br>(UVLO)                               | 2.59 | 2.71 | 2.83     | V    | Voltage below which the device turns off                                                        |

| VH1 and VH2 UVLO Hysteresis                                              |      | 111  |          | mV   | Voltage, above the UVLO voltage level, at which the device turns on                             |

| VH1 and VH2 Arbitration Hysteresis                                       | 90   |      |          | mv   | VH1 and VH2 = 3.3 V                                                                             |

|                                                                          | 317  |      |          | mV   | VH1 and VH2 = 5 V                                                                               |

|                                                                          | 987  |      |          | mV   | VH1 and VH2 = 12 V                                                                              |

| AVDD_CAP                                                                 | 3.2  | 3.3  | 3.355    | V    | Regulated AVDD_CAP low dropout (LDO) output; VH1 and VH2 > 3.6 V                                |

| DVDD_CAP                                                                 | 1.79 | 1.82 | 1.85     | V    | Regulated DVDD_CAP LDO output                                                                   |

| SUPPLY FAULT DETECTORS                                                   |      |      |          |      |                                                                                                 |

| VHx Pins                                                                 |      |      |          |      |                                                                                                 |

| Input Voltage Range                                                      | 0    |      | 15       | V    |                                                                                                 |

| Input Impedance                                                          |      |      |          |      |                                                                                                 |

| VH1 and VH2                                                              |      | 41   |          | kΩ   |                                                                                                 |

| VH3 and VH4                                                              |      | 153  |          | kΩ   |                                                                                                 |

| VPx Pins                                                                 |      |      |          |      |                                                                                                 |

| Input Voltage Range                                                      | 0    |      | 5        | V    |                                                                                                 |

| Input Impedance                                                          |      | 62   |          | kΩ   |                                                                                                 |

| VPx Pins, Differential (Odd and Next<br>Even) Common-Mode Voltage Offset | -100 |      | +100     | mV   | Maximum voltage difference from VP2, VP4, VP6, VP8, VP10, and VP12 to GND in differential sense |

| Threshold Resolution                                                     |      | 8    |          | Bits | mode                                                                                            |

| Digital Glitch Filter                                                    |      | 2    |          | μs   | Minimum programmable filter length                                                              |

| Digital differ life                                                      |      | 100  |          | μs   | Maximum programmable filter length                                                              |

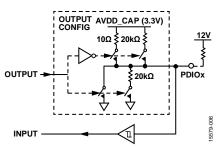

| PROGRAMMABLE DRIVER INPUT/OUTPUTS                                        |      | 100  |          | μ3   | Maximum programmable interferigin                                                               |

| Input Voltage, High (V <sub>IH</sub> )                                   | 1.4  |      |          | V    |                                                                                                 |

| Input Voltage, Low (V <sub>L</sub> )                                     |      |      | 0.6      | V    |                                                                                                 |

| Output Voltage, High (V <sub>OH</sub> )                                  | 2.8  |      | AVDD_CAP | V    | $I_{OH} = 0.5 \text{ mA}$                                                                       |

| Output Voltage, Low (Vol.)                                               | 0    |      | 0.50     | V    | I <sub>OL</sub> = 20 mA                                                                         |

| Output Current, High (I <sub>OH</sub> )                                  |      |      | 500      | μΑ   | Maximum source current per PDIOx pin                                                            |

| Source Current (Isource)                                                 |      |      | 3        | mA   | Maximum total source for all PDIOx pins                                                         |

| Output Current, Low (I <sub>OL</sub> )                                   |      |      | 20       | mA   | Maximum sink current per PDIOx pin                                                              |

| Sink Current (I <sub>SINK</sub> )                                        |      |      | 60       | mA   | Maximum total sink for all PDIOx pins                                                           |

| Pull-Up Resistance (R <sub>PULL-UP</sub> )                               |      | 20   |          | kΩ   | Internal pull-up                                                                                |

| Pull-Up Resistance (R <sub>PULL-DOWN</sub> )                             |      | 20   |          | kΩ   | Internal pull-down                                                                              |

| Tristate Leakage Current                                                 |      |      | 9        | μΑ   | $V_{PDIO} = 21 \text{ V}$                                                                       |

|                                                                          |      |      | 1        | μΑ   | $V_{PDIO} < 3.6 V$                                                                              |

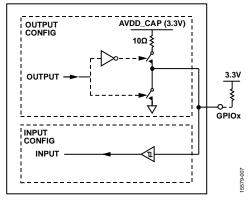

| GPIOs                                                                    |      |      |          |      |                                                                                                 |

| V <sub>IH</sub>                                                          | 1.63 |      |          | V    |                                                                                                 |

| $V_{IL}$                                                                 |      |      | 0.8      | V    |                                                                                                 |

| Voh                                                                      | 2.6  |      | AVDD_CAP | V    | I <sub>OH</sub> = 4 mA                                                                          |

| $V_{OL}$                                                                 | 0    |      | 0.50     | V    | $I_{OL} = 4 \text{ mA}$                                                                         |

| Іон                                                                      |      |      | 4        | mA   | Maximum source current per GPIOx pin                                                            |

| I <sub>SOURCE</sub>                                                      |      |      | 12       | mA   | Maximum total source for all GPIOx pins                                                         |

| loL                                                                      |      |      | 4        | mA   | Maximum sink current per GPIOx pin                                                              |

| I <sub>SINK</sub>                                                        |      |      | 12       | mA   | Maximum total sink for all GPIOx pins                                                           |

Rev. C | Page 8 of 68

| Min   | Тур                                                                                                                                | Max                                                       | Unit        | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                    | 1                                                         | μΑ          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                                                                                                    |                                                           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | 8                                                                                                                                  |                                                           | Bits        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                                                                                                    |                                                           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.501 | 0.506                                                                                                                              | 0.516                                                     | V           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.603 | 0.607                                                                                                                              | 0.618                                                     | V           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.804 | 0.809                                                                                                                              | 0.820                                                     | V           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.005 | 1.011                                                                                                                              | 1.021                                                     | V           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.256 | 1.264                                                                                                                              | 1.273                                                     | V           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | 606                                                                                                                                |                                                           | mV          | Same range, independent of center point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 2.376                                                                                                                              |                                                           | mV          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                                                                                                    | 3                                                         | mA          | Maximum total source for all DAC pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                                                                                                                                    | 1                                                         | μΑ          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                                                                                                    |                                                           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                                                                                                    | 0.25                                                      | mA          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                                                                                                    | 0.25                                                      | mA          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                                                                                                    | 50                                                        | рF          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

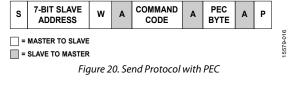

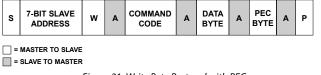

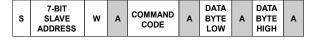

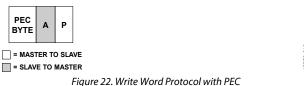

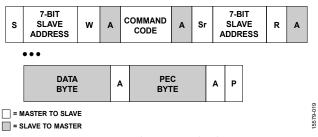

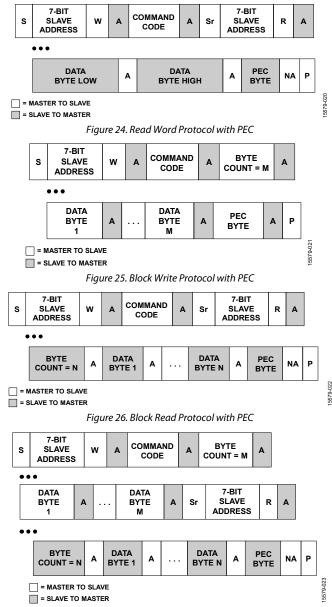

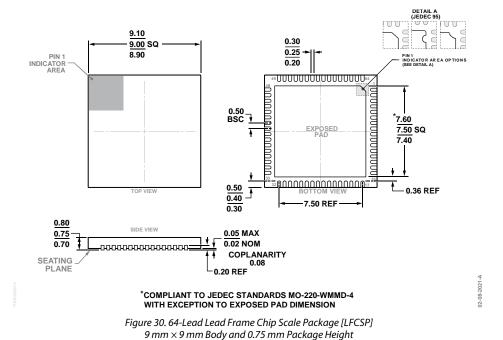

|       |                                                                                                                                    | 2                                                         | μs          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |