# **High Voltage Input Protection Device**

## **Data Sheet**

# ADM1270

### **FEATURES**

Controls supply voltages from 4 V to 60 V Gate drive for low voltage drop reverse supply protection Gate drive for P-channel FETs Inrush current limiting control Adjustable current limit Foldback current limiting Automatic retry or latch-off on current fault Programmable current-limit timer for safe operating area (SOA) Power-good and fault outputs Analog undervoltage (UV) and overvoltage (OV) protection 16-lead, 3 mm × 3 mm LFCSP 16-lead QSOP

### **APPLICATIONS**

Industrial modules Battery-powered/portable instrumentation

### **GENERAL DESCRIPTION**

The ADM1270 is a current-limiting controller that provides inrush current limiting and overcurrent protection for modular or battery-powered systems. When circuit boards are inserted into a live backplane, discharged supply bypass capacitors draw large transient currents from the backplane power bus as they charge. These transient currents can cause permanent damage to connector pins, as well as dips on the backplane supply that can reset other boards in the system.

The ADM1270 is designed to control the inrush current, when powering on the system, via an external P-channel field effect transistor (FET).

To protect the system from a reverse polarity input supply, there is a provision made to control an additional external P-channel FET. This feature prevents reverse current flow in case of a reverse polarity connection, which can damage the load or the ADM1270.

The ADM1270 is available in a 3 mm  $\times$  3 mm, 16-lead LFCSP and a 16-lead QSOP.

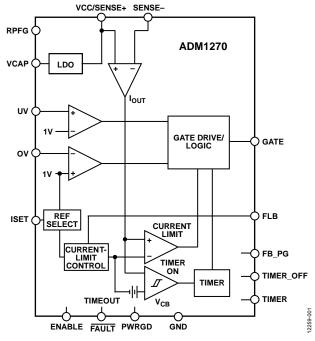

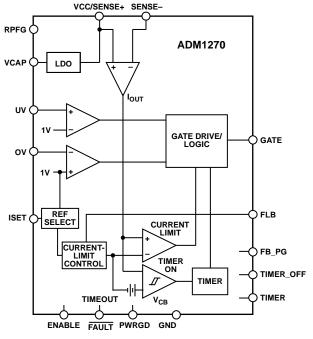

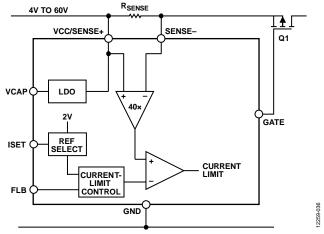

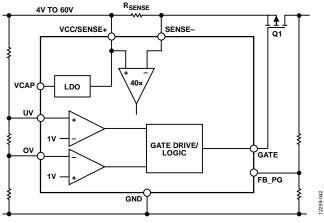

### SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

Figure 1.

#### Rev. A

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2014–2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## **TABLE OF CONTENTS**

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

| General Description1                         |

| Simplified Functional Block Diagram1         |

| Revision History                             |

| Specifications                               |

| Absolute Maximum Ratings                     |

| Thermal Characteristics                      |

| ESD Caution5                                 |

| Pin Configurations and Function Descriptions |

|                                              |

| Typical Performance Characteristics9         |

| Typical Performance Characteristics          |

|                                              |

## **REVISION HISTORY**

12/14—Revision 0: Initial Version

|   | Current Sense Inputs                | 16 |

|---|-------------------------------------|----|

|   | Current-Limit Reference             | 16 |

|   | Setting the Current Limit (ISET)    | 16 |

|   | Foldback                            | 17 |

|   | TIMER                               | 17 |

|   | TIMER_OFF                           | 18 |

|   | Hot Swap Retry Duty Cycle           | 18 |

|   | Gate and RPFG Clamps                | 19 |

|   | Fast Response to Severe Overcurrent | 19 |

|   | Undervoltage and Overvoltage        | 19 |

|   | Enable Input                        | 19 |

|   | Power Good                          | 20 |

| 0 | outline Dimensions                  | 21 |

|   | Ordering Guide                      | 21 |

## **SPECIFICATIONS**

$V_{CC}/V_{SENSE+} = 4 V$  to 60 V,  $V_{SENSE} = (V_{SENSE+} - V_{SENSE-}) = 0 V$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

| Parameter                                           | Symbol                   | Min   | Тур   | Max   | Unit | Test Conditions/Comments                                                                                                                             |

|-----------------------------------------------------|--------------------------|-------|-------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY                                        |                          |       |       |       |      |                                                                                                                                                      |

| Operating Voltage Range                             | Vcc                      | 4     |       | 60    | V    |                                                                                                                                                      |

| Quiescent Current                                   | lcc                      |       | 360   | 500   | μA   | GATE on                                                                                                                                              |

| UV PIN                                              |                          |       |       |       |      |                                                                                                                                                      |

| Input Current                                       | luv                      |       | 0.005 | 0.2   | μA   | $UV \le 5.5 V$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                                                                              |

|                                                     |                          |       | 0.005 | 1     | μA   | $UV \le 5.5 V$ , $T_A = -40^{\circ}C$ to $+125^{\circ}C$                                                                                             |

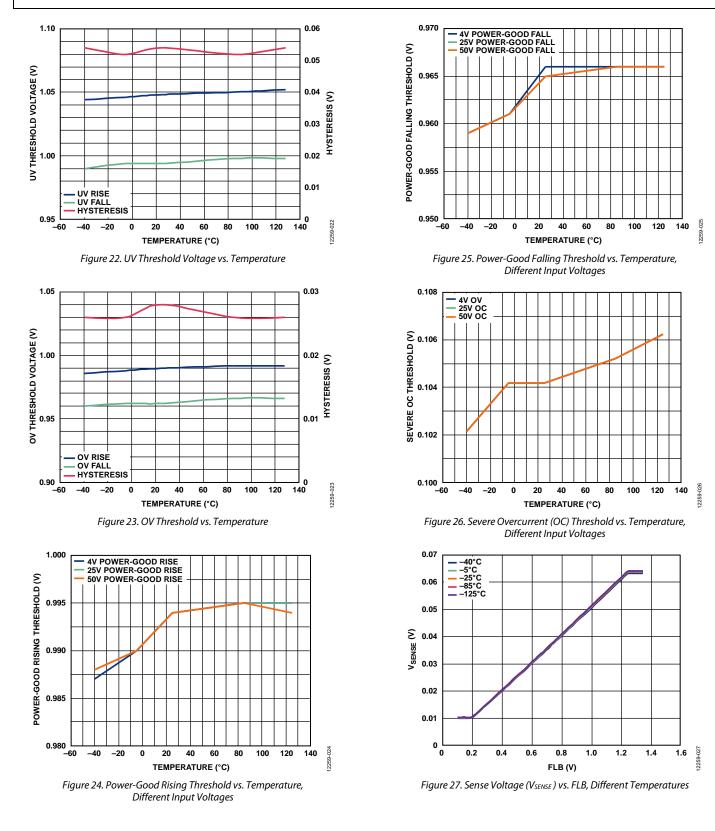

| UV Threshold                                        | UVTH                     | 0.985 | 1.0   | 1.015 | V    | UV falling                                                                                                                                           |

| UV Threshold Hysteresis                             | UV <sub>HYST</sub>       | 55    | 60    | 65    | mV   |                                                                                                                                                      |

| UV Glitch Filter                                    | $UV_{GF}$                | 4     |       | 7     | μs   | 50 mV overdrive                                                                                                                                      |

| UV Propagation Delay                                | UVPD                     |       | 6     | 8     | μs   | UV low to GATE pull-down circuit active                                                                                                              |

| OV PIN                                              |                          |       |       |       |      |                                                                                                                                                      |

| Input Current                                       | lov                      |       | 0.005 | 0.2   | μΑ   | $OV \le 5.5 V$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                                                                              |

|                                                     |                          |       | 0.005 | 1     | μΑ   | $OV \le 5.5 V$ , $T_A = -40^{\circ}C$ to $+125^{\circ}C$                                                                                             |

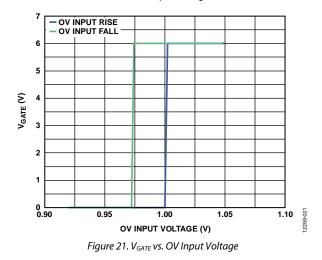

| OV Threshold                                        | OVTH                     | 0.985 | 1.0   | 1.015 | v    | OV rising                                                                                                                                            |

| OV Threshold Hysteresis                             | OV <sub>HYST</sub>       | 25    | 30    | 35    | mV   |                                                                                                                                                      |

| OV Glitch Filter                                    | $OV_{GF}$                | 0.5   |       | 2.0   | μs   | 50 mV overdrive                                                                                                                                      |

| OV Propagation Delay                                | OV <sub>PD</sub>         |       | 1.5   | 2.5   | μs   | OV high to GATE pull-up circuit active                                                                                                               |

| SENSE-                                              |                          |       |       |       |      |                                                                                                                                                      |

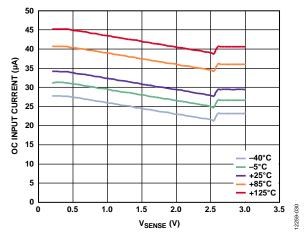

| Input Current                                       | I <sub>SENSE</sub>       | 20    | 40    | 70    | μΑ   | SENSE - = 60 V                                                                                                                                       |

| VCAP PIN                                            |                          |       |       |       |      |                                                                                                                                                      |

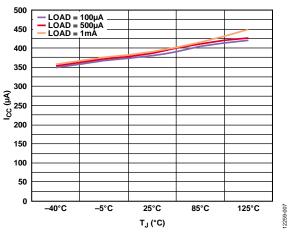

| Internally Regulated Voltage                        | VVCAP                    | 3.546 | 3.6   | 3.636 | V    | $0 \ \mu A \le I_{VCAP} \le 1 \ mA$ , $C_{VCAP} = 1 \ \mu F$                                                                                         |

| Undervoltage Lockout                                | UVLO                     |       |       |       |      |                                                                                                                                                      |

| Rising                                              | UVLORISE                 |       |       | 3.4   | V    | V <sub>cc</sub> rising                                                                                                                               |

| Falling                                             | UVLOFALL                 | 3.0   |       |       | V    | V <sub>cc</sub> falling                                                                                                                              |

| Hysteresis                                          | <b>UVLO</b> HYST         |       | 230   |       | mV   |                                                                                                                                                      |

| ISET PIN                                            |                          |       |       |       |      |                                                                                                                                                      |

| Input Current                                       | IISET                    |       | 0.005 | 0.2   | μΑ   | $V_{ISET} \le V_{VCAP}$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                                                                     |

|                                                     |                          |       | 0.005 | 1     | μΑ   | $V_{ISET} \leq V_{VCAP}, T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                               |

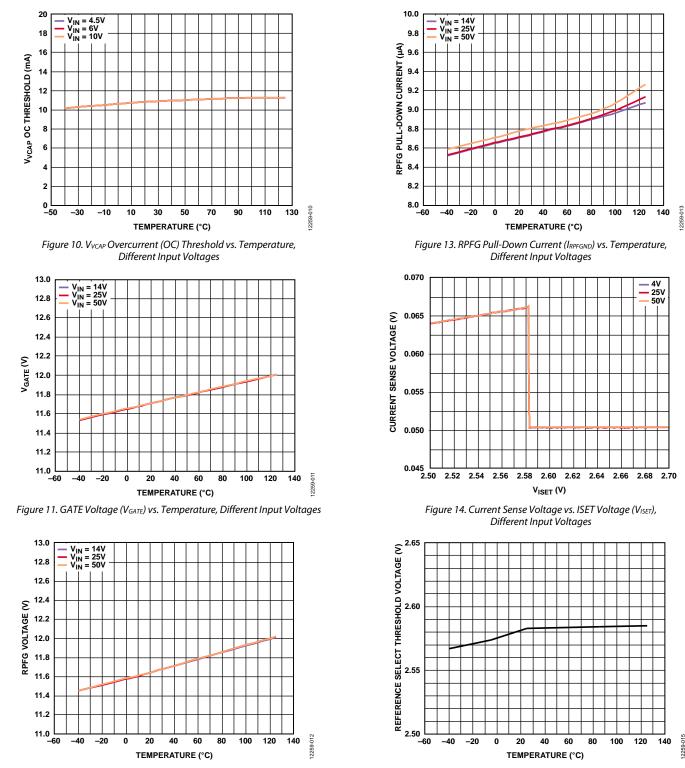

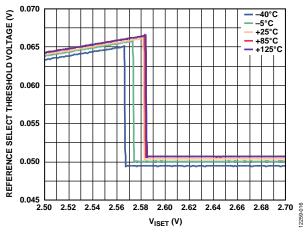

| Reference Select Threshold                          | VISETRSTH                | 2.55  | 2.6   | 2.65  | V    | If $V_{ISET} > V_{ISETRSTH}$ , an internal reference ( $V_{CLREF}$ ) is used                                                                         |

| Internal Reference                                  | VCLREF                   |       | 2     |       | V    | Accuracies included in total sense voltage                                                                                                           |

|                                                     |                          |       |       |       |      | accuracies                                                                                                                                           |

| Gain of Current Sense Amplifier                     | AV <sub>CSAMP</sub>      |       | 40    |       | V/V  | Accuracies included in total sense voltage accuracies                                                                                                |

| RPFG PIN                                            |                          |       |       |       |      |                                                                                                                                                      |

| Reverse Protection FET Gate Drive                   | VRPFG                    |       | 0     |       | v    | $V_{cc} \le 10 \text{ V}$                                                                                                                            |

| Voltage                                             | V RPFG                   |       | U     |       | v    |                                                                                                                                                      |

| Reverse Protection FET Gate Drive<br>Voltage Offset | $\Delta V_{\text{RPFG}}$ | 10    | 12    | 14    | V    | $\Delta V_{\text{RPFG}} = V_{\text{CC}} - V_{\text{RPFG}},  60 \text{ V} \geq V_{\text{CC}} \geq 14 \text{ V},  I_{\text{RPFG}} \leq 5  \mu\text{A}$ |

| RPFG Pull-Down (On) Current                         |                          | 7     | 9     | 12    | μA   | $V_{RPFG} = V_{CC}$                                                                                                                                  |

| GATE PIN                                            |                          | 1     |       |       |      |                                                                                                                                                      |

| GATE Drive Voltage                                  | $\Delta V_{GATE}$        | 10    | 12    | 14    | V    | $\Delta V_{GATE} = V_{CC} - V_{GATE}$ , 60 V $\geq V_{CC} \geq 14$ V, $I_{GATE} \leq 5 \ \mu A$                                                      |

| GATE Pull-Down (On) Current                         | IGATEDN                  | 20    | 25    | 30    | μA   | V <sub>GATE</sub> = V <sub>CC</sub>                                                                                                                  |

| GATE Pull-Up (Off) Current                          | IGATEUP                  |       |       |       |      |                                                                                                                                                      |

| Regulation                                          | IGATEUP_REG              | -50   | -65   | -80   | μA   | $\Delta V_{GATE} \ge 2 V$ , $(V_{SENSE+} - V_{SENSE-}) = 70 \text{ mV}$                                                                              |

| Fault                                               | IGATEUP_FLT              | -7    | -13   | -20   | mA   | $\Delta V_{GATE} = 2 V$                                                                                                                              |

| Parameter                                          | Symbol                        | Min   | Тур       | Max          | Unit     | Test Conditions/Comments                                                                                                                              |

|----------------------------------------------------|-------------------------------|-------|-----------|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| CURRENT SENSE VOLTAGE                              |                               |       |           |              |          |                                                                                                                                                       |

| Sense Voltage Current Limit<br>(Vsense+ – Vsense-) | VSENSECL                      | 47    | 50        | 53           | mV       | $V_{\text{ISET}} > 2.65 \text{ V}, V_{\text{FLB}} > 1.1 \text{ V}, \Delta V_{\text{GATE}} = 3 \text{ V},  I_{\text{GATE}} = 0  \mu\text{A}$           |

| Foldback Inactive                                  |                               |       | 62.5      |              | mV       | $V_{ISET} = 2.5 \text{ V}, V_{FLB} > 1.35 \text{ V}, \Delta V_{GATE} = 3 \text{ V}, I_{GATE} = 0 \mu\text{A}$                                         |

|                                                    |                               | 47    | 50        | 53           | mV       | $V_{ISET} = 2 V$ , $V_{FLB} > 1.1 V$ , $\Delta V_{GATE} = 3 V$ , $I_{GATE} = 0 \mu A$                                                                 |

|                                                    |                               | 22.5  | 25.0      | 27.5         | mV       | $V_{ISET} = 1 V$ , $V_{FLB} > 0.57 V$ , $\Delta V_{GATE} = 3 V$ , $I_{GATE} = 0 \mu A$                                                                |

|                                                    |                               | 10.0  | 12.5      | 15.0         | mV       | $V_{ISET} = 0.5 V$ , $V_{FLB} > 0.3 V$ , $\Delta V_{GATE} = 3 V$ , $I_{GATE} = 0 \mu A$                                                               |

| Foldback Active                                    |                               | 7     | 10        | 13           | mV       | $V_{FLB} = 0 V, \Delta V_{GATE} = 3 V, I_{GATE} = 0 \mu A$                                                                                            |

|                                                    |                               | 22    | 25        | 28           | mV       | $V_{ISET} > 2 V$ , $V_{FLB} = 0.5 V$ , $\Delta V_{GATE} = 3 V$ , $I_{GATE} = 0 \mu A$                                                                 |

| Circuit Breaker Offset                             | VCBOS                         | 0.5   | 1         | 1.5          | mV       | Circuit breaker trip voltage, $V_{CB} = V_{SENSECL} - V_{CBOS}$                                                                                       |

| SEVERE OVERCURRENT                                 |                               |       |           |              |          |                                                                                                                                                       |

| Voltage Threshold                                  | VSENSEOC                      | 90    | 100       | 110          | mV       | V <sub>ISET</sub> > 2.65 V                                                                                                                            |

| ronage meshola                                     | • SENSECC                     | 20    | 25        | 30           | mV       | $V_{\text{ISET}} = 0.5 \text{ V}$                                                                                                                     |

| Glitch Filter Duration                             |                               | 0.4   | 20        | 1.6          | μs       |                                                                                                                                                       |

| Response Time                                      |                               |       | 2.0       | 3.5          | μs       |                                                                                                                                                       |

| TIMER PIN                                          |                               |       |           | 2.2          | ~~       |                                                                                                                                                       |

| TIMER Pull-Up Current                              | ITIMERUP                      | -18   | -20       | -22          | μA       | Overcurrent fault, $0.2 V \le V_{\text{TIMER}} \le 2 V$                                                                                               |

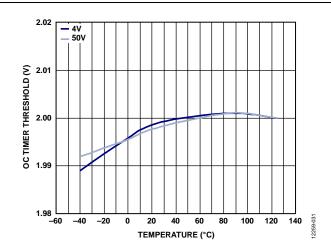

| TIMER High Threshold                               | VTIMERUP                      | 1.96  | 2.0       | 2.04         | V        |                                                                                                                                                       |

| TIMER Low Threshold                                | VTIMERL                       | 0.075 | 0.10      | 0.12         | v        |                                                                                                                                                       |

| TIMER Pull-Down Current                            |                               | 0.85  | 0.10      | 1.15         | μA       | Timer pin voltage = 0.2 V                                                                                                                             |

| niment di Down cancin                              | TIMERPD                       | 75    |           | 105          | μΑ       | Timer pin voltage = $0.2 \text{ V}$                                                                                                                   |

| TIMER_OFF PIN                                      |                               | 75    |           | 105          | μ, ι     |                                                                                                                                                       |

| Power-On Reset Pull-Up Current                     | IPOR                          | -18   | -20       | -22          | μA       | Initial power-on reset, $V_{\text{TIMER}_{OFF}} = 1 \text{ V}$                                                                                        |

| Retry Pull-Up Current                              | IPOR<br>I <sub>TMROFF</sub>   | -0.85 | -20<br>-1 | -22<br>-1.15 | μΑ       | After fault when GATE is off, $V_{\text{TIMER} OFF} = 1 \text{ V}$                                                                                    |

| TIMER_OFF High Threshold                           | VTMROFF                       | 1.96  | 2.0       | 2.04         | V        |                                                                                                                                                       |

| FOLDBACK (FLB PIN)                                 | V TMROFFH                     | 1.90  | 2.0       | 2.04         | v        |                                                                                                                                                       |

| Input Current                                      |                               |       | 0.005     | 0.2          |          | $V_{FLB} \le 5.5 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$                                                                |

| input current                                      | I <sub>FLB</sub>              |       | 0.005     | 0.2<br>1     | μA<br>μA | $V_{FLB} \le 5.5 \text{ V}, T_A = -40 \text{ C to } +65 \text{ C}$<br>$V_{FLB} \le 5.5 \text{ V}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |

| PWRGD FEEDBACK INPUT (FB_PG PIN)                   |                               |       | 0.005     | 1            | μΑ       | $v_{FLB} \le 5.5 v, T_A = -40 C t0 + 125 C$                                                                                                           |

|                                                    |                               |       | 0.005     | 0.2          |          |                                                                                                                                                       |

| Input Current                                      | IFBPG                         |       | 0.005     | 0.2          | μA       | $V_{FB_PG} \le 5.5 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$                                                              |

| DWDCD Dising Threshold                             | V                             | 0.005 | 0.005     | 1            | μA<br>V  | $V_{FB_PG} \le 5.5 \text{ V}, T_A = -40^{\circ}\text{C to} + 125^{\circ}\text{C}$                                                                     |

| PWRGD Rising Threshold                             |                               | 0.985 | 1.0       | 1.015<br>35  | -        | FB_PG rising                                                                                                                                          |

| PWRGD Threshold Hysteresis                         | PG <sub>HYST</sub>            | 25    | 30        |              | mV       |                                                                                                                                                       |

| Power-Good Glitch Filter                           | $PG_{GF}$                     | 0.5   |           | 1.5          | μs       | 50 mV overdrive                                                                                                                                       |

| FAULT PIN                                          |                               |       |           |              |          |                                                                                                                                                       |

| Output Low Voltage                                 | Vol_fault                     |       |           | 0.1          | V        | $I_{FAULT} = 100 \ \mu A$                                                                                                                             |

|                                                    |                               |       |           | 0.4          | V        | I <sub>FAULT</sub> = 1 mA                                                                                                                             |

| Leakage Current                                    | IFAULT                        |       | 0.005     | 1            | μΑ       | V <sub>FAULT</sub> = 5.5 V, FAULT output high-Z                                                                                                       |

| ENABLE PIN                                         |                               |       |           |              |          |                                                                                                                                                       |

| Input High Voltage                                 | VIH                           | 1.2   |           |              | V        |                                                                                                                                                       |

| Input Low Voltage                                  | VIL                           |       |           | 0.4          | V        |                                                                                                                                                       |

| Leakage Current                                    | I <sub>EN</sub>               |       | 0.005     | 1            | μΑ       | $V_{EN} = 5.5 V$                                                                                                                                      |

| PWRGD PIN                                          |                               |       |           |              |          |                                                                                                                                                       |

| Output Low Voltage                                 | $V_{\text{OL}\_\text{PWRGD}}$ |       |           | 0.1          | V        | $I_{PWRGD} = 100 \ \mu A$                                                                                                                             |

|                                                    |                               |       |           | 0.4          | V        | I <sub>PWRGD</sub> = 1 mA                                                                                                                             |

| Output Low Voltage                                 | $V_{\text{OL}_{PWRGD}}$       |       |           | 0.4          | V        | $V_{CC} = 1.7 \text{ V}, \text{ I}_{SINK} = 100 \ \mu\text{A},$                                                                                       |

| Leakage Current                                    | IPWRGD                        |       | 0.005     | 1            | μA       | $V_{PWRGD} = 60 V$ , PWRGD output high-Z                                                                                                              |

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Table 2.                             |                                   |

|--------------------------------------|-----------------------------------|

| Parameter                            | Rating                            |

| VCC/SENSE+                           | –0.3 V to +66 V                   |

| VCAP                                 | –0.3 V to +6 V                    |

| UV                                   | –0.3 V to +6 V                    |

| OV                                   | –0.3 V to +6 V                    |

| ISET                                 | -0.3 V to VCAP + 0.3 V            |

| FLB                                  | –0.3 V to +6 V                    |

| FB_PG                                | –0.3 V to +6 V                    |

| TIMER_OFF                            | -0.3 V to VCAP + 0.3 V            |

| TIMER                                | -0.3 V to VCAP + 0.3 V            |

| FAULT                                | –0.3 V to +6 V                    |

| ENABLE                               | –0.3 V to +6 V                    |

| PWRGD                                | –0.3 V to +66 V                   |

| GATE                                 | -0.3 V to V <sub>CC</sub> + 0.3 V |

| GATE to VCC/SENSE+                   | -22 V to +0.3 V                   |

| SENSE–                               | $-0.3$ V to V_{CC} + 0.3 V        |

| RPFG                                 | $-0.3$ V to V_{CC} + 0.3 V        |

| RPFG to VCC/SENSE+                   | -22 V to +0.3 V                   |

| Vsense (Vsense+ – Vsense-)           | ±0.3 V                            |

| Continuous Current into Any Pin      | ±10 mA                            |

| Storage Temperature Range            | –65°C to +150°C                   |

| Operating Temperature Range          | -40°C to +125°C                   |

| Lead Temperature, Soldering (10 sec) | 300°C                             |

| Junction Temperature                 | 150°C                             |

|                                      |                                   |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL CHARACTERISTICS

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

### Table 3. Thermal Resistance

| Package Type               | θιΑ    | οıc   | Ψյβ   | Unit |

|----------------------------|--------|-------|-------|------|

| 16-Lead, 3 mm × 3 mm LFCSP | 49.5   | 35.2  | 29.6  | °C/W |

| 16-Lead QSOP               | 106.03 | 28.31 | 43.22 | °C/W |

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

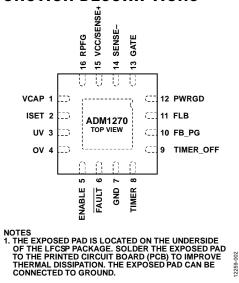

Figure 2. 16-Lead LFCSP Pin Configuration

### Table 4. 16-Lead LFCSP Pin Function Descriptions

| Pin No. | Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                  |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VCAP      | Internal Regulated Supply. Place a capacitor with a 1 µF or greater value on this pin to maintain good accuracy.<br>This pin can be used as a reference to program the ISET pin voltage.                                                                                                                                                                     |

| 2       | ISET      | Current Limit. This pin allows the current-limit threshold to be programmed. The default limit is set when this pin is connected directly to VCAP. To achieve a user defined sense voltage, the current limit can be adjusted using a resistor divider from VCAP. An external reference can also be used.                                                    |

| 3       | UV        | Undervoltage Input Pin. An external resistor divider is connected from the supply to this pin to allow an internal comparator to detect whether the supply is under the UV limit.                                                                                                                                                                            |

| 4       | OV        | Overvoltage Input Pin. An external resistor divider is connected from the supply to this pin to allow an internal comparator to detect whether the supply is above the OV limit.                                                                                                                                                                             |

| 5       | ENABLE    | Enable Pin. This pin is a digital logic input. This input must be high to allow the ADM1270 controller to begin a power-up sequence. If this pin is held low, the ADM1270 is prevented from powering up. There is no internal pull-up on this pin.                                                                                                           |

| 6       | FAULT     | Fault Output. This pin indicates that the device has shut down due to an overcurrent fault condition. The device can be configured for automatic retry after shutdown by connecting this pin directly to the ENABLE pin.                                                                                                                                     |

| 7       | GND       | Ground Pin.                                                                                                                                                                                                                                                                                                                                                  |

| 8       | TIMER     | Timer Pin. An external capacitor, CTIMER, sets an SOA overcurrent fault delay. The GATE pin is pulled off when the voltage on the TIMER pin exceeds the upper threshold.                                                                                                                                                                                     |

| 9       | TIMER_OFF | Timer Off Pin. An external capacitor, C <sub>TIMER_OFF</sub> , sets an initial timing cycle delay and the SOA off time delay. After an SOA overcurrent fault has occurred, the GATE pin is pulled off until the voltage on the TIMER_OFF pin exceeds the threshold.                                                                                          |

| 10      | FB_PG     | PWRGD Feedback Input Pin. An external resistor divider is connected from the output voltage to this pin to allow an internal comparator to detect when the output voltage is above the PWRGD threshold.                                                                                                                                                      |

| 11      | FLB       | Foldback Pin. A foldback resistor divider is placed from the source of the FET to this pin. Foldback reduces the current limit when the source voltage drops. The foldback feature ensures that the power through the FET is not increased beyond the SOA limits.                                                                                            |

| 12      | PWRGD     | Power-Good Signal. This signal indicates that the supply is within tolerance. This signal is based on the voltage present on the FB_PG pin.                                                                                                                                                                                                                  |

| 13      | GATE      | Gate Output Pin. This pin is the gate drive of an external P-channel FET. This pin is driven by the FET drive controller, which provides a pull-down current to charge the FET gate pin. The FET drive controller regulates to a maximum load current by regulating the GATE pin. GATE is held off when the supply is below the undervoltage lockout (UVLO). |

| 14      | SENSE-    | Negative Current Sense Input Pin. A sense resistor between the VCC/SENSE+ pin and the SENSE– pin sets the analog current limit. The hot swap operation of the ADM1270 controls the external FET gate to maintain the sense voltage ( $V_{SENSE+} - V_{SENSE-}$ ). This pin also connects to the FET drain pin.                                               |

## **Data Sheet**

| Pin No.          | Mnemonic   | Description                                                                                                                                                                                                                                                                                                                           |

|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15               | VCC/SENSE+ | Positive Supply Input Pin (VCC). A UVLO circuit resets the device when a low supply voltage is detected. GATE is held off when the supply is below UVLO. No sequencing is required.                                                                                                                                                   |

|                  |            | Positive Current Sense Input Pin (SENSE+). This pin connects to the main supply input. A sense resistor between the VCC/SENSE+ pin and the SENSE– pin sets the analog current limit. The hot swap operation of the ADM1270 controls the external FET gate to maintain the sense voltage (V <sub>SENSE+</sub> – V <sub>SENSE-</sub> ). |

| 16               | RPFG       | Reverse Protection FET Gate Driver Output. Connect this pin to the gate of the external reverse polarity protection P-channel FET for low voltage drop operation.                                                                                                                                                                     |

| N/A <sup>1</sup> | EP         | Exposed Pad. The exposed pad is located on the underside of the LFCSP package. Solder the exposed pad to the printed circuit board (PCB) to improve thermal dissipation. The exposed pad can be connected to ground.                                                                                                                  |

$^{1}$  N/A = not applicable.

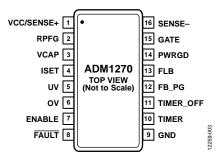

Figure 3. 16-Lead QSOP Pin Configuration

| Table 5. | 16-Lead | QSOP Pi | n Function | Descriptions |

|----------|---------|---------|------------|--------------|

|----------|---------|---------|------------|--------------|

| Pin No. | Mnemonic   | Description                                                                                                                                                                                                                                                                                                                           |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VCC/SENSE+ | Positive Supply Input Pin (VCC). A UVLO circuit resets the device when a low supply voltage is detected. GATE is held off when the supply is below UVLO. No sequencing is required.                                                                                                                                                   |

|         |            | Positive Current Sense Input Pin (SENSE+). This pin connects to the main supply input. A sense resistor between the VCC/SENSE+ pin and the SENSE– pin sets the analog current limit. The hot swap operation of the ADM1270 controls the external FET gate to maintain the sense voltage (V <sub>SENSE+</sub> – V <sub>SENSE-</sub> ). |

| 2       | RPFG       | Reverse Protection FET Gate Driver Output. Connect this pin to the gate of the external reverse polarity protection P-channel FET for low voltage drop operation.                                                                                                                                                                     |

| 3       | VCAP       | Internal Regulated Supply. Place a capacitor with a 1 μF or greater value on this pin to maintain good accuracy.<br>This pin can be used as a reference to program the ISET pin voltage.                                                                                                                                              |

| 4       | ISET       | Current Limit. This pin allows the current-limit threshold to be programmed. The default limit is set when this pin is connected directly to VCAP. To achieve a user defined sense voltage, the current limit can be adjusted using a resistor divider from VCAP. An external reference can also be used.                             |

| 5       | UV         | Undervoltage Input Pin. An external resistor divider is connected from the supply to this pin to allow an internal comparator to detect whether the supply is under the UV limit.                                                                                                                                                     |

| 6       | OV         | Overvoltage Input Pin. An external resistor divider is connected from the supply to this pin to allow an internal comparator to detect whether the supply is above the OV limit.                                                                                                                                                      |

| 7       | ENABLE     | Enable Pin. This pin is a digital logic input. This input must be high to allow the ADM1270 controller to begin a power-up sequence. If this pin is held low, the ADM1270 is prevented from powering up. There is no internal pull-up on this pin.                                                                                    |

| 8       | FAULT      | Fault Output. This pin indicates that the device has shut down due to an overcurrent fault condition. The device can be configured for automatic retry after shutdown by connecting this pin directly to the ENABLE pin.                                                                                                              |

| 9       | GND        | Ground Pin.                                                                                                                                                                                                                                                                                                                           |

| 10      | TIMER      | Timer Pin. An external capacitor, C <sub>TIMER</sub> , sets an SOA overcurrent fault delay. The GATE pin is pulled off when the voltage on the TIMER pin exceeds the upper threshold.                                                                                                                                                 |

| 11      | TIMER_OFF  | Timer Off Pin. An external capacitor, CTIMER_OFF, sets an initial timing cycle delay and the SOA off time delay. After an SOA overcurrent fault has occurred, the GATE pin is pulled off until the voltage on the TIMER_OFF pin exceeds the threshold.                                                                                |

| 12      | FB_PG      | PWRGD Feedback Input Pin. An external resistor divider is connected from the output voltage to this pin to allow an internal comparator to detect when the output voltage is above the PWRGD threshold.                                                                                                                               |

| 13      | FLB        | Foldback Pin. A foldback resistor divider is placed from the source of the FET to this pin. Foldback reduces the current limit when the source voltage drops. The foldback feature ensures that the power through the FET is not increased beyond the SOA limits.                                                                     |

| 14      | PWRGD      | Power-Good Signal. This signal indicates that the supply is within tolerance. This signal is based on the voltage present on the FB_PG pin.                                                                                                                                                                                           |

| 15      | GATE       | Gate Output Pin. This pin is the gate drive of an external P-channel FET. This pin is driven by the FET drive controller, which provides a pull-down current to charge the FET gate pin. The FET drive controller regulates to a maximum load current by regulating the GATE pin. GATE is held off when the supply is below UVLO.     |

| 16      | SENSE-     | Negative Current Sense Input Pin. A sense resistor between the VCC/SENSE+ pin and the SENSE– pin sets the analog current limit. The hot swap operation of the ADM1270 controls the external FET gate to maintain the sense voltage (V <sub>SENSE+</sub> – V <sub>SENSE-</sub> ). This pin also connects to the FET drain pin.         |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

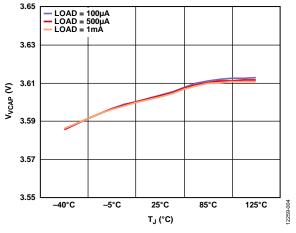

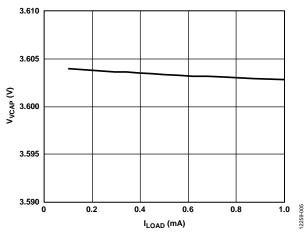

Figure 4. V<sub>VCAP</sub> vs. Junction Temperature (T<sub>J</sub>), Different Loads

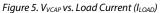

Figure 6. V<sub>VCAP</sub> vs. Input Voltage (V<sub>IN</sub>), Different Loads

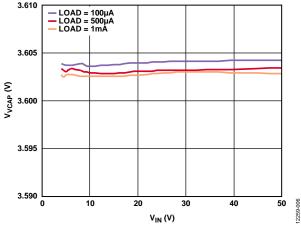

Figure 7. Supply Current (Icc) vs. Junction Temperature (T\_J), Different Loads

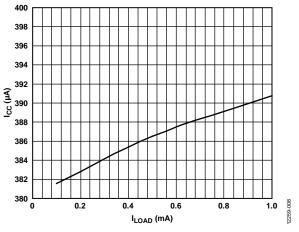

Figure 8. Supply Current (I<sub>CC</sub>) vs. Load Current (I<sub>LOAD</sub>)

Figure 9. Supply Current (Icc) vs. Supply Voltage (Vcc), Different Loads

## ADM1270

12259-014

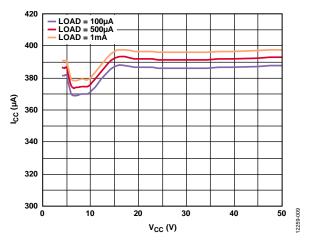

Figure 15. Reference Select Threshold Voltage ( $V_{ISETRSTH}$ ) vs. Temperature,  $V_{IN} = 4 V$

Figure 12. RPFG Voltage (V<sub>RPFG</sub>) vs. Temperature, Different Input Voltages

## **Data Sheet**

Figure 16. Reference Select Threshold Voltage (VISETINSTH) vs. ISET Voltage (VISET), Different Temperatures

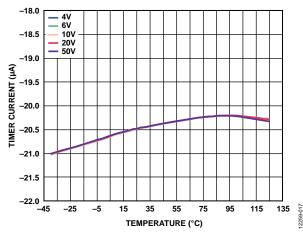

Figure 17. Timer Current vs. Temperature, Different Input Voltages

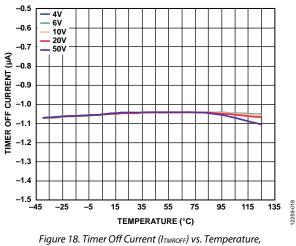

Different Input Voltages

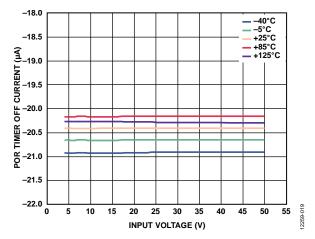

Figure 19. POR Timer Off Current ( $I_{POR}$ ) vs. Input Voltage ( $V_{IN}$ ), Different Temperatures

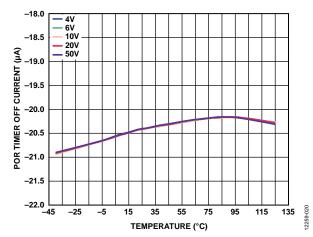

Figure 20. POR Timer Off Current (I<sub>POR</sub>) vs. Temperature, Different Input Voltages

## **Data Sheet**

#### 0.07 -40°C -5°C +25°C +85°C 0.06 +125°C 0.05 (2) 0.04 S<sup>ENSE</sup> 0.03 0.02 0.01 0 12259-028 0.5 2.5 1.0 1.5 2.0 3.0 3.5 0 V<sub>ISET</sub> (V) Figure 28. Sense Voltage (VSENSE) vs. ISET Voltage (VISET), Different Temperatures 50 - 10mV 20mV 30mV 40mV 50mV 60mV 45 40 OC INPUT CURRENT (µA) 35 30 25 20 15 10 5 0 └─ -60 2259-029 100 -40 -20 0 20 40 60 80 120 140 **TEMPERATURE (°C)**

Figure 29. OC Input Current vs. Temperature, Different Sense Voltages (VSENSE)

Figure 30. OC Input Current vs. Sense Voltage (VSENSE), Different Temperatures

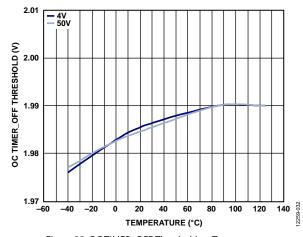

Figure 31. OC TIMER Threshold vs. Temperature, Different Input Voltages

Figure 32. OC TIMER\_OFF Threshold vs. Temperature, Different Input Voltages

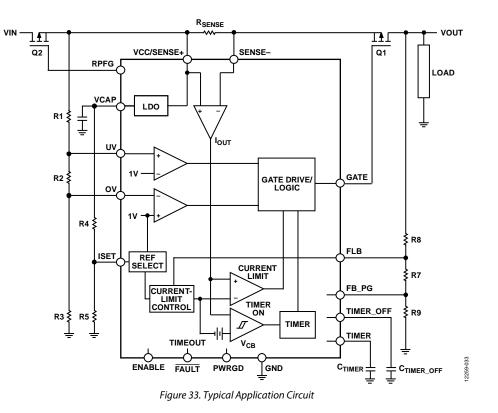

## **TYPICAL APPLICATION CIRCUIT**

## THEORY OF OPERATION

When circuit boards are inserted into a live backplane, discharged supply bypass capacitors draw large transient currents from the backplane power bus as they charge. These transient currents can cause permanent damage to connector pins, as well as voltage dips on the backplane supply that can reset other boards in the system.

The ADM1270 is designed to control the inrush current when powering on the system, allowing a board to be inserted safely into a live backplane by protecting it from excess currents.

The ADM1270 is a current-limiting controller that provides inrush current limiting and overcurrent protection for modular or battery-powered systems. The voltage developed across a sense resistor in the power path is measured with a current sense amplifier via the VCC/SENSE+ and SENSE– pins. A default limit of 50 mV is set, but this limit can be adjusted, if required, using a resistor divider network from the VCAP pin to the ISET pin.

The ADM1270 limits the current through the sense resistor by controlling the gate voltage of an external P-channel FET in the power path, via the GATE pin. The sense voltage and, therefore, the load current is maintained below the preset maximum. The ADM1270 protects the external FET by limiting the time that the FET remains on while the current is at its maximum value. This current-limit time is set by the choice of capacitors

connected to the TIMER pin and the TIMER\_OFF pin. This current-limit time helps to maintain the FET in its SOA.

In addition to the timer function, there is a foldback pin (FLB) that is used to provide additional FET protection. The current limit is linearly reduced by the voltage on the FLB pin, so that for large drain to source voltage ( $V_{DS}$ ) voltage drops, the actual current limit used by the device is lower, again helping to ensure the FET is kept within its SOA.

A minimum voltage clamp ensures that even if the FLB voltage is 0 V, the current is never reduced to zero, which otherwise prevents the device from powering up.

The ADM1270 features OV and UV protection, programmed using external resistor dividers on the UV and OV pins.

A PWRGD signal can be used to indicate when the output supply is greater than a voltage programmed using an external resistor divider on the FB\_PG pin.

To protect the system from a reverse polarity input supply, there is a provision made to control an additional external P-channel FET with the RPFG pin. This feature allows for a low on-resistance, low voltage drop FET to be used in place of a diode to perform the same function, thus saving power losses and improving overall efficiency. The reverse voltage protection FET prevents negative input voltages that can damage the load or the ADM1270.

2259-034

Figure 34. Simplified Functional Block Diagram

### POWERING THE ADM1270

A supply voltage from 4 V to 60 V is required to power the ADM1270 via the VCC/SENSE+ pin. The VCC/SENSE+ pin provides the majority of the bias current for the device; the remainder of the current needed to control the gate drive and to best regulate the gate to source voltage ( $V_{GS}$ ) is supplied by the SENSE- pin.

### **CURRENT SENSE INPUTS**

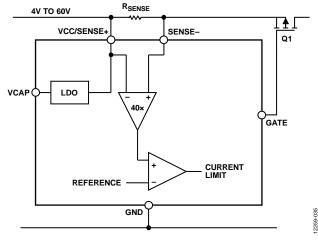

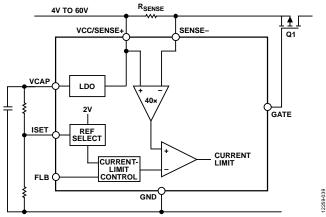

The load current is monitored by measuring the voltage drop across an external current sense resistor,  $R_{SENSE}$  (see Figure 35). An internal current sense amplifier provides a gain of 40 to the voltage drop detected across  $R_{SENSE}$ . The result is compared to an internal reference and is used by the hot swap control logic to detect an overcurrent condition.

Figure 35. Hot Swap Current Sense Amplifier

### **CURRENT-LIMIT REFERENCE**

The current-limit reference voltage determines the load current at which the ADM1270 limits the current during an overcurrent event. This reference voltage is compared to the amplified current sense voltage to determine when the current-limit threshold is reached.

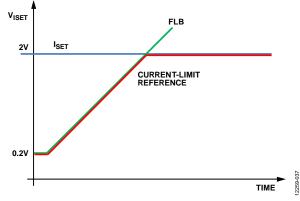

An internal current-limit reference selector block continuously compares the ISET and FLB voltages to determine which voltage is the lowest at any given time; the lowest voltage is used as the current-limit reference. This behavior ensures that the programmed current limit, ISET, is used in normal operation, and that the foldback feature reduces the current limit when required during startup and/or fault conditions.

Figure 36. Current-Limit Reference Selection

The FLB voltage varies during different modes of operation and, therefore, is clamped to a minimum level of 200 mV. This behavior prevents zero current flow due to the current limit being set too low. Figure 37 provides an example of how the FLB and ISET voltages interact during startup as the ADM1270 turns on the FET and charges the load capacitance. Depending on how the foldback feature is configured, the transition point varies to ensure that the FET operates within the correct limits.

Figure 37. Interaction of Foldback (FLB) and ISET Current Limits

## SETTING THE CURRENT LIMIT (ISET)

The maximum current limit is partially determined by selecting a sense resistor to match the current sense voltage limit on the controller for the desired load current. However, as currents become larger, the sense resistor value decreases for a given current sense voltage. Choosing an appropriate current sense resistor can be difficult due to the limited selection of low value resistors. The ADM1270 provides an adjustable current sense voltage limit to handle this issue. The device allows the user to program the required current sense voltage limit from 12.5 mV to 62.5 mV.

## **Data Sheet**

The default value is 50 mV and is achieved by connecting the ISET pin directly to the VCAP pin. This circuit configuration configures the device to use an internal 2 V reference, which results in 50 mV at the sense inputs (see Figure 38).

Figure 38. Fixed 50 mV Current Sense Limit

To program the sense voltage from 12.5 mV to 62.5 mV, an external resistor divider sets the reference voltage on the ISET pin (see Figure 39).

Figure 39. Adjustable 12.5 mV to 62.5 mV Current Sense Limit

The VCAP pin has a 3.6 V internally generated voltage that can set a voltage at the ISET pin. Assuming that  $V_{\text{ISET}}$  equals the voltage on the ISET pin, select the resistor divider values to set the ISET voltage as follows:

$V_{ISET} = V_{SENSE} \times 40$

where  $V_{SENSE}$  is the current sense voltage limit.

The VCAP rail also can be used as the pull-up supply for setting other pins. To guarantee that VCAP meets its accuracy specifications, do not apply a load to the VCAP pin greater than 100  $\mu$ A.

### FOLDBACK

Foldback is a method to actively reduce the current limit as the voltage drop across the FET increases. This technique keeps the power dissipation in the FET at a minimum during power-up, overcurrent, or short-circuit events. It also reduces the need to oversize the FET to accommodate worst-case conditions, resulting in board size and cost savings.

Assuming that the supply voltage remains constant and within tolerance, the ADM1270 detects the voltage drop across the FET by sensing output voltage through a resistor divider. The device, therefore, relies on the principle that the drain of the FET is at the maximum expected supply voltage, and that the magnitude of the output voltage is relative to that of the V<sub>DS</sub> of the FET. Using a resistor divider from the output voltage to the FLB pin, the relationship from V<sub>OUT</sub>, and thus V<sub>DS</sub>, to V<sub>FLB</sub> can be derived.

Design the resistor divider to result in a voltage equal to  $V_{ISET}/2$ when  $V_{OUT}$  falls below the desired level. This voltage must be well below the working tolerance of the supply rail. As  $V_{OUT}$ continues to drop, the current-limit reference follows  $V_{FLB}$ because it is now the lowest voltage input to the current-limit reference selector block, resulting in a reduction of the current limit and, therefore, the regulated load current. To prevent the current from decreasing to zero, a clamp activates when  $V_{FLB}$ reaches 200 mV. The current limit cannot drop below this level.

To ensure that the SOA characteristics of a particular FET are not violated, the minimum current for this clamp varies from design to design. However, the current-limit reference fixes this clamp at 200 mV, which equals 10 mV across the sense resistor. Therefore, the main ISET voltage can be adjusted to adjust the clamp to the required percentage current reduction. For example, if  $V_{ISET}$  equals 1.6 V, set the clamp at 25% of the maximum current.

### TIMER

The TIMER pin handles the timing function with an external capacitor, C<sub>TIMER</sub>. The two TIMER pin comparator thresholds are V<sub>TIMERL</sub> (0.1 V) and V<sub>TIMERH</sub> (2.0 V). There are two timing current sources as well: a 20  $\mu$ A pull-up current and a 1  $\mu$ A pull-down current.

These current and voltage levels, in combination with the user chosen value of  $C_{\text{TIMER}}$ , determine the fault current-limit time and the on-time of the hot swap retry duty cycle. The TIMER pin capacitor value is determined using the following equation:

$$C_{TIMER} = (t_{ON} \times 20 \ \mu A) / V_{TIMERH}$$

where:

*t*<sub>ON</sub> is the time that the FET is allowed to spend in regulation at the current limit.

$V_{TIMERH}$  is the TIMER high threshold.

The choice of FET is based on matching this time with the SOA characteristics of the FET. Foldback can also be used to simplify the selection.

## ADM1270

When the voltage across the sense resistor reaches the circuit breaker trip voltage,  $V_{CB}$ , the 20  $\mu$ A TIMER pull-up current is activated. The ADM1270 begins to regulate the load current at the current limit, initiating a rising voltage ramp on the TIMER pin. If the sense voltage falls below this circuit breaker trip voltage before the TIMER pin reaches  $V_{TIMERH}$ , the 20  $\mu$ A pull-up current is disabled, and the 1  $\mu$ A pull-down current is enabled. If the voltage on the TIMER pin falls below  $V_{TIMERL}$ , the TIMER pin is discharged to GND using a strong pull-down current on the TIMER pin.

However, if the overcurrent condition is continuous and the sense voltage remains above the circuit breaker trip voltage, the 20  $\mu$ A pull-up current remains active, and the FET remains in regulation. This condition allows the TIMER pin to reach V<sub>TIMERH</sub> and to initiate the GATE shutdown, and the FAULT pin is pulled low immediately.

The circuit breaker trip voltage is not the same as the hot swap sense voltage current limit. There is a small circuit breaker offset,  $V_{\text{CBOS}}$ , which causes the timer to start shortly before the current reaches the defined current limit.

In latch-off mode, the TIMER pin is discharged to GND when it reaches the V<sub>TIMERH</sub> threshold. The TIMER\_OFF pin begins to charge up. While the TIMER\_OFF pin is ramping up, the hot swap controller remains off and cannot be turned back on, and the FAULT pin remains low. When the voltage on the TIMER\_OFF pin rises above the V<sub>TMROFFH</sub> threshold, the hot swap controller can be reenabled by toggling the ENABLE pin from high to low and then high again.

### TIMER\_OFF

The TIMER\_OFF pin handles two timing functions with an external capacitor, C<sub>TIMER\_OFF</sub>. There is one TIMER\_OFF pin comparator threshold at V<sub>TMROFFH</sub> (2.0 V). There are two timing current sources, a 20  $\mu$ A pull-up current and a 1  $\mu$ A pull-up current.

These current and voltage levels, in combination with the user chosen value of  $C_{\text{TIMER}\_OFF}$ , determine the initial power-on reset time and also set the fault current-limit off time.

When VCC is connected to the input supply, the internal supply (VCAP) of the ADM1270 must charge up. VCAP starts up and settles in a very short time. When the UVLO threshold voltage is exceeded at VCAP, the device emerges from reset. During this first brief reset period, the GATE and TIMER pins are both held low.

The ADM1270 then proceeds through an initial timing cycle. The TIMER\_OFF pin is pulled high with 20  $\mu$ A. When the TIMER\_OFF pin reaches the V<sub>TMROFFH</sub> threshold (2.0 V), the initial timing cycle is complete. This initial power-on reset duration is determined by the following equation:

$t_{INITIAL} = V_{TMROFFH} \times (C_{TIMER_OFF}/20 \ \mu A)$

For example, a 100 nF capacitor results in a delay of approximately 10 ms. If the UV and OV inputs indicate that VCC is within the

defined window of operation when the initial timing cycle terminates, the device is ready to start a hot swap operation.

At the completion of this initial power-on reset cycle, the TIMER\_OFF pin is ready to perform a second function. When the voltage at the TIMER pin exceeds the fault current-limit time threshold voltage of  $V_{\text{TIMERH}}$  (2.0 V), the 1  $\mu$ A pull-up current is activated on TIMER\_OFF, and C<sub>TIMER\_OFF</sub> begins to charge initiating a voltage ramp on the TIMER\_OFF pin. When the TIMER\_OFF pin reaches  $V_{\text{TMROFFH}}$ , the TIMER\_OFF fault current-limit off time is complete.

This fault current-limit off time is determined by the following equation:

$t_{TIMER_OFF} = V_{TMROFFH} \times (C_{TIMER_OFF}/1 \,\mu A)$

For example, a 100 nF capacitor results in an off time of approximately 200 ms from the time that TIMER exceeds  $V_{\text{TIMERH}}$  to the time that TIMER\_OFF reaches  $V_{\text{TMROFFH}}$ .

## HOT SWAP RETRY DUTY CYCLE

The ADM1270 turns off the FET after an overcurrent fault and then uses the capacitor on the TIMER\_OFF pin to generate a delay before automatically retrying the hot swap operation. To configure the ADM1270 for automatic retry mode, tie the FAULT pin to the ENABLE pin. Note that a pull-up resistor to VCAP is required on the FAULT pin.

When an overcurrent fault occurs, the capacitor on the TIMER pin charges with a 20  $\mu$ A pull-up current. When the TIMER pin reaches V<sub>TIMERH</sub> (2.0 V), the GATE pin is pulled high, turning off the FET. When the FAULT pin is tied to the ENABLE pin for automatic retry mode, the TIMER\_OFF pin begins to charge with a 1  $\mu$ A current source. When the TIMER\_OFF pin reaches V<sub>TMROFFH</sub> (2.0 V), the ADM1270 automatically restarts the hot swap operation.

The automatic retry duty cycle is set by the ratio of 1  $\mu$ A/20  $\mu$ A and the ratio of C<sub>TIMER</sub>/C<sub>TIMER</sub>OFF. The retry duty cycle is set by the following equation:

$Duty\_Cycle = (C_{TIMER} \times 1 \ \mu A)/(C_{TIMER\_OFF} \times 20 \ \mu A)$

The value of the CTIMER and CTIMER\_OFF capacitors determine the on and off time of this cycle, which are calculated as follows:

$t_{ON} = V_{TIMERH} \times (C_{TIMER}/20 \ \mu \text{A})$

$t_{OFF} = V_{TMROFFH} \times (C_{TIMER_OFF}/1 \,\mu A)$

A 100 nF capacitor on the TIMER pin gives an on time of 10 ms. A 100 nF capacitor on the TIMER\_OFF pin gives an off time of 200 ms. The device retries continuously in this manner and can be disabled manually by holding the ENABLE pin low, or by disconnecting the FAULT pin. To prevent thermal stress in the FET, a capacitor on the TIMER\_OFF pin can be used to extend the retry time to any desired level.

### **GATE AND RPFG CLAMPS**

The circuits driving the GATE and RPFG pins are clamped to less than 14 V below the VCC/SENSE+ pin. These clamps ensure that the maximum  $V_{GS}$  rating of the external FETs is not exceeded.

The reverse protection FET gate pin (RPFG) drives the gate of an external PMOSFET. This PMOSFET, Q2, provides reverse polarity protection to the ADM1270 and the system being powered. If the VCC and GND pins have been reverse connected (that is, where power is actually applied to GND), VCC is negative with respect to the system ground. In this condition, Q2 prevents current from flowing in the reverse direction because the gate of Q2 is held at GND, and Q2 is off. V<sub>OUT</sub> is not pulled below GND, and the system is protected against a reverse polarity connection.

In the typical case where power is applied to VCC, the gate is still pulled down and allows the FET Q2 to turn on and conduct current in the forward direction. Operating Q2 in this way provides a low on-resistance, low voltage drop compared to a diode for reverse polarity protection, giving the system higher efficiency and more headroom for operation. Figure 33 shows the connection of Q2 and RPFG for proper operation.

### FAST RESPONSE TO SEVERE OVERCURRENT

The ADM1270 includes a separate, high bandwidth, current sense amplifier to detect a severe overcurrent that is indicative of a short circuit. The fast response time allows the ADM1270 to handle events of this type that could otherwise cause catastrophic damage if not detected and dealt with very quickly. The fast response circuit ensures that the ADM1270 can detect an overcurrent event of approximately 200% of the normal current limit and control the current within approximately 2 µs.

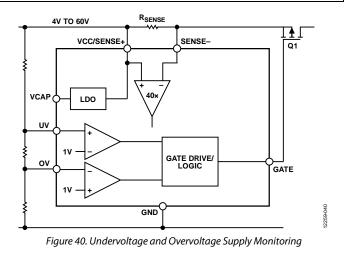

### UNDERVOLTAGE AND OVERVOLTAGE

The ADM1270 monitors the supply voltage for UV and OV conditions. The UV and OV pins are connected to the inputs of the voltage comparators and compared to an internal 1 V voltage reference.

Figure 40 illustrates the voltage monitoring input connections. An external resistor network divides the supply voltage for monitoring. An undervoltage event is detected when the voltage connected to the UV pin falls below 1 V, and the FET is turned off using the 10 mA pull-up current. Similarly, when an overvoltage event occurs and the voltage on the OV pin exceeds 1 V, the FET is turned off using the 10 mA pull-up current.

### **ENABLE INPUT**

The ADM1270 provides a dedicated ENABLE digital input pin. The ENABLE pin allows the ADM1270 to remain off by using a hardware signal, even when the voltage on the UV pin is greater than 1.0 V, and the voltage on the OV pin is less than 1.0 V. Although the UV pin can be used to provide a digital enable signal, using the ENABLE pin for this purpose keeps the ability of the UV pin free to monitor undervoltage conditions.

In addition to the conditions for the UV and OV pins, the ADM1270 ENABLE input pin must be high for the device to begin a power-up sequence.

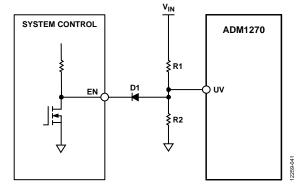

A similar function can be achieved using the UV pin directly. Alternatively, if the UV divider function is still required, the configuration shown in Figure 41 can be used.

Figure 41. Using the UV Pin as an Enable

Diode D1 prevents the external driver pull-up resistor from affecting the UV threshold. Select Diode D1 using the following criteria:

$(V_F \times D1) + (V_{OL} \times EN) << 1.0 V (I_F = V_{IN}/R1)$

Ensure that the EN sink current does not exceed the specified  $V_{\text{OL}}$  value. If the open-drain device has no pull-up, the diode is not required.

### **POWER GOOD**

The power-good (PWRGD) output can be used to indicate whether the output voltage exceeds a user defined threshold and can, therefore, be considered good. The PWRGD output is set by a resistor divider connected to the FB\_PG pin (see Figure 42).

Figure 42. Generation of PWRGD Signal

When the voltage at the FB\_PG pin exceeds the 1 V threshold (indicating that the output voltage has risen), the open-drain pull-down current is disabled, allowing PWRGD to be pulled high. The PWRGD pin is an open-drain output that pulls low when the voltage at the FB\_PG pin is lower than the 1 V threshold minus the hysteresis (power bad). Hysteresis on the FB\_PG pin is fixed at 30 mV. PWRGD is guaranteed to be in a valid state for  $V_{CC} \ge 1.7$  V.

Calculate the power-good threshold using the following equation:

$$V_{PWRGD} = 1 \text{ V} \times (1 + RPG1/RPG2)$$

where:

*RPG1* is the resistance from V<sub>OUT</sub> to FB\_PG. *RPG2* is the resistance from FB\_PG to GND.

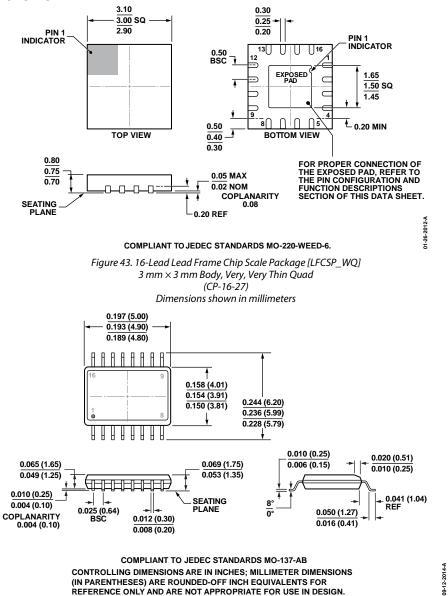

## **OUTLINE DIMENSIONS**

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 44. 16-Lead Body, Shrink Small Outline Package [QSOP] (RQ-16) Dimensions shown in inches (and millimeters)

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option | Brand Code |

|--------------------|-------------------|---------------------------------------------------|----------------|------------|

| ADM1270ACPZ-R2     | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]  | CP-16-27       | LNQ        |

| ADM1270ACPZ-R7     | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]  | CP-16-27       | LNQ        |

| ADM1270ARQZ        | -40°C to +125°C   | 16-Lead Body, Shrink Small Outline Package [QSOP] | RQ-16          |            |

| ADM1270ARQZ-R7     | -40°C to +125°C   | 16-Lead Body, Shrink Small Outline Package [QSOP] | RQ-16          |            |

| ADM1270CP-EVALZ    |                   | Evaluation Board for 16-Lead LFCSP_WQ             |                |            |

| ADM1270RQ-EVALZ    |                   | Evaluation Board for 16-Lead QSOP                 |                |            |

<sup>1</sup> Z = RoHS Compliant Part.

©2014–2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D12259-0-4/16(A)

www.analog.com

Rev. A | Page 21 of 21

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Hot Swap Voltage Controllers category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

LTC4227CUFD-4#PBF LTC4212IMS MAX16141ADF/V+ ADM1075-2ARUZ-RL7 LM5067MW-1/NOPB MAX5969BETB+T MIC22700YML-TR LT1640LIS8#PBF LTC4217CDHC-12#PBF LT4294HDD#PBF LTC4253CGN#PBF LTC4260IGN#PBF LTC4211CMS8#PBF LTC4230CGN#PBF LTC4214MS-1#PBF LTC4216IMS#PBF LTC4212IMS#PBF LTC4260CGN#PBF LTC4227CGN-2#PBF LTC4244IGN#PBF LTC4212CMS#PBF LT4250HCN8#PBF ADM1276-3ACPZ-RL LTC4260IUD-1#PBF ADM1075-2ACPZ ADM1075-1ACPZ ADM1073ARUZ ADM1073ARUZ-REEL7 ADM1075-1ARUZ ADM1075-2ARUZ ADM1170-1AUJZ-RL7 ADM1171-2AUJZ-RL7 ADM1172-1AUJZ-RL7 ADM1172-2AUJZ-RL7 ADM1177-1ARMZ-R7 ADM1177-2ARMZ-R7 ADM1275-3ARQZ ADM1275-1ARQZ ADM1275-3ARQZ-R7 ADM1276-3ACPZ ADM4210-1AUJZ-RL7 ADM1275-2ARQZ ADM1070ARTZ-REEL7 LTC1645IS#PBF LTC1645CS#PBF LTC4251BIS6-1#TRMPBF LTC1422IS8#PBF LT1641CS8#PBF LT1640HCS8#PBF LT1640HIS8#PBF